# **COMPUTER DESIGN**

#### THE MAGAZINE OF MODERN DIGITAL ELECTRONICS

NOVEMBER 1967

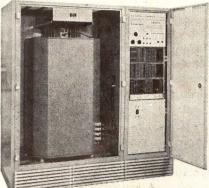

ICM-500 I/C CORE MEMOR New I/C 500-600 nsec Memory System ...

... Stores 1/4 million bits in single 5-1/4" high unit, features MTBF of 12 years under normal 40-hour week operation

Now you can get the new  $\mu$ -STORE ICM-500 in standard systems: 600 nanoseonds full cycle time. Special systems: cycle times as low as 500 nanoseconds. Up to 16,384 words with 54 bits/word; or up to 4096 words with 72 bits/word. (Over 3/4 of a million bits in little more than 15" of vertical rack space — including power supply). You also get I/C construction for all major functions including X-Y current drivers plus a choice of mechanical packaging.

Get the full story. And take advantage of our eight years' experience in solving core memory problems. Write today for our new brochure. Honeywell, Computer Control Division, Old Connecticut Path, Framingham, Massachusetts 01701.

\*Patent applied for.

CIRCLE NO. 1 ON INQUIRY CARD

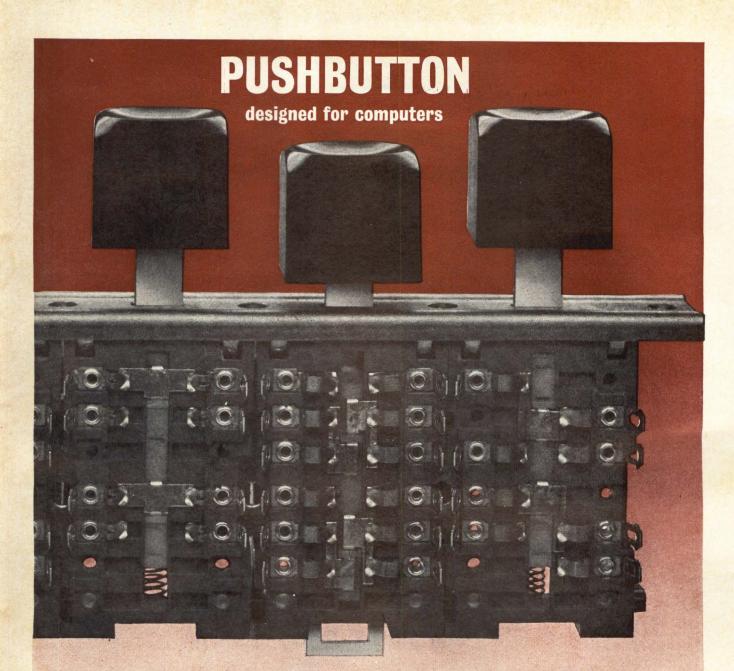

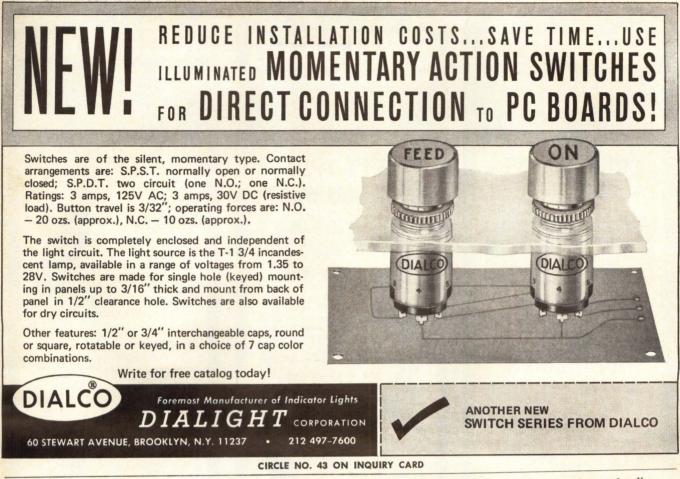

Computer manufacturers no longer have to "make-do" with a pushbutton switch designed for non-computer use. These new Oak switches give you highest reliability-with double-wiping clips locked firmly into recessed barriers for high voltage breakdown characteristics, and a Kel-F slider insulator for smooth action. Response is fast ... with stroke as short as 5/32" ... and operating pressure is light and consistent from button to button. Maximum circuitry available, 4 PDT. Inboard or outboard mounting; molded stator case has interlocking lugs for firmness... almost unlimited stacking. Many options available: Normal interlock, push-to-latch, push-to-release, momentary...or any combination of these. Also multiple latch bar arrangements for any number of buttons up to 12 buttons maximum. (Example: 4 groups of 3 buttons on a 12-button bank.) Pushbuttons are 3/4" on center with 23/4" maximum push rod length. Rated 0.5 amp. @ 115 vac or 1 amp @ 28 vdc. For full details, write for Bulletin CD-280.

DAK MANUFACTURING CO.

CRYSTAL LAKE, ILLINOIS 60014 Phone: 815-459-5000 TWX: 910-634-3353 CABLE: OAKMANCO And, for other computer applications Oak has the 184 Lever Switch...small, molded diallyl phthalate stator, long life, more clips per stator, low electrical leakage, no extra cost. Many options. For full details.

write for Bulletin SP 240.

CIRCLE NO. 25 ON INQUIRY CARD

#### All time winner, move overthe new PDP-8/I computer is here

The integrated circuit PDP-8/I is a brand new computer, but behind it are the two most successful small computers ever built. Over 1,000 PDP-8 systems are already installed — an all time high for real-time, on-line small general purpose machines. Nearly 1,000 PDP-8/S computers are installed — all sold and delivered within the last 15 months. Built into instrumentation. On-line in process control.

e en Kith Kith Man

So, PDP-8/I starts with a history and goes on from there. It has all the features of the PDP-8 plus a new ease of interfacing, expanded software and new options. It is more compact. PDP-8/I has a faster multiply-divide option (multiply 6.0, divide 6.5 microseconds). Its standard 1.5 microsecond 4K core memory expands to 32K (first extra 4K plugs into the basic configuration without further interfacing). PDP-8/I comes as a stand-alone console or mounted in a standard 19-inch rack. The processor is prewired so that it will accommodate a high-speed paper tape reader and punch, a 100 card-per-minute reader, an incremental plotter, and a scope display also without further interface.

And software. The same proven software that runs the PDP-8, drives the PDP-8/I. Auto-indexing. MACRO. FORTRAN. On-line editing and debugging. But that is not all. New systems software is available which takes full advantage of 32K or more of DECdisk or DECtape memory. Thousands of the most active computer users in the world exchange PDP-8 programs and techniques.

Peripherals that go with the PDP-8 and PDP-8/S go with the PDP-8/I. Hundreds of logic-compatible modules make interfacing easy. Peripherals are field-installed by an applications engineering and field service group second to none.

And the crusher. PDP-8/I sells for \$12,800 complete. Quantity discounts reduce that price. Deliveries in the spring. PDP-8 and PDP-8/S available now. Write for brochure. We'll throw in our new Small Computer Handbook free.

DIGITAL EQUIPMENT CORPORATION, Maynard, Massachusetts 01754. Telephone: (617) 897-8821 • Cambridge, Mass. • New Haven • Washington, D. C. • Parsippany, N. J. • Princeton, N. J. • Rochester, N. Y. • Long Island, N. Y. • Philadelphia • Huntsville • Pittsburgh • Chicago • Denver • Ann Arbor • Houston • Albuquerque • Los Angeles • Palo Alto • Seattle • Carleton Place and Toronto, Ont. • Montreal, Quebec • Reading, England • Walkden Manchester, England • Paris, France • Munich and Cologne, Germany • Noordwkerhoot, Holland • Sydney and West Perth, Australia • Modules distributed also through Allied Radio

Publisher and Editor ROBERT BROTHERSTON

Editorial Advisers RICHARD AHRONS ELI ANFENGER JAMES R. BRIGHT BERNARD M. GORDON WALDRON S. MacDONALD ROBERT S. SENATOR HAROLD H. SEWARD

> Contributing Editors T. PAUL BOTHWELL A. S. BUCHMAN RUDOLPH J. KADLEC ROBERT P. FORAN WALTER A. LEVY H. S. MIILLER RICHARD PETTERSEN MADELINE SULLIVAN

Washington Editor HAROLD V. SEMLING, JR.

> Art Director JAMES FLORA

Production Manager TERRY ARMENTI

Tech. Illus. JOHN BROTHERSTON

Editorial Ass't. PRISCILLA HANLON

> Adv. Prod. JOAN WASIUK

Circ. Mgr. ALMA BROTHERSTON

Vice Pres.-Sales LINDSAY H. CALDWELL

Editorial & Executive Offices Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1967 by Computer Design Publishing Corporation. Accepted as controlled circulation publication at Post Office at Boston, Massachusetts. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS — FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Winchester, Mass. 01890. Subscription rate to nonqualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 32,000

# COMPUTER DESIGN

THE MAGAZINE OF MODERN DIGITAL ELECTRONICS

#### FEATURES

#### **26** DIGITAL DATA TRANSMISSION

This article describes a range of digital data transmission that will permit synchronous transmission and operation.

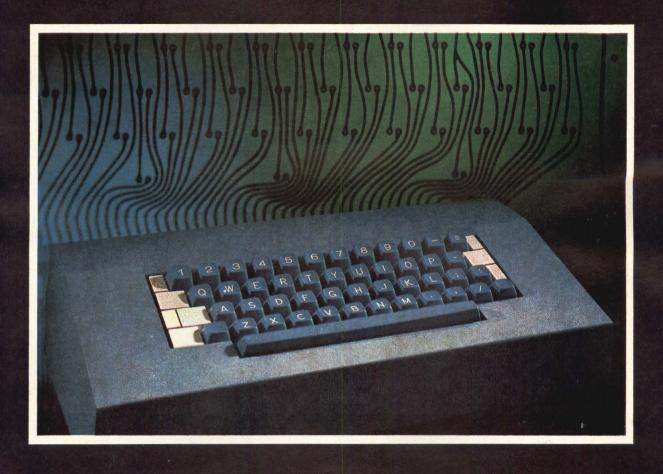

#### **32** ELECTRONIC KEYBOARD

A novel approach to keyboard code generation results in a keyboard design that eliminates coding errors in the circuit.

#### 34 IBM PROPOSES TRIPLE-REDUNDANT AEROSPACE COMPUTER

A computer configuration is described that would provide high mission availability, extremely high critical phase reliability and large data management and multiprocessing capability.

#### **38** ELECTRO-MECHANICAL DIGITAL TRANSDUCER RETAINS DATA UNTIL NEW SAMPLE IS TAKEN

Non-electronic, one-step, subsystem converts an analog function to a parallel, memorized, non-ambiguous and electrically expressed set of digits.

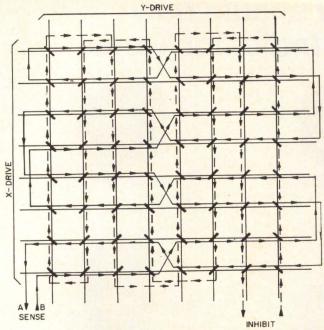

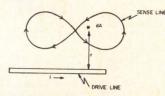

#### 42 A FRESH LOOK AT COINCIDENT CURRENT CORE MEMORIES

Certain advantages of 3-D and a new sense/digit circuit design for three-wire coincident current memories are discussed.

#### 46 NOISE PROBLEMS IN FERRITE CORE COINCIDENT CURRENT MEMORIES

This article describes sources of sense line noise existing within the memory stack.

#### 52 THE DESIGNER - THE SYSTEM AND THE "IC-MIX"

Examples of gains in system size, reliability and cost through intelligent selection of IC's for specific tasks.

#### 54 COMPUTER DESIGN — SOME PITFALLS TO AVOID

This article reviews and reflects on some engineering decisions of historical interest to the computer designer.

#### DEPARTMENTS

- 6 CD COMMENTARY

- 10 DC OUTPUT

- **16 INDUSTRY NEWS**

- 58 NEW PRODUCTS

- 74 NEW LITERATURE

- **80** ADVERTISERS' INDEX

Reader subscription cards ...... opposite Page 1 Reader inquiry cards ...... opposite Page 80

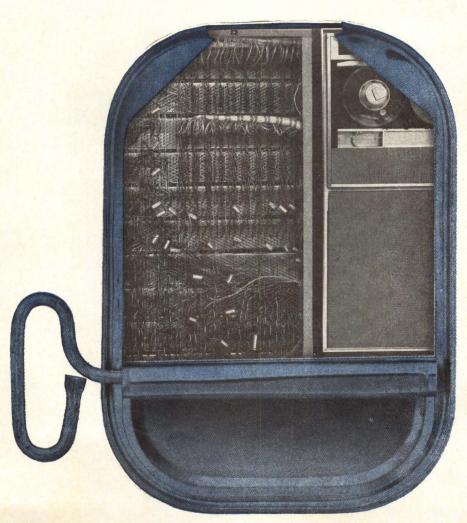

# What does the CD-65 have that all other 2½D memory systems don't?

MORE STRINGENT DESIGN CRITERIA + HIGHER RELIABILITY + GREATER USER VERSATILITY. The CD-65 is designed with the demanding user in mind. Operating margins in this unit are significantly greater than accepted industry standards. Mechanical packaging of key circuits and magnetics in the CD-65 provides a system organization easily adapted to custom application. All circuits are worst case designed and are verified by customer examination. packaging concept, the CD-65, with a 650 nanosecond cycle time, permits faster speeds and definite economies for larger word systems. The CD-65 is available in sizes from 8K to 65K words each containing from 16 to 144 bits. Speaking of words, may we have some with you? We'd like to tell you more about the CD-65. For more information, write: Lockheed Electronics Company, Memory Products, 6201 East Randolph Street, Los Angeles, Calif. 90022. Or phone (213) 722-6810.

CIRCLE NO. 4 ON INQUIRY CARD

gh

# the new price the new name in high-performance, low-priced computers

This new computer is the easiest to program and interface of all high-speed computers. It has 16-bit words, 4K expandable memory, 2 microsecond cycle time, plug-in I/O cards, multichannel priority interrupt, relocatable software and both FORTRAN and ALGOL compilers. Plug-in options including direct memory access and hardware multiply and divide are available. Peripherals such as high-speed disc memory and magnetic tape are standard. The price, with 4K memory and ASR-33 teletype: \$16,500. To find out how easy the 2115A is to use-and its big brother, the 2116A, write to Hewlett-Packard, Palo Alto, California 94304; Europe: 54 Route des Acacias, Geneva. 06714

CIRCLE NO. 5 ON INQUIRY CARD

#### commentary

Comments and opinions on topics of current interest to digital design engineering personnel. A monthly column organized and prepared under the direction of **T. PAUL BOTHWELL, Contributing Editor.**

# Effect of Microelectronics On Error Diagnosis

**Richard D. Eldred**

#### Hardware Errors Hard To Diagnose

The problems of diagnosis of hardware errors in computers is one which has never really been effectively solved, particularly in those portions of computers that are primarily electronic. Effective, albeit tedious, methods have been developed for producing test programs that will, if painstakingly written, guarantee the detection of an error if it exists. But the problem of producing a program to locate the error, once detected, has not really been satisfactorily solved. This is particularly true in the central processor where the ratio of control logic to data logic is far greater than in data-oriented areas such as memories and input/output units.

The author of this month's CD Commentary, Richard D. Eldred is the Manager of Equipment Analysis Dept. within the Programming Activity at Honeywell, Computer Control Div. He is responsible for test routines, design automation programs, and approving equipment specifications for programming. The basic problem has been that the test programmer has not had access to the input and output of individual logical functions. He cannot present a test pattern to one or a small number of logical functions and test the output immediately of that small group of functions. Rather, he must first present an input pattern to a very large logical array and then check the output at the end of the array. A recent attempt has been made to do immediate testing, but the total effort involved might be more than most organizations would care to muster, and, as of the moment, the returns are not in as to its degree of success.

Another problem: the field engineer is given increasingly less time for preventive maintenance, and when an error does occur during a customer run, he is under great pressure to get the computer back into condition almost immediately. If the diagnostic procedure is too cumbersome or complicated or time-consuming, he may discard it and resort to a more bushwhacking approach.

#### Neanderthal Days, Here We Come

If one looks into the future and believes, to whatever degree one wishes, the form of the final implementation of computers using large-scale-integration techniques, one can with a fair degree of seriousness envision a dramatic effect on the diagnostic procedures to be followed, and indeed, a possible return to the Neanderthal days of computers.

The problem of diagnosis obviously revolves around what is the largest replaceable module, since this is the level to which one must diagnose the error. In the beginning of time, the replaceable module, on the average, contained one logical function. This has moved through the five or ten functions per module area and in some recent machines is getting into the fifty to a hundred area. The hypothetical limit is, of course, one module equals one central processor. Even though this may be unrealistic, it should be considered for purposes of argument, since it may be the only case using present methods that will produce a major breakthrough in error diagnosis.

# Does your present custom power supply give you...

70% to 90% efficiency?

Instant fault repair by plug-in module replacement? Add-on power capability by using more modules? Ability to handle full load steps while maintaining out put in regulation band?

# **New Omnimod does!**

Omnimod power control module.

Omnimod control amplifier.

OMNIMOD gives you all these features—and more—and at a lower price! Want to know more?

OMNIMOD is a dc to dc converter using transistors in a CONSTANT PULSE WIDTH, variable repetition rate switching mode to regulate output voltage or current. Two small plug-in units make-up the OMNIMOD concept—a power control module and a control amplifier.

Output can be regulated between  $\pm 2$  and  $\pm 60$  dc at up to 20 amperes using the OMNIMOD family of modules WITHOUT MODIFICATION OR ADJUSTMENT. Higher current ratings are obtained by paralleling power control modules.

Any number of power controller modules can be controlled by one amplifier. OMNIMOD has a current limiting parameter, over voltage protection, voltage sequencing, and remote sensing.

To design a custom power supply, one must simply

1. design one input power converter to change unregulated line ac power to unregulated dc power

2. select the number of plug-in OMNIMOD power control modules to supply the power needed for each output

**3.** package these elements with filter capacitors and a plug-in amplifier module for each output

All the power used by every element in a typical data processing system could be supplied by custom power supplies constructed with interchangeable OMNIMOD modules.

Isn't this enough to consider OMNIMOD for your custom requirement? We will design an OMNIMOD custom power supply to your specs, or will help you design your own system using our plug-in OMNIMOD modules.

Write for the complete story. We'll have it to you within 48 hours.

EXTRA SERVICE TO THE DATA PROCESSING INDUSTRY

4838 West 35th Street, St. Louis Park, Minnesota 55416 • 612/920-6444 CIRCLE NO. 6 ON INQUIRY CARD

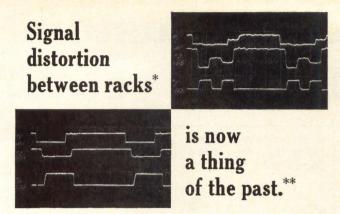

MONITOR offers a new line receiver card which terminates long transmission lines in their characteristic impedance for higher frequencies. Regardless of transmission line length, you can now have pulses as clean at the destination as they were when transmitted. You get four line receivers on one L-57 card.

The L-57 is just one of over 140 MONILOGIC<sup>TM</sup> IC cards, in both DTL and TTL logic, all completely compatible. For more information write to us.

\*Scope photo shows (top) transmitter output into 40-foot twisted pair; (middle) output of line: (bottom) output of gate. Reflections return to transmitter output, produce distortion in line, erroneous pulses at gate output. \*\*With L-57 Line Receiver terminating same line, reflections are eliminated. Transmitter output, line output, gate output are all clean, undistorted, and correct.

CIRCLE NO. 7 ON INQUIRY CARD

#### DIGITAL COMMUNICATIONS SYSTEMS

RADIATION INCORPORATED's expansion into store-and-forward message switching systems presents excellent opportunity for qualified engineers to contribute original ideas and establish a recognized reputation within a professional atmosphere.

#### MESSAGE SWITCHING SYSTEM DESIGNER

Senior level communication system designer with primary emphasis in the design and analysis of store-and-forward message switching systems. Must be familiar with processor requirements, programming, military message traffic procedures and existing networks such as AUTODIN.

#### PROJECT MANAGER

Senior level project manager capable of organizing and managing the design, fabrication, test and installation of message switching systems. Must have a technical background in the communication field, but primary responsibility will be in the project management area. Must be familiar with methods of cost and schedule control.

Want to explore the challenge? Then forward a resume in confidence to:

An Equal Opportunity Employer.

One would think that the more logical functions one can put on a replaceable module and therefore the fewer number of replaceable modules in a computer, the easier the job becomes for the diagnostic programmer to indicate the module that contains the fault, once detected. Unless, however, there has been a strong attempt on the part of the logical designer to partition his logic in a manner that easily allows program access to prime inputs and outputs of each replaceable module, there is no advantage whatsoever to the diagnostic programmer. If there is no strong relationship between the logic on a module and its function in the operation of the computer — such that direct programmable access is provided to prime inputs and outputs either by natural implication of the design or by fairly simple additional circuitry - diagnosis must still be attempted at the gate level. Then, in essence, it must work backwards to determine which replaceable module contains the faulty gate. This is true even to the somewhat ridiculous point where the processor consists of two modules. The problem is not really solved until the extreme case of one module equals one processor is reached, in which case, only a good test or error detection program is needed and the diagnosis consists of replacing the processor.

#### Whatever Happened To Diagnostic Programmers?

Since I, at least, have little faith in logic designers directing their efforts towards partitioning logic to aid maintainability, other than by company dictum, the chances of large-scale integration helping the diagnostic programmer appear slim. However, if there is a strong effort made towards reducing the number of module types at the same time that more and more components are placed on a module, then it appears that the only problam the diagnostic programmer will have is what he is going to do with his leisure time. If the number of module types becomes small and the total number of modules per processor becomes small, hopefully in the 200 or less area, then the problem is reduced to the level of an untrained homeowner fixing his TV set. Starting in the upper left hand corner he systematically replaces or tests each tube until the set works or he hits the bad tube. Providing a good error-detection program exists, and this can be produced presently, the field engineer can do exactly the same thing. If module types are kept few enough so that backup for each type can be kept on hand, then the replacement method can be used. Since the amount of logic on a module will be large, the test of an individual module obviously can become a problem in itself.

The point, then, is that the module replacement method of error diagnosis which was practiced in the early years of commercial computers — primarily due to customer pressure rather than its incidence of success — may become the recommended procedure for error diagnosis in the future, thereby solving the diagnostic programmer's problem by eliminating it and him.

Skill requirements for computer manufacturing have been examined by the U. S. Department of Labor. It found that white collar workers make up half of the employment in plants manufacturing electronic computers and about 1 worker in 4 is in a position which usually requires a college degree or its equivalent in experiences. Performance or management of R & D was the primary function of about 60 percent of the scientists and engineers. Labor breaks down the 24.7% of scientists, engineers, and related technicians as follows: engineers 13.7%, mathematicians 3.4%, chemists .4%, physicists .3%, electronic and electrical technicians 4.5%, draftsmen 1.8%, and other technicians .6%. The data refer to 1966.

#### .........................

Computer aided predictions and projections of election results are not now misleading the public, the Senate Commerce Committee has concluded. The Senate group expressed satisfaction in the way networks and broadcasters are taking appropriate steps to clearly label voting projections and predictions, and there is no immediate emergency and no qualified experience to predicate a change in the present system at this time.

#### ......

The Advisory Commission in Intergovernmental Relations would be authorized to study the feasibility of a computer system to help State and local governments participate more effectively in federally assisted programs under a proposal in Congress sponsored by Sen. Edward Kennedy (D. Mass.). The computer system would, Sen. Kennedy told the Senate, further provide Congress and the President with a better measure of State and local needs and performances under these programs. The system would make use of ADP equipment and other forms of advanced information technology to serve our States and localities. Sen. Kennedy said he had "long been impressed by the enormous potential of computer and information retrieval technology, and its possible application to the development of an intergovernmental information system."

#### ......

It is imperative that we begin now to plan for the great technological revolution which is almost upon us, Sen. Howard H. Baker, Jr. (R. Tenn.) told the Washington meeting of the Association for Computing Machinery. He urged the creation of a Select Committee of the U. S. Senate for Technology and Human Environment. According to Sen. Baker "we lack in the Senate, in Congress, in the Executive Branch, and among our State and local governments . . . a mechanism for inquiring into the broad impact of science and technology on man's thinking, his health, work, living habits and individual security over the next fifty years."

#### .....

License applications for electronic computers, data processing machines and peripherals valued at \$4 million were approved by the U. S. Department of Commerce for export to Eastern European countries during the second quarter of 1967. They were sent principally to Poland, East Germany, and Czechoslovakia.

#### .....

Computer shipments advanced during the first half of 1967 at a rate nearly double that registered in each half of last year, the Commerce Department reports. "Strong demand for versatile, general-purpose computers in foreign industrialized markets largely reflects the efforts of these countries to modernize their managerial methods in many phases of industrial, commercial, governmental, and scientific operations," according to Commerce. They add, "this country's computer industry offers machines with superior capabilities for high-speed calculations and data transfer and with larger data storage capacities."

#### .....

The U. S. Department of Commerce believes American manufacturers should find good business opportunities in Britain for desk-top computers and calculators; datalogging devices and other data-gathering equipment; liquid scintillators; x-y plotters; digital voltmeters; visual output devices, and special output printers.

#### \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

A speedy new IBM 9020 computer is going into operation at the Federal Aviation Administration's Cleveland Air Route Traffic Control Center (ARTCC), permitting more expeditious handling of the increasing number of aircraft in the busy New York-Chicago air corridor. The Cleveland installation's computer is the first to become operational in an FAA center. The agency eventually plans to use this equipment as the central computer complex in all of its ARTCCs. It is a key component in the semi-automated National Airspace System now being developed. Capable of making up to 200,000 calculations a second, the IBM 9020 can

# If you think your system can't afford computer power, take a look at the new DATA 620/i

Data 620/i was designed from scratch as a powerful systems computer. That's why it so efficiently solves problems previously considered too difficult or expensive for computer solution. Data 620/i has a bigger instruction set, one-half the components, and costs less than any computer in its class.

Data 620/i has speed – 1.8 microseconds cycle time, arithmetic power – long 16 or 18 bit words and 4K-32K word memories, control and I/O facilities, multilevel priority interrupts, and field-proven software.

Data 620/i is extremely compact, requiring only 10" of 19" rack space, and comes at an even more compact price, with a 4K 16-bit memory and an ASR 33 Teletypewriter. Write for our new Data 620/i brochure full of facts and figures.

from varian data machines

Warian/DATA MACHINES

a varian subsidiary

varian data machines

# A LONG STRAIGHT LINE...

# A Thin Straight Line...

of uniform luminous and infrared energy, perfectly aligned, to energize a series of photosensors this is what the Chicago Miniature Straight Line and Thin Line Lamps offer you.

The need for grouping several miniature lamps together with the attendant packaging and heat dissipation problems is eliminated.

Straight Line Lamps are available in lengths to 10 inches— Thin Line Lamps are available with or without reflector, in lengths for punch card or tape readout devices. Their small diameter enables mounting in close proximity for compact packaging.

This is just another demonstration of Chicago Miniature's unique capacity for designing that special lamp to fit the need.

For complete information, write for Catalog No. CMT-2. Lamps shown approx. 34 size.

CHICAGO MINIATURE 🌱 LAMP WORKS

4433 Ravenswood Ave., Chicago, Illinois 60640

CIRCLE NO. 10 ON INQUIRY CARD

perform some calculations 500 times faster than the equipment it replaces. As currently configured, the new computer can process over 500 flight plans an hour, and this can be expanded as necessary to keep pace with traffic increases. Initially, the computer will be used to relieve controllers of routine clerical and coordination duties such as processing flight data, calculating flight progress and relaying flight plan information. Eventually, as automation of the National Airspace System progresses, even more of the routine, time-consuming clerical flight DP tasks will be accomplished by the computer. It also will be used to detect potentially hazardous traffic conditions and suggest remedial controller actions.

#### \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Computer safety units might eliminate mid-air collisions. The Federal Aviation Administration has before it a plan for an airborne collision avoidance system. Basically, the system, costing \$30,000 to \$50,000 a unit would work like this: Each plane would carry a special digital computer, transmitting and receiving equipment, antennas, and a timekeeping device synchronized to world observatory standards. The planes, one at a time, would send out electronic signals lasting a fraction of a second while all other planes in the area listened. The time taken to complete one such count-off, called an epoch, would be about three seconds, during which as many as 2000 planes would send their positions to each other. Transmission times for each plane would be fixed and known by the computers, which would figure the time between when a signal was sent and when it was received. The computers would use the apparent time difference to calculate an approaching plane's altitude and the rate at which it was drawing closer. When two planes were 60 seconds apart, their pilots would be alerted about the situation, and 20 seconds later, the computers would direct the pilots to maneuver higher or lower to avoid one another.

#### .....

The National Agricultural Library has asked Control Data Corp. to convert 5,000 herbicide records into machine readable form. CD will have responsibility for modification of the Pesticides Information Center computer programs to accommodate the informational requirements of the Agricultural Research Service in the area of herbicides.

#### .....

A two-year program for indexing finding aids to archival and manuscript materials by computer is underway at the National Archives and Records Service, a part of the General Services Administration. It is hoped the project will make a significant contribution to the solution of a growing problem in the control of basic research materials. The project calls for major modification and development of existing computer indexing programs in order to take into account the unique nature of source materials in archival and manuscript collections. Tests on more than 25 manuscript and archival collections indicate the feasibility of developing one program that could be used for all collections, and yet allow enough variation for the unique problems of each.

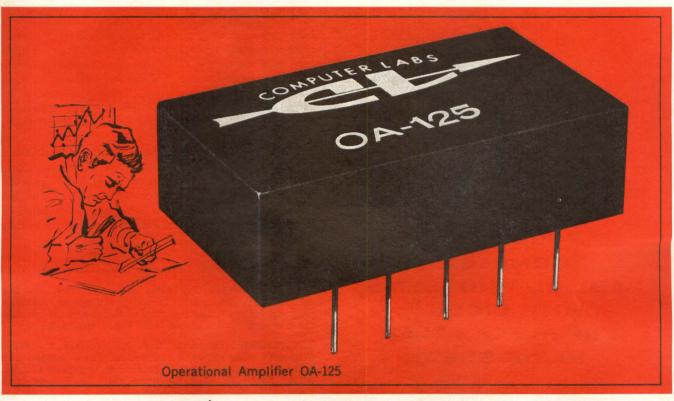

# Our OPAMP output rings (But only if the input does)

#### USEFUL

Our gain-bandwidth product is 125 MHz.

Roll-off is 6 db/octave. That makes our op amp unconditionally stable. For closed loop gain of 1, small-signal bandwidth is 125 MHz; for a gain of 2, 62.5 MHz; for a gain of 5, 25 MHz; etc.

Output voltage range  $\pm 2$  volts into 100 ohms. Open loop voltage gain 50,000 at DC; 50 at 10.0 MHz. Output slews full scale in 15 ns.

If you LIKE hanging compensating networks on op amps, ours will be a disappointment. All you hang on it are two resistors to set gain. But isn't that the way textbooks say a **good** operational amplifier works?

One to play with will cost you \$135. If you're REALLY serious, the boss says we can sell you 100 for \$99 each.

A REMINDER ...

HS-808 A/D CONVERTER We also make 12 A/D Converters from 4 bits at 25 MHz to 9 bits at 5 MHz. Speeds to 10 ns/bit and aperture time low as 0.2 ns!

(919) 292-6427 • 1109 VALLEY PARK DRIVE • GREENSBORO, N. C. 27403 A DIVISION OF STRANDBERG ENGINEERING LABORATORIES, INC. for tomorrow's technology today

CIRCLE NO. 11 ON INQUIRY CARD

#### SOLVE COMPLEX CABLING PROBLEMS WITH CICOIL SUPER-FLEX FLAT HARNESSES

GREATER FLEXIBILITY through the use of the finest silicone-rubber insulation material, tested to 75 million flexes without damage. Highly suited to gyro systems and other in-motion applications.

UP TO 75% SIZE AND WEIGHT REDUCTION, with complete design freedom.

**COMPLETELY RELIABLE**, even under extreme temperatures and unusual environmental conditions.

COMBINED CONDUCTORS, with the use of shielded and unshielded wires in single twisted pairs or coaxial conductors in a single, flat cable up to 8 inches wide and 12 feet long.

ONE SOURCE FROM CONNECTOR-TO-CON-NECTOR with full design engineering service to assist you with your special problems. Standard or custom connectors and terminal boards are available, providing a complete harness assembly. CICOIL SUPER-FLEX HARNESSES ARE

AVAILABLE FOR MILITARY, COMMER-CIAL AND MEDICAL APPLICATIONS.

WRITE FOR COMPLETE LITERATURE AND FREE SAMPLES

13833 Saticoy St. • Van Nuys, California 91402 Phone: (213) 781-3440 • TWX: VNUYS 7785

#### \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

The Food and Drug Administration, Washington, D. C., has installed an EDP system to serve the entire agency. The facility is the result of five years' work to manage more effectively the storage and retrieval of the great volume of data currently flowing into FDA. The heart of the new system is an IBM 360-30 located in FDA's main headquarters that has been specifically adapted to permit access to files established primarily for one user group by all other potentially interested groups in the headquarters and in the field. Included will be information on drug quality, food technology, or pesticides gathered in carrying out the scientific and regulatory missions of the FDA. The data already collected within a single bureau will be fed through the computer system for agency use. Other applications will be developed as rapidly as staff time and technology permit. The computer system is so designed that it may be connected by lines to each of the field facilities of FDA. Work is now proceeding, on a pilot basis, to link one of the district offices to the central computer. Ultimately it is expected that all the FDA district offices will be connected to the central computer. The IBM 360-30, rented for \$21,000 a month, is equipped for large scale storage of and rapid, direct access to data.

Recent Government Contracts: .....

BRANDON APPLIED SYSTEMS, INC., New York, has been awarded a \$111,000 contract to modify and maintain computer programs for the National Library of Medicine's central medical reference service of the U. S. Public Health Service.

BENDIX CORP., Teterboro, N. J., has received a \$1,453,783 fixed-price order for repair and modification of airborne computer components. Work will be done at Teterboro, N. J., and Wilkes Barre, Pa. The Oklahoma City Air Materiel Area, Tinker AFB, Okla., is the issuing agency.

GRUMMAN AIRCRAFT ENGINEERING CORP., Bethpage, Long Island, N. Y., has been issued a \$3,000,000 fixed-price letter contract to provide the initial design effort for an improved search radar, a new digital computer system, and a weapons release system in the A-6A aircraft. The Naval Air Systems Command issued the contract.

SPERRY RAND CORP., Long Island City, N. Y., has received a \$4,200,000 letter contract for production of computers to be installed in the subsystem of gunfire control systems. The Naval Ordnance Systems Command is the contracting activity.

CONTROL DATA CORP., Minneapolis, Minn., has been awarded a \$1,800,000 fixed-price contract to increase the capacity of the basic CD 6400 Computer Systems at the Fleet Numerical Weather Facility, Monterey, Calif. Work will be done at Arden Hills, Minn. The Naval Postgraduate School issued the contract.

CONTROL DATA CORP., Minneapolis, Minn., has been awarded a \$1,750,947 contract order for the rental of automatic data processing equipment at Patrick AFB, Fla. The contract was issued by the Air Force Eastern Test Range Base Procurement Office, Patrick AFB.

LEAR SIEGLER, INC., Grand Rapids, Mich., has been issued a \$1,779,400 initial increment to a \$4,400,000 contract for manufacture of airborne computer components. The Aeronautical Systems Division (Air Force Systems Command), Wright-Patterson AFB, Ohio, is issuing the contract.

RCA, Burlington, Mass., has received a \$2,798,995 initial increment to a \$4,370,000 contract for development of an airborne data automation system. The Electronic Systems Division (Air Force Systems Command), L. G. Hanscom Field, Mass., is the contracting agency.

# Now an instant Core Memory ...just plug in and solder

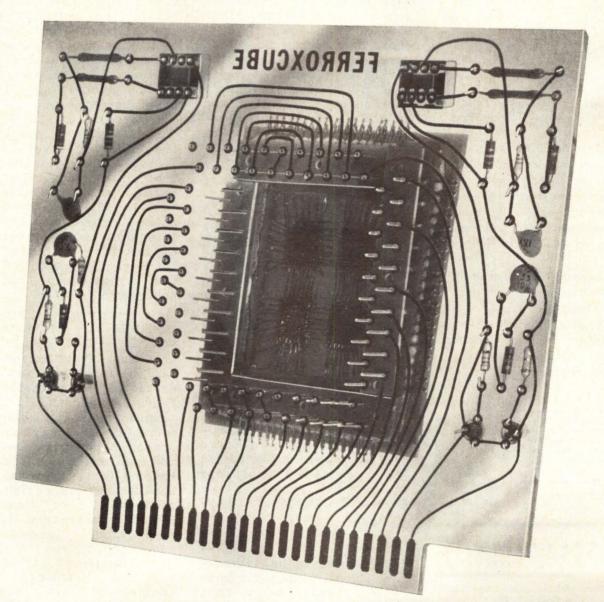

Ferroxcube Platrices are magnetic core matrices specially designed for desktop business machines, instrumentation and industrial control equipment. Not only are they priced far below conventional core memory planes; they save you even more money on assembly costs.

Platrices are provided with plug-in

connection pins for quick and simple direct mounting on printed circuit boards. You mount a Platrix as you would a transistor: push the leads through the board and solder. To illustrate, we built this mockup out of clear plastic so you can see both the pins and the Platrix itself.

The expensive cut frames of conventional planes are eliminated by a simplified yet rigid frame of glassepoxy laminate. For high resistance to shock and vibration, the cores are fixed to a base plate of this material by a special lacquer. Stacks of up to four Platrices can be supplied with series connected drive lines terminated at the bottom of the stack. Low drive currents allow use of simple drive and selection circuits. Platrices are available in 8 standard configurations with bit capacities from 256 to 1,024, but we can be persuaded to make other sizes if you really need them.

Platrices. Reliable. Simple. Inexpensive. Bulletin 6007 tells all. Write for it today.

Albuguerque—Electronic Enterprises, (505) 256-1585; Baltimore—Eastern Components, (301) 322-1412; Dayton—(513) 253-3158; Detroit—(313) 342-7722; Encino, Cal.—(213) 788-2060; Englewood, Col.—(303) 771-2000; Houston—Noakes Engineering, (713) 529-6213; Irving, Texas—Noakes Engineering, (214) 255-0441; Minneapolis—(612) 888-4681; North-lake, III.—(312) 261-7880; Orlando—(305) 841-6380; Philadelphia—Eastern Components, (215) 927-6262; Phoenix—(602) 265-1792; San Francisco—Wm. J. Purdy Agents, (415) 863-3300; Saugerties, N.Y.—(914) 246-2811; Union, N.J.—(21) 964-1844; Waltham, Mass.—(617) 889-3110; Toronto, Ontario—Philips Electron Devices, Ltd., (416) 425-5161.

INVAC

INVAC Tape Punch Packages, Series PH, feature long-life and reliability essential for compact low-cost data handling systems requiring long tapes and punch speeds up to 60 cps. The many available options adapt these Packages to virtually any system design.

- . . . Compact 10 1/2" panel height

- . . . Optional Punch Speeds

- . . . Optional Power Supply

- . . . Optional Drive Electronics

- . . . Optional Sequencer Electronics

- . . . Optional Code Delete

- . . . Optional Tape Feed

INVAC MODEL P-135 TAPE PUNCH is available separately. Solenoid operation eliminates maintenance-prone motors and clutches and also minimizes drive power requirements. 100,000,000 operations augaranteed.

Write for data

26 Fox Road, Waltham, Massachusetts 02154 Tel. (617) 899-2380

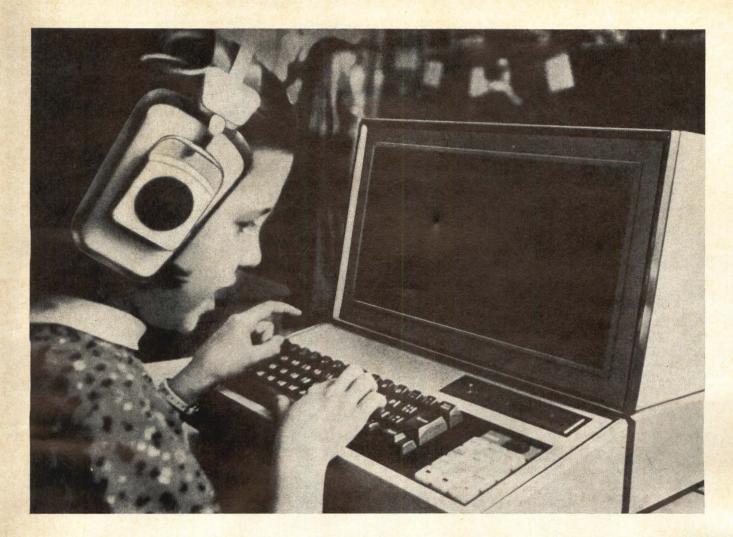

PHOTOELECTRIC KEYBOARDS • TAPE PUNCHES READERS AND HANDLERS • 1/O TYPEWRITERS PRINTERS AND SYSTEMS CIRCLE NO. 14 ON INQUIRY CARD

"WIDE GAP EFFECT" IN TRAN-SISTORS DEMONSTRATED-Scientists at Carnegie-Mellon University have announced a breakthrough in the design and construction of transistors, which, they say, has the possibility of making these devices ten times more effective. Professor Donald L. Feucht and Arthur G. Milnes, and graduate students D. K. Jadus and H. J. Hovel described their discovery last month at meetings of the Electromechanical Society in Chicago and of the Institute of Electrical and Electronics Engineers in Washington.

Although predicted for several years in electronic theory, the "Wide Gap Effect" has proved impossible to achieve in actual transistors until the successful demonstration by the Carnegie-Mellon team. Perhaps most important of the improvements that may be expected in transistor performance will be increased gain in high frequency ranges; more even distribution of current flow through the device, thus preventing overheating or partial breakdown of the transistor: and improved effectiveness of photo-electric cell action which would, for instance, make it possible to get much greater power from so-called "solar batteries".

The effect has been achieved by the Carnegie-Mellon group by using heavily "doped" transistor base regions, which means that controlled amounts of "impurities" have been introduced into the crystals to

facilitate transfer of electrons through the device. Working with gallium arsenide and zinc selenide layers on germanium, the experimenters kept their laboratory apparatus in a state of surgical cleanliness-only instead of concentrating on germ-free sterility, they managed to keep out any trace of contamination from unwanted chemical elements. It was probably failure to achieve such "clean" conditions which had frustrated all earlier attempts to create structures capable of achieving

NEWS

DUSTRV

Dr. Milnes pointed out that, although the effect has been achieved in laboratory conditions, there remains a great deal of work to be done in the technology of manufacture before effective production of the new transistors can be achieved on a large scale.

the wide-gap effect.

......

COMPUTERIZED VOICES-An ultra-high-speed computer that can convert speech into digital information as fast as the words are spoken was recently announced. Designed and built by Sylvania's Applied Research Laboratory, the system analyzes the basic elements of sound waves, as it performs its accelerated conversion, according to Dr. James E. Storer, laboratory direc-The quick-analysis tor. technique, called "fast fourier transform", is necessary for on-the-spot processing of low frequency audio signals, including sonar and speech, into digital data, Dr. Storer says.

Known as the Advanced Computational Processor (ACP), the computer selects only fundamental sound components and by-passes portions which do not destroy the signal if eliminated. Moreover, it allows reduction of the bandwidth necessary to transmit the information digitally. The smaller bandwidth permits simultaneous secure transmission of several signals over a channel that otherwise would handle only one unprocessed message.

Constructed entirely of integrated circuitry, the device is said to perform an average computation in one three-millionth of a second, about five times faster than digital equipment now employed for this purpose. According to Dr. Storer, "digital models currently in operation are unable to attain circulation rates necessary to computerize signals without a delay in processing; only complex, special-purpose analog circuitry previously has analyzed sound at input speeds."

The fast computation rate of the ACP is said to be due principally to its integrated circuit memory element, which replaces the slower, conventional core storage. In addition to its increased speed, the ACP, as a digital computer, has built-in versatility. It takes instructions from relatively uncomplicated programming rather than requiring separate wiring or specialized equipment for each of its jobs as does the analog process.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

FIRST POSITIVE ISOTOPE EF-FECT DISPLAYED BY SUPERCON-DUCTING URANIUM—In the current issue of "Physical Review Letters," Dr. Robert Fowler and co-workers at the Los Alamos Scientific Laboratory, New Mexico have reported the first positive isotope effect. The physi-

#### HIGH-SPEED PRINTERS

Rack or Table Mounted Size 1 to 24 columns 8<sup>3</sup>/<sub>4</sub> H x 19 W x 22 D 25 to 48 columns 2 drawers 8<sup>3</sup>/<sub>4</sub> x 19 x 22 each Codes — BCD — ASC11 — Baudot or your choice Data Rates — up to 600,000 char. per sec. Speed — numerics only — 40 lines per sec. Alpha-numeric 20 lines per second.

Shepard LABORATORIES, INC.

480 Morris Avenue Summit, N. J. 07901 Tel.: (201) 273-5255

CIRCLE NO. 16 ON INQUIRY CARD

# Always connect subminiatures with Winchester Electronics.

Take cable and panel mounted rectangulars. We've got them with solder or crimp removable contacts. From 4 to 50 contacts with current ratings of 3 to 7.5 amps. Standardized high-density rectangulars also, that allow you three current ratings — 3, 5, or 7.5 amps—with one size connector and one size panel cutout. Need pc connectors? We've got edge-board, right-angle or flat-mounted pc's on .050; .078 or .100 contact centers. With solder, eyelet or dip solder terminations for 1/32 to 1/4-inch boards. And we've got microminiature pc connectors for use with integrated thin film and semi-conductor circuitry.

If you're looking for circular cable or panel mounted connectors, you'll find them with 1 to 12 contacts. Contact centers from .025 to .040 with current ratings of 3 to 7.5 amps.

They're all on the shelf of

ald definited at the left

your Winchester Electronics distributor. You'll find him close as your phone – make the connection now. Winchester Electronics, Main St. & Hillside Avenue, Oakville, Conn. 06779.

B WINCHESTER ELECTRONICS

cists are of the opinion that their work is "final proof" that the phononelectron theory of superconductivity is inadequate.

Theoretical physicists have had difficulty explaining the strange behavior of superconductors since they were first observed in 1911. In fact, a satisfactory explanation was not formulated until 1957.

The current theory, called the BCS theory, explains superconductivity in terms of phonons (heat units) and electrons. BCS stands for the authors of the theory John Bardeen, Leon Cooper, and J. R. Schrieffer. Since its birth in 1957, the BCS theory has encountered new trouble each year.

One problem is that the theory implies that the critical temperature-the temperature at which a substance becomes superconducting-should be lower for the heavier isotope of This relaa substance. tionship between critical temperature and isotope mass is known as the negative isotope effect. It has been observed for a number of substances, but in several cases the temperature was not as low as the theory predicted.

Dr. Fowler's group began studying isotopes of uranium as a further check on the theory. They have measured critical temperatures for uranium-235 and its heavier isotope, uranium-238.

Samples of high-purity uranium were cooled below 2.5° Kelvin (degrees centigrade above absolute zero) with liquid helium. A1though trace contaminants in the samples made precision difficult, there was no doubt that in every case U-235 had a lower critical temperature than U-238. These results constitute a positive isotope effect, a phenomenon that had not been observed previously.

On the basis of other work with critical temperatures, the Los Alamos physicists had expected the positive isotope effect. The results, although somewhat higher than they had anticipated, confirmed their expectations.

"Physical Review Letters" is published by The American Physical Society.

#### ........................

COMPUTER DESIGNED MULTI-LAYER CIRCUIT BOARDS-Production-proven computer programs and processing techniques for designing and fabricating multi-layer circuit boards for subsystems was recently announced by the Systems Division of Librascope Group, General Precision Systems Inc. According to J. L. Deitz, Chief Engineer, the programs and processing techniques are perfected, and have been effective in reducing design time and costs in producing circuit boards for various applications.

Librascope is now making the programs and techniques available to the general electronic industry. Mr. Dietz says they are ideal for prototype, short run, or large-scale production programs requiring fast-reaction design and fabrication of functional subsystems.

The technique, long used at Librascope, employs a computer programmed to process schematics or logic The computer equations. controls an X-Y plotter which automatically produces the art work for printed circuit board mas-Librascope is sucters. cessfully using the process for designing and producing up to 12-layer multi-layer boards. Additional computer programs, production proven, also provide wire lists, parts lists, maintenance documentation and tapes for automatic hole drilling. These too are said to offer great savings in time, design, and documentation costs.

#### Please don't call EMR's 6130 Computer

If you think the *ADVANCE* 6130 computer from EMR is just another "little" computer, take a closer look. You could be fooled by the price low enough to compete with any small machine—or by the 16-bit word length, characteristic of smallscale systems. But that's where the comparison ends.

Analyze the 6130 and you'll realize it's the most productive system available. The instruction repertoire and internal architecture put it in a class by itself.

#### SMALL SCALE

To the potential buyer of a smallscale computer, there are a number of capable machines which are available to "do the job." However, aren't you looking for a system that can "do the job—plus"? The plus being able to expand to accommodate your next requirement. Many of the small-scale computers (under \$35,000) that are being sold cannot provide the user with any realistic approach to expansion.

The 6130 is in a different class, it is designed for expansion. With the 6130 you can add a second processor easily, with no operational software problems. This additional processing power is relatively inexpensive when compared to installing larger systems.

This built-in capability for growth insures that you won't be looking for another new system next year and have to face the re-programming problem.

#### HIGH PRODUCTIVITY

Next, how about the buyer who has a problem that actually requires a large-scale machine, but does not have the funds? The 6130 has a capability that stretches into this high-productivity market.

Historically in the computer field, the user's main problem is to justify a large financial investment to his management. Once the computer is installed, and the user can demonstrate to management what can be accomplished, he can build a good argument for expansion. The expansion is normally in the way of adding more peripheral equipment and additional core memory. This is further indicative that, with the large-scale approach, the user has started out with more "computer-power" than needed—and is paying for features that he cannot use or can do without. As the load increases, a point is reached where he has all of the options that use the software to the limit, but by that time, he runs out of "computer-power."

In the case of the *ADVANCE* 6130, the high-productivity user may run out of computer-power sooner but would be in a position to add another 6130 processor to immediately increase his computer power at a small financial addition. One 6130 can handle background processing while the second handles preprocessing and input/output. If this would not be an acceptable approach, a more powerful processor could be added and the 6130 retained as a satellite.

The 6130 alone can successfully offer this approach as competitive

small computers are just not powerful enough to handle the general purpose requirements.

#### **ADVANCE 6130 FEATURES**

- 16-bit data word with parity check and memory protect.

- 750 nanosecond memory cycle time as standard.

- Exceptionally large repertoire of more than 100 instructions.

- Three hardware index registers with indirect address.

- Relocation register with double indexing allowed is standard.

- 128 interrupt priority levels.

- Hardware multiply and divide a standard feature.

- Up to 128 external interrupts.

- Single instruction interrupt with both individual and group enable/ disable allowed.

- FORTRAN, real time FORTRAN and macro assembler available.

- Interlaced multiplexed I/O channel allows up to 16 devices to be connected to single channel.

If your application fits in either category, we urge you to contact EMR Computer Division immediately. The address is: 8001 Bloomington Freeway, Minneapolis, Minnesota 55420. Or call our Manager of Marketing collect, 612-888-9581.

We want to tell you about our notso-small 6130.

ETTIR COMPUTER DIVISION

# Planned parenthood is a family of computers from

NEW!

# • MODEL 2

NTERDAT

- 1,024 or 2,048 byte memory

- 45 µs add time

- 3.µs memory cycle time

## • MODEL 3

- FORTRAN

- Hardware multiply, divide, and block input/output

- High speed memory access channels

- 4,096 to 65,536 byte memory

- 34 µs add time

- 1.8 µs memory cycle time

# • MODEL 4 NEW!

- Hardware floating point

- FORTRAN

- Hardware multiply, divide, and block input/output

- High speed memory access channels

- 4,096 to 65,536 byte memory

- 3.9 µs add time

- 1.5 µs memory cycle time

0000 0000 0000

0000 0000 0000 0000

\$4,700

\$7,000

\$10,000

The INTERDATA family features a basic repertoire of 77 instructions, modular memory expansion plus standard peripheral devices and system components.

I6 General Registers used as accumulators or index registers.

All memory directly addressable to the byte level by the primary instruction word.

Priority interrupt facility provides for interface of 256 devices.

20440 Tower Center Lane Cupertino, California 95104 (408) 257-3418

Sales and Service in 48 states and Canada

2 Crescent Place Oceanport, New Jersey 07757 (201) 229-4040

### What bothers you about your memory?

Still working with "PRELIMINARY" drawings long after the memory is installed in your equipment? That's bad!

• Every Micra-STOR comes with a "FINAL" instruction manual.

Trying to remember all the "OPTIONS" you ordered? That's bad! •Every Micra-STOR has built-in Self Test, Data Saver and Displays on all registers.

Waiting for a pin connection chart so you can make up memory I/O cables? That's bad!

• All I/O assignments for Micra-STOR are published in our Technical Bulletin 402.

#### Why not try Micra-STOR?

•We've probably solved the rest of your memory problems too! . . . Ask for TB402.

STANDARD MEMORIES INCORPORATED

2401 SOUTH BROADWAY, SANTA ANA, CALIF. 92707 TELEPHONE (714) 540-3605

TORRINGTON

All 72 of these blowers are immediately available "off-the-shelf" units... models designed to lend themselves to a variety of adaptations. By merely interchanging standard parts these in-stock units have produced 216 different models for Torrington customers, and the end is nowhere in sight.

Whatever your specifications, whether high or low air flow, A.C. or D.C. motors, high or low resistance, single or double inlet, Torrington can make the centrifugal blower you need - faster, more economically, and in any quantity you desire, from mere dozens to the thousands.

We can't illustrate every type of blower produced in our plant. But if you'd care to see how far we'll go to meet your needs, write today for our catalog "Centrifugal Blowers by Torrington." Address your request to Torrington Manufacturing Company, Torrington, Connecticut.

#### TORRINGTON MANUFACTURING COMPANY

United States: Torrington, Connecticut/VanNuys, California/Rochester, Indiana Canada: Oakville, Ontario England: Swindon, Wilts. Belgium: Nivelles Australia: Sydney

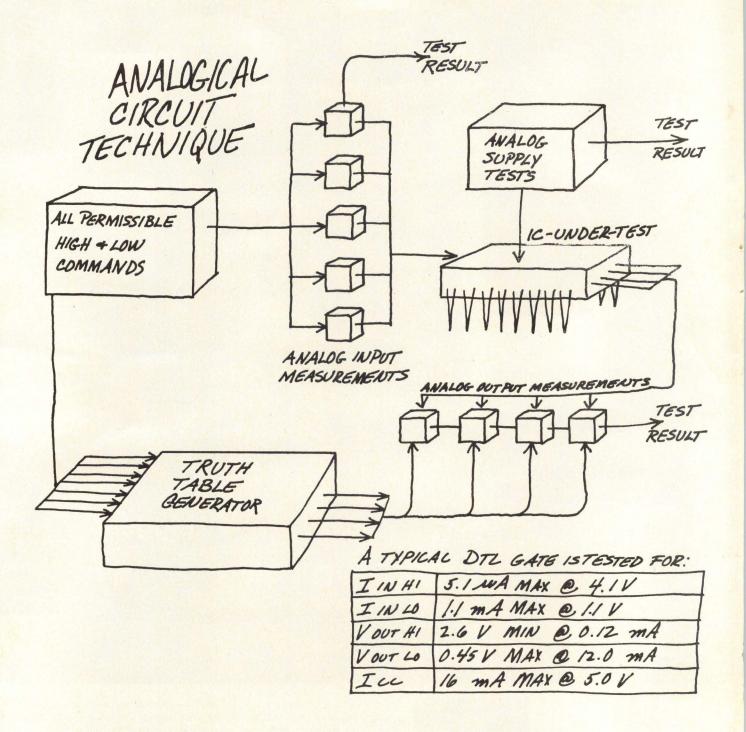

#### Intriguing, isn't it, this new way of testing digital integrated circuits?

Now you can make sure ALL of your ic's will work — because you can make both parameter and functional tests simultaneously, and for all permissible combinations of inputs. □ It's done by exercising all the LOGICAL inputs on the ic-under-test and selecting the appropriate ANALOG measurements that should be made. 5,000 such measurements are made in 1/100 of a second.

CIRCLE NO. 22 ON INQUIRY CARD

□ Even more exciting, our Analogical Circuit Technique is available on a little machine that weighs only 25 lbs. It's a cinch to program, and costs only about \$5,000. □ We call it ACT 1 (because of the fortunate acronym). □ To learn more about analogical testing, just write: ACT 1, Teradyne, 183 Essex Street, Boston, Massachusetts 02111.

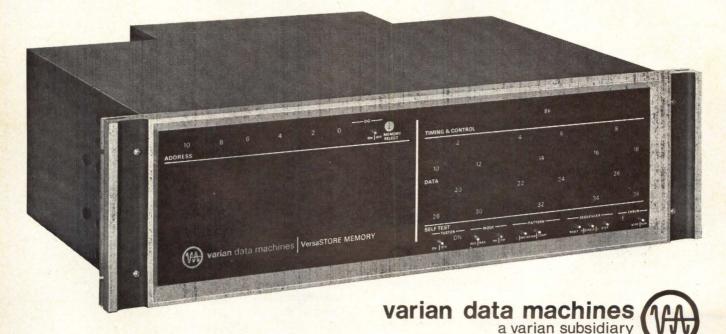

# we've cut microseconds we've cut size we've cut cost

# in the new VersaSTORE II core memory system

VersaSTORE II is a vastly improved version of our field-proven VersaSTORE core memory. It operates at a faster 1.7 micro-second asynchronous speed with 750 nano-second access time—with the same superb operating margins at elevated temperature, and uses IC's for reliability.

The new VersaSTORE II packs 50% more core memory in a 5¼" rack-mounted package.

And VersaSTORE II is more flexible than ever. It's available in increments of 4096 words of 36 bits or 8k words of 18 bits, and conveniently stacks in multiples for bigger memories, thanks to our exclusive Party Line.

And VersaSTORE II offers self-test features, timing and control flags, and test points for easy system check-out.

Remember, you'll get all these features only in the new VersaSTORE II-nowhere else! Why not get a VersaSTORE II brochure? Write or call:

1590 Monrovia Ave., Newport Beach, Calif. TEL. (714) 646-9371 TWX (910) 596-1358 CIRCLE NO. 23 ON INQUIRY CARD

Formerly Decision Control, Inc.

# **DIGITAL DATA TRANSMISSION**

G. P. Hyatt, Head, Computer Design Advanced System Division, Teledyne System Company, Hawthorne, California

Synchronous data transmission results in higher speed operation and hardware economy, by eliminating resynchronizing hardware and delays. Synchronous techniques require special propagation delay and clock pulse skew considerations. Signal degradation is also a factor. Selection of the proper transmission cable, line drivers, and line receivers minimizes potential problem areas. Clock pulse fanout and transmission line routing contribute to hazard free operation.

Digital data transmission is accomplished on macroscopic and microscopic levels; data transmission between spacecraft and the earth over millions of miles of space and data transmission between logic functions on a single integrated circuit substrate illustrate these extremes. This article describes a range of digital data transmission that will permit synchronous transmission and operation. This range is characterized by the primary constraint that the complete path propagation delay must be less than the clock period, covering a range from the microscopic to the intermediate length transmission line. Of particular interest is the intermediate length transmission, which will permit synchronous communication for high data rates over short distances (10 mc clock and 25 feet) or low data rates over long distances (10 kc and 5 miles). A second constraint, that the clock pulse propagate to all flip-flops prior to the data change propagation, will eliminate critical races associated with a large clock pulse skew condition.

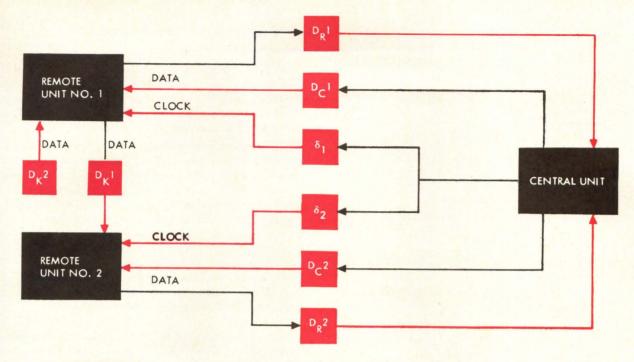

The synchronous data transmission technique will result in hardware economy and speed advantages when compared to an asynchronous digital communication link.

Communication within a centralized system is the trivial case of asynchronous data communication, while communication between a central unit and various remote units is the generalized case. A baseline system will be described to illustrate the important considerations, using synchronous design techniques within each unit and between units. A system that deviates from the primary constraint, where the propagation delays can exceed the clock pulse period, will require different design considerations involving asynchronous transmission of data between the various units, necessitating extra hardware. The baseline system is shown in functional form in Fig. 1, with characteristics listed in Table 1. The central unit will transmit the synchronizing clock pulses and digital data to the remote units, while the remote units will transmit synchronous digital data to the central unit and other remote units. All data transmission is synchronized with the central unit clock pulses. The transmission propagation delays are shown as D for the data lines and  $\delta$  for the clock lines.

Transmission of digital data involves design considerations pertaining to signal degradation, propagation delays, and clock pulses skew affects. Sub-categories involve impedance matching and waveform restoration considerations. A detailed description of these considerations and the resultant hardware implementation will be presented.

#### **Signal Degradation**

Transmission of digital data on long transmission lines results in degradation of the signal waveform, as a function of the characteristics and length of the transmission line. There are two predominating signal degradation mechanisms, defined as the frequency insensitive and frequency sensitive degradation affects.

The frequency insensitive degradation of the digital signals are termed the attenuation characteristic of the transmission line, and are primarily caused by the resistance in the non-ideal conductor. (When projected to higher frequencies in the hundred megacycle region, the "skin effect" will tend to produce a slightly frequency-sensitive attenuation characteristic, but in the low megacycle frequency region, the "skin effect" is not significant and the attenuation will be relatively frequency insensitive. The attenuation characteristic of the baseline transmission line is listed in Table 2, where the attenuation at 400 mcps is approximately 10 db per 100 feet and the attenuation at one megacycle is approximately 2 db per 100 feet. In the neighborhood of several megacycles and below, the attenuation parameter is virtually constant.)

The attenuation characteristic of the transmission line will degrade the amplitude of the digital data without significantly affecting the shape of the digital pulse. The relationship between attenuation and voltage amplitude

Fig. 1. Data flow functional diagram

degradation is illustrated in Equation 1, while the total attenuation for a 250 foot transmission line is calculated in Equation 2.

Attenuation

$$\equiv 20 \log \left(\frac{V_{out}}{V_{in}}\right) db$$

(Eq. 1)

ttenuation =  $(-2 db/100 \text{ ft.})$  (250 ft.) =  $-5 db$  (Eq. 2)

Substituting Equation 2 into Equation 1 yields:

A

Attenuation =

$$20 \log \left( \frac{V_{out}}{V_{in}} \right) = -5 \text{ db}$$

(Eq. 3)

$$V_{out} = \frac{V_{in}}{10^{0.25}} \approx 0.6 V_{in}$$

(Eq. 4)

Therefore, the pulse amplitude at the remote end of the transmission line will be attenuated to approximately 60% of the amplitude of the original pulse. This amplitude degradation will necessitate line drivers and line receivers to permit the restoration of the pulse amplitude for proper operation of the digital equipment.

The frequency sensitive degradation of the digital pulses is primarily caused by the capacitance associated with the transmission line. This capacitance is listed in Table 2 as 13 pf per foot. The total line capacitance for a 250 foot transmission line is, therefore, 3250 pf. A Fourier analysis of the digital pulse will illustrate that the higher frequency components result in the sharp rise and fall times, therefore the relatively greater attenuation of the higher frequency components will cause a larger degradation of the leading and trailing edges than of the peak pulse amplitude, resulting in more of a degradation of pulse shape than of pulse amplitude.

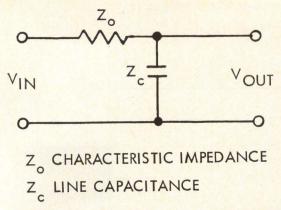

The capacitance parameter of the transmission line is distributed along the line length, but a good approximation of the frequency sensitive degradation can be obtained by assuming a lumped parameter transmission line, illustrated in Fig. 2. This lumped parameter equivalent transmission line schematic describes a voltage divide network with the characteristic impedance  $(Z_o)$  and capacitive impedance  $(Z_c)$  of the line forming the voltage divider. The characteristic impedance is relatively constant, independent of frequency, line length, and other parameters. The capacitive impedance parameter decreases with increased line length and frequency; therefore, the output signal amplitude is inversely proportional to the line length and the frequency of the Fourier frequency component. The capacitive impedance for the fundamental frequency component of the pulse is calculated in Equation 5.

$$Z_{c} = 1/(2\pi fc) = 1/[(2\pi) (10^{6}) (0.325 \times 10^{-8})] = 50 \Omega$$

(Eq. 5)

|        | Table 1. Baseline System Considerations                         |                           |  |

|--------|-----------------------------------------------------------------|---------------------------|--|

| C      | lock Rate                                                       | l mcps                    |  |

| Т      | ransmission Line                                                |                           |  |

|        | Length (max)                                                    | 250 feet                  |  |

| R      | ise-Fall Time                                                   | 20 ns                     |  |

|        | Table 2. Transmission Lin                                       | e Characteristics         |  |

|        | Table 2. Transmission Lin                                       | e Characteristics         |  |

| В      | Table 2. Transmission Lin<br>rand-Rex Coaxial Cable             | T-267                     |  |

| -      |                                                                 |                           |  |

| c      | rand-Rex Coaxial Cable                                          | T-267                     |  |

| c<br>c | rand-Rex Coaxial Cable                                          | <u></u> Τ-267<br>95 Ω     |  |

| C      | rand-Rex Coaxial Cable<br>haracteristic Impedance<br>apacitance | T-267<br>95 Ω<br>13 pf/ft |  |

The frequency sensitive degradation for the fundamental frequency component of the pulse is calculated in Equation 6 with respect to the lumped parameter approximation, illustrated in Fig. 2.

$$\frac{V_{out}}{V_{in}} = \frac{Z_c}{Z_c + Z_o} = \frac{50}{50 + 95} = 0.34$$

(Eq. 6a)

$V_{out} = 0.34 V_{in} \qquad (Eq. 6b)$

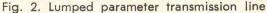

Therefore, the output amplitude of the fundamental frequency component is 34% of the input pulse amplitude. Under the assumption that a sharp leading edge can be obtained with a ten megacycle Fourier frequency component, the leading edge will be degraded to an amplitude 5% of the fundamental amplitude. This frequency sensitive degradation of the pulse results in a pulse shape that is significantly rounded at the edge with poor rise and fall times.

The total degradation of the peak amplitude of each pulse is proportional to the attenuation and frequency sensitive degradation of the pulse. The output pulse amplitude is calculated in Equation 7.

Degradation =

$$\frac{V_{out}}{V_{in}} \approx (0.6) (0.34) = 0.2$$

(Eq. 7a)

$$\mathbf{V_{out}} = 0.2 \ \mathbf{V_{in}} \tag{Eq. 7b}$$

The pulse degradation is illustrated in Fig. 3, with an input pulse of unity amplitude and sharp edges and an output pulse reduced to 20% amplitude with degraded edges.

Fig. 3. Pulse degradation

#### **Propagation Delay Considerations**

Propagation delay of digital pulses is generally caused by the delay through logic functions, determined by switching speed of the logic, and the delay through interconnections, determined by the velocity of propagation through the medium and settling of the signal due to impedance mismatches.

Interconnections in electronic systems are often treated as simple conductors. This approach is valid only in relatively slow speed, small dimensional systems. In applications with clock periods that approach the transmission propagation delays, the interconnections must be considered as transmisison lines. High speed switching of the digital logic can introduce Fourier frequency components in the hundred megacycle frequency range, which is in the low radar band. Much of the theory associated with electromagnetic fields and waves as applied to radar systems is directly applicable to these systems. The criterion for the treatment of interconnections as either conductors or transmission lines is based upon a comparison of the clock periods and transmission propagation delays. If the propagation delay down a line is in the order of magnitude of the clock period, the interconnections should be treated as transmission lines. An electrical signal will propagate at approximately one foot per nanosecond for a nominal permittivity  $(\varepsilon)$  and permeability  $(\mu)$  of the surrounding median. A transmitted signal will propagate along a line to an impedance mismatch interface, where a portion of the energy will be reflected. This reflection will propagate down the line in the reverse direction to another impedance mismatch interface, being reflected back and forth until the signal in the line stabilizes at the excitation level. The number of reflections that will occur prior to the signal stabilizing at an acceptable level is a function of the impedance mismatch. For larger mismatches, a larger number of reflections will occur prior to stabilization. For long transmission lines or lower propagation velocities, the delay for each reflection will be longer. Therefore, the propagation delay through a wire is a function of the impedance mismatch in addition to the line length and propagation velocity.

For short lines and relatively long clock periods, successive reflections will stabilize in a relatively short period compared to the clock period. For long interconnections or fast clock rates, line stabilization periods may become significant. Relatively long interconnections can be better tolerated if impedance matching is implemented. Integrated circuits typically contain a low output impedance and a relatively high input impedance to enhance noise immunity and fan-out. The transmission line selected for the baseline system has a low characteristic impedance, as listed in Table 2. This value provides a good impedance match with typical line driver output impedances, but provides a moderate impedance mismatch with typical line receiver input impedances. Impedance matching should generally be accomplished by adding terminating resistors to the high impedance end of long interconnections to minimize reflections and the resulting propagation delays. Pulse transformer techniques can also be used to satisfy the impedance matching considerations, but with a slightly higher hardware complexity than with resistive termination.

The propagation velocity of the transmission line for the baseline system is 80% of the propagation velocity of light, as listed in Table 2. The velocity of light is approximately 1 foot per nanosecond. Therefore, the transmission of the digital data will require approximately 300 ns to propagate along the line for a distance of 250 feet. The 600 nanosecond two-direction propagation delay is very close to the 1  $\mu$ s clock period, requiring impedance matching techniques to be implemented. A slower data rate or shorter transmission lines would reduce the impedance matching requirements.

The logic propagation delay, characterized by the delay in switching the electronic elements, is typically in the range of tens of nanoseconds. It is generally important that the propagation delay due to the logic elements be large compared to the difference in propagation delays between the various paths in order to minimize the clock pulse skew considerations. For the baseline system, the line propagation delays are an order of magnitude greater than the logic element propagation delays. This condition could result in clock pulse skew problems, requiring insertion of predetermined propagation delays to insure proper operation.

#### **Clock Pulse Skew Considerations**

The clock pulse skew affect is caused by unequal propagation delay paths for the data and the clock pulses. This condition may cause the data changes to propagate through the system more rapidly than the clock pulses, resulting in critical race conditions that can cause erroneous or ambiguous data to be set into the flip-flops. A data flow functional diagram, illustrated in Fig. 4, will be used to describe the clock pulse skew affect. The state of the flip-flop will be set to the input state with each clock pulse, which arrives at the  $\tau$  intervals. Therefore, the input data must propagate through the system and stabilize at the flip-flop input at time  $(n\tau - k)$ , which is prior to the arrival of the clock pulse, defined as time  $n_{\tau}$ . The clock pulse will cause the flip-flops to change state, resulting in new data propagating through the system. In an application where the clock pulse must propagate to remote parts of the system through long propagation delays, a race condition will result, where the new state of the earliest clocked flip-flops will propagate to the more remote flip-flops simultaneously with the clock pulse. If the clock pulse arrives first, the flipflops will be set to the state of the present data prior to the new data propagating to the flip-flop inputs, but if the clock pulse is excessively delayed, where the new data arrives at the remote flip-flop first, the new data will be erroneously clocked into the flip-flop.

Synchronous digital systems operate with non-critical race conditions, where the flip-flop propagation delay  $(\Delta)$  is long enough to insure proper operation. For systems in which the flip-flop propagation delay is small compared to the transmission propagation delay, transmission line length and velocity differences may permit the new data to arrive at the remote flip-flops prior to the clock pulse, resulting in a hazard condition.

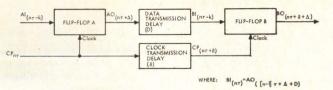

The waveforms in Fig. 5 illustrate shift register operation for a non-critical race condition with waveforms V and VI and a critical race condition with waveforms VII and VIII. Each clock pulse will cause the state of the flip-flop to be set to the input condition, with the

Fig. 4. Clock pulse skew diagram

change propagating to the flip-flop output after a  $\Delta$ propagation delay. The data will then propagate through the D delay to the input of the B flip-flop, to await the next clock pulse. If the delay of the clock pulse is less than the  $\Delta$  + D delays, illustrated in waveform V, the proper data will be clocked into the B flipflop, illustrated in waveform VI. If the  $\delta$  delay of the clock pulse is greater than the  $\Delta + D$  delays, illustrated in waveform VII, the new data will have arrived at the B flip-flop input before the clock pulse, resulting in this improper data being clocked into the flip-flop. The hazard associated with the clock pulse skew condition is prevented with the incorporation of controlled delays introduced into the data line receivers to insure that the clock pulse propagation delays are less than the data propagation delays.

#### System Mechanization And Considerations

A functional diagram of a typical system is illustrated in Fig. 1, where a central unit communicates with various remote units through relatively long transmission lines. The D and  $\delta$  parameters pertain to the propagation delays through the corresponding transmission lines. Communication is accomplished between the central unit and each of the remote units, where data is transmitted to and from each remote unit. Communication can be accomplished directly between the various remote units, with a minimum of constraints for synchronous transmission. The central unit will generate clock pulses to synchronize the digital data transmission and operation within units and will control the data transmitted between units.

The clock pulses are generated in the central unit, then fanned out to the various remote units. Therefore, the central unit will be clocked first, and the clock pulse will propagate to the remote units, and be followed by

the data change. The system will be constrained so that the clock pulse will arrive at each remote unit before the data change, resulting in the remote unit flipflops being set to the proper states. The data changes due to flip-flops transitions in the remote units will propagate to the central unit and other remote units with an inherently non-critical race condition.

The clock pulse fanout from the central unit should be in a radial manner, where a different clock line is routed directly to each remote unit. A "daisy chain" clock pulse fanout, where a single clock line is strung out from unit to unit, should be avoided to minimize clock pulse skew. The technique will also insure that clock pulse skew need only be considered for data transmissions from the central unit. Data transmissions from remote units will be inherently of a non-critical race type, because the propagation delays insure that data transmitted from the remote unit will not be available at the central unit until after the clock pulse has arrived.

This discussion will neglect certain propagation delays within the central unit and remote units which are of a trivial nature compared to a predominating propagation delay.

The primary system constraint for proper operation is that the largest sum of the data propagation delays must be less than the clock pulse period. The longest delay may be composed of data or clock pulses transmitted from the central unit propagating to a remote unit, data propagating to various other remote units, then data propagating back to the central unit. It should be noted that transmission will be between flip-flops, where the delay is the sum of the logic and transmission propagation delays, to be summed from the output of each flip-flop to the input of other flip-flops.

The primary constraint is described in Equation 8 as an inequality, where the clock period must be greater than the combined propagation delays for:

- a. The clock pulse from the central unit to the particular remote unit  $(\delta)$ .

- b. The data between the various remote units  $(\Sigma D_{\kappa})$ .

- c. The data between the remote unit and the central unit  $(D_R)$ .

The longest propagation delay must satisfy Equation 8 regardless of the combinations of path components. To satisfy this constraint, a compromise must be achieved between clock rate and transmission distance.

Clock Period >

$$\delta + \Sigma D_{\kappa} + D_{R}$$

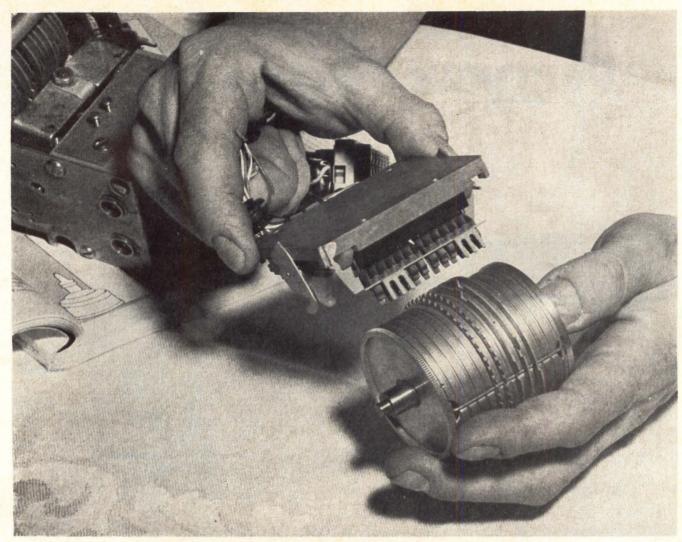

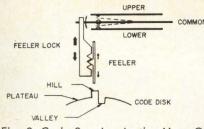

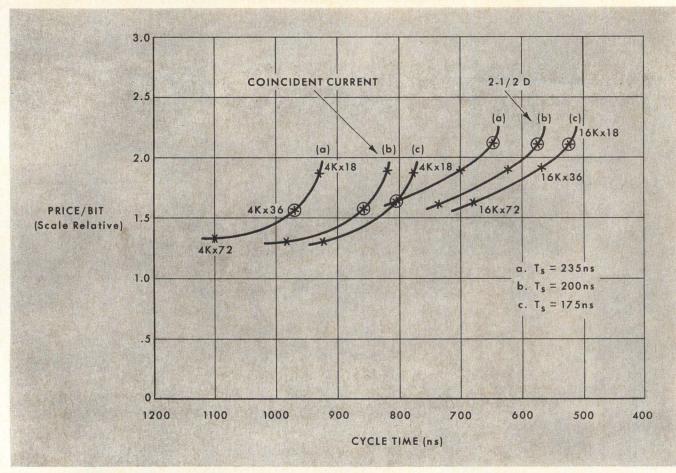

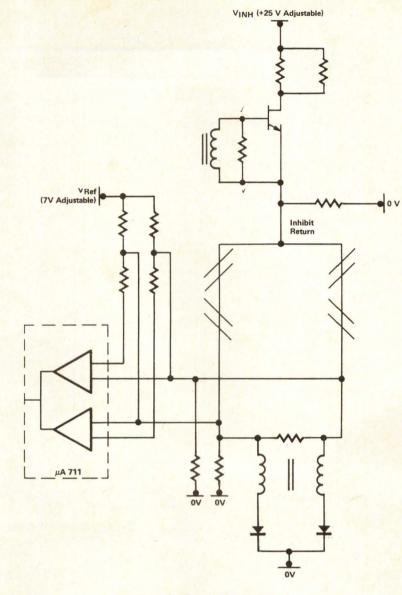

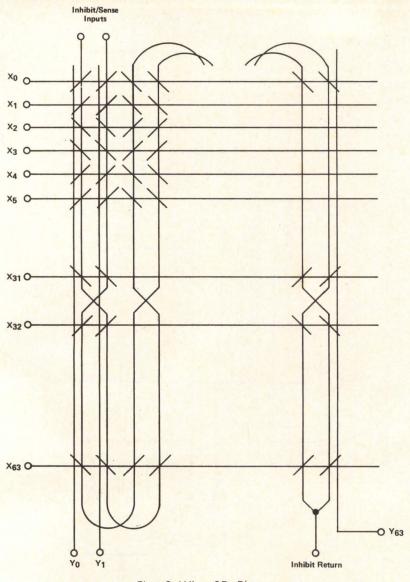

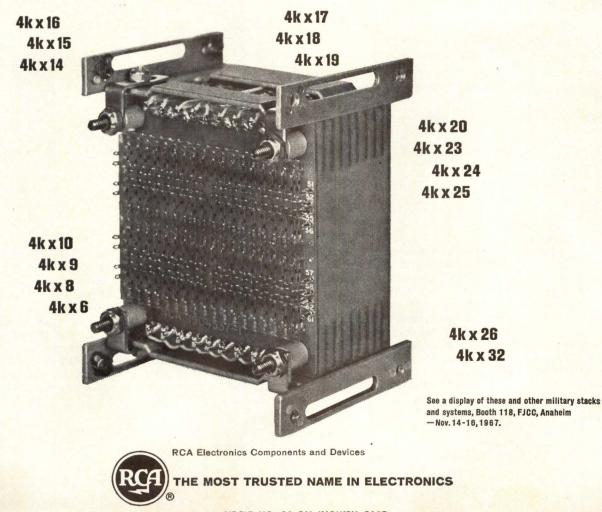

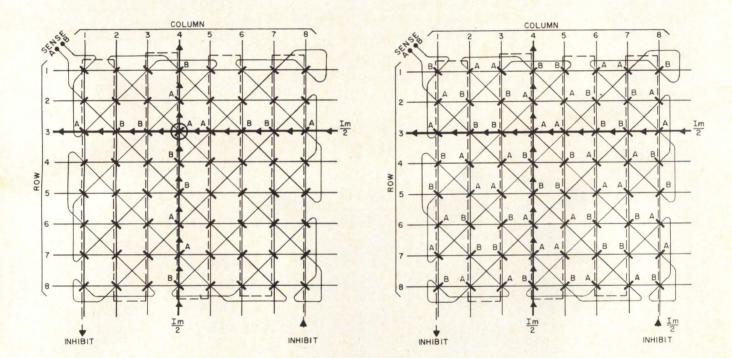

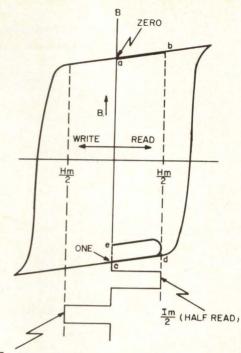

(Eq. 8)