### Alpine<sup>™</sup> VGA Family – CL-GD543X/'4X

**Technical Reference Manual**

February 1995

| Mode<br>No. | VESA®<br>No. | Colors   | Display<br>Resolution | Chars.   | CL-GD5430<br>CL-GD5440<br>Refresh (Hz) | CL-GD5434<br>Refresh (Hz) | CL-GD5436<br>Refresh (Hz) |

|-------------|--------------|----------|-----------------------|----------|----------------------------------------|---------------------------|---------------------------|

| 14, 55      | 109          | 16/256K  | 1056 × 400            | 132 × 25 | 70                                     | 70                        | 70                        |

| 54          | 10A          | 16/256K  | 1056 × 350            | 132 × 43 | 70                                     | 70                        | 70                        |

| 58, 6A      | 102          | 16/256K  | 800 × 600             | 100 × 37 | 56, 60,<br>72, 75                      | 56, 60,<br>72, 75         | 56, 60,<br>72, 75         |

| 5C          | 103          | 256/256K | 800 × 600             | 100 × 37 | 56, 60,<br>72, 75                      | 56, 60,<br>72, 75         | 56, 60,<br>72, 75         |

| 5D          | 104          | 16/256K  | 1024 × 768            | 128 × 48 | 43i, 60,<br>70, 72, 75                 | 43i, 60,<br>70, 72, 75    | 43i, 60,<br>70, 72, 75    |

| 5E          | 100          | 256/256K | 640 × 400             | 80 × 25  | 70                                     | 70                        | 70                        |

| 5F          | 101          | 256/256K | 640 × 480             | 80 × 30  | 60, 72, 75                             | 60, 72, 75                | 60, 72, 75                |

| 60          | 105          | 256/256K | 1024 × 768            | 128 × 48 | 43i, 60,<br>70, 72, 75                 | 43i, 60,<br>70, 72, 75    | 43i, 60,<br>70, 72, 75    |

| 64          | 111          | 64K      | 640 × 480             | -        | 60, 72, 75                             | 60, 72, 75                | 60, 72, 75                |

| 65          | 114          | 64K      | 800 × 600             | -        | 56, 60,<br>72, 75                      | 56, 60,<br>72, 75         | 56, 60,<br>72, 75         |

| 66          | 110          | 32K      | 640 × 480             | _        | 60, 72, 75                             | 60, 72, 75                | 60, 72, 75                |

| 67          | 113          | 32K      | 800 × 600             | _        | 56, 60,<br>72, 75                      | 56, 60,<br>72, 75         | 56, 60,<br>72, 75         |

| 68          | 116          | 32K      | 1024 × 768            | -        | 43i                                    | 43i, 60,<br>70, 75        | 43i, 60,<br>70, 75        |

| 69          | 119          | 32K      | 1280 × 1024           | -        | -                                      | 43i                       | 43i, 60                   |

| 6C          | 106          | 16/256K  | 1280 × 1024           | 160 × 64 | 43i                                    | 43i                       | 43i                       |

| 6D          | 107          | 256/256K | 1280 × 1024           | 160 × 64 | 43i                                    | 43i, 60,<br>71, 75        | 43i, 60,<br>71, 75        |

| 71          | 112          | 16M      | 640 × 480             | -        | 60                                     | 60                        | 60, 72, 75                |

| 72          | -            | 16M + A  | 800 × 600             | -        | _                                      | 56, 60                    | 56, 60                    |

| 73          | -            | 16M + A  | 1024 × 768            | -        | _                                      | 43i                       | -                         |

| 74          | 117          | 64K      | 1024 × 768            | _        | 43i                                    | 43i, 60,<br>70, 75        | 43i, 60,<br>70, 75        |

| 75          | 11A          | 64K      | 1280 × 1024           | -        | _                                      | 43i                       | 43i                       |

| 76          | -            | 16M + A  | 640 × 480             | -        | _                                      | 60, 72, 75                | 60, 72, 75                |

| 78          | 115          | 16M      | 800 × 600             |          | _                                      | _                         | 56, 60,<br>70, 75         |

| 79          | 118          | 16M      | 1024 × 768            |          | -                                      | -                         | 43i, 60,<br>72, 75        |

CL-GD543X/'4X Extended Video Modes Summary

# Alpine VGA Family CL-GD543X/'4X

### **Technical Reference Manual**

Fourth Edition

### Notice

Cirrus Logic, Inc., believes the information contained in this document is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic, Inc., for its use, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights. Trademarks in this document belong to their respective companies. Cirrus Logic, Inc., products are covered under one or more of the following U.S. patents: 4.293,783; Re. 31,287; 4,763,332; 4.777.635: 4.839.896: 4.931.946: 4.975.828; 4.979.173; 5.032.981; 5.122.783; 5,185,602; 5,220,295; 5,131,015; 5,140,595; 5,157,618; 5,179,292; 5,280,488; 5,293,474; 5,297,184; 5,298,915; 5.287.241; 5.291.499; 5,293,159; 5.300.835: 5,327,128; 5,329,554; 5,351,231; 5,359,631; 5,311,460; 5,313,224; 5,384,524; 5,384,786. Additional patents pending.

### **Copyright Notice**

This manual is copyrighted. All rights are reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, or otherwise, without the prior written consent of Cirrus Logic, Inc.

© Copyright 1993, 1994, 1995 — Cirrus Logic, Inc. All rights reserved. First edition published 1993. Fourth edition 1995.

## Contents

### **Revision History**

The following are major changes between the third edition, dated March 1994, and the fourth edition, dated February 1995, of this technical reference manual:

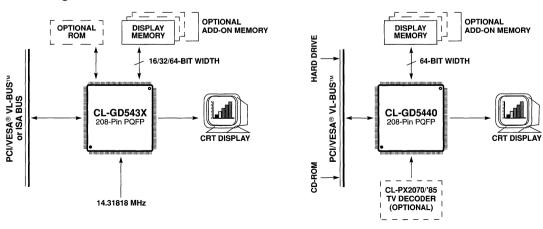

- The CL-GD5440 and the CL-GD5436 were added to the Alpine chip family. Pertinent register, timing, and functionality information was added to both the technical reference manual and the data book.

- Appendices B10 and B16 were added.

- The package diagram names in the data book were updated to remove HQFP package information.

### Table of Contents

| Secti | Section Page |                                                                                                                                 |  |  |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.    | INTR         | ODUCTION                                                                                                                        |  |  |

|       | 1.1          | Scope of Document 1-2                                                                                                           |  |  |

|       | 1.2          | Chip Types Covered 1-2                                                                                                          |  |  |

|       | 1.3          | Intended Audience                                                                                                               |  |  |

|       | 1.4          | Conventions                                                                                                                     |  |  |

| 2.    | OVEF         | RVIEW                                                                                                                           |  |  |

|       | 2.1          | Features                                                                                                                        |  |  |

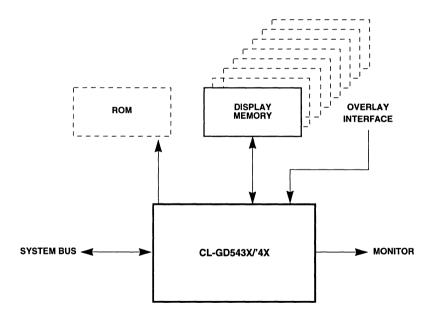

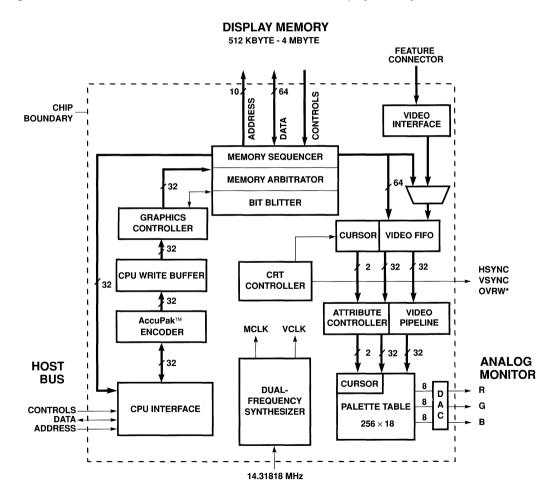

|       | 2.2          | Chip Architecture                                                                                                               |  |  |

|       |              | 2.2.1 Host Access to CL-GD543X/'4X Registers                                                                                    |  |  |

|       |              | 2.2.2 Host Access to Display Memory                                                                                             |  |  |

|       |              | 2.2.3 AccuPak <sup>™</sup> Encoding/Decoding2-4                                                                                 |  |  |

|       |              | 2.2.4 BitBLT Engine Access to Display Memory2-4                                                                                 |  |  |

|       |              | 2.2.5 Display Access to Display Memory2-4                                                                                       |  |  |

|       |              | 2.2.6 Display Memory Refresh2-4                                                                                                 |  |  |

|       | 2.3          | Major Components2-5                                                                                                             |  |  |

|       |              | 2.3.1 Sequencer                                                                                                                 |  |  |

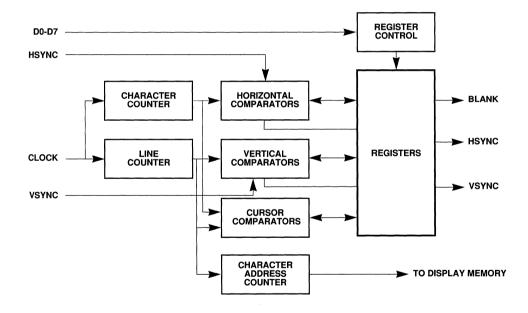

|       |              | 2.3.2 CRT Controller                                                                                                            |  |  |

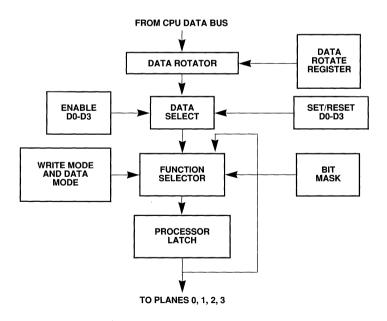

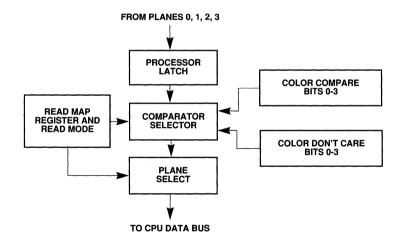

|       |              | 2.3.3 Graphics Controller                                                                                                       |  |  |

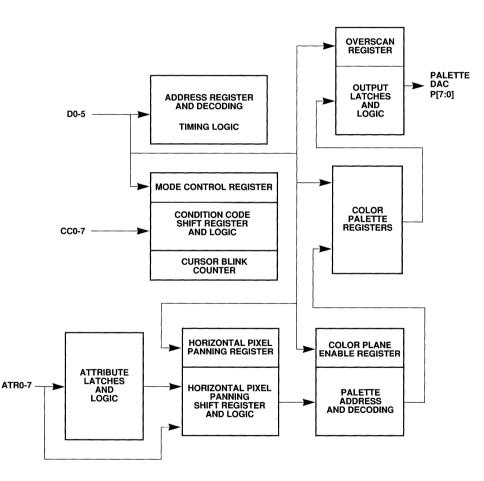

|       |              | 2.3.4 Attribute Controller                                                                                                      |  |  |

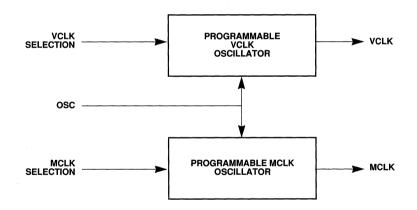

|       |              | 2.3.5 Programmable Dual-Frequency Synthesizer                                                                                   |  |  |

|       |              | 2.3.6 Palette DAC                                                                                                               |  |  |

|       |              | 2.3.7 Local Bus Interface                                                                                                       |  |  |

|       |              | 2.3.8 BitBLT Engine                                                                                                             |  |  |

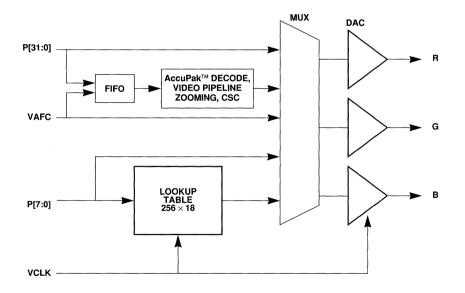

|       |              | 2.3.9 Video Overlay Logic                                                                                                       |  |  |

|       |              | 2.3.10         Video Pipeline (CL-GD5440)         2-12           2.3.11         Video Window Generator (CL-GD5440)         2-12 |  |  |

|       | 2.4          | 2.3.11 Video Window Generator (CL-GD3440)                                                                                       |  |  |

|       | 2.4          | Video Subsystem Architecture                                                                                                    |  |  |

| •     |              | -                                                                                                                               |  |  |

| 3.    | 1.           | A BOOK                                                                                                                          |  |  |

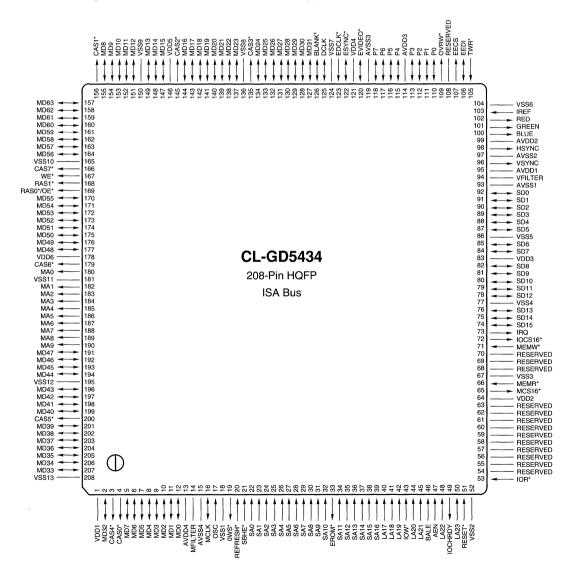

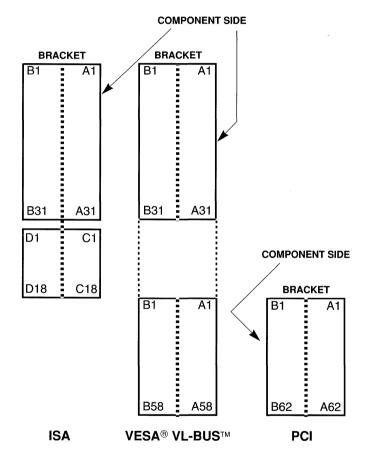

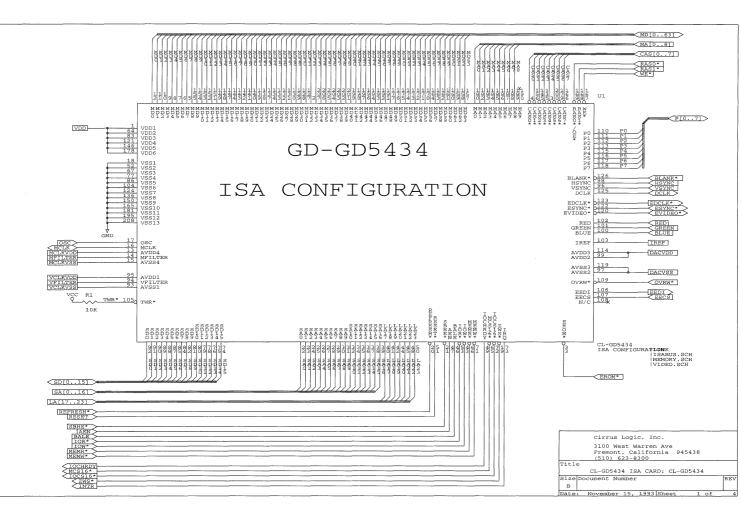

|       | 1.1          | Pin Diagram — ISA Bus (CL-GD5434 Only)                                                                                          |  |  |

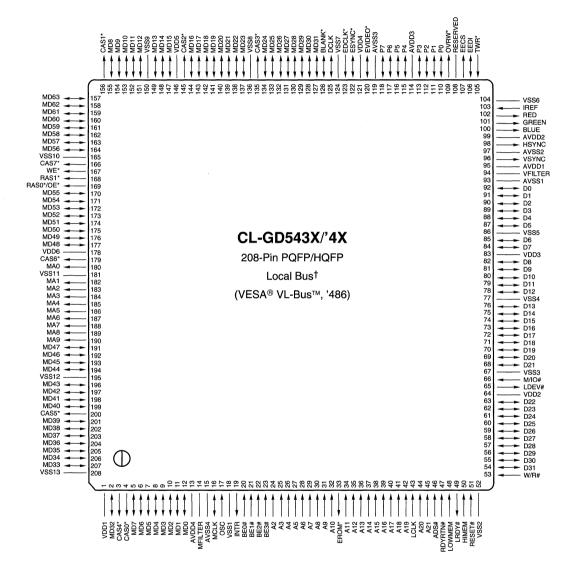

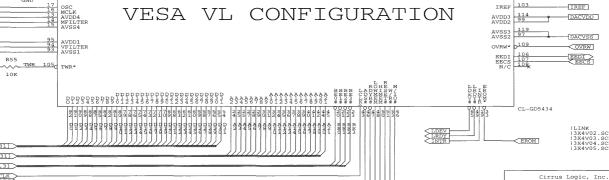

|       | 1.2          | Pin Diagram — Local Bus (VESA® VL-Bus™, '486)                                                                                   |  |  |

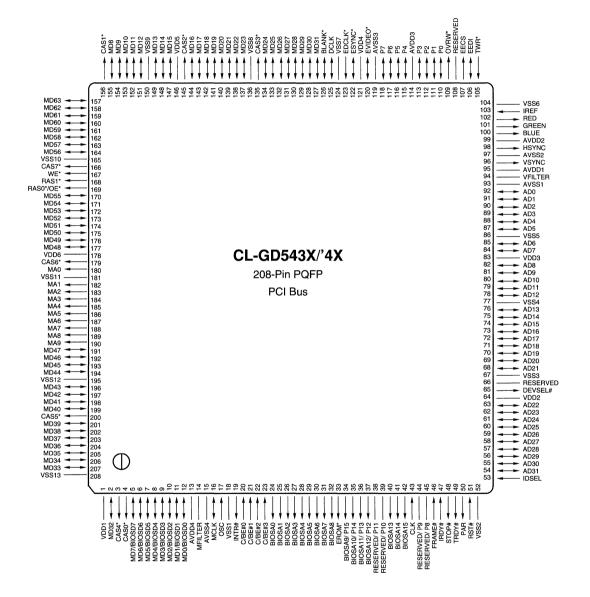

|       | 1.2          | Pin Diagram — PCI Bus                                                                                                           |  |  |

|       | 1.3          | Summary                                                                                                                         |  |  |

|       |              | •                                                                                                                               |  |  |

|       | 2.           | Detailed Pin Descriptions                                                                                                       |  |  |

|       | 2.1          | Host Interface — ISA Bus Mode (CL-GD5434 only)                                                                                  |  |  |

|       | 2.2          | Host Interface — Local Bus Mode                                                                                                 |  |  |

|       |              | 2.2.1 VESA® VL-Bus <sup>™</sup> and '486 Bus Interface                                                                          |  |  |

|       |              | 2.2.2 PCI Bus Interface 3-26                                                                                                    |  |  |

|       | 2.3          | Dual-Frequency Synthesizer Interface                                                                                            |  |  |

| 2.5       Display Memory Interface       3-32         2.6       Miscellaneous Pins       3-33         2.7       Power Pins       3-34         3.       Functional Description       3-35         3.1       General       3-35         3.2       Functional Blocks       3-36         3.2.1       CPU Interface       3-36         3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller       3-36         3.2.4       BitBLT Engine       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.4       Performance       3-38         3.6       Board Testability       3-3                                                                           | 2.4 | Video Interface                           |

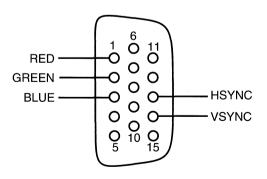

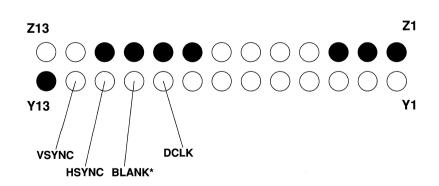

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------|

| 2.7       Power Pins       3-34         3.       Functional Description       3-35         3.1       General       3-35         3.2       Functional Blocks       3-36         3.2.1       CPU Interface       3-36         3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller       3-36         3.2.4       BitBLT Engine       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Arbitrator       3-36         3.2.7       CRT Controller       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller       3-37         3.2.10       Video Fipeloine (CL-GD5440)       3-37         3.2.11       Palete DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         4.       Configuration Tables       3-39         4.1       Video Modes       3-39         <                                                                                                 | 2.5 | Display Memory Interface                  |

| 3.       Functional Description       3-35         3.1       General       3-35         3.2       Functional Blocks       3-36         3.2.1       CPU Interface       3-36         3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller       3-36         3.2.4       BitBLT Engine       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller       3-37         3.2.8       Video FIFO       3-37         3.2.10       Video FIFO       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.2.14       Performance       3-38         3.5       Comfiguration Tables       3-38         3.6       Board Testability       3-38         3.6       Configuration Re                                                                  | 2.6 | Miscellaneous Pins                        |

| 3.1       General       3-35         3.2       Functional Blocks       3-36         3.2.1       CPU Interface       3-36         3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller.       3-36         3.2.4       BitBLT Engine.       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller.       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller.       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         3.6       Board Testability       3-38         3.6       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuration Register,                                                                  | 2.7 | Power Pins                                |

| 3.2       Functional Blocks       3-36         3.2.1       CPU Interface       3-36         3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller       3-36         3.2.4       BitBLT Engine       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Sequencer       3-37         3.2.7       CRT Controller       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.3       Functional Operation       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         3.6       Board Testability       3-38         3.6       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuratin Register, CF       3-443                                                                                  | З.  | Functional Description                    |

| 3.2.1       CPU Interface       3-36         3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller       3-36         3.2.4       BitBLT Engine       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller       3-37         3.2.10       Video Fipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.3       Functional Operation       3-37         3.4       Performance       3-38         5.       Compatibility       3-38         4.       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuration Register, CF       3-43         4.3       Host Interface Signals       3-44         5.       VGA Register Port MAP       3-45         6.       CL-GD543X/4X Registers       3                                                                           | 3.1 | General                                   |

| 3.2.2       CPU Write Buffer       3-36         3.2.3       Graphics Controller.       3-36         3.2.4       BitBLT Engine.       3-36         3.2.5       Memory Arbitrator       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller.       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller.       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         4.       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuration Register, CF       3-43         4.3       Host Interface Signals       3-44         5.       VGA Register Port MAP       3-45         6.       CL-GD543X/4X Registers       3-46         7.       Electrical Specifications                                                                        | 3.2 | Functional Blocks                         |

| 3.2.3       Graphics Controller.       3-36         3.2.4       BitBLT Engine.       3-36         3.2.5       Memory Arbitrator.       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller.       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller.       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.2       Tunctional Operation       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         4.       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuration Register, CF       3-44         5.       VGA Register Port MAP       3-45         6.       CL-GD543X/4X Registers       3-46         7.       Electrical Specifications       3-51         7.4       DC Specifications (Palett                                                                  |     | 3.2.1 CPU Interface                       |

| 3.2.4       BitBLT Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 3.2.2 CPU Write Buffer                    |

| 3.2.5       Memory Arbitrator.       3-36         3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller.       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller.       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         3.6       Board Testability       3-38         4.       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuration Register, CF       3-43         4.3       Host Interface Signals       3-44         5.       VGA Register Port MAP       3-45         6.       CL-GD543X/4X Registers       3-46         7.1       Absolute Maximum Ratings       3-51         7.2       DC Specif                                                                  |     | 3.2.3 Graphics Controller                 |

| 3.2.6       Memory Sequencer       3-36         3.2.7       CRT Controller       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.3       Functional Operation       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         3.6       Board Testability       3-38         4.       Configuration Tables       3-39         4.2       Configuration Register, CF       3-43         4.3       Host Interface Signals       3-44         5.       VGA Register Port MAP       3-45         6.       CL-GD543X/4X Registers       3-46         7.4       DC Specifications (Digital)       3-52         7.3       DC Specifications (Palette DAC)       3-53         7.4       DC Specifications (Frequency Synthesizer)       3-53         7                                                         |     | 3.2.4 BitBLT Engine                       |

| 3.2.7       CRT Controller.       3-37         3.2.8       Video FIFO       3-37         3.2.9       Attribute Controller.       3-37         3.2.10       Video Pipeline (CL-GD5440)       3-37         3.2.11       Palette DAC       3-37         3.2.12       Dual-Frequency Synthesizer       3-37         3.2.13       VESA®/VGA Pass-through Connector       3-37         3.3       Functional Operation       3-37         3.4       Performance       3-38         3.5       Compatibility       3-38         3.6       Board Testability       3-38         3.6       Board Testability       3-38         4.       Configuration Tables       3-39         4.1       Video Modes       3-39         4.2       Configuration Register, CF       3-43         4.3       Host Interface Signals       3-44         5.       VGA Register Port MAP       3-45         6.       CL-GD543X/4X Registers       3-46         7.       Electrical Specifications (Digital)       3-52         7.3       DC Specifications (Palette DAC)       3-53         7.4       DC Specifications (Frequency Synthesizer)       3-53 <td< td=""><td></td><td>3.2.5 Memory Arbitrator 3-36</td></td<> |     | 3.2.5 Memory Arbitrator 3-36              |

| 3.2.8Video FIFO3-373.2.9Attribute Controller.3-373.2.10Video Pipeline (CL-GD5440)3-373.2.11Palette DAC3-373.2.12Dual-Frequency Synthesizer3-373.2.13VESA®/VGA Pass-through Connector3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-383.6Board Testability3-384.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Frequency Synthesizer)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 3.2.6 Memory Sequencer 3-36               |

| 3.2.9Attribute Controller.3-373.2.10Video Pipeline (CL-GD5440)3-373.2.11Palette DAC.3-373.2.12Dual-Frequency Synthesizer3-373.2.13VESA®/VGA Pass-through Connector3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 3.2.7 CRT Controller                      |

| 3.2.10Video Pipeline (CL-GD5440)3-373.2.11Palette DAC3-373.2.12Dual-Frequency Synthesizer3-373.2.13VESA®/VGA Pass-through Connector3-373.3Functional Operation3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                                           |

| 3.2.11Palette DAC3-373.2.12Dual-Frequency Synthesizer3-373.2.13VESA®/VGA Pass-through Connector3-373.3Functional Operation3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Frequency Synthesizer)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                                           |

| 3.2.12Dual-Frequency Synthesizer3-373.2.13VESA®/VGA Pass-through Connector3-373.3Functional Operation3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |                                           |

| 3.2.13VESA®/VGA Pass-through Connector3-373.3Functional Operation3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                                           |

| 3.3Functional Operation3-373.4Performance3-383.5Compatibility3-383.6Board Testability3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                                           |

| 3.4Performance3-383.5Compatibility3-383.6Board Testability3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | •                                         |

| 3.5Compatibility3-383.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | •                                         |

| 3.6Board Testability3-384.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                                           |

| 4.Configuration Tables3-394.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.5 |                                           |

| 4.1Video Modes3-394.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.6 |                                           |

| 4.2Configuration Register, CF3-434.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/'4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.  |                                           |

| 4.3Host Interface Signals3-445.VGA Register Port MAP3-456.CL-GD543X/'4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.1 | Video Modes                               |

| 5.VGA Register Port MAP3-456.CL-GD543X/'4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.2 | Configuration Register, CF3-43            |

| 6.CL-GD543X/4X Registers3-467.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.3 | Host Interface Signals3-44                |

| 7.Electrical Specifications3-517.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.  | VGA Register Port MAP3-45                 |

| 7.1Absolute Maximum Ratings3-517.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.  | CL-GD543X/'4X Registers3-46               |

| 7.2DC Specifications (Digital)3-527.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.  | Electrical Specifications                 |

| 7.3DC Specifications (Palette DAC)3-537.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.1 | Absolute Maximum Ratings3-51              |

| 7.4DC Specifications (Frequency Synthesizer)3-537.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.2 | DC Specifications (Digital)               |

| 7.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.3 | DC Specifications (Palette DAC)           |

| 7.5DAC Characteristics3-547.6List of Waveforms3-557.7Electrical Specifications3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.4 | DC Specifications (Frequency Synthesizer) |

| 7.6       List of Waveforms       3-55         7.7       Electrical Specifications       3-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.5 |                                           |

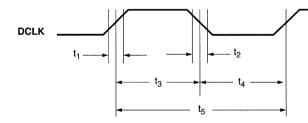

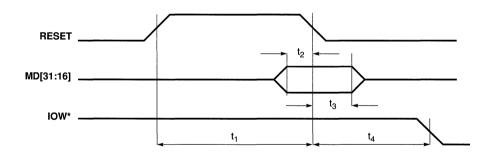

| 7.7 Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.6 |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                                           |

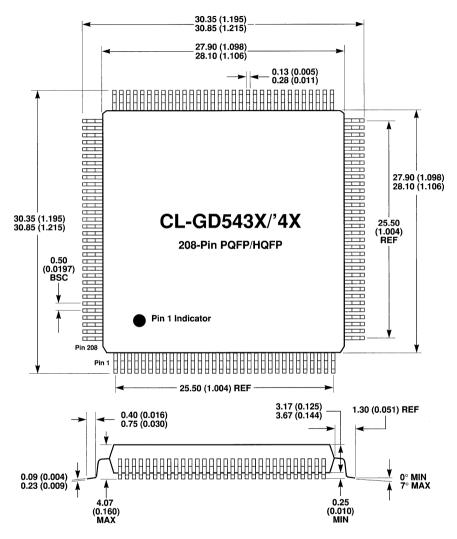

| 8. Package Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.  | Package Specifications                    |

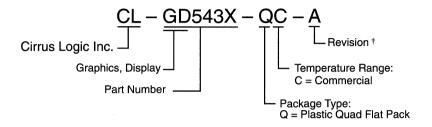

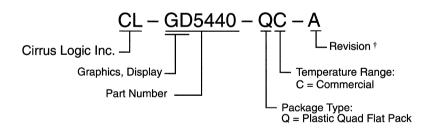

| 9. Ordering Information Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 5                                         |

| 4. | EXTE | RNAL AND GENERAL REGISTERS4-2                                            |

|----|------|--------------------------------------------------------------------------|

|    | 4.1  | POS94: POS94 Register 4-3                                                |

|    | 4.2  | POS102: POS102 Register 4-4                                              |

|    | 4.3  | VSSM: 3C3 Sleep Address Register 4-5                                     |

|    | 4.4  | VSSM: 46E8 Sleep Address Register 4-6                                    |

|    | 4.5  | MISC: Miscellaneous Output Register 4-7                                  |

|    | 4.6  | FC: Feature Control Register4-9                                          |

|    | 4.7  | FEAT: Input Status Register 0 4-10                                       |

|    | 4.8  | STAT: Input Status Register 1 4-11                                       |

|    | 4.9  | Pixel Mask Register 4-12                                                 |

|    | 4.10 | Pixel Address Register (Read Mode, Write-only)4-13                       |

|    | 4.11 | DAC State Register (Read Mode)4-14                                       |

|    | 4.12 | Pixel Address Register (Write Mode)4-15                                  |

|    | 4.13 | Pixel Data Register4-16                                                  |

|    | 4.14 | PCI00: PCI Device/Vendor ID Register 4-17                                |

|    | 4.15 | PCI04: PCI Command Register4-18                                          |

|    | 4.16 | PCI04: PCI Status Register4-19                                           |

|    | 4.17 | PCI08: PCI Class Code Register 4-20                                      |

|    | 4.18 | PCI10: PCI Display Memory Base Address Register                          |

|    | 4.19 | PCI14: PCI Relocatable I/O Base Address Register ('30/'36/'40 only) 4-22 |

|    | 4.20 | PCI30: PCI Expansion ROM Base Address Enable Register                    |

|    | 4.21 | PCI3C: PCI Interrupt Line Register                                       |

|    | 4.22 | PCI3C: PCI Interrupt Pin Register 4-25                                   |

| 5. | VGA  | SEQUENCER REGISTERS5-2                                                   |

|    | 5.1  | SRX: Sequencer Index Register5-3                                         |

|    | 5.2  | SR0: Reset Register5-4                                                   |

|    | 5.3  | SR1: Clocking Mode Register5-5                                           |

|    | 5.4  | SR2: Plane Mask Register5-7                                              |

|    | 5.5  | SR3: Character Map Select Register5-8                                    |

|    | 5.6  | SR4: Memory Mode Register5-10                                            |

| 6. | CRT  | CONTROLLER REGISTERS6-2                                                  |

|    | 6.1  | CRX: CRTC Index Register6-4                                              |

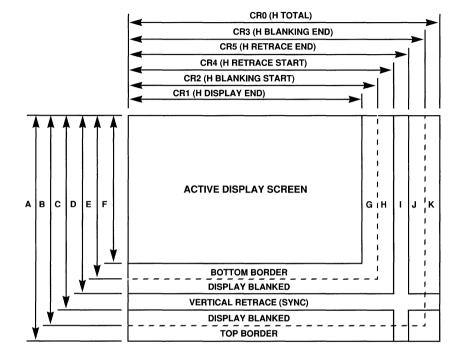

|    | 6.2  | CR0: Horizontal Total Register6-7                                        |

|    | 6.3  | CR1: Horizontal Display End Register6-8                                  |

|    | 6.4  | CR2: Horizontal Blanking Start Register6-9                               |

|    | 6.5  | CR3: Horizontal Blanking End Register6-10                                |

|    | 6.6  | CR4: Horizontal Sync Start Register6-12                                  |

|    | 6.7  | CR5: Horizontal Sync End Register6-13                                    |

|    | 6.8  | CR6: Vertical Total Register6-15                                         |

|    | 6.9  | CR7: Overflow Register6-16                                               |

|    | 6.10 | CR8: Screen A Preset Row-Scan Register                                   |

|    | 6.11 | CR9: Character Cell Height Register6-18                 |

|----|------|---------------------------------------------------------|

|    | 6.12 | CRA: Text Cursor Start Register6-19                     |

|    | 6.13 | CRB: Text Cursor End Register6-20                       |

|    | 6.14 | CRC: Screen Start Address High Register6-21             |

|    | 6.15 | CRD: Screen Start Address Low Register6-22              |

|    | 6.16 | CRE: Text Cursor Location High Register6-23             |

|    | 6.17 | CRF: Text Cursor Location Low Register6-24              |

|    | 6.18 | CR10: Vertical Sync Start Register6-25                  |

|    | 6.19 | CR11: Vertical Sync End Register6-26                    |

|    | 6.20 | CR12: Vertical Display End Register6-27                 |

|    | 6.21 | CR13: Offset Register6-28                               |

|    | 6.22 | CR14: Underline Row Scanline Register6-29               |

|    | 6.23 | CR15: Vertical Blank Start Register6-30                 |

|    | 6.24 | CR16: Vertical Blank End Register6-31                   |

|    | 6.25 | CR17: Mode Control Register6-32                         |

|    | 6.26 | CR18: Line Compare Register6-34                         |

|    | 6.27 | CR22: Graphics Data Latches Readback Register6-35       |

|    | 6.28 | CR24: Attribute Controller Toggle Readback Register6-36 |

|    | 6.29 | CR26: Attribute Controller Index Readback Register6-37  |

| 7. | VGA  | GRAPHICS CONTROLLER REGISTERS                           |

|    | 7.1  | GRX: Graphics Controller Index Register7-3              |

|    | 7.2  | GR0: Set/Reset Register7-4                              |

|    | 7.3  | GR1: Set/Reset Enable Register7-5                       |

|    | 7.4  | GR2: Color Compare Register7-6                          |

|    | 7.5  | GR3: Data Rotate Register7-7                            |

|    | 7.6  | GR4: Read Map Select Register7-8                        |

|    | 7.7  | GR5: Mode Register7-9                                   |

|    | 7.8  | GR6: Miscellaneous Register7-12                         |

|    | 7.9  | GR7: Color Don't Care Register7-13                      |

|    | 7.10 | GR8: Bit Mask Register7-14                              |

| 8. |      | RIBUTE CONTROLLER REGISTERS 8-2                         |

|    | 8.1  | ARX: Attribute Controller Index Register8-3             |

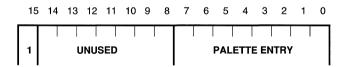

|    | 8.2  | AR0-ARF: Attribute Controller Palette Registers8-4      |

|    | 8.3  | AR10: Attribute Controller Mode Register8-5             |

|    | 8.4  | AR11: Overscan (Border) Color Register8-7               |

|    | 8.5  | AR12: Color Plane Enable Register8-8                    |

|    | 8.6  | AR13: Pixel Panning Register8-9                         |

|    | 8.7  | AR14: Color Select Register8-10                         |

| 9. |      | ENSION REGISTERS                                        |

|    | 9.1  | SR6: Unlock All Extensions Register9-5                  |

|    | 9.2  | SR7: Extended Sequencer Mode Register9-6                |

| 9.3  | SR8: EEPROM Control / DDC2B Control Register                              |

|------|---------------------------------------------------------------------------|

| 9.4  | SR9, SRA: Scratch Pad 0, 1 Registers9-11                                  |

| 9.5  | SRB, SRC, SRD, SRE: VCLK0, 1, 2, 3 Numerator Registers9-12                |

| 9.6  | SRF: DRAM Control Register9-13                                            |

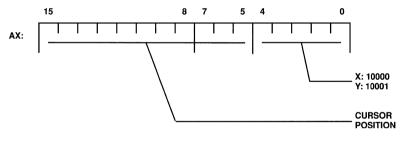

| 9.7  | SR10: Graphics Cursor X Position Register9-15                             |

| 9.8  | SR11: Graphics Cursor Y Position Register9-16                             |

| 9.9  | SR12: Graphics Cursor Attributes Register9-17                             |

| 9.10 | SR13: Graphics Cursor Pattern Address Offset Register9-18                 |

| 9.11 | SR14, SR15: Scratch Pad 2, 3 Registers9-19                                |

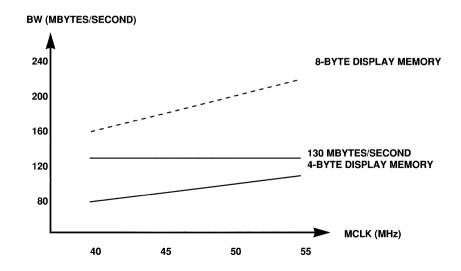

| 9.12 | SR16: Performance Tuning Register9-20                                     |

| 9.13 | SR17: Configuration Readback and Extended Control Register9-22            |

| 9.14 | SR18: Signature Generator Control Register9-24                            |

| 9.15 | SR19: Signature Generator Result Low-Byte Register9-26                    |

| 9.16 | SR1A: Signature Generator Result High-Byte Register9-27                   |

| 9.17 | SR1B, SR1C, SR1D, SR1E: Denominator and Post-Scalar Registers9-28         |

| 9.18 | SR1F: MCLK Select Register9-29                                            |

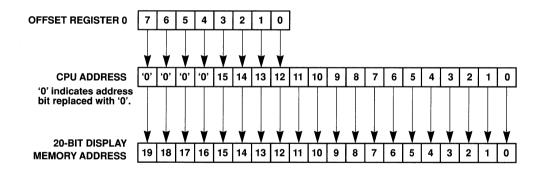

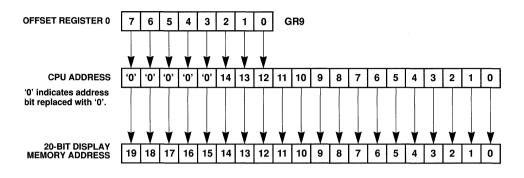

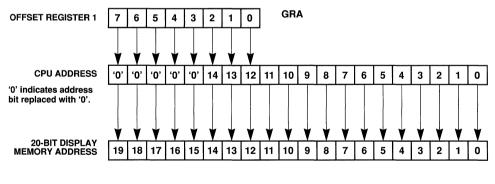

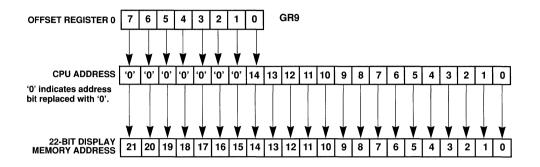

| 9.19 | GR9: Offset Register 09-31                                                |

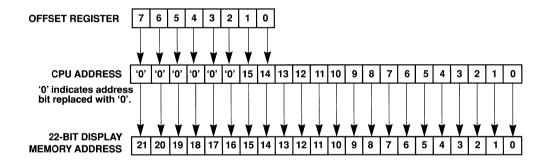

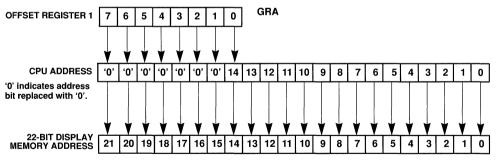

| 9.20 | GRA: Offset Register 19-33                                                |

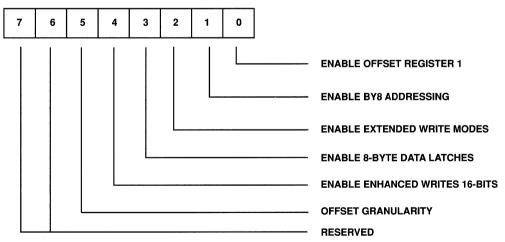

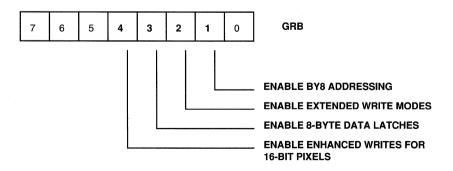

| 9.21 | GRB: Graphics Controller Mode Extensions Register9-34                     |

| 9.22 | GRC: Color Key Compare Register9-36                                       |

| 9.23 | GRD: Color Key Compare Mask Register9-37                                  |

| 9.24 | GRE: Power Management Register9-38                                        |

| 9.25 | GR10: Background Color Byte 1 Register9-40                                |

| 9.26 | GR11: Foreground Color Byte 1 Register9-41                                |

| 9.27 | GR12: Background Color Byte 2 Register (CL-GD5434/'36 only)9-42           |

| 9.28 | GR13: Foreground Color Byte 2 Register (CL-GD5434/'36 only)9-43           |

| 9.29 | GR14: Background Color Byte 3 Register (CL-GD5434/'36 only)9-44           |

| 9.30 | GR15: Foreground Color Byte 3 Register (CL-GD5434/'36 only)9-45           |

| 9.31 | GR18: Extended DRAM Controls (CL-GD5430/'36/'40 Only)9-46                 |

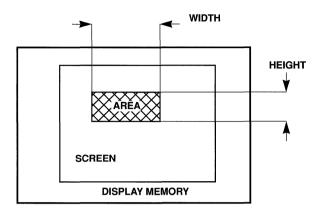

| 9.32 | GR20, 21: BLT Width Byte 0, 1 Registers9-48                               |

| 9.33 | GR22, 23: BLT Height Byte 0, 1 Registers9-49                              |

| 9.34 | GR24, 25: BLT Destination Pitch Byte 0, 1 Register9-50                    |

| 9.35 | GR26, 27: BLT Source Pitch Byte 0, 1 Registers9-51                        |

| 9.36 | GR28, 29, 2A: BLT Destination Start Byte 0, 1, 2 Registers9-52            |

| 9.37 | GR2C, 2D, 2E: BLT Source Start Byte 0, 1, 2 Registers9-53                 |

| 9.38 | GR2F: BLT Destination Write Mask Register<br>(CL-GD5430/'36/'40 only)9-54 |

| 9.39 | GR30: BLT Mode Register9-55                                               |

| 9.40 | GR31: BLT Start/Status Register9-58                                       |

| 9.41 | GR32: BLT Raster Operation (ROP) Register9-60                             |

| 9.42 | GR33: BLT Mode Extensions Register9-62                                    |

| 9.43 | CR19: Interlace End Register                                              |

|     | 9.44 | CR1A: Miscellaneous Control Register                                                     | 9-64 |

|-----|------|------------------------------------------------------------------------------------------|------|

|     | 9.45 | CR1B: Extended Display Controls Register                                                 | 9-66 |

|     | 9.46 | CR1C: Sync Adjust and GENLOCK Register (CL-GD5434/'36 only)                              | 9-68 |

|     | 9.47 | CR1D: Overlay Extended Control Register                                                  | 9-70 |

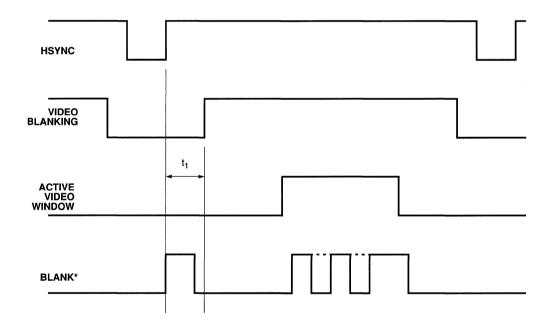

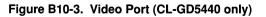

|     | 9.48 | CR1E: Video Port Configuration (CL-GD5440 only)                                          | 9-72 |

|     | 9.49 | CR25: Part Status Register (Read-only)                                                   | 9-74 |

|     | 9.50 | CR27: ID Register (Read-only)                                                            | 9-75 |

|     | 9.51 | CR28: Class ID Register (Read-only) (CL-GD5430 only)                                     | 9-76 |

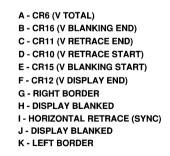

|     | 9.52 | CR31: Video Window Horizontal Zoom Control (CL-GD5440 only)                              | 9-77 |

|     | 9.53 | CR32: Video Window Vertical Zoom Control (CL-GD5440 only)                                | 9-78 |

|     | 9.54 | CR33: Video Window Horizontal Region 1 Size (CL-GD5440 only)                             | 9-79 |

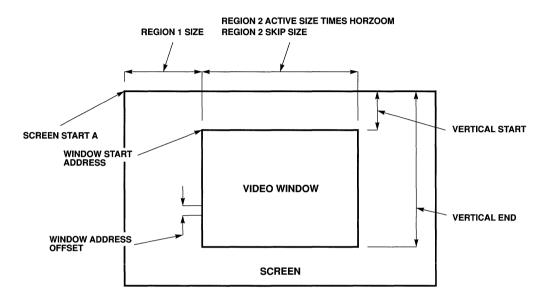

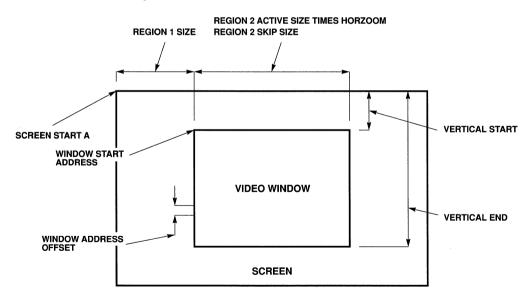

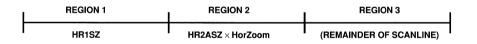

|     | 9.55 | Video Window Definition: An Overview (CL-GD5440 only)                                    | 9-80 |

|     | 9.56 | CR34: Video Window Region 2 Skip Size (CL-GD5440 only)                                   | 9-81 |

|     | 9.57 | CR35: Video Window Region 2 Active Size (CL-GD5440 only)                                 | 9-82 |

|     | 9.58 | CR36: Video Window Horizontal Overflow (CL-GD5440 only)                                  | 9-83 |

|     | 9.59 | CR37: Video Window Vertical Start (CL-GD5440 only)                                       | 9-84 |

|     | 9.60 | CR38: Video Window Vertical End (CL-GD5440 only)                                         | 9-85 |

|     | 9.61 | CR39: Video Window Vertical Overflow (CL-GD5440 only)                                    | 9-86 |

|     | 9.62 | CR3A, 3B: Video Window Start Address Byte 0, 1 (CL-GD5440 only)                          | 9-87 |

|     | 9.63 | CR3C: Video Window Start Address Byte 2 (CL-GD5440 only)                                 | 9-88 |

|     | 9.64 | CR3D: Video Window Address Offset (CL-GD5440 only)                                       |      |

|     | 9.65 | CR3E: Video Window Master Control (CL-GD5440 only)                                       | 9-90 |

|     | 9.66 | CR3F: Host Video Data Path Control (CL-GD5440 only)                                      | 9-92 |

|     | 9.67 | HDR: Hidden DAC Register                                                                 | 9-94 |

| 10. | VGA  | BIOS                                                                                     | 10-2 |

|     | 10.1 | BIOS Overview                                                                            |      |

|     |      | 10.1.1 Main BIOS Features                                                                | 10-2 |

|     |      | 10.1.2 Extended Video Mode Support                                                       | 10-2 |

|     |      | 10.1.3 Direct-Color Operation                                                            | 10-2 |

|     |      | 10.1.4 High Performance                                                                  |      |

|     |      | 10.1.5 System Integration                                                                |      |

|     |      | 10.1.6 Customization                                                                     |      |

|     |      | 10.1.7 Compatibility                                                                     |      |

|     | 10.2 | CL-GD543X/'4X VGA BIOS Initialization and Power-Up Diagnostics                           |      |

|     | 10.3 | Video BIOS Interrupt Vectors                                                             |      |

|     |      | 10.3.1 Interrupt 10H: BIOS Video Service Routines Contents                               |      |

|     | 10.4 | Description Of Functions                                                                 |      |

|     |      | 10.4.1 Function: 00H I Set Video Mode                                                    |      |

|     |      | 10.4.2 Function: 01H   Set Cursor Type                                                   |      |

|     |      | 10.4.3 Function: 02H I Set Cursor Position<br>10.4.4 Function: 03H I Get Cursor Position |      |

|     |      | 10.4.5 Function: 04H I Get Light Pen Position                                            |      |

|     |      | 10.4.6 Function: 05H I Select Active Display Page                                        |      |

|     |      | To the induction of the colocition to bolicate Display I age                             |      |

|     |                      | 10                                                                                                                                                   | 0.4.7 Function: 06H I Window Scroll Up                                                                                       | 10-12                                                                                                                                |