Technical Manual No. 799816-007 Revision B

### MODELS M890 AND M891 CACHETAPE UNIT

### VOLUME II

## THEORY OF OPERATION

Cipher Data Products 10225 Willow Creek Road San Diego, California 92131

• Copyright 1984 by Cipher Data Products Printed in U.S.A.

January 1985

## VOLUME II

## TABLE OF CONTENTS

# Section

I

11

# Title

## Page No.

| DESCRIPTION AND SPECIFICATIONS                      | - :  |

|-----------------------------------------------------|------|

| PHYSICAL DESCRIPTION                                | _    |

| PHYSICAL TAPE DRIVE MECHANISM                       | 1-1  |

| FUNCTIONAL DESCRIPTION                              | 1-2  |

| MECHANICAL AND ELECTRICAL SPECIFICATIONS            | _4   |

| INTERFACE SPECIFICATIONS                            | 1-4  |

| THEORY OF OPERATION                                 | 2-1  |

| GENERAL                                             | 2-1  |

| BASIC CONCEPTS OF DIGITAL RECORDING                 | 2-1  |

| DATA RECORDING/READING WITH MAGNETIC TAPE.          | 2-1  |

| Phase-Encode System                                 | 2-3  |

| CACHE-TAPE OPERATION                                | 2-5  |

| STREAMING-TAPE OPERATION                            | 2-5  |

| Repositioning                                       | 2-7  |

| MAJOR TRANSPORT COMPONENTS                          | 2-10 |

| Power Supply/System Failure Detect Circuit          | 2-10 |

| Control Logic Circuitry                             | 2-10 |

| Takeup/Supply Servo Circuits                        | 2-10 |

| Sensor Input Circuits                               | 2-10 |

| Write Circuitry                                     | 2-10 |

| Read Circuitry                                      | 2-10 |

| DETAILED CIRCUIT DESCRIPTIONS                       | 2-10 |

| Power Supply                                        | 2-10 |

| Voltage Regulators                                  | 2-10 |

| Power Control and System<br>Failure Detect Circuits | 2-12 |

## TABLE OF CONTENTS (Continued)

Section

## Title

| Microprocessor Section            | 2-12 |

|-----------------------------------|------|

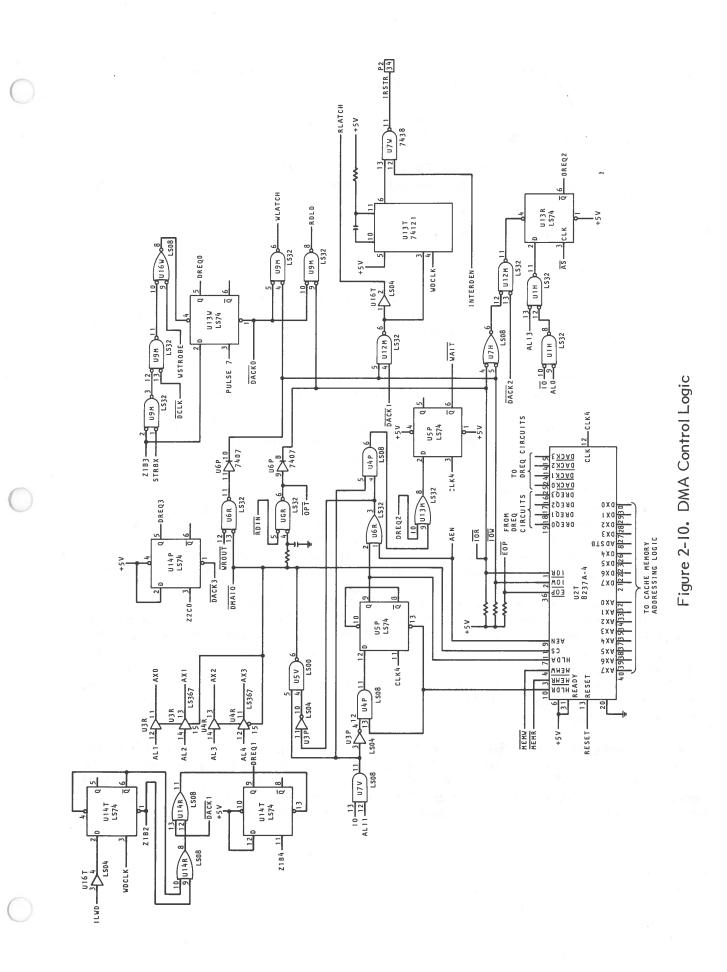

| DMA Control Logic                 | 2-16 |

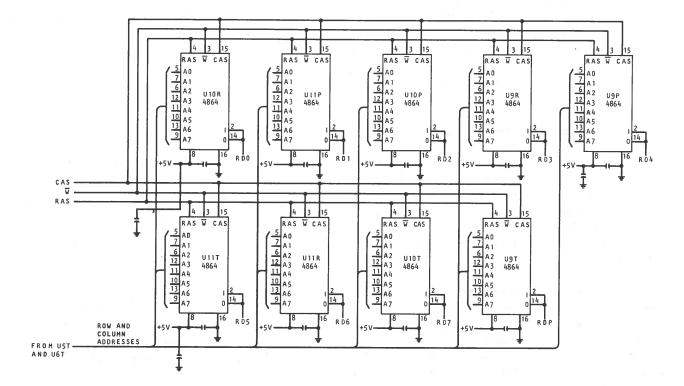

| Cache Memory                      | 2-18 |

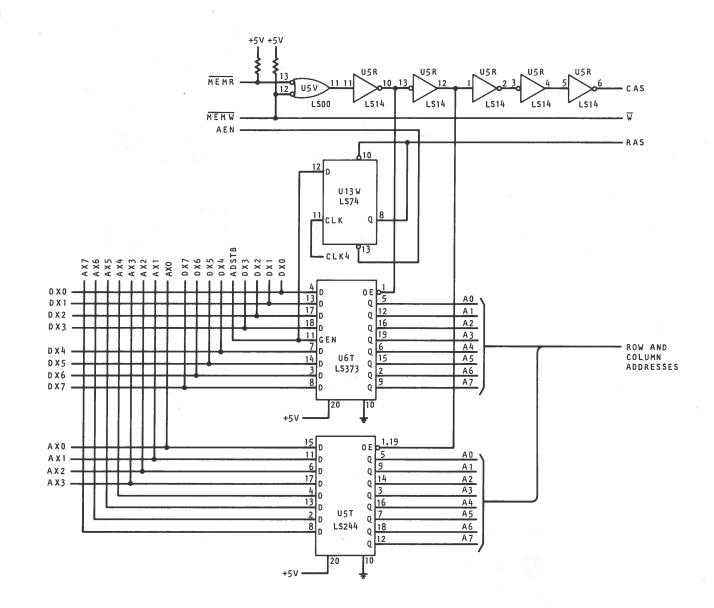

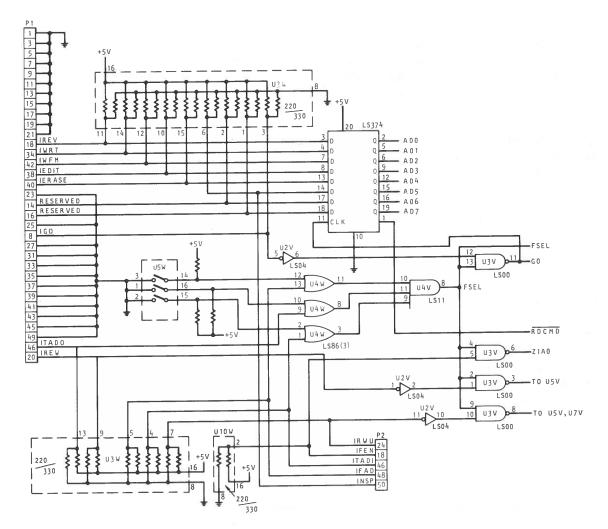

| Cache Memory Addressing Logic     | 2-20 |

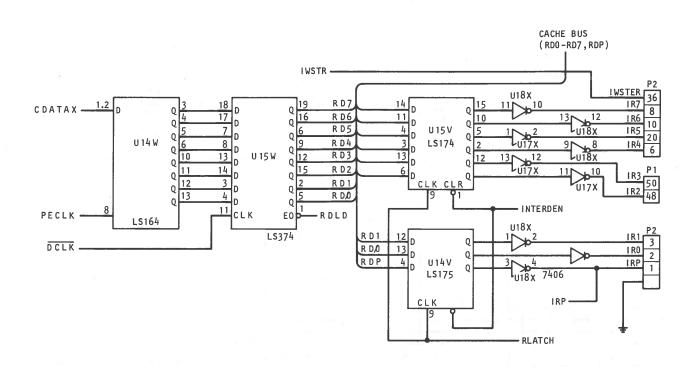

| Cache Read Circuit                | 2-20 |

| Cache Write Circuit               | 2-20 |

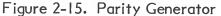

| Parity Generator                  | 2-20 |

| EPROM and RAM Circuits            | 2-23 |

| Transport Status Registers        | 2-23 |

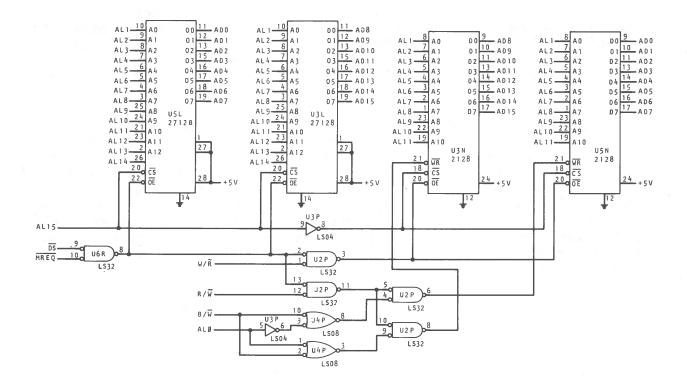

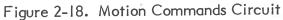

| Motion Commands Circuit           | 2-26 |

| Input Sensors                     | 2-26 |

| EOT/BOT Sensors                   | 2-26 |

| File Protect/Reel Seat Sensor     | 2-26 |

| Tape–In–Path Sensor               | 2-26 |

| Optical Tachometer                | 2-28 |

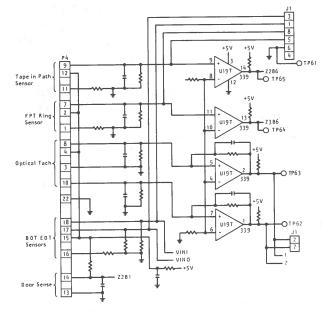

| Digital-To-Analog Converter (DAC) | 2-28 |

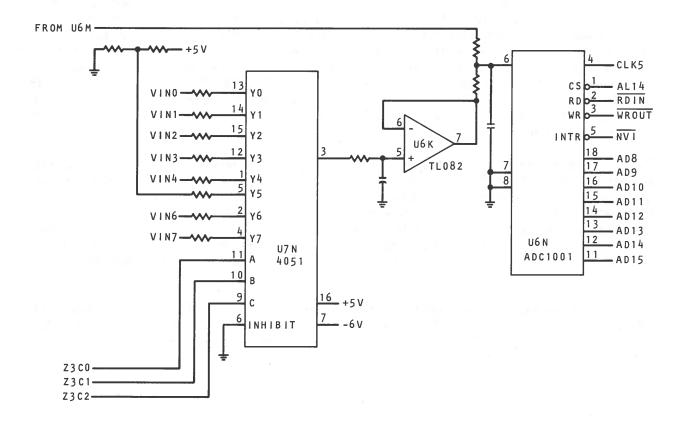

| Analog-To-Digital Converter       | 2-28 |

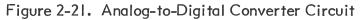

| Supply and Takeup Servo Circuit   | 2-30 |

| Arm Position and Rate Circuit     | 2-30 |

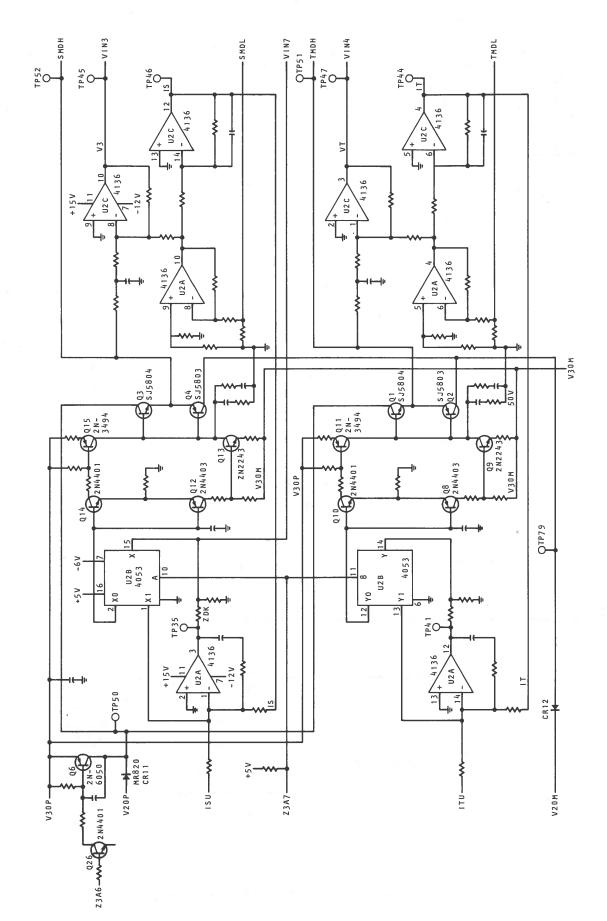

| Write Voltage Control             | 2-30 |

| Write Formatting Control Circuit  | 2-30 |

| ID Burst Generation               | 2-34 |

| Preamble Generation               | 2-34 |

| Write Data Block Operation        | 2-38 |

| Postamble Generation              | 2-38 |

| File Mark Generation              | 2-41 |

| Test/Diagnostic Write Operation   | 2-41 |

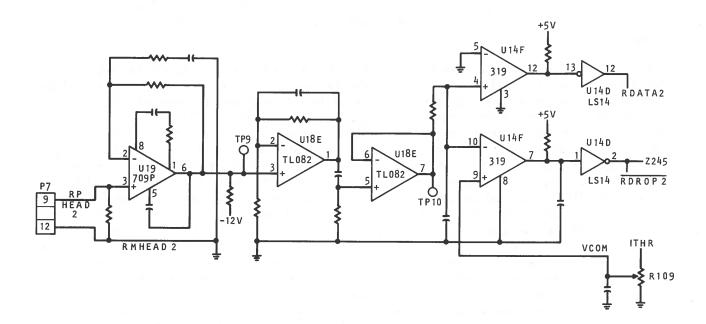

| Read Amplifier Circuits           | 2-41 |

| Read Discriminator Circuits       | 2-41 |

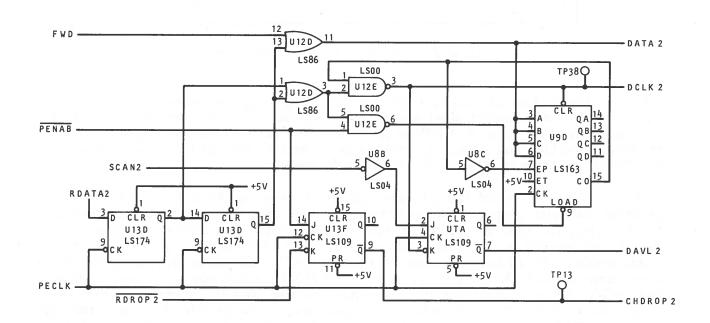

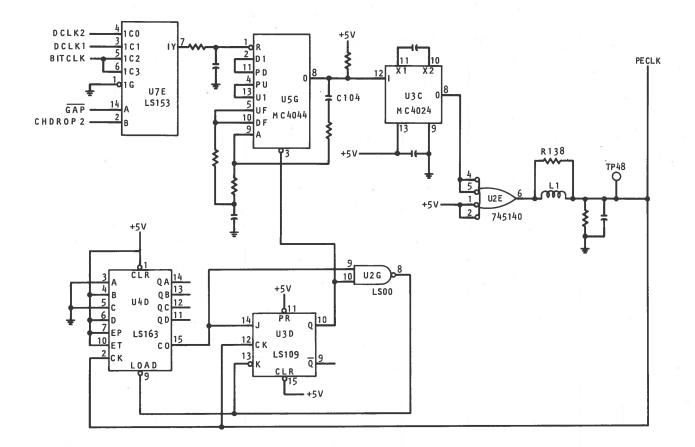

| PECLK Circuit                     | 2-44 |

| Scan Generator                    | 2-49 |

# TABLE OF CONTENTS (Continued)

| Section | Title                                | Page No. |  |

|---------|--------------------------------------|----------|--|

|         | Read Skew Buffer Circuit             | 2-49     |  |

|         | Block/Gap Detect Interrupt Generator | 2-52     |  |

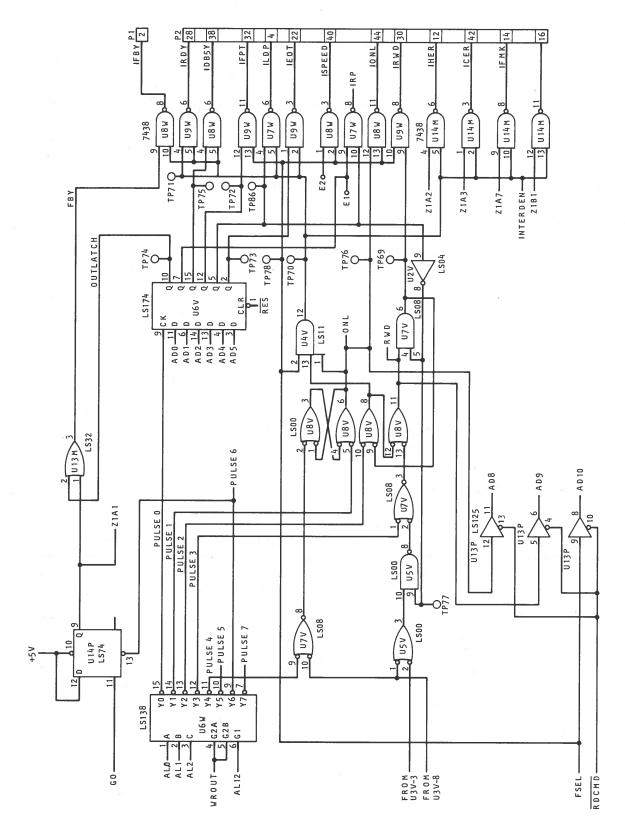

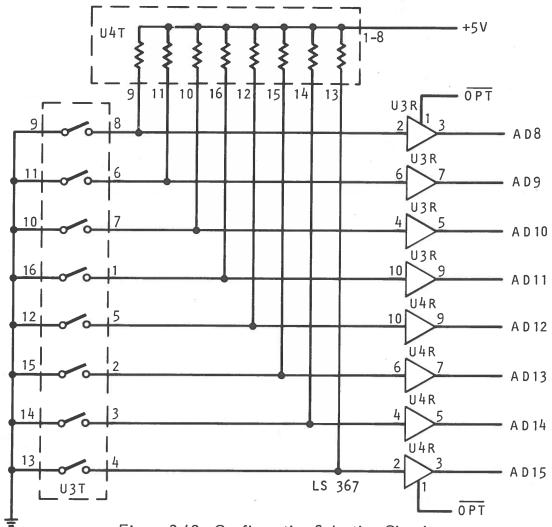

|         | Configuration Selection Circuit      | 2-52     |  |

| 111     | GLOSSARY OF TERMS                    | 3-1      |  |

## VOLUME II

## LIST OF TABLES

| Table No. | Title                                              | Page No. |

|-----------|----------------------------------------------------|----------|

| -         | Mechanical and Electrical Specifications           | . 1-6    |

| 1-2       | Interface Input Connections                        | . 1-10   |

| 1-3       | Interface Output Connections                       | . 1-13   |

| 2-1       | Latched Addresses ALØ-AL15 Functions               | . 2-15   |

| 2-2       | Analog-To-Digital Converter MUX Inputs             | . 2-28   |

| 2-3       | Reference Clock Selection                          | . 2-44   |

| 2-4       | Configuration Switches U3T Selections (Model M890) | . 2-54   |

| 2-5       | Configuration Switches U3T Selections (Model M891) | . 2-55   |

## **VOLUME TI**

### LIST OF ILLUSTRATIONS

| Figure No. | Title                                 | Page No. |

|------------|---------------------------------------|----------|

| -          | System Block Diagram                  | . 1-3    |

| 1-2        | Interface Configuration               | . 1-5    |

| 2-1        | Phase-Encoded (PE) Tape Magnetization | 2-2      |

| 2-2        | Nine-track PE Data Format             | 2-4      |

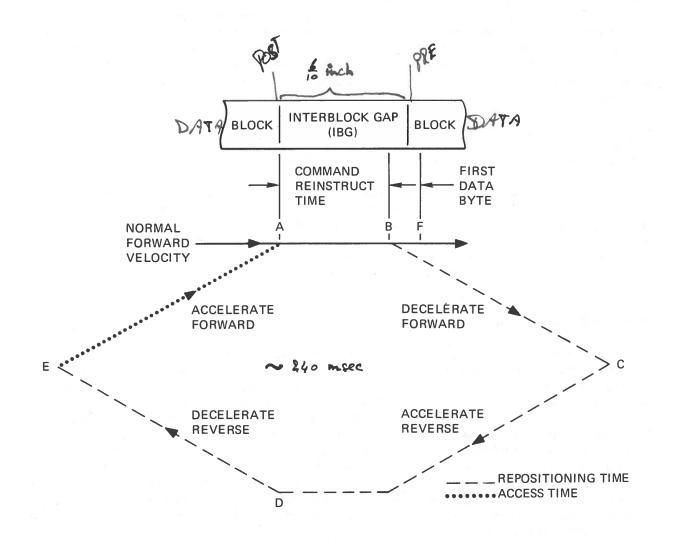

| 2-3        | Repositioning Cycle                   | 2-6      |

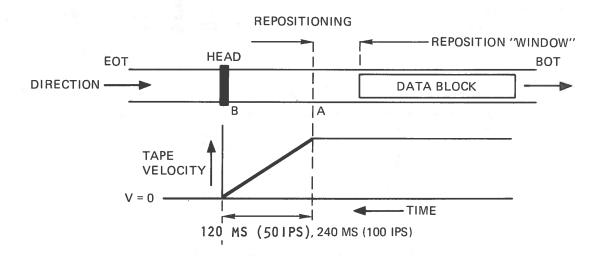

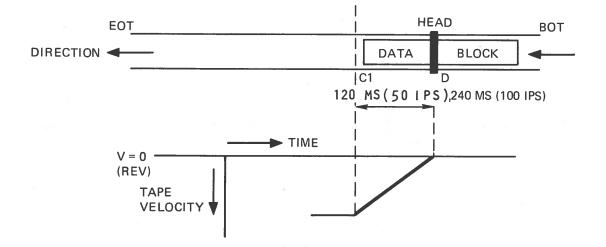

| 2-4A       | Ramp Down (FWD)                       | 2-7      |

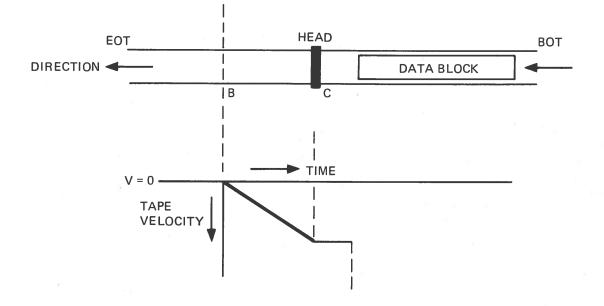

| 2-4B       | Ramp Up (REV)                         | 2-8      |

| 2-4C       | Ramp Down (REV)                       | 2-8      |

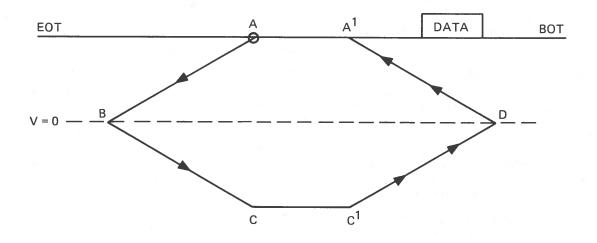

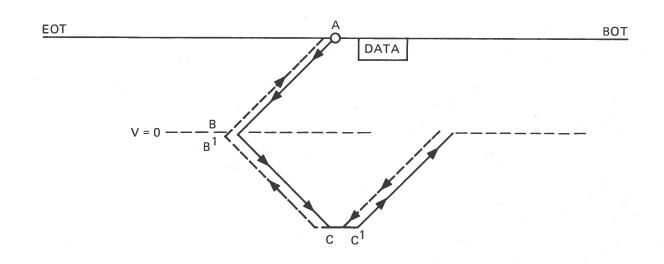

| 2-4D       | Composite Ramps at 100 ips            | 2-9      |

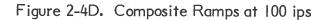

| 2-5        | Reverse Direction Repositioning       | 2-9      |

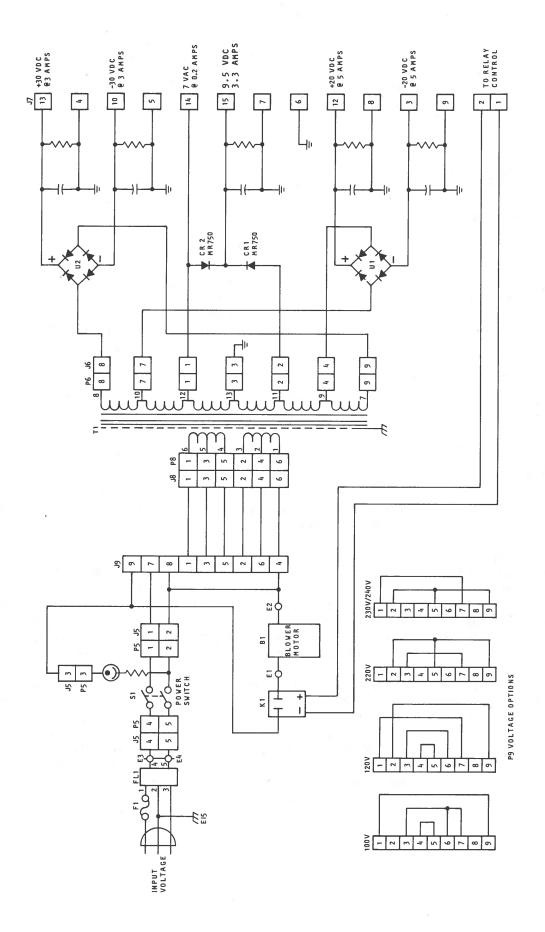

| 2-6        | Power Supply Circuit                  | 2-11     |

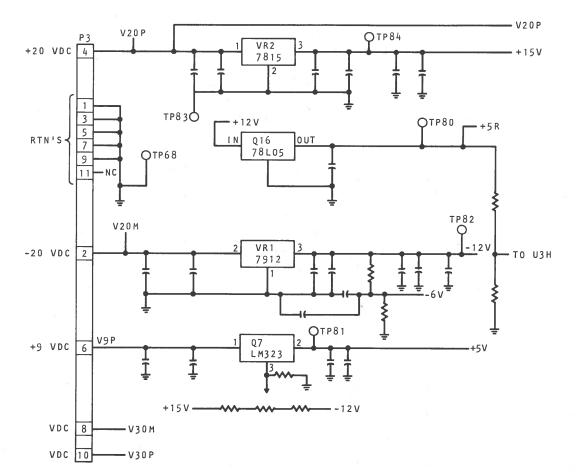

| 2-7        | Voltage Regulator Circuits            | 2-13     |

| 2-8        | System Failure Detect Circuit         | 2-13     |

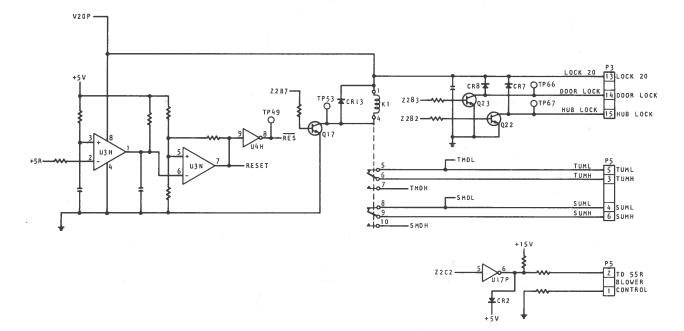

| 2-9        | Microprocessor Section                | 2-14     |

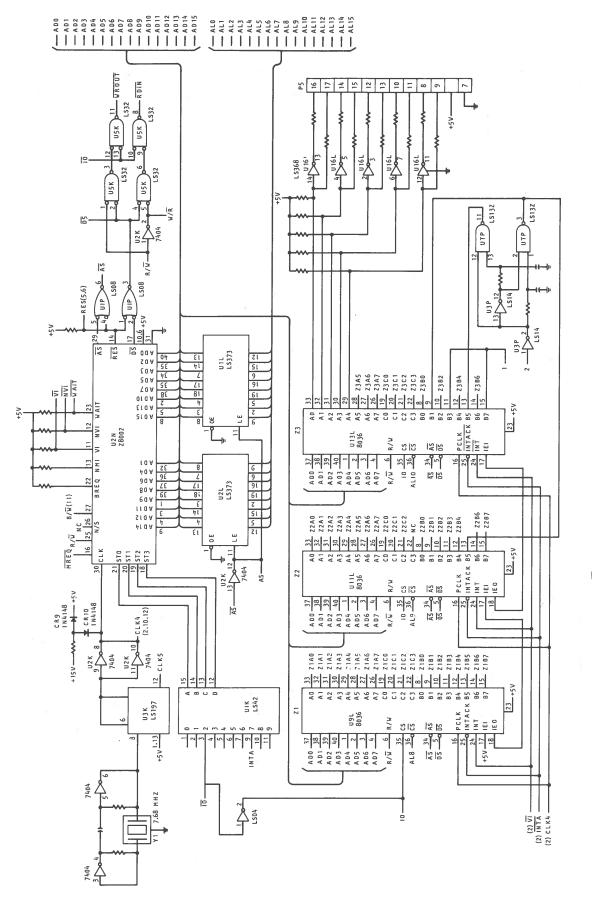

| 2-10       | DMA Control Logic                     | 2-17     |

| 2-11       | Cache Memory                          | 2-19     |

| 2-12       | Cache Memory Addressing Logic         | 2-21     |

| 2-13       | Cache Read Circuit                    | 2-22     |

| 2-14       | Cache Write Circuit                   | 2-22     |

| 2-15       | Parity Generator                      | 2-24     |

| 2-16       | EPROM and RAM Circuits                | 2-24     |

| 2-17       | Transport Status Register Circuits    | 2-25     |

| 2-18       | Motion Commands Circuit               | 2-27     |

| 2-19       | Input Sensors                         | 2-27     |

| 2-20       | Digital-To-Analog Converter           | 2-29     |

| 2-21       | Analog-To-Digital Converter Circuit   | 2-29     |

| 2-22       | Supply and Takeup Servo Circuit       | 2-31     |

| 2-23       | Arm Position and Rate Circuit         | 2-32     |

| 2-24       | Write Voltage Control Circuit         | 2-32     |

| 2-25       | Write Formatting Control Circuit      | 2-33     |

# LIST OF ILLUSTRATIONS (Continued)

| Figure No. | Title                                            |      |  |  |  |

|------------|--------------------------------------------------|------|--|--|--|

| 2-26       | Write Formatter Circuit                          | 2-35 |  |  |  |

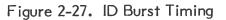

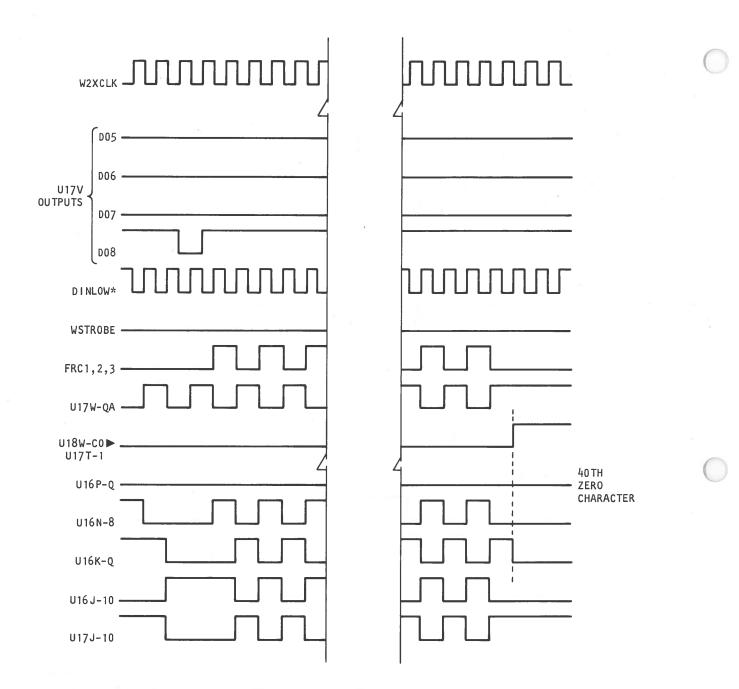

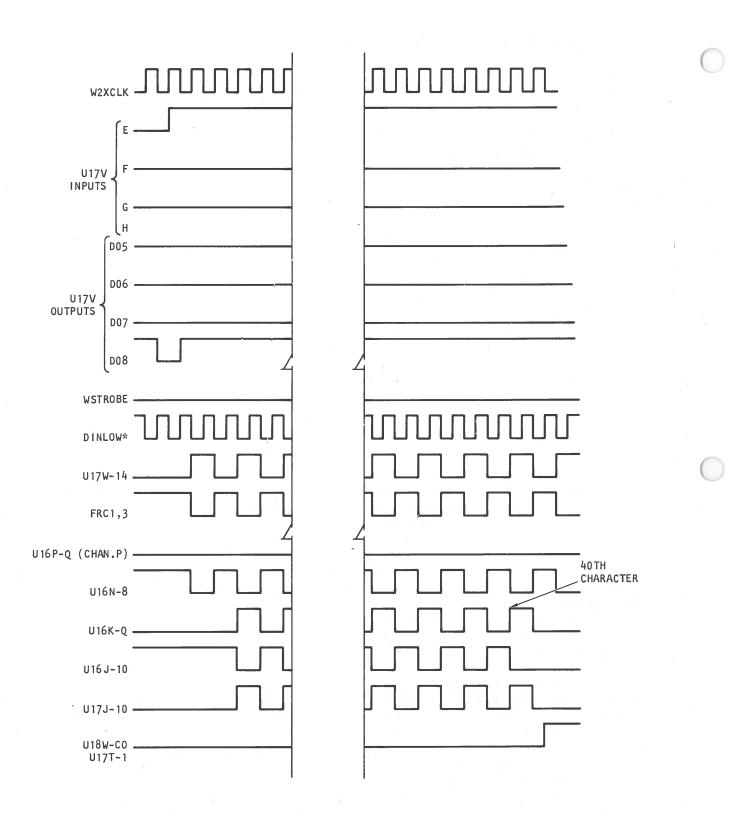

| 2-27       | ID Burst Timing                                  | 2-36 |  |  |  |

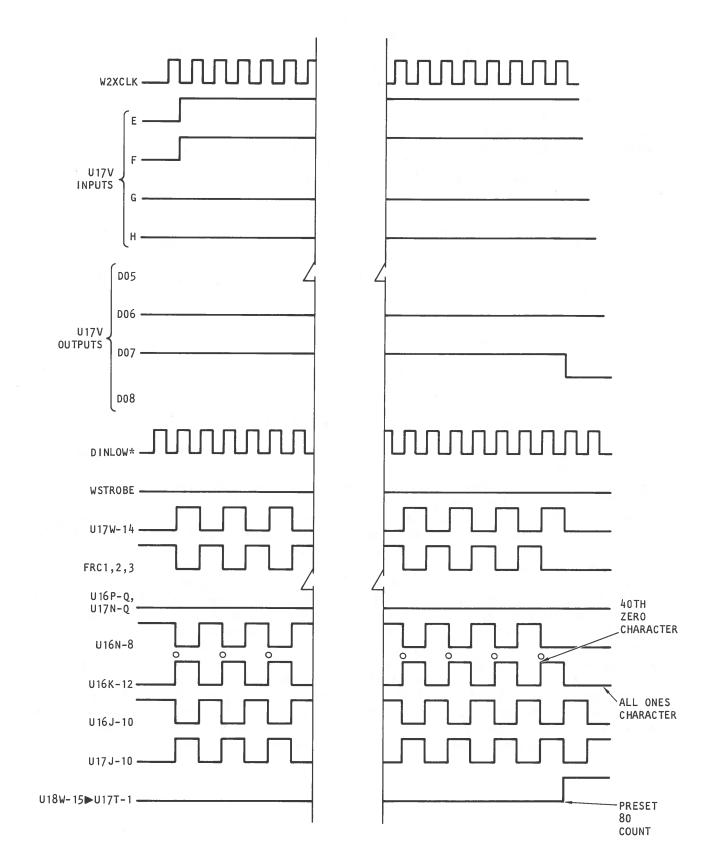

| 2-28       | Write Preamble Timing                            | 2-37 |  |  |  |

| 2-29       | Write Data Block Timing                          | 2-39 |  |  |  |

| 2-30       | Write Postamble Timing                           | 2-40 |  |  |  |

| 2-31       | Write File Mark Timing                           | 2-42 |  |  |  |

| 2-32       | Read Amplifier Circuit (Typical)                 | 2-43 |  |  |  |

| 2-33       | Read Discriminator Circuit (Typical)             | 2-43 |  |  |  |

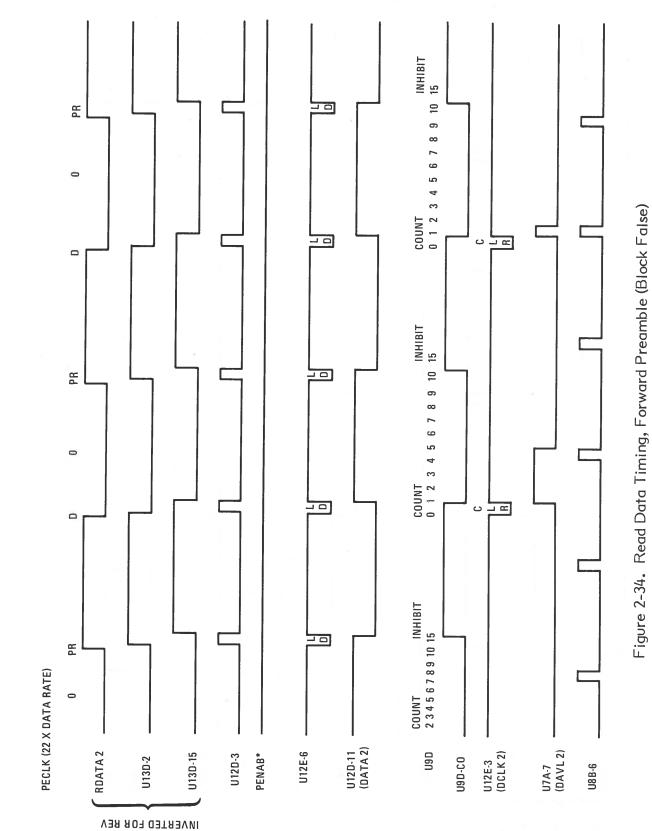

| 2-34       | Read Data Timing, Forward Preamble (Block False) | 2-45 |  |  |  |

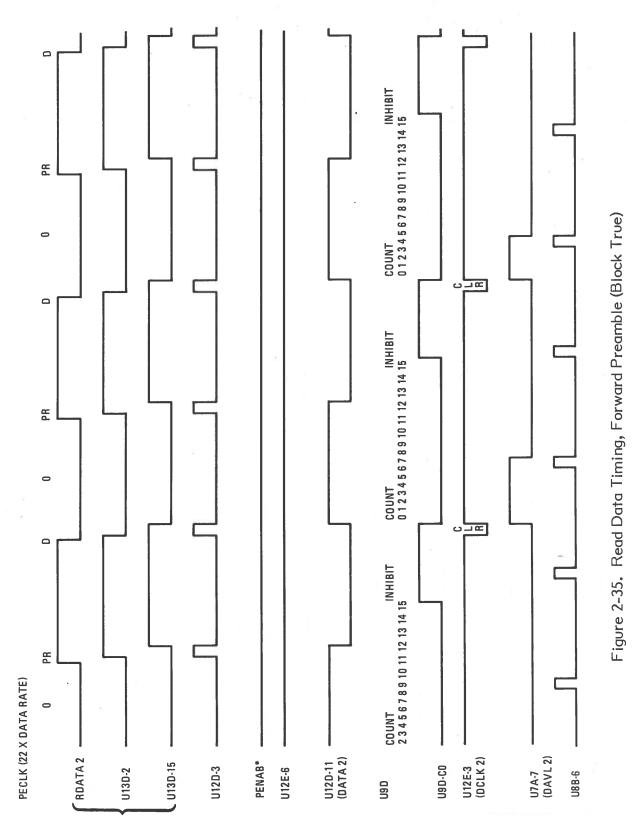

| 2-35       | Read Data Timing, Forward Preamble (Block True)  | 2-46 |  |  |  |

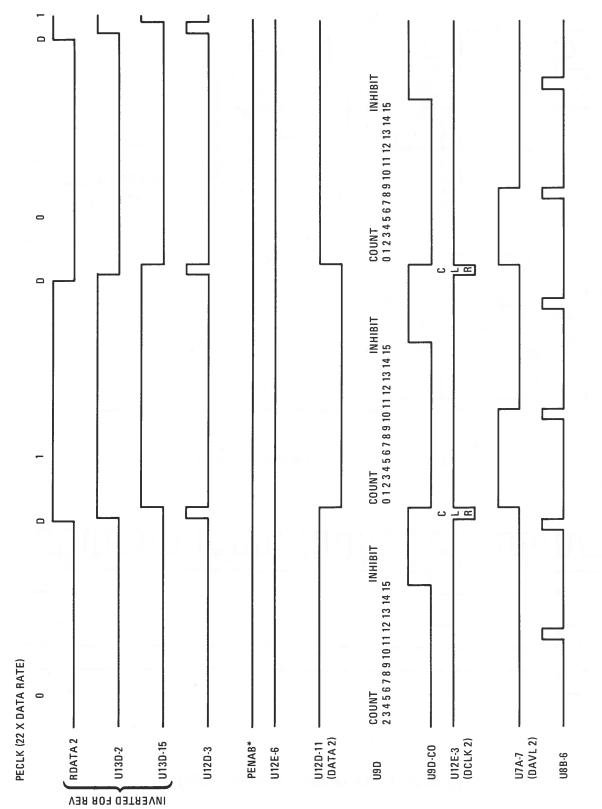

| 2-36       | Read Data Timing (Forward)                       | 2-47 |  |  |  |

| 2-37       | PECLK Generation Circuit                         | 2-48 |  |  |  |

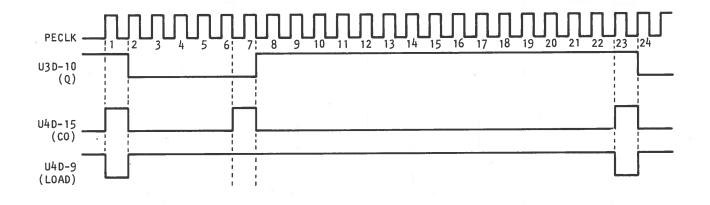

| 2-38       | Divide-By-22 Circuit Timing                      | 2-48 |  |  |  |

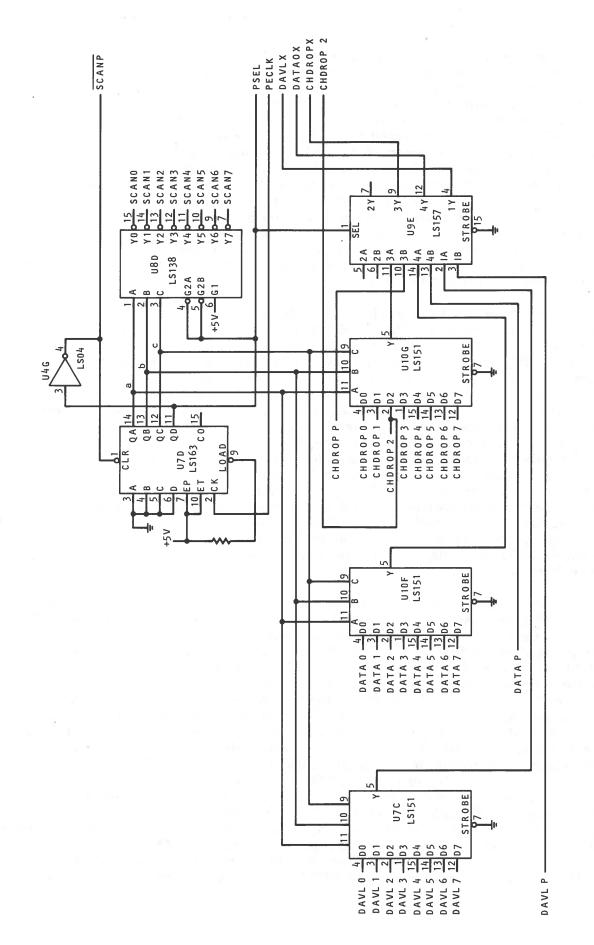

| 2-39       | Scan Generator Circuits                          | 2-50 |  |  |  |

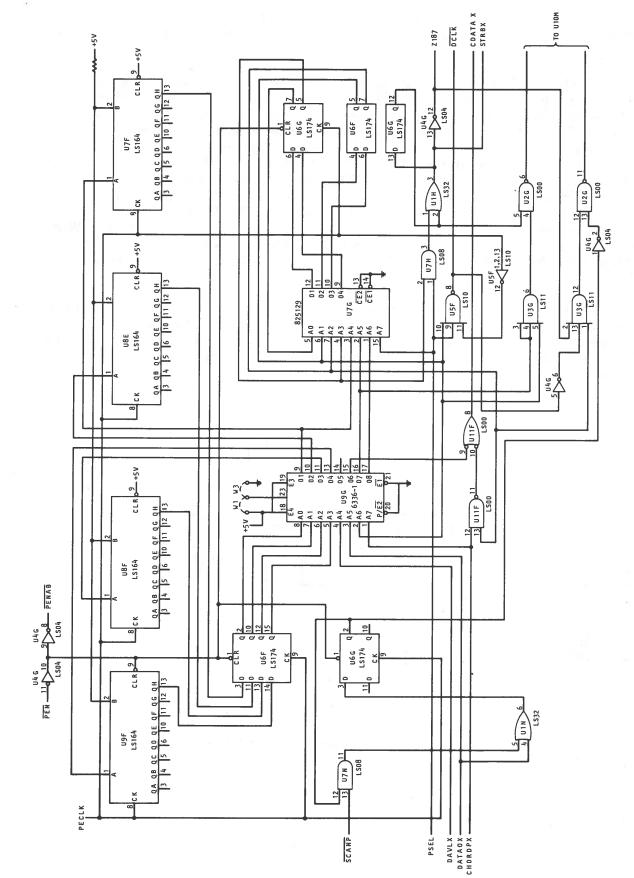

| 2-40       | Read Skew Buffer Circuit                         | 2-51 |  |  |  |

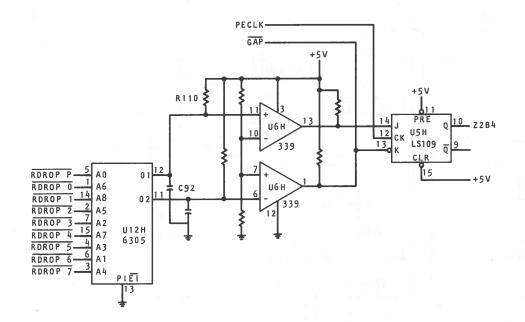

| 2-41       | Block/Gap Detect Interrupt Generator             | 2-52 |  |  |  |

| 2-42       | Configuration Selection Circuit                  | 2-53 |  |  |  |

#### SECTION I

### DESCRIPTION AND SPECIFICATIONS

#### PHYSICAL DESCRIPTION

I-I. The CacheTape Unit (CTU) is a dual-speed, dual-density tape transport manufactured by Cipher Data Products, Inc., San Diego, California. The CTU is designed to be rack-mounted in a standard I9-inch equipment rack. All components are mounted on a precision-machined, cast aluminum plate. When the equipment rack is securely anchored, the PWB and other internal components can be made accessible from the front by releasing the equipment latch located inside the front panel (bottom) and pulling the CTU forward on slides.

1-2. The CTU simulates traditional tape drives by means of an internal cache memory that performs the logical functions of a physical drive. The host system interfaces directly with the logical drive. Data records from the host are stored in cache memory and then written on tape by the physical drive, independent of the host. The physical drive is thus virtually transparent to the host system.

1-3. There are two CTU models: the Model M890 and the Model M891. Each model records at 1600 bytes-per-inch (BPI), and each has an option of recording at 3200 BPI. The primary differences in the two models are performance factors. The Model M890 has a maximum data transfer rate of 120 kilobytes-per-second (KBS) and has built-in start delays to simulate the physical tape ramp time of conventional start/stop transports. The Model M891 has a maximum data transfer rate of 384 KBS and has the capability of burst mode operation in which the simulated ramp delays are not used. The burst mode is switch-selected during system setup.

1-4. There are two different access positions for the CTU. The first position, operator maintenance access, provides accessibility to the supply reel, head, and tape roller guides. The second position, service access, provides access to all electronic components as well as mechanical parts. Refer to Volume I for instructions on each position.

### PHYSICAL TAPE DRIVE MECHANISM

1-5. The reel-to-reel drive mechanism employs two direct-drive, dc, torque motors to drive the tape reels. An optical tachometer assembly on the takeup hub regulates tape speed. Tape tension is maintained at approximately 7 ounces by a single tension arm.

| - |

1-6. The tape path includes roller guides, a dual-gap head, and a tape cleaner. All roller guides incorporate precision bearings to minimize friction and wear. The roller guides, positioned on both sides of the head, utilize polished ceramic washers to guide the tape across the head. This arrangement minimizes skew and the effect of tape-width variations.

1-7. A tape cleaner is mounted adjacent to the head to minimize tape contamination.

### FUNCTIONAL DESCRIPTION

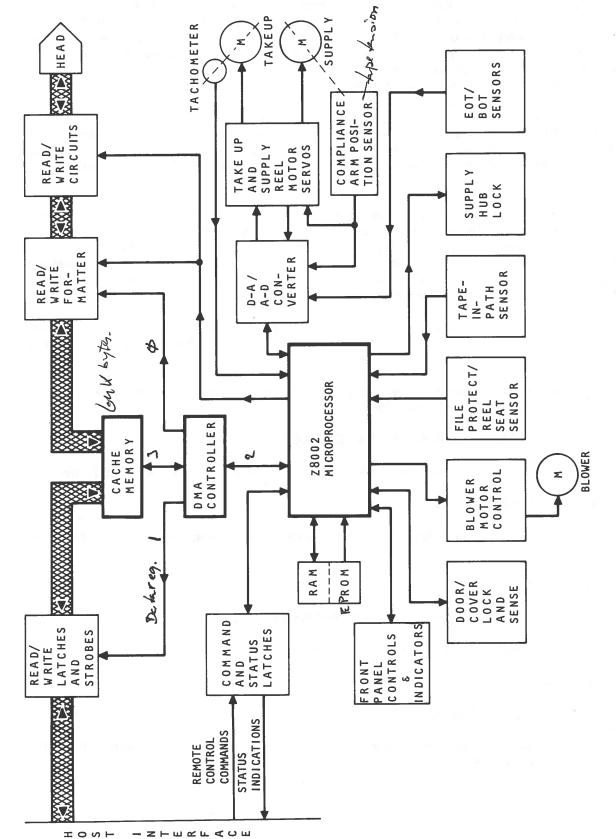

I-8. Figure I-I is a system block diagram. The CTU can be functionally divided into the logical tape unit and the physical tape unit, both of which are controlled by the Z8002 microprocessor. The logical unit consists of the cache memory and associated logic circuits, while the physical unit consists of the read/write circuits, read/write head, the physical drive mechanisms, and the related sensing and controlling devices. The DMA controller, under the overall control of the microprocessor, directly controls the cache memory.

1-9. The microprocessor is supported by 16K words of control storage (ROM) and 2K words of RAM. The microprocessor also has analog input and output ports for diagnostic purposes, control of motor drivers, and read threshold selection.

I-10. The interface logic in the CTU consists of the following:

- a. Read/write latches and strobes.

- b. Command and status latches.

The read/write latches and strobe logic are connected to the DMA controller and cache memory through device request logic. The microprocessor determines the rate of access. The command and status latches interface directly with the microprocessor logic. The host interface communicates only with the logical tape drive.

1-11. Cache memory consists of nine 64K dynamic random access memories (DRAM's). The memory is logically a circular buffer and is addressed by the DMA controller. The four channels of the DMA controller perform the following services in the priority listed:

- a. Physical tape drive

- b. Logical tape drive

- c. Microprocessor/Cache memory communications

- d. DRAM refresh

1-12. The write formatter is under the direct control of the microprocessor. The ID burst, preamble, postamble, and file mark are generated internally by the formatter. The formatter output is sent to the write electronic circuits, which drive the physical tape drive head to write the formatted data on the tape.

Figure I-I. System Block Diagram

1-13. During a read operation, the read electronic circuits recover the low-voltage read signals from the read head, condition the signals, and route the signals to the read formatter. The read formatter detects the polarity of the data transitions and sends input requests to the serial processing and skew buffer in the read formatter logic. When a full data character is assembled by the skew buffer, the buffer requests that the DMA controller recover the character and place it in cache memory.

I-I4. Tape movement in the physical tape drive is controlled primarily by the takeup servo and tachometer assembly. The velocity information generated by the tachometer assembly is used to develop the drive voltage for the takeup motor. The tachometer is also used to develop the drive position displacement information between the beginning and end of consecutive tape records.

1-15. The supply motor is the driving mechanism of a position servo loop that maintains the tape at the proper tension. The compliance arm is held at a position between its two limit stops. Any tape movement causes a change in position of the compliance arm, resulting in a feedback signal from the compliance arm position sensor to the supply reel servo. The servo adjusts or decreases the supply reel motor speed and direction to correct the compliance arm position.

1-16. The end-of-tape (EOT) and beginning-of-tape (BOT) sensors consist of twochannel infrared detectors operating on reflections from ANSI metallized markers applied to standard tape reels.

1-17. An infrared detector adjacent to the supply reel senses that the tape is in the tape path. This ensures reliable tape loading.

#### MECHANICAL AND ELECTRICAL SPECIFICATIONS

1-18. The mechanical and electrical specifications for the CTU are shown in Table 1-1.

#### INTERFACE SPECIFICATIONS

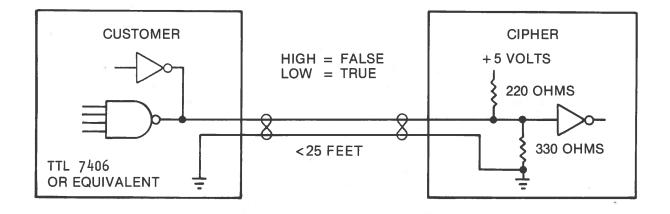

1-19. Table 1-2 and 1-3 contain a list of interface connections. Signal characteristics are as follows:

- a. Levels

- (1) True is low: 0 to +0.4 volt (approximately).

- (2) False is high: +3.0 volts (approximately).

- b. Pulses

- (1) Levels as above.

- (2) Edge transmission delay over 25 feet of cable is not greater than 200 nanoseconds.

1-20. The interface circuits are so designed that a disconnected wire results in a false signal. Figure 1-2 shows the interface configuration for which the transport is designed.

Figure I-2. Interface Configuration

| Recor  | ding Method                                                                                                                                 | Phase Encoded (PE)                                                                                                                                    |  |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data 7 | Tracks                                                                                                                                      | 8                                                                                                                                                     |  |  |  |  |

| Parity | <sup>7</sup> Tracks                                                                                                                         | I .                                                                                                                                                   |  |  |  |  |

| Densit | τ <b>γ</b>                                                                                                                                  | 1600 bpi standard,<br>3200 bpi optional                                                                                                               |  |  |  |  |

| Opera  | tion Speeds                                                                                                                                 | 100 ips (1600 bpi),<br>50 ips (3200 bpi)                                                                                                              |  |  |  |  |

|        | cter Rate<br>ytes per second)                                                                                                               | <u>M890</u><br>20 kbs-120 kbs<br>(Selectable) (Selectable)                                                                                            |  |  |  |  |

| Burst  | Mode (Ramp Disable)                                                                                                                         | Not Available Standard (Ramp<br>may be inserted in<br>logical interface<br>by DIP switch<br>selection.)                                               |  |  |  |  |

|        | cal Dimensions<br>leight<br>/idth<br>/idth (front panel)<br>/epth (from mounting surface)<br>/verall Depth<br>/eight<br>/eight<br>pommental | 8.75 inches (22.2 cm)<br>17.0 inches (43.18 cm)<br>19.0 inches (43.26 cm)<br>22.0 inches (55.80 cm)<br>24.5 inches (62.23 cm)<br>82 pounds (37.65 kg) |  |  |  |  |

|        | NO                                                                                                                                          | DTE                                                                                                                                                   |  |  |  |  |

|        | The ambient temperatu<br>media be retained withi<br>integrity to be maintair<br>centigrade ambient may                                      | n ANSI limits for data<br>ned; i.e., 32 degree                                                                                                        |  |  |  |  |

|        | Dry Bulb Temperature                                                                                                                        | 10° to 40°C                                                                                                                                           |  |  |  |  |

|        | Wet Bulb Temperature                                                                                                                        | 26 <sup>0</sup> C maximum                                                                                                                             |  |  |  |  |

|        | Relative Humidity                                                                                                                           | 20 to 85%                                                                                                                                             |  |  |  |  |

|        | Barometric Pressure                                                                                                                         | 20" Hg to 32" Hg<br>(68 kPa to 109 kPa)                                                                                                               |  |  |  |  |

|        | Altitude                                                                                                                                    | Sea Level to 10,000 ft (3 km)                                                                                                                         |  |  |  |  |

|        | Temperature Shock<br>Generated Heat                                                                                                         | l min. minimum per 1 <sup>0</sup> C change<br>270 watts rated maximum;<br>750 BTU/hour average maximum<br>(vented to enclosure)                       |  |  |  |  |

Table 1-1. Mechanical and Electrical Specifications

|      | Non-operating (Long Term)             |

|------|---------------------------------------|

|      | Dry Bulb Temperature                  |

|      | Wet Bulb Temperature                  |

|      | Relative Humidity                     |

|      | Altitude                              |

|      | Shipping and Short Term Storage       |

|      | Dry Bulb Temperature                  |

|      | Wet Bulb Temperature                  |

|      | Relative Humidity                     |

|      | Altitude                              |

| Vibr | ation                                 |

|      | Operating                             |

|      | Frequency Range                       |

|      | Peak Acceleration Level               |

|      | Application                           |

|      | Non-operating (in shipping container) |

|      | Frequency Range                       |

|      | Peak Acceleration Level               |

|      | Application                           |

| Shoc | k                                     |

|      | Operating                             |

|      | Non-operating (in shipping container) |

|      | Peak Acceleration                     |

|      | Duration                              |

|      | Waveshape                             |

|      | Application                           |

Pollutants

Dust

-40° to 50°C 30° maximum 90% maximum Sea level to 10,000 ft (3 km)

-40° to 70°C 40°C maximum 95% maximum Sea level to 49,000 ft (15 km)

5 to 500 Hz 0.3g Each direction of 3 orthogonal axes

5 to 500 Hz 1.5g Each direction of 3 orthogonal axes

Undefined

5g 5 to 50 ms

5 10 50 113

1/2 Sine

Each direction of 3 orthogonal axes

60 milligrams/1000 cu ft of air by weight of particles (5 micron diameter)

Table 1-1. Mechanical and Electrical Specifications (Continued)

| Tape Speed (Determined by density)                   | 100 ips (at 1600 BP1)<br>or 50 ips (at 3200 BP1) |

|------------------------------------------------------|--------------------------------------------------|

| Long Term Speed Variation (LSV)                      | ±1% of nominal                                   |

| Instantaneous Speed Variation (ISV)                  | ±2% of long term                                 |

| Write Skew                                           | 300 micro-inches maximum                         |

| Rewind Speed                                         | 180 ips typical (10-1/2" reel)                   |

| Tape (computer grade) ANSI X3.40-1976                |                                                  |

| Width                                                | 0.5 inch                                         |

| Thickness                                            | 1.5 milli-inch                                   |

| Reel Size                                            | 7 in, 8.5 in, or 10.5 in                         |

| Tape Tension                                         | 7 oz nominal                                     |

| Data Reliability (errors other<br>than media faults) |                                                  |

| Write                                                | l error in 10 <sup>8</sup> bytes                 |

| Read Recoverable                                     | l error in 10 <sup>9</sup> bytes                 |

| Read Permanent                                       | l error in 10 <sup>10</sup> bytes                |

| Undetected                                           | l error in 10 <sup>11</sup> by tes               |

| MTBF (20% duty cycle)                                | 5,500 hours                                      |

| MTTR (to isolate and repair major assemblies)        | 30 minutes                                       |

| Interblock Gap                                       | 0.6 in                                           |

| Formatter Interface                                  | Industry compatible                              |

| Interface Impedance                                  | 130 ohms at 3 Vdc                                |

| Logic Low                                            | 0.4 Vdc maximum                                  |

| Logic High                                           | 2.4 Vdc minimum                                  |

| Rise/Fall                                            | 100 nanoseconds maximum                          |

| Cable Characteristics                                | 28 AWG flat ribbon                               |

|                                                      | 22 or 24 AWG twisted pair                        |

| Daisy Chain                                          | 25 feet maximum                                  |

|                                                      |                                                  |

Table 1-1. Mechanical and Electrical Specifications (Continued)

| Power                                                                |                              |

|----------------------------------------------------------------------|------------------------------|

| Nominal input voltage<br>(slow-averaged rms, including<br>brownouts) | 100, 120, 220, 240, 208, 230 |

| Range of nominal voltage<br>except 208, 230                          | +10%, -15%                   |

| Range of nominal<br>208, 230 voltage                                 | +10%, -10%                   |

| Modulation                                                           | l% max                       |

| Harmonics (total)                                                    | 10% max                      |

| Operating Frequency                                                  |                              |

| Frequency                                                            | 49 to 63 Hz                  |

| Tolerance                                                            | included above               |

| Rate of Change                                                       | 1.5 Hz/sec max               |

|                                                                      |                              |

Table 1-1. Mechanical and Electrical Specifications (Continued)

| FUNCTION    | When true, during write, indicates that the character to be strobed into the formatter is the last character of the record. |                    | With CTU ready and on line, the command specified on the command lines is latched into the CTU on the trailing edge of IGO. | 1                  | I                  | When true, with CTU ready and on line, causes tape<br>to move in the reverse direction, and when false,<br>causes tape to move in the forward direction. | With CTU ready, on line, and not at BOT, this pulse causes tape to rewind in reverse direction. | 1                          | ſ                  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------|--------------------|

| ТҮРЕ        | Level                                                                                                                       | Level              | Pulse                                                                                                                       | Level              | Level              | Level                                                                                                                                                    | Pulse                                                                                           | Level                      | Level              |

| SIGNAL      | Last Word (ILWD)                                                                                                            | Write Data 4 (IW4) | Initiate Command<br>(IGO)                                                                                                   | Write Data 0 (IWO) | Write Data I (IWI) | Reverse (IREV)                                                                                                                                           | Rewind (IREW)                                                                                   | Write Data Parity<br>(IWP) | Write Data 7 (IW7) |

| GRD<br>PIN  | с                                                                                                                           | 5                  | 7                                                                                                                           | 6                  | Ξ                  | 17                                                                                                                                                       | 61                                                                                              | 21                         | 23                 |

| LIVE        | 4                                                                                                                           | 9                  | ω                                                                                                                           | 01                 | 12                 | 18                                                                                                                                                       | 20                                                                                              | 22                         | 24                 |

| PLUG<br>NO. | ٩                                                                                                                           | <u> </u>           | Ē                                                                                                                           | Ē                  | Ы                  | Ы                                                                                                                                                        | Ē.                                                                                              | Id                         | Id                 |

Table 1-2. Interface Input Connections

| FUNCTION    |                    |                    | 1                  |                    | When true, specifies the write mode of operation,<br>and when false, specifies the read mode of<br>operation. | When true, with IWRT true, causes the CTU to operate in the edit mode. | When true, with CTU on line, specifies the erase mode of operation. | When true, and IWRT also true, causes a file mark<br>to be written on the tape. | The CTU is selected by a combination of<br>levels on the ITAD0, ITAD1, and IFAD lines and the<br>position of switches S1, S2, and S4. |

|-------------|--------------------|--------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| ТҮРЕ        | Level              | Level              | Level              | Level              | Level                                                                                                         | Level                                                                  | Level                                                               | Level                                                                           | Level                                                                                                                                 |

| SIGNAL      | Write Data 3 (IW3) | Write Data 6 (IW6) | Write Data 2 (IW2) | Write Data 5 (IW5) | Write (IWRT)                                                                                                  | Edit (IEDIT)                                                           | Erase (IERASE)                                                      | Write File Mark<br>(IWFM)                                                       | Transport Address 0<br>(ITAD0)                                                                                                        |

| GRD<br>PIN  | 25                 | 27                 | 29                 | 31                 | 33                                                                                                            | 37                                                                     | 39                                                                  | 14                                                                              | 45                                                                                                                                    |

| LIVE        | 26                 | 28                 | 30                 | 32                 | 34                                                                                                            | 38                                                                     | 40                                                                  | 42                                                                              | 46                                                                                                                                    |

| PLUG<br>NO. | ٩١                 | ΡI                 | Ы                  | Ы                  | ۱d                                                                                                            | Ī                                                                      | Id                                                                  | Ы                                                                               | -<br>-                                                                                                                                |

Table 1-2. Interface Input Connections (Continued)

1 - 1 [

| FUNCTION    | Enables the CTU. With CTU on line and IDBY true, pulse will reset a command "runaway" condition. | When true, with CTU on line, causes the selected unit to go off line and rewind tape to the BOT marker. The CTU will unload the tape when BOT marker is detected. | The CTU is selected by a combination of levels on<br>the ITAD0, ITAD1, and IFAD lines and the position<br>of switches S1, S2, and S4. | The CTU is selected by a combination of levels on<br>the ITAD0, ITAD1, and IFAD lines and the position<br>of switches S1, S2, and S4. |

|-------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| ТҮРЕ        | Pulse                                                                                            | Pulse                                                                                                                                                             | level                                                                                                                                 | Level                                                                                                                                 |

| SIGNAL      | Formatter Enable<br>(IFEN)                                                                       | Rewind/Unload<br>(IRWU)                                                                                                                                           | Transport Address I<br>(ITADI)                                                                                                        | Formatter Address<br>(IFAD)                                                                                                           |

| GRD<br>PIN  | 17                                                                                               | 23                                                                                                                                                                | 45                                                                                                                                    | 47                                                                                                                                    |

| LIVE<br>PIN | 18                                                                                               | 24                                                                                                                                                                | 46                                                                                                                                    | 817                                                                                                                                   |

| PLUG<br>NO. | P2                                                                                               | P2                                                                                                                                                                | P2                                                                                                                                    | P2                                                                                                                                    |

Table 1-2. Interface Input Connections (Continued)

|-|2

| FUNCTION    | Goes true within one microsecond of trailing<br>edge of IGO; goes false on completion of tape<br>motion. | I                 | I                 | I                         | 1                 | 1               | True when BOT marker is positioned in front of photosensor. |                   |                   |                   |

|-------------|----------------------------------------------------------------------------------------------------------|-------------------|-------------------|---------------------------|-------------------|-----------------|-------------------------------------------------------------|-------------------|-------------------|-------------------|

| ТҮРЕ        | Level                                                                                                    | I                 | 1                 | 1 9                       | 1                 | 8               | Level                                                       | I                 | 1                 |                   |

| SIGNAL      | Formatter Busy<br>(IFBY)                                                                                 | Read Data 2 (IR2) | Read Data 3 (IR3) | Read Data Parity<br>(IRP) | Read Data 0 (IR0) | Read Data (IRI) | Load Point (ILDP)                                           | Read Data 4 (IR4) | Read Data 7 (IR7) | Read Data 6 (IR6) |

| GRD<br>PIN  | _                                                                                                        | <i>L</i> ‡        | 64                | t                         | 1                 | I               | I                                                           | 5                 | 7                 | 6                 |

| PINE        | 2                                                                                                        | 817               | 50                | _                         | 2                 | m               | 4                                                           | 9                 | Ø                 | 0                 |

| PLUG<br>NO. | Ē                                                                                                        | Ы                 | ΡI                | P2                        | P2                | P2              | P2                                                          | P2                | P2                | P2                |

Table 1-3. Interface Output Connections

| FUNCTION    | When true, indicates that an uncorrectable read error has been detected by the CTU. | When true indicates that the CTU has detected a file mark. | Pulsed when the BOT marker passes over the read head, to identify 1600 bpi (PE) tapes. | I                 | When true, indicates that the EOT marker has been<br>detected. IEOT remains true until the EOT marker<br>is sensed in the reverse direction. | True when load sequence is complete and CTU is on<br>line and not rewinding. (CTU is ready to receive a<br>remote command.) | True when CTU is in a rewind to beginning of tape sequence. |  |

|-------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| ТҮРЕ        | Pulse<br>or<br>Level                                                                | Pulse                                                      | Pulse                                                                                  | 1                 | Level                                                                                                                                        | Level                                                                                                                       | Level                                                       |  |

| SIGNAL      | Hard Error (IHER)                                                                   | File Mark (IFMK)                                           | ldentification<br>(IDENT)                                                              | Read Data 5 (IR5) | End of Tape (IEOT)                                                                                                                           | Ready (IRDY)                                                                                                                | Rewinding (IRWD)                                            |  |

| GRD<br>PIN  | =                                                                                   | 13                                                         | 15                                                                                     | 61                | 21                                                                                                                                           | 27                                                                                                                          | 29                                                          |  |

| LIVE        | 12                                                                                  | 14                                                         | 16                                                                                     | 20                | 22                                                                                                                                           | 28                                                                                                                          | 30                                                          |  |

| PLUG<br>NO. | P2                                                                                  | P2                                                         | P2                                                                                     | P2                | P2                                                                                                                                           | P2                                                                                                                          | Ρ2                                                          |  |

Table 1-3. Interface Output Connections (Continued)

| - | 4

| FUNCTION    | True when CTU is selected and a reel of tape<br>without a write-enable ring is mounted on the CTU. | Pulses to indicate a read character is present on the controller interface. | When true (trailing edge), indicates that the character on the data lines has been written on tape and the next character is needed. | True after simulated ramp delay; remains true<br>during active execution of all commands initiated by<br>IGO. | When pulsed during a write/read operation, indicates that a single-track correctable error has occurred. | When true, indicates that the selected CTU is accessible to the host controller. |

|-------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| ТҮРЕ        | Level                                                                                              | Pulse                                                                       | Pulse                                                                                                                                | Level                                                                                                         | Pulse                                                                                                    | Level                                                                            |

| SIGNAL      | File Protect (IFPT)                                                                                | Read Strobe (IRSTR)                                                         | Write Strobe<br>(IWSTR)                                                                                                              | Data Busy (IDBY)                                                                                              | Corrected Error<br>(ICER)                                                                                | On Line (IONL)                                                                   |

| GRD<br>PIN  | 31                                                                                                 | 33                                                                          | 35                                                                                                                                   | 37                                                                                                            | 41                                                                                                       | 43                                                                               |

| LIVE<br>PIN | 32                                                                                                 | 34                                                                          | 36                                                                                                                                   | 38                                                                                                            | 42                                                                                                       | tt                                                                               |

| PLUG<br>NO. | P2                                                                                                 | P2                                                                          | P2                                                                                                                                   | P2                                                                                                            | P2                                                                                                       | P2                                                                               |

$\bigcirc$

Table 1-3. Interface Output Connections (Continued)

|-|5

### SECTION II

### THEORY OF OPERATION

#### GENERAL

2-1. The basic concepts of digital recording, magnetic tape transport applications, and principles of operation of the Cachetape Unit (CTU) are presented in this section. A thorough knowledge of this section will be of considerable value in troubleshooting this equipment.

#### BASIC CONCEPTS OF DIGITAL RECORDING

2-2. The use of magnetic tape as a digital recording medium has increased steadily as a result of the increased use of microprocessor technology and the increasing versatility and decreasing cost of tape transports. The digital recording process involves methods and equipment capable of recording and reading information expressed in digital (binary) code.

#### DATA RECORDING/READING WITH MAGNETIC TAPE

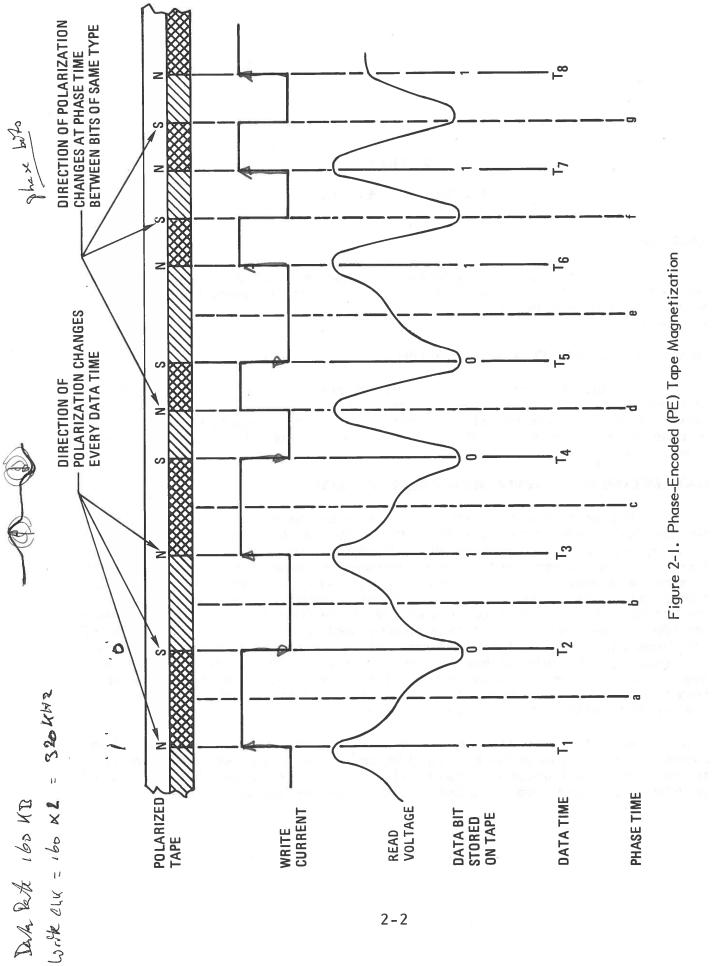

2-3. The recording of data on magnetic tape originates with the input device, whose nine channels of digital signals are transmitted to the corresponding data channels of the transport in parallel bytes composed of 9 bits aligned across the width of the magnetic tape. A bit is a binary I or 0 which is presented in magnetic tape recording by the presence or absence of a flux reversal, or by a plus or minus direction of flux reversal, depending upon the coding system. (One of these channels is the parity channel, which is used to correct errors which occur when one of the other eight bits is not properly recorded.) These signals produce corresponding electrical currents in the write head of the transport, which, in turn, produces positive and negative magnetic polarities corresponding to the original data and parity signals in the tracks of the tape passing over it. In phase-encode writing, a binary I signal produces a transition to the erase polarity on the tape when moving tape in the forward direction (Figure 2-1); a binary 0 produces a transition away from the erase polarity.

2-4. As written tape passes across the magnetic read head of a transport, the head responds to each change of flux arriving at its gap and produces a read voltage waveform for each track as illustrated in Figure 2-1. (Refer to paragraph 2-5 for a detailed description of magnetic tape recording/reading in the phase-encode mode.)

2-2

2-5. **Phase-Encode System.** Phase-encoded (PE) recording is used for 1600 bits per inch (bpi) format in the nine-track mode only. A major advantage offered by the PE format is the fact that the data is self clocking which allows each channel to be synchronized using a preamble. This allows greater packing density.

- a. There must be a change of tape polarity between data bits of the same polarity (consecutive I or 0 bits) at phase time.

- b. There must be a change of tape polarity at each data bit time.

- c. There must not be a change of tape polarity at phase time between I and 0 bits.

- d. A change of tape polarity at data bit time, when reading forward, to erase polarity is a 1; away from erase polarity, a 0.

- e. The PE transport records and reads data at a density of 1600 and 3200 bits per inch (bpi).

2-6. For clarification, the term "change of polarity" is also referred to as a flux change or flux reversal. As noted above, there must be a flux reversal with each data bit, whether it be a 0 or 1. Therefore, 1600 bpi equates to a minimum of 1600 flux reversals per inch (frpi) in any given channel. (This would occur in the case of alternate 0 and 1 bits.) The maximum case would occur with consecutive 0 or 1 bits, resulting in 3200 frpi. The flux reversal at each bit time accounts for the self-clocking feature of PE writing.

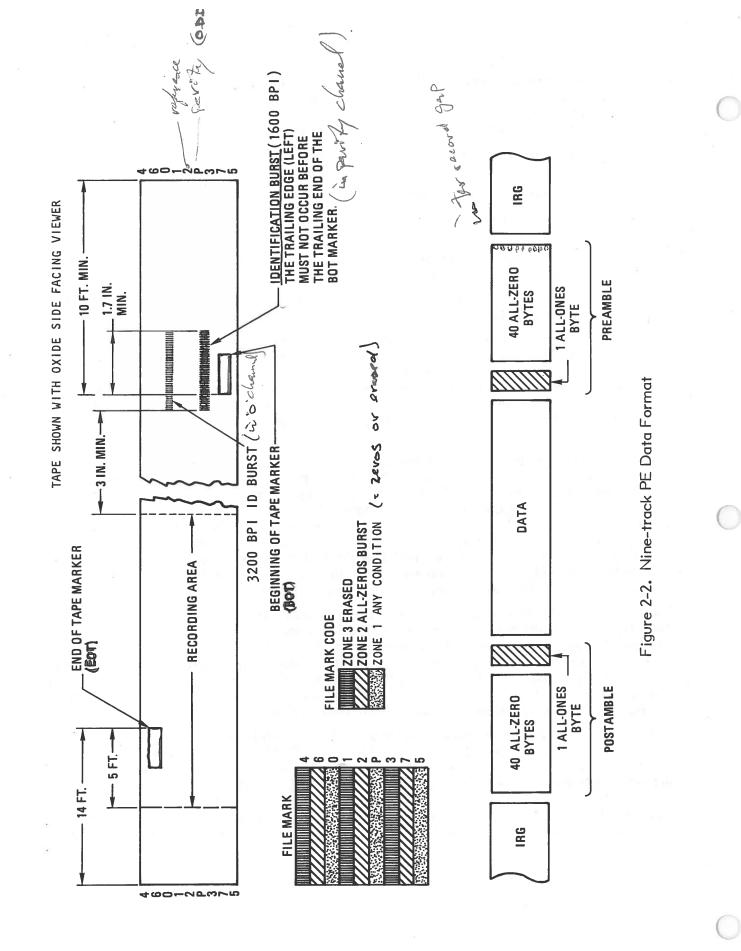

2-7. Details of the PE format are given in Figure 2-2. Channels 0 through 7 contain data bits, with the bit in channel 0 as the most significant bit. Channel P contains the parity bit, which in the PE format is always odd. No Cyclic Redundancy Characters (CRC) or Longitudinal Redundancy Characters (LRC) are used in the PE format. Each PE data block, however, is preceded by a preamble consisting of 40 bytes of all zeros followed by one byte of all ones. This is used to establish synchronization for the data block. The all ones byte identifies the end of the preamble and the start of the data bytes in the block. Following each PE data block is a postamble which is the mirror image of the preamble; i.e., one byte of all ones and 40 bytes of all zeros.

2-8. A 1600 BPI phase-encoded tape requires an identification burst (ID) of 1600 frpi in the P channel and erasure in all other channels at the beginning of the tape. The burst must begin at least 1.7 inches ahead of the trailing edge of the beginning of tape (BOT) marker and extend beyond the trailing edge of the marker and end at least 0.5 inch before the first block of data. The initial gap requirements are given in Figure 2-2. The typical distance for a gap is 3.75 inches. A similar ID burst is generated during 3200 bpi (optional) except that it is written on Channel O.

2-9. The ANSI specification defines a PE file mark as a special control block consisting of 64 to 256 flux reversals (at 3200 frpi) in channels 2, 6, and 7. Channels 1, 3 and 4 are dc erased, but channels 0, P, and 5 in any combination, may be dc erased or recorded in the manner stated for channels 2, 6, and 7. The CTU writes an IBM compatible file mark with 80 flux reversals (40 characters) at 3200 frpi in channels P, 0, 2, 5, 6, and 7 with channels I, 3, and 4 dc erased. The PE file mark is preceded by a gap of approximately 3.56 inches followed by a normal interblock gap (IBG) of 0.6 inch.

2-4

#### CACHE-TAPE OPERATION

2-10. Cache-tape operation consists of the CTU receiving data from the host computer, placing the data in cache memory, and then writing the data on tape when the physical write head is available. This permits faster write speeds, when viewed from the host system, in that write data as it is available, is transferred to the cache-tape unit and stored in cache memory. The CTU then writes the data on tape in a time frame independent of the host transfer rate. The cache memory allows the CTU to perform most of the housekeeping chores normally assigned to the host, freeing the host for other system activities. The cache memory thus acts as a logical drive in its interfacing with the host.

2-11. The cache memory can contain 150 records or 64K bytes of data. Exceeding either limit will cause the logical interface to wait until the physical drive fixes data to tape and reduces the cache memory data to the above limits.

2-12. The cache memory has storage limits that are reduced as the amount of tape remaining on the supply reel approaches end-of-tape (EOT). The system determines an impending EOT detection approximately ten feet in advance of the EOT marker and lowers the cache limits accordingly to assure that all data contained in cache will be written on the tape. The system operates in a streaming mode, as described in Paragraph 2-13, when the cache is full and no further write data can be accepted from the host.

#### STREAMING-TAPE OPERATION

2-13. Streaming-tape operation is simply writing data to tape without stopping and starting between each record block. Interblock gaps, as required in the ANSI format, are inserted automatically "on the fly". Figure 2-3 illustrates in the simplest form what a streaming drive will automatically perform if for any reason the unit must start and stop after each block. As can be seen in the diagram, there is a period of time called Command Reinstruct Time. This is the time after reading or writing the last character of the last block in which the system must instruct the tape drive to continue or, after reaching point B, the tape drive will enter what is called repositioning cycle. If the command to continue reading or writing is not received by the time normal forward velocity reaches point B, the drive automatically accelerates, coming to rest at point E. This sequence is called repositioning. After coming to rest at point E, the unit waits for the next command to read or write.

2-14. Because the tape acceleration and deceleration times required by the CTU are not related to tape velocity by the usual formula, it is not possible to start and stop the tape in the normal 0.6 inch interblock gap (IBG). It therefore becomes necessary, during certain command sequences, to reposition the tape so that it will be in the correct position with respect to the record head when record velocity is attained following a subsequent command. However, if the subsequent command is of the same category and is given within the reinstruct time, repositioning will not be required; tape motion will continue at the normal recording velocity.

Figure 2-3. Repositioning Cycle

#### 2-15. **Repositioning.** Repositioning is accomplished in three steps:

- a. Deceleration of tape to a rest position (forward).

- b. Acceleration of tape to a maximum velocity in the opposite direction (reverse).

- c. Deceleration of tape to rest position (reverse).

Figure 2-4 illustrates these three steps and shows the relative positions of the record head with respect to the recorded data. The velocity achieved during acceleration is equal to the record velocity of the tape (100 ips). A write operation is used for the purpose of illustration; however, a read operation is identical, except that recorded data might be on either side of the record head. Figures 2-4A, B, and C show the position of the head and the last data block following acceleration or deceleration. Figure 2-4D is a composite showing the position of the record head at any instant in time during repositioning. Segments AB, BC, and CD represent the actual repositioning, and segment DA is the acceleration after another command is issued (access time).

2-16. To allow for minor variations in acceleration and deceleration rates, the tape is allowed to run at speed for short distances during repositioning. This provides an offset, which is shown as points C and C' in Figure 2-4D. After repositioning, the record head might be left several data blocks in front of the point at which the next write or read operation is to take place. If one microprocessor command is followed by another in the opposite direction, it becomes necessary to perform an additional repositioning to allow the required distance for tape acceleration, as illustrated in Figure 2-5. This illustration represents a reverse read following a write forward. It can be seen that the second reposition is a retrace of the first. It is shown offset in time for clarity only.

Figure 2-4A. Ramp Down (FWD)

Figure 2-4C. Ramp Down (REV)

Figure 2-5. Reverse Direction Repositioning

### MAJOR TRANSPORT COMPONENTS

2-17. The CTU is composed of three main assemblies: the drive assembly, which includes the tape drive components and the compliance arm system; the power supply system, which consists of a transformer and a power supply assembly mounted on the bottom of the top plate; and the formatter printed wiring board (PWB), which contains the voltage regulation circuitry, servo control logic circuitry, reel motor servos, sensor circuits, write and read circuits, and input/output (1/0) interface circuits.

2-18. **Power Supply/System Failure Detect Circuit.** The power supply assembly consists of an RFI line filter, ac line fuse, and rectifier circuits. The voltage regulators and system failure detect circuits are located on the formatter PWB. The system failure detect circuitry removes the drive voltage from the servo motors in the event of a power failure.

2-19. Control Logic Circuitry. A Z8002 microprocessor with associated I/O chips serves as the primary control element in the CTU. The program is stored in 16K of onboard programmable read-only memory (PROM) circuits.

2-20. Takeup/Supply Servo Circuits. Both takeup and supply servos incorporate current feedback lines which are used to control the speed and torque of the reel motors. The voltage mode of operation is simulated by the microprocessor.

2-21. Sensor Input Circuits. The CTU utilizes 3 optical sensors as inputs to the microprocessor to monitor tape position and speed, tape in path, write enable, and EOT/BOT. Door sense status is indicated by a microswitch.

2-22. Write Circuitry. The write circuitry converts the phase encoded data from the system to write current levels which are applied to the write head. A full width erase bar is also used to ensure thorough erasure of the tape prior to normal write operation. A protection circuit is used to eliminate erroneous operation of the write head when the transport is powered up initially.

2-23. **Read Circuitry.** The analog signals generated in the read head are amplified, detected, and converted to phase encoded digital inputs for the data formatting circuitry. The formatter multiplexes the digital inputs into a set of buffers which allows electronic deskewing of the read data before it is strobed to the interface.

### DETAILED CIRCUIT DESCRIPTIONS

2-24. **Power Supply.** (Refer to Figure 2-6.) The ac input to the power supply is filtered by EMI filter FLI. The ac voltage is then routed through J5 to the POWER switch on the front panel and then through J9 to the primary of transformer TI. Solid state relay KI, located on the power supply PWB, is controlled by microprocessor output port Z2C2 which, when low, activates the blower motor BI.

2-25. The four secondary outputs of TI are rectified by UI, U2, CRI, and CR2. The +30- and -30-volt power supplies are rectified by U2. A 50/60 Hz, 7Vac signal is output at J7 pin 14 for use in the +5Vdc noise injection circuitry. The +9-volt power supply is rectified by CRI and CR2. Rectifier UI produces the +20- and -20-volt power supplies.

2-26. Voltage Regulators. The voltage control and regulator circuits are located on the formatter PWB and shown in Figure 2-7. The V20P signal is routed to VR2 which produces the +15V signal at TP84. A +12V signal is input to Q16 which produces the +5R signal at TP63. Q16 provides a constant current source to the system failure detect and servo position sensor circuits to isolate these inputs from the +5VCC loading. The V20M signal is regulated by VR1 to provide -12Vdc at TP82 and -6Vdc at R314. Q7 regulates the V9P input to provide +5Vdc at TP81 for the -5VCC circuits.

Figure 2-6. Power Supply Circuit

2-27. **Power Control and System Failure Detect Circuits.** (See Figure 2-8.) The +5R and +5Vdc voltages initiate the power-on sequence by charging C124 and C108 through R187 and R146. After an RC delay of greater than 1/2 but less than 1 second, the ouput of U3H-1 switches from low to high which clears the RES\* line and enables the microprocessor.

2-28. The V20P signal is routed to the door lock and hub lock circuits and energizes the door lock solenoid when the CIO output Z2B3 is high. The hub lock solenoid is activated when the CIO output Z2B2 is high.

2-29. **Microprocessor Section.** (See Figure 2-9.) The microprocessor circuit controls the operation of the CTU. When power is applied to the unit, the crystal-controlled (YI) oscillator circuit generates a 7.68-MHz clock signal. The 7.68-MHz clock signal is applied to a counter (U3K), which divides the signal by two to produce a 3.84-MHz clock signal at U3K-5. The counter also produces a divide-by-sixteen output (0.48 MHz) at U3K-12 that is used by the digital-to-analog converter logic. The 3.84-MHz clock signal is inverted at U2K-8 and U2K-10. The U2K-8 signal clocks the microprocessor (U2N), and the U2K-10 signal (CLK4) is used as a peripheral clock (PCLK) by the CIO's, and by the DMA controller logic and the cache memory addressing circuit.

2-30. When the 3.84-MHz microprocessor clock is initiated, the microprocessor begins executing instructions at address location 0 in memory. Typical instructions may be to jump to another location in memory, change a register, output a command, etc. The microprocessor obtains these instructions by way of multiplexed address/data lines ADØ through AD15. The ADØ through AD15 outputs from the microprocessor are also latched by U2L and U1L to produce latched address signals ALØ through AL15. The latched address signals address memory to obtain the instructions that are returned to the microprocessor on the ADØ through AD15 lines. An instruction is fetched from memory and strobed into the microprocessor by DS\* when MREQ\* and latched address AL15 are low and R/W from the microprocessor is high.

2-31. Address/data lines ADØ through AD15 route instructions and data to the microprocessor from the EPROM's and RAM's. Address/data lines AD6 through AD15 provide input data to the digital-to-analog converter (U6M), and address/data lines AD8 through AD15 interface with the cache memory bus. The functions of latched address lines ALØ through AL15 are detailed in Table 2-1. The WAIT\* input to the microprocessor is sent from the DMA control logic during a communication cycle between the microprocessor and the DMA controller to synchronize the operation.

2-32. Read and write operations of bus data are initiated by the microprocessor. The state of the R/W\* signal at U2N-25 determines whether a read or write operation is specified. An active (low) data strobe (DS\*) signal from U2N-17 causes a low at U1IP-3 to be applied gates U5K-2 and U5K-4. When R/W\* is high, signalling a read operation, it is inverted at U2K-2 to assert RDIN\* at U5K-8 when I/O\* is active. When R/W\* is low, signalling a write operation, WROUT\* is asserted at U5K-11 when I/O\* is active. RDIN\* and WROUT\* are used by the transport status register logic, the DMA control logic, and the DAC to specify read or write I/O functions.

Figure 2-8. System Failure Detect Circuit

Figure 2-9. Microprocessor Section

|    | LATCHED<br>ADDRESS LINE(S) | FUNCTION(S)                                                                                                                                                                                                                                            |

|----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40 | ALI-ALII                   | RAM addressing                                                                                                                                                                                                                                         |

|    | ALI-ALI4                   | EPROM addressing                                                                                                                                                                                                                                       |

|    | ALI-AL4                    | Inputs to address drivers AXØ-AX3 in DMA control logic                                                                                                                                                                                                 |

|    | ALØ-AL2                    | Transport status register<br>circuit addressing                                                                                                                                                                                                        |

|    | AL8-AL10                   | Chip Select (CS*) inputs to CIO's<br>ZI (U9L), Z2 (UIIL), and Z3 (UI3L)<br>in microprocessor section                                                                                                                                                   |

|    | ALØ                        | Control signal to RAM write control circuit                                                                                                                                                                                                            |

|    | ALII                       | Enables DMA controller to assume<br>control of DMA bus during an<br>I/O operation                                                                                                                                                                      |

|    | AL12                       | Transport status register circuit<br>enabling signal                                                                                                                                                                                                   |

|    | AL14                       | Chip Select (CS) input to<br>analog-to-digital converter (U6N)                                                                                                                                                                                         |

|    | AL 15                      | <ol> <li>Gated with Read Data In (RDIN*)<br/>from microprocessor section to<br/>produce Read Command (RDCMD*),<br/>which enables transport status<br/>register drivers and enables<br/>outputs of input tape motion<br/>command latch (U2W)</li> </ol> |

|    |                            | (2) Chip Select (CS) input to digital-to-analog converter (U6M)                                                                                                                                                                                        |

|    |                            | (3) Chip Select (CS*) input to<br>EPROM's and RAM's                                                                                                                                                                                                    |

## Table 2-1. Latched Addresses ALØ-AL15 Functions

2-33. The microprocessor section utilizes counter/timer and parallel I/O units (CIO's) (U9L, U11L, and U13L) to provide both timing and I/O communications for internal CTU circuits. The programmable CIO's each contain three I/O ports and three counter/timers. The CIO's are clocked by peripheral clock signal CLK4 and are sequentially selected by latched addresses AL8, AL9, and AL10. The microprocessor addresses the CIO's on the address/data bus (AD0-AD7). Bi-directional communications with system circuits is provided on the A0-A7, B0-B7, and C0-C3 output lines from each CIO. The inputs from system circuits are returned to the microprocessor on the AD0-AD7 address/data bus.

2-34. **DMA Control Logic.** (See Figure 2-10.) The DMA control logic consists of DMA controller U2T and associated logic circuit. The DMA control logic controls the operation of the cache memory in response to service requests from the microprocessor requests on a priority basis, as follows:

| <b>Priority</b> | Request/Function                                                                |

|-----------------|---------------------------------------------------------------------------------|

|                 | DREQ $\emptyset$ - 1/O, cache to physical tape                                  |

| 2               | DREQ 1 – 1/O, interface to cache<br>DREQ 2 – Z8002/Cache communications via DMA |

| 4               | DREQ 3 - Refresh cache                                                          |

When the DMA control logic is busy performing a function in response to a microprocessor request, and one or more additional requests are received, the DMA controller completes its present cycle and then selects the highest priority request pending.

## NOTE

DREQ 3, the refresh cache request, is always set when a refresh is not taking place. As other requests are received, the controller processes them in the order of their priorities. However, after every three cycles of servicing higher priority requests, the controller will service DREQ 3. The longest period between refreshes is 8.4 microseconds. Refreshing is disabled during active channel 0 and 1 operations. When no other requests are pending, cache is continuously being refreshed.

2-35. The service requests from the microprocessor are latched by D-type flipflops. The respective Data Request signals are sent to the DMA controller (U2T), which sets Hold Request (HLDR) to request control of the cache from the microprocessor. When the microprocessor acknowledges the request, Hold Acknowledge (HLDA) is received by the DMA controller, which then issues a Data Acknowledge (DACK) signal to reset the DREQ line. The microprocessor signals, request/acknowledge signals, and the devices for each of the DREQ signals are as follows:

2-36. A typical example of the data request sequence and the response of the DMA control logic when servicing a DREQ I is as follows:

- a. UI4T is set by ZIB4 (Formatter Interface Clock) from the processor CIO, asserting DREQ I at UI4T-9.

- b. DREQ I is sent to the DMA controller (U2T-18), which generates Hold Request (HLDR) to request control of the cache bus from the microprocessor.

- c. HLDR is sent to flip-flop U5P-13 and gate U4P-13. This removes the low reset signal at U5P-13 and conditions AND gate U4P-11 for the signal from inverter U3P-4.

- d. The IO signal from the microprocessor is high at U7V-13 and AL11 is low at U7V-12. The resulting low at U7V-11 is inverted by U3P-4, sending a high to U4P-12 to enable the AND gate.

- e. The high at U4P-11 sets U5P on the next CLK4 pulse from the microprocessor section clock logic, resulting in a high at U5P-9 that is sent to the Hold Acknowledge (HLDA) input of the DMA controller.

- f. The DMA controller assumes control of the cache bus and generates DACKI\* to acknowledge receipt of HLDA. DACKI\* resets UI4T via OR gate UI4R and returns DREQ I to low.