# HARDWARE REFERENCE MANUAL

CGC 7900 SERIES COLOR GRAPHICS COMPUTERS

## CHROMATICS

## CGC 7900 COLOR GRAPHICS COMPUTER SYSTEM

HARDWARE REFERENCE MANUAL April, 1982

Copyright (C) 1982 by Chromatics, Inc. 2558 Mountain Industrial Boulevard Tucker, Georgia 30084

Phone (404) 493-7000 TWX 810-766-8099

This document, submitted in confidence, contains proprietary information which shall not be reproduced or transferred to others or used for manufacturing or any other purpose without prior written permission of Chromatics, Incorporated.

This manual is Chromatics Part Number 070203A. It was previously released as the Preliminary OEM Manual. This edition contains corrections and new information.

# PUBLICATION COMMENT FORM

Please use this sheet to give us feedback on the enclosed documentation. Your comments on errors or omissions, suggested changes, format of presentation, etc., will be helpful in preparing future manuals. Wherever possible, refer to specific page numbers in your comments below. After completing this form, mail to:

Chromatics, Inc. 2558 Mountain Industrial Boulevard Tucker, GA 30084

Attn: R & D Department

| Name:_   |                         |          | Date:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|----------|-------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Company  | y Name:                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          | odel Number of Product: |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          | of Publication:         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          | f Publication Release:  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| Page No. |                         | Comments |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|          |                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ |

|          |                         |          | and the second s | _ |

# TABLE OF CONTENTS

| INTRODUCTION                                                                                                                                                                      | 1                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| CGC 7900 HARDWARE OVERVIEW                                                                                                                                                        | 2                                    |

| CPU CARD EPROM/RASTER PROCESSOR CARD BUFFER MEMORY CARDS IMAGE MEMORY CARDS CONFIGURATION OF MEMORY CARDS VIDEO CONTROL CARDS DMA/PIO SERIAL PORT CONTROLLER                      | 3<br>4<br>5<br>5<br>5<br>6<br>7<br>8 |

| POWER SUPPLY                                                                                                                                                                      | 9                                    |

| CGC 7900 SYSTEM MEMORY MAP (Illustration)                                                                                                                                         | 11                                   |

| CGC 7900 MEMORY MAP                                                                                                                                                               | 13                                   |

| EPROM INSTALLATION                                                                                                                                                                | 14<br>15                             |

| IMAGE MEMORY PLANE MODE Z MODE COLOR STATUS MODE                                                                                                                                  | 16<br>17<br>18<br>20                 |

| COLOR LOOKUP TABLE ADDRESSES                                                                                                                                                      | 22<br>23                             |

| OVERLAY MEMORY ADDRESSING<br>OVERLAY CHARACTER CELL ADDRESSES                                                                                                                     | 2 4<br>26                            |

| CGC 7900 DETAILED MEMORY MAP                                                                                                                                                      | 27                                   |

| CONFIGURING 128K BUFFER MEMORY CARDS CONFIGURING 512K BUFFER MEMORY CARDS BUFFER MEMORY CARD ADDRESS SELECTION CONFIGURING IMAGE MEMORY PLANES IMAGE MEMORY CONFIGURATION JUMPERS | 31<br>32<br>33<br>34<br>40           |

| HARDWARE LATCHES AND CMOS/STATIC RAM                                                                                                                                              | 41                                   |

| BITMAP ROLL COUNTER<br>X PAN                                                                                                                                                      | 42<br>43                             |

|             | Y PAN X AND Y ZOOM BLINK SELECT PLANE SELECT PLANE VIDEO SWITCH COLOR STATUS FOREGROUND/BACK OVERLAY ROLL COUNTER IMAGE SELECT OVERLAY CURSOR BLINK OVERLAY CHARACTER BLINK | KGROUND | 44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>51 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------|

| <b>I/</b> 0 | MAP                                                                                                                                                                         |         | 53                                                 |

|             | SERIAL PORTS SERIAL PORT PINOUTS INTERFACING RS232 AND F                                                                                                                    | RS449   | 54<br>55<br>56                                     |

|             | BAUD RATE GENERATOR                                                                                                                                                         |         | 57                                                 |

|             | JOYSTICK                                                                                                                                                                    |         | 58                                                 |

|             | BEZEL SWITCHES                                                                                                                                                              |         | 6 Ø                                                |

|             | INTERRUPT HANDLING<br>INTERRUPT MASK<br>BUS INTERRUPTS (BINT)                                                                                                               |         | 61<br>62<br>63                                     |

|             | BUS CHIP SELECTS  BCS1 ADDRESSES  LIGHT PEN  SYNC ADDRESSES  BUFFER MEMORY PARITY                                                                                           |         | 64<br>65<br>65<br>66                               |

|             | DISK PORT PINOUT                                                                                                                                                            |         | 68<br>70                                           |

|             | REAL TIME CLOCK                                                                                                                                                             |         | 71                                                 |

|             | PROGRAMMABLE SOUND GENERATOR<br>PROGRAMMING THE PSG<br>PSG REGISTERS<br>PSG MUSICAL NOTES                                                                                   | ₹       | 74<br>75<br>76<br>78                               |

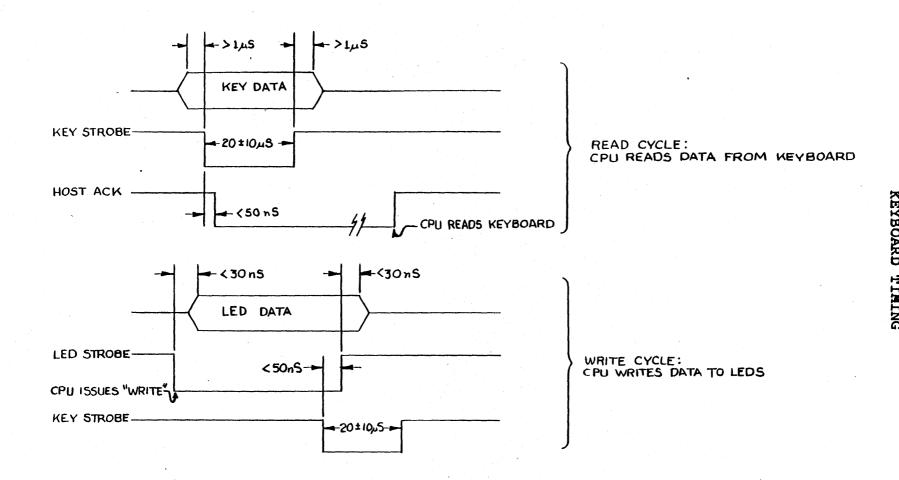

|             | KEYBOARD KEYBOARD CABLE PINOUT KEYBOARD DATA BUS KEYBOARD LED SELECT COI INTERFACING PERIPHERALS KEYBOARD TIMING                                                            |         | 79<br>81<br>82<br>83<br>84<br>85                   |

|             |                                                                                                                                                                             |         |                                                    |

HARDWARE VECTOR GENERATOR

87

| SAMPLE HVG PROGRAMS                                                                                                       | 89                            |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| INTERFACE SUGGESTIONS                                                                                                     | 91                            |

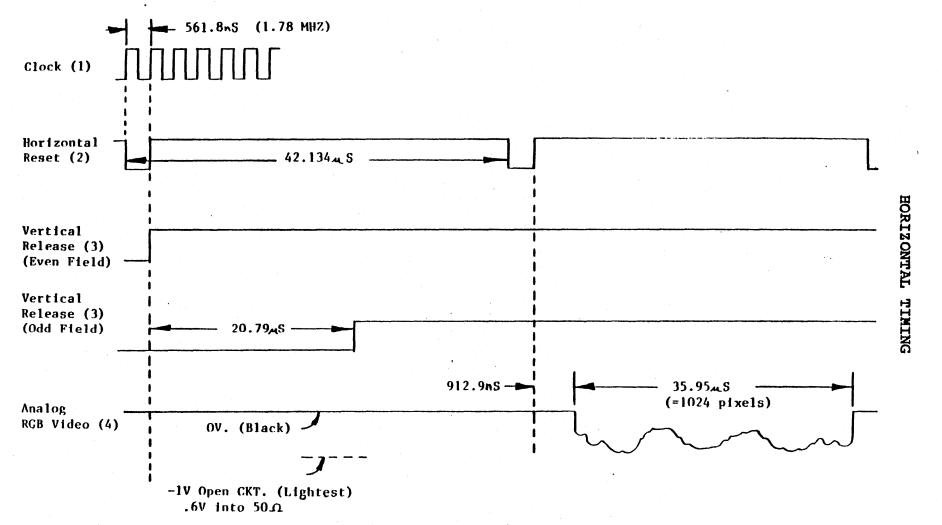

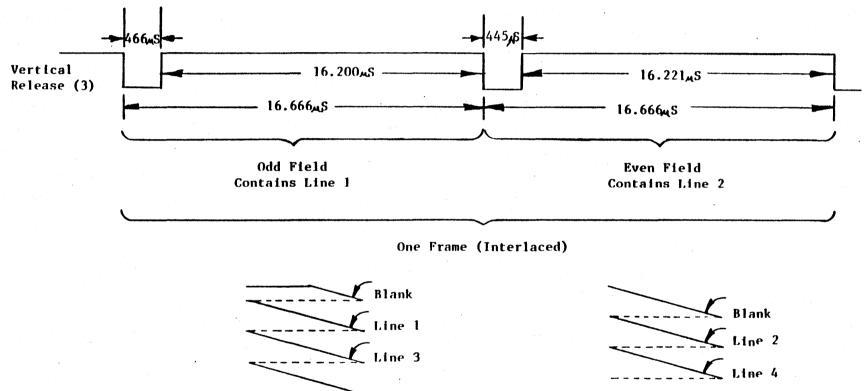

| SYNC SIGNALS HORIZONTAL TIMING VERTICAL TIMING                                                                            | 93<br>95<br>96                |

| CGC 7900 SYSTEM BUS P1 CONNECTOR IDENTIFICATION P1 SIGNAL DESCRIPTIONS P2 CONNECTOR IDENTIFICATION P2 SIGNAL DESCRIPTIONS | 97<br>98<br>100<br>103<br>105 |

#### INTRODUCTION

This manual provides hardware information to users of Chromatics CGC 7900 Color Graphics Computer System. The information contained in this manual should be considered proprietary in nature. It is provided solely to aid our customers in interfacing to the 7900 hardware.

This manual should be used in conjunction with other CGC 7900 manuals. The 7900 Operator's Manual gives detailed information about standard 7900 firmware, including the graphics functions and the Terminal Emulator program, TERMEM. The 7900 DOS Manual describes the Disk Operating System, MC68000 assembler, and text editor, which will be useful in developing programs on the 7900. The 7900 also supports the Idris multi-tasking operating system, and complete Idris documentation is also available from Chromatics.

The information in this manual will be of assistance in writing custom software drivers for the 7900 hardware. Be aware, however, that nearly all of the 7900 system can be controlled through the Terminal Emulator program and routines in standard firmware. It will not be necessary to re-invent the wheel in many applications.

While the information in this document is believed to be accurate, no guarantees are made. Chromatics reserves the right to make product changes at any time.

# CGC 7900 HARDWARE OVERVIEW

The CGC 7900 is a self-contained computer system. It is capable of extremely high-resolution color graphics displays. The 7900 Central Processing Unit (CPU) uses the MC68000 microprocessor. The system may be equipped with a hard disk and two floppy disks, a light pen, joystick, and several megabytes of memory for images and programs.

The chassis contains a motherboard with 12 or 24 card connectors. The lower portion of the chassis houses the digital electronics, and the upper portion contains the analog circuitry. Power supplies and the hard disk drive are mounted in the bottom of the chassis. Six fans mounted below the card cage ventilate the chassis. The system is mounted on casters for easy transportation.

The analog chassis contains a high-resolution, 19-inch color Cathode Ray Tube (CRT). The CRT is treated with a long persistance phosphor, to minimize the problem of interlace flicker. All high voltages are present only in the analog chassis.

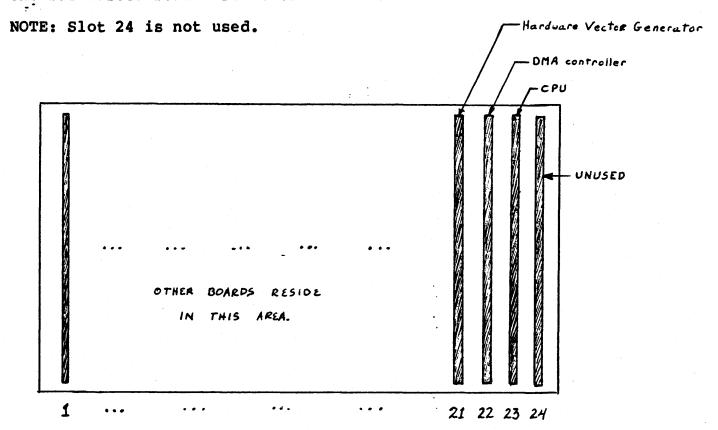

CGC 7900 Addendum -- Card cage layout

The following information corrects any previous information on this topic.

All bus masters (CPU, DMA, hardware vector generator) must be in the highest numbered slots in the CGC 7900 card cage. Thus, bus master boards work their way downward from slot 23. The Raster Processor must be in slot 1. Bitmap boards begin in slot 5 and work toward higher slots. I/O and memory boards pick up where the bus master boards leave off and work downward.

Hypothetical CGC 7900 card cage

# CPU CARD

The CGC 7900 Central Processing Unit (CPU) card contains the MC68000 microprocessor, which can directly address 16 Megabytes of memory. This card generates most of the control signals used by the processor to control memory.

The CPU card contains 4K bytes of static memory. This may optionally be replaced by CMOS memory, powered by a battery backup supply on this card. The CMOS option includes a Real-Time Clock, also located on the CPU card.

All input/output interface hardware in the standard 7900 system is found on the CPU card. This includes the keyboard, joystick, disk, bezel keys, and two serial ports. I/O is connected to the CPU card by edge connectors on the back of the card. Each of the I/O interfaces is discussed in a separate section of this manual.

A Programmable Sound Generator is installed on the CPU card. It may be operated by the CGC system programs or by user programs. It connects to a speaker, below the keyboard, on the chassis front. A Quiet Lock key on the keyboard disables the speaker.

## EPROM/RASTER PROCESSOR CARD

EPROM sockets on this card are addressed from 800000 to 80FFFF. The EPROMs must be 2532 type (32K bits), 350 nanoseconds or faster. See the "Memory Map" section of this manual for programming requirements.

The Raster Processor is a bipolar circuit, microprogrammed to perform an address translation function in the 7900 system. This device assists the MC68000 in moving pixels on the image memory screen.

This card also contains bus terminators which decrease noise on the motherboard. Because of the extremely high processor speeds (up to 8 MHz), these terminators are very important in the 7900 system.

## BUFFER MEMORY CARDS

The 7900 contains one or more Buffer Memory cards. Each card holds 128K or 512K bytes of dynamic RAM for system memory requirements and user programs. The first card is addressed at zero, and other cards are usually addressed consecutively.

Each card stores a parity bit for each byte of data stored. Parity is stored with each write, and checked with each read. If a parity error is detected the card will notify the processor. Systems which use the parity checking feature must write data to ALL buffer memory when the system is powered-up, or risk a parity error if a location is read that was not previously written. (Parity checking will only function if a parity jumper is installed on each Buffer Memory card.)

## IMAGE MEMORY CARDS

Up to 16 Image Memory cards, or planes, may be installed in the 7900. The number of planes determines how many simultaneous colors may be displayed in the high-resolution Bitmap memory. Typical systems will contain 1, 4, 8 or 16 Image planes.

Each plane may be accessed through several addressing modes. These are discussed under "Image Memory" in the Memory Map section of this manual. Because of the varied addressing modes, a plane might respond to addresses anywhere between A00000 and Elffff.

## CONFIGURATION OF MEMORY CARDS

A later section of this document discusses the requirements for configuring memory cards (setting switches and jumpers).

# VIDEO CONTROL CARDS

Three cards in the 7900 are used for generating and controlling the video image. These are the Overlay, Color Lookup, and Memory Controller. These cards have no programmable functions, and the descriptions below are for information only.

The Memory Controller generates all signals for operating the video memories. It allows CPU accesses, refresh accesses, and video data accesses to occur without conflicts. It produces refresh signals to sustain the dynamic RAM chips in the image memories. A ribbon cable connects the Memory Controller to the Raster Processor. This path allows the Raster Processor full access to the image memory in several addressing modes. A twisted-pair cable carries sync signals from the Memory Controller to the analog chassis.

The Overlay contains the 85 by 48 character-cell memory, and logic to generate Overlay characters and plot dots, with their associated attributes. This information is carried to the Color Lookup card over a ribbon cable. Light Pen logic is also on the Overlay.

The Color Lookup card receives image data from up to 16 Refresh Planes. Each pixel is used as an index into a high-speed RAM table, which contains the color lookup assignments. Data out of the lookup RAM is combined with Overlay data, according to the transparency attributes of the Overlay. This combined data is sent up to the analog chassis where it is converted to analog video signals by D-to-A converters. The Color Lookup is a three-layer card, to provide shielding for the high-speed ECL logic.

# DMA/PIO

The 7900 DMA/PIO is an optional card. It contains a DEC-compatible DMA interface, capable of connecting to a DRV-11B, DR11-W, or DR11-B interface. The DMA interface uses two 16-bit parallel ports, one for input and one for output, and supports burst or single-cycle DMA transfers up to 500K transfers per second.

The PIO section of the DMA/PIO card is a general-purpose parallel input/output port. It has two 16-bit parallel ports, one for input and one for output; these can also be used as 8-bit parallel ports. The PIO can operate through polled or interrupt-driven software, at rates up to 150K transfers per second (software-dependent).

Additional information on the PIO/DMA hardware is available from Chromatics, in a separate document.

(DEC, DRV-11B, DR11-W, and DR11-B are trademarks of Digital Equipment Corporation.)

# SERIAL PORT CONTROLLER

The 7900 Serial Port Controller (SPC) is an optional card. It contains four RS232 serial I/O ports, and an onboard Z80 processor to handle buffering and handshaking.

The SPC holds up to 8K bytes of EPROM (2532 type). It also has 4K of onboard RAM for the Z80's use in buffering data, and 1K of two-port RAM for data transfer between the 68000 and the Z80. 16 baud rates are standard. User-written firmware may be installed to support external clocking and synchronous protocols.

Additional information on the SPC is available from Chromatics, in a separate document.

# POWER SUPPLY

The 7900 is powered by high-efficiency switching power supplies. The switching frequency is approximately 25 KHz, and is synchronized to the system clocks. Either one or two power supplies may be installed, depending on the options ordered in a 7900 unit. All voltages from the supplies are regulated, eliminating the need for on-card regulation.

Power supply A is always installed. It provides power for a 7900 without disk drives, and with less than 12 cards installed in the card cage. Supply A delivers the following outputs:

- +5 Volts at 20 Amps -5 Volts at 10 Amps

- +6.3 Volts at 1 Amp

- +12 Volts at 7 Amps -12 Volts at 0.3 Amp

- +25 Volts at 3.5 Amps -25 Volts at 2 Amps

- +9 Volts at 1 Amp

- -9 Volts at 1 Amp

- +100 Volts at 1.25 Amp

The +100, +9 and -9 Volts supplies are used only by the analog chassis. Other supplies may be used by either chassis.

CAUTION! The motherboard is designed so that two power supplies may share the +5 and +12 volt loads. The motherboard runs for these supply lines are split, and fed to separate terminals at the top of the motherboard. If only supply A is installed, it must be jumpered to feed +5 and +12 to both halves of the card cage. If supply B is installed as well, the jumpers MUST NOT be installed or extreme currents will be drawn.

Supply B is required if more than 12 cards are installed, or if any disk drives are installed. Supply B delivers the following outputs:

+5 Volts at 10 Amps (to card cage and disks)

-5 Volts at 1 Amp (to disks only)

+12 Volts at 6 Amps (to card cage only)

+24 Volts at 9 Amps (to disks only)

The CGC 7900 requires approximately 13 amperes of 110 volt AC power. The system has a rear panel fuse rated at 15 amperes. Each power supply is internally fused at 10 amperes.

NOTE: Because of the design of the switching regulators, it is required that the +5 volt output of each supply MUST BE LOADED AT ALL TIMES. All other voltages are referenced to the +5 output. If the +5 is not loaded, extreme voltages will result and the supply will shut down.

If excessive currents are drawn from the supply, it will fold back the output voltage in an attempt to reduce the overload. If the overload persists, the internal or external fuses may blow.

# CGC 7900 SYSTEM MEMORY MAP

|             | 000000                                | 200000 | 400000 | 600000 | 800000 | AØØØØØ | CØØØØØ         | EØØØØØ |

|-------------|---------------------------------------|--------|--------|--------|--------|--------|----------------|--------|

| 000000      | Buffer                                |        |        |        | EPROM  |        | Image          | Color  |

|             | Memory                                |        |        |        |        | _      | Plane          | Status |

| 020000      | Card Ø<br>Buffer                      |        |        |        |        | Z      | Ø              | Map    |

| 020000      | Memory                                |        |        |        |        |        | Image<br>Plane | Misc   |

|             | Card 1                                |        |        |        |        | М      | 1              | 100    |

| 040000      |                                       |        |        |        |        | 0      | Image          |        |

|             |                                       |        | ·      |        |        | đ      | Plane          |        |

| 262222      | <u> </u>                              |        |        |        |        | e      | 2              |        |

| 060000      |                                       |        |        |        |        |        | •              |        |

|             |                                       |        |        | ,      |        | s      | •              |        |

| 080000      |                                       |        |        |        |        | C      | •              |        |

|             |                                       |        |        |        |        | r      |                |        |

|             |                                       | 7      |        |        |        | е      | •              |        |

| 0 A 0 0 0 0 |                                       |        |        |        |        | е      | •              |        |

|             |                                       |        |        |        |        | n      | •              |        |

| 00000       |                                       |        |        |        |        |        |                |        |

| DCDDDD      |                                       |        |        |        |        | M      | •              |        |

|             |                                       |        |        |        | ·      | e      | •              |        |

| ØEØØØØ      |                                       |        |        |        |        | m      | Image          |        |

|             |                                       |        |        |        |        | 0      | Plane          |        |

|             |                                       |        |        |        |        | r      | 7              |        |

| 100000      |                                       | . '    |        |        |        | У      | Image          |        |

|             |                                       |        |        |        |        |        | Plane          |        |

| 120000      |                                       |        |        |        |        |        | 8              |        |

| 120000      |                                       |        |        |        |        |        | •              |        |

|             |                                       |        |        |        | 100    |        |                | 1      |

| 140000      |                                       |        | One    |        |        |        | •              |        |

|             |                                       |        | Block  |        |        |        | •              |        |

| 160000      |                                       |        | = 128K |        |        |        | •              |        |

| 160000      |                                       |        |        |        |        |        | •              | 1      |

|             |                                       |        |        |        |        |        | •              | l      |

| 180000      |                                       |        |        |        |        |        | •              |        |

|             |                                       |        |        |        |        |        |                |        |

|             |                                       |        |        |        |        |        |                |        |

| 1A0000      |                                       |        |        |        |        |        | •              |        |

|             |                                       |        |        |        |        |        | •              | 1      |

| 100000      |                                       |        |        |        |        |        |                |        |

| 70000       |                                       |        |        |        |        |        | •              |        |

|             |                                       |        |        |        |        |        |                |        |

| 1E0000      |                                       |        |        |        |        | ·      | Image          |        |

|             | , , , , , , , , , , , , , , , , , , , |        |        |        |        |        | Plane          |        |

|             |                                       |        |        |        |        |        | 15             | I/O    |

# CGC 7900 MEMORY MAP

The processor in the CGC 7900 is capable of directly addressing over 16 Megabytes of memory, using a 24-bit address bus. The addressing range is 000000 to FFFFFF (hex). Chromatics reserves the upper half of this space, beginning at 800000 (hex).

The lower half of the 7900 address space will normally contain one or more Buffer Memory cards. Each card contains 128K or 512K bytes of dynamic RAM. The first card must be located at address 000000-1FFFFF (the first 128K of memory) to provide the processor with room for interrupt vectors. The remainder of this card, plus any other Buffer Memory cards which may be installed, is allocated among various system functions, and user programs.

The "Thaw" command in firmware allocates memory among input/output buffers, stacks, the Create Buffer, function key buffers, etc. If battery-powered CMOS RAM (optional) is installed in your system, the parameters set up by "Thaw" will be remembered and used to allocate memory next time the system is powered up. If CMOS RAM is not present, memory will be allocated according to default parameters in PROM.

## EPROM

System EPROM begins at address 800000. The Raster Processor card contains EPROM for the standard system. Space is provided for 32K words (64K bytes), addressed from 800000 to 80FFF. The card will accommodate Motorola 2532-C35 EPROMs (or equivalent) which have access times of 350 nanoseconds or faster.

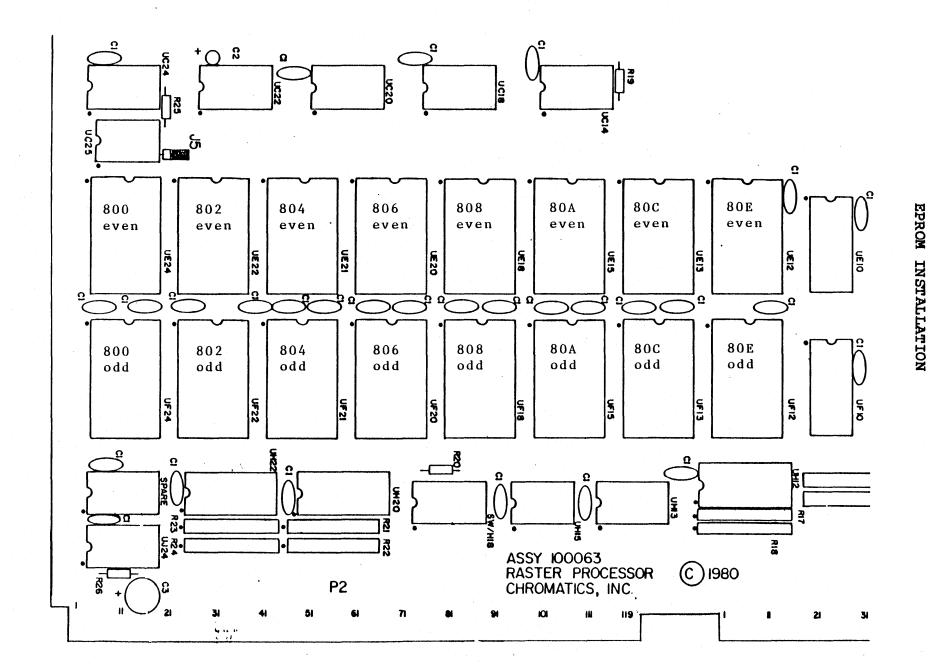

2532 EPROMs are capable of storing 32K bits of data, arranged as 4K of 8-bit bytes. Since the 68000 fetches all instructions as 16-bit words, two 2532s must be accessed simultaneously for each instruction fetch. This requires that data in the 2532s be separated into "odd" bytes and "even" bytes. Each 4K of words in EPROM thus requires two 2532s, one containing all the "odd" numbered bytes in the program, and one containing all the "even" numbered bytes. A total of 16 2532s may be inserted in the sockets provided on the Raster Processor card.

A special mapping is provided for convenience during processor startup. When external Reset is applied, the 68000 fetches its stack pointer and program counter as two 32-bit words, from addresses 000000 and 000004, respectively. The EPROM circuitry maps addresses 800000 and 800004 into this space. Thus, the first two long words in EPROM should contain the initial values of stack pointer and program counter.

The figure on the following page shows where system EPROMs are installed on the Raster Processor card. Each socket is labeled with "even" or "odd", depending on whether it contains the even or odd bytes of code. Each socket is also labeled with the first three digits of its address. For example, the first socket is labeled "800 even", and it contains all even bytes between addresses 800000 and 801FFF.

# IMAGE MEMORY

Image memory on the CGC 7900 consists of from one to sixteen Refresh Memory cards. Each Refresh Memory card, or plane, contains 128K bytes of dynamic RAM. The bits on these planes are manipulated by software to produce high-resolution Bitmap images. Then, the information in the planes is brought out through the image control logic and the Color Lookup Table, to produce an image on the screen.

All areas of the memory map designated as image memory are protected against Bus Errors. Regardless of the number of planes installed in the image memory of a 7900 system, it is impossible to receive a Bus Error from image memory accesses.

The CGC 7900 provides several ways to address image memory. Each of these methods is discussed in turn.

# PLANE MODE

In Plane mode, each plane of image memory is accessed as an independent 128K chunk of memory. Writing a byte, word, or long word into the image memory in Plane mode will write only into that plane. Plane mode addressing is equivalent to the way memory is addressed in most computer systems, and is the same way that Buffer Memory is addressed in the 7900.

Plane mode addressing begins at address C00000 and ends at DFFFFF (hex). Each plane occupies 128K bytes. The planes are numbered from 0 to 15, although many systems will not have all planes installed. In particular, most systems will be configured in one of the following ways:

| Total  | Planes | In System | Plane | Numbers | Assigned |

|--------|--------|-----------|-------|---------|----------|

|        |        | 1         | Ø     |         |          |

|        |        | 4         | Ø     | ,1,2,7  |          |

|        |        | 8         | ø     | thru 7  |          |

| *<br>% |        | 16        | Ø     | thru 15 |          |

Plane 7 is normally assigned for use as the "blink" plane, so it is important that a plane 7 exist in all but the most basic systems.

# Z MODE

Z mode is one of the two special modes provided for accessing image memory planes.

Consider the image memory to be arranged as a set of 16 planes, one in front of another. Each plane contains 1024 x 1024 bits, or 128K bytes. Each pixel on the screen is represented by a single bit from each of the 16 planes. Z mode allows the processor to write a 16-bit word to memory, and have each bit fall into the corresponding location of its plane.

For example, consider an instruction to write the first pixel in image memory (the upper left corner of the screen):

MOVE.W #PixelData, \$A00000

Bit Ø of "PixelData" will be moved into the first bit of image plane Ø. Bit I will be moved into the first bit of image plane I, and so on. The Z mode hardware allows writing to individual bits, without the problem of modifying adjacent bits in each plane.

Z mode addressing occupies a full 2 Megabytes of the address space. It begins at address A00000 and ends at BFFFFF. Note that since only 768 lines of the image memory are visible at a time, the pixel addressed at BFFFFF is not normally visible. The last visible pixel of image memory is addressed at B7FFFF (assuming pan and zoom are not in effect).

In Z mode, no assumptions are made concerning the number of planes in a system. If a plane does not exist, any bits which should be written into that plane are simply thrown away. When reading back data in Z mode, any bits which should come from non-existant planes will be returned as logical highs, or ones.

Z mode access to individual planes is restricted by Plane Select. Plane Select is a 16-bit latch, located at address E40012. If a bit of this latch is a one, the corresponding plane is enabled. If a bit is zero, the plane is disabled. Disabled planes may not be written into using Z mode, and reading from them in Z mode will return a zero in the bit positions of the disabled planes. In this way, non-existant

planes may be masked using Plane Select so that bits returned from them will be zeros.

## COLOR STATUS MODE

Color Status mode provides a very fast way to write color information into the image memory planes. Color Status occupies 128K bytes, the same area one image plane occupies in Plane mode. Color Status mode is mapped from E00000 to Elffff. This is a "write-only" area of memory. Attempts to read from this area will return indefinite data.

Before using Color Status mode, it is necessary to load the Color Status Foreground and Background latches. Each of these contains a 16-bit number. Color Status Foreground is located at E40016, and Color Status Background is at E40018. Each of these should be loaded with the 16-bit quantity you would write into image memory if you were using Z mode addressing. For example, if the foreground of the pattern you are writing requires color number 5, you would load the Color Status Foreground latch with 5. Similarly, Color Status Background might be loaded with color number 0. (These numbers refer to entries in the Color Lookup Table.)

After loading the latches, you may write to the Color Status area of memory. Each bit you write will affect a single pixel of the image, one bit in each of the 16 image planes. If you write a bit which is a 1, the pixel will be written in foreground color, as defined by the Color Status Foreground latch. If a bit is 0, the pixel will be written in background color, defined by Color Status Background.

For example: to make the first 32 pixels of the screen white, we might execute the following code.

| ForeG   | EQU | \$E40016 | Foreground latch           |      |

|---------|-----|----------|----------------------------|------|

| BackG   | EQU | \$E40018 | Background latch           |      |

| ColStat | EOU | SE00000  | Color Status mode starts h | iere |

MOVE.W #7, ForeG set up FG Color Status (assume color 7 = white)

WRITE MOVE.L #\$FFFFFFFF, ColStat write 32 bits of ones

The single instruction at label WRITE modifies the color of 32 pixels. The same operation would require 32 writes in Z mode, or 16 writes in Plane mode (to write all 16 planes).

The following example will write an alternating series of 32 red and green pixels into the first 32 pixels of the screen.

MOVE.W #4,ForeG make foreground color = 4 MOVE.W #2,BackG make background color = 2 (assume 4 = red, 2 = green)

MOVE.L #\$AAAAAAA, ColStat write alternating bits

Color Status mode allows writing bytes, words, or long words, to modify 8, 16, or 32 pixels, respectively.

The image memory planes are grouped into two sets of 8 planes each. Each of these two sets may contain an image, and Plane Select is normally used to decide which of the two is written into when a 16-bit Z mode write is performed. When writing with Color Status, it may be useful to write both images with the same color (otherwise one image would be written with zeros). To prevent this problem from occurring, always load the Color Status latches with the same number in the upper and lower bytes. Following this rule, our first example above must be corrected to contain the statement

MOVE.W #\$0707,ForeG set up FG Color Status (assume color 7 = white)

(Copying the lower byte into the upper byte of the latch information.)

# COLOR LOOKUP TABLE

The Color Lookup Table consists of 256 locations, each of which holds a 24-bit number. Eight of these bits determine the red component of a color, eight for green, and eight for blue. A pixel in the Bitmap (image memory) is given a color by summing the bits in whichever set of 8 planes is being viewed (weighted binary sum), and the resulting value points to an entry in the Color Lookup Table. The color components in that entry of the Color Lookup Table provide the color of that pixel.

The table is arranged as 256 long words (1K bytes), starting at address E30000. Each long word is organized as follows:

| Bits | 31-24 | 23-16     | 15-8        | 7-0        |

|------|-------|-----------|-------------|------------|

|      | FF    | 8-bit red | 8-bit green | 8-bit blue |

The high byte (bits 31-24) of each entry are undefined, so they read out as FF hex. The next 8 bits set the red intensity, followed by green and blue.

The Color Lookup Table may be read or written at any time. Values written into the table are not used on the screen until the next vertical retrace, so it is not useful to write a single entry more than once per screen scan (1/60 second with 60 Hz power). Writing to the Color Lookup Table at any time will not cause the display to "glitch."

# COLOR LOOKUP TABLE ADDRESSES