## CHIPS AND TECHNOLOGIES, INC. 3050 ZANKER ROAD, SAN JOSE, CA 95134 408-434-0600

## PRELIMINARY SPECIFICATION

# CHIPS/280 MODEL 70/80 COMPATIBLE CHIPSET (16-, 20-, 25-, & 33-MHZ\*)

\* 33MHZ TIMING WAVEFORMS & T-NUMBERS ARE AVAILABLE IN A SEPARATE DOCUMENT

August 9, 1989 CPI022.1/8-89 Rev 1.0 STK#10022-002

#### CHIPS AND TECHNOLOGIES, INC. 3050 ZANKER ROAD, SAN JOSE, CA 95134 408-434-0600

## PRELIMINARY SPECIFICATION

# CHIPS/280 MODEL 70/80 COMPATIBLE CHIPSET (16-, 20-, 25-, & 33-MHz\*)

\* 33MHZ TIMING WAVEFORMS & T-NUMBERS ARE AVAILABLE IN A SEPARATE DOCUMENT

AUGUST 9, 1989 CPI022.1/8-89 Rev 1.0

**COPYRIGHT NOTICE**

COPYRIGHT 1989, CHIPS AND TECHNOLOGIES, INC. ALL RIGHTS RESERVED.

THIS MANUAL IS COPYRIGHTED BY CHIPS AND TECHNOLOGIES, INC. YOU MAY NOT REPRODUCE, TRANSMIT, TRANSCRIBE, STORE IN A RETRIEVAL SYSTEM, OR TRANSLATE INTO ANY LANGUAGE OR COMPUTER LANGUAGE, IN ANY FORM OR BY AN MEANS, ELECTRONIC, MECHANICAL, MAGNETIC, OPTICAL, CHEMICAL, OR OTHERWISE, ANY PART OF THIS PUBLICATION WITHOUT THE EXPRESS WRITTEN PERMISSION OF CHIPS AND TECHNOLOGIES, INC.

#### TRADEMARKS

CHIPS, AND CHIPS/280 ARE COPYRIGHTS OF CHIPS AND TECHNOLOGIES, INC. PS/2 IS A TRADEMARK OF INTERNATIONAL BUSINESS MACHINES CORPORATION. INTEL, 386, 387, 386SX AND 387SX ARE TRADEMARKS OF INTEL CORPORATION.

#### DISCLAIMER

CHIPS AND TECHNOLOGIES, INC. MAKES NO REPRESENTATIONS OR WARRANTIES REGARDING THE CONTENTS OF THIS MANUAL. WE RESERVE THE RIGHT TO REVISE THE MANUAL OR MAKE CHANGES IN THE SPECIFICATIONS OF THE PRODUCT DESCRIBED WITHIN IT AT ANY TIME WITHOUT NOTICE AND WITHOUT OBLIGATION TO NOTIFY ANY PERSONS OF SUCH REVISION OR CHANGE.

THE INFORMATION CONTAINED IN THIS MANUAL IS PROVIDED FOR GENERAL USE BY OUR CUSTOMERS. OUR CUSTOMERS SHOULD BE AWARE THAT THE PERSONAL COMPUTER FIELD IS THE SUBJECT OF MANY PATENTS. OUR CUSTOMERS SHOULD ENSURE THAT THEY TAKE APPROPRIATE ACTION SO THAT THEIR USE OF OUR PRODUCTS DOES NOT INFRINGE UPON ANY PATENTS. IT IS THE POLICY OF CHIPS AND TECHNOLOGIES, INC. TO RESPECT THE VALID PATENT RIGHTS OF THIRD PARTIES AND NOT TO INFRINGE UPON OR ASSIST OTHERS TO INFRINGE UPON SUCH RIGHTS. .

# Contents

| 1. | 82C321 | (CPU/Bus Controller)           | . 1 |

|----|--------|--------------------------------|-----|

| 2. | 82C322 | (DRAM Controller)              | 55  |

| 3. | 82C325 | (Data Buffers)                 | 110 |

| 4. | 82C223 | (DMA Controller)               | 146 |

| 5. | 82C226 | (System Peripheral Controller) | 169 |

# 82C321, 82C322, 82C325, 82C223, 82C226, 82C607, 82C451/452 CHIPS/280: Complete IBM PS/2 TM Model 70/80 Compatible CHIPSetTM

- 100% functionally compatible to IBM PS/2<sup>TM</sup> Models 70/80

- Supports 16, 20, and 25 MHz compatible PS/2<sup>TM</sup> Models 70/80

- High performance Matched Memory Interface for Micro Channel Memory Adapters at 16, 20 and 25 MHz

- Advanced Page Interleaved Memory Controller with integrated Bad Block Remapping Capability

- Near zero wait states (average 0.5 0.7 wait states)

#### Memory on Local Data Bus

120 ns DRAMs at 16 MHz 100 ns DRAMs at 20 MHz 80 ns DRAMs at 25 MHz

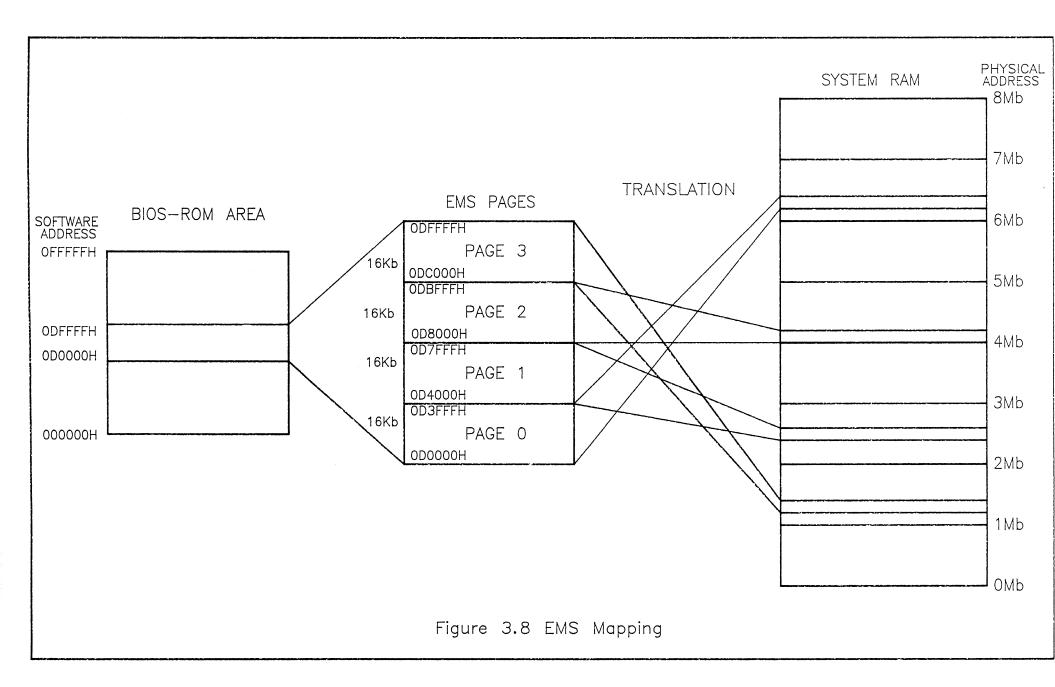

- Integrated Lotus-Intel-Microsoft Memory Specification (LIM EMS 3.2) Memory Controller with 4 register sets, expandable to full LIM EMS 4.0 specification with 8 register sets of 64 mapping registers using the 82C631 EMS mapper chip.

- Supports IBM Matched Memory Cycle and CHIPS Fast Micro Channel Matched Memory Cycle.

- High performance, Fast VGA interface to the 82C451 and 82C452 VGA controllers.

- Asynchronous CPU and DMA state machines.

- PS/2<sup>TM</sup> Model 70/80 compatible Address Recovery logic.

- Low power, high speed CMOS technology.

CHIPS/280 is a 7-device, enhanced CMOS implementation of most of the system logic necessary to implement personal computers compatible to IBM PS/2<sup>TM</sup> Model 70/80. CHIPS/280 enables OEMs to offer compatible PS/2<sup>TM</sup> models 70/80, that are more integrated and superior in performance than IBM's Model 70/80.

CHIPS/280 includes the CS8238 System Logic CHIPSet<sup>TM</sup>, the 82C607 Multi-Function Controller with Analog Data Separator and 16550 compatible serial port, and the Enhanced Gate-Level Compatible 82C451/452 VGA chip as indicated in Figures 1a and 1b. With these 7 VLSI devices, it requires only 59 additional components plus memory to implement compatible PS/2<sup>TM</sup> Models 70/80 superior to IBM's models.

#### SYSTEM LOGIC CS8238 CHIPSETTM

The CS8238 System Logic CHIPSet<sup>TM</sup> consists of the following devices:

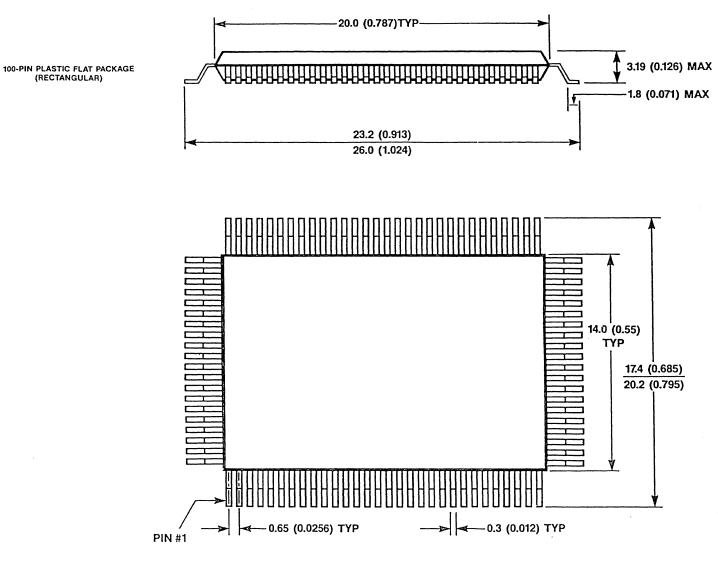

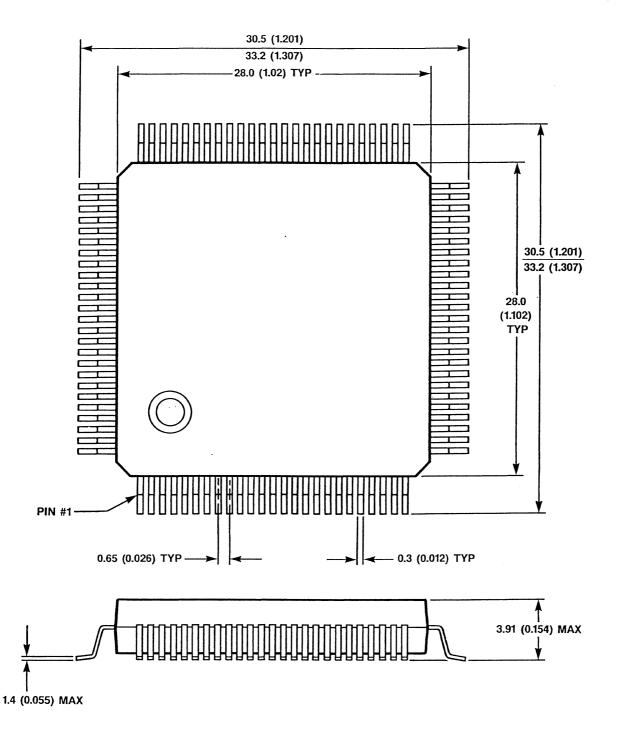

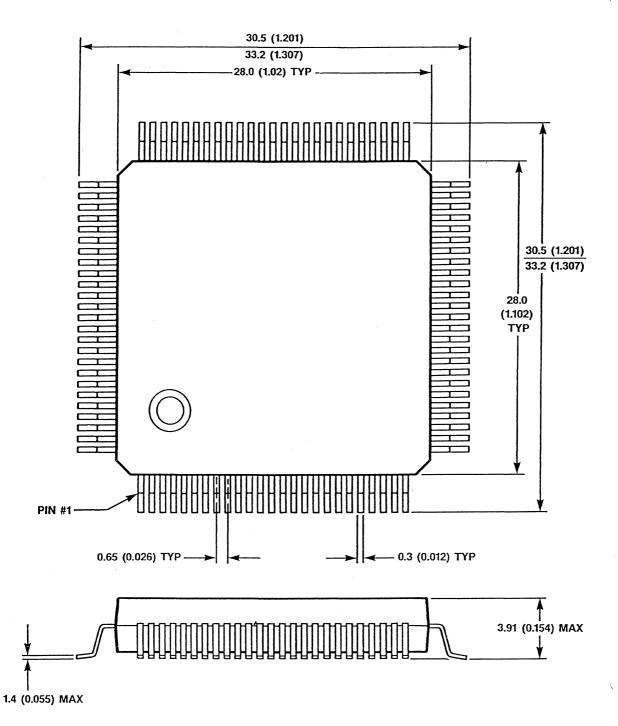

| Device | Function                                   | Number of Pins     |

|--------|--------------------------------------------|--------------------|

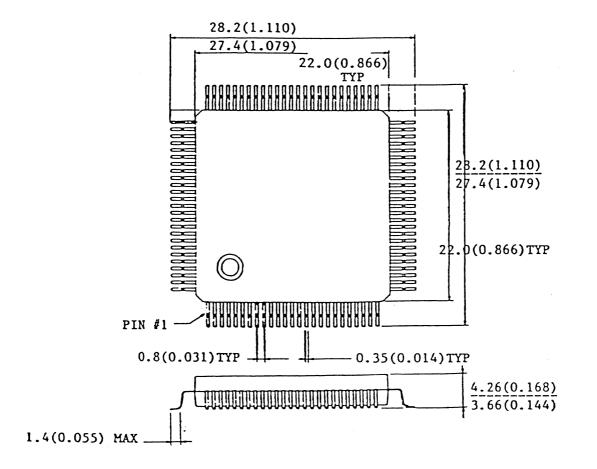

| 82C321 | CPU/Micro Channel Adapter (MCA) Controller | 100 PFP            |

| 82C322 | Page/Interleaved Memory Controller         | 144 PFP            |

| 82C325 | Data Buffer                                | 144 PFP            |

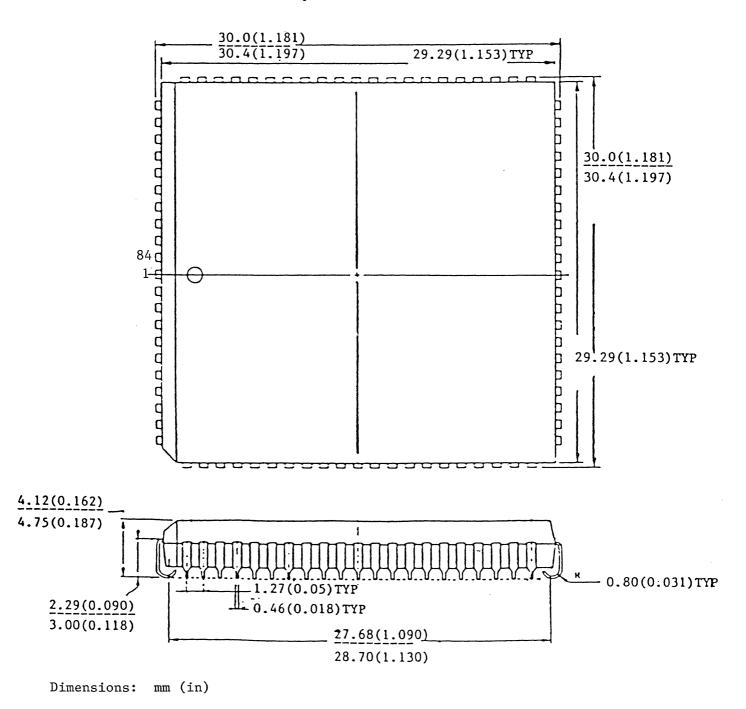

| 82C223 | DMA Controller                             | 84 PLCC or 100 PFP |

| 82C226 | System Peripherals Controller              | 84 PLCC or 100 PFP |

#### 82C321 CPU and MCA Controller

The 82C321 CPU and MCA Compatible Controller manages the system timing for the asynchronous 80386 CPU, DMA and MCA cycles. It supports CPU clock speeds 16, 20 and 25 MHz. It supports all Micro Channel Architecture (MCA) compatible cycles including CHIP's proprietary Fast VGA cycle. It includes the state machines for command and control logic signal generation, DMA and refresh logic control. The 82C321 also supports a CHIPS Fast MCA Matched Memory Cycle which can improve accesses to the memory on the MCA channel by up to 33%.

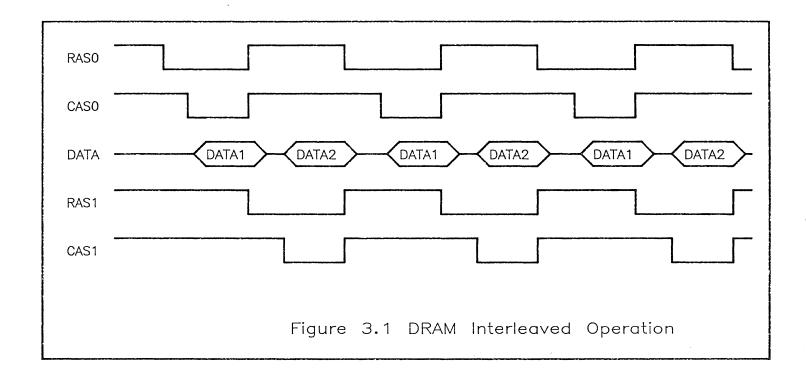

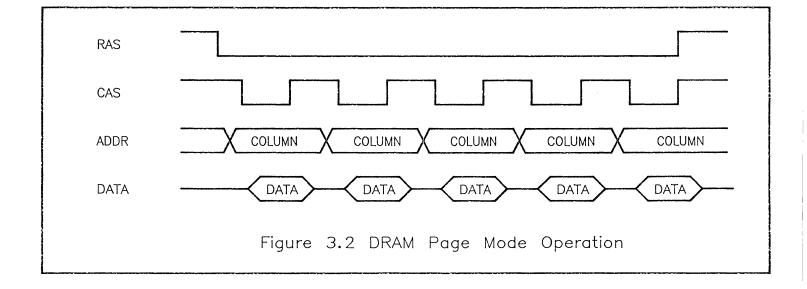

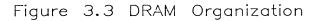

#### 82C322 Page/Interleaved Memory Controller

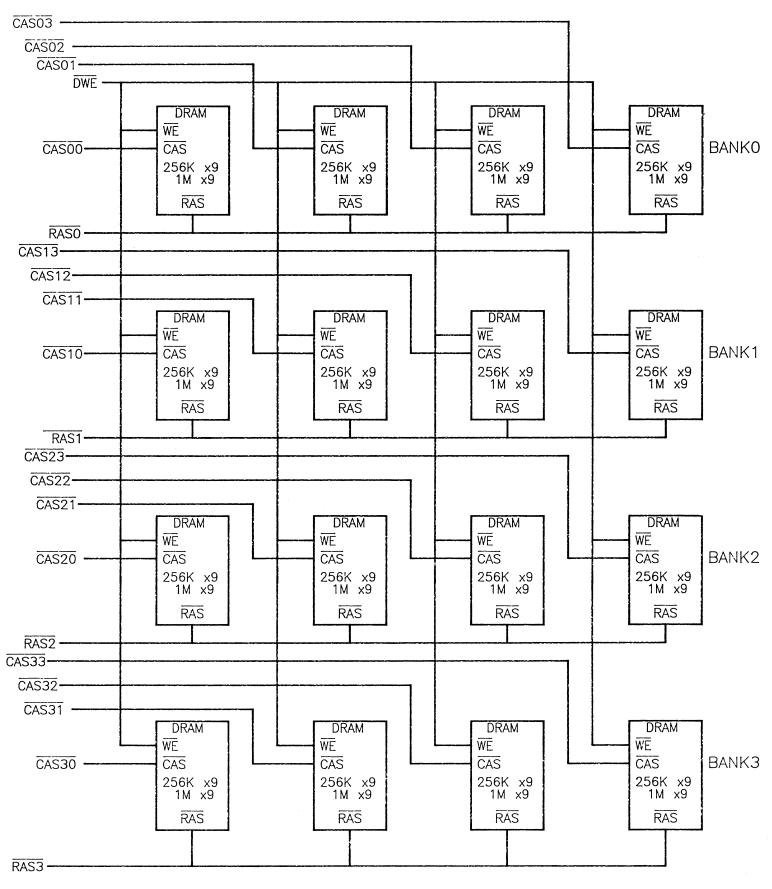

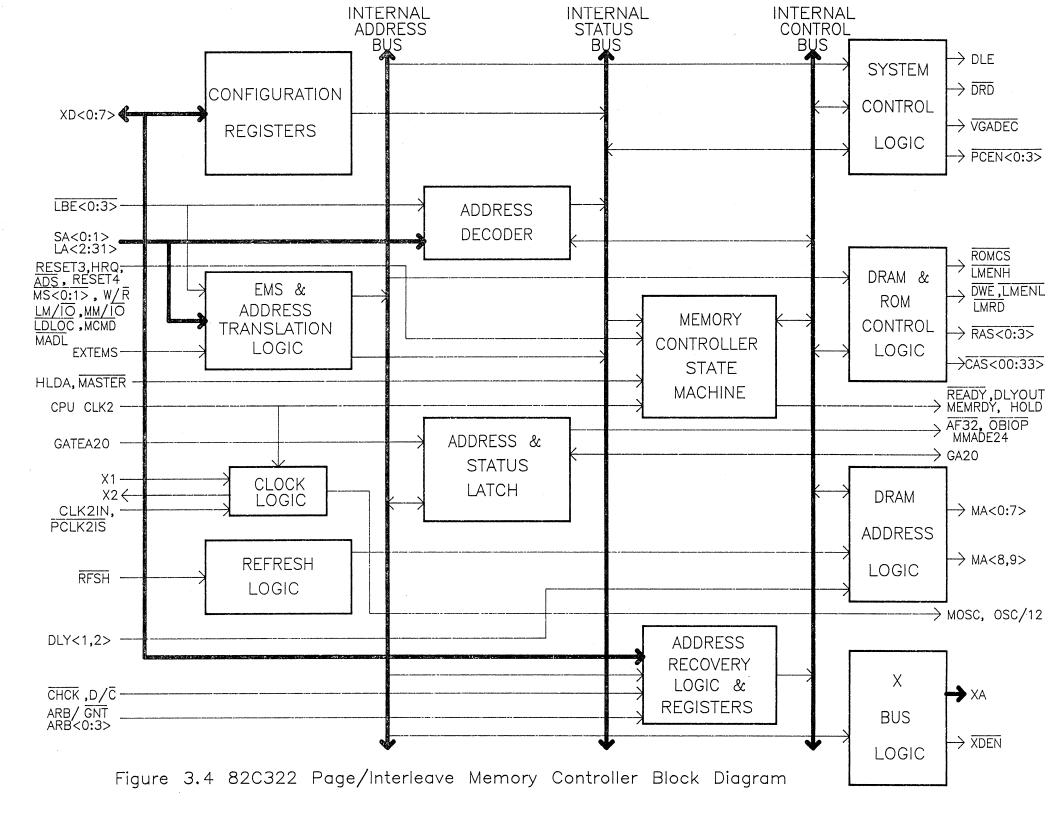

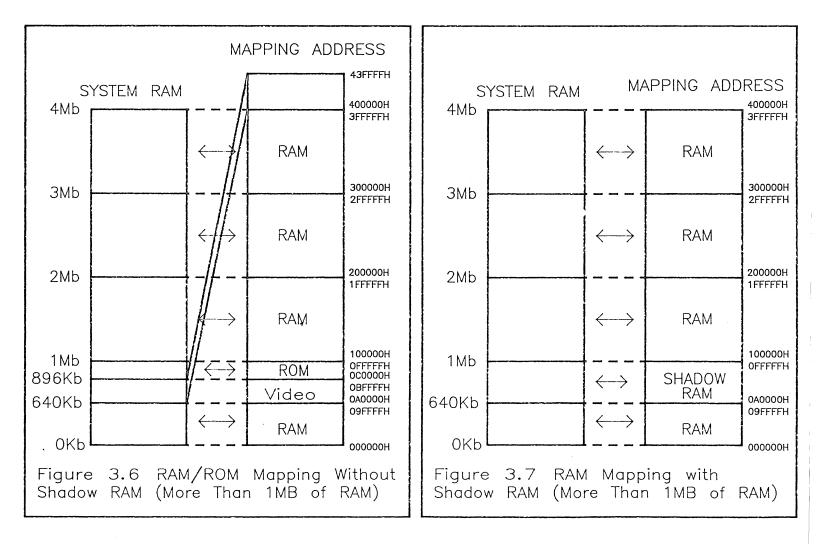

The 82C322 Page/Interleaved Memory Controller provides an interleaved memory sub-system design with page mode operation. It supports 4 memory banks, with memory configuration ranging from 1MB to 16 MB. While operating in the DOS environment, the memory above 1 MB can be utilized as EMS memory, significantly improving the value of large memory configuration requirements of the OS/2 era. The on-chip EMS logic provides 4 mapping registers. However, with external EMS mapper chip, the full LIM EMS 4.0 specification of 8 register sets of 64 mapping registers can be realized. It interfaces to either static column or page mode DRAMs. The 82C322 supports shadowing of the EPROM into RAM space, allowing faster execution of code. The 82C322 integrates the on-board I/O decode logic and IBM compatible address recovery logic.

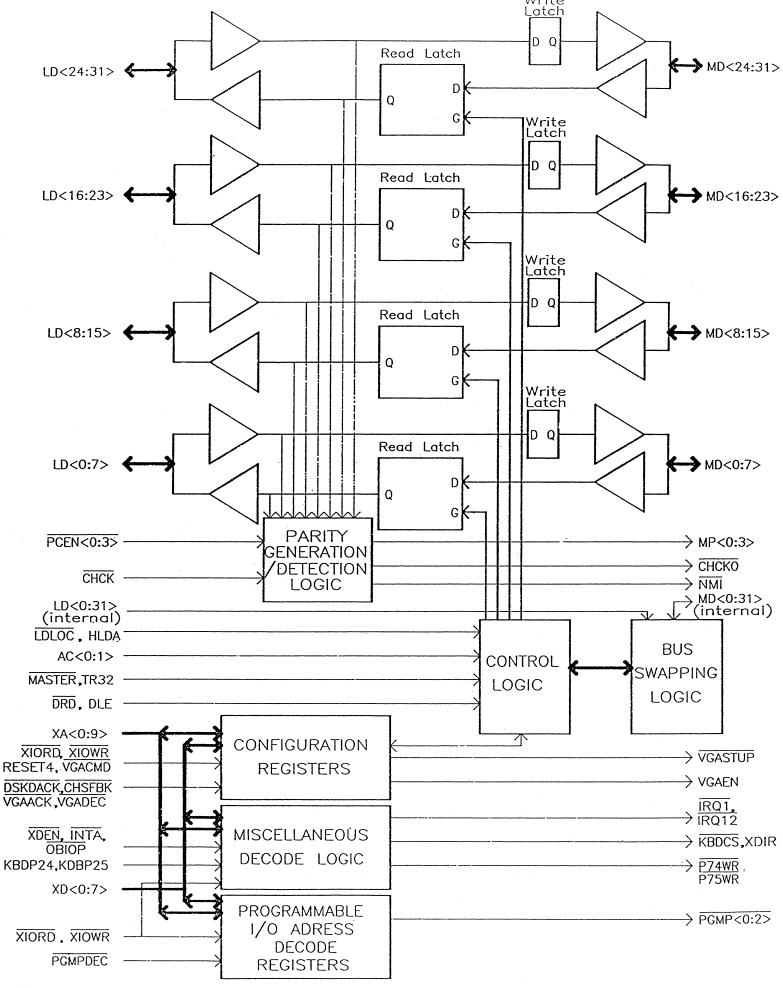

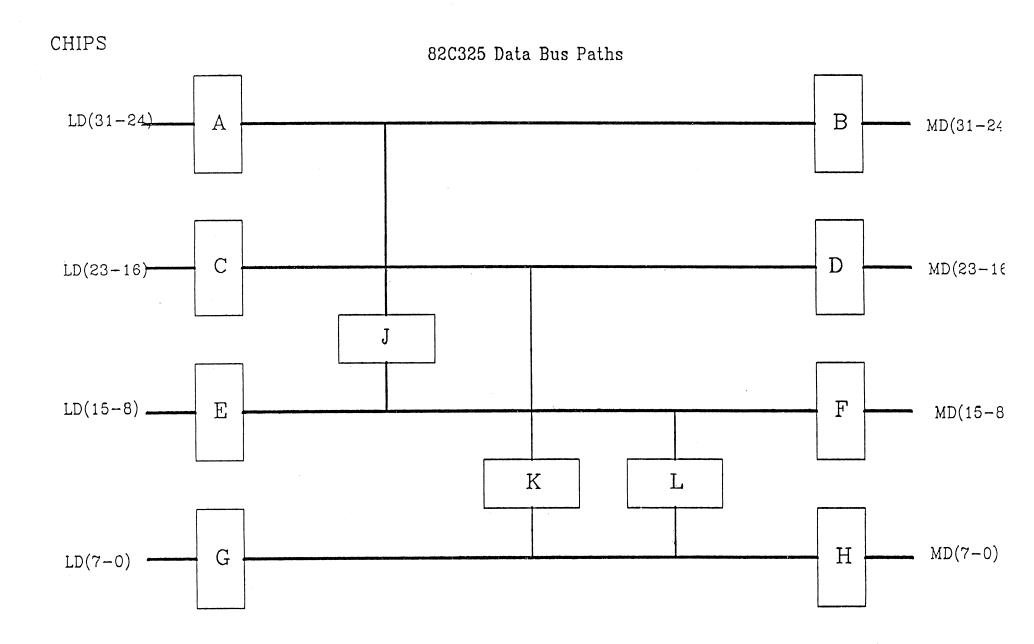

#### 82C325 Data Buffer

The 82C325 Data Buffer provides electrical isolation between the Memory Data Bus and the Local Data Bus. Additionally, it performs the latching and bus steering function. The Data Buffer also provides the programmable I/O decode registers for user I/O decoding requirements. It contains the system POS registers, NMI logic, as well as DRAM parity generation and detection logic. 82C607 decode signals, 82C451/82C452 VGA setup and enable signals are also contained in the 82C325.

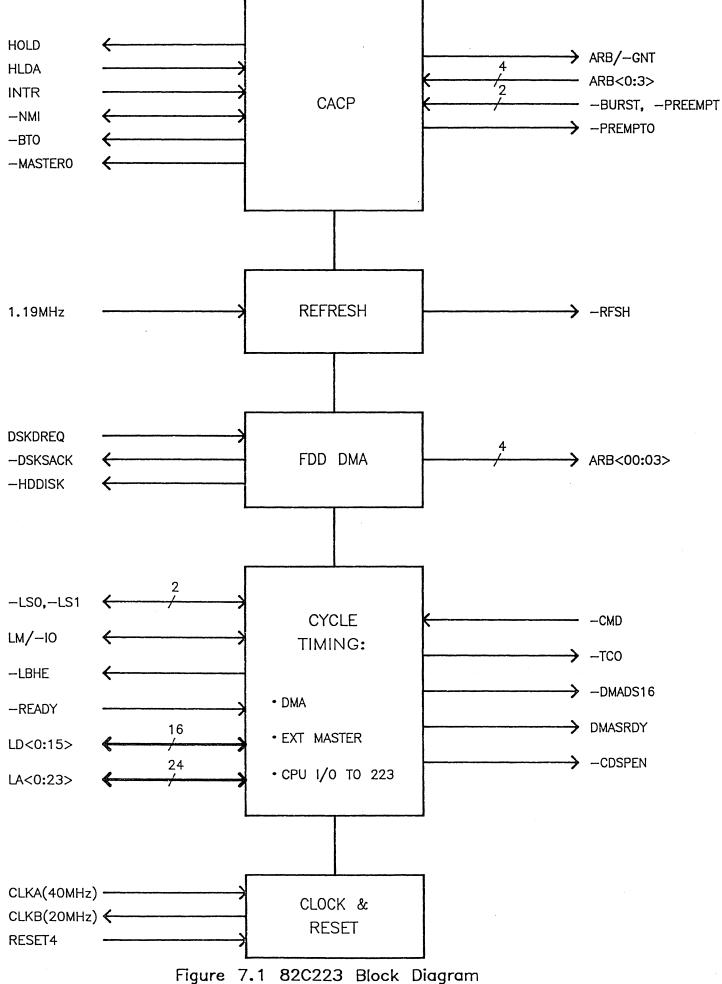

#### 83C223 DMA Controller

The 82C223 DMA Controller provides 8 DMA channels for slave devices and the Central Arbitration Control Point (CACP) for the entire system. Each DMA Channel has 24-bit addressing capability and can perform 8-bit or 16-bit transfers. It also supports Virtual DMA, wherein DMA channels 0 and 4 can be used to service multiple DMA slaves by multiplexing the DMA channels between the arbitration levels assigned to those slaves. It supports multiple Bus Masters via the CACP arbitrator and control logic. The Bus Arbitration logic includes protection against error conditions like burst mode devices not relinquishing the bus within specified time.

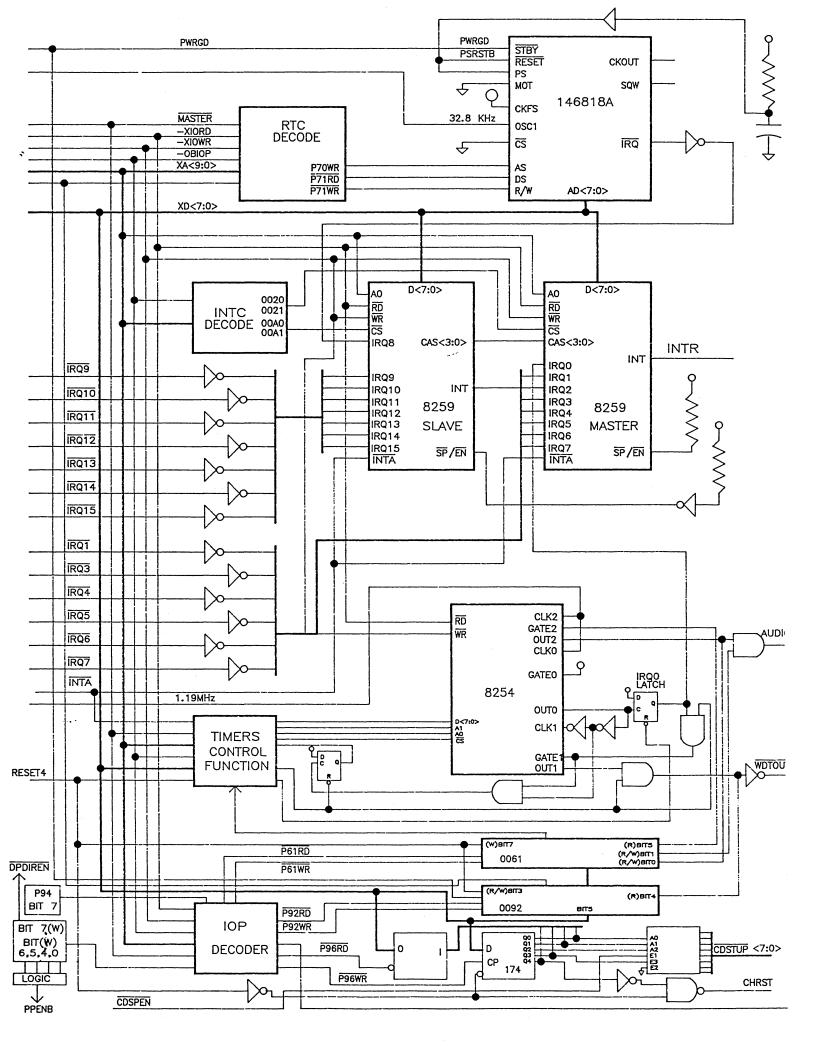

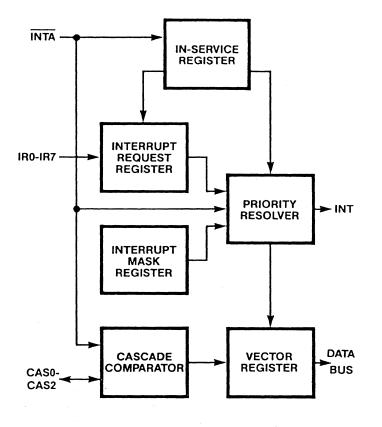

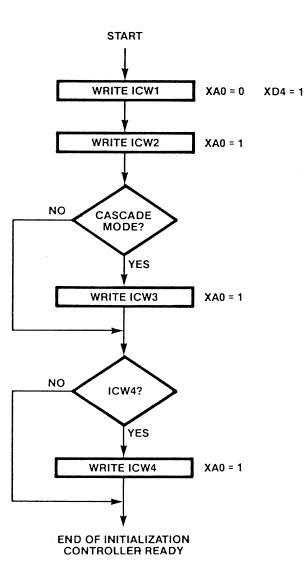

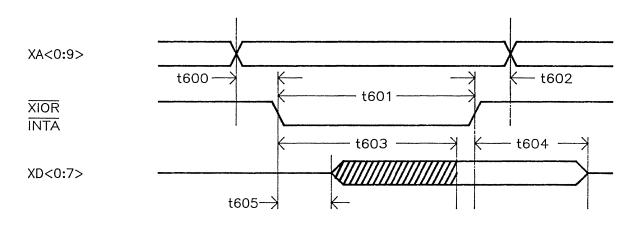

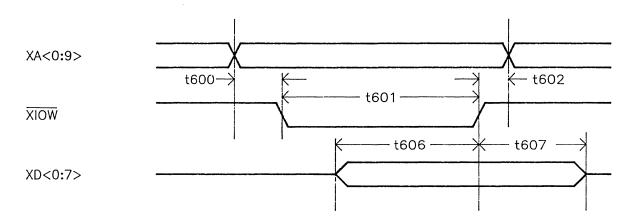

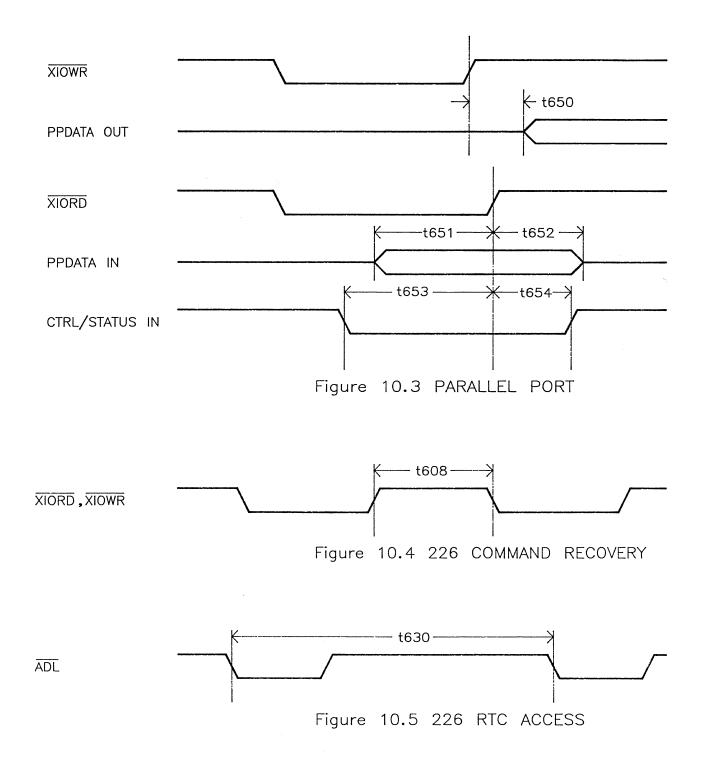

#### 82C226 System Peripherals Controller

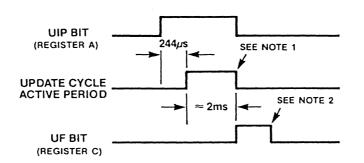

The 82C226 System Peripherals Controller integrates PS/2TM Compatible peripherals in one compact package with an optimized bus interface to the Peripheral Bus. It includes two 8259 Programmable Interrupt Controllers, one 8254 compatible timer, two 146818 compatible real-time clocks, 114 bytes of CMOS battery back-up SRAM and one PS/2TM compatible bi-directional Parallel Port.

#### GRAPHICS

The 82C451 Gate Level compatible VGA provides 100% VGA compatible graphics with backward compatibility to EGA, CGA, MDA and Hercules. In VGA graphics modes, it provides resolutions from 320 x 480 with 16 colors. In VGA text mode, it supports fonts up to 9 x 32. It supports all standard monitors - IBM PS/2TM analog, Multi frequency, EGA, CGA and digital Monochrome. The 82C451 boosts graphics performance with a tightly coupled high performance interface to the CPU and a 16-bit memory interface. The 82C451 is packaged in 144 pin PFP package.

#### PERIPHERAL SUPPORT

The 82C607 Multi-Function Controller integrates PS/2TM compatible peripherals in one compact package. It includes one 16550 Compatible UART, an Analog Data Separator, POS Registers and Glue logic for a NEC 765A Floppy Disk Controller. The 82C607 is available in 68 pin PLCC package.

#### SYSTEM OVERVIEW

CHIPS/280 is designed to maximize the performance of the 80386 microprocessor by coupling it to a high performance page/interleaved memory sub-system. The maximum page size supported by the CHIPS/280 architecture is 16 KBytes when 1 Mbyte DRAMs are used (16 MB of onboard Memory) and the four way interleaved mode of operation is selected. When executing within a page, the DRAM memory sub-system can execute at the same speed as the processor. To the 386, the memory sub-system appears as a 16 KByte direct mapped cache, using relatively inexpensive DRAMs. When operating at 16, 20 or 25 MHZ, the average waitstate incurred is less than 0.7. Additionally, by using Shadow RAM techniques, the BIOS code can also be executed with near zero wait states.

In addition to the high performance memory interface, CHIPS/280 supports a fast Matched Memory Cycle reducing the access time from 200 ns to 120 ns at 25 MHz. CHIPS proprietary Fast VGA cycle allows VGA I/O accesses to be performed within 187.5 ns @ 16 MHz, 150 ns @ 20 MHz, and 120 ns @ 25 MHz.

Regardless of the CPU speed, the DMA controller operates at 10 MHz. Once the DMA and the peripherals are tuned, for example, with a 1:1 interleaving on the Hard Disk, CHIPS/280 continues to deliver dependable high performance.

#### ARCHITECTURE

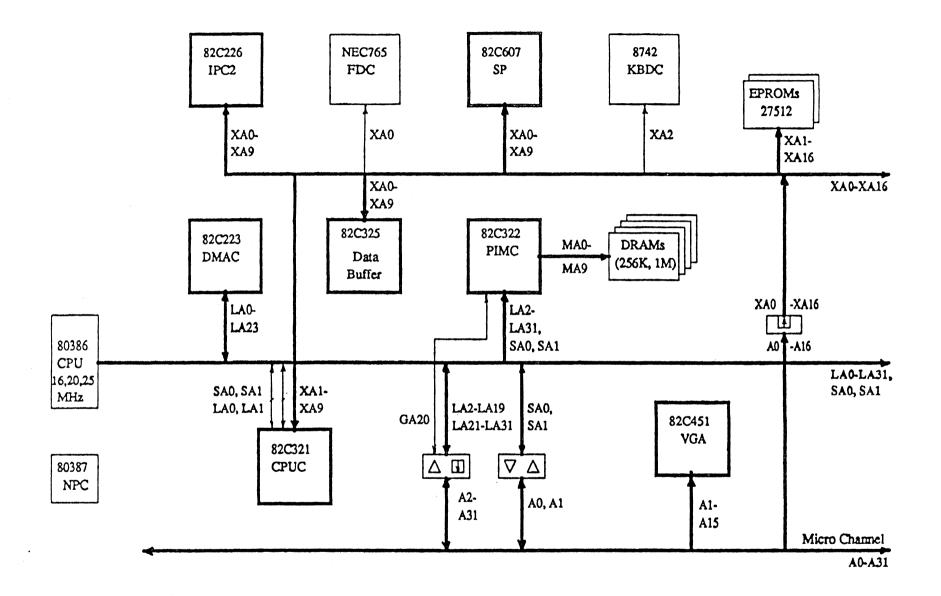

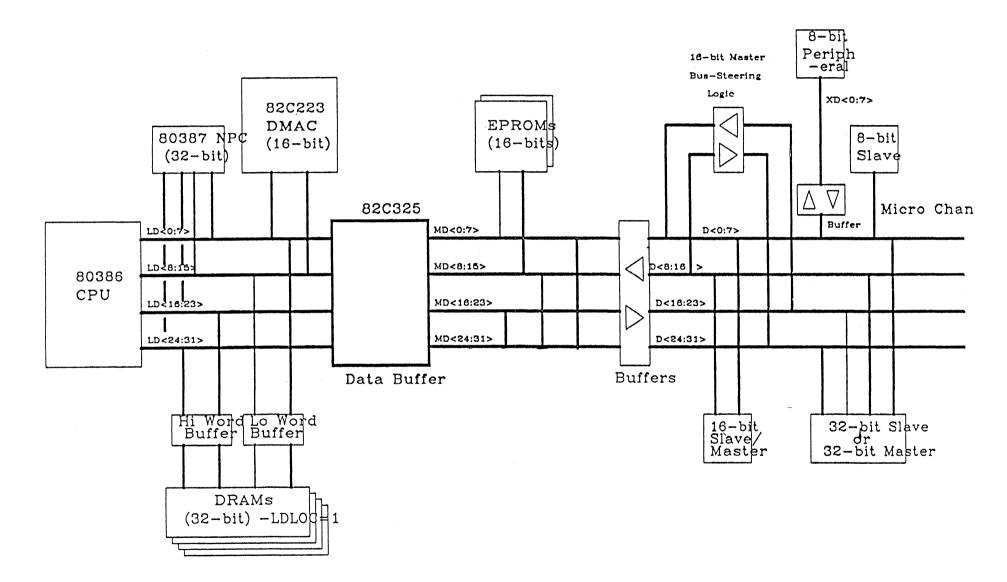

Figures 1-1 and 1-2 illustrates the Address and Data Bus Architecture.

## **CHIPS/280 ADDRESS PATHS**

Figure 1-1

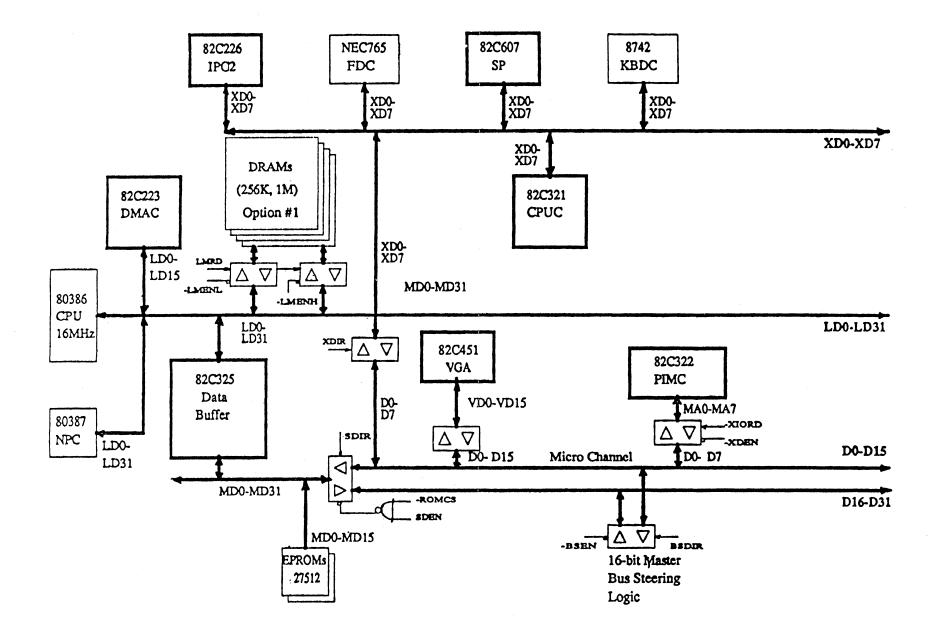

**CHIPS/280 DATA PATHS**

Figure 1-2

#### ADDRESS BUS ARCHITECTURE

The CHIPS/280 supports the following address busses:

- Local Address Bus (LA BUS)

- Memory Address Bus (MA BUS)

- MCA Address Bus (A BUS)

- Peripheral Address BUS (XA BUS)

#### Local Address Bus (LA <31:0>)

The 80386, the 82C322 Page/Interleaved Memory Controller, and the 82C223 DMA controller share the Local Address Bus. The Local Address Bus is buffered to generate the MCA Address Bus. The buffer used is bi-directional and the direction of the address bus is determined by the polarity of the -MASTER input from the MCA channel.

#### Memory Address Bus (MA <9:0>)

The lower addresses of the memory address bus (MA <0.7>) are bi-directional. During accesses to the internal configuration registers, these pins are used to program the 82C322. During memory accesses, (MA <0.9>) address outputs contain row and column address information. The memory address lines are derived from the bus master currently in charge, and could be either the CPU, DMA or an external Bus Master that has gained control of the bus.

#### MCA Address Bus (A<31:0>)

The MCA Address Bus is bi-directional. These are outputs to MCA compatible adapters, when either the CPU or the DMA controller is the bus master. These address lines are driven by the external Bus Masters when they are in control.

#### XA Address Bus (XA<16:0>)

The XA Address bus is derived from the MCA Address Bus. The address information is latched by the leading edge of -VGACMD. XA<0:15> are derived by latching A<0:15> address lines. XA16 is driven by the 82C322 Page/Interleaved Memory Controller.

#### **DATA BUS ARCHITECTURE**

The CHIPS/280 supports the following data busses:

- Local Data Bus (LD BUS)

- Memory Data Bus (MD BUS)

- MCA Data Bus (D BUS)

- Peripheral Data Bus (XD BUS)

#### Local Data Bus (LD <31:0>)

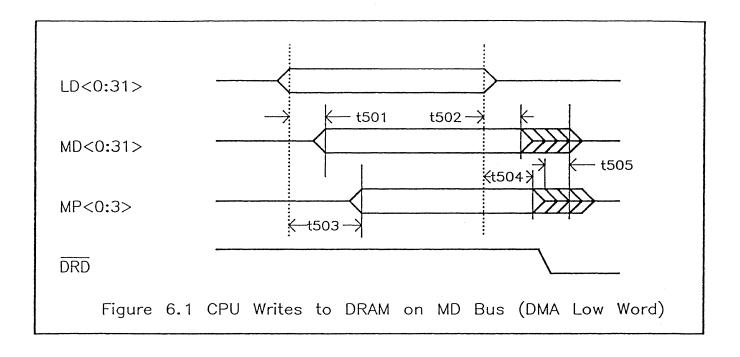

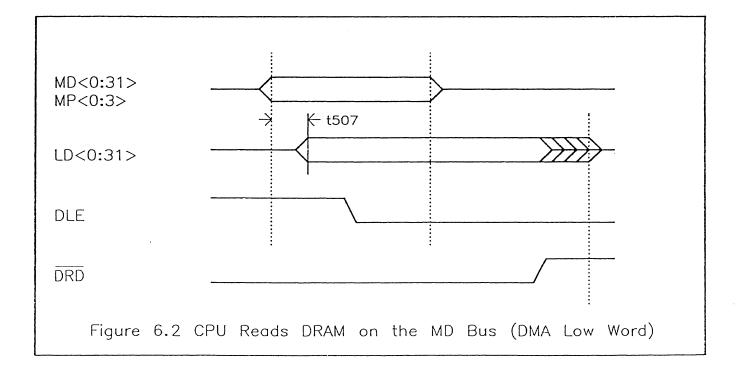

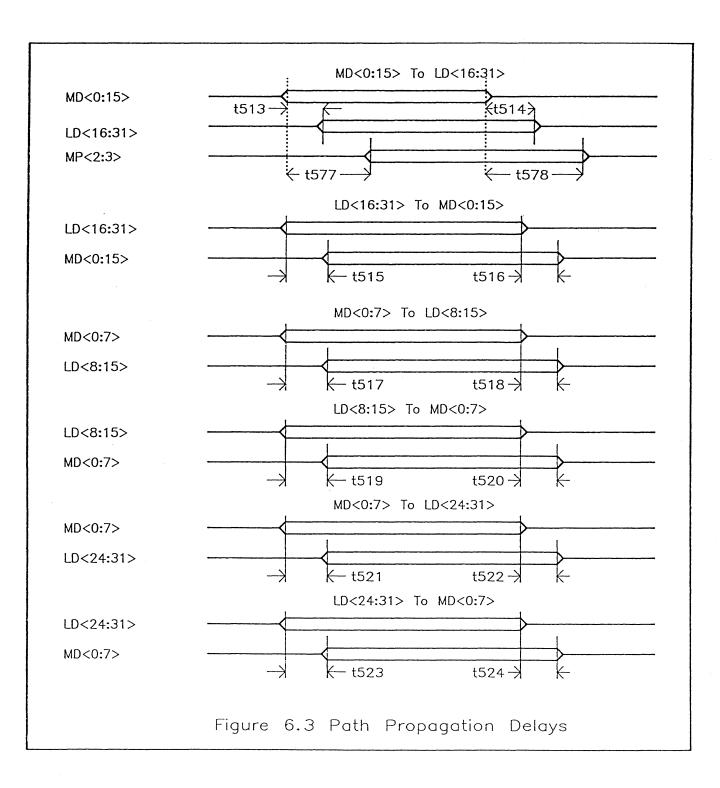

The Local Data Bus (LD BUS) is shared by the 80386, the 80387, the 82C322(Memory controller) and the 82C223 (DMA Controller). The 80386 BS16# input is strapped high to enable 32-bit accesses. The DMA controller is the only 16 bit device on the local data bus (LD BUS). When accessing the DMA controller, the 82C325 steers the processor data bus information appropriately to the DMA controller. The parity bits (MP <0:3>) are generated by 82C325.

#### Memory Data Bus (MD<31:0>)

The Memory Data Bus (MD BUS) is driven by the 82C325 Data Buffer. The MD BUS sources the BIOS EPROMS.

#### MCA Data Bus (D<31:0>)

The MD BUS is buffered by transceivers to generate the MCA Data Bus (D BUS), the direction of which is controlled by SDIR generated by 82C321. These buffers are always enabled (except for ROM accesses) for accessing on-board resources or MCA accesses. The D Bus is used to communicate with the MCA adapters. The D Bus should be tri-stated to prevent MCA adapter cards from accessing BIOS EPROMs.

#### Peripheral Data Bus (XD <7:0>)

The Peripheral data Bus (XD BUS) is derived from the MCA Data Bus by bi-directional buffers. The Peripheral Data Bus is 8-bits wide (XD<0:7>) in a CHIPS/280 implementation. The XD BUS provides communications to the internal registers of the CHIPS/280 CHIPsetTM, as well as other on-board peripherals such as the Floppy Disk Controller, Key Board Controller, etc.

The XDIR out of the 82C325 controls the direction of the XD BUS transceivers. XDIR is activated only when the -XDEN signal from the 82C322 Page/Interleaved Memory Controller is in-active. When accessing the internal configuration registers of the 83C322, XDEN is active and XDIR is inactive. The data transfer direction is from the D Bus to XD Bus preventing data bus contention.

#### **Miscellaneous Ports and POS Registers**

The CHIPS/280 POS (Programmable Option Select) registers and I/O ports 61, 70, 91, 94, and 3C3 are provided. These ports are distributed in among the CHIPset<sup>TM</sup>, as a result more than one chip may respond for a single port access.

#### INDEX REGISTERS

CHIPS/280 CHIPSetTM has several additional registers required for programming the various modes of operation that are available. An indexing scheme is used to reduce the I/O ports required for all the registers of the CHIPSetTM. Port 22H is used as an Indexing register and Port 23H is used as the Data register. The index value is placed in port 22H and the data to be written to or read from the indexed register is placed in port 23H. Every access to port 23H must be preceded by a write of the index value to port 22H, even if the same register data is accessed again. All reserved bits are set to zero by default and when written to, must be set to zero. Only the registers used in the 82C321, 82C322, and 82C325 are discussed, since the other registers are described in the 82C226, 82C607,8042, 82C223 and 82C451 documentation. Registers R22-R29 are accessed directly (instead of through index registers). Table 1 lists these registers:

| Reg # | Register Name                   | Index | Location |

|-------|---------------------------------|-------|----------|

| R0    | Version Register                | 8DH   | 82C321   |

| R1    | System Speed Select             | 8EH   | 82C321   |

| R2    | System Option Register          | 8FH   | 82C321   |

| R3    | Version and Memory Enable       | B4    | 82C322   |

| R4    | ROM Configuration               | B5H   | 82C322   |

| R5    | Memory Enable Register 1        | B6H   | 82C322   |

| R6    | Memory Enable Register 2        | B7H   | 82C322   |

| R7    | Reserved Register               | B8H   | 82C322   |

| R8    | Memory Type                     | B9H   | 82C322   |

| R9    | Operating Mode                  | BAH   | 82C322   |

| R10   | Timing Control                  | BBH   | 82C322   |

| R11   | EMS Base Address                | BCH   | 82C322   |

| R12   | EMS Address Extension 1         | BDH   | 82C322   |

| R13   | EMS Address Extension 2         | BEH   | 82C322   |

| R14   | EMS Range Address Register      | BFH   | 82C322   |

| R15   | Faulty DRAM Address Extension 1 | СОН   | 82C322   |

| R16   | Faulty DRAM Address Extension 2 | C1H   | 82C322   |

| R17   | Faulty DRAM Base Address 1      | C2H   | 82C322   |

#### Table 1

# Table 1 (continued)

| Reg # | Register Name                  | Index | Location |

|-------|--------------------------------|-------|----------|

| R18   | Faulty DRAM Base Address 2     | СЗН   | 82C322   |

| R19   | Faulty DRAM Base Address 3     | C4H   | 82C322   |

| R20   | Faulty DRAM Base Address 4     | C5H   | 82C322   |

| R21   | Faulty DRAM Relocation Address | C6H   | 82C322   |

| R30   | Miscellaneous Register         | 80H   | 82C325   |

| R31   | Programmable I/O Setup #0      | 81H   | 82C325   |

| R32   | Programmable I/O Decode #0     | 82H   | 82C325   |

| R33   | Programmable I/O Setup #1      | 83H   | 82C325   |

| R34   | Programmable I/O Decode #1     | 84H   | 82C325   |

| R35   | Programmable I/O Setup #2      | 85H   | 82C325   |

| R36   | Programmable I/O Decode #2     | 86H   | 82C325   |

| R37   | Upper System ID Byte           | 87H   | 82C325   |

| Reg # | Register Name                       | Address | Location |

|-------|-------------------------------------|---------|----------|

| R22   | Split Ram Address Register          | EOH     | 82C322   |

| R23   | Split Enable Register               | E1H     | 82C322   |

| R24   | Channel Recovery Register(A30-A24)  | E2H     | 82C322   |

| R25   | Channel Recovery Register(A23-A16)  | E3H     | 82C322   |

| R26   | Channel Recovery Register(A8-A15)   | E4H     | 82C322   |

| R27   | Channel Recovery Register(A2-A7)    | E5H     | 82C322   |

| R28   | Channel Recovery Register(ARB13-10) | E6H     | 82C322   |

| R29   | Channel Recovery Register(D/C)      | E7H     | 82C322   |

#### FEATURES

- Supports 16, 20 and 25 MHz 80386 Processors

- 100% Compatibility with MCA specifications at all CPU speeds

- Programmable wait state option

- Matched Memory Cycle Support

- Fast Matched Memory Cycle Support

- Fast VGA Cycle

- Bus Conversions for 16 and 8-bit devices

- 80387 Interface Logic

#### FUNCTIONS

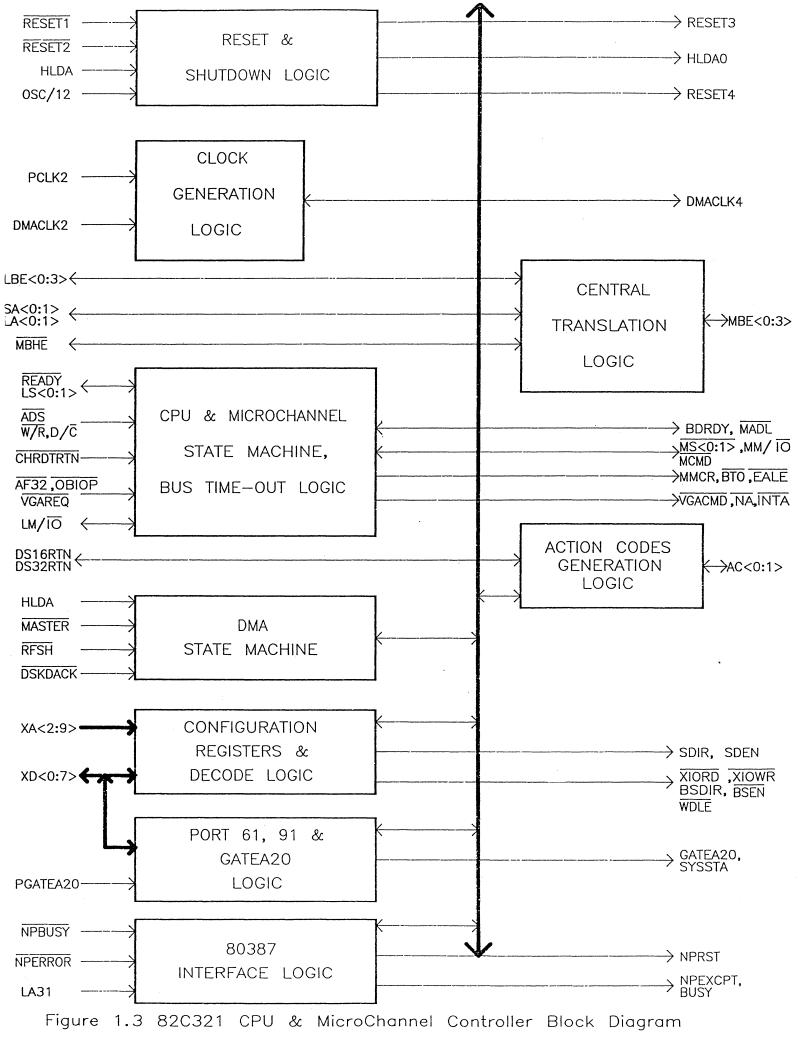

The 82C321 MCA/CPU controller performs the following functions in a CHIPS/280 implementation. Figure 1-3 shows the block diagram of 82C321.

- Reset generation

- Bus Cycle Control providing the following:

- MCA compatible default (I/O and Memory) Cycle (CPU cycle time of 250 ns @ 16 MHz, 250 ns @ 20 MHz, and 240 ns @ 25 MHz).

- \* MCA Compatible Matched memory Cycle (CPU Cycle time of 187.5 ns @ 16 MHz, 250 ns @ 20 MHz, and 240 ns @ 25 MHz)

- \* Fast Matched memory Cycle (CPU Cycle time of 187.5 ns @ 16 MHz, 150 ns @ 20 MHz, and 120 ns @ 25 MHz)

- \* Fast VGA Cycle (CPU cycle time of 187 ns @ 16 MHz, 150 ns @ 20MHz, and 120 ns @ 25 MHz)

- Data bus sizing and steering for CPU, DMA and data bus steering for external bus masters

- MCA bus memory and I/O cycles to 8,16 or 32 bit peripherals

- Waitstate generation logic to provide support for the following:

- \* -Slow MCA compatible adapter cards

- -Slow system board peripherals and index registers.

- 80387 Numeric coprocessor interface logic

- MCA compatible status (S0, S1), Address Decode Latch (-ADL) and Command (-CMD) generation

- GateA20 generation

#### **1.0 RESET GENERATION LOGIC**

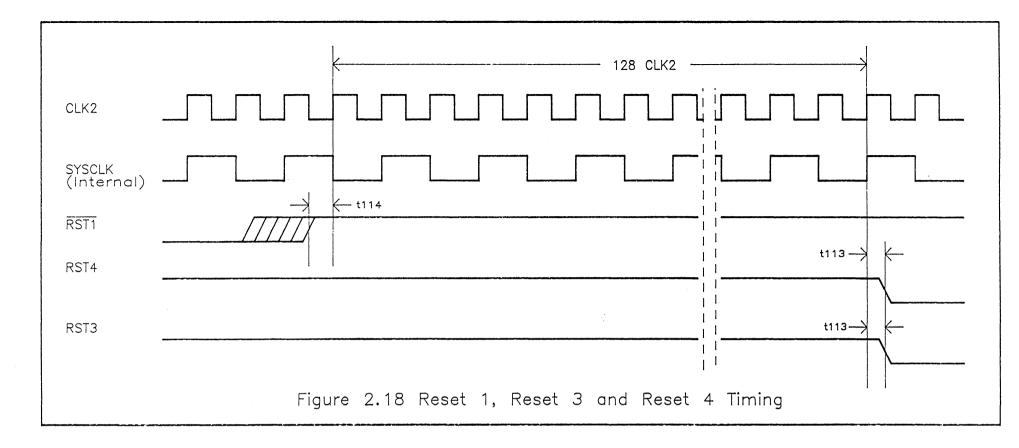

The 82C321 receives two reset inputs: - RESET1 and -RESET2. -RESET1 is the Power Good input from the power supply. When -RESET1 is active, the 82C321 activates RESET3 and RESET4 for a system reset. -RESET2 is generated from the 8042 keyboard controller when a warm reset is required. -RESET2 activates RESET3 to the 80386. RESET3 is also activated by the 82C321 when a CPU shutdown condition is detected. Additionally, setting bit 0 in the System Port A (92H) causes RESET3 to be active, after the I/O command goes inactive. RESET3 is held active for at least 128 PCLK2 cycles following the de-activation of -RESET1.

RESET3 is synchronized with respect to PCLK2 to ensure the proper phase between the CPU/DMA state machine and the internal phase of the 80386 Microprocessor. RESET4 performs the system reset function, resetting the 82C322 Page/Interleaved Memory Controller, the 82C223 DMA Controller, the 82C226 Peripheral Controller and the 8742 (or the 8042) key board controller to their default values. RESET3 and RESET4 are held valid for at least 128 PCLK2 cycles, following the deactivation of -RESET1.

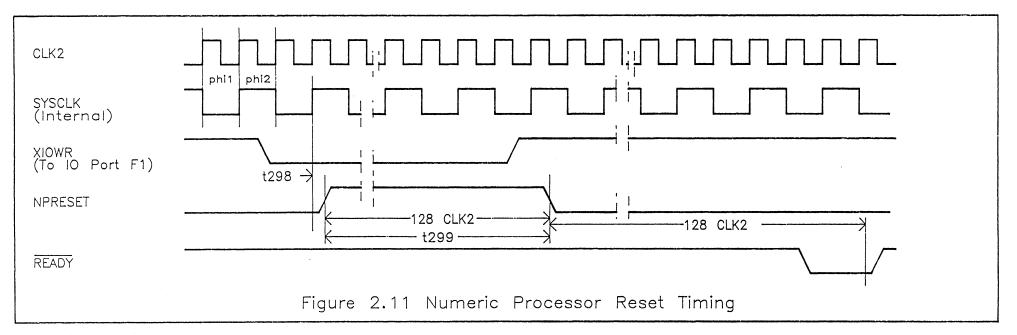

The 82C321 generates the NPRESET output to reset the 80387 Numeric Coprocessor. The NPRESET is activated when RESET3 is activated or when port 0F1H is written to. During accesses to port 0F1, the NPRESET is held high for 128 PCLK2 cycles. NPRESET is then forced low for 128 PCLK2 cycles before -READY is returned to the processor. This ensures that the Numeric Coprocessor Reset High and Low time requirements are satisfied.

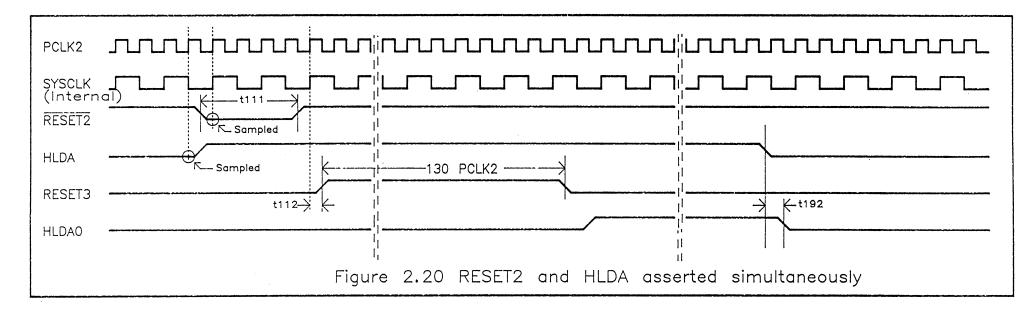

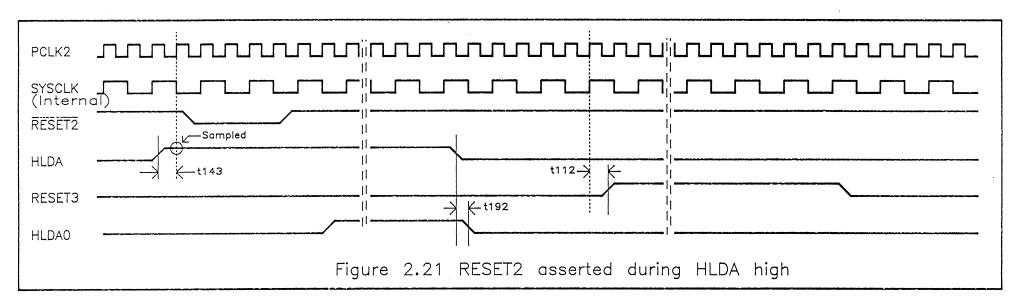

**NOTE:** The 80386 deasserts HLDA when RESET3 goes active. This can end a DMA cycle in progress. The 82C321 generates HLDA0 (which goes to 82C223 DMA controller) to correct this problem. If RESET2 and HLDA occurs simultaneously RESET3 is generated, and HLDA0 is not asserted thus blocking the DMA cycle from starting. When RESET3 is completed, HLDA0 is sent to the 82C223 DMA Controller. If the DMA cycle is already in progress and RESET2 becomes active then RESET3 is not asserted until the DMA cycle is completed. The same applies to port 92 RESET operation.

#### 2.0 CPU/DMA STATE MACHINE

The 82C321 supports two state machines, the CPU State Machine and the DMA State Machine. The control logic automatically selects the proper state machine for the CPU or DMA cycles. No clock switching is involved when transitioning from the CPU to the DMA state machine, eliminating clock synchronization delays.

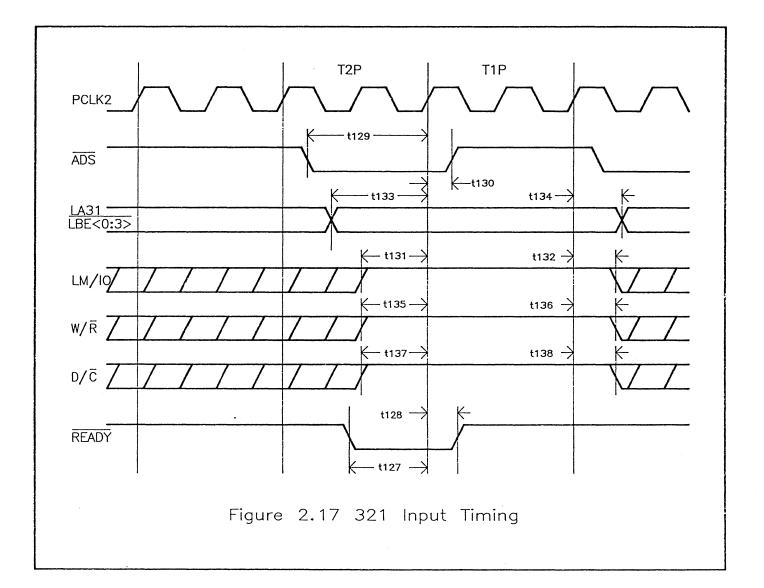

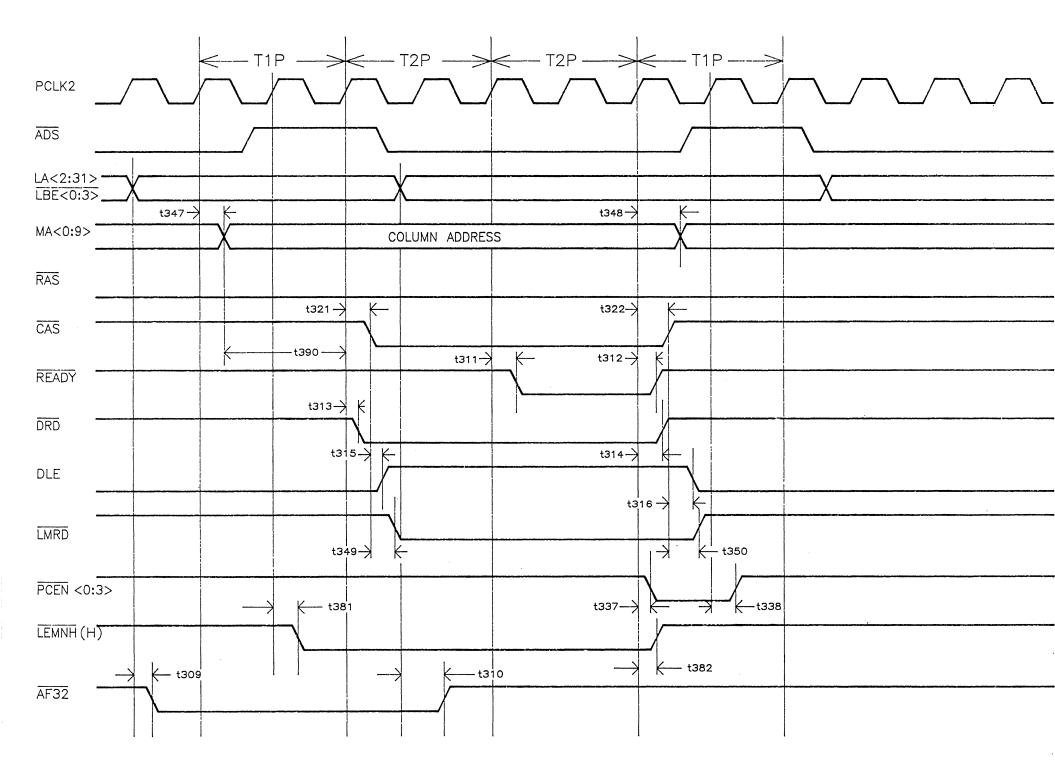

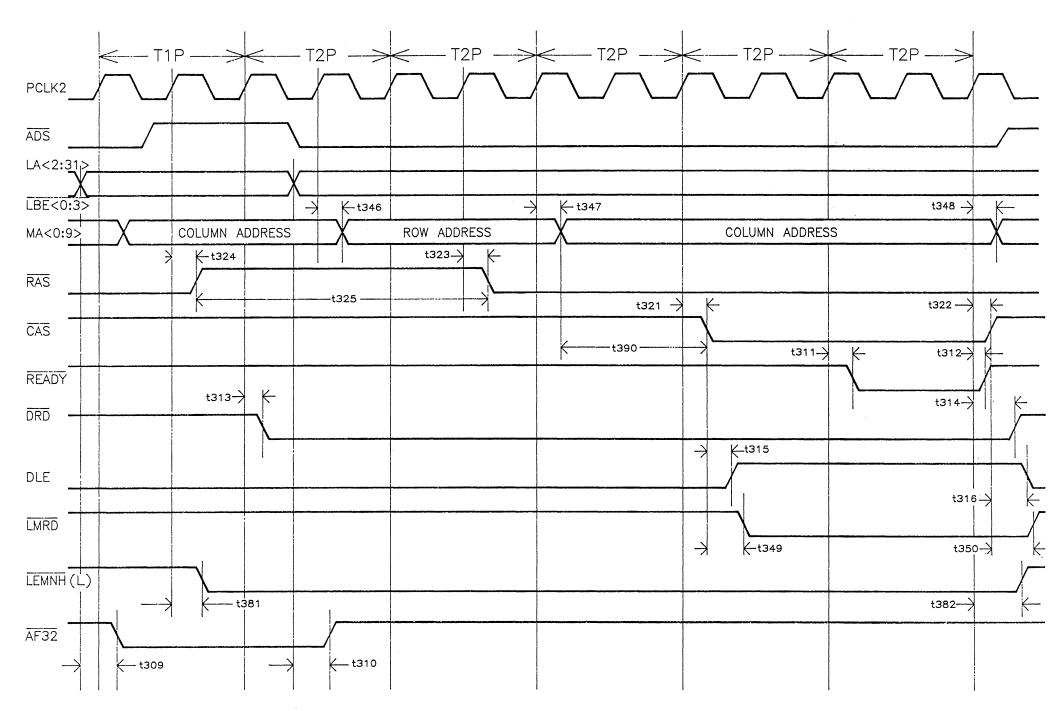

#### 2.1 CPU State Machine

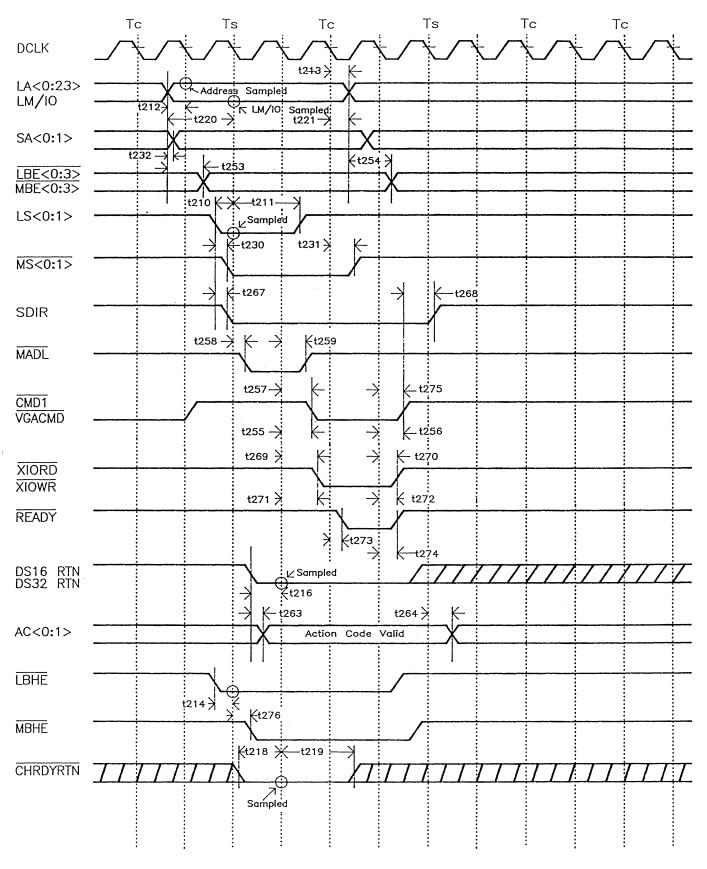

Interface to the 80386 requires interpretation of the 80386 status lines -ADS, M/-IO, D/-C, W/-R during the T1 (non-pipelined) cycle and the synchronization and generation of -READY to the CPU upon the completion of the cycle. The CPU initiates a cycle by driving the -ADS, M/-IO, W/-R and D/-C lines. Upon detecting the start of a new cycle, the 82C321 monitors the -AF32 input to determine if the current access is a local memory cycle or an MCA access. If -AF32 is sampled active, the CPU state machine waits for -READY from the memory controller to terminate the cycle. For all other cycles, (-AF32 inactive), the 82C321 generates the various MCA timing signals including the Matched Memory Cycle, Fast VGA Cycle timing. 82C321 also generates timing signals for Fast Matched Memory cycles. It subsequently generates - READY signal to the CPU to terminate the cycle.

The 82C321 supports 8, 16 and 32-bit transfers between the processor and the MCA I/O or memory adapter cards. The Action Code (AC<1:0>) outputs are used by the 82C325 for bus sizing and conversions.

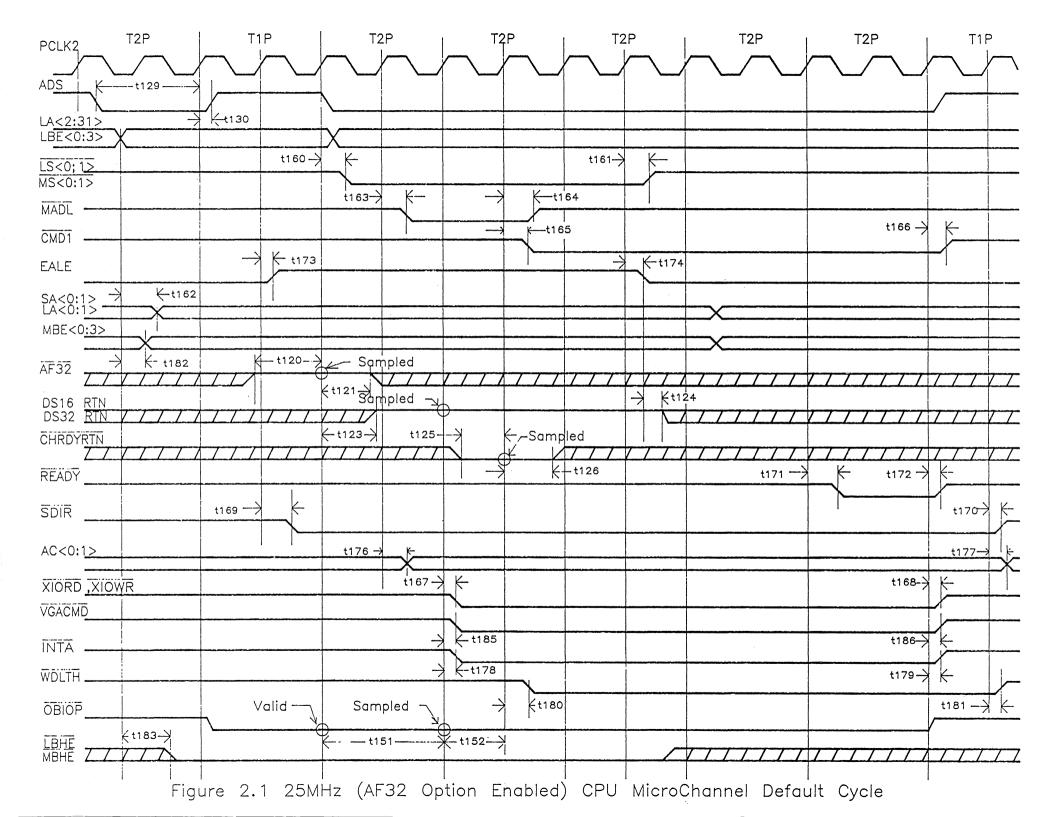

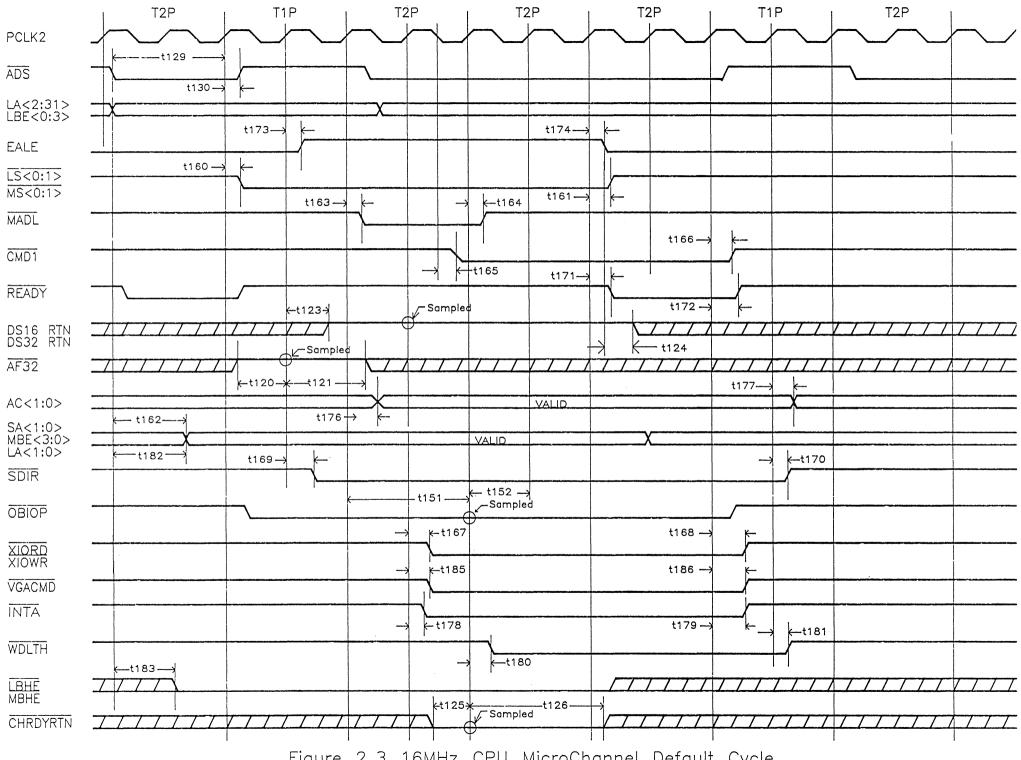

#### 2.2 MCA Default Cycle

At 16 and 20 MHz operation, two CPU wait states are required for generating the default MCA Cycle. At 25 MHz, three wait states are required in pipeline mode. One more additional wait state is required in non pipeline mode. If delayed sampling of -AF32 is enabled @ 20 or 25 MHz, 3 wait states are required @ 20 MHz, and 4 wait states are required @ 25 MHz. There is always the addition of 1 wait state in the non pipeline mode.

The MCA cycle is initiated when -AF32 is sampled inactive. The status lines -S0, -S1 and M/-IO to the MCA are generated by decoding the -ADS, W/-R, M/-IO and D/-C (when CPU is in control). When The DMA controller is in control, the 82C321 buffers the -LS0, -LS1, LM/-IO to generate the -MS0, -MS1 and MM/-IO outputs to the MCA. When external Master is in control, it drives the -MS0, -MS1, MM/IO inputs and 82C321 passes these inputs on to -LS0, -LS1 and LM/-IO signals respectively.

When the CPU is in control LSO, and LS1 are not asserted during interrupt acknowledge or during second and subsequent bus convert cycles.

When the CPU is in control, the latched status information is made available on the MCA. the 82C321 subsequently generates -ADL and -CMD. The signal timings conform to MCA timing specifications.

When the 82C321 is programmed in 25 or 20 Mhz mode and if the CPU is running at 25 or 20 Mhz, the delayed sampling of -AF32 should be enabled to generate timings conforming to MCA specification. This option is enabled by setting bit 6 in Register R1 (index 8E) to 1. This option when activated delays the sampling of -AF32 by one CLK2 period and also inserts one CPU wait state in all MCA cycles. This also results in delaying all MCA signals by one CLK2 period and also increases the -CMD pulse width by one CLK2.

The 82C321 generates EALE for all MCA accesses . EALE is low at the start of the cycle to allow the processor addresses to flow through to the MCA. EALE is driven high to latch the processor addresses. EALE is de-asserted a minimum of 30 ns after the de-assertion of -ADL to conform to MCA specifications (MCA requires a 30 ns address hold time following the removal of -ADL).

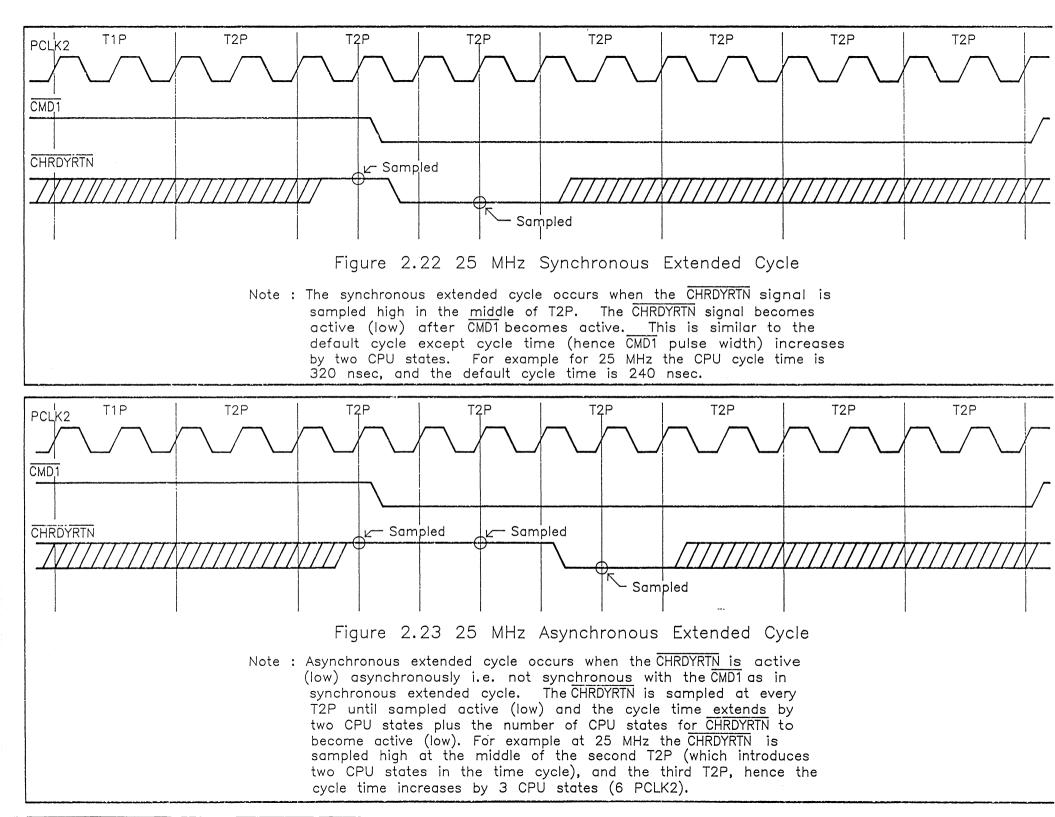

-CHRDYRTN is sampled by the 82C321 to determine if the current cycle can be completed within the default 200 ns timing. If -CHRDYRTN is active, the 82C321 activates -READY at the start of T2 or T2P to terminate the cycle. -CHRDYRTN is a "NANDED" function of all the CDCHRDY <1:8>, DMARDY, MEMRDY and VGARDY signals. If -CHRDYRTN is sampled inactive, then additional wait states are introduced.

DS16RTN and DS32RTN are sampled by the 82C321 to determine the data size of the accessed device. If DS32RTN and DS16RTN are sampled active, then the 82C321 assumes the current access is to a 32-bit device. If DS32RTN is inactive and DS16RTN is active, then the current access is to a 16-bit device. If both DS32RTN and DS16RTN are sampled inactive, then an 8-bit device is assumed. The 82C321 monitors these inputs to generate the corresponding action codes to the 82C325 for bus sizing and conversion. For example, if the current access is a 32-bit access from a CPU to an 8-bit device, the 82C321 generates the appropriate control signals to enable four back to back cycles, before generating -READY to the CPU to terminate the cycle.

The 82C321 receives the On Board I/O Peripheral (-OBIOP) signal, when the I/O address is less than 03FFH. It is used to determine if the current access is to the local devices and the peripheral devices. The 82C321 considers the Timer, Serial Port, Diskette Controller, Interrupt Controller, Real Time Clock, CMOS RAM and Keyboard Controller as Peripheral I/O devices.

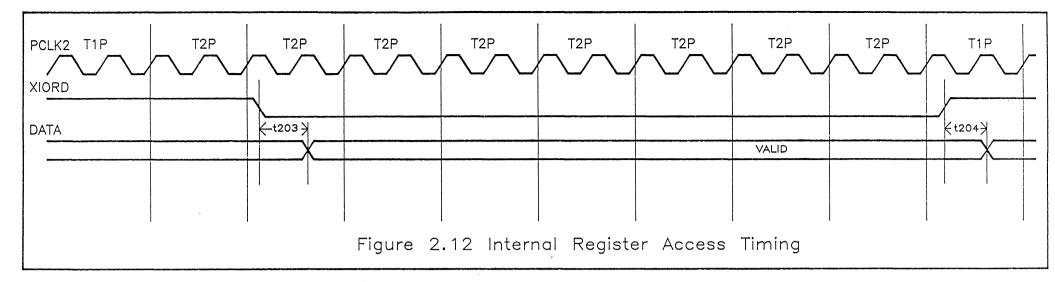

All I/O addresses that are below 03FFH and are not peripheral devices are considered as on board devices. The -OBIOP is active from 0 to 03FFH. The 82C321 generates -XIORD and -XIOWR signals for all I/O accesses, and they are valid for the duration -CMD1 is valid. The CPU cycle time and -CMD1 pulse width for on board I/O and peripherals varies with the frequency of operation and are listed below, where cycle time and pulse width are in nsec and frequency in Mhz.

| ITEMS          |       | ON BOARD DEVICES |     | PERI | AL DEVICES |     |     |

|----------------|-------|------------------|-----|------|------------|-----|-----|

| Frequency      | (MHz) | 16               | 20  | 25   | 16         | 20  | 25  |

| Cycle<br>time  | (ns)  | 437.5            | 400 | 360  | 562.5      | 550 | 520 |

| -CMD<br>pulse  | (ns)  | 312.5            | 275 | 260  | 437.5      | 425 | 420 |

| Wait<br>states |       | 5                | 6   | 7    | 5          | 9   | 11  |

**NOTE:** The above numbers refer to the CPU in the pipeline mode, and when the delayed sampling of -AF32 option is enabled at 20 and 25 MHz.

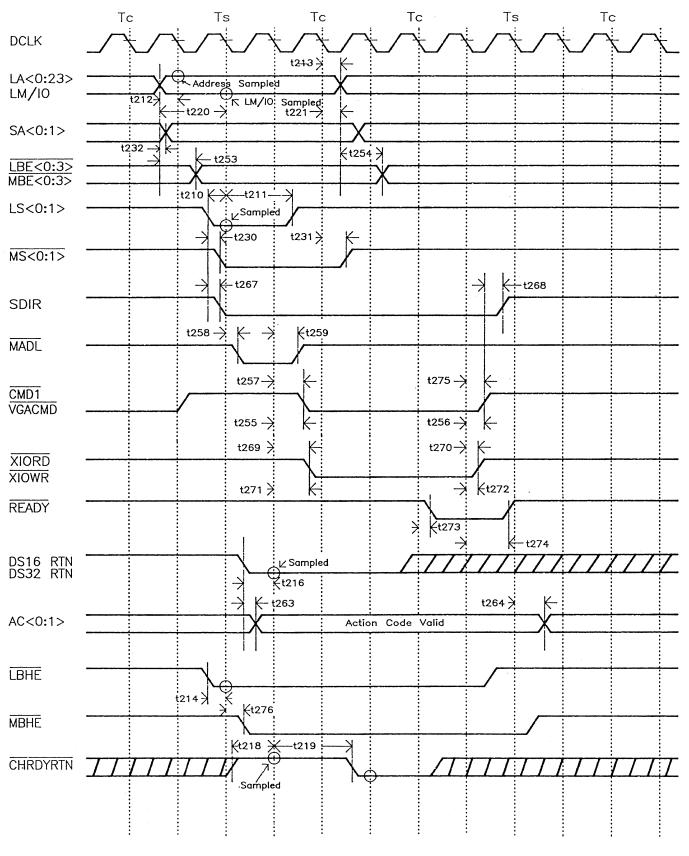

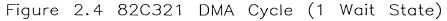

#### 2.3 DMA State Machine

The DMA State machine is driven by the DMACLK2 input from the 82C223 DMA controller. It operates asynchronously to the CPU state machine. The DMA state machine monitors the HLDA and -MASTER inputs to determine if it should generate the control signals for the current access. Control is passed to the DMA state machine when HLDA is active and -MASTER is inactive. When the 82C321 detects valid inputs on -LS0, -LS1 and LM/-IO, it generates -ADL and -CMD. The status and address information are allowed to flow through to the MCA. -CMD is held valid for the duration of the cycle. If the current access is to an I/O device, the 82C321 activates the -XIORD or -XIOWR.

The 82C321 does not generate EALE for normal DMA cycles, not requiring bus conversion. EALE is generated when the DMA accesses an 8-bit device, wherein two 8-bit bus convert cycles are required. EALE is used to latch and maintain the address for the second cycle. -READY is activated to the DMA controller after the completion of the second cycle. During Refresh cycles -READY is generated by 321.

If -CHRDYRTN is sampled inactive, then additional wait states are introduced.

If DS16RTN is sampled active by the 82C321, then 16-bit transfer is assumed and no bus conversion cycles are performed. If DS16RTN is sampled inactive, then an 8-bit device is assumed the 82C321 performs the necessary bus steering and conversions.

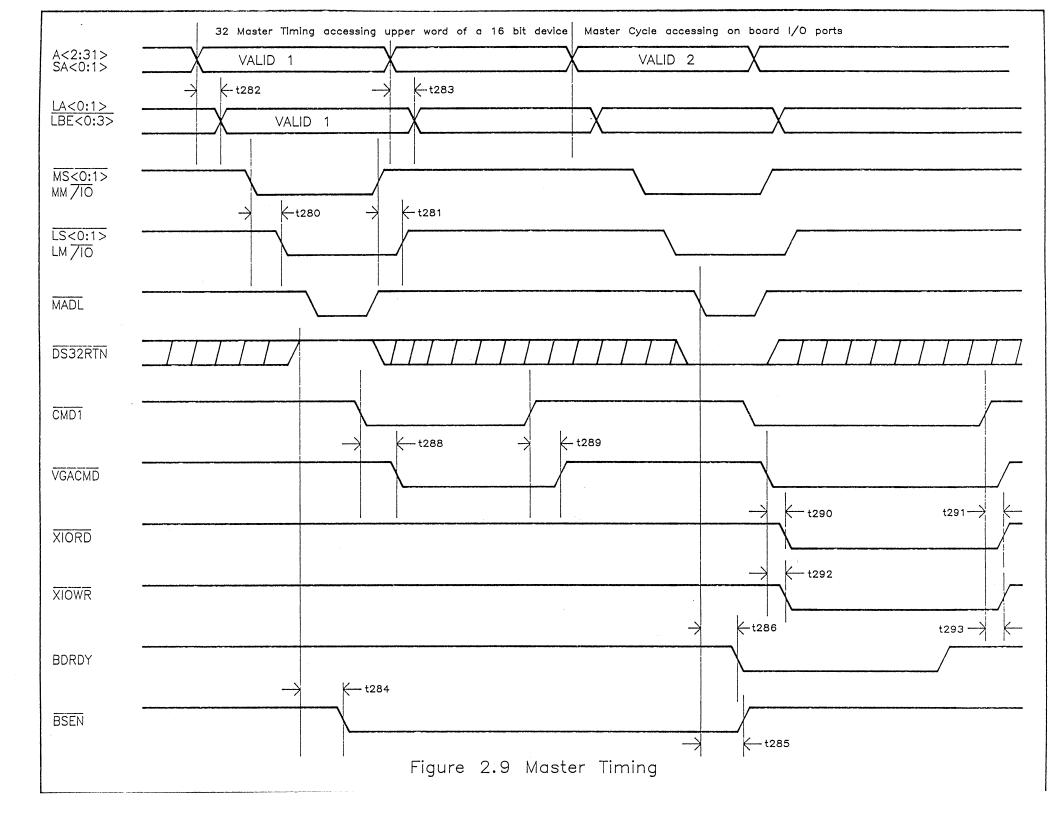

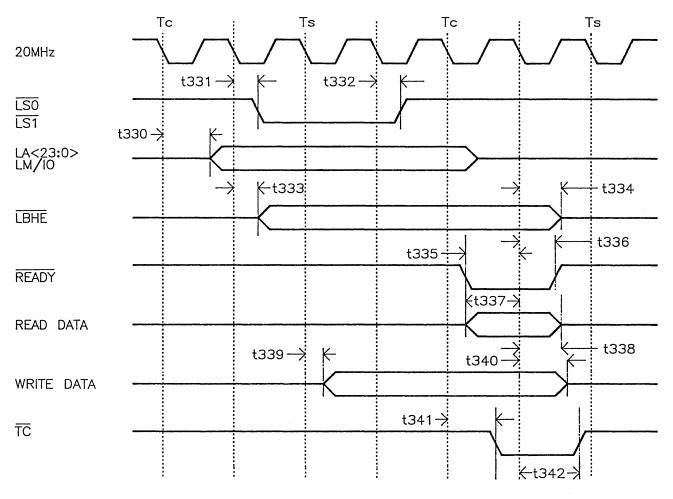

#### 3.0 MASTER CYCLES

The 82C321 provides complete support for external bus masters to access global resources on the system board. The bus master in control provides the required address, status and command signals.

The Bus Master requests control of MCA by activating the -PREEMPT line. The Central Arbitration Control Point (CACP) raises the ARB/-GNT line signifying the start of an arbitration cycle. The Master drives its arbitration level on to the 4 ARB pins in response to a high level on the ARB/-GNT line. If another device requests the bus, it drives its priority level on the ARB <3:0> pins. Each competing device compares the level it is driving on the pins with the levels already on the pins. If the device priority is higher than what is being presented on the bus, that device is declared the winner. If the device sees a higher priority on the bus than it is asserting, then it is declared a looser.

At the end of arbitration cycle, ARB/-GNT is driven low, indicating the end of the arbitration cycle and the winner of the arbitration process raises its -PREMPT line.

The Bus Master can access system board peripherals or memory via the 82C321. Two basic cycles are supported:

- 1. Accessing local memory controlled by 82C322

- 2. Accessing on-board peripherals

#### 3.1 Local Memory Access

The Bus Master in control of the MCA, drives valid addresses -MS0, -MS1 and -MM/-IO status lines, -ADL and -CMD signals on the MCA for the desired memory access. The 82C322 and the 82C321 receive -MS0, -MS1 and MM/-IO from the MCA. The 82C322 monitors the address and status information being presented to determine if the address requested resides in its memory space, and if so, it asserts the -RAS, -CAS and -WE signals to the DRAMs. 82C322 drives the MEMRDY signal inactive at the start of the cycle and activates it at the end of the cycle. The -MEMRDY signal is factored into the CHRDYRTN (Note: The MCA receives CHRDYRTN and the 82C321 receives -CHRDYRTN) signal. The -MASTER samples the CHRDYRTN signal and if inactive extends the cycle. The MASTER initiated memory access is terminated 60 ns(minimum) after CHRDYRTN is sampled active.

The 82C322, in response to memory requests from the MCA drives -AF32 active. External Bus Masters should monitor the -DS32RTN,s and -DS16RTN lines to determine the data sizing of the current access and perform the necessary bus steering.

If the current bus master is 16-bits (as determined by the polarity of MTR32 input), the 82C321 generates the Action Codes to perform the necessary bus steering.

#### 3.2 On-Board Peripherals

The Bus Master in control can access the on board peripherals, except peripherals residing in 00 to 0FFH address space (This is a programmable option, where the 82C223 could be programmed for MASTER to access DMA registers). It requires CPU intervention to access the DMA controller, the interrupt controller and other on-board peripherals residing below 0FFH. The Bus Master asserts valid address, status and control signals to access on board peripherals. The 82C321 samples -MS0, -MS1,-MM/IO,-ADL,-CMD inputs from the MCA. The 82C322 asserts - OBIOP signal to 82C321. The 82C321 generates the appropriate -XIORD or -XIOWR signals to the selected I/O peripherals (For all I/O cycles -XIORD or -XIOWR is generated). -CMD1 is used to gate the -XIORD and -XIOWR signals. -XIORD or -XIOWR are also generated when accessing programmable I/O ports PGMP0-2 (defined in 82C325).

Additionally, for Master cycles the 82C321 de-asserts BDRDY output at the start of the cycle. The BDRDY is factored into the -CHRDYRTN logic. When BDRDY goes active the -CHRDYRTN is sampled active and subsequently, the cycle is terminated.

When accessing 8-bit devices, DS16RTN and DS32RTN (inputs to the 82C321, the MCA receives -DS16RTN and -DS32RTN) are both sampled inactive. The 82C321 generates the appropriate Action Codes to perform the necessary bus steering operations. The MASTER samples the -DS16RTN and -DS32RTN to determine the data sizing of the current transaction. The MASTER performs the necessary bus conversion cycles.

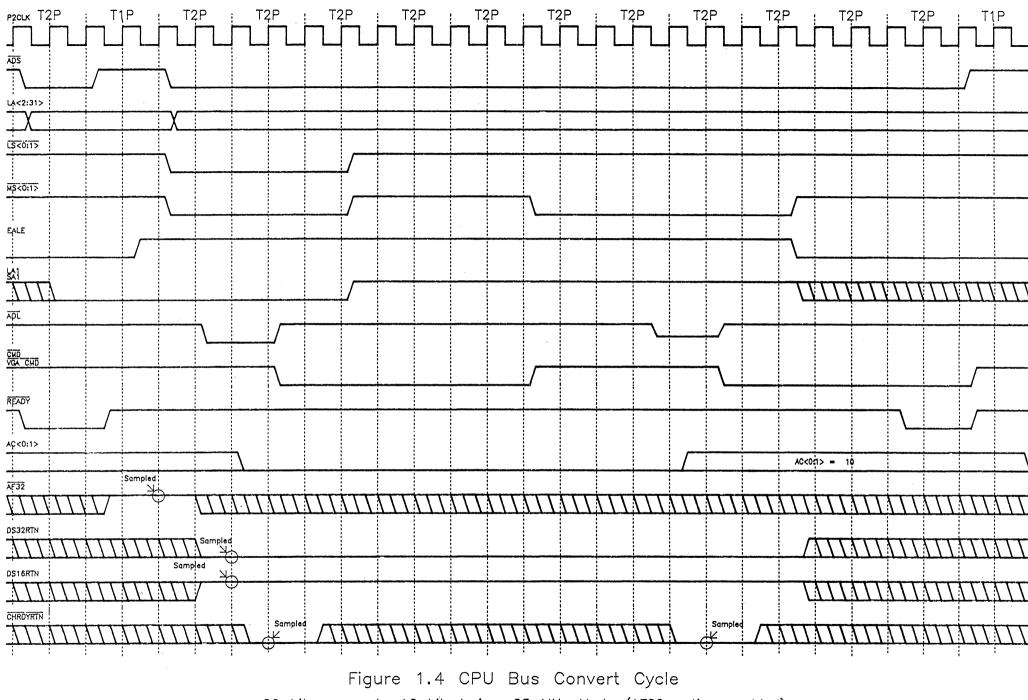

#### 4.0 Bus Conversion

The 82C321 provides a means for the system to perform 32 or 16-bit transfers to 16 or 8-bit devices. The Conversion Logic will detect when a conversion is necessary, signal the Wait State Control Logic to assert wait states to the CPU, and perform the conversion by manipulating the SA1, SA0 and -BHE output pins. During a bus conversion cycle, the CPU is held in a wait condition, with -READY inactive. The 82C321 determines the number of conversion cycles to be performed for the access, and generates the correct action codes and address information for each of the convert cycles.

For example, if a 32 bit access is performed to a 16-bit device, the 82C321 will detect DS32RTN inactive and DS16RTN active. It will perform two bus convert cycles. The sequence of events for the bus convert process, when the processor is in control, are described as follows. Refer to Figure 1-4.

- 1. The 82C321 samples -AF32 after detecting a valid cycle. If -AF32 is sampled inactive, then a non-local memory access is assumed.

- 2. EALE is low to allow the processor addresses to flow through to the MCA. It is driven high to latch the processor address and maintain it for the duration of the bus convert cycle. EALE is driven low in the middle of the last bus convert cycle, ensuring 30 ns address hold time following the de-activation of -ADL.

32 bit access to 16 bit device, 25 MHz Mode (AF32 option enabled)

- 3. It then samples DS16RTN and DS32RTN to determine if the current access is to an 8, 16 or 32-bit device. The BE<0:3> informs the 82C321 if the current access is a 32, 16 or an 8 bit access. Bus conversion cycles are performed for the following cases:

- a. 32-bit access to an 8 or 16-bit device

- b. 16-bit access to an 8-bit device

- c. 24-bit access to 8 or 16-bit device

- d. 16-bit cross word (BE1 & BE2 active) to 16-bit device.

If DS16RTN is sampled active and DS32RTN sampled inactive, and BE<3:0> are active, then two bus convert cycles are performed. -S0, -S1, -ADL and -CMD are asserted for each cycle, and removed at the end of the cycle. The SA0, SA1 are manipulated to access the correct locations. Example, when performing 32-bit access to 16-bit EPROMs, the SA1 is zero for the first access and one for the subsequent access.

At the completion of the last bus convert cycle, the -READY is generated to the processor to terminate the cycle.

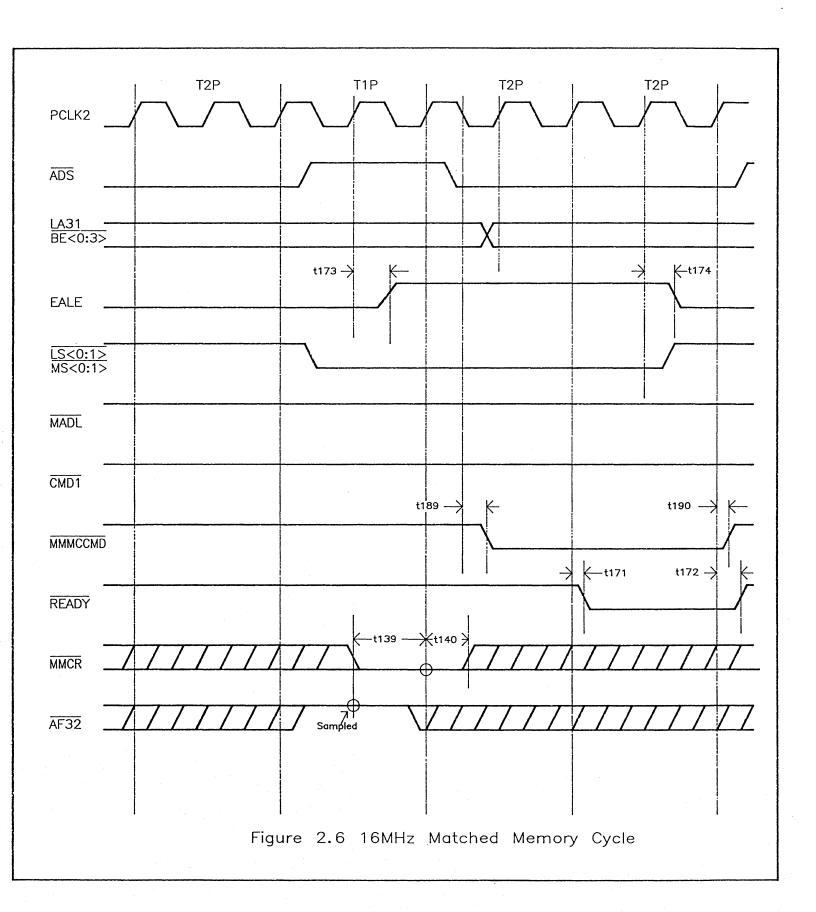

### 5.0 MATCHED MEMORY CYCLES

Matched Memory Cycles are allowed only for 16 or 32 bit Slave Devices and are only permitted when the CPU is in control. Matched Memory cycles allow for efficient data transfer between memory cards residing on the MCA and the system processor.

Matched Memory Cycle output to the MCA is active only when the CPU is in control. It is generated by HLDA (Hold Acknowledge, -MMC is inversion of HLDA). When HLDA is active, either when DMA or an external Bus Master is in control of the MCA, -MMC is inactive, indicating to the slave device that no matched memory cycles will be performed.

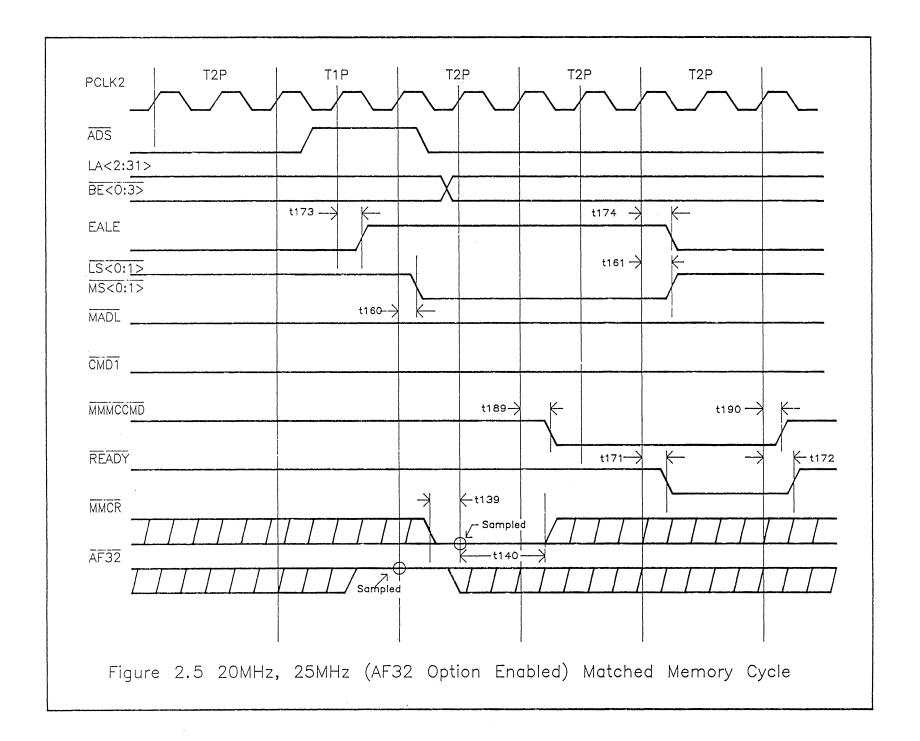

Matched Memory Cycles require one wait state at 16 MHz 20 Mhz, or 25 Mhz when enabled. The adapters residing on the MCA have to request a MMC (Matched Memory Cycle) on a cycle by cycle basis.

On the MCA, the address and the status information become available at the beginning of an MCA cycle. The 82C321 activates -MMC output, when the CPU is in control of the bus. The Adapter card should monitor the -MMC output to determine if it can initiate a Matched Memory Cycle By asserting -MMCR.

When the 82C321 samples MMCR active (high), it activates -MMMCMD. The -MMMCMD informs the adapter cards that data is valid on the Bus. The trailing edge indicates the end of the cycle.

The Matched Memory cycle can be extended by asserting -CHRDYRTN. The Matched Memory Cycle can be disabled or enabled by programming the register R2(index 8F). When disabled(bit 0 of R2 = 0) the default cycles are performed(250 ns @ 16Mhz, 250 ns @ 20MHz, and 240ns @ 25 Mhz), when enabled(bit 0 = 1) Matched Memory cycles are performed(187.5ns @ 16 Mhz,150ns @ 20 Mhz and 120 ns @ 25 Mhz)

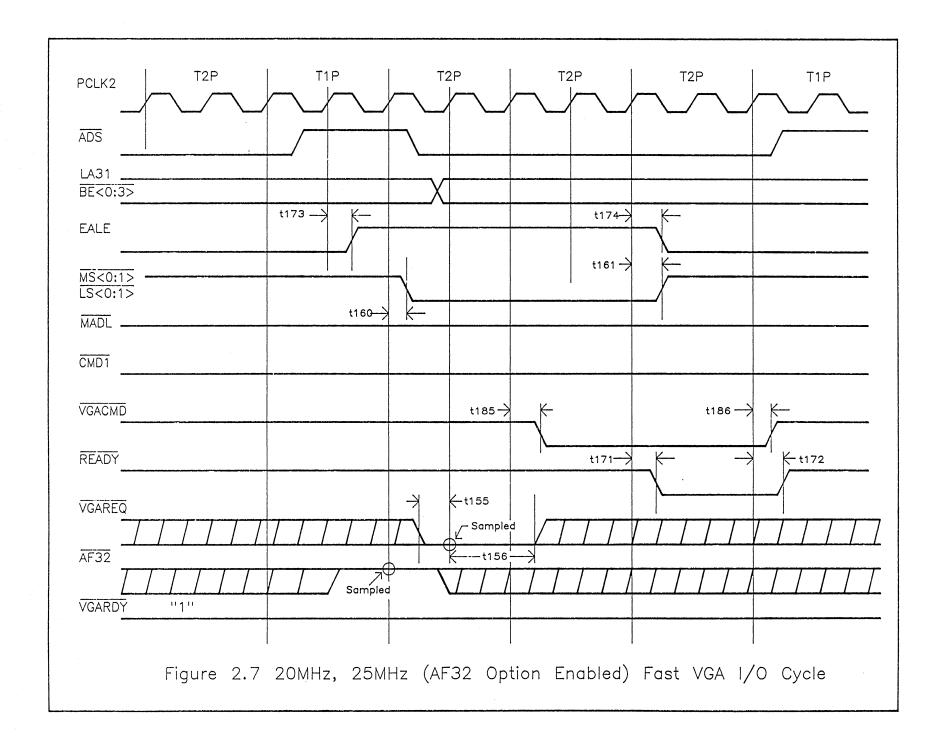

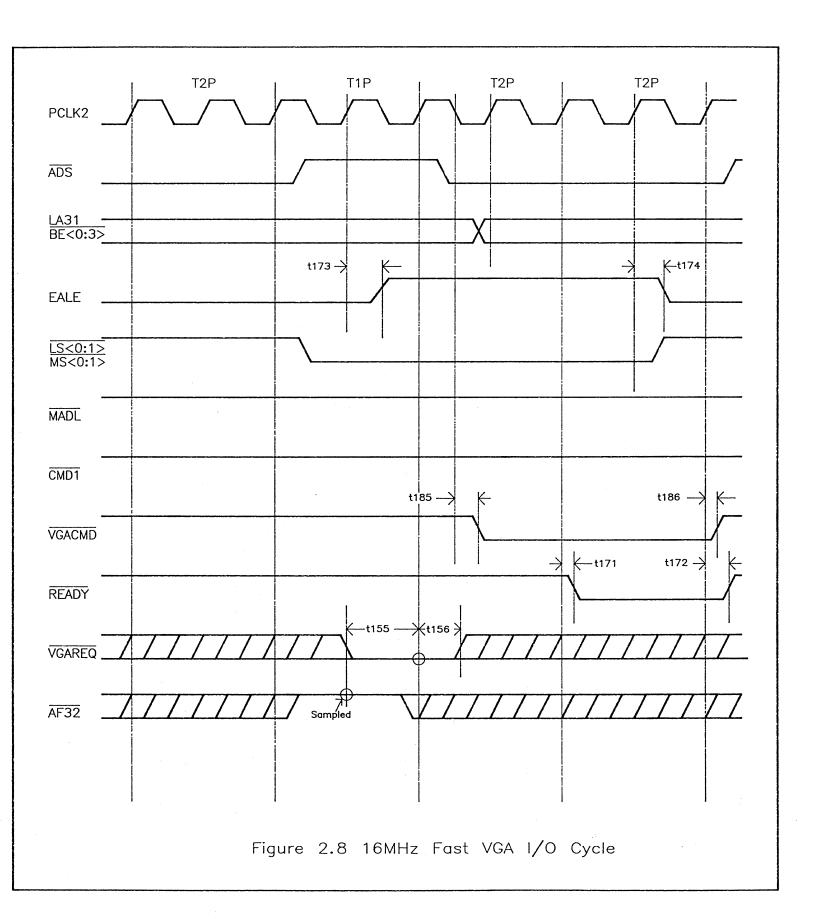

### 6.0 FAST VGA CYCLE

The cycle time for normal VGA I/O accesses is the default cycle time (250 ns @ 16 MHz, 250 ns @ 20 MHz, and 240 ns @ 25 MHz). The 82C321 supports a special fast protocol for the VGA I/O accesses to cut down VGA I/O cycle time. Two pins, -VGAREQ and -VGACMD are reserved for this purpose. The VGA will request a fast cycle with -VGAREQ signal and -VGACMD provides the strobe. The s

fast VGA cycle can be activated by enabling the generation of VGAREQ on the 82C451/452, and enabling the fast VGA cycle on the 82C321 by setting bit 1 in R2 register (Index 8F).

When the fast VGA cycle is enabled, the 82C321 samples -VGAREQ and if -VGAREQ is active, 82C321 performs fast VGA cycles. During fast VGA cycles, -CMD1 and -ADL are not generated but status -MSO, -MS1, and -VGACMD are generated. The cycle time for fast VGA cycles is 187.5 ns @ 16 MHz, 150 ns @ 20 MHz and 120 ns @ 25 MHz (AF32 option disabled). When delayed, AF32 option is enabled @ 20 and 25 MHz. The cycle time for fast VGA cycle is 200 ns @ 20 MHz and 160 ns @ 25 MHz.

The option of fast VGA cycles are not restricted to VGA accesses only. If the -VGAREQ and -VGACMD timings are met any I/O device can run a fast cycle. The Fast VGA cycle can be extended by activating CHRDYRTN.

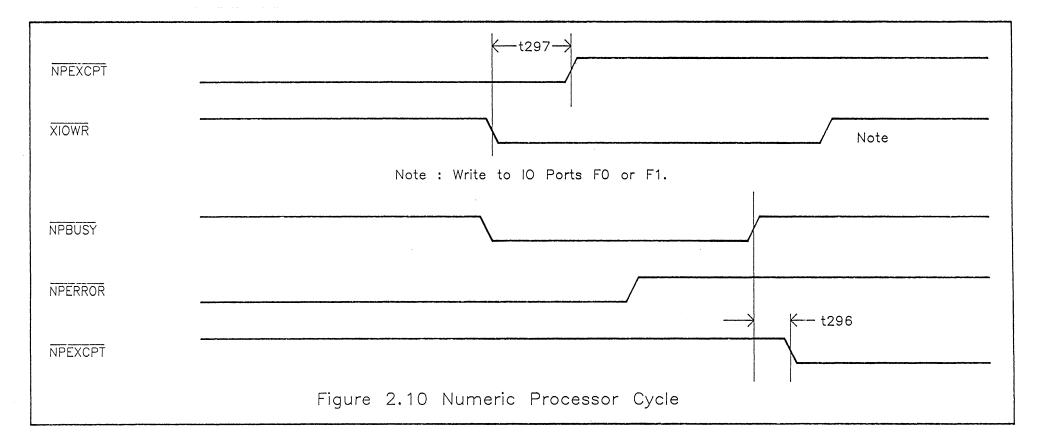

### 7.0 NUMERIC COPROCESSOR INTERFACE

Incorporated on the 82C321 is the circuitry to interface the 80387 Numeric Coprocessor to the 80386. The circuitry handles the decoding required for selecting and resetting the numeric coprocessor. The 82C321 also handles -NPBUSY and -ERROR signals from the 80387.

The 82C321 automatically recognizes the presence of the 80387, using a mechanism similar to the 80386 numeric coprocessor detection logic. It samples ERROR output of the 80387 on the falling edge of reset to detect the presence or absence of the 80387.

It supports two methods of -READY generation

- 1. The 82C321 generates -READY for all numeric coprocessor accesses. The bit 5 of System Speed Register R1 should be set to 0 for this option.

- 2. The -READY of the 80387 can be used to generate the -READY for numeric coprocessor cycles. This option provides better performance for numeric operations as the number of wait states for NP cycles can be controlled. In order to use this option bit-5 of Register R1 should be set to 1 and also the READY interface circuit as suggested by the manufacturer of 80387 should be implemented. The READY generated by the interface circuit is connected to the CPU READY through a tristate buffer which is enabled when the input signal (which is READY of interface circuit) is present.

Miscellaneous Ports: The 82C321 responds to various miscellaneous ports such as port 61, 92, and 94. The details are listed at the end of this manual.

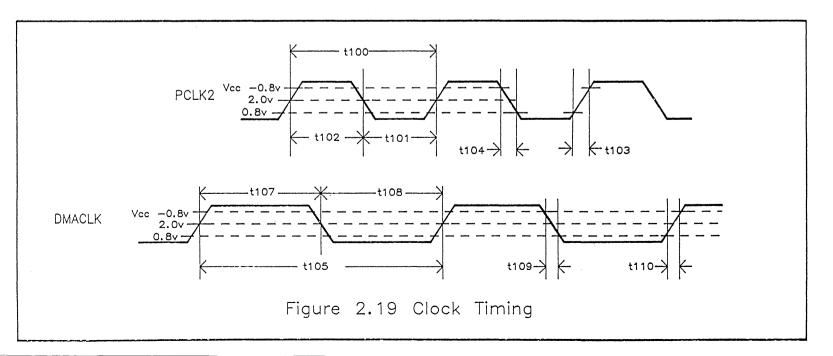

# 8.0 82C321 PIN DESCRIPTIONS CLOCKS

| Symbol  | Туре | PGA | PFP | Description                                                                                                                                                                                                                                               |

|---------|------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUCLK2 | Ι    | 26  | 79  | CPU CLOCK 2 input from<br>the 82C322) Memory<br>Controller or from an<br>external clock source, having<br>a maximum frequency of<br>twice the rated frequency of<br>the 80386 processor clock. It<br>is referred to as PCLK2<br>throughout this document. |

| DMACLK2 | I    | 63  | 62  | DMA CLOCK2 input from<br>the 82C223 DMA Controller<br>(20MHz). This clock input is<br>used for the DMA state<br>machine.                                                                                                                                  |

| DMACLK4 | 0    | 6   | 38  | DMA CLOCK4 output is<br>used to drive the Keyboard<br>controller clock. It is half the<br>frequency of DMACLK2 and<br>has a duty cycle of<br>approximately 50%.                                                                                           |

| OSC/12  | I    | 38  | 4   | OSCILLATOR CLOCK /12<br>is the 1.19 MHz TTL level<br>clock input from the 82C322.                                                                                                                                                                         |

## CONTROL

| Symbol  | Туре | PGA | PFP | Description                                                                                                                                                                                                |

|---------|------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -RESET1 | I    | 5   | 35  | RESET1 is an active low<br>input generated by the power<br>good signal of the power<br>supply. When low, it<br>activates RESET3 and<br>RESET4.                                                             |

| -RESET2 | Ι    | 89  | 36  | RESET2 is an active low<br>input(8042) generated from<br>the keyboard controller for a<br>"warm reset" not requiring<br>the system power to be shut<br>off. It forces a CPU reset by<br>activating RESET3. |

# CONTROL (continued)

| Symbol | Туре | PGA | PFP | Description                                                                                                                                                                                                                    |

|--------|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET4 | 0    | 72  | 84  | RESET4 is an active high<br>output used to reset the<br>MCA, 82C226, 8042<br>keyboard controller, and the<br>82C322 memory controller.<br>It is synchronized with the<br>processor clock.                                      |

| RESET3 | 0    | 27  | 81  | RESET3 is an active high<br>output to the 80386 when<br>RESET1 or RESET2 is<br>active. It is also activated<br>when a shut-down condition<br>in the CPU is detected or<br>when I/O port 92H, bit 0 is<br>set from zero to one. |

## **CPU INTERFACE**

| Symbol | Туре | PGA | PFP | Description                                                                                                                                                                                                                                                                        |

|--------|------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -READY | I/O  | 68  | 76  | READY is an open drain<br>output, and is driven low to<br>terminate the current CPU or<br>DMA cycle after<br>-CHRDYRTN is low. When<br>-AF32 is sampled active, then<br>it is an input from the<br>82C322. It is connected to<br>the 80386 -READY pin and<br>is normally inactive. |

| -LSO   | I/O  | 18  | 63  | LOCAL STATUS active low.                                                                                                                                                                                                                                                           |

| -LS1   | I/O  | 64  | 64  | The local status signals, when<br>output, are used by the<br>82C223 DMA controller<br>during DMA register<br>accesses, CPU or MASTER<br>cycles. These signals are<br>inputs during DMA<br>operation. Pull up resistors of<br>10K Ohms are required for<br>these signals.           |

| Symbol | Туре | PGA | PFP | Description                                                                                                                                                                                                                                                                                                                    |

|--------|------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LM/-IO | I/O  | 94  | 69  | Local MEMORY<br>INPUT/OUTPUT when high,<br>indicates a memory access.<br>When low, it indicates an I/O<br>access. It is used to generate<br>memory and I/O signals for<br>the system. It is output for<br>MASTER cycles and input<br>for CPU and DMA cycles. A<br>pull up resistor of 10K Ohms<br>is required for this signal. |

| -MBHE  | I/O  | 10  | 47  | BYTE HIGH ENABLE is an<br>active low signal which<br>indicates the transfer of data<br>on the upper byte of a 16 bit<br>data word. It is an input<br>during DMA and MASTER<br>cycles, and an output during<br>CPU cycles. A pull up<br>resistor of 10K Ohms is<br>required for this signal.                                    |

| -LBE0  | I/O  | 23  | 74  | LOCAL BYTE ENABLE 0<br>is an active low input from<br>the 80386 CPU indicating<br>data transfer on the lowest<br>byte. It is an output during<br>DMA and MASTER cycles<br>for the 82C322 Memory<br>Controller.                                                                                                                 |

| -LBE1  | I/O  | 67  | 73  | LOCAL BYTE ENABLE 1<br>is an active low input from<br>the 80386 CPU indicating<br>data transfer on the second<br>lowest byte. It is an output<br>during DMA and MASTER<br>cycles for the 82C322<br>Memory Controller.                                                                                                          |

| -LBE2  | I/O  | 22  | 72  | LOCAL BYTE ENABLE 2<br>is an active low input from<br>the 80386 CPU indicating<br>data transfer on the second<br>highest byte. It is an output<br>during DMA and MASTER<br>cycles for the 82C322<br>Memory Controller.                                                                                                         |

| Symbol | Туре | PGA | PFP | Description                                                                                                                                                                                                     |

|--------|------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -LBE3  | I/O  | 66  | 71  | LOCAL BYTE ENABLE 0<br>is an active low input from<br>the 80386 CPU indicating<br>data transfer on the highest<br>byte. It is an output during<br>DMA and MASTER cycles<br>for the 82C322 Memory<br>Controller. |

| -ADS   | I    | 24  | 75  | ADDRESS STATUS is an active low signal from the 80386 CPU indicating the initiation of a CPU cycle.                                                                                                             |

| W/-R   | I    | 21  | 70  | WRITE/READ is input from<br>the CPU. When low, it<br>indicates a write cycle. When<br>high, it indicates a read cycle.                                                                                          |

| D/-C   | I    | 65  | 68  | DATA/CONTROL is input<br>from the CPU. When high, it<br>indicates a data transfer.<br>When low, it indicates a<br>control transfer.                                                                             |

| -INTA  | 0    | 98  | 11  | INTERRUPT<br>ACKNOWLEDGE is an<br>active low output to the<br>interrupt controller of the<br>82C226 (IPC2), in response<br>to an interrupt request.                                                             |

## MCA INTERFACE

| Symbol | Туре | PGA | PFP | Description                                                                                                                                                                                                                                                             |

|--------|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDRDY  | 0    | 42  | 13  | BOARD READY is an active<br>high output. When low it<br>indicates a local device not-<br>ready condition leading to<br>wait state generation via the<br>MCA -CHRDYRTN signal,<br>to external MASTERs. When<br>high it allows termination of<br>the current local cycle. |

| Symbol                                           | Туре                                   | PGA                             | PFP                              | Description                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------|----------------------------------------|---------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CHRDYRTN                                        | I                                      | 41                              | 10                               | CHANNEL READY<br>RETURN is an active low<br>input. It is derived from<br>NANDing the -CD CHRDY<br>inputs from all the MCA<br>connectors, and other on<br>board ready signals (like<br>DMASRDY from 82C223,<br>MEMRDY from 82C322<br>etc.).                                                                        |

| -MADL                                            | 0                                      | 75                              | 93                               | ADDRESS DECODE<br>LATCH is an active low<br>output. It controls the address<br>latches used to hold the<br>addresses during bus cycles.<br>This signal is inactive for<br>Matched Memory Cycles.                                                                                                                  |

| EALE                                             | 0                                      | 76                              | 96                               | EXTERNAL ADDRESS<br>LATCH ENABLE is an<br>active high output used to<br>latch the LA2-LA31 address<br>lines (from CPU), to the A2-<br>A31 lines on the MCA.                                                                                                                                                       |

| -MBE0<br>-MBE1<br>-MBE2<br>-MBE3<br>-MS0<br>-MS1 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | 56<br>9<br>91<br>55<br>29<br>95 | 46<br>45<br>44<br>43<br>85<br>86 | M BUS STATUS lines are<br>active low. These lines<br>are output for CPU, DMA<br>and Refresh cycles and<br>input for MASTER cycles.                                                                                                                                                                                |

| -CMD1                                            | 0                                      | 74                              | 89                               | M BUS COMMAND is<br>active low, indicating when<br>data is valid on the data bus.<br>The trailing edge indicates<br>the end of a cycle. It is output<br>for CPU, DMA and Refresh<br>cycles, and input for<br>MASTER cycles. This signal<br>could be used by the slaves to<br>latch the address on the MCA<br>bus. |

| Symbol  | Туре | PGA | PFP | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -MMMCMD | 0    | 54  | 39  | M BUS MATCHED<br>MEMORY COMMAND is<br>an active low output<br>signal, indicating that data is<br>valid on the data bus for<br>matched memory cycles.<br>Valid address has to be<br>latched on the leading edge.<br>It is output for CPU cycles<br>only.                                                                                                                                                                                                          |

| MMCR    | I    | 8   | 42  | MATCHED MEMORY<br>CYCLE REQUEST is an<br>active high input from the<br>MCA logic from 32 bit slaves<br>requesting a matched<br>memory cycle.                                                                                                                                                                                                                                                                                                                     |

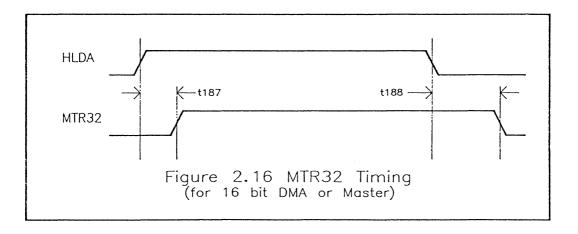

| MTR32   | I/O  | 57  | 48  | M BUS TRANSLATE 32 is<br>an active high signal. It is<br>low output for CPU, DMA<br>and Refresh cycles, and input<br>for MASTER cycles. When a<br>16-bit MASTER (or DMA) is<br>active the MTR32 is tristated,<br>and remains high hence a<br>10K Ohm pull up resistor is<br>required to make MTR32<br>tristate active high. If a 32<br>bit MASTER is active, the<br>MTR32 pin is tristated (but<br>goes high due to pull up), the<br>MASTER drives MTR32<br>low. |

| Symbol     | Туре       | PGA      | PFP      | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS16RTN    | Ι          | 40       | 8        | DATA SIZE 16 RETURN is<br>an active high input. It is<br>derived from "NAND"ing the<br>-CDDS16 inputs from all the<br>MCA connectors, and other<br>on board DS16 signals (like<br>DMADS16 from the<br>82C223, VGADS16 from<br>82C322 etc.). If only<br>DS16RTN is high, it<br>indicates a 16-bit data<br>transfer request. If DS16RTN<br>and DS32RTN are high, it<br>indicates a 32-bit data<br>transfer request. |

| DS32RTN    | Ι          | 82       | 9        | DATA SIZE 32 RETURN is<br>an active high input It is<br>derived from NANDing the -<br>-CD DS32 inputs from all the<br>MCA connectors DS32RTN<br>indicates a 32-bit data<br>transfer request.                                                                                                                                                                                                                      |

| -BTO       | I          | 62       | 59       | BUS TIME-OUT is an active<br>low input from the DMA<br>controller, indicating that a<br>bus time out has occurred and<br>the current I/O cycle should<br>be terminated. It terminates -<br>XIORD or -XIOWR signal.                                                                                                                                                                                                |

| SA0<br>SA1 | I/O<br>I/O | 97<br>33 | 94<br>95 | ADDRESS LINES SA0, SA1<br>These lines are output for<br>CPU and DMA cycles and<br>are latched. They are<br>buffered to generate the<br>MCA address lines A0, and<br>A1. They are input for<br>Master cycles.                                                                                                                                                                                                      |

| LA0<br>LA1 | I/O<br>I/O | 17<br>92 | 60<br>61 | LOCAL ADDRESS LINES<br>LA0, LA1. CPU and<br>MASTER cycles to the<br>82C223 DMA Controller,<br>and input for DMA, and<br>Refresh cycle from the DMA<br>Controller.                                                                                                                                                                                                                                                 |

| Symbol | Туре | PGA | PFP | Description                                                                                                                                                                 |

|--------|------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LA31   | I    | 71  | 82  | LOCAL ADDRESS LINE<br>LA31 is input from the 80386<br>for CPU cycles to identify<br>80387 accesses. It should be<br>pulled up with a 4.7K Ohm<br>resistor.                  |

| -LBHE  | I/O  | 20  | 67  | LOCAL BTYE HIGH<br>ENABLE from the 82C223<br>DMA controller, used to<br>generate action codes<br>LBHE is an output during<br>CPU cycles generated by<br>decoding -LBE<0:3>. |

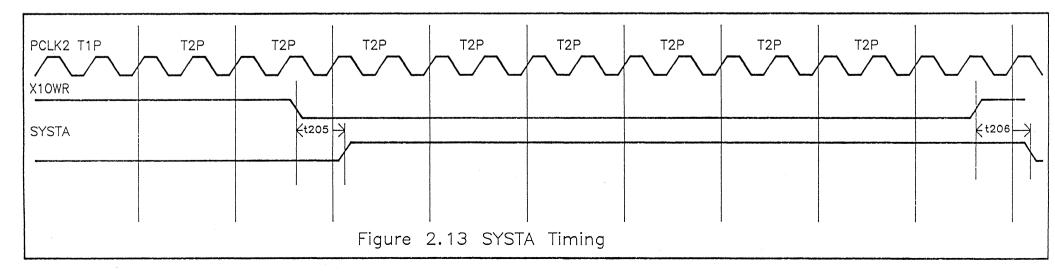

| SYSSTA | 0    | 83  | 12  | SYSTEM STATUS is an active high output indicating a system disk access.                                                                                                     |

## **DMA INTERFACE**

| Symbol | Туре | PGA | PFP | Description                                                                                                                                         |

|--------|------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| HLDA   | Ι    | 70  | 80  | HOLD ACKNOWLEDGE is<br>an active high input<br>generated by the CPU,<br>relinquishing the bus to the<br>DMA controller or to an<br>external MASTER. |

.

| Symbol   | Туре | PGA | PFP | Description                                                                                                                                                                                                                                                 |

|----------|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HLDAO    | 0    | 32  | 92  | HLDAO is active high output<br>generated by 321 in response<br>to HLDA input from CPU.<br>This output goes to HLDA of<br>82C223. This makes sure<br>that HLDA to the 82C223 is<br>not deasserted (until the<br>DMA cycle is complete)<br>when CPU is reset. |

| -MASTER  | I    | 16  | 58  | MASTER is an active low<br>input indicating that a<br>MASTER device on the<br>MCA is in control of the<br>system.                                                                                                                                           |

| -RFSH    | I    | 34  | 97  | REFRESH is an active low<br>input from the DMA<br>controller initiating a system<br>refresh cycle. This input is<br>registered in bit 4 of Port 61.                                                                                                         |

| -DSKDACK | I    | 61  | 57  | DISK CONTROLLER DMA<br>ACKNOWLEDGE from the<br>DMA Controller is an active<br>low input. This introduces<br>additional wait states when<br>accessing the floppy disk<br>controller during DMA<br>operations.                                                |

## MEMORY CONTROL

| Symbol   | Туре | PGA | PFP | Description.                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -AF32    | I    | 30  | 88  | AF32 is an active low input<br>from the 82C322 Memory<br>Controller, indicating a 32 bit<br>local DRAM access, and<br>82C322 generates ready for<br>the CPU.                                                                                                                                                                                                                                |

| -OBIOP   | I    | 28  | 83  | ON BOARD I/O PORT is an active low input from the 82C322 Memory controller, indicating I/O access in the address range 0-3FF.                                                                                                                                                                                                                                                               |

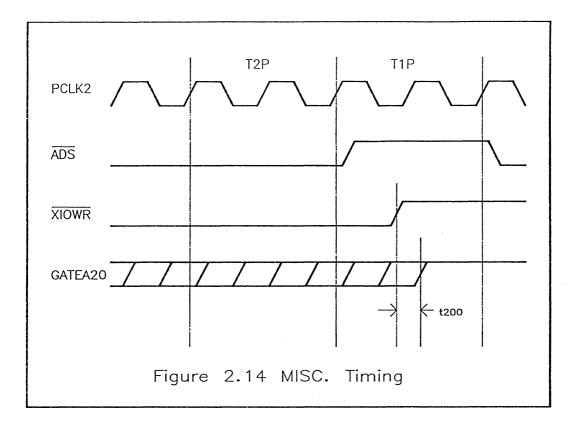

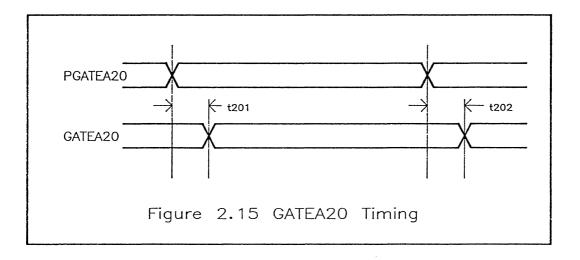

| PGATEA20 | I    | 53  | 37  | PGATE A20 input active<br>high from the 8042 Keyboard<br>controller. This is ORred<br>with bit 1 of Port 92 to<br>generate GA20 signal to 322.                                                                                                                                                                                                                                              |

| GATEA20  | 0    | 73  | 87  | GATE A20 output to the<br>82C322 memory controller.<br>When low, forces the LA20<br>line low and when high, it<br>propagates the CPU A20 line.<br>It is used to keep address<br>under 1Mb in DOS<br>environments. It is high for<br>DMA and MASTER cycles.<br>It is OR of GATEA20 input<br>and bit 1 of Port 92. The<br>actual gating of A20 is done<br>in the memory Controller<br>82C322. |

## **BUS INTERFACE**

| Symbol | Туре | PGA | PFP | Description                                                                                                 |

|--------|------|-----|-----|-------------------------------------------------------------------------------------------------------------|

| -XIORD | 0    | 11  | 49  | X BUS I/O READ is an<br>active low output strobe<br>directing an I/O port to place<br>data on the data bus. |

| -XIOWR | 0    | 12  | 50  | X BUS I/O WRITE is an<br>active low strobe directing an<br>I/O port to accept data from<br>the data bus.    |

# **BUS INTERFACE (continued)**

| Symbol                                               | Туре                                                 | PGA                                           | PFP                                          | Description                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XD0<br>XD1<br>XD2<br>XD3<br>XD4<br>XD5<br>XD6<br>XD7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | 4<br>51<br>3<br>50<br>2<br>88<br>48<br>47     | 33<br>32<br>31<br>30<br>29<br>26<br>25<br>24 | X DATA BUS bits <7:0> to<br>access internal registers<br>of the 82C321.                                                                                                                                                                                                                                              |

| XA2<br>XA3<br>XA4<br>XA5<br>XA6<br>XA7<br>XA8<br>XA9 | I<br>I<br>I<br>I<br>I<br>I<br>I<br>I                 | 43<br>44<br>85<br>100<br>45<br>86<br>46<br>87 | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | X ADDRESS lines <2:9> to<br>access the internal<br>registers of the 82C321.<br>These lines are also used to<br>determine the address range,<br>and introduce appropriate<br>wait states during I/O cycles.                                                                                                           |

| -BSEN                                                | 0                                                    | 80                                            | 5                                            | BUS STEERING ENABLE<br>is an active low output, used<br>by the MCA bus steering<br>logic to enable a 16 bit<br>Master to access the upper<br>word of channel slaves. It is<br>active when a 16-bit<br>MASTER is accessing the<br>upper word (when SA1 = 1).                                                          |

| -WDLTH                                               | 0                                                    | 58                                            | 51                                           | WRITE DATA LATCH<br>ENABLE is an active low<br>output, used by the 82C325<br>Data Buffer during CPU<br>cycles, to meet the hold time<br>for MCA write cycles. When<br>high allows data to pass<br>through. This signal is low<br>when -CMD1 is low during<br>CPU cycles, and is high<br>during DMA/MASTER<br>cycles. |

### **BUFFER CONTROL**

| Symbol     | Туре   | PGA      | PFP     | Description                                                                                                                                              |

|------------|--------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDIR       | 0      | 81       | 7       | MCA DATA BUS<br>DIRECTION output. A low<br>sets the data path from the<br>MCA to the MD bus. A high<br>sets the data path from the<br>MD bus to the MCA. |

| SDEN       | 0      | 39       | 6       | Presently not used.                                                                                                                                      |

| AC1<br>AC0 | 0<br>0 | 60<br>14 | 5<br>54 | ACTION CODE is a two bit<br>encoded output for bus size<br>control and byte assembly<br>operations performed in the<br>82C325 Data Buffer.               |

# COPROCESSOR INTERFACE

| Symbol   | Туре | PGA  | PFP | Description                                                                                                                                                                                                                                           |

|----------|------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -NPBUSY  | Ι    | 77 . | 98  | NUMERICAL PROCESSOR<br>BUSY is an active low input<br>from the NPC, indicating that<br>it is currently executing a<br>command. It is used to<br>generate the BUSY signal to<br>the CPU. A 4.7K Ohm pull<br>up resistor is required on this<br>signal. |

| -NPERROR | I    | 35   | 99  | NUMERIC PROCESSOR<br>ERROR is an active low<br>input from the NPC<br>indicating that an unmasked<br>error condition exists. A 4.7K<br>Ohm pull up resistor is<br>required on this signal.                                                             |

| NPRESET  | 0    | 36   | 100 | NUMERICAL PROCESSOR<br>RESET is an active high reset<br>to the 80387. It is active<br>when RESET3 is active or<br>when a write operation is<br>made to Port 0F1H. In the<br>later case, it is active for a<br>pre-defined period.                     |

# COPROCESSOR INTERFACE (continued)

| Symbol  | Туре | PGA | PFP | Description                                                                                                                                                       |

|---------|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NPEXCPT | 0    | 78  | 1   | NUMERICAL PROCESSOR<br>EXCEPTION is an active<br>low output to the 82C226<br>IPC2. It is connected to the -<br>IRQ13 line in a PS/2 <sup>TM</sup><br>environment. |

# **VGA INTERFACE**

| -VGAREQ | I | 52 | 34 | VIDEO GRAPHICS<br>ADAPTER REQUEST is an<br>active low input from the<br>82C451 VGA Controller,<br>requesting a Fast VGA cycle.<br>The 82C321 should be<br>enabled to sample this input.                                                                                                                                                                             |

|---------|---|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -VGACMD | 0 | 15 | 56 | VIDEO GRAPHICS<br>ADAPTER COMMAND is<br>an active low Fast VGA<br>command indicating data<br>transfer. During default<br>cycles, -VGACMD is<br>generated identical to CMD1.<br>When fast VGA cycle is in<br>progress only -VGACMD is<br>generated. No -CMD1 is<br>generated. This is also used<br>as latching signal to drive XA<br><0:15> from MCA address<br>bus. |

| POWER | SUPPLIES |

|-------|----------|

|-------|----------|

| Symbol | PGA                                                     | PFP                                                     | Description  |

|--------|---------------------------------------------------------|---------------------------------------------------------|--------------|

| VDD    | 84<br>7<br>13<br>93<br>31<br>37                         | 2<br>14<br>41<br>52<br>65<br>91                         | Power Supply |

| VSS    | 79<br>99<br>1<br>49<br>90<br>59<br>19<br>69<br>96<br>25 | 3<br>15<br>27<br>28<br>40<br>53<br>66<br>77<br>78<br>90 | Ground       |

Table 2 lists the programming registers that are located on the 82C321 chip.

| Table | 2 |

|-------|---|

|-------|---|

| Reg # | Register Name          | Index | Location |

|-------|------------------------|-------|----------|

| R0    | Version Register       | 8DH   | 82C321   |

| R1    | System Speed Select    | 8EH   | 82C321   |

| R2    | System Option Register | 8FH   | 82C321   |

# 82C321 Register Descriptions

### **Version Register R0:**

Index Register Port: 22H Data Register Port: 23H Index: 8DH (Read Only)

| Bits | Value             | Function                                |

|------|-------------------|-----------------------------------------|

| 1,0  |                   | 82C321 version number (R)               |

|      | 0,0<br>0,1<br>1,1 | Initial version<br>Reserved<br>Reserved |

| 2-7  |                   | Reserved                                |

### System Speed Select Register R1:

Index Register Port: 22H Data Register Port: 23H Index: 8EH

,

| Bits | Value                    | Function                                                                         |

|------|--------------------------|----------------------------------------------------------------------------------|

| 1,0  |                          | Processor clock select (R/W)                                                     |

|      | 0,0<br>0,1<br>1,0<br>1,1 | 16MHz<br>20 MHz<br>25 MHz<br>Reserved                                            |

| 2,3  |                          | Reserved                                                                         |

| 4    |                          | Indicates presence of 80387 Numeric coprocessor following power up.              |

|      | 10                       | 80387 Numeric coprocessor installed.<br>80387 Numeric coprocessor not installed. |

| 5    |                          | Math Ready                                                                       |

|      | 1<br>0                   | Numeric coprocessor generates Ready. (Default)<br>82C321 generates Ready         |

# System Speed Select Register R1: (continued)

| Bits | Value  | Function                                                                                                                                                                                                                                                                                                                                                                       |

|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | 1<br>0 | <ul> <li>This bit enables the delayed sampling of -AF32 signal used when the CPU clock is at 20 or 25 MHz. Setting of this bit delays the sampling of -AF32 by one CLK2 and also inserts one wait state in all bus cycles. It also delays generation of all MCA signals by one CLK2 cycleCMD pulse width increases by one CLK2.</li> <li>Enabled (Default) Disabled</li> </ul> |

| 7    |        | Reserved                                                                                                                                                                                                                                                                                                                                                                       |

# **System Option Select Register R2:**

Index Register Port: 22H Data Register Port: 23H Index: 8FH