### 82C5059 SINGLE CHIP PC-AT DISK CONTROLLER

### **Memory Controller Features**

- Two Independent DMA Channels

- 13 Megabyte Device Bandwidth at 40MHz Clock

- 20-bit Address and 16-Bit Transfer Count Registers For Each Channel

- Holding Registers for Addresses Counts for Non-Contiguous Memory Transfers

- Bus Access Resolved on Channel Priority Basis

- Programmable:

- Interrupt Polarity

- Auto-Count Re-Initialization

- Memory Access Cycle Timing (2 To 5 Clock Cycles)

- Buffer Memory Address for 64K SRAM (2 Memory Chip Enables for 32K x 8 SRAM)

- DRAM Support For Up To 1 Megabyte

# Programmable Data Sequencer Features

- High Level Instruction Set

- Supports up to 20MHz Serial Bit Rate (NRZ)

- Programmable Disk Format

- NRZ Serial Disk Interface

- Direct Interface to ESDI Type Drives

- Multi-Sector Transfer Capability with Automatic Sector Increment

- **Programmable Automatic ID Retries**

- **ESDI ID Sync Timeout Programmable**

- ESDI Write Gate to AM ENABLE Programmable

- **■** Format Track With Data From Buffer

- Programmable Write Gate Disable for Embedded Servo

- 32, 48, 56 Bit ECC Polynomial

#### **AT Interface Features**

- Direct Interface to AT-Compatible Systems, Including 40-Pin Bus Interface

- High Current Drivers for Host Interface

- Schmidt Trigger Inputs Form Host Interface

- Configurable Primary or Secondary Address

- 2 Word FIFO

- Automatic BUSY, INTRQ and ECC Mode

- Flexible Interrupt Capability

- Advanced 1.5 µ CMOS, Low Power Techonology

- 100-Pin Quad Flat Pack Packaging

#### Introduction

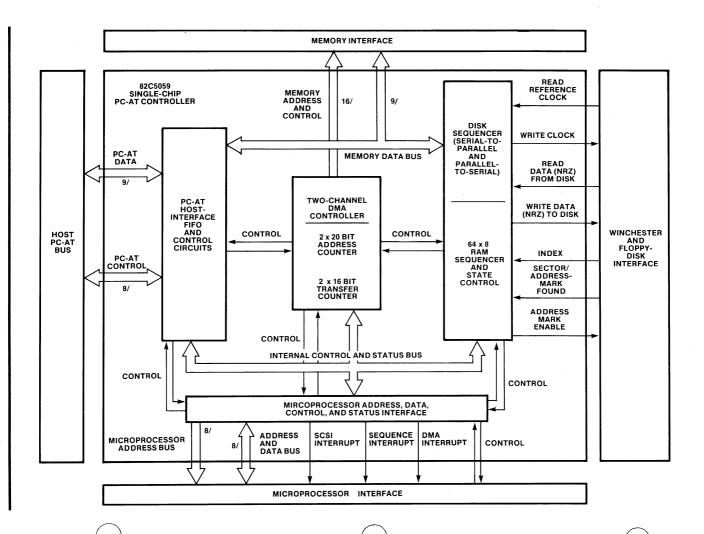

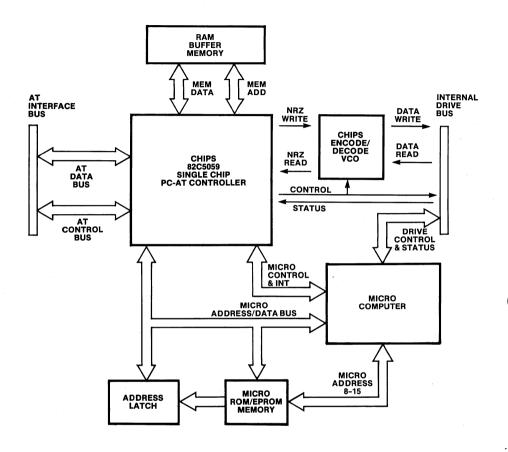

The 82C5059 Single Chip PC-AT Controller is a CMOS LSI Applications Specific Integrated Circuit (ASIC) designed to be the primary component in a high-performance intelligent PC-AT Winchester disk controller system. The 82C5059 single chip controller provides three essential functions in a disk controller system: it manages the flow of data for a serial peripheral, it controls access to the external RAM buffer memory that is required for such transfers and it directly interfaces to a PC-AT type system bus. The 82C5059 is designed to be used with a microprocessor having either a Z8-or 8051-type bus structure.

The 82C5059 consists of three functional sections:

- 1. A DMA controller

- 2. A data sequencer

- 3. A PC-AT interface controller

The 82C5059 incorporates a dual-bus architecture, providing separate ports for microprocessor and memory buffer operations. With the goal of achieving the highest possible performance, this dual-bus structure is used so that disk data transfers can occur simultaneously with microprocessor operations.

In the DMA controller, Channel 0 is used for moving blocks of data between the data sequencer and the external buffer, while Channel 1 is used for moving blocks of data between the PC-AT host interface and the buffer. When the data sequencer is not using Channel 0, this channel can also be used to allow the microprocessor to access the RAM buffer. DMA controller operation is programmed by writing the DMA controller registers, while operation may be monitored by reading the DMA controller registers.

The programmable data sequencer provides format control, error detection, and serial/ parallel (SERDES) conversion functions normally associated with disk controllers. It is designed to be used with NRZ (Non-Return to Zero) interfaces such as those used in the ESDI (Enhanced Small Device Interface) or any of the CHIPS family of encode/decode VCO devices. Flexible operation of the sequencer is made possible by write registers that program its operation, while read registers allow the firmware to monitor operation. In addition, complete flexibility in disk formatting is permitted by a 64-byte on-device format RAM, which is accessed through three of the data sequencer write registers (WR25, WR30 & WR31).

In addition to an external RAM buffer, a byteoriented microprocessor such as the Z8 or 8051, with its associated memory, the 82C5059 may be connected with the CHIPS 10C5070 Encode/Decode/PLL for MFM encoding/ decoding up to 5 Mbits/second, or the 10C5027 Encode/Decode/PLL for RLL 2,7 encoding/decoding up to 10 Mbits/second thus providing a complete controller solution for an embedded PC-AT interfacing disk drive.

### **Ordering Information**

The 82C5059 can be ordered using the following part number:

F82C5059 (100-Pin QFP)

Evaluation samples are available now. Production orders accepted with standard leadtimes.

F82C5059 Typical System Configuration

|                  |              | <del></del> | 99            | 8        | 97     | 8         | 95       | 94      | 93        | ខ       | 열    | 8        | 89      | 8        | 87       | 86        | 8         | 8      | 83      | 82       | 으       |      |        |    |          |

|------------------|--------------|-------------|---------------|----------|--------|-----------|----------|---------|-----------|---------|------|----------|---------|----------|----------|-----------|-----------|--------|---------|----------|---------|------|--------|----|----------|

|                  |              | ě           | Ρ             | 2.       | ဂ္ဂ    | l ii      | š        | AD7     | AD6       | AD5     | 5    | <u>-</u> | Α.      | AD3      |          | AD1       | ADO       | ᅙ      | ᅙ       | ō        | ٩       |      |        |    |          |

|                  |              |             |               |          | ő      | S         | 쯢        | 7       | 6         | 5       | VSS6 | Ď        | AD4     | చ        | ž        | Ξ.        | ĕ         | ORD DS | IOWR RW | MEM DM   | ALE AS  |      |        |    |          |

| _                |              |             |               |          |        |           | •••      |         |           |         |      |          |         |          |          |           |           | S      | 歄       | S        | SI      |      |        |    |          |

| 1                | IORD         |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         | š        |         |      | PRO    |    | 80       |

| 2                | IOWR         |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | INTR   |    | 79       |

| 3                | MEM WRT      |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         | SEQ  | INTR   | 1  | 78       |

| 3<br>4<br>5<br>6 | MEM CE1      |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D1     |    | 77<br>76 |

| <u>-</u>         |              |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D1     |    | 75       |

| 7                | MA14         |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D1     |    | 74       |

|                  | MA13         |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | VSS    |    | 73       |

| 8                | MA12         |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D1     |    | 72       |

| 9                | MA11<br>MA10 |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D1     |    | 71       |

| 11               | MA9          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      |        | 9  | 70       |

| 12               | MA8          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | _      | 8  | 69       |

| 13               | MA7          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      |        | 7  | 68       |

| 14               | MA6          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      |        | 6  | 67       |

| 15               | VSS0         |             | CHIPS VSS4    |          |        |           |          |         |           |         |      |          |         |          |          |           | 66        |        |         |          |         |      |        |    |          |

| 16               | MA5          |             | F82C5059 VDD1 |          |        |           |          |         |           |         |      |          |         |          |          | 65        |           |        |         |          |         |      |        |    |          |

| 17               | MA4          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D      |    | 64       |

| 18               | MA3          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D      |    | 63       |

| 19               | MA2          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D      |    | 62       |

| 20               | MA1          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D      |    | 61       |

| 21               | MA0          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D      |    | 60       |

| 22               | MDP          |             |               |          |        | ,         |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | vss    | 3  | 59       |

| 23               | MD7          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | D      | 0  | 58       |

| 24               | MD6          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         | IOC  | HRD    | Υ  | 57       |

| 25               | MD5          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         | ī    | OCS1   | 6  | 56       |

| 26               | MD4          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         | 7        | CT      | SLV  | PRE    | ริ | 55       |

| 27               | MD3          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         |      | vss    | 2  | 54       |

| 28               | MD2          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          | ī       | PASS | DIA    | G  | 53       |

| 29               | MD1          |             |               |          |        |           |          |         |           |         |      |          |         |          |          |           |           |        |         |          |         | ı    | NTR    | Q  | 52       |

| 30               | MD0          |             |               | ≥        |        | R         | ٤        |         | ş         |         |      |          |         | ଦ୍ରା     | ଯା       | 핆         | Æ         |        |         | ×        |         | RES  | SET II | N  | 51       |

|                  |              |             | SE            | AM FOUND | ,      | RD REFCLK | WRT GATE | RD      | AM ENABLE | ¥       |      |          | NRZ OUT | GROUP WR | GROUP RD | RESET OUT | RESET CMD |        |         | XTAL OUT | ×       |      |        |    |          |

|                  |              | Z           | SECTOR        | ĕ        | NRZ IN | 뛰         | ย์       | RD GATE | Æ         | WRT CLK | á    | <u> </u> | 20      | 듬        | 뒤        | ə         | C         | SO     | 0       | Ċ        | XTAL IN |      |        |    |          |

|                  |              | INDEX       | Ğ,            | ğ        | Ž      | 붓         | Ħ        | Ħ       | Ę         | Ķ       | VDD0 | VSS1     | Ĭ       | ₽        | 핑        | Ĭ         | Š         | 0SC 2  | osc     | Ĕ        | ž       |      |        |    |          |

| Į.               | L            | т           |               | _        |        |           |          |         |           |         |      | _        | Ė       |          |          | _         |           |        | _       |          | _       |      | _      | _  | ł        |

|                  |              | 얼           | 8             | မ္မ      | 34     | 35        | 36       | 37      | 38        | 39      | 4    | 4        | 25      | 4        | 4        | 45        | 46        | 47     | 48      | 49       | 50      |      |        |    |          |

# NOTES

## NOTES

# Chips and Technologies, Inc.

3050 Zanker Road, San Jose, CA 95134 408-434-0600 telex 272929 CHIPS UR

CHIPS, CHIPSet, NEAT, NEATsx, LeAPSet, LeAPSetsx, PEAK, CHIPS/280, CHIPS/250, CHIPS/230, CHIPS/450, MICROCHIPS, CHIPSPak, CHIPSPort, CHIPSlink are trademarks of Chips and Technologies, Inc.

IBM AT, XT, PS/2, Micro Channel, Personal System/2, Enhanced Graphics Adapter, Color Graphics Adapter, IBM Color Display, IBM Monochrome Display are trademarks of International Business Machines.

Intel, iAPX 386 are trademarks of Intel Corporation.

Motorola is a trademark of Motorola.

Lotus is a trademark of Lotus Corporation. Microsoft is a trademark of Microsoft.

Copyright 1988, 1989 Chips and Technologies, Inc.

These data sheets are provided for the general information of the customer. Chips and Technologies, Inc. reserves the right to modify these parameters as necessary and customer should ensure that it has the most recent revision of the data sheet. Chips makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.