CDC® 2550-2(MOS)

HOST COMMUNICATIONS PROCESSOR

2554-16/-32 MEMORY EXPANSION MODULES

2556-2/-3/-4 COMMUNICATIONS LINE

**EXPANSION UNITS**

2558-1 COMMUNICATIONS COUPLER

2571-1 PERIPHERAL CONTROLLER

SYSTEM DESCRIPTION

FUNCTIONAL DESCRIPTIONS

OPERATING INSTRUCTIONS

INSTRUCTION DESCRIPTIONS

PROGRAMMING INFORMATION

|            | REVISION RECORD                                               |

|------------|---------------------------------------------------------------|

| REVISION   | DESCRIPTION                                                   |

| 01         | Preliminary Edition                                           |

| (10-13-75) | ,                                                             |

| A          | Manual released. This edition obsoletes all previous editions |

| (6-17-77)  |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

| 1 -        |                                                               |

|            |                                                               |

| -          |                                                               |

|            |                                                               |

| ·          |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

|            |                                                               |

© 1975 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation

Publications & Graphics Division

3519 West Warner Avenue

Santa Ana, California 92704

or use Comment Sheet in the back of this manual.

74375500

# LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE                                                                     | REV              | PAGE | REV | PAGE | REV | PAGE | REV | PAGE | REV |

|--------------------------------------------------------------------------|------------------|------|-----|------|-----|------|-----|------|-----|

| Cover Title Page ii thru xii 1-1 thru 1-17 2-1 thru 2-44 3-1 thru        | -<br>A<br>A<br>A |      |     |      |     |      |     |      |     |

| 3-32<br>4-1 thru<br>4-53<br>5-1 thru<br>5-73<br>A-1 thru                 | A<br>A<br>A      |      |     |      |     |      |     |      |     |

| A-4 B-1 C-1 thru C-3 D-1 thru D-4 E-1, E-2 F-1 thru F-9 G-1, G-2 H-1 I-1 | A<br>A           |      |     |      |     |      |     |      |     |

| J-1<br>Index-1,-2                                                        | A<br>A           |      |     |      |     |      |     |      |     |

|                                                                          |                  |      |     |      |     |      |     |      |     |

|                                                                          |                  |      |     |      |     |      |     |      | -   |

|                                                                          |                  |      |     |      |     |      |     |      |     |

|                                                                          |                  |      |     |      |     |      |     |      |     |

# **PREFACE**

This manual describes the functional, operational and programming characteristics of the CONTROL DATA $^{\tiny (R)}$  2550-2 (MOS) Host Communications Processor (HCP). The manual also provides information on seven products which are used to expand the 2550-2 HCP capabilities. These products are the 2554-16 and 2554-32 Memory Expan-

sion Modules; 2556-2, 2556-3 and 2556-4 Communications Line Expansion Units; 2558-1 Communications Coupler, and 2571-1 Peripheral Controller.

The related publications listed below are available through the CDC Literature Distribution Services, Minneapolis, Minnesota.

| Publication                                                                                               | Publication Number |

|-----------------------------------------------------------------------------------------------------------|--------------------|

| 2550-2 (MOS) Host Communica-<br>tions Processor - Hardware<br>Maintenance Manual                          | 74701000           |

| 2550 Series Host Communications<br>Processor - Site Preparation Manual                                    | 74641200           |

| 2560-1/-2/-3 Synchronous Communi-<br>cations Line Adapters - Hardware<br>Reference and Maintenance Manual | 74700700           |

| 2561-1 Asynchronous Communications<br>Line Adapter - Hardware Reference<br>and Maintenance Manual         | 74700900           |

| 1714 Computer System - Reference Manual                                                                   | 60364900           |

| Basic Microprogrammable Processor -<br>Hardware Maintenance Manual                                        | 3945140            |

| CW212-A I/O TTY Controller -<br>Hardware Maintenance Manual                                               | 96728900           |

| DE402-A/1700 Transform with<br>Micromemory - Hardware Mainte-<br>nance Manual                             | 96728700           |

| AA109-A/B 1700 Enhanced Processor<br>with MOS Memory and Interface -<br>Hardware Maintenance Manual       | 96768600           |

| FAl04-A Tape Cassette Controller -<br>Hardware Maintenance Manual                                         | 96711900           |

74375500 A

2558-2 Communications Coupler 3000L - Hardware Reference/Maintenance Manual

60470400

6671/6676 Emulation Coupler - Hardware Reference/Maintenance Manual

74849600

# **CONTENTS**

|                               |      | /                                      |            |

|-------------------------------|------|----------------------------------------|------------|

| 1. SYSTEM DESCRIPTION         | 1-1  | Tape Cassette Transport and Controller | 1-15       |

| Introduction                  | 1-1  | Optional Peripherals and               |            |

| Host Interfacing Capability   | 1-1  | Controller                             | 1-15       |

| Communications Interfacing    |      | Communications Coupler                 | 1-15       |

| Capability                    | 1-1  | Main Data Paths                        | 1-15       |

| MP17 Communications Processor | 1-1  | Hari Bata raths                        | 1 1        |

| Main Memory Capacity          | 1-1  |                                        |            |

| Communications Console        | 1-1  | 2. FUNCTIONAL DESCRIPTIONS             | 2-1        |

| Optional Peripherals          | 1-3  | 2. FUNCTIONAL DESCRIPTIONS             | 2-1        |

| Physical Characteristics      | 1-3  | Communications Processor               | 2-1        |

| Communications Processor      | 1-3  |                                        | 2-1<br>2-1 |

| Microprocessor                | 1-3  | Microprocessor                         |            |

| · ·                           |      | Micromemory                            | 2-3        |

| Maintenance Panel             | 1-3  | Transform                              | 2-5        |

| Panel I/F, I/O TTY IF and     | 7 57 | Arithmetic and Logical Unit            | 2-6        |

| Cyclic Encoder                | 1-7  | Status Mode Interrupt                  | 2-9        |

| Main Memory                   | 1-7  | Real-time Clock                        | 2-15       |

| Communications Coupler        | 1-7  | Breakpoint                             | 2-15       |

| 6671/6676 Emulation Coupler   | 1-8  | Parity                                 | 2-16       |

| Multiplex Subsystem           | 1-8  | Maintenance Panel                      | 2-16       |

| Multiplex Loop Interface      |      | Maintenance Panel/Communica-           |            |

| Adapter                       | 1-8  | tions Console Interface                | 2-16       |

| Loop Multiplexer and Com-     |      | Panel Interface                        | 2-17       |

| munications Line Adapters     | 1-8  | I/O TTY Interface                      | 2-17       |

| Tape Cassette Transport and   |      | Cyclic Encoder                         | 2-17       |

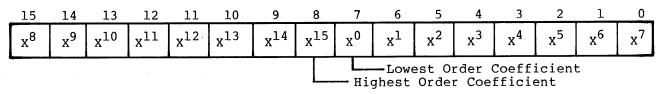

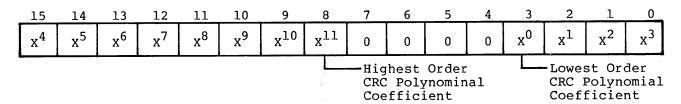

| Controller                    | 1-8  | A* Register                            | 2-18       |

| Wired Cabinet Assembly        | 1-11 | X* Register                            | 2-19       |

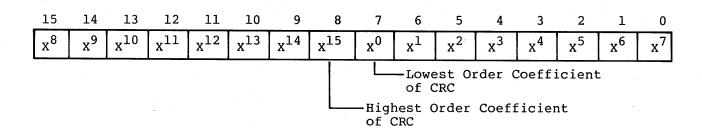

| Power Supplies                | 1-11 | CRC Format                             | 2-19       |

| Air Blower and Filter         |      | Sequence of Operation                  | 2-20       |

| Assemblies                    | 1-11 | Main Memory                            | 2-20       |

| Cabling                       | 1-11 | Memory Management System               | 2-22       |

| Power Requirements            | 1-11 | MOS Memory Interface - Data            | 2-22       |

| Functional Characteristics    | 1-11 | MOS Memory Interface -                 |            |

| Communications Processor      | 1-11 | Address/Control                        | 2-22       |

| Microprocessor                | 1-11 | Multiplex Subsystem                    | 2-23       |

| Maintenance Panel and         |      | Loop Transmission                      | 2-24       |

| Interface                     | 1-12 | Input Sequence                         | 2-24       |

| Communications Console        |      | Output Sequence                        | 2-25       |

| and Interface                 | 1-13 | Multiplex Loop Interface               |            |

| Cyclic Encoder                | 1-13 | Adapter                                | 2-25       |

| Main Memory                   | 1-13 | Input Functional Sequence              | 2-26       |

| Multiplex Subsystem           | 1-14 | Output Functional Sequence             | 2-26       |

| Loop Multiplexer              | 1-14 | MLIA Partitioning                      | 2-26       |

| Communications Line Adapter   | 1-14 | 1 01 01 01011119                       | 2 20       |

|                               |      |                                        |            |

74375500 A vii

| Loop Multiplexer Input Section                          | 2-29 | Start-up Procedure                           | 3-26    |

|---------------------------------------------------------|------|----------------------------------------------|---------|

| Output Section                                          | 2-29 | Operating Procedures                         | 3-26    |

|                                                         | 2-31 | Master Clear                                 | 3-26    |

| Communications Line Adapter<br>Tape Cassette Controller | 2-32 | Display FCR Contents                         | 3-26    |

| Interface                                               | 2-33 | Clear Bit in FCR                             | 3-27    |

|                                                         | 2-33 | Set Bit in FCR                               | 3-27    |

| CP Interface                                            | 2-33 | Change FCR in Hex Digit Mode                 | 3-27    |

| Deadstart Interface                                     | 2-33 | Change FCR in Bit Mode                       | 3-27    |

| Transport Interface                                     | 2-33 | Toggle Upper Indicator                       | 3-27    |

| Addressing and Operations                               | 2-33 | Display Register Defined                     |         |

| Data Transfer                                           | 2-34 | in Display O                                 | 3-28    |

| Write                                                   | 2-34 | Display Register Defined                     |         |

| Read                                                    | 2-35 | in Display l                                 | 3-28    |

| Echo                                                    | 2-36 | Load Register Defined                        |         |

| Auto-Data Transfer                                      | 2-36 | in Display 0                                 | 3-28    |

| Deadstart                                               | 2-37 | Load Register Defined                        |         |

| Reject Conditions                                       | 2-37 | in Display l                                 | 3-29    |

| Tape Cassette Transport                                 | 2-38 | Tape Cassette Autoload                       | 3-29    |

| Communications Coupler                                  | 2-38 | Card Reader Autoload                         | 3-29    |

| Host Computer Interface                                 | 2-41 | Host Computer Autoload                       | 3-30    |

| Internal Data Channel                                   |      | Start Processor                              | 3-30    |

| Interface                                               | 2-41 | Stop Processor                               | 3-30    |

| Memory Address Register                                 | 2-41 | Procedure Examples                           | 3-30    |

| Direct Memory Access                                    |      | Display Main Memory                          | 3-30    |

| Interface T                                             | 2-42 | Location                                     | 2-20    |

| Peripheral Controller                                   | 2-43 | Write into Main Memory                       | 3-30    |

| Controller/Microprocessor                               | _ 10 | Display P Register in                        | 3-31    |

| Interface                                               | 2-43 | Repeat Mode                                  | 2 21    |

| Controller/Line Printer                                 | 2 15 | Operation in Step Mode                       | 3-31    |

| Interface                                               | 2-43 | Load and Execute                             | 3-31    |

| Controller/Card Reader                                  | 2 45 |                                              | 2 2 2 3 |

| Interface                                               | 2-44 | Macroprogram                                 | 3-31    |

|                                                         | 2 33 | Emergency-Off Procedure                      | 3-32    |

|                                                         |      | Checks and Adjustments<br>Shutdown Procedure | 3-32    |

| 3. OPERATING INSTRUCTIONS                               | 3-1  | Shucdown Procedure                           | 3-32    |

| Control                                                 |      |                                              |         |

| Controls and Indicators                                 | 3-1  | 4. INSTRUCTION DESCRIPTIONS                  | 4-1     |

| Function Control Register                               | 3-1  |                                              |         |

| Function Control Register                               |      | Introduction                                 | 4 - 1   |

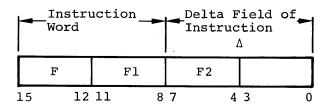

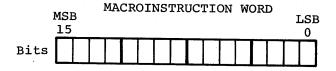

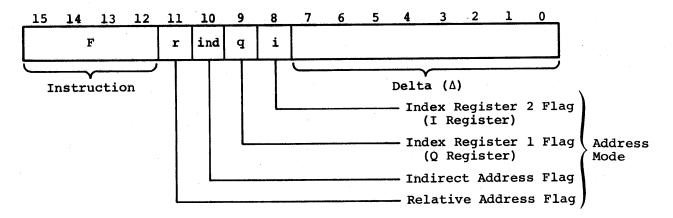

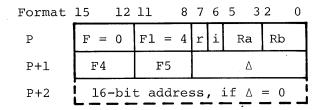

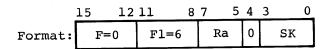

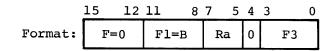

| Bit Definitions                                         | 3-1  | Macroinstruction Formats                     |         |

| Maintenance Panel                                       | 3-5  | and Descriptions                             | 4 - 1   |

| Communications Console                                  | 3-5  | Basic Macroinstructions                      | 4-1     |

| I/O TTY Interface Circuit Card                          |      | Storage Reference                            |         |

| Cyclic Encoder                                          | 3-14 | Instructions                                 | 4 - 1   |

| LM Printed Circuit Card                                 | 3-14 | Register Reference                           |         |

| Multiplex Loop Interface                                |      | Instructions                                 | 4-6     |

| Adapter                                                 | 3-14 | Enhanced Macroinstructions                   | 4-12    |

| MLIA-Processor Interface                                |      | Type 2 Storage Reference                     |         |

| Circuit Card                                            | 3-14 | Instructions                                 | 4-12    |

| MLIA-Input Loop Interface                               |      | Field Reference                              |         |

| Circuit Card                                            | 3-17 | Instructions                                 | 4-19    |

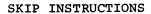

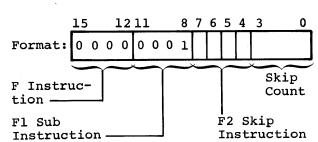

| MLIA-Output Loop Interface                              |      | Type 2 Skip Instructions                     | 4-20    |

| Circuit Card                                            | 3-17 | Decrement and Repeat                         | . 20    |

| Communications Coupler                                  | 3-17 | Instructions                                 | 4-20    |

| Micromemory                                             | 3-20 | Type 2 Interregister                         | . 20    |

| Tape Cassette Controller                                | 3-22 | Instructions                                 | 4-21    |

| Tape Cassette Transport                                 | 3-24 | Miscellaneous Instructions                   | 4-21    |

| Elapsed Time Indicators                                 | 3-24 | Auto-Data Transfer                           | - L     |

| Circuit Breakers and Fuses                              | 3-24 | Instructions                                 | 4-26    |

|                                                         |      |                                              | 0       |

Viii

| Macroinstruction Timing        | 4-29  | Input Memory Address         |               |

|--------------------------------|-------|------------------------------|---------------|

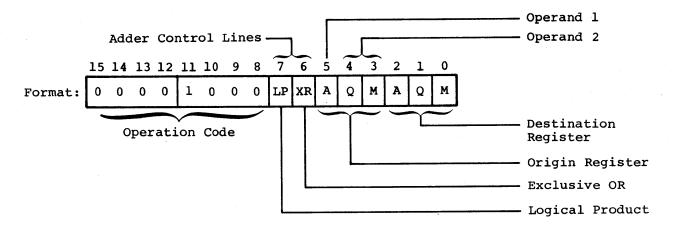

| Microinstruction Formats       | 4-29  | One (X001)                   | 5-25          |

| Microinstruction Descriptions  | 4-32  | Input Data (X003)            | 5-25          |

| M Field Operations             | 4-32  | Input CP Status (X004)       | 5-27          |

| F Field Operations             | 4-32  | Input Coupler Status (X005)  |               |

| Split Adder Option             | 4-32  | Input Order Word (X006)      | 5-27          |

| Logical Operations             | 4-32  |                              | 5-29          |

| Arithmetic Operations          | 4-32  | Input Program (X007)         | 5-29          |

| Overflow Capture Option        | 4-32  | Output Memory Address        |               |

| Shift Operations               |       | Zero (X101)                  | 5-29          |

| Scale Operations               | 4-34  | Output Memory Address        | -             |

|                                | 4-35  | One (X011)                   | 5-29          |

| A Input Operations             | 4-35  | Output Data (X014)           | 5-29          |

| A' Input Operations<br>B Codes | 4-37  | Output Program (X015)        | 5-30          |

|                                | 4-37  | Output Order Word (X016)     | 5-30          |

| B' Codes                       | 4-37  | CP Set/Sample Commands       | 5-31          |

| D Code Transfers               | 4-37  | Input Memory Address         |               |

| D' Code Transfers              | 4-37  | Zero (0600)                  | 5-31          |

| D" Code Transfers              | 4-37  | Input Memory Address (0610)  | 5-31          |

| DD" Codes                      | 4-37  | Input First/Present Char-    |               |

| T and T' Addressing Modes      | 4-43  | acter Displacement (0630)    | 5-31          |

| Subformat Select Bit           | 4-43  | Input CP Status (0640)       | 5-31          |

| S Field Codes                  | 4-43  | Input Coupler Status (0650)  | 5-31          |

| C Code Operations              | 4-43  | Input Order Word (0660)      | 5-31          |

| Microinstruction Timing        | 4-50  | Input I/O (0670)             |               |

|                                | - 00  | Input Last Word From Data    | 5-33          |

| 5. PROGRAMMING INFORMATION     | 5-1   |                              | F 22          |

|                                | J 1   | Channel (0604)               | 5-33          |

| Communications Processor       | 5-1   | Input FDMARO/FDMAR1 (0614)   | 5-33          |

| I/O Programming Requirements   |       | Input FDMARO/Flag            |               |

| Communications Console         | 5-1   | Mux (0624)                   | 5-33          |

|                                | 5-1   | Input FDMARO/Flag Mux/       |               |

| Control Signals                | 5-1   | Flag Register (0634)         | 5-33          |

| Addressing                     | 5-2   | Input Switch Status (0654)   | 5-33          |

| I/O Operations                 | 5-3   | Input Character (0674)       | 5-34          |

| Real-Time Clock                | 5-5   | Output Memory Address        |               |

| Interrupt System               | 5-7   | Zero (0608)                  | 5-34          |

| Logical Description            | 5-7   | Output FCD/PCD/LCD (0638)    | 5-34          |

| Interrupt System               |       | Output CP Status (0648)      | 5-34          |

| Programming                    | 5-9   | Output Buffer Length (0658)  | 5-34          |

| Program Protect                | 5-11  | Output Order Word (0668)     | 5-34          |

| Program Protect Violations     | 5-11  | Clear Coupler (060C)/        | 3 34          |

| Set/Clear Program Protect      |       | CP Master Clear              | 5-34          |

| Bit                            | 5-12  | Terminate Transfer (061C)    | 5-34          |

| Programming Requirements       | 5-12  | Output Test (064C)           | 5-35          |

| Peripheral Equipment           |       |                              |               |

| Protection                     | 5-12  | Input Test (065C)            | 5-35          |

| Instruction Summary            | 5-12  | Output Memory Address (066C) | 5-35          |

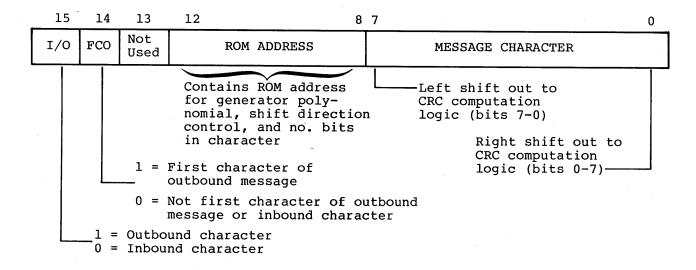

| Cyclic Encoder                 | 5-19  | Output Character (067C)      | 5-35          |

| Introduction                   | 5-19  | CP Interrupts                | 5-35          |

| Characteristics                |       | Tape Cassette Controller     | 5-35          |

|                                | 5-19  | Control Functions            | 5-35          |

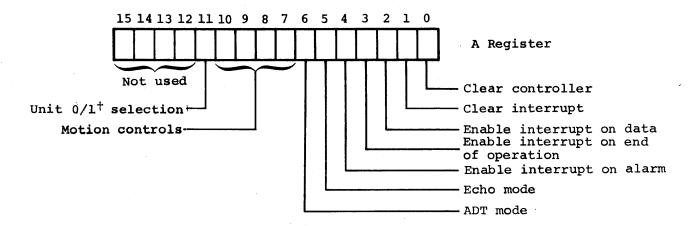

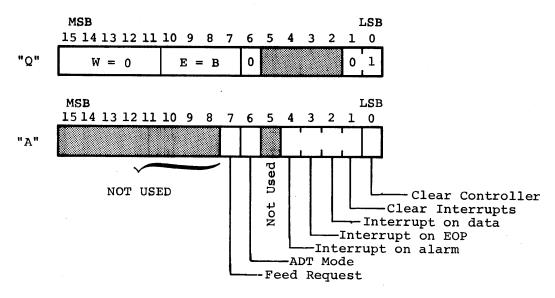

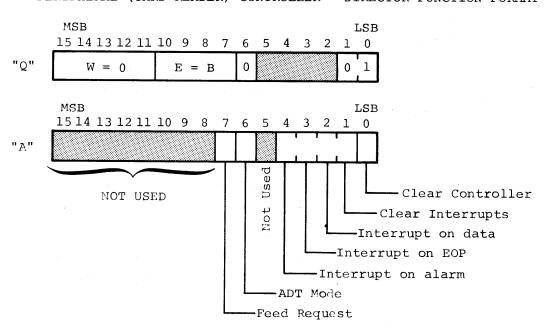

| Communications Coupler         | 5-23  | Clear Controller             | 5-36          |

| PPU Functions                  | 5-23  | Clear Interrupt              | 5 <b>-</b> 36 |

| Clear Coupler (X400)/PPU       |       | Enable Interrupt on Data     | 5-37          |

| Master Clear                   | 5-24  | Enable Interrupt on End      |               |

| Master Clear                   | 5-24  | of Operation                 | 5-37          |

| Stop CP (X100)                 | 5-24  | Enable Interrupt on Alarm    | 5-37          |

| Start CP (X040)                | 5-24  | Echo Mode                    | 5-37          |

| Input Memory Address           |       | ADT Mode                     | 5-37          |

| Zero (X000)                    | 5-25  | Search Tape Mark (Reverse)   | 5-37          |

|                                | 300 m | (1000EDC)                    | J J I         |

74375500 A

| Search Tape Mark (Forward)<br>Write Tape Mark<br>Write One Record<br>Backspace<br>Rewind | 5-37<br>5-37<br>5-38<br>5-38<br>5-38 | Multiplex Subsystem Loop Cell Arrangement Loop Batches CLA | 5-55<br>5-55<br>5-55 |

|------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------|----------------------|

| Erase                                                                                    |                                      | Loop Multiplexer                                           | 5-55                 |

|                                                                                          | 5-38                                 | Input Loop                                                 | 5-55                 |

| Read One Record                                                                          | 5-38                                 | Input Loop Restart                                         | 5-58                 |

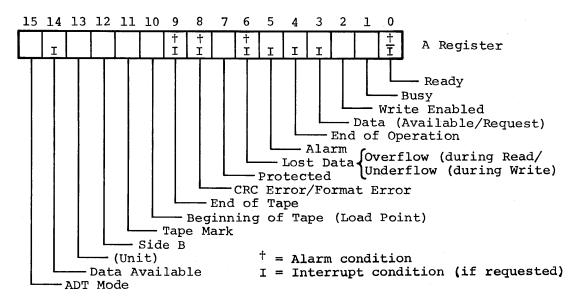

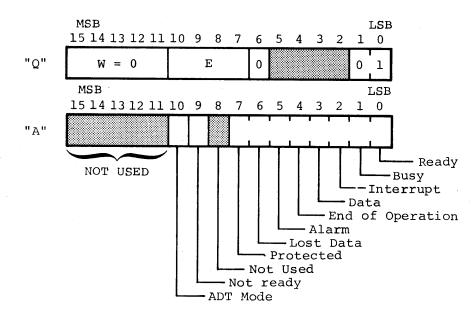

| Status                                                                                   | 5-38                                 | Output Loop                                                | 5-58                 |

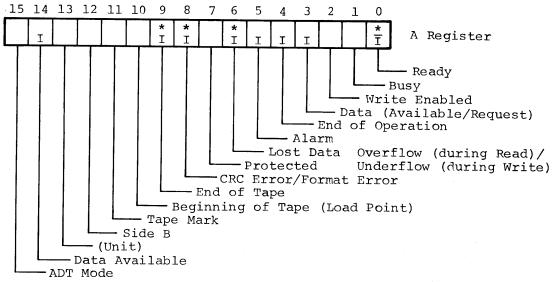

| Ready                                                                                    | 5-39                                 | Redundant Operation                                        | 5-58                 |

| Busy                                                                                     | 5-39                                 | Loop Multiplexer to CLA Logic                              |                      |

| Write Enable                                                                             | 5-39                                 | Signal Definitions (Input)                                 | 5-59                 |

| Data (Available/Request)                                                                 | 5-39                                 | Loop Multiplexer to CLA Logic                              |                      |

| End of Operation                                                                         | 5-39                                 | Signal Definitions (Output)                                | 5-60                 |

| Alarm                                                                                    | 5-39                                 | OSL - Output Select                                        | 5-60                 |

| Lost Data                                                                                | 5-39                                 | OSC - Output Select Clear                                  | 5-60                 |

| Protected                                                                                | 5-40                                 | OF1, OF2, OF3 - Output                                     |                      |

| Cyclic Redundancy Checksum                                                               | - 40                                 | Format                                                     | 5-60                 |

| (CRC) Error/Format Error                                                                 | 5-40                                 | IO1 to IO8 - Information                                   |                      |

| End of Tape                                                                              | 5-40                                 | Output                                                     | 5-60                 |

| Beginning of Tape (Load                                                                  |                                      | OST - Output Strobe                                        | 5-60                 |

| Point)                                                                                   | 5-40                                 | OER - Output Error                                         | 5-60                 |

| Tape Mark                                                                                | 5-40                                 | Multiplex Loop Interface                                   |                      |

| Side B                                                                                   | 5-40                                 | Adapter                                                    | 5-60                 |

| Unit 1                                                                                   | 5-40                                 | Channel Addressing                                         |                      |

| Data Available                                                                           | 5-40                                 | (Q Register)                                               | 5-60                 |

| Auto Data Transfer Mode                                                                  | 5-41                                 | CDC 1700-AQ Channel                                        | 5-60                 |

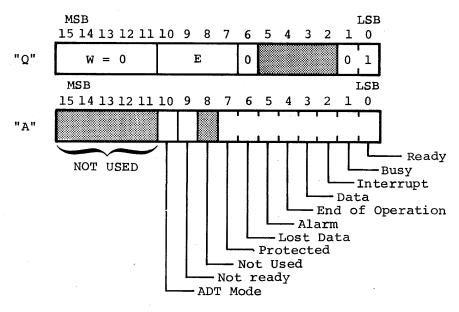

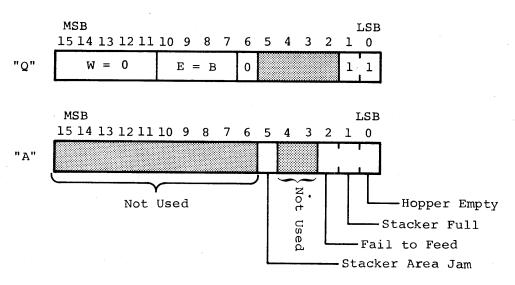

| Peripheral Controller                                                                    | 5-41                                 | AQ Channel Output Operations                               |                      |

| Card Reader Controller Oper-                                                             |                                      | AQ Channel Input Operations                                | 5-66                 |

| ating Characteristics                                                                    | 5-41                                 | DMA/Device Interface                                       | 5-69                 |

| Addressing                                                                               | 5-41                                 | DMA Channel Input                                          |                      |

| Program Protect                                                                          | 5-41                                 | Operations                                                 | 5-71                 |

| Director Functions                                                                       | 5-41                                 | DMA Channel Output                                         |                      |

| Director Status 1                                                                        | 5-43                                 | Operations                                                 | 5-71                 |

| Director Status 2                                                                        | 5-44                                 | Interrupts                                                 | 5-71                 |

| Data Transfers                                                                           | 5-45                                 | CP Interrupt System                                        | 5-71                 |

| Line Printer Controller                                                                  |                                      | Interrupt Implementation                                   | 5-72                 |

| Operating Characteristics                                                                | 5-47                                 | Program Interrupts                                         | 5-72                 |

| Addressing                                                                               | 5-47                                 | Output Data Demand                                         |                      |

| Program Protect                                                                          | 5-47                                 | Interrupts                                                 | 5-72                 |

| Director Function                                                                        | 5-47                                 | Input Line Frame Interrupts                                | 5-72                 |

| Director Status                                                                          | 5-51                                 | Communications Line Adapters                               | 5-73                 |

| Data Transfers                                                                           | 5-53                                 | _                                                          |                      |

| Control Characters                                                                       | 5-53                                 |                                                            |                      |

|                                                                                          |                                      |                                                            |                      |

|                                                                                          |                                      |                                                            |                      |

|                                                                                          | APPE                                 | NDIX                                                       |                      |

| A Mnemonics Listing                                                                      | A-1                                  | E Type 2 Storage Reference                                 |                      |

| B Hexadecimal/Decimal                                                                    |                                      | Instructions                                               | E-1                  |

| Conversion                                                                               | B-1                                  |                                                            |                      |

| C Functional Listing of                                                                  |                                      | G Auto-Data Transfer (ADT                                  |                      |

| Macroinstructions                                                                        | C-1                                  | Mode Formats                                               | G-1                  |

| D Numeric Listing of                                                                     |                                      | H Status Mode Bit Assignments                              | H-1                  |

| Macroinstructions                                                                        | D-1                                  | I Interrupt Bit Assignments                                | I-1                  |

|                                                                                          |                                      | J Interrupt and Equipment                                  | <br>.T-1             |

# INDEX

# **FIGURES**

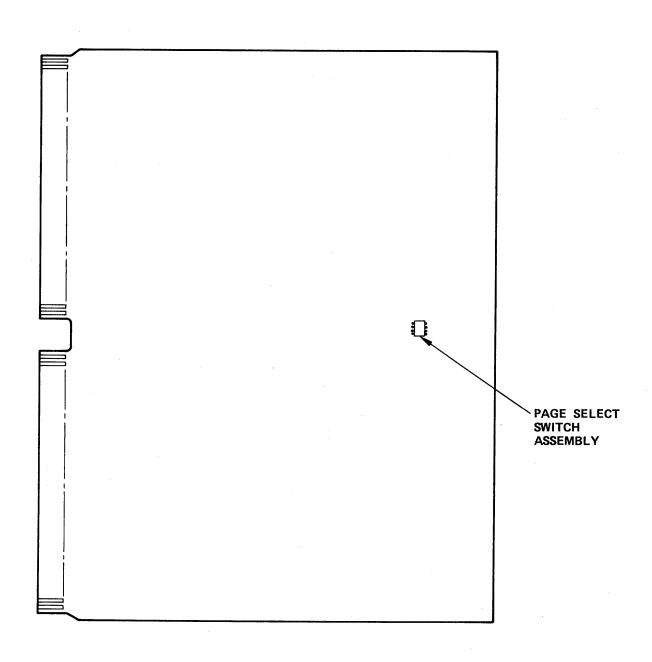

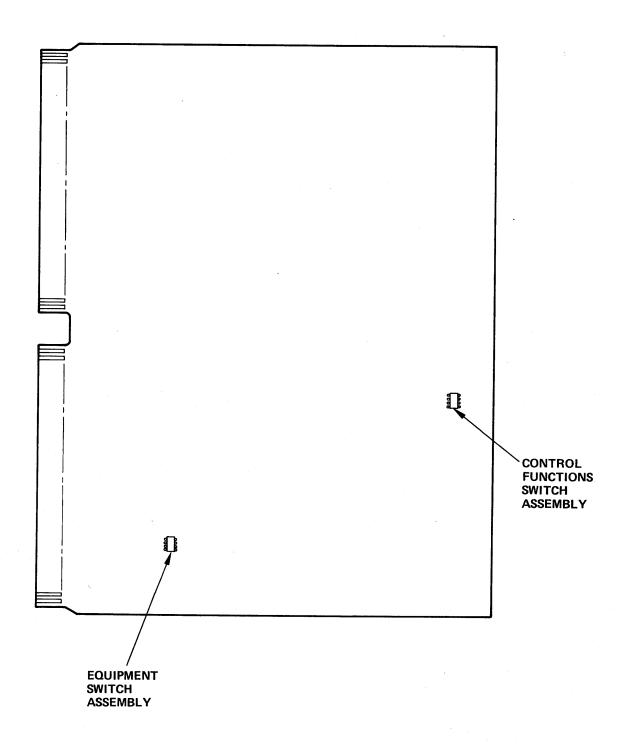

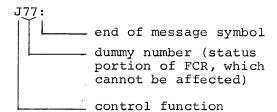

| 1-1          | 2550-2 Host Communications<br>Processor, Block | 5       | 3-7          | MLIA, Output Loop Inter- |              |

|--------------|------------------------------------------------|---------|--------------|--------------------------|--------------|

|              | Diagram                                        | 1-2     |              | face Circuit Card -      |              |

| 1-2          | 2550-2 Host Communications                     | 1 2     | 3-8          | Indicators               | 3-18         |

|              | Processor, Front View                          | 1-4     | 3-8          | Communications Coupler,  |              |

| 1-3          | 2550-2 Host Communications                     | T 4     |              | Host Interface Circuit   |              |

|              | Processor, Side View                           | 1-5     |              | Card - Controls and      |              |

| 1-4          | Communications Processor                       | 1-2     | 2 0          | Indicators               | 3-19         |

|              | Card Cage Assembly                             | 7 (     | 3-9          | Micromemory Circuit      |              |

| 1-5          | CP Card Cage Configuration                     | 1-6     | 2 7 0        | Card - Controls          | 3-21         |

|              | for 2550-100/2558-2                            | ~       | 3-10         | Tape Cassette Controller |              |

|              | Emulation Couplers                             | 7 0     | 2 7 7        | - Controls               | 3-23         |

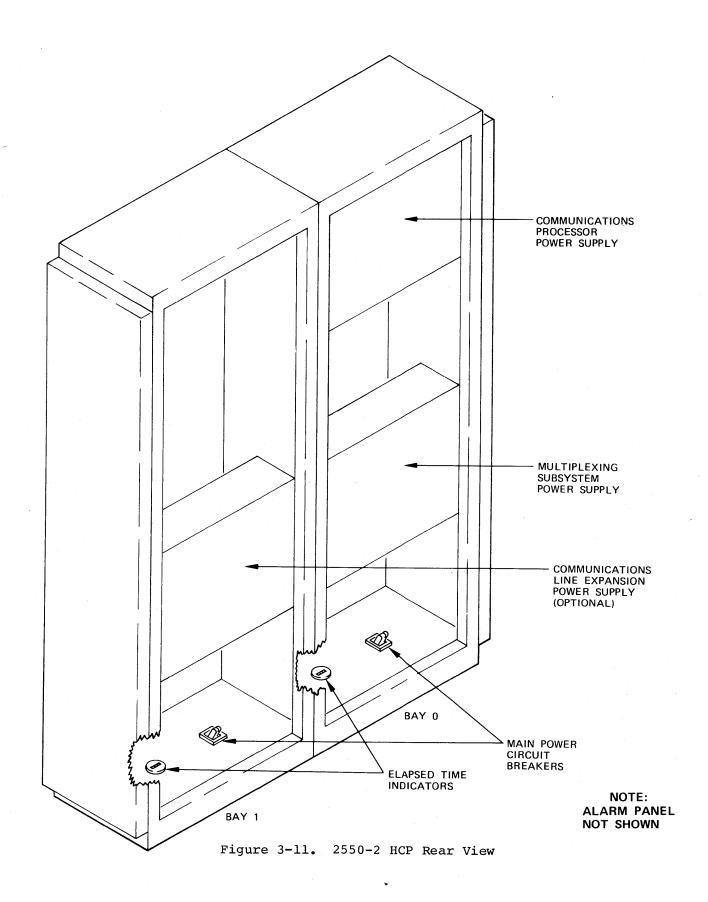

| 1-6          | Indiation of Lon Multi                         | 1-9     | 3-11         | 2550-2 HCP Rear View     | 3-25         |

| T-0          | Location of Loop Multi-                        |         | 4-1          | Storage Reference        |              |

|              | plexer and Typical Com-                        |         |              | Instructions Format      | 4-2          |

| 1-7          | munications Line Adapter                       | T-T0    | 4-2          | Interregister Instruc-   |              |

|              | 2550-2 HCP Main Data Paths                     | T-T6    |              | tions Format             | 4 <b>–</b> 8 |

| 2-1          | Detailed Microprocessor                        |         | 4-3          | Microinstruction Formats | 4-30         |

| 2 2          | Block Diagram                                  | 2-2     | 4 - 4        | Microinstruction Classi- |              |

| 2-2          | Maintenance Panel/Commu-                       |         |              | fication                 | 4-52         |

|              | nications Console Inter-                       |         | 4 <b>-</b> 5 | Calculation of Micro-    | *            |

|              | face, Block Diagram                            | 2-16    |              | program Sequence         |              |

| 2-3          | A* Word Format (11th                           |         |              | Execution Time           | 4-53         |

|              | Degree Generator                               |         | 5-1          | Q Register - Address     |              |

|              | Polynomial)                                    | 2-18    |              | Format                   | 5-2          |

| 2-4          | A* Word Format (12th                           | :       | 5 <b>-</b> 2 | Q Register - Command     |              |

|              | Degree Generator                               |         |              | Format                   | 5-3          |

|              | Polynomial)                                    | 2-18    | 5 <b>-</b> 3 | A Register - Data Format | 5-3          |

| 2 <b>-</b> 5 | X* Word Format                                 | 2-19    | 5-4          | Q Register - I/O Address |              |

| 2-6          | CRC Word Format (16th                          |         |              | Format                   | 5-3          |

|              | Degree Generator                               |         | 5 <b>-</b> 5 | Storage Reference        | 5-12         |

|              | Polynomial)                                    | 2-19    | 5-6          | Register Reference       | 5-13         |

| 2-7          | CRC Word Format (12th                          |         | 5-7          | SKIP Format              | 5-13         |

|              | Degree Generator                               |         | 5-8          | SHIFT Format             | 5-13         |

|              | Polynomial)                                    | 2-20    | 5-9          | Interregister Format     | 5-13         |

| 2-8          | Communications Coupler                         |         | 5-10         | Field Reference          | 5-14         |

|              | Block Diagram                                  | 2-39    | 5-11         | Miscellaneous            | 5-14         |

| 3-1          | Maintenance Panel - Con-                       |         | 5-12         | A* Register Word Format  | 2 14         |

|              | trols and Indicators                           | 3-6     |              | (16th Degree Generator   |              |

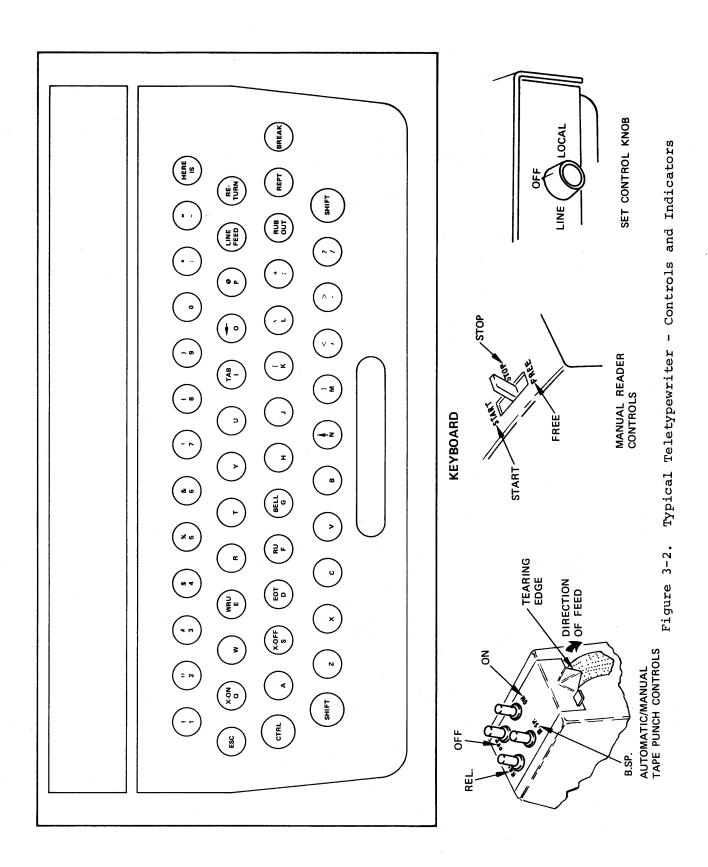

| 3-2          | Typical Teletypewriter -                       |         |              | Polynomial)              | 5-21         |

|              | Controls and Indicators                        | 3-11    | 5-13         | A* Register Word Format  | J 21         |

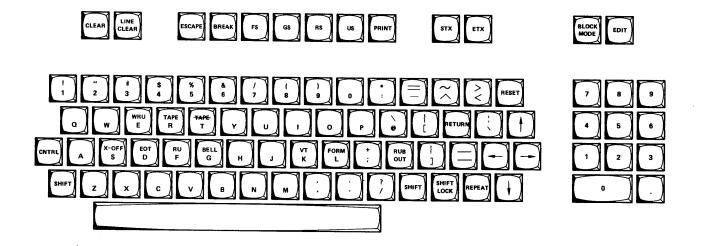

| 3-3          | Typical Cathode Ray Tube                       |         |              | (12th Degree Generator   |              |

|              | Conversational Display -                       |         |              | Polynomial)              | 5-21         |

|              | Controls and Indicators                        | 3-12    | 5-14         | X* Register Word Format  | 5-22         |

| 3-4          | I/O TTY Interface Circuit                      | J 12    | 5-15         | CRC Word Format          | 3-22         |

|              | Card - Controls                                | 3-13    | 3 13         | (16th Degree Generator   |              |

| 3 <b>-</b> 5 | Typical Circuit Card -                         | 3 13    |              | Polynomial)              | F 22         |

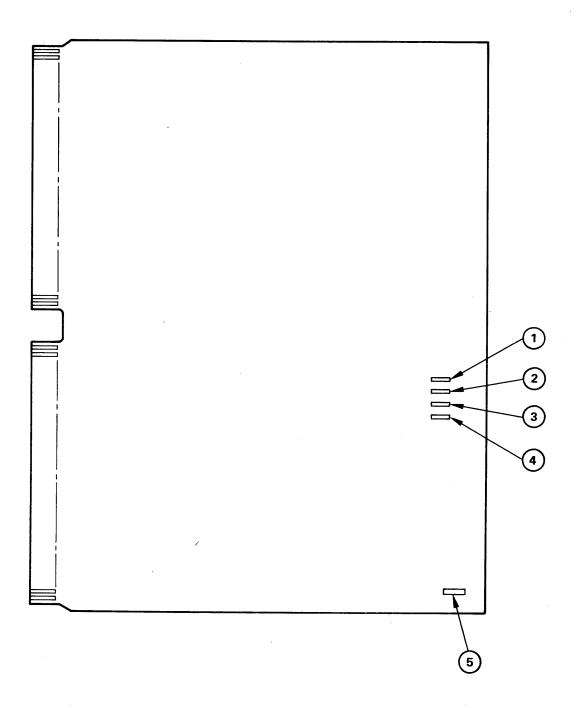

| -            | Power Indicator                                | 3-15    | 5-16         | CRC Word Format (12th    | 5-22         |

| 3-6          | Loop Multiplexer Circuit                       | 5 15    | 2 10         | Degree Generator         |              |

| . •          | Card - Controls and                            |         |              | Polynomial)              | E . 2 2      |

|              | Indicators                                     | 3-16    | 5-17         | PPU Function Code        | 5-23         |

|              |                                                | J _ 1 U | J 11         | TTO TUILCUTOIL COUR      | 5-24         |

74375500 A

| 2-10 | CP Data Bullet Format      | 5-26          | 5-29         | True brinter priector      |        |

|------|----------------------------|---------------|--------------|----------------------------|--------|

| 5-19 | Coupler Status Format      | 5-27          |              | Functions                  | 5-47   |

| 5-20 | CP Set/Sample Instruction  |               | 5-30         | Auto-Data Transfer         |        |

|      | Format                     | 5-32          |              | Mode Format                | 5-49   |

| 5-21 | Status Bit Configuration   | 5-33          | 5-31         |                            | 5 17   |

|      | Control Europiana Crossi   | 5-33          | 2-21         | Printer Status Responses   | 1      |

| 5-22 | Control Functions Speci-   |               |              | Format                     | 5-51   |

|      | fied by A Register         | 5-36          | 5-32         | Printer Data Transfer      |        |

| 5-23 | Status Responses           | 5 <b>-</b> 38 |              | Command Format             | 5-53   |

| 5-24 | Card Reader Director       |               | 5-33         | Line Printer Controller    |        |

|      | Functions                  | 5-42          |              | Spacing Control            |        |

| 5-25 | Director Status 1          |               |              | Characters                 | 5-54   |

|      | Responses                  | 5-43          | 5-34         | Format of Loop Cells       | 5-56   |

| 5-26 | Director Status 2          | 3 13          | 5-35         | Input Loop Batch and       | 5 50   |

| J 20 |                            | E 1E          | 5-35         |                            | E E 7  |

| E 27 | Responses                  | 5-45          | F 26         | Line Frame Structure       | 5-57   |

| 5-27 | Data Transfer Command      | 5-45          | 5-36         | MLIA Commands              | 5-61   |

| 5-28 | Test Mode Command          | 5-46          | 5-37         | Read Status Format         | 5-67   |

|      |                            | TABL          | E S          |                            |        |

| 1-1  | Communications Line        |               |              | Instruction Addressing     | 4-4    |

|      | Expansion Options          | 1-1           | 4-2          |                            | 44     |

| 1-2  |                            |               | 4-2          | Inter-Register Instruc-    | 4 0    |

|      | MOS Memory Capacity        | 1-7           | 4 0          | tion Truth Table           | 4-9    |

| 1-3  | HCP Functional Features    | 1-12          | 4-3          | Type 2 Storage Address-    |        |

| 2-1  | Status Mode Register       |               |              | ing Relationships          | 4-15   |

|      | Bit Assignments            | 2-10          | 4 - 4        | M Field Operations         | 4-33   |

| 2-2  | Operating Mode Bits        | 2-11          | 4-5          | Logical Operations         | 4-33   |

| 2-3  | Event Occurrence Bits      | 2-13          | 4-6          | Arithmetic Operations      | 4-34   |

| 2-4  | Control and Timing         |               | 4-7          | Shift Operations           | 4-36   |

|      | Driver Bits                | 2-13          | 4-8          | Scale Operations           | 4-36   |

| 2-5  | Status Mode Register       |               | 4-9          | A Input Operations         | 4-38   |

|      | Flag Bits                  | 2-13          | 4-10         |                            | 4-38   |

| 2 (  | 2                          |               |              | A' Input Operations        |        |

| 2-6  | Interrupt Bit Assignments  | 2-14          | 4-11         | B Codes                    | 4-39   |

| 2-7  | Timing Differences for     |               | 4-12         | B' Codes                   | 4 - 40 |

|      | Fast-Access and Slow-      |               | 4-13         | D Code Transfers           | 4 - 40 |

|      | Access MOS Memory          |               | 4-14         | D' Code Transfers          | 4 - 41 |

|      | Elements                   | 2-21          | 4-15         | D" Code Transfers          | 4 - 42 |

| 2-8  | Tape Cassette Controller   |               | 4-16         | DD" Codes                  | 4-42   |

|      | Operation Selection        | 2-33          | 4 - 17       | T Addressing Modes         | 4-44   |

| 3-1  | Function Control Regis-    |               | 4-18         | T' Addressing Modes        | 4-45   |

|      | ter - Bit Definitions      |               | 4-19         | S Field Codes              | 4-46   |

|      | and Digit Functions        | 3-2           | 4-20         | C Code Operations          | 4-47   |

| 3-2  |                            | J 2           |              |                            | 4-4/   |

| 3-2  | Function Control Regis-    |               | 4-21         | Microinstruction           | 4 - 7  |

|      | ter - Display Code         | 2 2           |              | Execution Times            | 4-51   |

|      | Definitions                | 3-3           | 5-1          | ADT Table for the Clock    | 5-6    |

| 3-3  | Maintenance Panel Controls |               | 5-2          | Interrupt State            |        |

|      | and Indicators             | 3-7           |              | Definitions                | 5-8    |

| 3-4  | Control Character Code/    |               | 5-3          | Interrupt Priority Levels  | 5-10   |

|      | Functions                  | 3-9           | 5-4          | Macro Instruction Mnemonic |        |

| 3-5  | Switch Settings - I/O TTY  |               | -            | Summary and Execution      |        |

|      | Interface Circuit Card     | 3-14          |              | Times                      | 5-15   |

| 3-6  | Switch Settings - Com-     | 2 14          | 5-5          |                            | J T.J  |

| 3-0  |                            |               | 5-5          | Generator Polynomial       | F 20   |

|      | munications Coupler Host   | 2 20          | F 6          | Addresses and Format       | 5-20   |

|      | Interface Circuit Card     | 3-20          | 5-6          | Coupler Status Set/Clear   |        |

| 3-7  | Switch Settings - Micro-   |               |              | Condition                  | 5-28   |

|      | memory Page Select         | 3-20          | 5 <b>-</b> 7 | Tape Cassette Control-     |        |

| 3-8  | Control Functions (S2) -   |               |              | ler - Motion Controls      | 5-36   |

|      | Tape Cassette              |               | 5-8          | Q Register Command Code    | 5-41   |

|      | Controller                 | 3-22          | 5-9          | Printer Options            | 5-48   |

| 4-1  | Storage Reference          |               | 5-10         | DMA Signal Line Usage      | 5-70   |

74375500 A

# **INTRODUCTION**

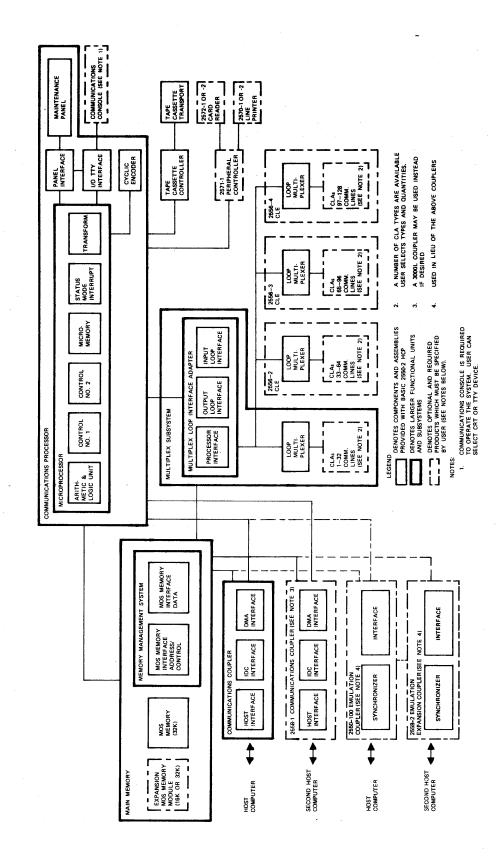

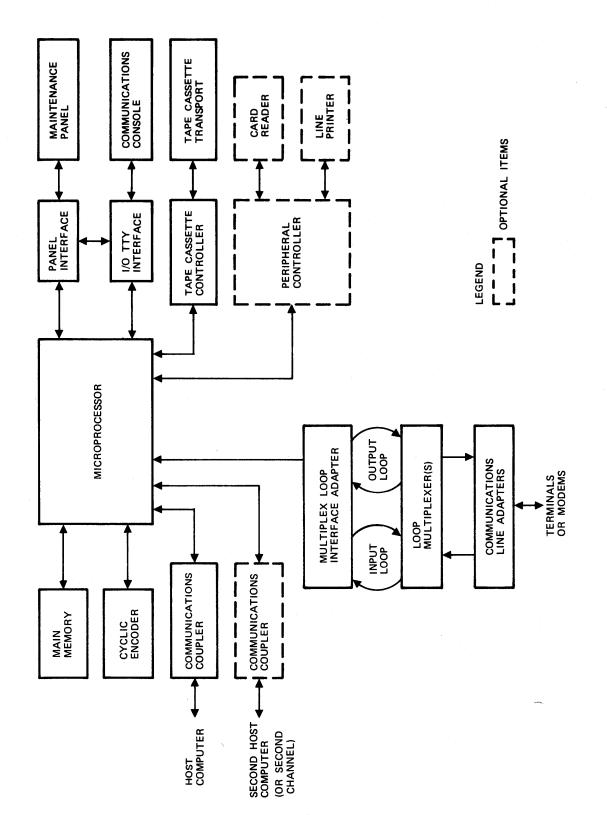

The 2550-2 HCP is a medium-size, digital, data communications system that serves as a communications front-end to a CONTROL DATA® 6000, CYBER 70, CYBER 170, or a lower 3000 series host computer. The 2550-2 HCP also interfaces with selected terminal devices. See block diagram, figure 1-1.

### HOST INTERFACING CAPABILITY

The 2550-2 HCP normally interfaces with one host computer. However, by adding a 2558-1 communications coupler to the system, the HCP can interface either with a second host computer, or with another channel of the same host.

The 3000L coupler is available to interface the 2550-2 HCP with the CDC 3000L series processor. See preface.

The 2550-100 emulation module and the 2558-2 emulation coupler used with the 2550-2 HCP emulates multiples of the 6671 and 6676 data set controllers without host software modifications. See figure 1-1.

# COMMUNICATIONS INTERFACING CAPABILITY

The 2550-2 HCP provides multiplexer capabilities to interface as many as 32 communications line adapters (CLAs). This interfacing capability can be expanded to as many as 128 CLAs by adding 2556-2, -3, and -4 communications line expansion (CLE) units. Each CLE configuration provides multiplexer capacity to interface 32 additional CLAs. A variety of CLA types are available for use with the HCP, as required. See table 1-1.

TABLE 1-1. COMMUNICATIONS LINE EXPANSION OPTIONS

| Incre- | Configuration    | Number of<br>CLAs to be<br>Interfaced |

|--------|------------------|---------------------------------------|

| 1      | Basic 2550-2 HCP | 1-32                                  |

| 2      | Add 2556-2 CLE   | 33-54                                 |

| 3      | Add 2556-3 CLE   | 65-96                                 |

| 4.     | Add 2556-4 CLE   | 97-128                                |

#### MP17 COMMUNICATIONS PROCESSOR

The 2550-2 HCP contains an MP17 communications processor (CP). The MP17 CP is a modified MP16 computer frame and associated modules. The MP17 transform module (and 1700 emulation controlware stored on it) effects the conversion to MP17. Several special purpose modules were added to accommodate the 2550 HCP configuration.

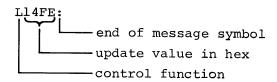

#### MAIN MEMORY CAPACITY

The main MOS memory for the 2550-2 HCP holds 32,768 16-bit words. This capacity can be expanded to 49,152 words by addition of a 2554-16 memory expansion module or to 65,536 words by addition of a 2554-32 memory expansion module.

#### COMMUNICATIONS CONSOLE

A communications console is required to operate the HCP, and the user can select from either a number of commercially-available teletypewriters (TTYs) or cathode ray tube (CRT) conversational display terminals for this purpose. The 713-10 CRT or the 1711-4, -5 and 1713-4, -5 TTYs are compatible with the 2550-2 HCP.

2550-2 Host Communications Processor, Block Diagram Figure 1-1.

The 713-10 Conversational Display Terminal is a desktop unit containing a CRT display and a keyboard. The unit operates at variable speeds up to 1200 characters per second (9600 baud).

The 1711-4 and -5 TTYs are capable of operating in the keyboard sendreceive (KSR) mode only. The 1713-4 and -5 TTYs contain paper-tape punches and decoders, and are capable of automatic send-receive (ASR) operations, as well as KSR operation.

#### **OPTIONAL PERIPHERALS**

The addition of a 2571-1 Peripheral Controller to the system enables the HCP to receive input from a card reader and provide output to a line printer. Either a 2572-1, or 2572-2 Card Reader may be used with the 2550-2 HCP. These units are identical except that the 2572-1 Card Reader operates at a speed of 300 cards per minute, while the 2572-2 configuration reads 600 cards per minute. The 2550-2 HCP is also compatible with either the 2570-1 or the 2570-2 Line Printers. The 2570-1 unit employs a drum-printing mechanism and prints 300 lines per minute; the 2570-2 configuration contains a train-printing mechanism and prints 1200 lines per minute.

# PHYSICAL CHARACTERISTICS

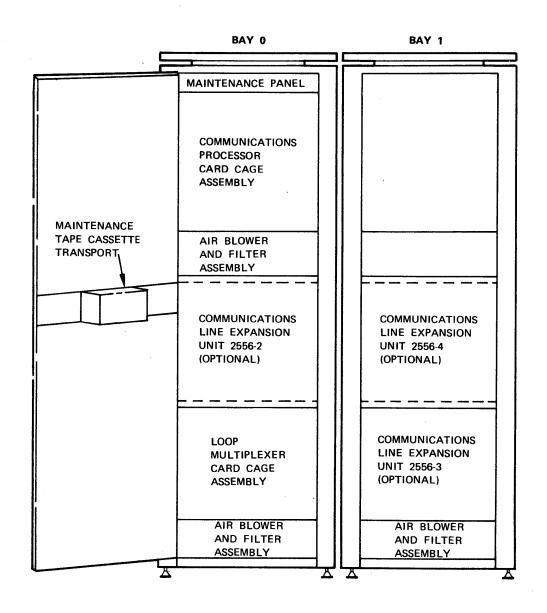

A front view of the HCP is shown as figure 1-2, and a side view as figure 1-3.

The major system components of the 2550-2 HCP are listed below:

- Communications Processor 1.

- 2. Main Memory

- 3. Multiplex Subsystem

- Tape Cassette Transport and Controller

- 5. Communications Coupler

- 6. Wired Cabinet Assembly

- 7. Communications Console

- Optional Peripherals and Controller

#### COMMUNICATIONS PROCESSOR

The communications processor (CP) contains the following assemblies and components:

- Microprocessor

- 2. Maintenance Panel

- 3. Maintenance Panel Interface

- 4. I/O TTY Interface

- Cyclic Encoder

#### Microprocessor

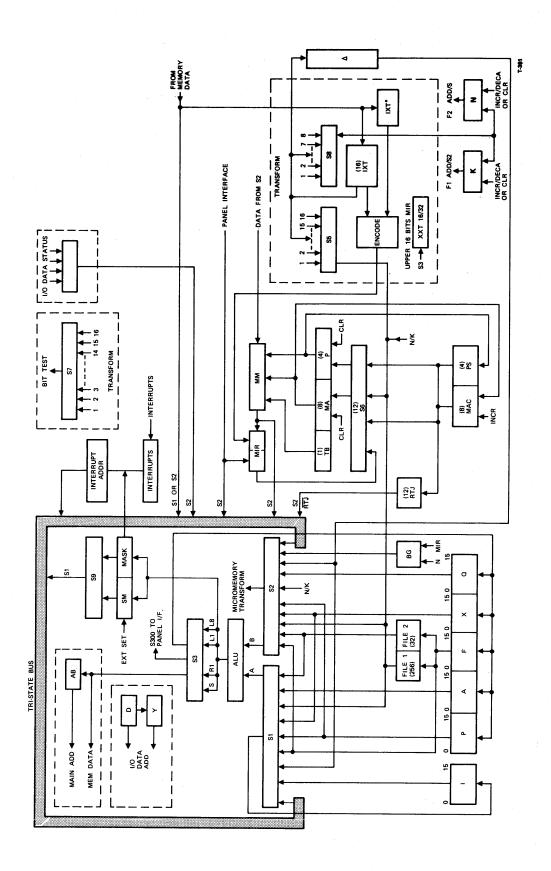

The microprocessor contains the following six printed circuit cards which are located in the slots indicated within the CP card cage assembly. See figure 1-4.

| Card<br>Slot | Printed Circuit Card<br>Nomenclature |

|--------------|--------------------------------------|

| М            | Arithmetic and Logic Unit (ALU)      |

| P            | Control No. 1                        |

| N            | Control No. 2                        |

| ${f T}$      | Micromemory                          |

| $\mathbf{L}$ | Status Mode Interrupt                |

| R            | 1700 Transform                       |

Each of these circuit cards is 11 in. x 14 in. (28 cm x 36 cm). These cards contain the circuitry which performs the various arithmetic and logic operations which control the flow of data through the HCP system.

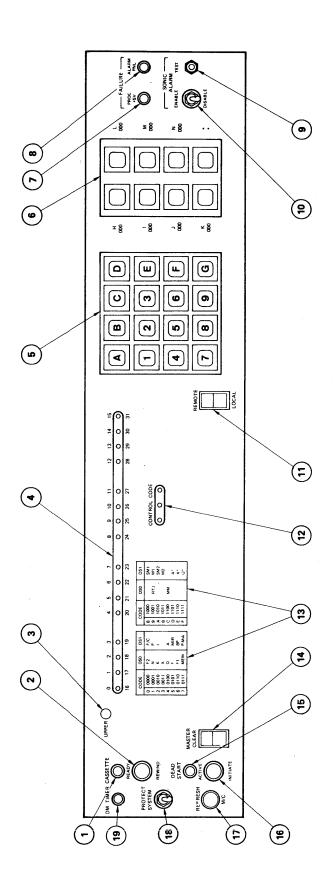

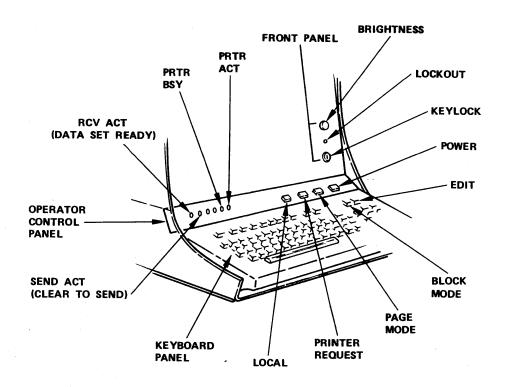

#### Maintenance Panel

As shown in figure 1-2, the maintenance panel is located above the CP card cage assembly in Bay 0. Maintenance panel controls and indicators are described in section 3. The maintenance panel is illustrated in figure 3-1.

Figure 1-2. 2550-2 Host Communications Processor, Front View

Figure 1-3. 2550-2 Host Communications Processor, Side View

EXPANSION (OPTIONAL)

PRIMARY (STANDARD)

| COMMUNICATIONS COUPLER (HOST I/F)  COMMUNICATIONS COUPLER (IDC I/F)  COMMUNICATIONS COUPLER (DMA I/F) | A AB    |

|-------------------------------------------------------------------------------------------------------|---------|

|                                                                                                       | 4       |

| COMMUNICATIONS COURLED (DMA 1/E)                                                                      | <b></b> |

| COMMONICATIONS COOPLER (DIVIA 1/F)                                                                    | ∢       |

| COMMUNICATIONS COUPLER (HOST I/F)                                                                     | 89      |

| COMMUNICATIONS COUPLER (IDC I/F)                                                                      | ပ       |

| COMMUNICATIONS COUPLER (DMA I/F)                                                                      | ٥       |

| MLIA-1 (INPUT LOOP I/F)                                                                               | ш       |

| MLIA-2 (OUTPUT LOOP I/F)                                                                              | L.      |

| MLIA-3 (PROCESSOR I/F)                                                                                | 9       |

| TAPE CASSETTE CONTROLLER                                                                              | I       |

| 2571-1 PERIPHERAL CONTROLLER                                                                          | 7       |

| I/O TTY INTERFACE                                                                                     | ¥       |

| STATUS MODE INTERRUPT                                                                                 |         |

| ARITHMETIC AND LOGIC UNIT                                                                             | Σ       |

| CONTROL 2                                                                                             | Z       |

| CONTROL 1                                                                                             | ٩       |

| 1700 TRANSFORM (W/EMULATOR ROM)                                                                       | æ       |

| CYCLIC ENCODER                                                                                        | တ       |

| MICROMEMORY (2K)                                                                                      | _       |

| PANEL INTERFACE                                                                                       | n       |

| MOS MEMORY INTERFACE - DATA                                                                           | >       |

| MOS MEMORY INTERFACE - ADDRESS/CONTROL                                                                | ≥       |

| MOS MEMORY (32K)                                                                                      | ×       |

| EXPANSION MOS MEMORY MODULE (16K OR 32K)                                                              | >       |

| (NOT USED)                                                                                            | Z       |

| (NOT USED)                                                                                            | AC      |

Figure 1-4. Communications Processor Card Cage Assembly

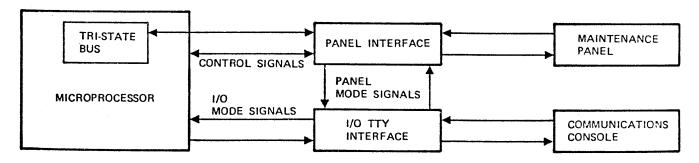

# Panel I/F, I/O TTY I/F, and Cyclic Encoder

Three additional printed circuit cards are used in the CP for the basic 2550-2 configuration. These cards are 11 in. x 14 in. (28 cm x 36 cm), and are located in the slots indicated within the card cage assembly. See figure 1-4.

| Card | Printed Circuit Card |

|------|----------------------|

| Slot | Nomenclature         |

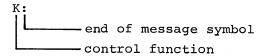

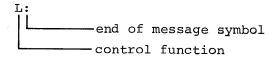

| U    | Panel Interface      |

| K    | I/O TTY Interface    |

| S    | Cyclic Encoder       |

The panel and I/O TTY interface circuit cards provide the interfaces for the maintenance panel and the communications console to the CP. The cyclic encoder generates check characters.

#### MAIN MEMORY

Main memory, for the basic 2550-2 HCP configuration, consists of three printed circuit cards which are installed in the slots indicated within the CP card cage assembly. See figure 1-3.

| Slot | Circuit Card              |    |

|------|---------------------------|----|

| V    | MOS Memory Interface - Da | ta |

| W    | MOS Memory Interface -    |    |

|      | Address/Control           |    |

| X    | MOS Memory (32K)          |    |

The MOS memory circuit card provides 32,768 words of main memory. The other two circuit cards (known as the Memory Management System) provide the interface between main memory and the microprocessor. All of these circuit cards are 11 in. x 14 in. (28 cm x 36 cm).

Main memory capacity can be increased by adding either of the MOS memory expansion circuit cards listed in table 1-2.

TABLE 1-2. MOS MEMORY CAPACITY

| Control Data<br>Product No. | Added<br>Memory<br>Capacity | Total<br>System<br>Memory<br>Capacity |

|-----------------------------|-----------------------------|---------------------------------------|

| 2554-16                     | 16,384                      | 49,152                                |

| 2554-32                     | 32,768                      | 65,536                                |

#### NOTE

If a 2554-16 memory expansion module has been installed in a system, it must be removed prior to adding the 2554-32 memory expansion module.

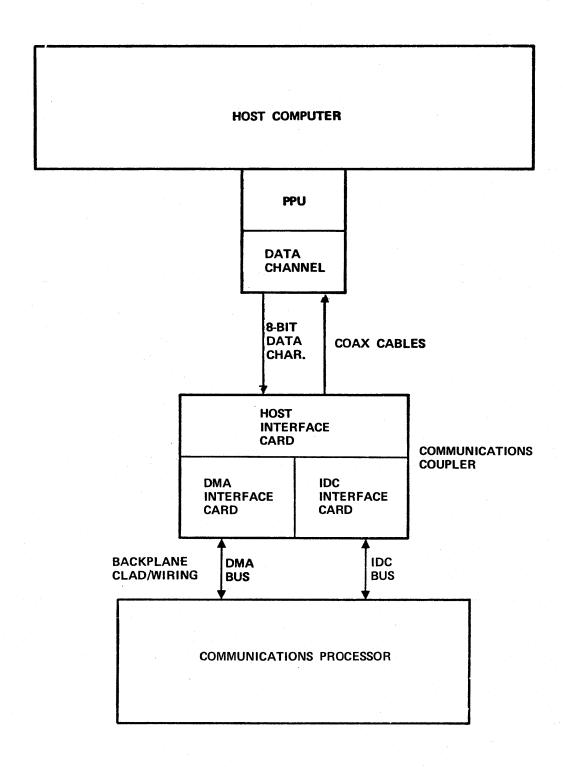

#### **COMMUNICATIONS COUPLER**

In the basic 2550-2 HCP configuration, the communications coupler consists of the following three printed circuit cards which are located in the indicated slots of the CP card cage assembly. See figure 1-4.

| Card | Printed Circuit Card |

|------|----------------------|

| Slot | Nomenclature         |

|      |                      |

| В    | Host Interface       |

| C    | IDC Interface        |

| D    | DMA Interface        |

The expansion 2558-1 Communications Coupler consists of the following three printed circuit cards which are located in the indicated slots of the CP card cage assembly. See figure 1-3.

| Card | Printed Circuit Card |  |  |

|------|----------------------|--|--|

| Slot | Nomenclature         |  |  |

| AB   | Host Interface       |  |  |

| AA   | IDC Interface        |  |  |

| A    | DMA Interface        |  |  |

#### 6671/6676 EMULATION COUPLER

The 6671/6676 emulation coupler requires one 2550-100 emulation module which contains two circuit cards. See figure 1-5. The emulation coupler expansion is accomplished by addition of a 2558-2 emulation coupler which also contains two circuit cards. The 2550-100 interface and synchronizer circuit cards form the primary 6671/6676 emulation coupler and are located in slots C and B. The 2558-2 circuit cards located in card slots AA and AB form the expansion 6671/6676 emulation coupler.

### **MULTIPLEX SUBSYSTEM**

The multiplex subsystem comprises the following major system components:

- Multiplex Loop Interface Adapter (MLIA)

- 2. Loop Multiplexer (LM)

- Communications Line Adapters (CLAs)

## Multiplex Loop Interface Adapter

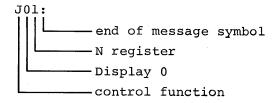

The multiplex loop interface adapter (MLIA) comprises the following three printed circuit cards which are located in the slots indicated in the CP card cage assembly (see figure 1-4):

| Card<br>Slot | Printed Circuit Card<br>Nomenclature |

|--------------|--------------------------------------|

| E            | Input Loop Interface                 |

| F            | Output Loop Interface                |

| G            | Processor Interface                  |

Each of these circuit cards is 11 in. z 14 in.  $(28 \text{ cm} \times 36 \text{ cm})$ .

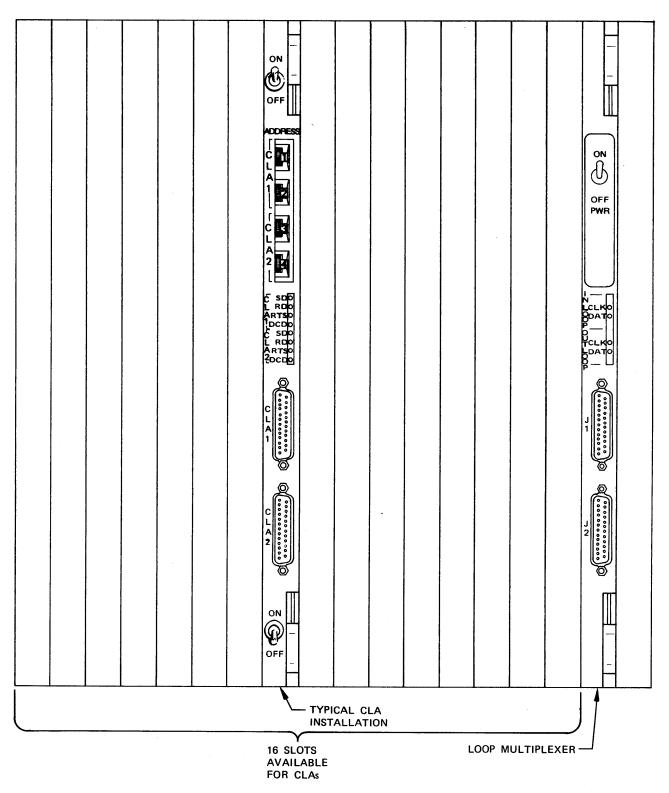

# Loop Multiplexer and Communications Line Adapters

The loop multiplexer (LM) is located in the second circuit card slot from the right, in the LM card cage assembly as shown in figure 1-6. The 16

circuit card slots to the left of the LM can be used for CLAs. A typical CLA installation is shown in figure 1-4; however, the total number of CLAs used, as well as the types of CLAs, is determined by the user.

All configurations of the communications line expansion units (2556-2, -3, -4) have the same placement of LM and CLA cards as that described above for the LM card cage assembly.

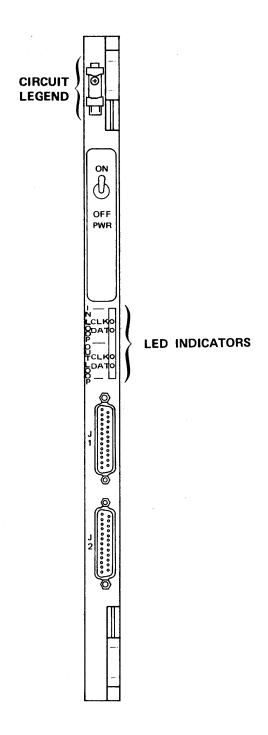

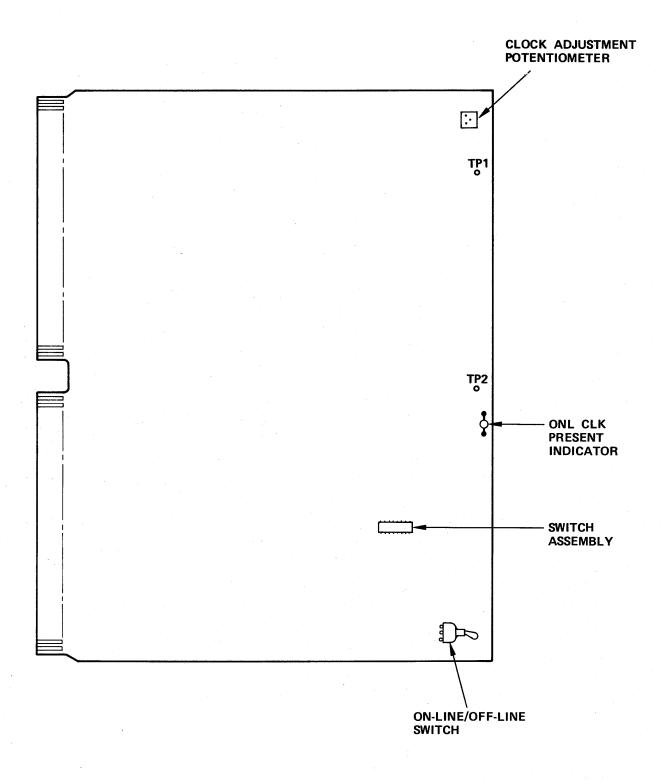

The LM and CLA circuit cards are 11 in. x 14 in. (28 cm x 36 cm). A narrow (7/8-inch [2.2 cm]-wide) control panel is mounted on the frontfacing edge of each card, which contains controls and indicators.

The LM printed circuit card contains a power (PWR) switch and the following four light-emitting diode (LED) indicators:

- 1. IN LOOP CLK

- 2. IN LOOP DATA

- 3. OUT LOOP CLK

- 4. OUT LOOP DATA

The function of the switch and indicators is described in section 3 of this manual.

The CLA controls and indicators vary according to the type(s) of CLAs selected, and the user should refer to the appropriate CLA manual(s) (see Preface).

# TAPE CASSETTE TRANSPORT AND CONTROLLER

The tape cassette transport is mounted on the inner surface of the door for Bay 0 as shown in figure 1-1.

The length of the transport is approximately 7.5 in. (19 cm); this is the length of the transport surface which contacts the door.

The height of the transport is approximately 5.4 in. (13.7 cm) with the top cover closed. The depth of the transport is 5.1 in. (13 cm); this is

2558-2 EMULATION COUPLER SYNCHRONIZER AB EXPANSION (OPTIONAL) 2558-2 EMULATION COUPLER INTERFACE (NOT USED) 4 2550-100 EMULATION COUPLER SYNCHRONIZER **PRIMARY** 8 (STANDARD) 2550-100 EMULATION COUPLER INTERFACE ပ (NOT USED) ۵ MLIA-1 (INPUT LOOP I/F) ш MLIA-2 (OUTPUT LOOP I/F) ш MLIA-3 (PROCESSOR I/F) G TAPE CASSETTE CONTROLLER I 2571-1 PERIPHERAL CONTROLLER 7 I/O TTY INTERFACE ¥ STATUS MODE INTERRUPT \_ ARITHMETIC AND LOGIC UNIT Σ **CONTROL 2** Z CONTROL 1 ۵ 1700 TRANSFORM (W/EMULATOR ROM)  $\alpha$ CYCLIC ENCODER S MICROMEMORY (2K)  $\vdash$ PANEL INTERFACE MOS MEMORY INTERFACE - DATA MOS MEMORY INTERFACE - ADDRESS/CONTROL ≥ MOS MEMORY (32K) × EXPANSION MOS MEMORY MODULE (16K OR 32K) > (NOT USED) Ν AC (NOT USED)

Figure 1-5. CP Card Cage Configuration for 2550-100/2558-2 Emulation Couplers

Figure 1-6. Location of Loop Multiplexer and Typical Communications Line Adapter

the dimension of the transport which extends into the cabinet when the HCP door is closed.

The tape cassette controller is an 11 in. x 14 in. (28 cm x 36 cm) circuit card which is installed in slot H of the CP card cage assembly. See figure 1-4.

### WIRED CABINET ASSEMBLY

The following major system components are installed in the wired cabinet assembly:

- 1. Power Supplies

- 2. Air Blower and Filter Assemblies

- 3. Cabling

#### **POWER SUPPLIES**

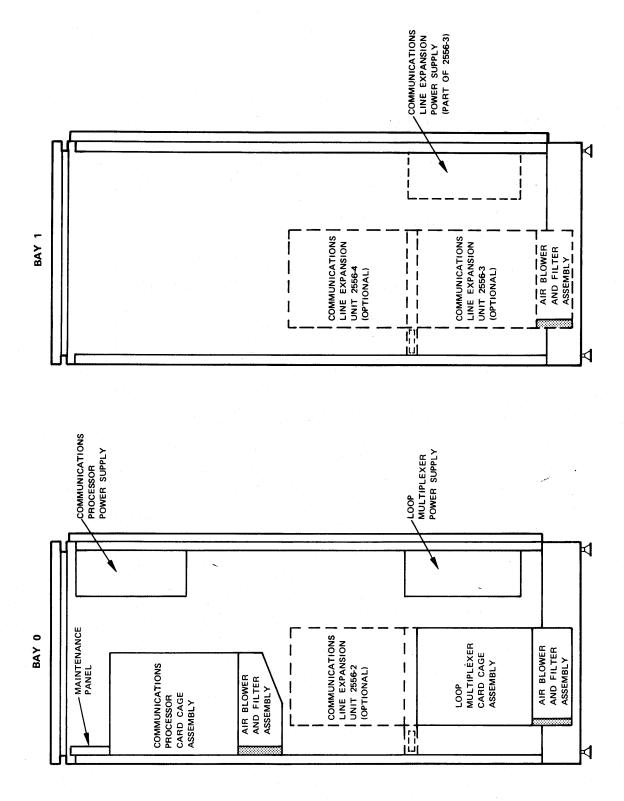

As shown in figure 1-3, two power supplies are provided with the basic 2550-2 HCP, and a third is provided as a part of the optional 2556-3 CLE product. These power supplies are identified as follows:

- 1. Communications Processor Power Supply

- 2. Loop Multiplexer Power Supply

- 3. Communications Line Expansion

Power Supply (part of

optional 2556-3 CLE)

All of the power supplies are mounted on hinges, and can be swung outward (from the rear of the HCP) to provide access to circuit breakers, fuses, and voltage-adjustment controls. All three power supplies have the following dimensions:

Height: 17.6 in. (45 cm)

Width: 15.3 in. (39 cm)

Depth: 8.4 in. (21 cm)

## AIR BLOWER AND FILTER ASSEMBLIES

As shown in figure 1-3, two air blower and filter assemblies (ABFAs) are provided with the basic 2550-2 HCP, and a third is provided as part

of the optional 2556-3 CLE product. These ABFAs are identified as follows:

- 1. Communications Processor ABFA

- 2. Loop Multiplexer ABFA

- 3. Communications Line Expansion

ABFA (part of optional 2556-3

CLE)

#### **CABLING**

The cabling for the 2550-2 HCP is described in detail in the Site Preparation Manual (see preface).

#### POWER REQUIREMENTS

Refer to the Site Preparation Manual (see preface) for 2550-2 HCP power requirements.

# **FUNCTIONAL CHARACTERISTICS**

A block diagram of the 2550-2 HCP is presented in figure 1-1. This diagram shows the major functional units and subsystems of the basic 2550-2 HCP, the components and assemblies of these larger functional units, and the optional and required products which the user must specify by product number. The HCP macroinstruction set is compatible with the Control Data 1700 instruction set, and also includes a set of enhanced instructions.

The functional features of the HCP are listed in table 1-3.

## **COMMUNICATIONS PROCESSOR**

# Microprocessor

The communications processor (CP) is capable of either emulating the CDC 1700 Series processor or directly executing microcode. The CP contains arithmetic and logical elements, a series of general purpose registers, two files, a status mode register, 16 macro and 16 micro interrupts

## TABLE 1-3. HCP FUNCTIONAL FEATURES

## MAIN MEMORY

32,768 words (expand-Capacity:

able to 65,536 words)

16 bits (plus a Word Length:

parity bit and a protect bit)

550 nanoseconds Read-access time:

Memory addressing modes: 8

Memory word and region protection

Memory parity detection

Direct memory access (4 users)

External CPU access

Automatic interlaced refresh

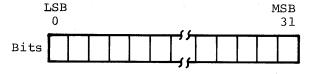

#### MICROMEMORY

Capacity:

3,072 words (2,048 read/write; 1,024 read

only emulator)

Word length: 32 bits

Read-access time: 168 nanoseconds

## INTERRUPTS

16 (correspond Macrointerrupts:

to CDC 1700 interrupts)

Macrointerrupts: 16 (internal to

this processor)

REGISTERS:

#### FILES

File 1: 256 words

File 2: 32 words

(with masks), a 1700 transform and emulator and 3072 32-bit words of memory plus necessary timing and control.

Also included is an internal data channel (capability for interfacing peripherals utilizing either an NCR MO5 protocol or a CDC 1700 AQ proto-To provide timing for communications protocols, a real-time clock generates a continuous series of pulses at a 300 pps rate. Special algorithm hardware provides a capability for checking/generating a wide variety of LRC/CRC error check characters for messages in either direction. Integral to the CP are two sets of files accessible directly by the microprocessor.

As an enhanced emulative microprocessor, the CP executes microprograms; either those emulation routines residing in the 1024 fixed (read only) portion of micromemory or those real-time character-processing routines residing in the 2048 alterable read-write portion. When emulating, macroinstructions residing in main memory in 1700 format are emulated (not executed). The net effect is comparable; however, the implementation is totally different.

Multiplex subsystem operations generally are controlled by the realtime character-processing microcode. Communication between the emulator and the real-time microcode is via the microinterrupts.

The basic execution time for a micromemory instruction is 168 nanoseconds; however, longer times are required for some types of instructions. A typical main memory readaccess requires 550 nanoseconds.

#### Maintenance Panel and Interface

The maintenance panel provides the following capabilities:

- 1. Starting the processor

- 2. Stopping the processor

- Selecting any two registers (listed in table 3-2) for display

- Modifying the contents of any register

- 5. Displaying the contents of main memory

- 6. Modifying the contents of main memory

Setting the macro or microbreakpoint

NOTE

All of these capabilities also are available at the operator communications console.

Use of this panel is described in detail in section 3 of this manual.

#### Communications Console and Interface

The communications console can be either a CRT or TTY. In each case, the console serves as the operator's primary point of interface with the system. The communications console can function in either of two modes: I/O mode or panel mode. The mode of operation can be selected either by the software or by the operator using the communications console keyboard.

In the I/O mode, all communication between the console and the MP is routed only through the I/O TTY interface. The console thus operates as a standard peripheral device on the I/O bus.

In the panel mode, the console is used essentially as a maintenance panel. Operating modes can be switched from the communications console.

#### Cyclic Encoder

The primary function of the cyclic encoder is to compute cyclic redundancy checksum (CRC) and longitudinal redundancy checksum (LRC) characters in minimum time. These characters are used in error code generation and verification of both incoming and outgoing data to the terminals. Choice of encoding polynomials is controlled by software.

#### Main Memory

Main memory provides storage for macroprograms, tables, and data buffers needed to perform the special communications tasks of the HCP. Up to 64K words can be directly addressed by the processor and up to 128K words can be directly addressed by the host (e.g., CYBER 70/170) via the communications coupler.

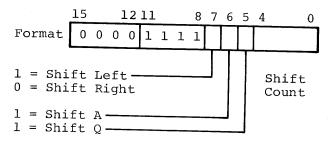

Memory can be expanded up to 128K (92K if error correction features are included). Beyond 64K locations are addressed through the use of a memory paging system whereby memory is functionally divided into 2K pieces. Any combination of 32 registers constitutes the effective memory when either of two sets of paging are selected. As currently implemented, the 2550 operational software does not use the paging feature.

Each memory location contains a word-parity check-bit to provide one form of error control. Another form of error control is the memory protect system of which two types are provided. In the first, a protect bit is associated with each word location and can be set under program control to provide word-by-word protection. The second consists of an upper and lower bounds register used to protect on a contiguous block basis. The protect can be manually selected or disabled.

Main memory modules are interconnected to preclude simultaneous read operations from two or more locations in main memory. However, there are three ports for main memory. These ports are identified as input/output (I/O), direct memory access (DMA), and external. The I/O port serves as the normal access path for the CP to main memory. The DMA port provides access paths for the multiplex subsystem, and for direct memory-tomemory transfers from the host computer's peripheral processing unit (PPU) via the coupler. The external port is not used in single-processor application.

## **MULTIPLEX SUBSYSTEM**

The multiplex subsystem contains the hardware, firmware, and software elements which provide the data and control paths for information flow between communications lines and user program software. Many of the line/protocol dependent functions that were performed by fixed hardware in previous systems are implemented in common alterable firmware/software allowing reduced development and recurring hardware costs for each line and protocol that is added to the communications system.

The primary task performed by the multiplex subsystem is to receive data from many communications lines and distribute the characters to line-related input buffers, and to obtain characters from line-related output buffers and distribute these characters to communications lines. The subsystem provides for special table-driven and dynamically controlled processing on each character as it is being distributed from a communications line. Circuit, modem and subsystem status are detected and transferred in the form of work demands to user programs for processing. Control information received from user programs in the form of commands to the subsystem is decoded and executed within one or more subsystem element.

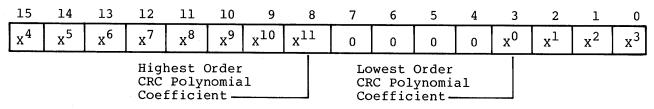

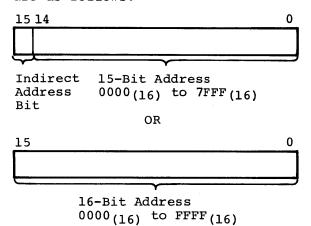

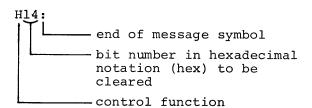

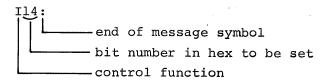

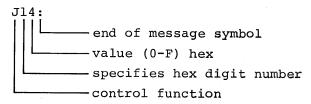

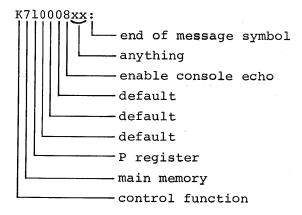

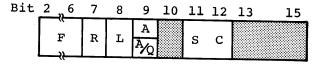

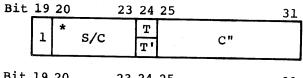

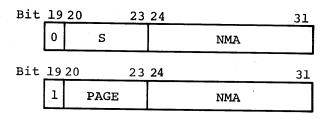

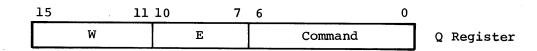

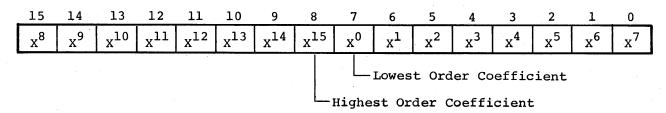

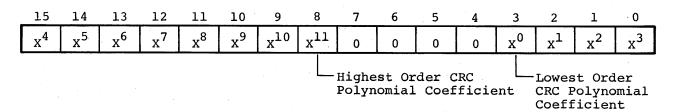

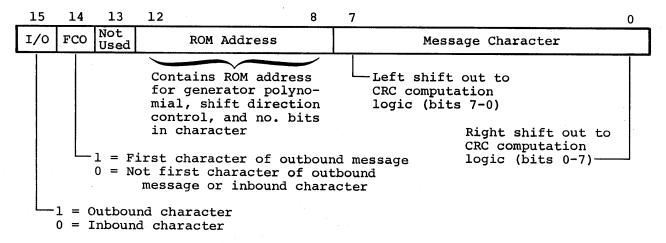

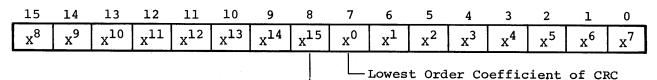

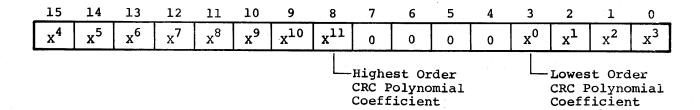

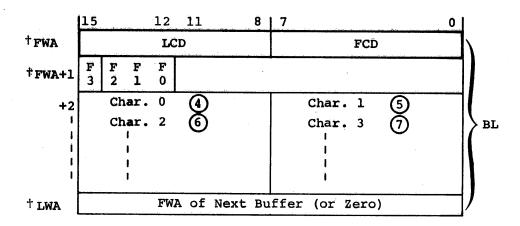

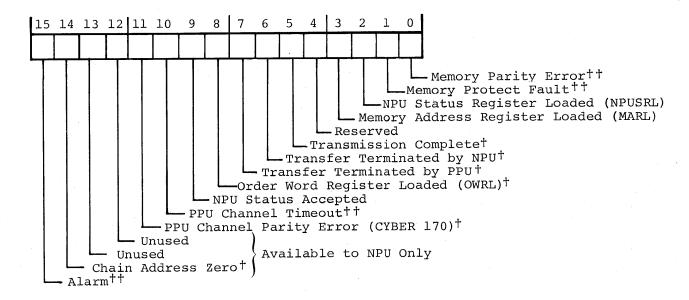

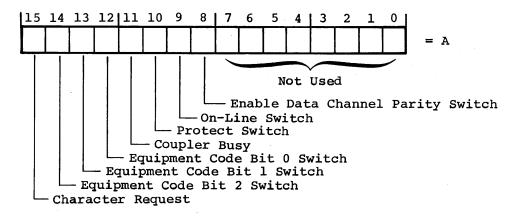

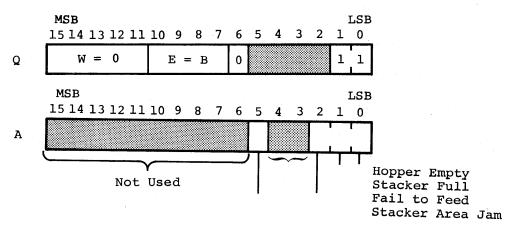

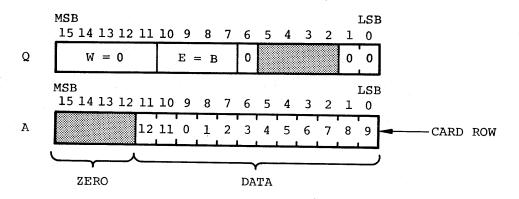

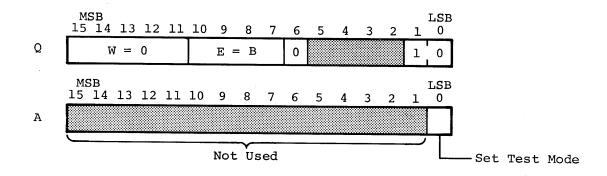

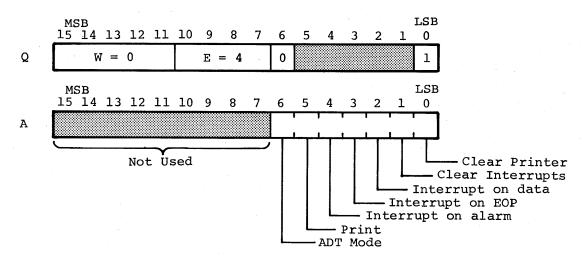

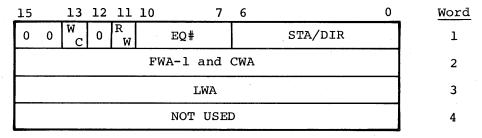

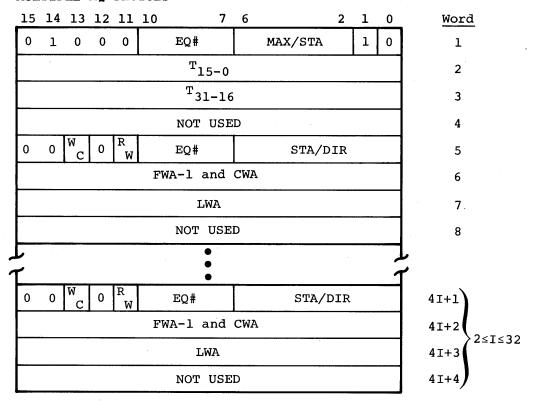

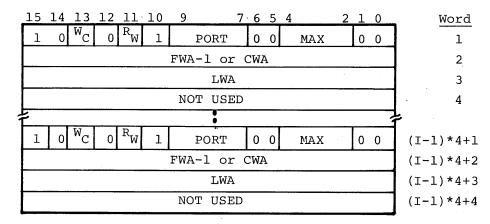

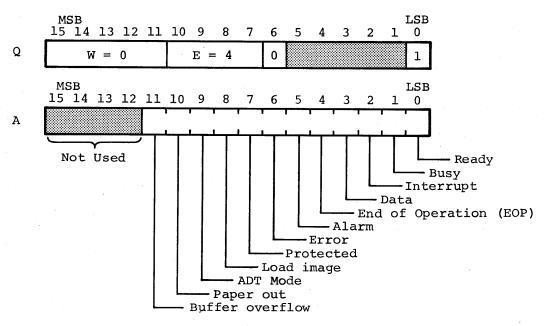

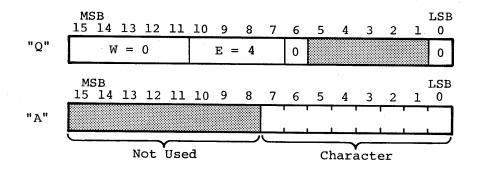

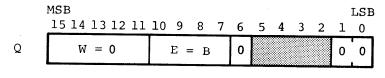

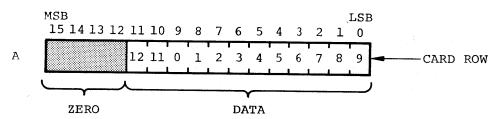

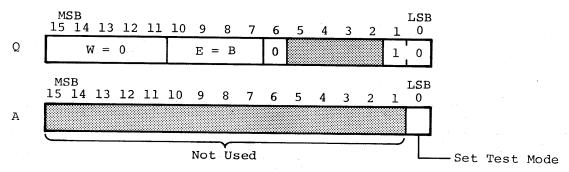

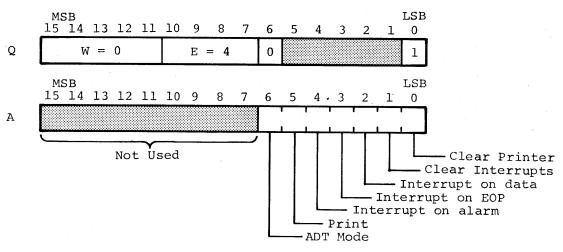

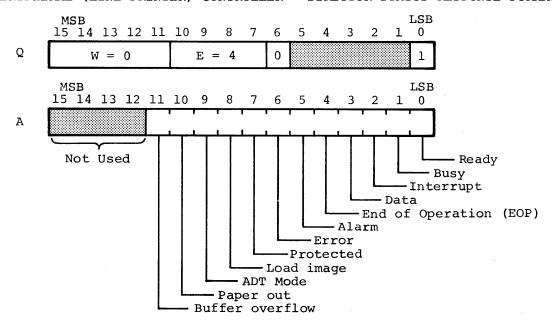

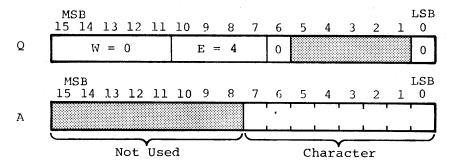

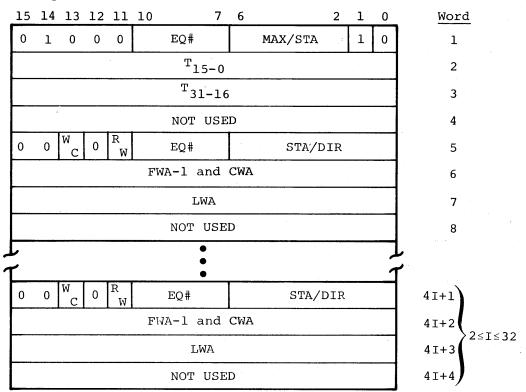

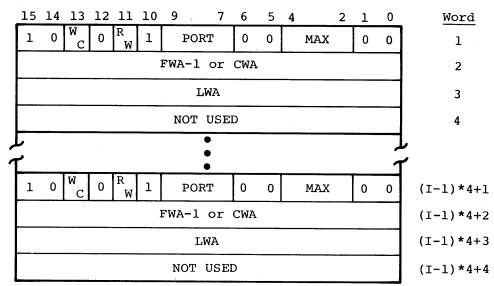

The multiplexing scheme used in the multiplex subsystem design is based on a demand-driven multiplex loop concept. The multiplex subsystem gathers input data and status from, and distributes output data and control to, many communications lines on a real-time basis. The design provides an economical method of connecting many communications lines to a controlling processor while using a minimum of the processor resources to manage the mechanism.