# CONTROL DATA® 1700 Computer System

# STANDARD PERIPHERAL REFERENCE MANUAL

# CONTROL DATA® 1700 Computer System

# STANDARD PERIPHERAL REFERENCE MANUAL

| RECORD of REVISIONS                                                                                 |                                                                                                 |  |  |  |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                     |                                                                                                 |  |  |  |

| A                                                                                                   | Initial Printing. Final Edition.                                                                |  |  |  |

| (10-14-66)                                                                                          |                                                                                                 |  |  |  |

| В                                                                                                   | Publications Change Order 15110 which adds 1738-A/B Disk Drive Controller to Mass Storage       |  |  |  |

| (11-8-66)                                                                                           | Equipment Section.                                                                              |  |  |  |

| С                                                                                                   | Publications Change Order 15448 which adds 1718-A Satellite Coupler to Interface Equipment      |  |  |  |

| (12-23-66)                                                                                          | Section.                                                                                        |  |  |  |

| D                                                                                                   | Publications Change Order 15582 which adds 1716-A Coupling Data Channel to Interface Equipment  |  |  |  |

| (1-13-67)                                                                                           | Section.                                                                                        |  |  |  |

| E                                                                                                   | Publications Change Order 17487 which adds 1742-A/B Line Printer Controller to Part 5, Visual   |  |  |  |

| (10-26-67)                                                                                          | Recording Equipment Section.                                                                    |  |  |  |

| F                                                                                                   | Publications Change Order 18309 which adds 1732-A/B Magnetic Tape Controller to Magnetic Tape   |  |  |  |

| (1-4-68)                                                                                            | Equipment Section; also new Record of Revisions page and General Contents page. Revised, pages  |  |  |  |

|                                                                                                     | 8, 9, 11 and 12 of 1731-A/B Magnetic Tape Controller, Magnetic Tape Equipment Section; pages 10 |  |  |  |

|                                                                                                     | 14, 15 and 16 of 1738-A/B Disk Drive Controller, Mass Storage Equipment Section.                |  |  |  |

| G                                                                                                   | Publications Change Order 19029 which adds 1728-A/B Card Reader/Punch Controller to Part 4,     |  |  |  |

| (3-14-68)                                                                                           | Card Equipment Section.                                                                         |  |  |  |

| Н                                                                                                   | Publications Change Order 18706 which revises page 13 of 1732-A/B Magnetic Tape Controller in   |  |  |  |

| (5-25-68)                                                                                           | Part 3, Magnetic Tape Equipment.                                                                |  |  |  |

| J                                                                                                   | Publications Change Order 19529 which adds 1726 Card Reader Controller to Part 4, Card          |  |  |  |

| (5-25-68)                                                                                           | Equipment Section.                                                                              |  |  |  |

| K                                                                                                   | Publications Change Order 19545 which adds 1740 Line Printer Controller to Part 5, Visual       |  |  |  |

| (5-25-68)                                                                                           | Recording Equipment Section.                                                                    |  |  |  |

| L                                                                                                   | Engineering Change Order 19932. Pages 10 and 20 revised of the 1738 section.                    |  |  |  |

| (7-31-68)                                                                                           |                                                                                                 |  |  |  |

| M                                                                                                   | Engineering Change Order 20210. Page v of the General Contents section, 1706 page 2, 1738 pages |  |  |  |

| (7-31-68)                                                                                           | 10, 19 and 20, 1731 pages 14 and 15, 1732 pages 1, 10 and 17, 1742 section revised.             |  |  |  |

| N                                                                                                   | Manual revised, includes Engineering Change Order 21412, publications change only. Pages 1, 4,  |  |  |  |

| (1-15-69) 5, 7, 10, 12, 13, 14, 15, 16 revised and page 17 in the 1728 section added. Add 1729-2 Se |                                                                                                 |  |  |  |

|                                                                                                     | (pages i, ii and 1 thru 16), General v changed.                                                 |  |  |  |

| P                                                                                                   | Manual revised, includes Engineering Change Order 22398, publication change only. Page 1 of     |  |  |  |

| (6-3-69)                                                                                            | section 1706 and pages 11, 12 and 13 of section 1716 revised.                                   |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

|                                                                                                     |                                                                                                 |  |  |  |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

Pub.No. 60182700 © 1967, 1968, 1969 by Control Data Corporation Printed in United States of America

# FOREWORD

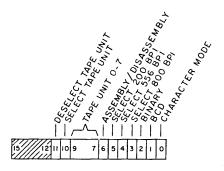

Input to A and Output from A, the two 1704 input/output instructions, are the key to all computer communication with its peripheral equipment. These instructions alone do not specify all information necessary to control a device. The programmer, therefore, must select a device, request status, specify operating conditions, and initiate data transfer via these instructions together with the 1700 register contents.

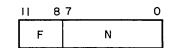

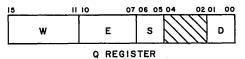

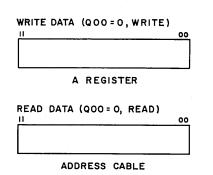

As suggested by the name A/Q Channel, the equipment has access to the information in the A and Q registers. The contents of these two registers (32 total bits available), combined with the two I/O instructions, can specify all the information needed to operate the peripheral equipment. The Q register specifies addresses and operations, while the A register further specifies or directs the operation, receives information, or is available for input or output data.

Logically, if the A register is to be used to supply a control or data word, A must be loaded with that word. Executing an Output from A instruction presents this 16-bit word to the equipment. The Q register directs the controller how to use this word; e.g., as the first word address minus one for a buffered operation, for interrupt selection, or as data. Similarly, if information is to be brought into the A register, an Input to A instruction is used and (Q)\* specify the type of information to be brought into A (e.g., status or data).

The reader may notice two paradoxes when examining a table of codes for a 1700 peripheral equipment:

- 1) The same value in Q may be used for two distinct operations.

- 2) An input operation using the Direct Storage Access Bus (i.e., a buffered input) is initiated by an Output from A instruction.

The effects of the two 1704 I/O instructions readily explain these paradoxes. In the first case, the OUT instruction and (Q) or the INP instruction and (Q) do indeed uniquely define an operation. In the second case, the A register initially holds the address the converter needs to specify the buffer area. Executing the Output from A instruction sends this address to the converter, whereupon the input buffer operation can begin.

As indicated in the preceding paragraphs, the 1704 I/O instructions do not necessarily transfer data in the usual sense of the word data. These instructions can transfer a word between the A register and the peripheral equipment which is either data or a control word. They directly control the input/ output of a single word to/from the A register. Once they have been used to send the proper control words to the device, the transfer of data to or from memory may occur, not under control of the 1704 instructions but under control of the converter and the Direct Storage Access Bus.

This manual supplies to the programmer the codes for the A and Q registers which are used in conjunction with the two 1704 I/O instructions to operate the 1700 peripheral equipments. It presents a brief physical description of these equipments, the relationship of the equipment to the computer system, definitions of programming operations, special programming considerations, and instructions for manual operation. It assumes the programmer is familiar with the 1704 instructions and procedures. It does not supply information on the basic peripherals. For these devices and further information on input and output, refer to the 1700 Computer System Reference Manual, Pub. No. 60153100.

\* Parentheses around a letter are used to indicate the contents of a register.

iii

$\bigcirc$  $\int$  $\sum_{i=1}^{n}$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\sum_{i=1}^{n}$  $\left( \begin{array}{c} \\ \\ \\ \\ \\ \end{array} \right)$

# **GENERAL CONTENTS**

()

| PART 1 | INTERFACE EQUIPMENT                   |

|--------|---------------------------------------|

|        | 1706-A Buffered Data Channel          |

|        | 1716-A Coupling Data Channel          |

|        | 1718-A Satellite Coupler              |

| PART 2 | MASS STORAGE EQUIPMENT                |

|        | 1738-A/B Disk Drive Controller        |

| PART 3 | MAGNETIC TAPE EQUIPMENT               |

|        | 1731-A/B Magnetic Tape Controller     |

|        | 1732-A/B Magnetic Tape Controller     |

| PART 4 | CARD EQUIPMENT                        |

|        | 1726 Card Reader Controller           |

|        | 1728-A/B Card Reader/Punch Controller |

|        | 1729-2 Card Reader Subsystem          |

| PART 5 | VISUAL RECORDING EQUIPMENT            |

|        | 1740 Line Printer Controller          |

1742-A/B Line Printer

General Contents Rev N

$\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\langle \gamma \rangle$  $\bigcirc$

. . .

# CONTENTS

| Introduction           | 1 | Programming                        | 2 |

|------------------------|---|------------------------------------|---|

| Functional Description | 1 | Summary of Programming Information | 2 |

| System Relationship    | 1 | Addresses                          | 3 |

| Interrupt              | 2 | Operations                         | 3 |

| Program Protection     | 2 | Status Response                    | 5 |

| Reply/Reject           | 2 | Programming Considerations         | 6 |

# FIGURES

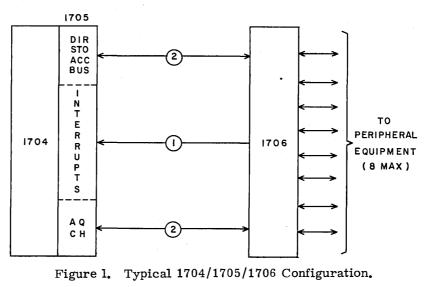

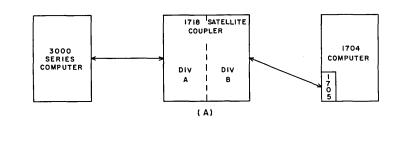

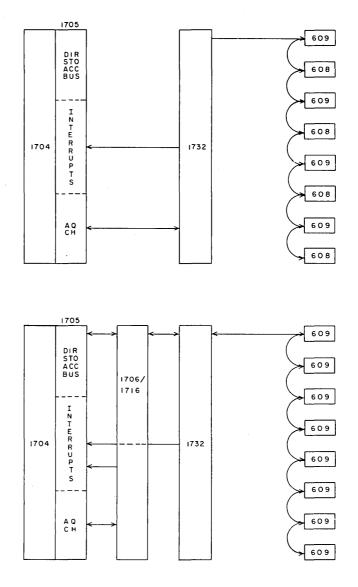

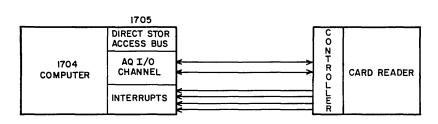

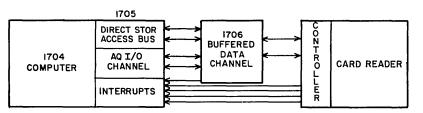

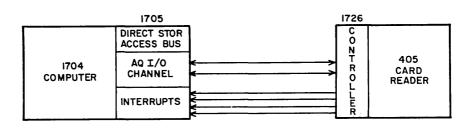

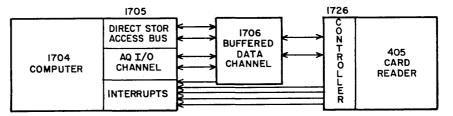

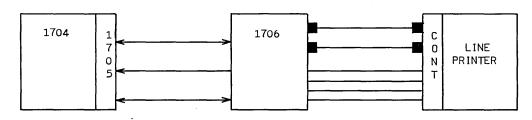

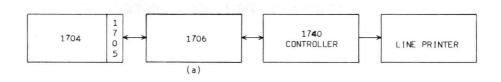

1. Typical 1704/1705/1706 Configuration 1

# TABLES

2

3

1706 Addresses and Operations

21706 Functions

3 1706 Status Response Bits

5

# 1706-A BUFFERED DATA CHANNEL

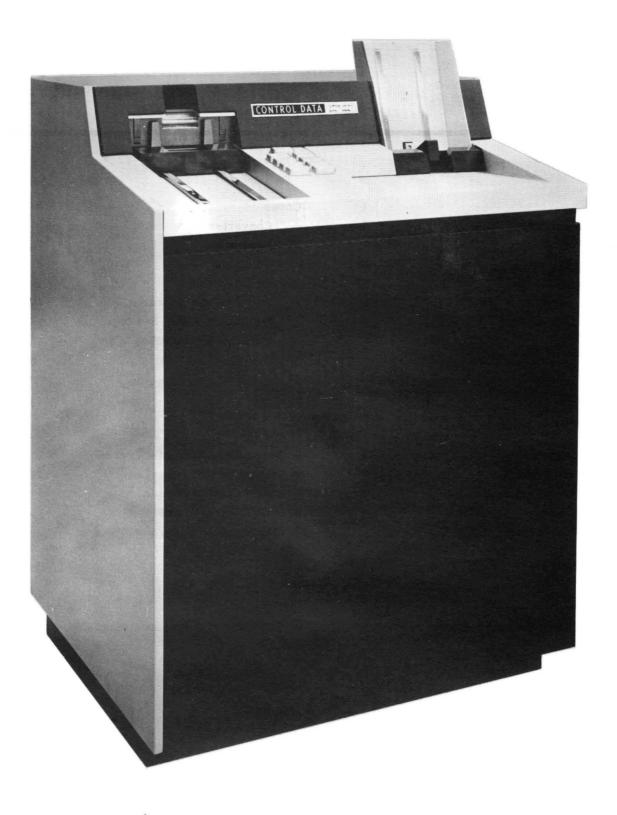

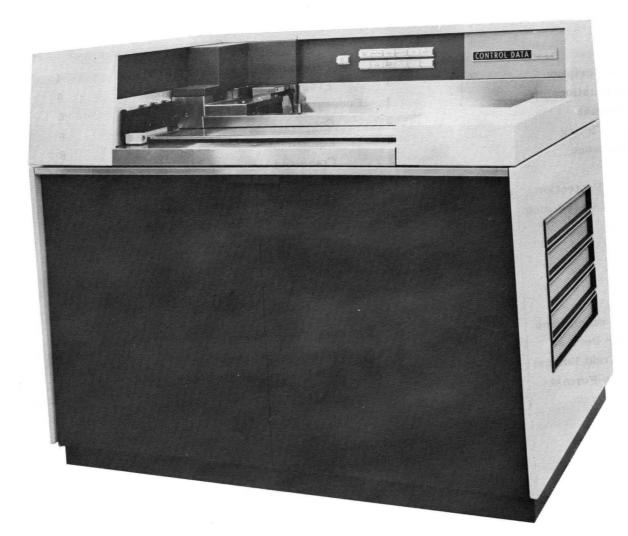

This section describes the CONTROL DATA\* 1706-A Buffered Data Channel (BDC), its physical system, and programming information. There is no operating information since the 1706 has no indicators or manual controls.

# FUNCTIONAL DESCRIPTION

System Relationship

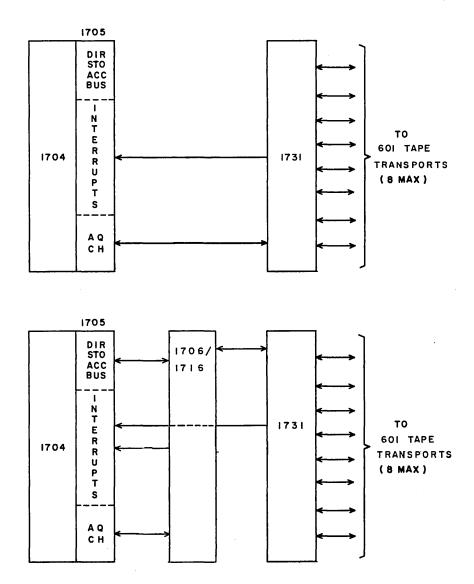

The 1706 provides a 16-bit, bidirectional, buffered input/output path between the 1704 Computer with a 1705 Interrupt Data Channel (IDC) and up to eight peripheral equipments. Figure 1 shows the connections between the 1706 and other equipments. The circled numbers indicate the number of connecting cables.

A maximum of three 1706 BDC's may be attached to the 1705 IDC. A 1716 Coupling Data Channel may replace any or all of the 1706's.

Since the 1706 contains no indicators or manual controls, all operations must be initiated by the computer. In response to any I/O instructions and the contents of the Q register, the 1706 connects the computer to one of the external controllers and sends the appropriate Read or Write signal. The 1706 then controls the Read or Write operation. If the contents of the Q register specify a buffered operation, the 1706 obtains access to storage via the Direct Storage Access Bus (DSA) when necessary to fetch or store information. If the (Q) specify a direct input or output, a 16-bit word is transferred from the selected peripheral device to the A register of the 1704 or vice versa.

1

\* Registered trademark of Control Data Corporation

Interrupt

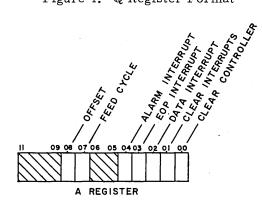

An interrupt to the computer can be generated when the 1706 terminates a buffered transfer, i.e., upon end of operation. This interrupt is enabled by an Output from A instruction with the W field (bits 11-15) of the Q register selecting a function to the 1706, and bits 15 and 00 of the A register set. It is disabled by a function to the 1706 and bit 15 of A clear, bit 00 of A set.

An interrupt itself from the 1706 is cleared by a function to the 1706 with bit 00 of A set. Thus, either reselecting or disabling the interrupt selection also clears the interrupt.

# **Program Protection**

The 1706 rejects non-protected Status, Terminate Buffer, Function, and Current Address instructions during a buffer operation that is initiated by a protected instruction. The 1706 has no program protect switch; the program protect feature of a 1700 System is governed by the PROTECT switches on the 1704 and the specific device connected to the 1706. However, if a program protect fault occurs, a status bit is set in the 1706 status reply word.

# **Reply/Reject**

The 1706 responds to an Input or Output instruction within 4 microseconds with-either a Reply or Reject signal. The 1706 returns a Reply whenever it can perform the requested operation. Three conditions will cause a Reject to be returned to the computer:

- 1) The 1706 is Busy when a request for a buffered transfer, a direct input, or a direct output is received;

- 2) A program protect fault occurs (also see Program Protection);

- 3) A device returns a Reject upon a direct input/output request.

If for some reason the computer receives no response (for example, the 1706 addressed does not exist in the system), the computer will generate an Internal Reject.

# PROGRAMMING

# Summary of Programming Information

Tables 1, 2 and 3 are a synopsis of the information necessary to program the 1706. Explanations of the information presented here can be found in the sections following. These tables are intended as a quick reference for the experienced programmer, a preview for the reader studying the following material, and a summary for the reader interested in the general programming capabilities of the 1706.

| W*            |               |               | COMPUTER INSTRUCTION                      |                                          |

|---------------|---------------|---------------|-------------------------------------------|------------------------------------------|

| 1706<br>No. 3 | 1706<br>No. 2 | 1706<br>No. 1 | Input to A                                | Output from A                            |

| 0C            | 07            | 02            | Direct Input                              | Direct Output                            |

| 0D            | 08            | 03            | Terminate Buffer;<br>1706 Current Address | Function<br>(See 1706<br>Function Table) |

| 0E            | 09            | 04            | 1706 Status                               | Buffered Output                          |

| 0F            | 0A            | 05            | 1706 Current Address                      | Buffered Input                           |

TABLE 1. 1706 ADDRESSES AND OPERATIONS

\* The left digit is binary, the right digit hexadecimal.

| Bit in A Register                   | Meaning                                       |

|-------------------------------------|-----------------------------------------------|

| A 155                               | Set condition for ones<br>in bits A14 - A00   |

| $A15 \begin{cases} = 0 \end{cases}$ | Clear condition for ones<br>in bits A14 - A00 |

| A14 - A01                           | (Not defined)                                 |

| A00                                 | Enable Interrupt on<br>1706 End of Operation  |

TABLE 2. 1706 FUNCTIONS

Addresses

Bits 11-15 of the Q register, called W, are used to select the desired 1706. Bits 00-10 of Q are used to select the peripheral device. The 1706 provides a W=0 signal to devices connected to it. Bit 15, the continue bit, is ordinarily zero when using the 1706. However, this bit may be used by:

- 1) Addressing the device with the correct code and Q15 set to "0".

- 2) Using Q15 = 1 for all succeeding addresses to this device.

- 3) Using Q15 = 0 and a new address to access a different device.

The 1706 interprets an access attempt with Q15 = 1 as a direct input following an Input to A instruction and as a direct output following an Output from A instruction.

Operations

Besides selecting a particular 1706, the W field of Q, combined with a 1704 Input or Output instruction, specifies an operation. The function operation may be further modified by the contents of the A register. Tables 1 and 2 list the addresses, the operations, and the functions. Because W is a 5-bit field and the upper bit (the Continue bit) has a separate use, W is written as two digits; the left digit is binary, the right digit is hexadecimal.

Operations Defined by W and Input to A

Direct Input: Whenever the computer executes an Input instruction to a 1706 with the W field of Q selecting direct input, (Q) is stored in the 1706 and presented to the devices attached to the 1706, and one 16-bit word is transferred into the A register from the selected device. The word may be a data word or the status of the device on the 1706. This mode of operation is identical in every way to that on the AQ channel. The Continue bit (Q15) functions as described under Addresses and in connection with the device being used. If an attempt is made to execute a direct input when the 1706 is busy, the 1706 responds with a Reject. For this reason, it is impossible to determine the status of a device connected to the 1706 during a buffer operation.

<u>Terminate Buffer, 1706 Current Address</u>: This code terminates a buffered operation and loads into the A register the address of the current word being transferred. The Terminate Buffer operation is intended primarily to terminate hung-up input buffers and in this case the A register contains the address of the next word to have been transferred. Otherwise, the current address may be the address of the last word transferred or of the next word to be transferred, depending on when the Terminate Buffer reaches the 1706 with respect to the timing of the data transfer of the peripheral device. A buffered operation initiated by a protected instruction cannot be terminated by a nonprotected Terminate Buffer instruction. <u>1706 Current Address</u>: This code is a status request which loads into the A register the address of the current word being transferred. A non-protected request for the current address is rejected during a buffer operation initiated by a protected instruction.

### Operations Defined by W and Output from A

<u>Direct Output</u>: Whenever the computer executes an Output instruction to a 1706 with the W field of Q selecting a direct output, (Q) is stored in the 1706 and presented to the devices attached to the 1706, and one 16-bit word is transferred from the A register to the selected device. This mode of operation is identical in every way to that on the AQ Data Channel. The Continue bit (Q15) functions as described under Addresses and in connection with the device being used. If an attempt is made to do a direct output when the 1706 is busy, the 1706 responds with a Reject.

<u>Function</u>: This code enables and disables Interrupt on End of Operation and clears the interrupt condition, depending upon the contents of the A register. If A15 and A00 = 1, the interrupt is enabled. If A15 = 0, A00 = 1, the interrupt is disabled. When a function is executed with A00 = 1, the interrupt condition is cleared. Thus either reselecting (enabling) the interrupt or disabling the interrupt clears this interrupt condition. A non-protected function instruction is rejected during a buffer operation initiated by a protected instruction.

Buffered Output on the 1706: A buffered output is initiated when the computer executes an Output instruction and the W field of Q selects a buffered output. (Q) is stored in the 1706, then placed on the 1706 channel and the contents of A are transferred to the 1706. The contents of A specifies the first word address minus 1 (FWA-1) of the block to be transferred. The contents of location FWA-1 specifies the last word address plus one (LWA+1) of the block to be transferred. The 1706 begins the data transfer by raising the Write signal to the device. The device responds within 4  $\mu$ sec by raising the Reply signal to the 1706. The 1706 then advances to the next data word, repeating this cycle until the block of data has been transferred. If the 1706 receives a Reject, it indefinitely repeats the transfer of the word until the word is accepted. The address is not reissued to storage. The 1706 does not generate an Internal Reject. If an attempt is made to establish a buffered output when the 1706 is Busy, the 1706 responds with a Reject.

Buffered Input on the 1706: A buffered input is initiated when the computer executes an Output instruction and the W field of Q selects a buffered input. (Q) is stored in the 1706, then placed on the 1706 channel and the contents of A is transferred to the 1706. The contents of A specifies the location of the first word address minus one (FWA-1) of the block where data is to be stored. The contents of location FWA-1 specifies the last word address plus 1 (LWA+1) of this block. The 1706 begins the data transfer by raising the Read signal to the device. The device responds within 4  $\mu$ sec by raising the Reply signal to the 1706. The 1706 then advances to the next data word and repeats this cycle until the block of data has been transferred. If the 1706 receives a Reject from the device, it repeats the transfer of the word indefinitely until the word is accepted. The 1706 does not generate an Internal Reject. If an attempt is made to establish a buffered input when the 1706 is Busy, the 1706 will respond with a Reject.

# Status Response

# 1706 Operating Status

Table 3 lists the bits which may be set in the A register following a status request for 1706 operating conditions. The information following Table 3 defines these bits.

| Bit Set In A Register | Meaning               |

|-----------------------|-----------------------|

| 0                     | Ready                 |

| 1                     | Busy                  |

| 2                     | Interrupt             |

| 3                     | (Not used)            |

| 4                     | End of Operation      |

| 5                     | (Not used)            |

| 6                     | Program Protect Fault |

| 7                     | (Not used)            |

| 8                     | Device Reject         |

| 9                     | Device Reply          |

| 10 - 15               | (Not used)            |

TABLE 3. 1706 STATUS RESPONSE BITS

Ready (Bit 0 = 1) - This bit is set when power is on.

Busy (Bit 1 = 1) - This bit is set from the time the 1706 accepts an output word from the computer initiating a block transfer until the block transfer is terminated, or during a direct operation.

Interrupt (Bit 2 = 1) - An End of Operation Interrupt is being sent to the computer from the 1706.

End of Operation (Bit 4 = 1) - A buffer transfer input or output has been completed.

Program Protect Fault (Bit 6 = 1) - A reference to computer storage caused a program protect fault. The 1700 Reference Manual defines the conditions causing a program protect fault in its Interrupt Section.

Device Reject (Bit 8 = 1) - This bit, if set, means the peripheral device rejected the last word transfer attempted from the 1706.

Device Reply (Bit 9 = 1) - This bit, if set, means the peripheral device accepted the last word transfer attempted from the 1706.

# 1706 Current Address

This status shows the address of the current word being transferred. It is loaded into the A register following a Terminate Buffer or a 1706 Current Address operation.

# Programming Considerations

|                     | Г <del></del>                                                                                                                                   | <u>,                                     </u> | ······································                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1704<br>Instruction | Q Register                                                                                                                                      | Step                                          | Action                                                                                             |

| LDQ                 | Selected 1706<br>Status Request                                                                                                                 | 1)                                            | Initiate operating status check of desired 1706                                                    |

| INP                 |                                                                                                                                                 | 2)                                            | A register now contains the operating status of the desired 1706                                   |

|                     |                                                                                                                                                 | 3)                                            | Check status in A for Ready and Not<br>Busy                                                        |

| LDQ                 | W = Direct Input<br>on selected 1706,<br>Bits 0-10 specify<br>status request<br>for equipment                                                   | 4)                                            | Initiate status check of equipment to be<br>used                                                   |

| INP                 |                                                                                                                                                 | 5)                                            | A register now contains the equipment status                                                       |

|                     |                                                                                                                                                 | 6)                                            | Check equipment status for desired conditions.                                                     |

|                     |                                                                                                                                                 | 7)                                            | Repeat 4-6 for station and unit, if necessary.                                                     |

| LDQ                 | Selected 1706<br>Function                                                                                                                       | 8)                                            | Initiate selection or clearing of Inter-<br>rupt on End of Operation.                              |

| LDA                 |                                                                                                                                                 | 9)                                            | Load A with desired operation                                                                      |

| OUT                 |                                                                                                                                                 | 10)                                           | Interrupt on End of Operation is now<br>enabled or disabled. Any existing<br>interrupt is cleared. |

| LDQ                 | W = Direct Output<br>on selected 1706.<br>Bits 0-10 specify<br>an operation on<br>the equipment or<br>station.                                  | 11)                                           | Initiate selection of peripheral equip-<br>ment operating conditions and inter-<br>rupts.          |

| LDA                 |                                                                                                                                                 | 12)                                           | If necessary, load A with the code<br>further specifying the operation indi-<br>cated by (Q).      |

| OUT                 |                                                                                                                                                 | 13)                                           | Execute Output from A instruction                                                                  |

|                     |                                                                                                                                                 | 14)                                           | Repeat 11-13 until all desired oper-<br>ating conditions are specified.                            |

|                     | For a Dire                                                                                                                                      | ct Inpu                                       | t or Output of Data                                                                                |

| LDQ                 | W = Direct Input<br>or Direct Output<br>on selected 1706.<br>Bits 1-10 select<br>equipment and<br>station. Bit 0 =<br>"0" for data<br>transfer. | 15D)*                                         | Select desired type of I/O.                                                                        |

| LDA                 |                                                                                                                                                 | 16D)                                          | If doing a direct output, load the data<br>into A; if direct input, skip this step.                |

\* D indicates a step for the direct transfer of data.

Programming Considerations

(Cont'd)

00000

| 1704          |                                                                                                                                                          |         |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction   | Q Register                                                                                                                                               | Step    | Action                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INP or<br>OUT |                                                                                                                                                          | 17D)    | Execute 1704 Input to A or Output from A, depending on desired direction of data transfer.                                                                                                                                                                                                                                                                                                                                          |

|               |                                                                                                                                                          | 18D)    | Skip to 19)                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               | For a B                                                                                                                                                  | uffered | Transfer of Data                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LDQ           | W = Buffered<br>Input or Buff-<br>ered Output on<br>selected 1706.<br>Bits 1-10 select<br>equipment and<br>station. Bit 0 =<br>"0" for data<br>transfer. | 15B)*   | Select desired type of buffered I/O.                                                                                                                                                                                                                                                                                                                                                                                                |

| LDA           |                                                                                                                                                          | 16B)    | Load A with the FWA-1 of the buffer<br>area. The contents of memory at this<br>address must contain the LWA + 1 of<br>the buffer area.                                                                                                                                                                                                                                                                                              |

| OUT           |                                                                                                                                                          | 17B)    | The buffered transfer is now initiated and under control of the 1706.                                                                                                                                                                                                                                                                                                                                                               |

|               |                                                                                                                                                          | 18B)    | Go to step 19).                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |                                                                                                                                                          | 19)     | Status the converter (as in steps 1-3,<br>checking for desired conditions, or by<br>using the 1706 current address status)<br>or proceed with the main program until<br>an interrupt occurs. Using interrupts<br>takes advantage of the capabilities of<br>the buffered data channel to do I/O with-<br>out hanging up the computer. It is not<br>possible to status a device connected to<br>the 1706 as long as the 1706 is Busy. |

\*B indicates a step for the buffered transfer of data.

### COMMENTS

If a buffered operation becomes hung up, LDQ with W selecting Terminate Buffer for the appropriate 1706, and execute an INP instruction. The buffered operation is terminated and the current address is sent to A. The program can check this address and take the desired action.

One method of determining if the 1706 is hung up is to select the device's Interrupt on End of Operation. When the interrupt is recognized, check the operating status of the 1706. If the 1706 is still Busy, the buffered operation is hung up. Do a status check of the 1706 current address. If the current address does not equal the LWA + 1, the equipment is hung up.

A second method is to do a status check of the 1706 current address. Then wait until at least one more word should have been transferred and again check the current address. If it is unchanged, the buffered operation is hung up. This method requires knowing instruction execution times and the rate of data transfer.

If an INP or OUT instruction results in a Reject, the program proceeds as described in connection with these instructions in the computer reference manual.

.

# CONTENTS

Introduction Functional Description System Relationship Interrupt Program Protection Reply/Reject

| Programming                           | 2 |

|---------------------------------------|---|

| Summary of Programming<br>Information | 2 |

| Addresses                             | 4 |

| Operations                            | 4 |

| Programming Considerations            | 9 |

# FIGURES

1

1

$\frac{1}{2}$

2 2

1

4

| 3 | Address Arrangement for Buffered<br>Input and Output | 7 |

|---|------------------------------------------------------|---|

| 4 | Address Arrangement for Buffered<br>Transfer         | 8 |

# TABLES

3

3

1716 Addresses and Operations 1716 Functions

Typical 1716 Configuration

1700 Q and A Registers

3

1716 Status Bits

3

1

2

1

2

# **1716 COUPLING DATA CHANNEL**

# INTRODUCTION

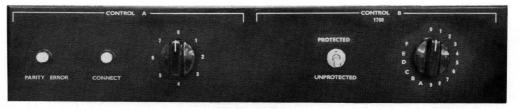

This section describes the CONTROL DATA\* 1716-A Coupling Data Channel, its physical system and programming information. There is no operating information, as there are no controls or indicators on the 1716 other than the Program Protect Switches, which are covered under Program Protection.

# FUNCTIONAL DESCRIPTION

# System Relationship

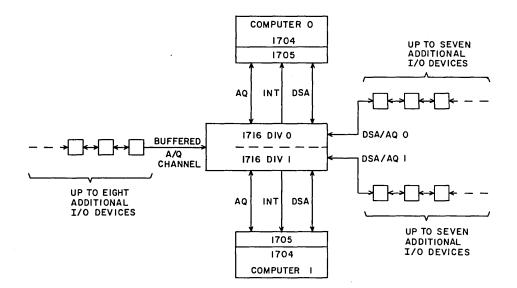

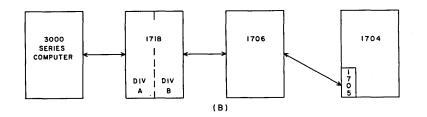

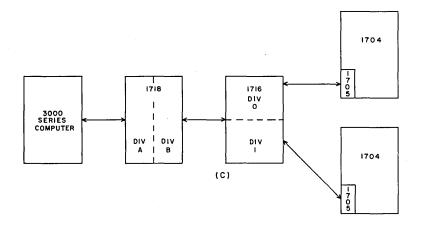

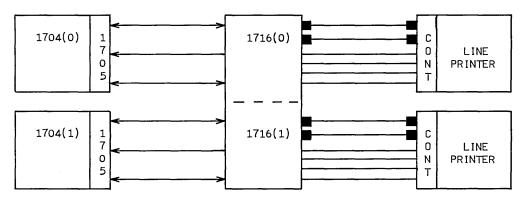

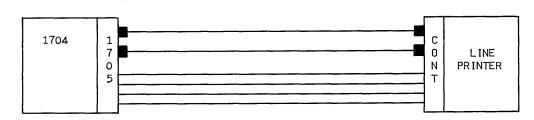

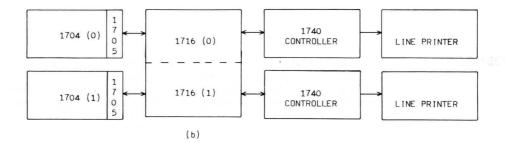

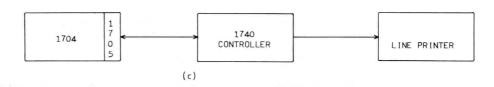

The 1716 provides a bidirectional 16-bit data path between two 1704 Computers, each with a 1705 Interrupt Data Channel. It also provides a Buffered Data Channel to which may be attached up to eight peripheral equipments, with a maximum word transfer rate of 900 kc. Figure 1 shows the relationship between the 1716 and other equipments.

Figure 1. Typical 1716 Configuration

The 1716 is divided into two sections, called division 0 and division 1. Each of these sections is connected to a 1705 Interrupt Data Channel and a 1704 computer. The computer attached to division 0 will be called computer 0, the one on division one, computer 1. A maximum of three 1716's may be connected to a 1705 Interrupt Data channel. A 1706 Buffered Data Channel may replace any or all of the 1716's.

<sup>\*</sup>Registered trademark of Control Data Corporation

With the exception of the Program Protect switches, the 1716 is controlled entirely by the Input to A and Output from A instructions from the 1704. The operations for the 1716 are the same as those for the 1706 BDC, with the addition of a Buffered Transfer operation. This operation allows the sending of data directly between the storage of the two connected computers, or from one portion of one computer's storage to another portion of the same computer's storage. In response to an I/O instruction from either computer (and the contents of the respective Q registers) the 1716 connects the computer to the other computer, or to one of the peripheral equipments, and sends the appropriate Read or Write signal; it then controls the transfer of the information. On buffered operations, the 1716 obtains access to storage through the Direct Storage Access Bus of either computer.

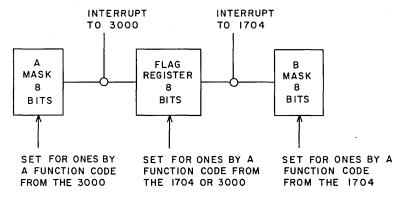

Interrupt

The 1716 has one interrupt line to each computer. The interrupts are generated by End of Operation (if enabled) or by matching conditions in the flag and mask bits. The End of Operation interrupt is sent to the computer that initiated the operation. The Flag/Mask interrupt is sent to the computer having a mask bit matching the corresponding flag bit. The flags are shared while each computer has its own mask bits. Use of the interrupt conditions is explained in detail under the Function operation.

**Program Protection** The 1716 has two Program Protect switches, one associated with each division. When a switch is ON, only those I/O instructions having a "1" on the protect line will be recognized. An instruction not having a "1" on the protect line will be rejected. The Function instruction will not be rejected; it will be ignored. When the switch is OFF, protected and unprotected instructions will be recognized.

Reply/Reject

The 1716 responds within 4 microseconds to an Input to A or Output from A instruction with either a Reply or a Reject signal. A Reply will be sent whenever the computer can perform the requested operation. The following conditions will cause a Reject to be sent:

- 1) a program protect violation

- 2) the 1716 is Busy (if attempting a direct or buffered operation)

- 3) a device returns a Reject (direct output or input)

If the computer receives no response, it will generate an internal Reject. Function is not rejected on a program protect violation.

# PROGRAMMING

Summary of Programming Information

Tables 1, 2, and 3 are a summary of the information necessary to program the 1716. Explanations of the information presented here can be found in the following sections. The tables here are intended as a quick reference for the experienced programmer, and a summary for the reader interested in the general programming capabilities of the 1716.

| W*            |            |            | COMPUTER INSTRUCTION                     |                                       |  |

|---------------|------------|------------|------------------------------------------|---------------------------------------|--|

| 1716<br>#3    | 1716<br>#2 | 1716<br>#1 | INPUT TO A                               | OUTPUT FROM A                         |  |

| 0B            | 06         | 01         |                                          | Buffered Transfer                     |  |

| 0C            | 07         | 02         | Direct Input                             | Direct Output                         |  |

| $0\mathrm{D}$ | 08         | 03         | Terminate Buffer<br>1716 Current Address | Function (See 1716<br>Function Table) |  |

| $0\mathrm{E}$ | 09         | 04         | 1716 Status                              | Buffered Output                       |  |

| 0F            | 0A         | 05         | 1716 Current Address                     | Buffered Input                        |  |

# TABLE 1. 1716 ADDRESSES AND OPERATIONS

\*The left digit is binary, the right digit hexidecimal.

( )

$\bigcirc$

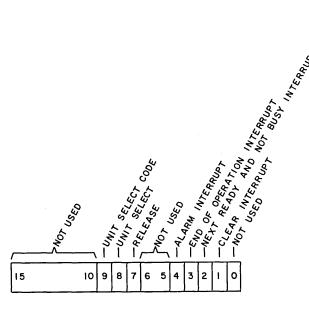

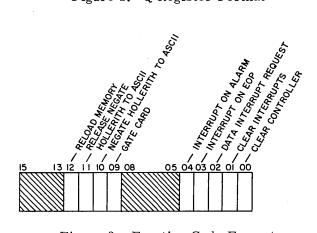

TABLE 2. 1716 FUNCTIONS

| MEANING                              |  |

|--------------------------------------|--|

| Set condition for ones in A14-A00*   |  |

| Clear condition for ones in A14-A00* |  |

| Flag 4                               |  |

| Flag 3                               |  |

| Flag 2                               |  |

| Flag 1                               |  |

| Flag 0                               |  |

| Mask 4                               |  |

| Mask 3                               |  |

| Mask 2                               |  |

| Mask 1                               |  |

| Mask 0                               |  |

| (Not defined)                        |  |

| Reserve flag                         |  |

| (Not defined)                        |  |

| (Not defined)                        |  |

| Interrupt on 1716 End of Operation*  |  |

|                                      |  |

\*Functions also used in the 1706.

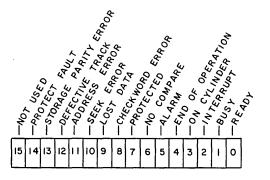

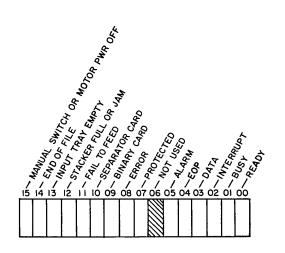

TABLE 3. 1716 STATUS BITS

| BIT SET IN A REGISTER | MEANING                |

|-----------------------|------------------------|

| 15                    | (Not used)             |

| 14                    | Flag 4                 |

| 13                    | Flag 3                 |

| 12                    | Flag 2                 |

| 11                    | Flag 1                 |

| 10                    | Flag 0                 |

| 9                     | Device Reply*          |

| 8                     | Device Reject*         |

| 7                     | (Not used)             |

| 6                     | Program Protect Fault* |

| 5                     | (Not used)             |

| 4                     | End of Operation*      |

| 3                     | Reserve Flag           |

| 2                     | Interrupt*             |

| 1                     | Busy*                  |

| 0                     | Ready*                 |

\*Status also used in the 1706.

3

Addresses

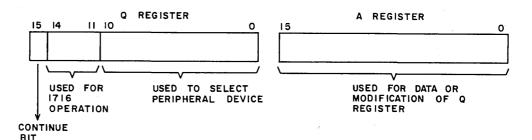

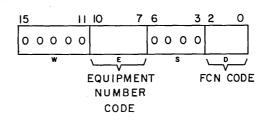

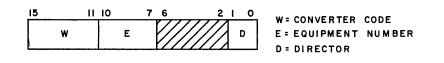

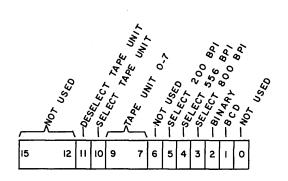

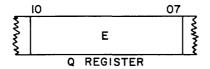

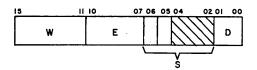

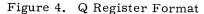

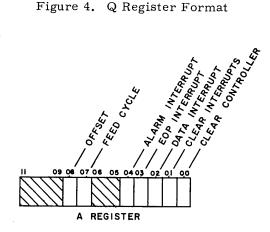

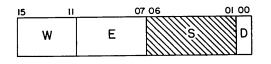

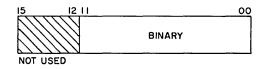

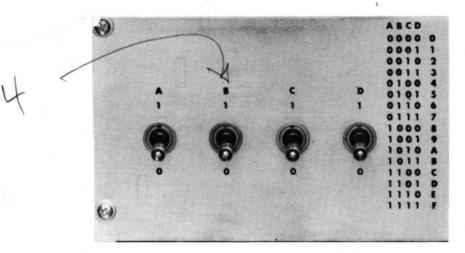

Figure 2. 1700 Q and A Registers

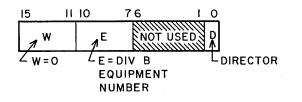

Bits 11-15 of the Q register are used to select the desired 1716 operation, while bits 00-10 are used to select the desired peripheral device. (See Figure 2). The 1716 provides a W = 0 signal to devices connected to it. Bits 11-14 are used to define 1716 operations (see Table 1) and bit 15 is the continue bit, \* used as follows:

- 1) Address the device with Q15 = 0 and the remainder of Q set to select that device; the device is then connected.

- 2) All succeeding addresses with Q15 = 1 will be recognized by this device. Thus 15 bits of addressing are available to the device.

- 3) The next address with Q15 = 0 will disconnect the device unless it is the address of that device.

The 1716 will interpret an address with Q15 = 1 as a direct input on an Input to A instruction, and as a direct output on an Output from A instruction.

**Operations**

Besides selecting a particular 1716, the W field of Q, combined with a 1704 Input to A or Output from A instruction, specifies an operation. The Function operation may be further modified by the contents of the A register. Tables 1 and 2 list the addresses, operations, and functions. Because W is a 5-bit field and bit 15 is used as a Continue bit, W is expressed as a 2-digit number: the right digit is hexadecimal (4 bits), the left digit binary (1 bit).

# Operations Defined by W and Input to A

<u>Direct Input</u>: Whenever the computer executes an Input to A instruction to a 1716 with the W field of Q selecting a direct input, Q is stored in the 1716 and presented to the devices attached to the 1716 and one 16-bit word is transferred into the A register from the selected device. The word may be a data word or the status of a device on the 1716. This mode of operation is in every way identical to that of the AQ channel. The Continue bit functions as described previously. If an attempt is made to do a direct input when the 1716 is busy, the 1716 will respond with a Reject. It is therefore impossible to status a device on the 1716 during a buffered operation.

\*This only on certain devices. The 1718 is one such device.

<u>Terminate Buffer, 1716 Current Address</u>: This terminates a buffered operation and loads the current address of the word being transferred into the A register. This instruction is intended to terminate hung-up input buffers, and in this case the A register will contain the address of the next word to be transferred. Otherwise, the address sent may be either that of the last word or the next word. Which one will depend on the timing of the 1704/1716 device; i.e., when the instruction reaches the 1716.

<u>1716 Status</u>: This operation will load the status word from the 1716 into the A Register of the computer. Table 3 lists the bits in the status word. The following list explains their meaning.

Flag 4 (Bit 14 = 1) - Shared flag 4 is set. \* Flag 3 (Bit 13 = 1) - Shared flag 3 is set. Flag 2 (Bit 12 = 1) - Shared flag 2 is set. Flag 1 (Bit 11 = 1) - Shared flag 1 is set. Flag 0 (Bit 10 - 1) - Shared flag 0 is set.

Device Reply (Bit 9 = 1) - The peripheral device accepted the last word transfer attempted from the 1716.

Device Reject (Bit 8 = 1) - The peripheral device rejected the last word transfer attempted from the 1716.

Program Protect Fault (Bit 6 = 1) - A reference to computer storage has caused a program protect violation.

End Of Operation (Bit 4 = 1) - A buffered input, output, or transfer has been completed.

Reserve Flag (Bit 3 = 1) - The reserve flag for this computer is set. This indicates that the other computer is not using the 1716.

Interrupt (Bit 2 = 1) - An interrupt has been sent from the 1716 to the computer.

Busy (Bit 1 = 1) - This bit is set from the time the 1716 accepts an output word from the computer initiating a block transfer until the transfer is completed, or during a direct input or output operation.

Ready (Bit 0 = 1) - The power is on.

<u>1716 Current Address</u>: This code will cause the address of the current word being transferred on a buffered operation to be loaded into the A register of the computer requesting the status. This same word is also loaded into the A register following a Terminate Buffer operation.

#### NOTE

Status requests are never rejected on the 1716 unless a prógram protect violation has occurred.

<sup>\*</sup>Flags are explained in more detail under 1716 Function.

# Operations Defined by W and Output from A

<u>Direct Output</u>: Whenever the computer executes an Output from A instruction with W selecting direct output, Q is stored in the 1716 and sent to the attached peripheral devices, and one 16-bit word is transferred from the A register to the selected device. This mode of operation is identical in every way to that of the AQ Channel. The Continue bit functions as described before. If an attempt is made to do a direct output when the 1716 is busy, the 1716 responds with a Reject.

<u>Function</u>: This code transmits the function word to the 1716. Table 2 lists the bits in the word. The following list explains their meaning.

(Bit 15 = 1) - If bit 15 is a "1", those conditions indicated by "1's" in bits 0 through 14 will be set in the 1716. Bits not set will not be affected by bit 15.

(Bit 15 = 0) - If bit 15 is a "0", those conditions indicated by "1's" in bits 0 through 14 will be cleared in the 1716. Bits not set will not be affected by bit 15.

| Flag 4 (Bit 14 = 1)              | The flag and mask bits are used to send interrupts        |

|----------------------------------|-----------------------------------------------------------|

| Flag 3 (Bit 13 = 1)              | between the two computers. The five flag bits are         |

| Flag 2 (Bit 12 = 1)              | shared by both computers. Each computer has its           |

| Flag 1 (Bit 11 = 1)              | own set of mask bits. If a mask bit and its correspond-   |

| Flag 0 (Bit 10 = 1) $\downarrow$ | ing flag bit are both set (for example mask 1 and flag 1) |

| Mask 4 (Bit 9 = 1)               | an interrupt will be sent to the computer whose mask      |

| Mask 3 (Bit 8 = 1)               | bit is set. The interrupt will be cleared by the End      |

| Mask 2 (Bit 7 = 1)               | of Operation interrupt, or if the flag or mask bit        |

| Mask 1 (Bit 6 = 1)               | causing it is cleared.                                    |

| Mask 0 (Bit 5 = 1) 🗸             |                                                           |

Reserve flag (Bit 4 = 1) - One reserve flag bit is associated with each computer; it is set and cleared in the same manner as the other flag bits. The two reserve flags cannot be set at the same time; that is, when one is set, the other will not respond to a function signal intended to set it. The function will not be rejected. The reserve flag can be cleared by a function from the computer that set the flag, or by a Master Clear or Terminate Buffer operation from either computer. The intended purpose of the reserve flag bit is to indicate to the computer whether or not the other computer is using the 1716. Before issuing instructions to move data, a function to set the reserve flag should be executed, followed by a status instruction. If the reserve flag is set, it indicates the other computer is not using the 1716; i. e., its flag is not set.

Interrupt on End of Operation (Bit 0 = 1) - An interrupt will be sent at the end of a buffered operation. The interrupt will be sent to the computer that initiated the operation. Clearing this bit will also clear the interrupt.

# NOTE

Function requests are never rejected by the 1716.

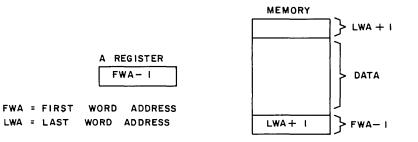

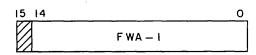

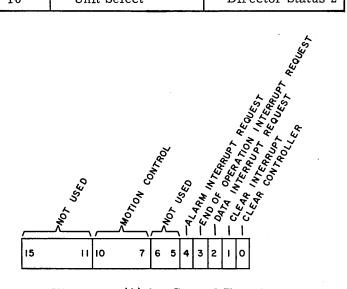

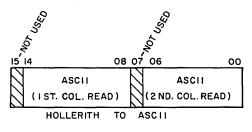

Figure 3. Address Arrangement for Buffered Input and Output

$\bigcirc$  $\bigcirc$  $\bigcirc$  <u>Buffered Output:</u> A buffered output is initiated when the computer executes an Output from A instruction and the W field of Q selects a buffered output. (See Figure 3.) Q is stored in the 1716, then placed on the 1716 channel, and the contents of A is transferred to the 1716. The contents of A specifies the first word address minus one (FWA-1) of the block to be transferred. The contents of location FWA-1 specifies the last word address plus one (LWA+1) of the block to be transferred. The 1716 begins the data transfer by raising the Write signal to the device. The device responds within four microseconds by raising the Reply signal to the 1716. The 1716 then advances to the next data word, repeating this cycle until the block of data has been transferred.

If the 1716 receives a Reject, it indefinitely repeats the transfer of the word until the word is accepted. The address is not reissued to storage. The 1716 does not generate an internal reject. If an attempt is made to establish a buffered output when the 1716 is busy, the 1716 responds with a Reject.

<u>Buffered Input</u>: A buffered input is initiated when the computer executes an Output from A instruction and the W field of Q selects a buffered input. (See Figure 3.) Q is stored in the 1716, then placed on the 1716 channel and the contents of A is transferred to the 1716. The contents of A specifies the location of the first word address minus one (FWA-1) of the block where the data is to be stored. The contents of the location FWA-1 specifies the last word address plus one (LWA+1) of this block. The 1716 begins the data transfer by raising the Read signal to the device. The device responds within four microseconds by raising the Reply signal to the 1716. The 1716 then advances to the next data word and repeats this cycle until the block of data has been transferred.

If the 1716 receives a Reject from the device, it repeats the transfer of the word indefinitely until the word is accepted. The 1716 does not generate an internal reject. If an attempt is made to establish a buffered input when the 1716 is busy, the 1716 will respond with a Reject.

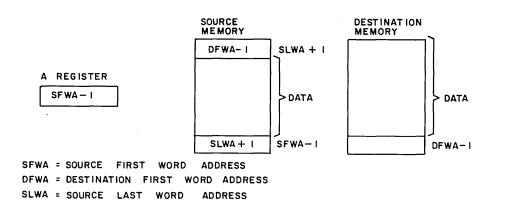

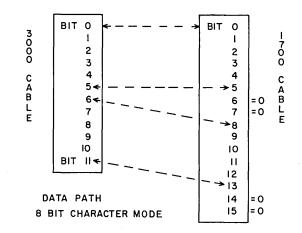

Figure 4. Address Arrangement for Buffered Transfer

<u>Buffered Transfer:</u> In this mode, data is transferred directly to/from computer core storage via the 1716 (see Figure 4). The transfer is initiated by one computer executing an Output from A instruction with the W field of Q selecting a buffered transfer (see Table 4). The transfer is accomplished by defining the bounds of the source data and the FWA-1 of the destination location. The output to the 1716 initiates the buffer transfer and sends via the A register the source data FWA-1 (SFWA-1). The contents of SFWA-1 is the source data LWA+1 (SLWA+1). The contents of SLWA+1 is the destination data FWA-1 (DFWA-1). Bit 15 of all these addresses refers to the "other" computer if it is set; "this" computer if not set. It is thus possible to make a block transfer within a single computer's core storage. All flag, mask, and status functions of the 1716 are available in the buffer transfer mode.

#### NOTE

On all buffered operations, bit 15 of the address is used to determine which computer is to send or receive the data. If bit 15 is a "1", it means the "other" computer; if bit 15 is a "0", it means "this" computer.

Care should be taken to keep the starting and ending addresses of blocks of data to be transferred within the following limits:

#### 0000 - 7FFF, or 8000 - FFFF

If, during the transfer, the range of addresses crosses either of the above boundaries (7FFF to 8000, or FFFF to 0000), bit 15 will change value and data may be sent to or received by the wrong computer.

# $\bigcirc$

# Programming Considerations

| Co | nsi | de | rai | non | S |

|----|-----|----|-----|-----|---|

|    |     |    |     |     |   |

| ·                   |                                                                                                                |      |                                                                                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------|

| 1704<br>Instruction | Q Register                                                                                                     | Step | Action                                                                                             |

| LDQ                 | Selected 1716<br>Status Request                                                                                | 1)   | Initiate operating status check of desired 1716.                                                   |

| INP                 |                                                                                                                | 2)   | A register now contains the operat-<br>ing status of the desired 1716.                             |

|                     |                                                                                                                | 3)   | Check status in A for Ready and Not Busy.                                                          |

| LDQ                 | Selected 1716<br>Function                                                                                      | 4)   | Initiate setting of reserve flag.                                                                  |

| LDA                 |                                                                                                                | 5)   | Set reserve flag.                                                                                  |

| OUT                 |                                                                                                                | 6)   | If reserve flag is available, it will be set.                                                      |

|                     |                                                                                                                | 7)   | Repeat 1-3 to check for reserve<br>flag set. If not set, wait and repeat<br>1-6.                   |

| LDQ                 | W = Direct Input<br>on selected 1716,<br>Bits 0-10 specify<br>status request<br>for equipment                  | 8)   | Initiate status check of equipment<br>to be used.                                                  |

| INP                 |                                                                                                                | 9)   | A register now contains the equip-<br>ment status.                                                 |

|                     |                                                                                                                | 10)  | Check equipment status for desired conditions.                                                     |

|                     |                                                                                                                | 11)  | Repeat 8-10 for station and unit, if necessary.                                                    |

| LDQ                 | Selected 1716<br>Function                                                                                      | 12)  | Initiate selection or clearing of<br>Interrupt on End of Operation.                                |

| LDA                 |                                                                                                                | 13)  | Load A with desired operation.                                                                     |

| OUT                 |                                                                                                                | 14)  | Interrupt on End of Operation is<br>now enabled or disabled. Any<br>existing interrupt is cleared. |

| LDQ                 | W = Direct Output<br>on selected 1716.<br>Bits 0-10 specify<br>an operation on<br>the equipment or<br>station. | 15)  | Initiate selection of peripheral<br>equipment operating conditions and<br>interrupts.              |

| LDA                 |                                                                                                                | 16)  | If necessary, load A with the code<br>further specifying the operation<br>indicated by (Q).        |

| OUT                 |                                                                                                                | 17)  | Execute Output from A instruction                                                                  |

|                     |                                                                                                                | 18)  | Repeat 15-17 until all desired operating conditions are specified.                                 |

|                     |                                                                                                                |      |                                                                                                    |

| 1704<br>Instruction                  | Q Register                                                                                                                                               | Step     | Action                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For a Direct Input or Output of Data |                                                                                                                                                          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LDQ                                  | W = Direct Input<br>or Direct Output<br>on selected 1716.<br>Bits 1-10 select<br>equipment and<br>station. Bit 0 =<br>"0" for data<br>transfer.          | 19D*)    | Select desired type of I/O.                                                                                                                                                                                                                                                                                                                                                                                                           |

| LDA                                  |                                                                                                                                                          | 20D)     | If doing a direct output, load the data into A; if direct input, skip this step.                                                                                                                                                                                                                                                                                                                                                      |

| INP or<br>OUT                        |                                                                                                                                                          | 21D)     | Execute 1704 Input to A or Output<br>from A, depending on desired<br>direction of data transfer.                                                                                                                                                                                                                                                                                                                                      |

|                                      |                                                                                                                                                          | 22D)     | Skip to 22B.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | For a Buffere                                                                                                                                            | ed Input | or Output of Data                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LDQ                                  | W = Buffered<br>Input or Buff-<br>ered Output on<br>selected 1716.<br>Bits 1-10 select<br>equipment and<br>station. Bit 0 =<br>"0" for data<br>transfer. | 19B†)    | Select desired type of buffered I/C                                                                                                                                                                                                                                                                                                                                                                                                   |

| LDA                                  |                                                                                                                                                          | 20B)     | Load A with the FWA-1 of the<br>buffer area. The contents of<br>memory at this address must<br>contain the LWA + 1 of the buffer<br>area.                                                                                                                                                                                                                                                                                             |

| OUT                                  |                                                                                                                                                          | 21B)     | The buffered transfer is now initiated and under control of the 1716.                                                                                                                                                                                                                                                                                                                                                                 |

|                                      |                                                                                                                                                          | 22B)     | Status the converter (as in steps<br>1-3, checking for desired condi-<br>tions, or by using the 1716 curren<br>address status) or proceed with th<br>main program until an interrupt<br>occurs. Using interrupts takes<br>advantage of the capabilities of the<br>buffered data channel to do I/O<br>without hanging up the computer.<br>It is not possible to status a devic<br>connected to the 1716 as long as th<br>1716 is Busy. |

$\ast$  D indicates a step for the direct transfer of data.

† B indicates a step for the buffered input or output of data.

## **Buffered** Transfer

The buffered transfer is programmed in much the same way as the buffered input or buffered output. There are four basic transfers:

- "this" computer to "this" computer "this" computer to "other" computer "other" computer to "this" computer "other" computer to "other" computer 1)

- 2)

- 3)

- 4)

Bit 15 of the 3-address word determines the type of transfer.

1) this to this - Bit 15 of SFWA\*, SLWA+1, and DFWA-1 is zero. This transfer can be used to relocate data in memory.

Computer 1

#### Computer 2

Computer 2

DFWA

| Q = 1   | W  | For Buffer            | XFER |

|---------|----|-----------------------|------|

| A = [   | 0  | For Buffer<br>SFWA-11 |      |

| INSTR = | οτ | JT                    |      |

| SFWA-1 | O SLWA+1      |

|--------|---------------|

|        | DATA<br>OUT · |

| SLWA+1 | O DFWA-1      |

| DFWA   | DATA<br>IN    |

- Bit 15 of SFWA-1, SLWA+1 is zero. Bit 15 of DFWA-1 is one. This will transfer data to the other 2) this to other computer and store it beginning at DFWA.

Computer 1

Q = W For Buffer XFER A = O SFWA-1

INSTR = OUT

| SFWA-1 | 0 | SLWA+1      |

|--------|---|-------------|

| ,      |   | DATA<br>OUT |

| SLWA+1 | 1 | DFWA-1      |

other to this

3)

- Bit 15 of SFWA-1 is a one, SLWA+1 is a zero. Bit 15 of DFWA-1 is one. This will move data from the other computer and store it in this computer, beginning at DFWA. Use of this transfer requires some prearranged programming so this computer knows where in the other computer the data to be transferred is located.

DATA IN

Computer 1

Computer 2

Q = W For Buffer XFER A = 1 SFWA-1 INSTR = OUT

| С                                                            |

|--------------------------------------------------------------|

| $\bigcirc$                                                   |

| С                                                            |

| $\bigcirc$                                                   |

| $\bigcirc$                                                   |

|                                                              |

| $\left(\begin{array}{c} \\ \end{array}\right)$               |

| $\left( \begin{array}{c} \cdot \\ \cdot \end{array} \right)$ |

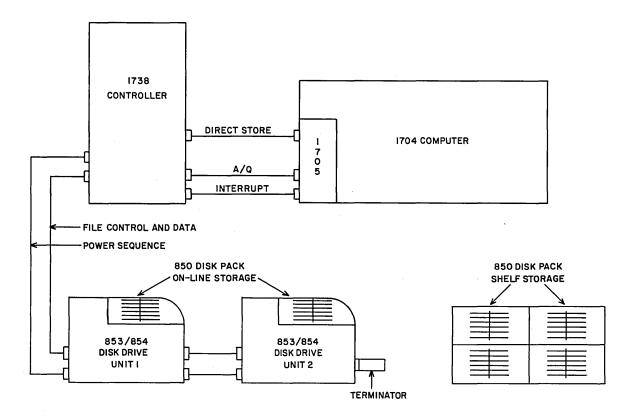

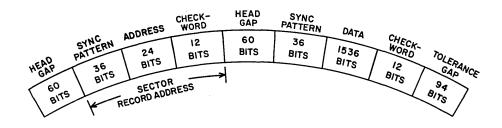

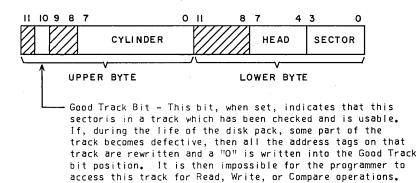

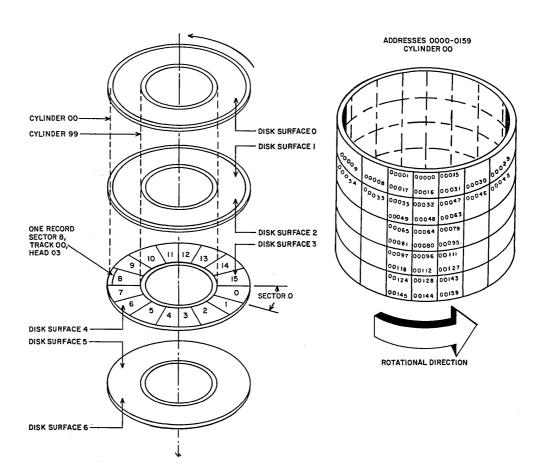

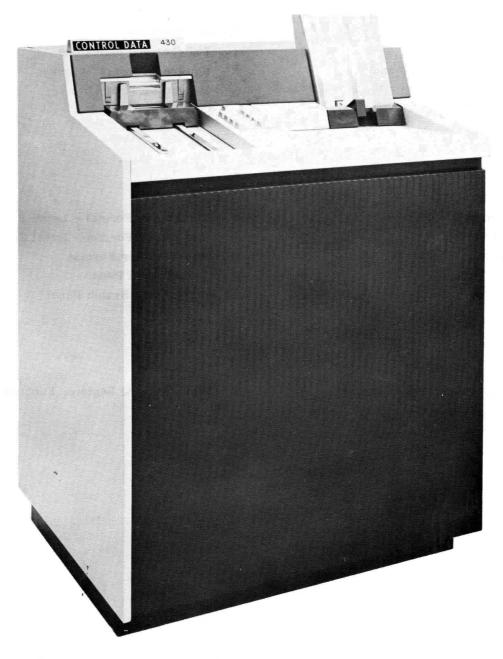

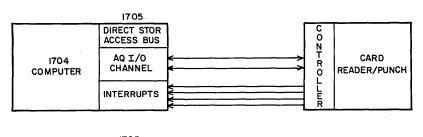

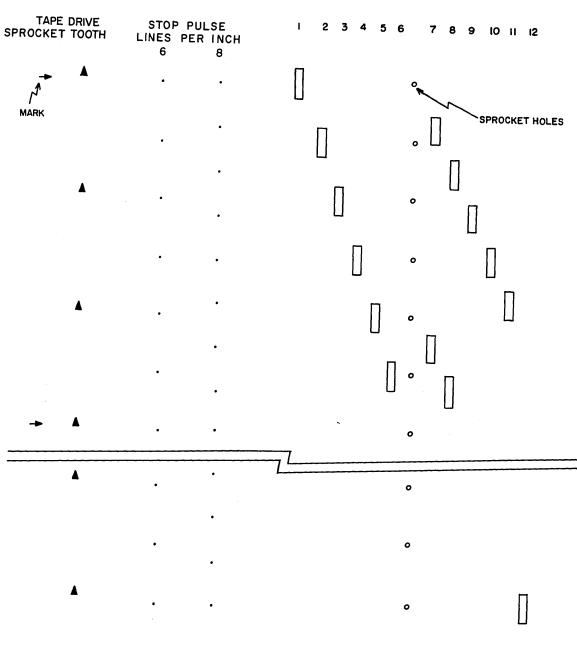

|                                                              |