CL550/CL560 JPEG COMPRESSION PROCESSOR USER'S MANUAL

## CL550/CL560 JPEG Compression Processor User's Manual

C-Cube Microsystems This document is preliminary. The specifications contained herein are derived from functional specifications and performance estimates, and have not been verified against production parts.

C-Cube Microsystems reserves the right to change any products described herein at any time and without notice. C-Cube Microsystems assumes no responsibility or liability arising from the use of the products described herein, except as expressly agreed to in writing by C-Cube Microsystems. The use and purchase of this product does not convey a license under any patent rights, copyrights, trademark rights, or any other intellectual property rights of C-Cube Microsystems.

#### **Trademark Acknowledgment:**

C-Cube, CL550, and CL560 are trademarks of C-Cube Microsystems. The corporate logo is a registered trademark of C-Cube Microsystems.

Windows and Video-for-Windows are trademarks of Microsoft Corporation. Apple and Apple QuickTime are trademarks of Apple Computer, Inc.

© C-Cube Microsystems 1993 All rights reserved

> C-Cube Microsystems 1778 McCarthy Boulevard Milpitas, CA 95035 Telephone (408) 944-6300 Fax (408) 944-6314

#### **Customer Comments and Feedback:**

If you have comments about this document, send them to the C-Cube Technical Publications Department at the address listed above, or send e-mail to:

techpubs @ c-cube.com

C-Cube Part # 90-1556-101, Revision A

## Preface

This manual is the primary users guide for the C-Cube CL550 and CL560 JPEG Compression Processors. It contains detailed information about the CL550 and CL560 hardware and also provides general information on how to program the parts.

This manual is intended for:

- System designers and managers who are evaluating the CL550 and CL560 for possible use in a system

- Designers and hardware engineers who are designing a system based on the CL550 and CL560

- Programmers and software engineers who are writing application programs that interact with the CL550 and CL560

This manual is divided into these chapters:

□ Chapter 1, Introduction, presents an introduction to the architecture of the CL550 and CL560

#### Audience

Organization

Preface iii

| Charter 2 IDEC Occernicate analytics a brief evention of the IDEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Chapter 2, JPEG Overview, provides a brief overview of the JPEG<br/>algorithm used by the compression processors.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

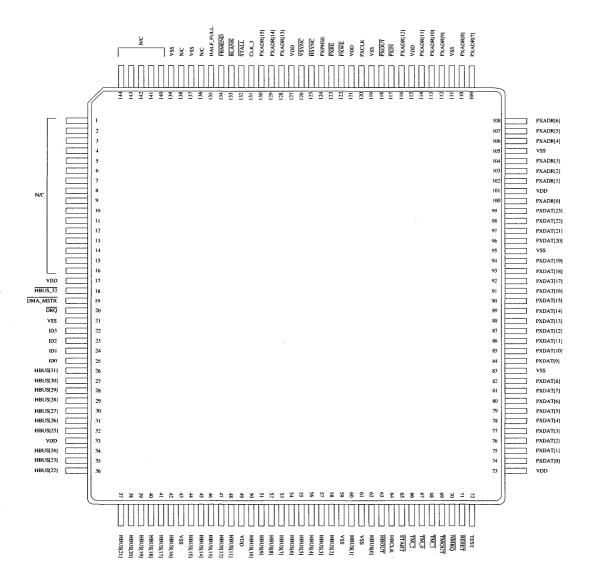

| <ul> <li>Chapter 3, Signal Descriptions, describes the function of each of<br/>the external signals on the CL550 and CL560.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>Chapters 4 and 5, Host Interface and Video Interface, present<br/>functional descritions for the main interfaces of the CL550 and<br/>CL560.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Chapter 6, Specifications, includes detailed electrical and me-<br/>chanical specifications.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Chapter 7, Registers, describes in detail each of the internal registers of the CL550 and CL560.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>Chapter 8, System Designer's Guide, provides a general overview<br/>on programming the CL550 and CL560 with initialization proce-<br/>dures and compression/decompression procedure flowcharts.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Please note the following conventions that are used in this manual:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>Hexadecimal numbers are indicated by the prefix 0x, for example,<br/>0xFF. Binary numbers are indicated by a subscript, for example,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $10_2$ . Otherwise, all numbers used in this guide are decimal numbers unless otherwise noted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $10_2$ . Otherwise, all numbers used in this guide are decimal num-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul><li>102. Otherwise, all numbers used in this guide are decimal numbers unless otherwise noted.</li><li>This manual, part # 90-1556-101 Rev A., supersedes the previous revi-</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>10<sub>2</sub>. Otherwise, all numbers used in this guide are decimal numbers unless otherwise noted.</li> <li>This manual, part # 90-1556-101 Rev A., supersedes the previous revision by the same name. The major content changes include: <ul> <li>Chapter 6, Specifications: AC timing parameters are listed for 7 products and speed grades:</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>10<sub>2</sub>. Otherwise, all numbers used in this guide are decimal numbers unless otherwise noted.</li> <li>This manual, part # 90-1556-101 Rev A., supersedes the previous revision by the same name. The major content changes include: <ul> <li>Chapter 6, Specifications: AC timing parameters are listed for 7 products and speed grades:</li> <li>Chapter 6, Chapter 6, Chapt</li></ul></li></ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **Contents**

| 1 | Intr | oduction                        |     |

|---|------|---------------------------------|-----|

|   | 1.1  | CL550 Features                  | 1-2 |

|   | 1.2  | CL560 Improvements              | 1-2 |

|   | 1.3  | Applications                    | 1-3 |

|   | 1.4  | Product Family                  | 1-3 |

|   | 1.5  | CL550 Functional Description    | 1-4 |

|   | 1.6  | CL560 Functional Description    | 1-6 |

| 2 | JPE  | G Overview                      |     |

|   | 2.1  | JPEG Background Information     | 2-2 |

|   | 2.2  | Operation of the JPEG Algorithm | 2-3 |

|   | 2.3  | Discrete Cosine Transform       | 2-4 |

|   | 2.4  | Quantization                    | 2-5 |

|   | 2.5  | Zero Run-length Coding          | 2-7 |

|   | 2.6  | Entropy Encoding                | 2-8 |

|   | 2.7  | Summary of JPEG Baseline        | 2-8 |

| 3 | Sig  | nal Descriptions                |     |

|   | 3.1  | Host Interface                  | 3-3 |

|   |      | 3.1.1 Data Transfer Signals     | 3-3 |

|   |      | HBUS[31:0]                      | 3-3 |

|     |         | HBOUT                                     | 3-4  |

|-----|---------|-------------------------------------------|------|

|     |         | HBUS_32                                   | 3-4  |

|     |         | ID[3:0]                                   | 3-4  |

|     | 3.1.2   | DMA Signals                               | 3-4  |

|     | 0.1.2   | DRO                                       | 3-4  |

|     |         | DMA_MSTR                                  | 3-4  |

|     | 3.1.3   | Interrupt Signals                         | 3-5  |

|     | 00      | NMRQ                                      | 3-5  |

|     |         | HALF_FULL                                 | 3-5  |

|     |         | IRQ1                                      | 3-5  |

|     |         | IRQ2                                      | 3-5  |

|     | 3.1.4   | Timing and Control Signals                | 3-6  |

|     |         | START                                     | 3-6  |

|     |         | TMO                                       | 3-6  |

|     |         | TM1                                       | 3-6  |

|     |         | TM2                                       | 3-7  |

|     |         | TMOUT                                     | 3-7  |

|     |         | FRMEND                                    | 3-7  |

|     |         | HBCLK                                     | 3-7  |

|     |         | RESET                                     | 3-7  |

|     |         | TEST                                      | 3-8  |

| 3.2 |         | Interface                                 | 3-8  |

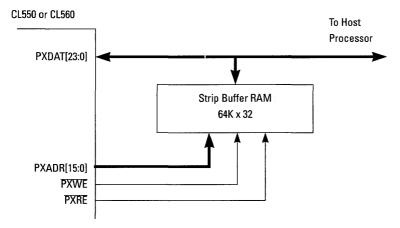

|     | 3.2.1   | Pixel Data, Address and Handshake Signals | 3-8  |

|     |         | PXDAT[23:0]                               | 3-8  |

|     |         | PXADR[15:0]                               | 3-8  |

|     |         | PXRE                                      | 3-8  |

|     |         | PXWE                                      | 3-9  |

|     |         | PXIN                                      | 3-9  |

|     |         | PXOUT                                     | 3-9  |

|     |         | STALL                                     | 3-10 |

|     | 3.2.2   | Video Synchronization Signals             | 3-10 |

|     |         | HSYNC                                     | 3-10 |

|     |         | VSYNC                                     | 3-10 |

|     |         | BLANK                                     | 3-10 |

|     | 3.2.3   | Video Clock Signals                       | 3-11 |

|     |         | PXCLK                                     | 3-11 |

|     |         | PXPHASE                                   | 3-11 |

|     |         | CLK3                                      | 3-11 |

| Hos | st Inte | rface                                     |      |

| 4.1 | Regis   | ter Access Timing                         | 4-3  |

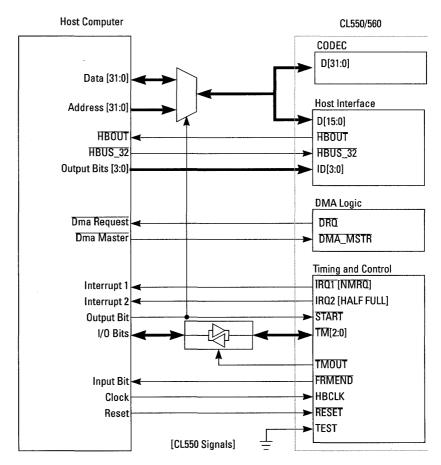

|     | 4.1.1   | Signal Descriptions                       | 4-3  |

4.1.1 Signal Descriptions

4

|   |      | 4.1.2 Register Access Timing                        | 4-7  |

|---|------|-----------------------------------------------------|------|

|   |      | 4.1.3 Host Bus Register Access                      | 4-9  |

|   |      | 4.1.4 Host Bus Register Write                       | 4-11 |

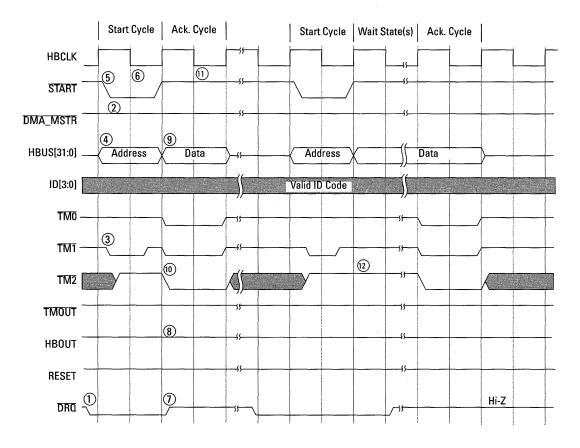

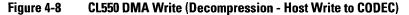

|   | 4.2  | DMA Access Timing                                   | 4-12 |

|   |      | 4.2.1 CL560 DMA Transfers                           | 4-14 |

|   |      | 4.2.2 CL560 DMA Write Transaction Timing            | 4-15 |

|   |      | 4.2.3 CL560 DMA Read Transaction Timing             | 4-17 |

|   |      | 4.2.4 Alternative Method of CL550/560 DMA Transfers | 4-19 |

|   |      | 4.2.5 CL550 Burst-mode Write Transaction Timing     | 4-20 |

|   |      | 4.2.6 CL550 Burst-mode Read Transaction Timing      | 4-22 |

|   |      | 4.2.7 Operational Considerations                    | 4-23 |

|   | 4.3  | Control Signals                                     | 4-25 |

|   |      | 4.3.1 RESET                                         | 4-25 |

|   |      | 4.3.2 NMRQ                                          | 4-26 |

|   |      | 4.3.3 HALF_FULL                                     | 4-26 |

|   |      | 4.3.4 IRQ1, IRQ2                                    | 4-26 |

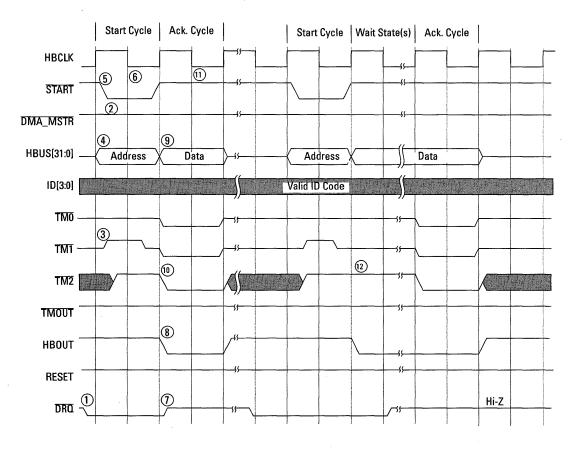

| 5 | Vide | eo Interface                                        |      |

| - | 5.1  | Overview                                            | 5-2  |

|   |      | 5.1.1 Signal Descriptions                           | 5-3  |

|   |      | 5.1.2 Video Interface Clocks                        | 5-4  |

|   |      | 5.1.3 Master/Slave Mode Operation                   | 5-7  |

|   |      | 5.1.4 STALL Operation                               | 5-7  |

|   | 5.2  | Video Interface Logic                               | 5-10 |

|   |      | 5.2.1 Pixel Order Conversion                        | 5-10 |

|   |      | 5.2.2 Window Management and Control                 | 5-12 |

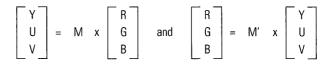

|   |      | 5.2.3 Color Conversion                              | 5-12 |

|   | 5.3  | Basic System Configurations                         | 5-14 |

|   | 5.4  | Timing Diagrams Compression Mode                    | 5-17 |

|   | 5.5  | Timing Diagrams Decompression Mode                  | 5-29 |

| 6 | Spe  | cifications                                         |      |

|   | -    | Operating Conditions                                | 6-2  |

|   | 6.2  | AC Characteristics                                  | 6-3  |

|   |      | 6.2.1 Host Interface Control Signal Timing          | 6-4  |

|   |      | 6.2.2 Video Interface Signal Timing                 | 6-16 |

|   | 6.3  | Package Specifications                              | 6-23 |

|   |      | 6.3.1 144-Pin Ceramic Pin-Grid Array                | 6-24 |

|   |      | 6.3.2 144-Pin MQUAD Package                         | 6-29 |

| 7 | Rea  | isters                                              |      |

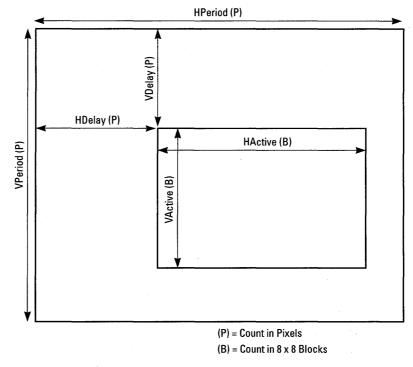

|   | 7.1  | Video Interface Registers                           | 7-6  |

|   |      | HPeriod Register                                    | 7-7  |

| HSync Register                               | 7-8    |

|----------------------------------------------|--------|

| HDelay Register                              | 7-8    |

| HActive Register                             | 7-9    |

| VPeriod Register                             | 7-9    |

| VSync Register                               | 7-10   |

| VDelay Register                              | 7-10   |

| VActive Register                             | 7-11   |

| Video Latency Register                       | 7-11   |

| Vertical Line Count Register                 | 7-12   |

| HControl Register                            | 7-12   |

| VControl Register                            | 7-12   |

| HV Enable Register                           | 7-13   |

| Color Transformation Matrix                  | 7-13   |

| DCT Tables                                   | 7-15   |

| Compression and Decompression Registers      | 7-15   |

| Quantizer Tables                             | 7-15   |

| Quantizer A/B Table Select Register          | 7-16   |

| Quantizer Y/C Table Sequence Register        | 7-17   |

| Quantizer A/B Table Sequence Register        | 7-18   |

| Quantizer Sync Register                      | 7-18   |

| Coder/Decoder DPCM Reg. Seq. Registers, RH   | 7-19   |

| Coder/Decoder DPCM Reg. Seq. Registers, RL   | 7-19   |

| Decoder DPCM Reset Register                  | 7-20   |

| Huffman Code Tables                          | 7-20   |

| Huffman Table Load Enable Register           | 7-20   |

| Huffman Table Sequence Register              | 7-21   |

| Coder Attributes Register                    | 7-21   |

| Coder Coding Interval Registers              | 7-22   |

| Coder Sync Register(CL560)                   | . 7-22 |

| Compressed Word Count Register, High (CL560) | 7-23   |

| Compressed Word Count Register, Low (CL560)  | 7-23   |

| Coder Rate Control Active Register(CL560)    | 7-24   |

| Coder Rate Control Enable Register (CL560)   | 7-24   |

| Coder Robustness Active Register (CL560)     | 7-25   |

| Coder RST Padding Control Register (CL560)   | 7-25   |

| Start of Frame Register                      | 7-26   |

| Decoder Table Sequence Length Register       | 7-26   |

| Decoder Marker Register                      | 7-26   |

| Decoder Resume Flag (CL550)                  | 7-26   |

| Decoder Code Order Register                  | 7-27   |

| Decoder Start Register (CL560)               | 7-27   |

| Decoding Mismatch Register (CL560)           | 7-27   |

7.2

.

|   |     |       | Decoding Mismatch Error Code Register (CL560)     | 7-28             |

|---|-----|-------|---------------------------------------------------|------------------|

|   |     |       | Configuration Register                            | 7-28             |

|   |     |       | S-Reset Register                                  | 7-2 <del>9</del> |

|   |     |       | Start Register                                    | 7-29             |

|   |     |       | Version Register                                  | 7-30             |

|   |     |       | Init Registers                                    | 7-30             |

|   |     |       | Flags Register                                    | 7-31             |

|   |     |       | NMRQ Interrupt Mask Register (CL550)              | 7-33             |

|   |     |       | IRQ1 Mask Register (CL560)                        | 7-34             |

|   |     |       | DMA Request Interrupt Mask Register               | 7-35             |

|   |     |       | IRQ2 Interrupt Mask Register (CL560)              | 7-37             |

|   |     |       | FRMEND Enable Register (CL560)                    | 7-38             |

|   |     |       | CODEC Register (CL550)                            | 7-39             |

|   |     |       | CODEC FIFO (CL560)                                | 7-40             |

|   |     |       | FIFO Level Register (CL560)                       | 7-40             |

| 8 | Sys |       | esigner's Guide                                   |                  |

|   | 8.1 |       | al System Configurations                          | 8-1              |

|   | 8.2 |       | Video Concepts                                    | 8-4              |

|   | 8.3 |       | Compression Operation                             | 8-5              |

|   |     | 8.3.1 | Overview                                          | 8-5              |

|   |     |       | CL550 Operation as a Still-image Coprocessor      | 8-7              |

|   |     |       | Operation as a Video Compression Processor        | 8-10             |

|   |     | 8.3.4 | I I I I I I I I I I I I I I I I I I I             | 8-12             |

|   |     | 8.3.5 | DMA System Programming Example                    | 8-14             |

|   | 8.4 |       | Compression Operation                             | 8-16             |

|   |     | 8.4.1 | CL560 Enhancements                                | 8-16             |

|   |     | 8.4.2 |                                                   | 8-18             |

|   |     |       | Compressed Data Rate Control Mechanisms           | 8-19             |

|   |     |       | Typical Compression System Using the CL560        | 8-21             |

|   |     |       | Slave-mode Compression Operation                  | 8-23             |

|   | 8.5 |       | Decompression Operation                           | 8-25             |

|   |     |       | Overview                                          | 8-25             |

|   | 8.6 |       | Decompression Operations                          | 8-28             |

|   | 8.7 |       | Initialization Procedures                         | 8-30             |

|   |     | 8.7.1 | Overview                                          | 8-30             |

|   |     | 8.7.2 | Programming the Video Interface Control Registers | 8-32             |

|   |     |       | HControl, VControl Registers Programming          | 8-34             |

|   |     |       | DCT Lookup Table                                  | 8-35             |

|   |     | 8.7.5 | Color Conversion Matrix                           | 8-35             |

|   |     | 8.7.6 | Sequence Control Registers                        | 8-35             |

|   |     | 8.7.7 | Selection of the RST Interval (Compression)       | 8-36             |

ix

|      | 8.7.8  | Pipeline Configuration Registers                       | 8-36 |

|------|--------|--------------------------------------------------------|------|

|      | 8.7.9  | Quantizer Tables Loading                               | 8-37 |

|      | 8.7.10 | Huffman Tables Loading                                 | 8-37 |

|      | 8.7.11 | CL5xx Start-up Sequence                                | 8-37 |

|      | 8.7.12 | Device Reset Considerations                            | 8-38 |

| 8.8  | Progra | amming the Huffman Tables                              | 8-41 |

|      | 8.8.1  | Extracting Huffman Tables from ISO JPEG                |      |

|      |        | Interchange Format                                     | 8-41 |

|      | 8.8.2  | CL550 Huffman Table Formats                            | 8-41 |

|      | 8.8.3  | CL560 Huffman Table Format                             | 8-47 |

| 8.9  | CL5xx  | Quantizer Table Programming                            | 8-50 |

|      | 8.9.1  | Overview                                               | 8-50 |

|      | 8.9.2  | Q Table Scaling Function                               | 8-51 |

|      | 8.9.3  | Generating Machine-Loadable Q Tables for CL5xx Devices | 8-53 |

| 8.10 | Custor | n Block Sequencing                                     | 8-56 |

|      | 8.10.1 | Restrictions                                           | 8-56 |

|      | 8.10.2 | CL5xx Internal Component Sequencing                    | 8-56 |

|      | 8.10.3 | CL550 Component Sequence Programming                   | 8-57 |

# **Figures**

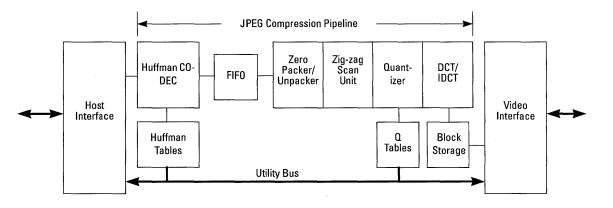

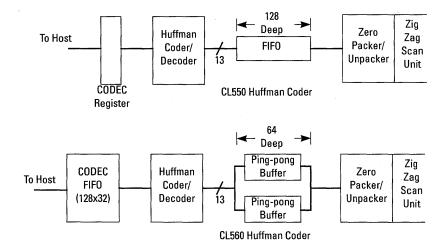

| 1-1 | CL550 Block Diagram                                        | 1-4  |

|-----|------------------------------------------------------------|------|

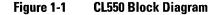

| 1-2 | CL560 Block Diagram                                        | 1-6  |

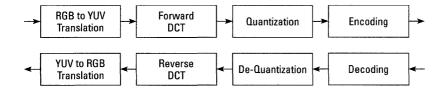

| 2-1 | Basic Image Compression Scheme for Coder and Decoder       | 2-3  |

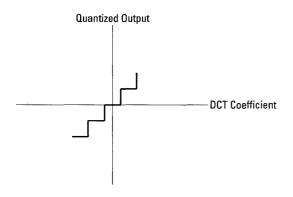

| 2-2 | Quantizer Stepping (Uniform Quantization)                  | 2-5  |

| 2-3 | Psychovisual Weighting Functions for the Luminance and     |      |

|     | Chrominance Components                                     | 2-6  |

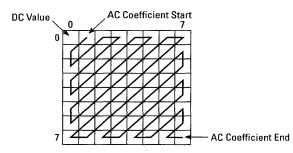

| 2-4 | Zigzag Pattern for Reordering the 8 x 8 DCT Coefficients   | 2-7  |

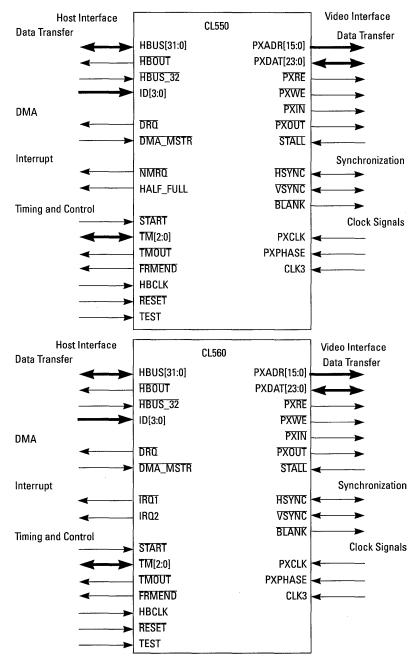

| 3-1 | CL550 and CL560 Logic Diagrams                             | 3-2  |

| 3-2 | Strip Buffer RAM Connections                               | 3-9  |

| 4-1 | CL550 and CL560 Host Interface Block Diagram               | 4-2  |

| 4-2 | ID[3:0] Chip Select Address Format                         | 4-4  |

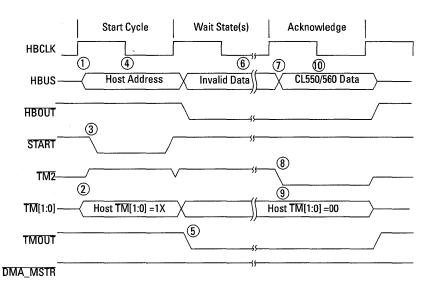

| 4-3 | Register Read Transaction                                  | 4-10 |

| 4-4 | Register Write Transaction                                 | 4-11 |

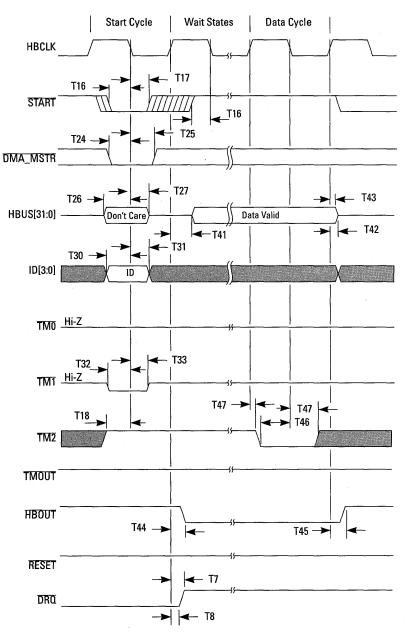

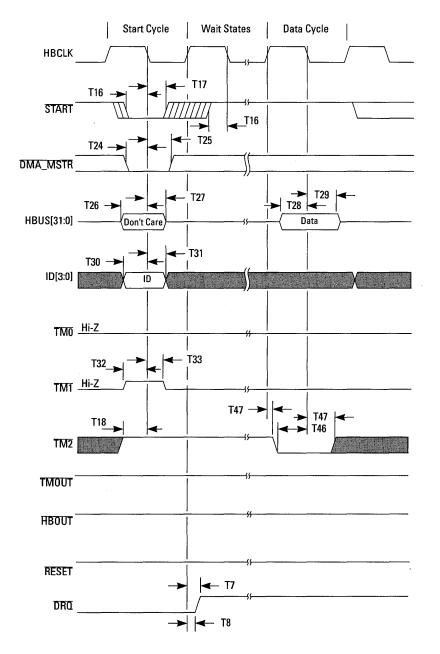

| 4-5 | DMA Mode Operation                                         | 4-13 |

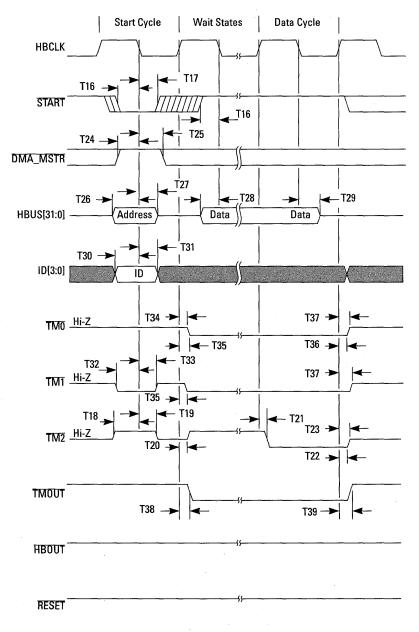

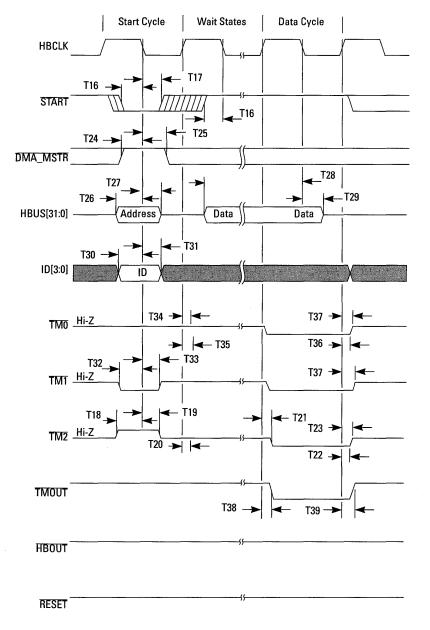

| 4-6 | CL560 DMA Write (Decompression - Host Write to CODEC)      | 4-15 |

| 4-7 | CL560 DMA Read (Compression - Host Read from CODEC)        | 4-17 |

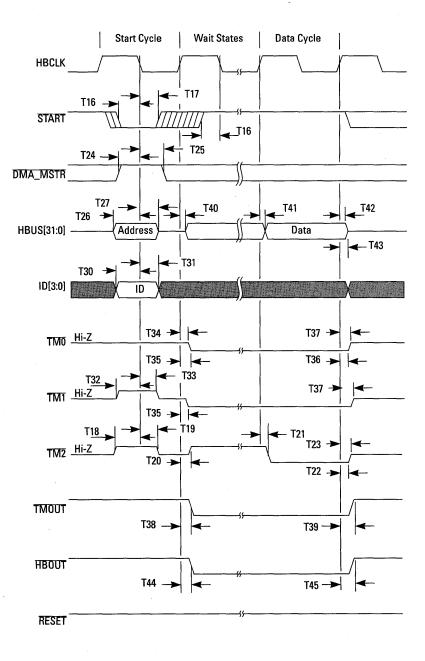

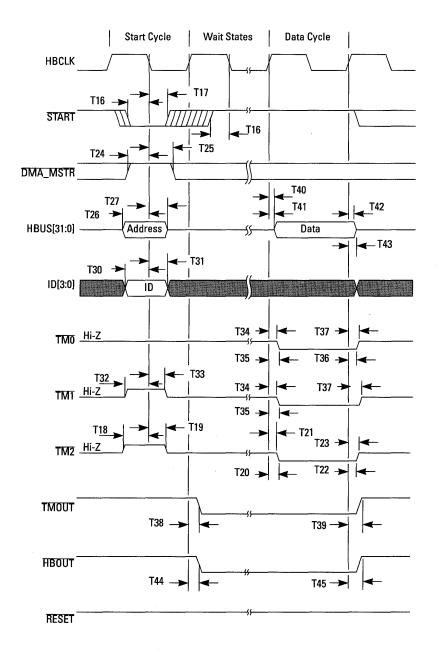

| 4-8 | CL550 DMA Write (Decompression - Host Write to CODEC)      | 4-20 |

| 4-9 | CL550 DMA Read (Compression - Host Read from CODEC)        | 4-22 |

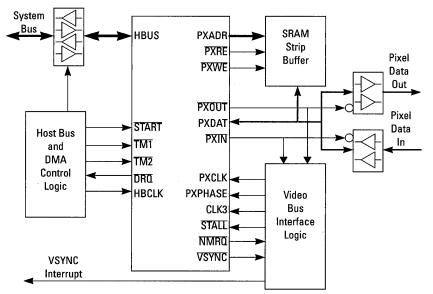

| 5-1 | Video Interface Block Diagram                              | 5-2  |

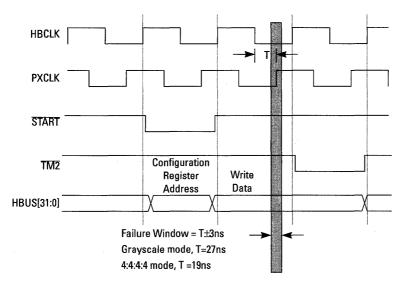

| 5-2 | CL550 Host Bus Write Timing for the Configuration Register | 5-5  |

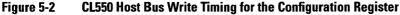

| 5-3  | STALL Timing, YUV 4:2:2 Compression Example                   | 5-8  |

|------|---------------------------------------------------------------|------|

| 5-4  | Pixels in Raster Order                                        | 5-10 |

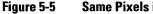

| 5-5  | Same Pixels in 8 x 8 Block Order                              | 5-10 |

| 5-6  | Video Field Descriptions                                      | 5-13 |

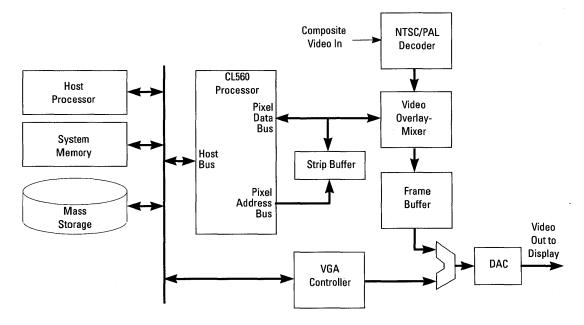

| 5-8  | Typical Video System Application                              | 5-14 |

| 5-7  | RGB to YUV Conversion Operation                               | 5-14 |

| 5-9  | Typical Still-frame Application                               | 5-15 |

| 5-10 | Typical Multimedia System Application                         | 5-16 |

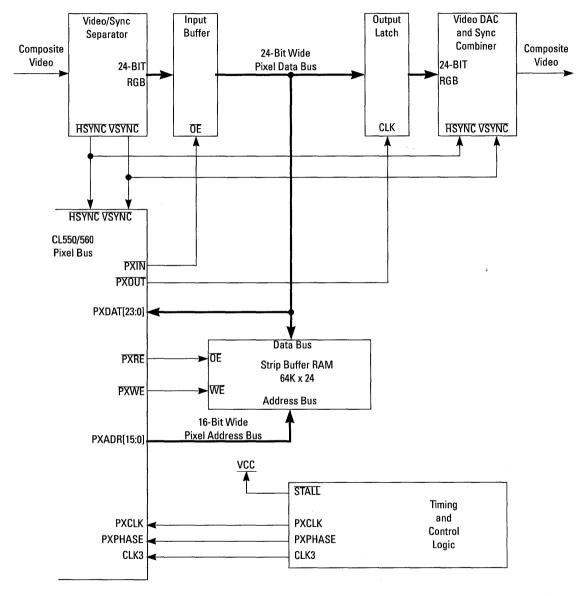

| 5-11 | Typical CL560 Synchronous Interface                           | 5-18 |

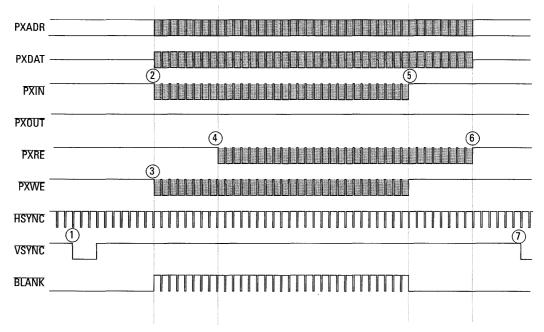

| 5-12 | Compression Overview                                          | 5-19 |

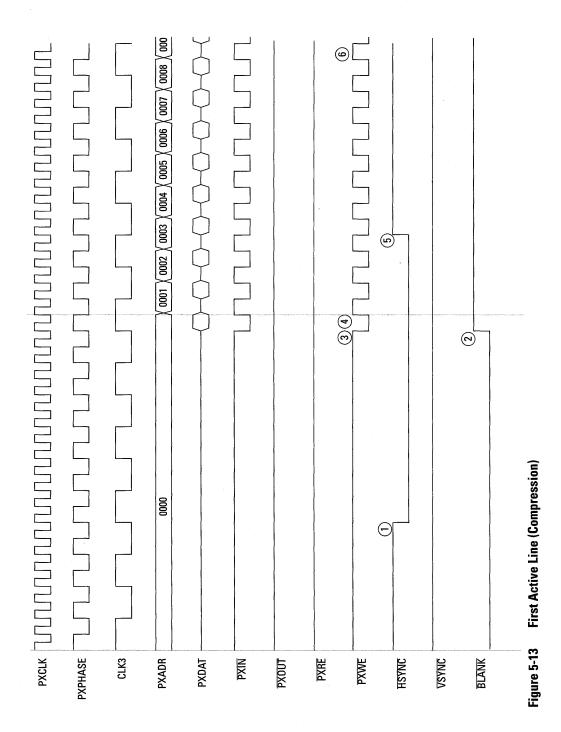

| 5-13 | First Active Line (Compression)                               | 5-22 |

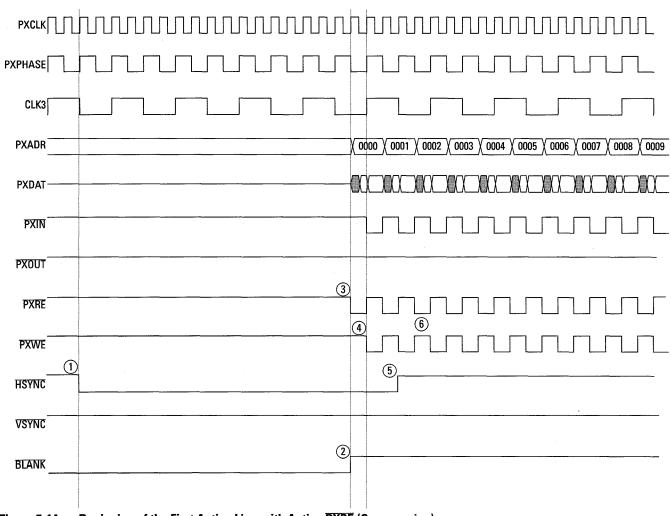

| 5-14 | Beginning of First Active Line with Active PXRE (Compression) | 5-24 |

| 5-15 | Last Line with Active PXIN (Compression)                      | 5-26 |

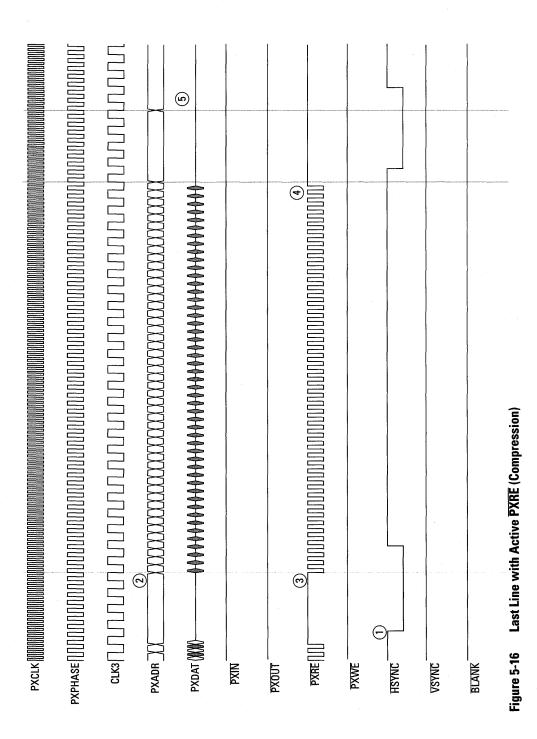

| 5-16 | Last Line with Active PXRE (Compression)                      | 5-28 |

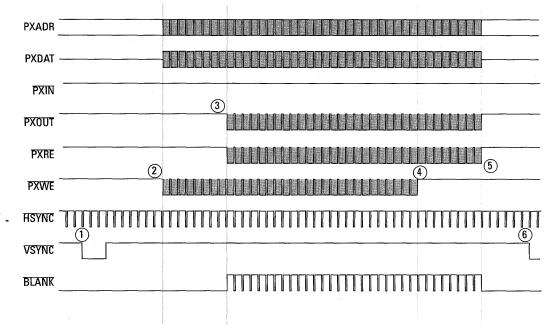

| 5-17 | Decompression Overview                                        | 5-30 |

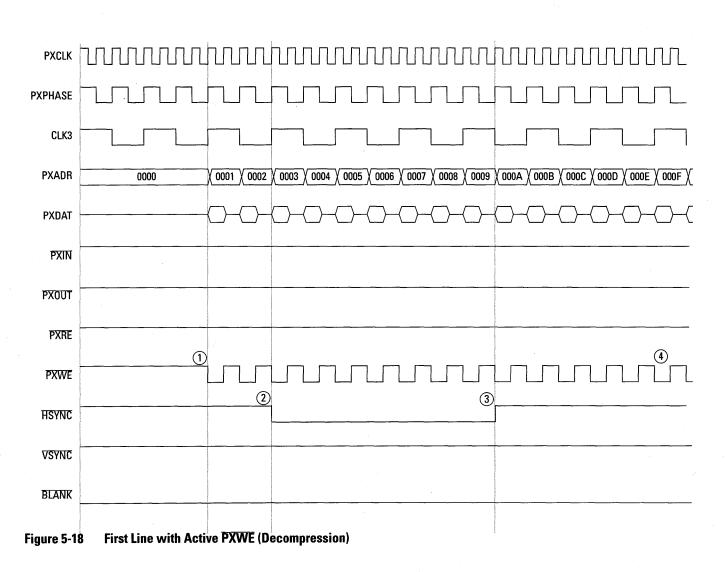

| 5-18 | First Line with Active PXWE (Decompression)                   | 5-32 |

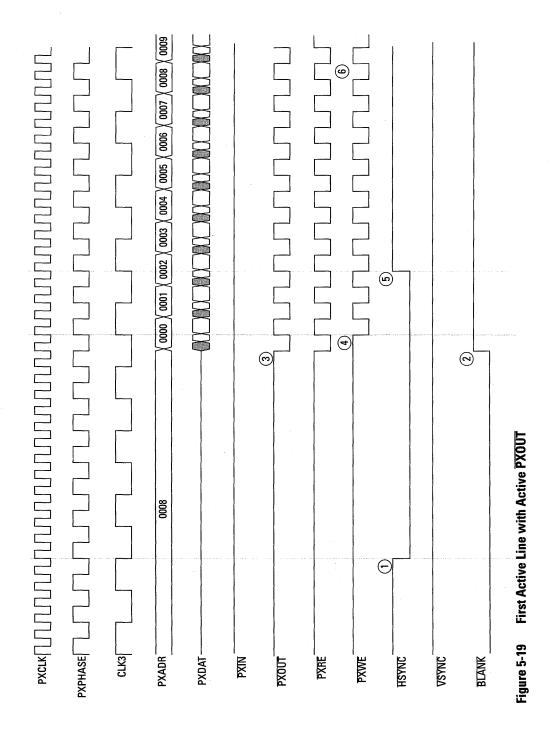

| 5-19 | First Active Line with Active PXOUT                           | 5-34 |

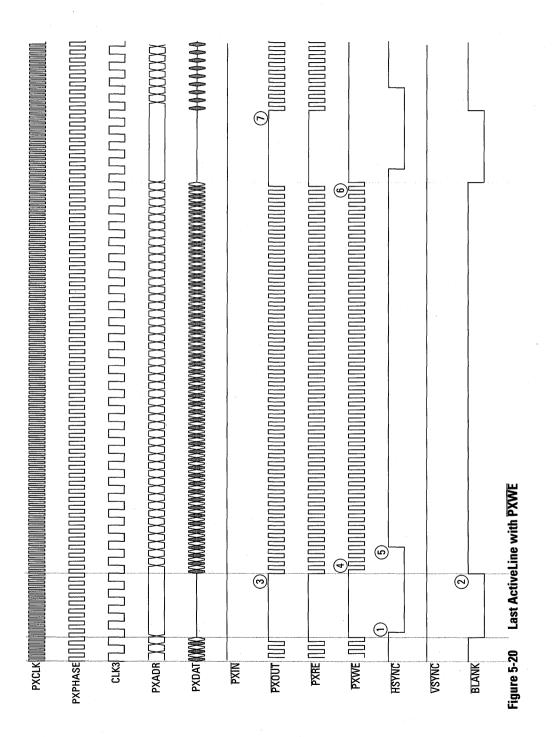

|      | Last ActiveLine with PXWE                                     | 5-36 |

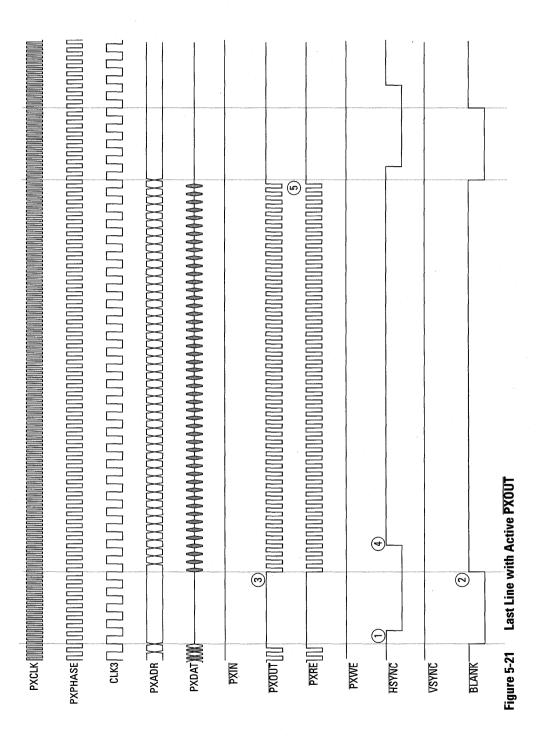

| 5-21 | Last Line with Active PXOUT                                   | 5-38 |

| 6-1  | HBCLK and RESET Timing                                        | 6-4  |

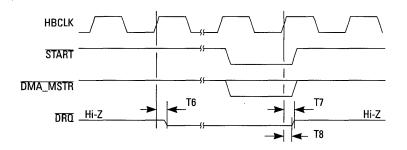

| 6-2  | DRQ Timing                                                    | 6-5  |

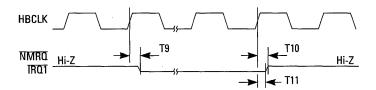

| 6-3  | NMRQ, IRQ1 Timing                                             | 6-6  |

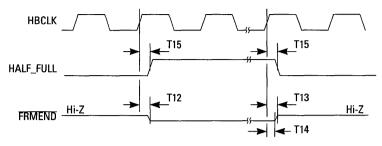

| 6-4  | CL550 HALF_FULL, FRMEND Timing                                | 6-7  |

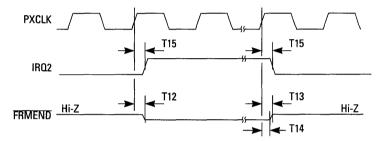

| 6-5  | CL560 IRQ2, FRMEND Timing                                     | 6-7  |

| 6-6  | CL550 Host Interface Timing: Register and Memory Write        | 6-8  |

| 6-7  | CL560 Host Interface Timing: Register and Memory Write        | 6-9  |

| 6-8  | CL550 Host Interface Timing: Register and Memory Read         | 6-10 |

| 6-9  | CL560 Host Interface Timing: Register and Memory Read         | 6-11 |

|      | CL560 Host Interface Timing: Burst Mode Read                  | 6-12 |

|      | CL560 Host Interface Timing: Burst Mode Write                 | 6-13 |

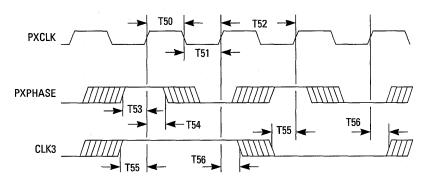

|      | Video Interface Clock Timing                                  | 6-16 |

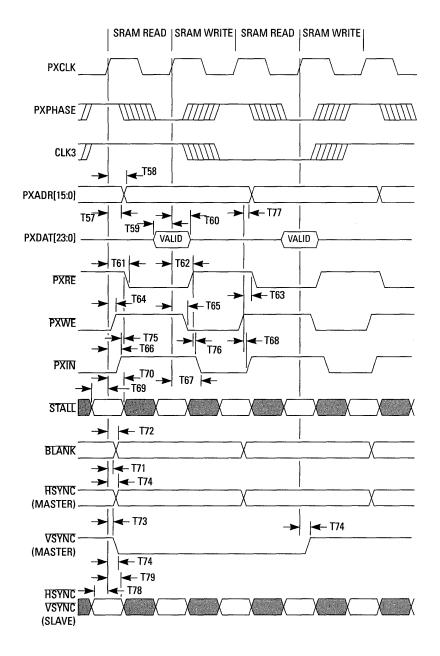

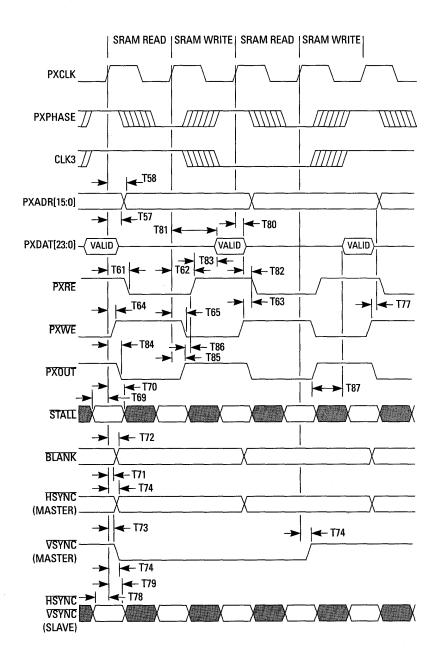

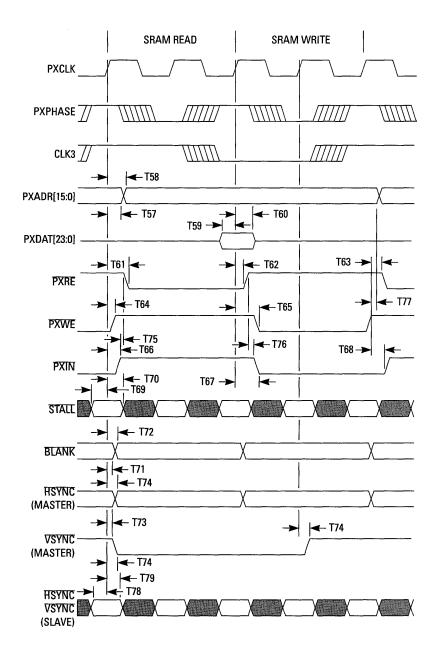

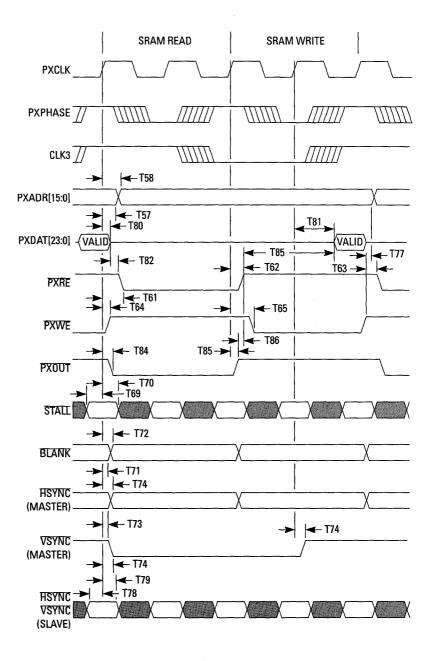

|      | Video Interface Timing: Compression, Full Rate Mode           | 6-17 |

|      | Video Interface Timing: Decompression, Full Rate Mode         | 6-18 |

|      | Video Interface Timing: Compression, Half-Rate Mode           | 6-19 |

|      | Video Interface Timing: Decompression, Half-Rate Mode         | 6-20 |

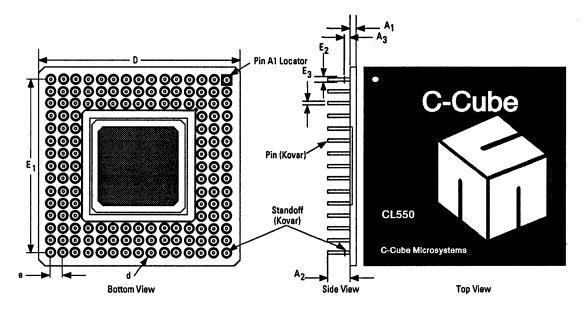

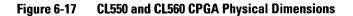

|      | CL550 and CL560 CPGA Physical Dimensions                      | 6-24 |

|      | CL550 and CL560 CPGA Pin Layout (Bottom View)                 | 6-25 |

|      | CL550 and CL560 CPGA Pinout Diagram (Top View Through Chip)   | 6-26 |

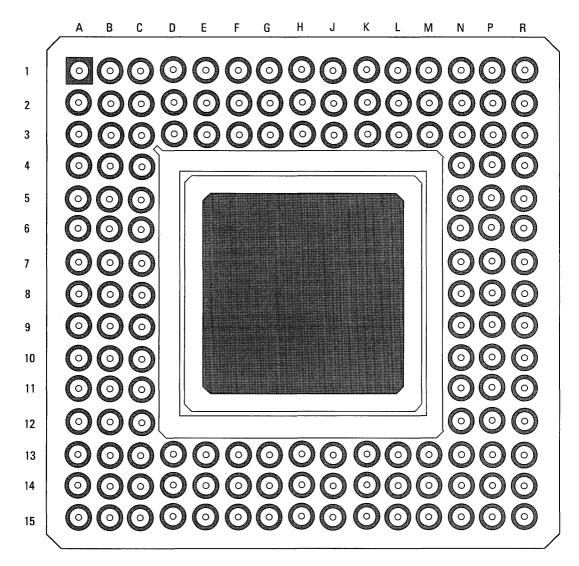

|      | MQUAD Physical Dimensions                                     | 6-29 |

|      | CL550 MQUAD Pinout Diagram                                    | 6-30 |

| 7-1  | Video Field Registers                                         | 7-6  |

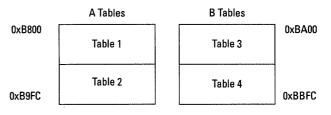

| 7-2  | Quantizer Tables Configuration (Double-buffer Mode)           | 7-15 |

| 7-3  | Quantizer Tables Configuration (Four-table Mode)      | 7-16 |

|------|-------------------------------------------------------|------|

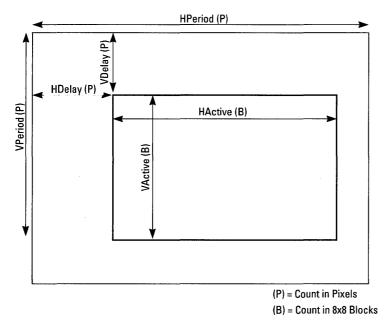

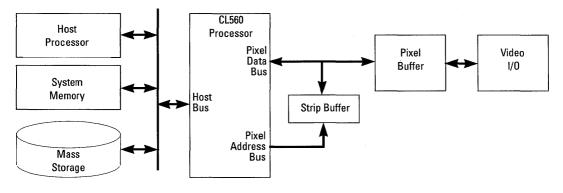

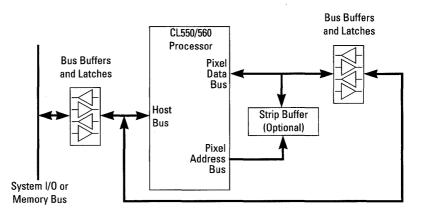

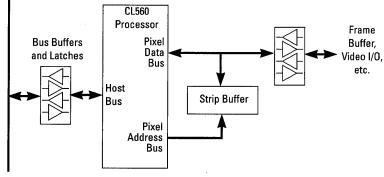

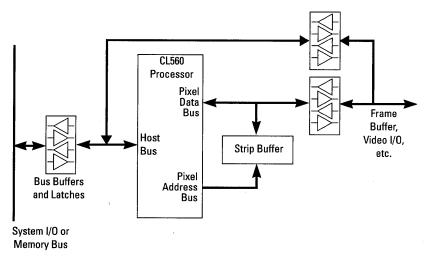

| 8-1  | Coprocessor Configuration                             | 8-2  |

| 8-2  | I/O Peripheral Configuration                          | 8-3  |

| 8-3  | Combined I/O Peripheral and Coprocessor Configuration | 8-3  |

| 8-4  | JPEG Video Data in Frame-by-Frame Organization        | 8-4  |

| 8-5  | JPEG Video Data Organized as a Continuous-Stream      | 8-5  |

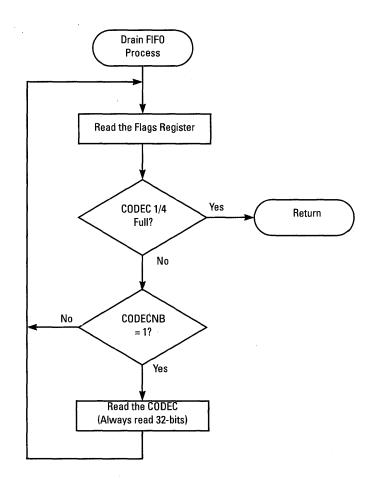

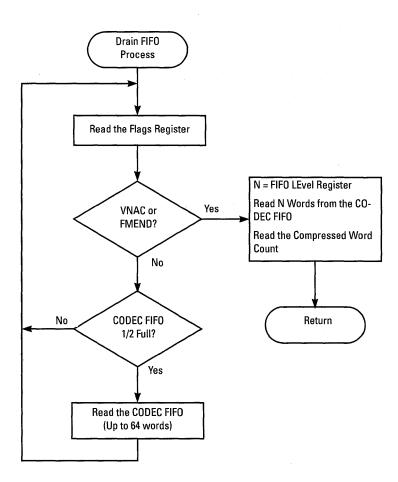

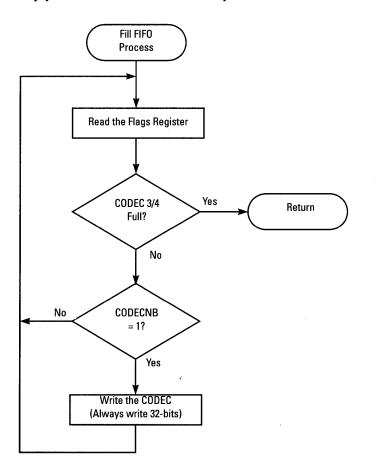

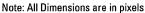

| 8-6  | Flow Chart for the CL550 FIFO Drain Loop              | 8-8  |

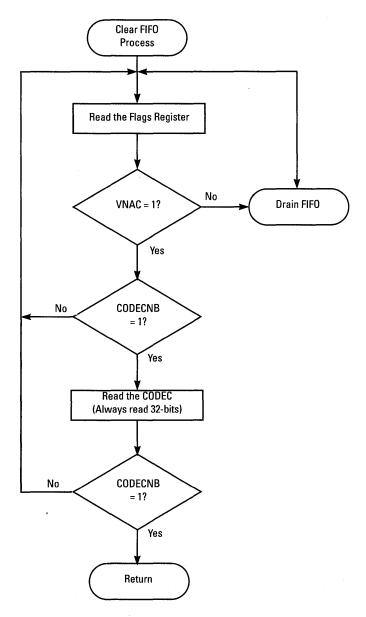

| 8-7  | Flow Chart for Flushing the CL550 FIFO                | 8-9  |

| 8-8  | Typical CL550 Video Compression System                | 8-11 |

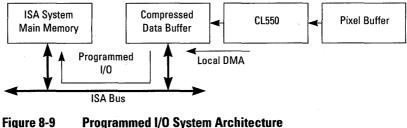

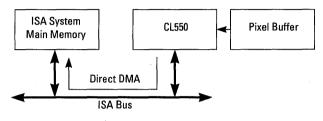

| 8-9  | Programmed I/O System Architecture                    | 8-12 |

| 8-10 | Direct DMA Architecture                               | 8-13 |

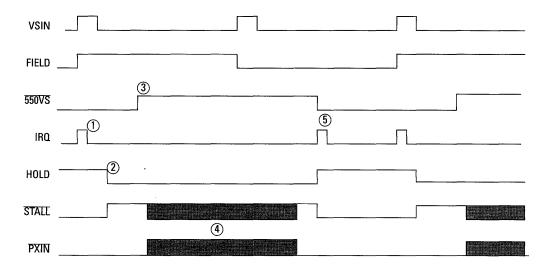

| 8-11 | Interrupt Timing for 30 Frame/Second Compression      | 8-15 |

|      | CL550 and CL5660 Architecture Differences             | 8-16 |

| 8-13 | Flow Chart for the CL560 FIFO Drain Loop              | 8-20 |

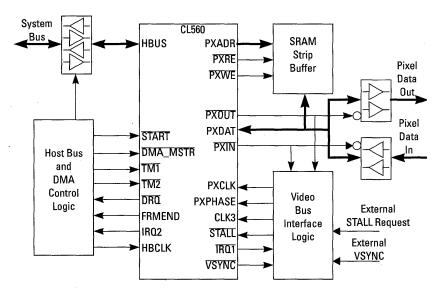

| 8-14 | Typical CL560-based Compression System                | 8-22 |

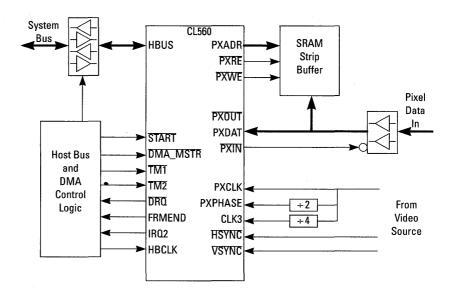

| 8-15 | Typical CL560-based Slave-mode Compression System     | 8-24 |

| 8-16 | Flow Chart for Filling the CL550 FIFO                 | 8-27 |

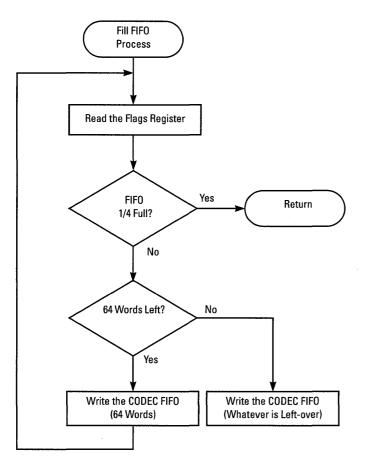

| 8-17 | Program Flow for Filling the CL560 FIFO               | 8-29 |

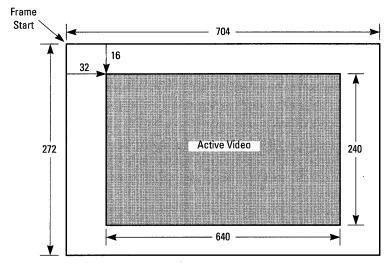

| 8-18 | Programming Parameters for Video Window Example       | 8-33 |

| 8-19 | CL550 Huffman Table Formats for Compression           | 8-43 |

| 8-20 | CL550 Huffman Table Format for Decompression          | 8-45 |

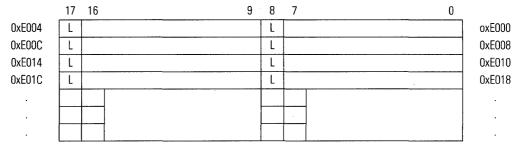

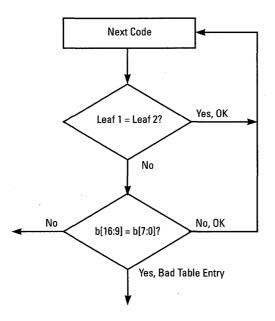

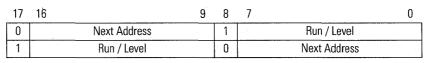

| 8-21 | Detecting a Bad Huffman Table                         | 8-46 |

| 8-22 | CL550 Huffman Table Layouts in Compression Mode       | 8-48 |

| 8-23 | CL560 Machine-Specific Huffman Table Entry Format     | 8-49 |

| 8-24 | Example for Accessing a Table Entry at Address 0xE000 | 8-49 |

| 8-25 | Typical Flow for Generating a CL5xx Quantizer Table   | 8-51 |

|      | Quantizer Table Scaling Function                      | 8-52 |

| 8-27 | Make CL5xx Quantizer Table Function Listing           | 8-54 |

| 8-27 | Make CL5xx Quantizer Table Function Listing           | 8-55 |

|      | CL5xx Block Storage Unit Component Sequencing         | 8-57 |

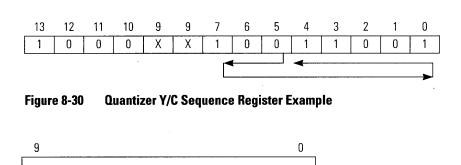

| 8-29 | Quantizer Y/C Sequence Register                       | 8-58 |

| 8-30 | Quantizer Y/C Sequence Register Example               | 8-59 |

| 8-31 | Quantizer A/B Sequence Register                       | 8-59 |

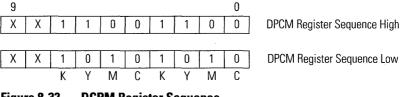

| 8-32 | DCPM Register Sequence                                | 8-60 |

xiv C-Cube Microsystems

## **Tables**

| 2-1  | Converting RGB Components to YCbCr Components               | 2-4  |

|------|-------------------------------------------------------------|------|

| 2-2  | Zigzag Sequence of Quantized DCT Coefficients               | 2-7  |

| 3-1  | CL550 and CL560 Redefined Signal Pins                       | 3-3  |

| 3-2  | Address and Data Bus Configuration                          | 3-3  |

| 4-1  | CL550 and CL560 Redefined Signal Pins                       | 4-3  |

| 4-2  | Address and Data Bus Configuration                          | 4-5  |

| 4-3  | TM Signals During a Host Bus Register Read (CL550 to Host)  | 4-6  |

| 4-4  | TM Signals During a Host Bus Register Write (Host to CL550) | 4-6  |

| 4-5  | TM Signals During a Host Bus Register Read (CL560 to Host)  | 4-6  |

| 4-6  | TM Signals During a Host Bus Register Write (Host to CL560) | 4-7  |

| 4-7  | TM Signals During a DMA Read (CL560 to Host)                | 4-7  |

| 4-8  | TM Signals During a DMA Write (Host to CL560)               | 4-7  |

| 4-9  | CL550 Bus Error Conditions                                  | 4-9  |

| 4-10 | External Buffers Direction Control                          | 4-14 |

| 5-1  | CL550/560 Color Modes and Pixel Data Configurations         | 5-6  |

| 5-2  | Video Field Control Registers                               | 5-12 |

| 5-3  | Compression Timing Example Register Values                  | 5-17 |

| 5-4  | Timing Example Video Parameters                             | 5-29 |

| 6-1  | Absolute Maximum Ratings                                    | 6-2  |

| 6-2  | Operating Conditions                                        | 6-2  |

|      |                                                             |      |

| 6-3  | DC Characteristics                                 | 6-2    |

|------|----------------------------------------------------|--------|

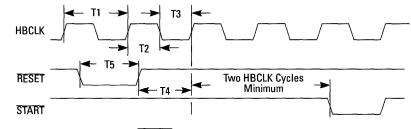

| 6-4  | HBCLK and RESET Timing Parameters, CPGA Package    | 6-4    |

| 6-5  | HBCLK and RESET Timing Parameters, MQUAD Package   | 6-4    |

| 6-6  | DRO Timing, CPGA Package                           | 6-5    |

| 6-7  | DRO Timing, MQUAD Package                          | 6-5    |

| 6-8  | NMRQ, IRQ1 TIming, CPGA Package                    | 6-6    |

| 6-9  | NMRQ, IRQ1 TIming, MQUAD Package                   | 6-6    |

|      | HALF_FULL, FRMEND Timing, CPGA Package             | 6-7    |

| 6-11 | HALF_FULL, FRMEND Timing, MQUAD Package            | 6-7    |

| 6-12 | Host Interface Timing, CPGA Package                | 6-14   |

| 6-13 | Host Interface Timing, MQUAD Package               | 6-15   |

|      | Video Interface Clock Timing, CPGA Package         | 6-16   |

| 6-15 | Video Interface Clock Timing, MQUAD Package        | 6-16   |

| 6-16 | Video Interface Timing Table, CPGA Package         | 6-21   |

| 6-17 | Video Bus Timing Table, MQUAD Package              | 6-22   |

| 6-18 | CPGA Pin List Sorted by Pin Number                 | 6-27   |

| 6-19 | CPGA Pin List Sorted by Pin Name                   | 6-28   |

| 6-20 | CL550/CL560 MQUAD Pinout Differences               | 6-30   |

| 6-21 | CL550 (CL560) MQUAD Pin List Sorted by Pin Number  | 6-31   |

| 6-22 | CL550 (CL560) MQUAD Pin List Sorted by Pin Name    | 6-32   |

| 7-1  | CL550 Register and Summary                         | 7-2    |

| 7-2  | CL560 Register and Summary                         | 7-4    |

|      | HPeriod Register Value Calculation                 | 7-7    |

| 7-4  | HDelay Register Value Calculation                  | 7-8    |

| 7-5  | HActive Register Value Calculation                 | 7-9    |

| 7-6  | Video Latency Register Values                      | 7-11   |

|      | RGD-YUV Color Transformation Coefficient Addresses | 7-14   |

|      | DCT Values                                         | 7-15   |

|      | Quantizer Y/C Values                               | 7-17   |

|      | Quantizer A/B Values                               | 7-18   |

|      | Quantizer Sync Register Data Sync Field Values     | 7-19   |

|      | DPCM Sequence Register Values                      | 7-19   |

|      | Huffman Sequence Register Values                   | . 7-21 |

|      | MCU Block Number Values                            | 7-22   |

|      | Coder Sync Register Initialization Values          | 7-23   |

|      | FIFO Threshold Levels                              | 7-25   |

|      | Video Mode Select Bits                             | 7-28   |

|      | Version Number Register Contents                   | 7-30   |

|      | Initialization Registers                           | 7-30   |

|      | CL5xx Register Reset Values                        | 8-39   |

|      | Registers Required for Minimized Restart Procedure | 8-40   |

| 8-3  | CL550 Huffman Layouts in Compression Mode          | 8-43   |

# 1 Introduction

The C-Cube CL550 and CL560 are high-performance single-chip compression/decompression processors that implement the baseline CCITT/ISO Joint Photographic Experts Group (JPEG) digital image compression algorithm. The CL550 and CL560 processors are designed for applications that require manipulation of high-quality digital pictures and motion sequences.

These parts can encode and decode grayscale and color images at video rates. The image compression ratio is controlled by the on-chip quantization tables. Compression ratios from 8:1 to 100:1 are possible depending on the quality, storage and bandwidth requirements of each application.

The CL550 and CL560 have on-chip video and host bus interfaces. The video interface supports 8-bit grayscale, RGB, CMYK or 4:4:4:4, and YUV (4:2:2 and 4:4:4) input and output. The host bus interface provides a direct interface to the system bus for ease of system integration.

### CL550 Features

| ·                     |                                                                                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>CL550 Features | The CL550 compression/decompression processor features the follow-<br>ing:                                                                                            |

| <u></u>               | <ul> <li>Compressed output conforms to the JPEG Baseline Process as de-<br/>fined by ISO IS 10918-1</li> </ul>                                                        |

|                       | <ul> <li>Real-time compression and decompression of CIF (320 x 240 x 30 fields per second) and 1/2 CCIR 601 video (640 x 240 x 25 or 30 fields per second.</li> </ul> |

|                       | <ul> <li>Up to 2 Mbytes/second sustained compressed data rate (CL550-<br/>35)</li> </ul>                                                                              |

|                       | <ul> <li>Highly pipelined DCT/IDCT processor running at up to 35 Mhz<br/>(CL550-35)</li> </ul>                                                                        |

|                       | <ul> <li>Support for 8-bit grayscale, RGB, CMYK or 4:4:4:4, and YUV color space input and output</li> </ul>                                                           |

|                       | User-accessible quantizer and Huffman tables                                                                                                                          |

|                       | Frame-by-frame adjustment of compression ratios                                                                                                                       |

|                       | □ High integration                                                                                                                                                    |

|                       | On-chip DCT/IDCT processor                                                                                                                                            |

|                       | On-chip quantizer and Huffman tables                                                                                                                                  |

|                       | □ On-chip video interface                                                                                                                                             |

|                       | □ On-chip 16-bit or 32-bit host bus interface                                                                                                                         |

|                       | Standard 144-pin MQUAD and ceramic PGA packages                                                                                                                       |

|                       | CMOS technology                                                                                                                                                       |

| 1.2<br>CL560          | The CL560 Compression processor has all of the features of the CL550, with these improvements:                                                                        |

| Improvements          | Up to 60 Mbytes/second sustained compression rate                                                                                                                     |

|                       | □ Up to 15 million pixels/second processing rates                                                                                                                     |

|                       | Highly pipelined DCT/IDCT processor runs at up to 30 MHz                                                                                                              |

|                       | <ul> <li>Real-time compression of CCIR 601 video frames at broadcast-<br/>quality levels</li> </ul>                                                                   |

|                       | <ul> <li>Improved Huffman table architecture allows the same table to be<br/>used for compression and decompression, allowing faster switch-</li> </ul>               |

ing between modes

- □ Single cycle per 32-bit word Huffman CODEC

- □ Synchronous or asynchronous video interface operation

- On-chip 128 x 32 compressed data FIFO supports burst access

- □ Improved interrupt structure and DMA support

- □ Compression rates as high as 50:1 for real-time video applications

- □ Compression rates as low as 1:1 for high-quality printer, copier and professional video applications

The CL560 pinout is a superset of the CL550 pinout. Although the function of two pins has changed, most CL550 users can upgrade to the CL560 with only minor changes to printed circuit board layouts.

These JPEG processors can be used in any of the following applications:

- Multimedia

- □ Video editing

- □ Color publishing and graphics arts

- □ Image-processing, storage and retrieval

- □ Color printers, scanners and copiers

- High-speed image transmission systems for LANs, modem and color facsimile

- Digital cameras

The CL550 and the CL560 are the two members in the JPEG compression/decompression processor family. The CL560 is an enhanced version of the CL550.

The CL550 is the first product in the family. It is designed for use in PC multimedia and still-image based systems where cost is a factor.

The CL560 is a new-generation JPEG processor designed for high-end still image and real-time video compression and decompression. The CL560 can compress and decompress full CCIR 601-resolution video frames in real time, at compression ration as high as 50:1 or as low as

### 1.3 Applications

## 1.4 Product Family

1:1. The CL560 is ideally suited for used in high-end printing and scanning systems, high-speed digital copiers and printers, and a wide range of broadcast-quality video editing applications.

## 1.5 CL550 Functional Description

This section describes the functional characteristics of each block within the C-Cube CL550 processor. Figure 1-1 shows the processor's major functional blocks. The CL550 is a highly pipelined machines: there are over 320 processing stages in the data path. Each stage in the JPEG Baseline Sequential Process is implemented within this pipeline.

During compression operations, uncompressed pixel data is written into the Video interface. The first operation that the video interface performs is a raster-to-block conversion of the pixel data. This is necessary because video generation and display devices normally deal with pixel data as raster lines, while the JPEG compression algorithm requires that the pixel data be organized as 8 x 8 blocks. Logic in the CL550 device performs that conversion.

The next step is the optional RGB-to-YUV color space conversion. This is also done in the video interface. Video generation and display devices frequently present data to the CL550 as RGB pixels. The CL550 can also perform the color space conversion. Other functions done by the Video interface are pixel formatting and window sizing.

Once the Video interface has formatted the pixel data, it writes the data into the Block Storage unit. The Block Storage unit stores the  $8 \times 8$  blocks until the JPEG compression pipeline is ready to process them. It then sequences them into the pipeline one block at a time.

Each component block is then processed by the Discrete Cosine Transform (DCT) unit. The resulting DCT coefficients are quantized by the quantizer according to user-programmable quantization matrices. The CL550 allows up to four 64-word quantization matrices to be stored onchip, and provides programmable sequence registers to allow the user to select the appropriate matrix for each component block.

The quantized terms are then serialized by the Zig-zag scan unit and the AC terms are run-length coded by the Zero Packer/Unpacker unit before being loaded into the FIFO. The FIFO serves as an intermediate buffer between the Zero Packer/Unpacker unit and the Huffman Coder/ Decoder (CODEC) unit.

The Huffman CODEC draws the packed symbols from the FIFO, performs Differential Pulse Code Modulation (DPCM) calculations on the DC terms, and performs Huffman coding of both the DC and the AC terms. Huffman codes are specified by the user, and stored in on-chip table RAM that is loaded at initialization.

The Huffman codes are finally sent to the Host interface as JPEG compressed data. The Host interface is designed to operate in either slave mode or master mode. In slave mode, the CL550 acts as a peripheral device to the host processor, using a data request/data available handshake to control the transfer of data. In master mode, the CL550 works in conjunction with an external DMA controller chip to allow high-speed DMA transfers of data. The Host interface is explained in detail in Chapter 4, Host Interface.

Compression operations follow the opposite procedure. JPEG compressed data is written to the Host interface. The Host interface then transfers the data to the Huffman CODEC, where it is decoded. The packed symbols are put back into the FIFO. The Zero Packer/Unpacker Unit accesses the FIFO symbols, generates the AC values, and passes them to the Zig-zag Scan unit for reordering into 8 x 8 block format. The DC terms are treated separately. Dequantization and Inverse DCT (IDCT) are then performed on the reassembled blocks before they are sent to the Block Storage unit. The Video interface optionally performs YUV-to-RGB color space conversion of the pixel data, realigns the 8 x 8 block data as raster lines, and outputs the lines to the external video display device.

With this architecture, it is possible to construct very high-performance compression systems for still-frame applications or motion video. The CL550 parts can be reinitialized on a frame-by-frame basis, allowing the programmer to change compression ratios at the end of each frame. It also allows systems to be designed where the CL550 switches back and forth between compressing and decompressing frames for half-duplex image communication.

### 1.6 CL560 Functional Description

This section describes the functional characteristics of each block within the C-Cube CL560 processor. Figure 1-2 shows the processor's major functional blocks. The CL560 is a highly pipelined machine with over 320 processing stages in the data path. Each stage in the JPEG Baseline Sequential Process is implemented within this pipeline. The major difference between the CL560 architecture and the CL550 architecture is in the Huffman CODEC. The synchronous CODEC in the CL560 allows data to be encoded or decoded in a single clock cycle, whereas the asynchronous CODEC in the CL550 takes several clock cycles, thus allowing higher throughput.

CL560 Block Diagram

During compression operations, uncompressed pixel data is written into the Video interface. The first operation that the Video interface performs is a raster-to-block conversion of the pixel data. This operation is necessary because video generation and display devices normally deal with pixel data as raster lines, while the JPEG compression algorithm requires that the pixel data be organized as 8 x 8 blocks. Logic in the CL560 device performs that conversion.

The next step is the optional RGB-to-YUV color space conversion, also performed by the Video interface. Video generation and display devices frequently present data to the CL560 as RGB pixels. The CL560 also performs optional color space conversion. Other functions done by the Video interface are pixel formatting and window sizing.

Once the video interface is through formatting the pixel data, it writes the data into the Block Storage unit. The Block Storage unit stores the  $8 \times 8$  blocks until the JPEG compression pipeline is ready to process them. It then sequences them into the pipeline one block at a time.

Each component block is then processed by the Discrete Cosine Transform (DCT) unit. The resulting DCT coefficients are quantized by the quantizer according to user-programmable quantization matrices. The CL560 allows up to four 64-word quantization matrices to be stored onchip, and provides programmable sequence registers to allow the user to select the appropriate matrix for each component block. Up until this point, the CL560 compression process has been identical to the CL550 compression process.

The quantized terms are then serialized by the Zig-zag scan unit and the AC terms are run-length coded by the Zero Packer/Unpacker unit before being loaded into the Ping-pong buffer. The Ping-pong buffer is a pair of synchronous 64-word registers used to smooth the flow of data to and from the Huffman CODEC.

The Huffman CODEC draws the packed symbols from the Ping-pong buffer, performs Differential Pulse Code Modulation (DPCM) calculations on the DC terms, and performs Huffman Coding of both the DC and the AC terms. Huffman codes are specified by the user, and stored in on-chip table RAM that is loaded at initialization.

The Huffman codes are then stored in a 128 x 32 CODEC FIFO. The FIFO acts as a rubber-band buffer between the synchronous JPEG com-

pression pipeline and the asynchronous Host Bus interface. The FIFO is used to filter out fluctuations in the data rate. It allows fast-burst access to the CL560 to minimize the time needed to transfer data.

The Host interface is designed to operate in either register access mode or DMA access mode. In register access mode, the CL560 acts as a peripheral device to the host processor, using a data request/data available handshake to control the transfer of data. In DMA access mode, the CL560 works in conjunction with an external DMA controller chip to allow high-speed DMA transfers of data. The Host interface is explained in detail in Chapter 4, Host Interface.

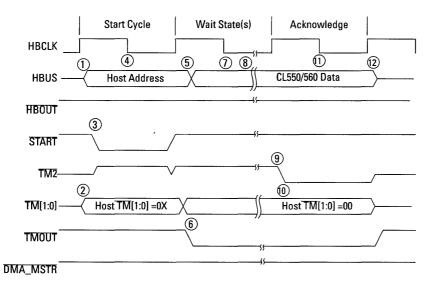

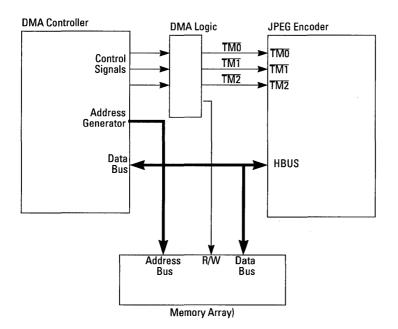

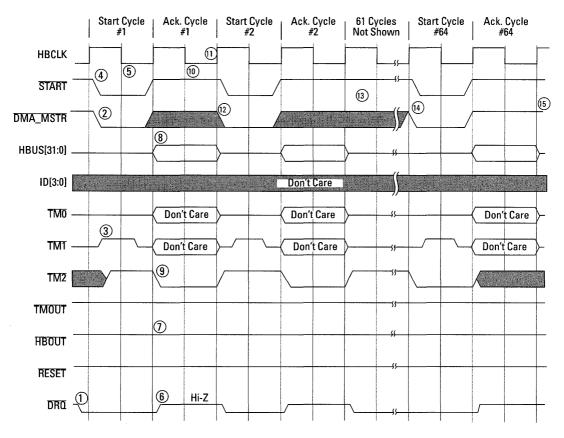

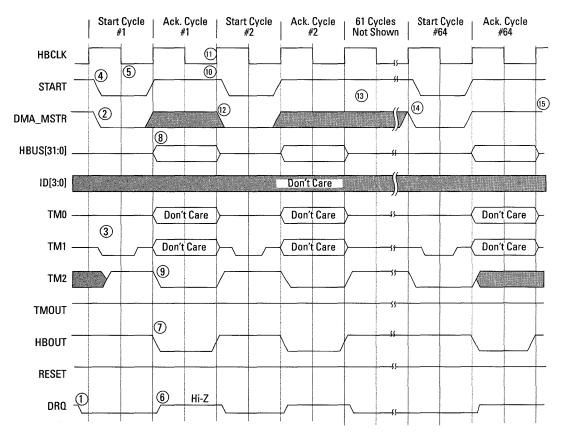

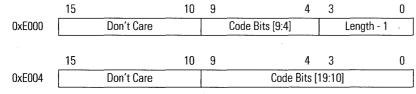

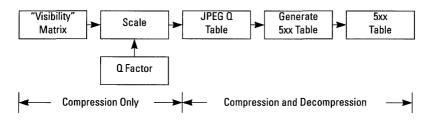

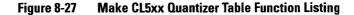

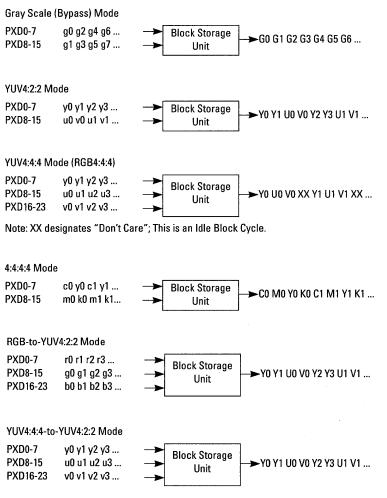

Compression operations follow the opposite procedure. JPEG compressed data is written to the Host interface. The Host interface then stores the compressed data in the CODEC FIFO until it can be transferred to the Huffman CODEC for decoding. After decoding, the packed symbols are stored in the Ping-pong buffer. The Zero Packer/Unpacker Unit reads the Ping-pong buffer to retrieve the packed symbols, generates the AC values, and passes them to the Zig-zag Scan unit for reordering into 8 x 8 block format. The DC terms are treated separately. Dequantization and Inverse DCT (IDCT) are then performed on the reassembled blocks before they are sent to the Block Storage unit. The Video interface optionally performs YUV -to-RGB color space conversion of the pixel data, realigns the 8 x 8 Block data as raster lines, and outputs the lines to the external video display device.