THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORA-TION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

Form 2101333

2.

#### COURSE REQUIREMENTS

#### **TRAINING PREREQUISITES :**

Ability to operate MTR routines on the available host system

and

**Principles of Micro-Based Computer Systems**

or

Business Machine Fundamentals: Course Number 300002, part of introduction to Field Engineering Form No. 1075602 (BMG)

#### **COURSE DURATION:**

The course is self-paced. Students should normally complete the course within 15 hours. A guide to the approximate time required to complete each lecture is given in the Student Introduction.

#### AUDIO-VISUAL REQUIREMENTS:

**35mm Slide Projector**

#### Preferably with remote control

**Cassette Tape Player**

Preferably with tape "pause" control and a tape position counter.

#### Screen

In addition to this package, the following materials are required to complete the B 9468 ICMD Training Program.

-1-

**TECHNICAL LITERATURE:**

Field Engineering Technical Manual:

Volume 1 Volume 2 (Parts Catalogue) Form 1084308 Form 1101771

Field Test and Reference Documentation Package.

Current RIN's/LIN's and ATI's.

Host system documentation and MTR.

## HARDWARE AND TOOLS:

**Host System**

B 9489-5 ICMD Unit

Any available unit with controller/ adaptor.

The unit may be mounted in a host system or be part of B 9489-15, -16, -17 or -18 freestanding unit connected to host system.

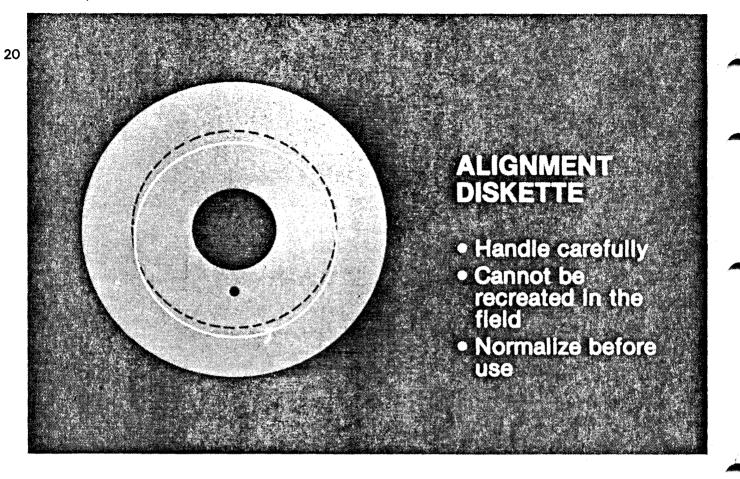

**Alignment Diskette**

Standard Tool Roll

BMD 1250 or Equivalent

Oscilloscope

2029 1852

**Tektronix 453 or Equivalent**

MACHINE SUPPLIES:

Diskette

#### 43-0010-081

#### COURSE SUPERVISOR INTRODUCTION

The B 9489 ICMD Field Engineering Training Program is a self-study course requiring a minimum of supervision in either a Branch or Training Center environment. The course divides into three lectures, each using a variety of instructional methods to give the student the required skills and knowledge. The course should be supervised by a Training Instructor, Branch FE Manager or assigned representative. The Course Supervisor responsibilities are outlined as follows:

#### TRAINING SITE:

Select an area which is free from distraction and provides a sufficiently large area for the student to work comfortably. To view the slides, it is necessary to reduce the level of light in the work area.

#### COURSE MATERIALS:

The student must be provided with all the materials listed in the Course Requirements section of this manual.

Any available style of host system can be used to drive the ICMD unit during this course. However, the student requires the ability to operate the ICMD MTR routines on the available host system and may require assistance to achieve this.

#### **DOCUMENTATION:**

The blue course binder contains a master copy of the workbook and lecture material. Order one copy of the document per student. The student should answer the review tests on the question pages provided in the ordered copy. Do not use the master. The student is allowed to retain the copy (without the question pages) for future reference.

### **REVIEW TESTS:**

Both Lecture 1 and Lecture 2 contain review tests which the Course Supervisor is required to grade. Although questions are numbered sequentially for the complete test, the tests are divided into several parts. Each part must be graded immediately on completion to identify any part of the preceding Lecture which the student should review.

THE ANSWER SHEETS FOR THE REVIEW TEST FOLLOW THIS INTRODUCTION AND MUST BE REMOVED BEFORE THE PACKAGE IS GIVEN TO THE STUDENT. THESE SHEETS ARE ONLY INCLUD-ED IN THE MASTER COPIES OF THE WORKBOOK.

After reviewing the test with the student, the Question/Answer pages must be retained by the course supervisor or destroyed.

#### **PRACTICAL WORK:**

The course contains a number of practical exercises requiring the student to disassemble, reassemble and adjust the unit. On completion of the course, a qualified Field Engineer must check the unit to ensure that it is correctly adjusted and operating to specification. Any deficiencies should be brought to the attention of the student for correction.

#### QUESTIONS:

The students are encouraged to determine the answers to any questions for themselves. If a question is asked which you are unable to answer, refer the question to a Training Center or other technical support facility for resolution.

#### COURSE CONTENT AND PRESENTATION:

Due to the variety of different controllers used by different host systems, this course does not include host system controllers or the optional medium/large system adaptor. These should be included in the host system training course.

The workbook contains copies of each of the Lecture scripts with black and white copies of each slide. This document is provided for personal reference by the student and cannot be used as a subsitute for the cassette and slide presentations.

# COURSE RECORDS:

INTERNATIONAL -- Complete a Field Engineering Training Report (Form INT 1591) for each student. Distribute copies per instructions on form. Send additional copy to Subisidiary FE Training Manager when applicable.

BMG -- Upon completion of the course, a "Training Report" (Form 1902202) must be initiated for each student. These reports should be forwarded to:

# BMG FE TRAINING ADMINISTRATION WHQ-DETROIT, ROOM 2D22

Refer to F.M.M. 10.3.10 for further references. When these reports are received and processed, a "Certificate of Accomplishment" will be sent to each student.

# **REVIEW TEST ANSWERS**

THE FOLLOWING REVIEW TEST ANSWER PAGES MUST BE RE-MOVED FROM THIS PACKAGE BEFORE IT IS GIVEN TO THE STUDENT.

# **REVIEW TEST ANSWERS**

## **LECTURE 1**

- 1. (b) One disk drive housed in the 44 inch cabinet.

- 2. (c) Reference the beginning of each track.

- 3. (a) True

- 4. (b) False

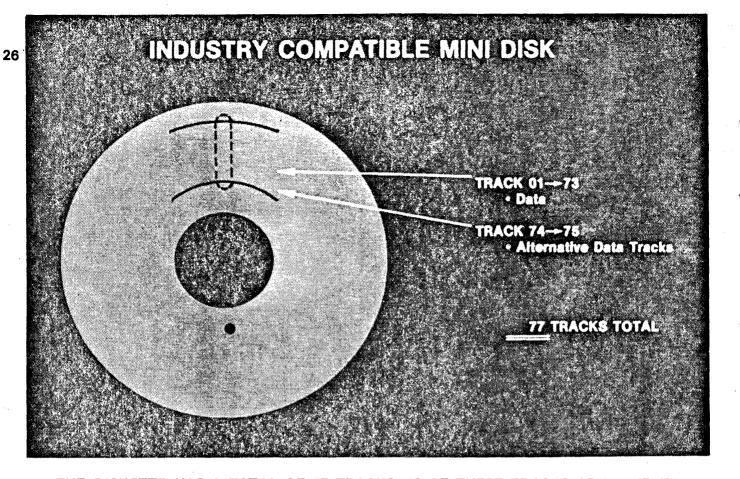

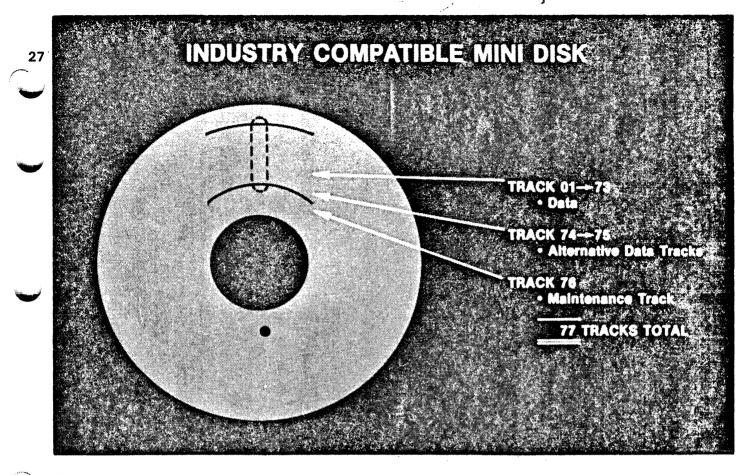

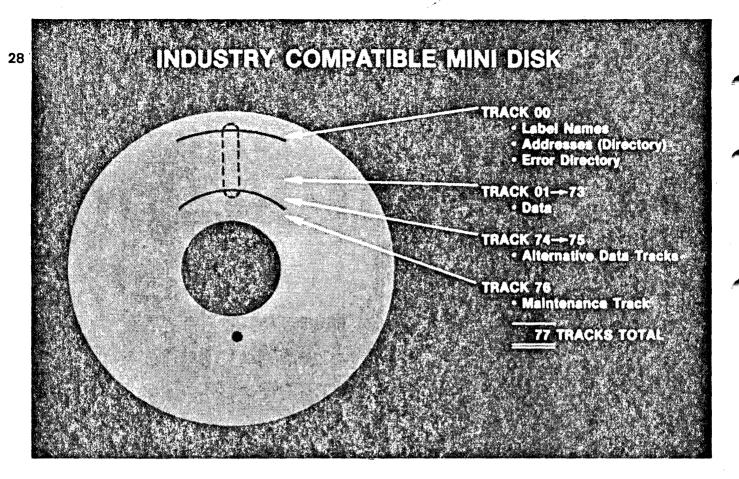

- 5. (e) 77

- 6. (e) 26

- 7. (d) Write the sector address on the diskette.

- 8. (e) A positive or negative going peak between clocks.

- 9. (a) 242,944 data bytes.

#### **REVIEW TEST ANSWERS**

### **LECTURE 2**

1. (b) Allow for head load settle time.

2. (b) Indicates that the read/write head is at track 00.

- 3. (d) 43

- 4. False

5. (c) A false or logic 0 is indicated by a 5v signal level.

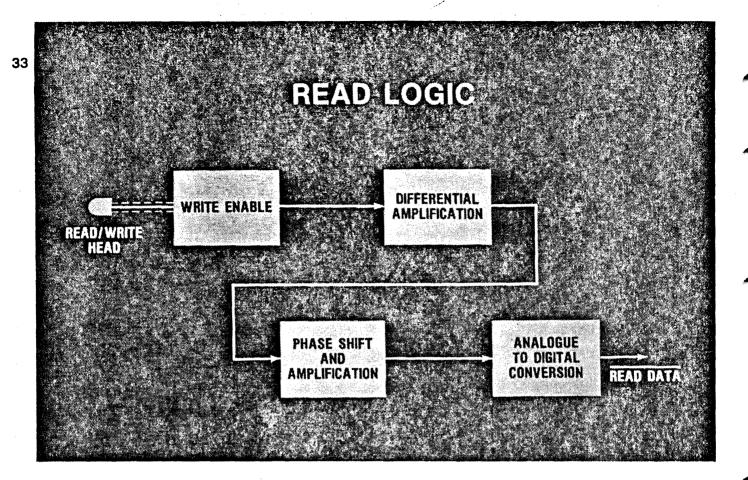

- 6. Write Enable (Any Order) Differential Amplification Phase Shift and Amplification Analogue to Digital Conversion

- 7, (e) Differential video amplifier

- 8. True

- 9. True

- 10. (d) Q2, Q3, U1, U2, U20

- 11. (b) Write Data

- 12. False

- 13. (Any Order)

A write enable is issued when the head is not loaded

Write data are sent at the wrong clock rate

A write is issued and data not received within 450uS

- 14. (e) Q18

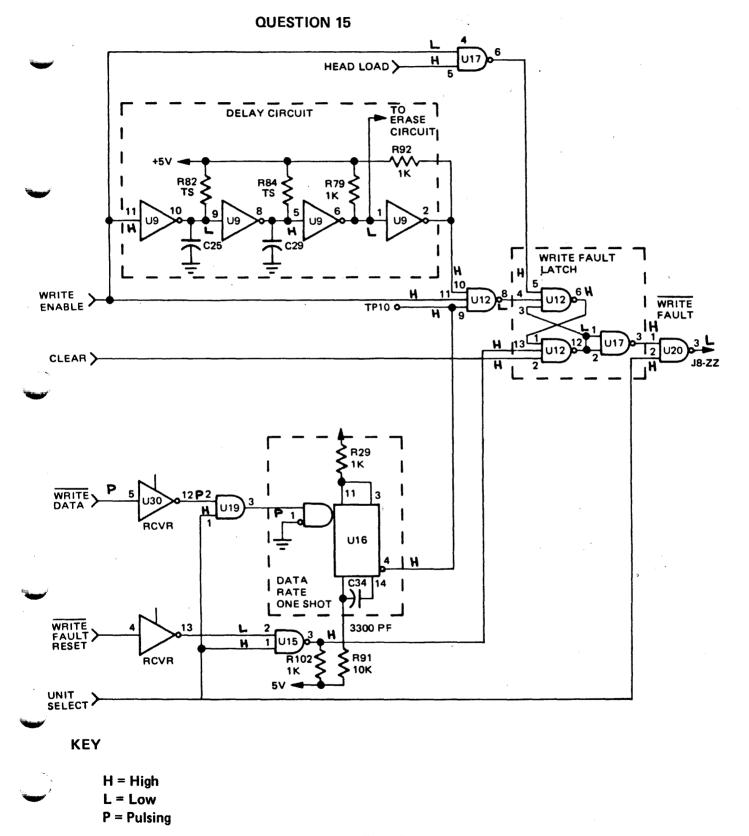

- 15. IC U16 Pin 4

- 16. (a) 3

#### (Continued on following page)

-6B-

# **REVIEW TEST ANSWERS**

# **LECTURE 2 CONTINUED**

17. (e) 15 degrees (Any Order) Track 00 Detector Output 18. a. Phase "A" Active b. Reset the stepper motor phase counter (Any Order) 19. a. Reset the write fault latch b. (Any Order) 20. U3 Q5 **Q6** CR3 21. True 22. (e) 170mS (Any Order) 23. U25 U27 SW1

#### **STUDENT INTRODUCTION**

The B 9489 ICMD Field Engineering Training Program is an objective oriented course designed for self-study with minimum supervision.

#### COURSE GOAL:

On completion of this course, you will be able to install, maintain and repair to the component level, any configuration of B 9489 ICMD unit including the power supply incorporated in the free standing styles.

#### **LECTURE OBJECTIVES:**

Each Lecture is preceded by one or more Lecture Objectives. These objectives broadly define the knowledge and skills you will acquire during the following Lecture. Read each Lecture Objective carefully before proceeding to the first Practice Objective.

#### PRACTICE OBJECTIVES:

Each Lecture is divided into sections. The activities within a section are designed to enable you to achieve each of the associated Practice Objectives. Read each Practice Objective carefully before proceeding to the Practice.

#### **PRACTICE:**

The Practice lists the various tasks you are required to complete. A typical sequence will ask you to view part of the Lecture and then complete an exercise. This exercise may be a review test or a practical exercise. Complete each exercise in sequence.

#### **REVIEW TESTS:**

Complete each Review Test on the question sheets contained in the workbook. On completion of each Review Test, give your completed answers to the Course Supervisor for grading. Lecture 3 does not include a Review Test. There is no time limit for completion of the Review Tests. You may refer to any available documentation or equipment when completing your answers.

#### TIME ALLOCATION:

The course is self-paced. Dependent on your previous knowledge and local circumstances, the course will normally require less than 15 hours to complete.

#### **QUESTIONS:**

Should you have a question which you are unable to answer for yourself, make a note of the question and proceed with the Lecture -- you may find the answer in a later section. If, after completing the Lecture, you are still unable to find the answer, refer your question to the Course Supervisor.

#### START:

Check that you have all the equipment required to complete the course and proceed to Lecture 1 in the Study Guide.

**LECTURE 1**

## **READ THE STUDENT INTRODUCTION BEFORE STARTING**

### LECTURE INTRODUCTION:

The first Lecture divides into two sections:

- i) The first section introduces the various B 9489 ICMD unit styles and options, examines the physical characteristics of the media giving attention to the need for correct handling and storage before describing operation of the unit.

- ii) The second section describes the Industry Compatable diskette format and encoding method, concluding with a summary of the B 9489 ICMD units capacities and performance characteristics.

-9-

3

# READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

## PRACTICE OBJECTIVES:

- 1. Identify the style and hardware options for any B 9489 ICMD Unit.

- 2. Identify the physical characteristics of the media.

- 3. Operate the B 9489 ICMD Unit observing proper media handling and storage procedures.

## **PRACTICE:**

- 1. Listen to the cassette for Lecture 1 and view slides 1 to 34.

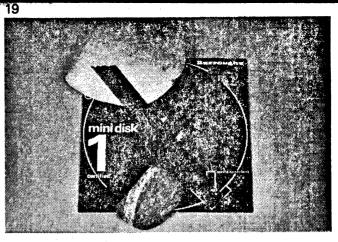

- 2. Remove a diskette from the protective envelope and locate the following: (DO NOT touch the recording surface)

- a) The index hole.

- b) The reinforced spindle hole.

- c) The read head slot.

- 3. Observing proper handling precautions, insert a diskette into a drive and determine that the unit is ready.

- 4. Complete the following Review Test.

#### **REVIEW TEST**

#### LECTURE 1

- 1. The B 9489-15 unit consists of:

- a) Two disk drives housed in the 33 inch cabinet.

- b) One disk drive housed in the 44 inch cabinet.

- c) One disk drive housed in the 44 inch cabinet with an adaptor card.

- d) One disk drive housed in the 33 inch cabinet.

- e) One disk drive for housing in the host system cabinet.

- 2. The Index hole is used to:

- a) Register the diskette.

- b) Locate the diskette.

- c) Reference the beginning of each track.

- d) Enable the read/write head.

- e) Access the recording surface.

- 3. The write protect hole feature is not used by the Burroughs B 9489 ICMD Units.

- a) True

- b) False

- 4. Contaminated diskettes can be removed from the jacket and cleaned.

- a) True

- b) False

Give your answers to the Course Supervisor for grading. If any answer is incorrect, review the relevant part of the Lecture before continuing.

# READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

# **PRACTICE OBJECTIVES:**

- 1. Identify the diskette media format and encoding method which determine that the media is Industry Compatable.

- 2. Relate the Industry Compatable media format and capacities to the performance characteristics of the B 9489 ICMD Unit.

# PRACTICE:

- 1. Continue listening to the cassette for Lecture 1 and view slides 35 to 53.

- 2. Complete the following Review Test.

# **REVIEW TEST**

£.

# **LECTURE 1**

2

5. How many tracks are there on an ICMD diskette in total?

a) 26 b) 73 c) 64 d) 128 e) 77

# 6. How many sectors are there on each track?

a) 4 b) 16 c) 12 d) 8 e) 26

7. The primary function of the diskette initialization is to:

a) Align the read/write head with track 00.

b) Register and align the diskette in the drive unit.

c) Read the diskette error directory.

d) Write the sector addresses on the diskette.

e) Trim the inter track spaces.

#### (Continued on next page)

8. In the double frequency encoding method used, a data one bit is indicated in the read head output signal by:

- a) A positive going peak between clocks.

- b) A negative going peak between clocks.

- c) A positive or negative going peak between clocks.

- d) A positive level between clocks.

- e) A negative level between clocks.

- 9. The data capacity of the ICMD diskette is:

- a) 242,944 data bytes

- b) 401,016 data bytes

- c) 65,536 data bytes

- d) 129,072 data bytes

- e) 258,144 data bytes

## **LECTURE 2**

# LECTURE INTRODUCTION:

The second Lecture divides into two sections:

- i) The first section identifies the physical locations and functions of the major components and sub-assemblies in the unit.

- ii) The second section describes the theory of operation for the unit using block diagrams to relate the function of each area of logic to the schematic drawings.

# READ THE FOLLOWING LECTURE OBJECTIVES

### LECTURE OBJECTIVES

- 1. Interpret the unit schematics to determine the function and mode of operation of any part of the unit logic.

- 2. Given any unit logic failure, use your knowledge of the unit logic to supplement the unit MTR's.

- 3. Make measurements of the unit logic signals to determine correct or incorrect operation of any given circuit.

# READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

## **PRACTICE OBJECTIVES:**

- 1. Locate and correctly identify the function of each major subassembly within the basic B 9489-5 unit.

- 2. Locate any given test point on the logic PCB.

- 3. Determine the number of head load and power on hours for any unit.

#### **PRACTICE:**

1. Listen to the cassette for Lecture 2 and view slides 1 to 10.

2. Locate the following sub-assemblies:

Disk Load Arm Head Load Solenoid Read/Write Head Index Hole Detector

- 3. Observe the mechanical operation of the unit with the unit powered off by performing the following:

- Open and close the door to observe the action of the Registration Cone.

- Rotate the stepper motor screw shaft to observe the action of the Read/Write Head carriage assembly.

- Press and release the Head Load Solenoid Clapper to observe the action of the Head Load Bail assembly.

## **PRACTICE (CONTINUED)**

- 4. With the unit powered on and a diskette inserted, locate the test point on the logic PCB for the Index Pulse. (Refer to FETM Volume 1 Page 4-13.) Use a BDM 1250, or equivalent, to measure the frequency of the Index Pulse.

- Note: This test point is the output of the Index phototransistor which is not a TTL logic level. The peak voltage is approximately 4 volts.

- 5. On the unit with which you are working, determine:

- i) The number of head load hours to date.

- ii) The number of power on hours to date.

# READ THE FOLLOWING PRACTICE OBJECTIVES

# **PRACTICE OBJECTIVES:**

- 1. Identify and determine the correct function of any interface signal.

- 2. Determine the unit drive number for any ICMD unit.

#### PRACTICE:

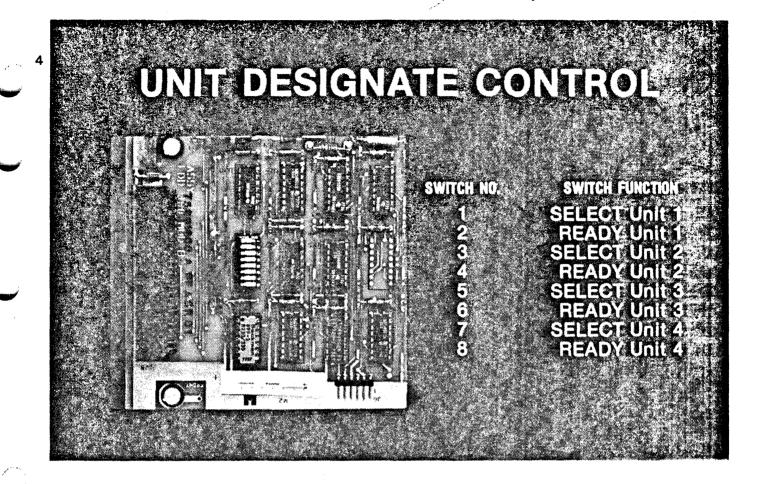

- 1. Continue listening to the cassette for Lecture 2 and view slides 11 to 20.

- 2. Use the unit logic schematic to determine the unit drive number for your unit by observing the position of the dual in line package switches on the logic PCB.

- 3. Complete the following Review Test.

#### **REVIEW TEST**

#### **LECTURE 2**

- 1. The Head Load command must be initiated 60 milliseconds before a read or write operation to:

- a) Register the diskette on the spindle.

- b) Allow for head load settling time.

- c) Ensure the Write Fault latch is reset.

- d) Give the head time to step to the required track.

- e) Provide time for the unit to sense the Index hole.

- 2. The Track 00 signal:

- a) Steps the read/write head to track 00.

- b) Indicates that the read/write head is at track 00.

- c) Reads data from track 00.

- d) Inhibits a write to track 00.

- e) Allows time for the read/write head to reach track 00.

- 3. The Low Current signal from the controller reduces the write current when a write operation is taking place on a track above:

- a) 24

- b) 34

- c) 36

- d) 43

- e) 47

(Continued on next page)

-20-

### **REVIEW TEST (CONTINUED)**

4. Data written to the diskette is checked during a write operation by the Write fault logic.

True/False

- 5. A convention used on the signal interface is:

- a) A false or logic 1 is indicated by a 5v signal level.

- b) A true or logic 1 is indicated by a 5v signal level.

- c) A false or logic 0 is indicated by a 5v signal level.

- d) A true or logic 0 is indicated by a 5v signal level.

Give your answers to the Course Supervisor for grading. If any answer is incorrect, review the relevant section of the lecture before continuing.

## **READ THE FOLLOWING PRACTICE OBJECTIVES**

#### **PRACTICE OBJECTIVES:**

•

- 1. Determine the function and mode of operation of any part of the Read Logic.

- 2. Given any Read Logic failure, use your knowledge of the Read Logic to determine the cause of the failure.

#### **PRACTICE:**

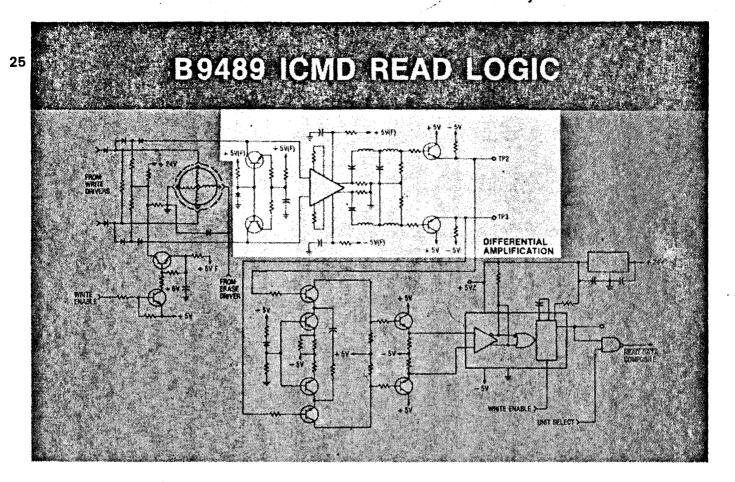

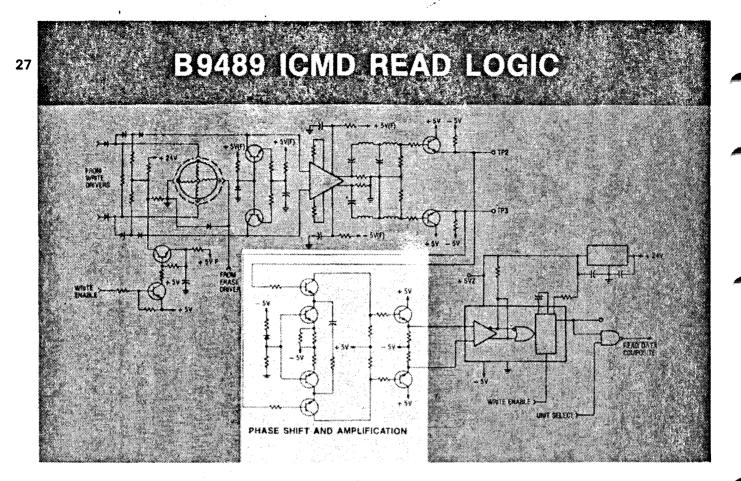

- 1. Continue listening to the cassette for Lecture 2 and view slides 21 to 34.

- 2. Complete the following Review Test.

## **REVIEW TEST**

# **LECTURE 2**

6. State the four main functional blocks of the Read Logic:

- 1. 2. 3. 4.

- 7. Component U4 is a:

- a) Differential voltage comparator.

- b) One shot multivibrator.

- c) Multi stage circuit.

- d) Analogue to digital converter.

- e) Differential video amplifier.

- 8. The Read Data signal output to the controller represents individual clock and one data bits by a pulse of nominally 250 nano-seconds.

True/False

9. The value of certain resistors is Test Selected during manufacture. When an associated component is replaced, it may be necessary to change the value of some Test Selected components.

True/False

(Continued on next page)

# **REVIEW TEST (CONTINUED)**

10. Refer to the Logic Schematic for the ICMD unit and consider the following failure condition:

A read operation is attempted, the head loads but checking Read Data Composite at TP12 shows no data. A further check between TP2 and TP3 shows data. Which major components would you suspect?

- a) Q15, Q16, U4, Q1, Q2

- b) Q1, Q2, Q3, U1, U20

- c) U4, Q1, Q2, U1, Q4

- d) Q2, Q3, U1, U2, U20

- e) U20, U29, U1, U2, Q3

Give your answers to the Course Supervisor for grading. If any answer is incorrect, review the relevant section of the Lecture before continuing.

-24-

2

# **READ THE FOLLOWING PRACTICE OBJECTIVES**

#### **PRACTICE OBJECTIVES:**

- 1. Determine the function and mode of operation of any part of the Write Logic.

- 2. Given any Write Logic failure, use your knowledge of the Write Logic to determine the cause of the failure.

#### **PRACTICE:**

- 1. Continue listening to the cassette for Lecture 2 and view slides 35 to 51.

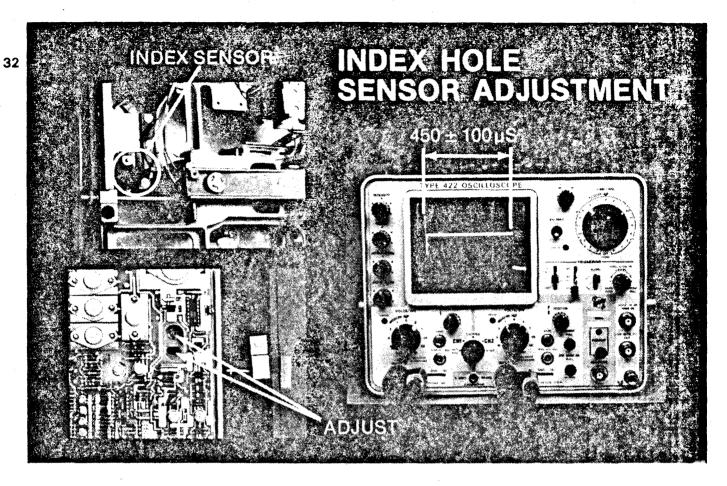

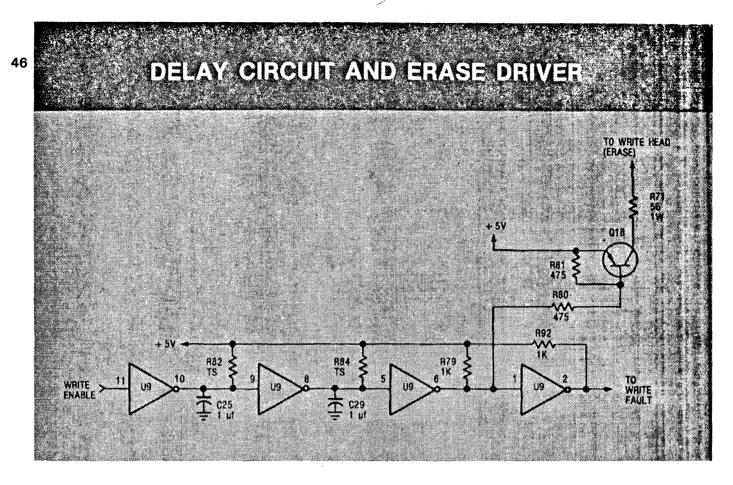

- 2. Use a BDM 1250 or equivalent to measure the Write Enable leading edge delay between U30-6 and U9-6 and the trailing edge delay between U30-6 and U9-6. Compare these values with the theoretical value of 450uS.

- 3. Complete the following Review Test.

## **REVIEW TEST**

## **LECTURE 2**

- 11. The clock input to the Write Toggle flip flop U21 when the unit is selected is the signal:

- a) Write Clock

- b) Write Data

- c) Write Enable

- d) Data Write Clock

- e) Write Enable Delayed

- 12. During a write operation below track 43, Q14 and Q17 conduct simultaneously to provide the necessary current.

True/False

- 13. List the three conditions which determine a Write Fault.

- 1. 2.

- 3.

14. Which component is the Erase Driver?

- a) Q7

- b) CR22

- c) Q9

- d) U9

- e) Q18

(Continued in next page)

-26-

## **REVIEW TEST (CONTINUED)**

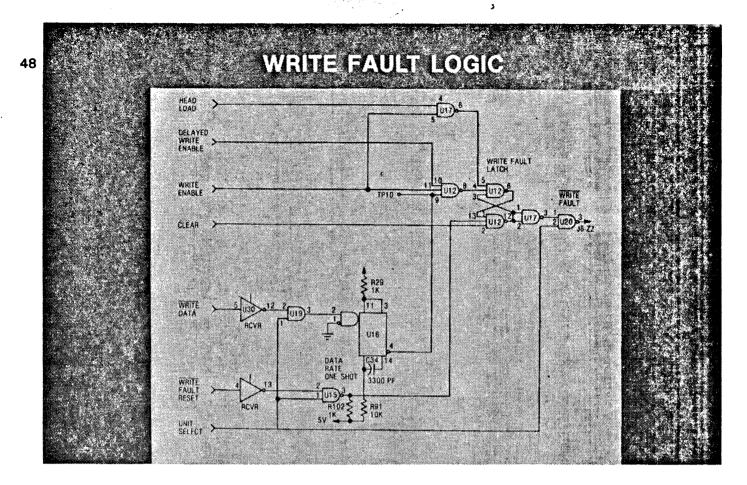

15. Refer to the drawing of the Write Fault logic given on the next page and consider the following failure condition:

The failing unit is one of two drives connected to the same host system controller. The other drive functions normally. The failing unit indicates a continuous Write Fault.

The drawing gives the condition of the various signals associated with the Write Fault latch measured during a continuous write operation.

Determine the source of the erroneous signal from the information on the drawing.

IC

PIN

## **REVIEW TEST**

## **LECTURE 2**

Write Fault Logic

## **READ THE FOLLOWING PRACTICE OBJECTIVES**

## PRACTICE OBJECTIVES:

- 1. Determine the function and mode of operation of any part of the Control Logic.

- 2. Given any Control Logic failure, use your knowledge of the Control Logic to determine the cause of the failure.

## **PRACTICE:**

- 1. This section of the Lecture assumes that you are familiar with the operation of a stepper motor. Review the section covering the theory of operation of a stepper motor in the FE Technical Manual, Volume 1 pages 6-5 to 6-6.

- 2. Continue listening to the cassette for Lecture 2 and view slides 52 to 65.

- 3. Using a BDM 1250, measure the time period that the signal Clear/ (U11-1) remains low after the +5 volt level is true.

- 4. Complete the following Review Test.

(Note: This Practice continues after the Review Test.)

## **REVIEW TEST**

## LECTURE 2

K

16. How many phases does the stepper motor have?

- a) 3

- b) 6

- c) 8

- d) 12

- e) 15

17. Each step rotates the stepper motor rotor and lead screw by:

- a) 30 degrees

- b) 120 degrees

- c) 60 degrees

- d) 12 degrees

- e) 15 degrees

- 18. State the two conditions required by the logic to determine that the read/write head is at track 00.

- 1.

- 2.

# 19. State the two functions performed by the clear signal.

- 1.

- 2.

(Continued on next page)

## **REVIEW TEST (CONTINUED)**

20. Refer to the Logic Schematic for the ICMD unit and consider the following failure condition:

The stepper motor is excessively hot. Checking the output of U7 pin 4 with a BDM 1250 indicates a 16 millisecond negative going pulse after each single step command.

List the four components most likely to account for the overheating motor.

)

- 1.

- 2.

3.

4.

Give your answers to the Course Supervisor for grading. If any answer is incorrect, review the relevant section of the Lecture before continuing.

**PRACTICE (CONTINUED)**

- 5. Continue listening to the cassette for Lecture 2 and view slides 66 to 70.

- 6. Determine whether the unit you are working with is equipped with the Head Load Time Out Option, by visual inspection.

- 7. Complete the following Review Test.

#### **REVIEW TEST**

#### **LECTURE 2**

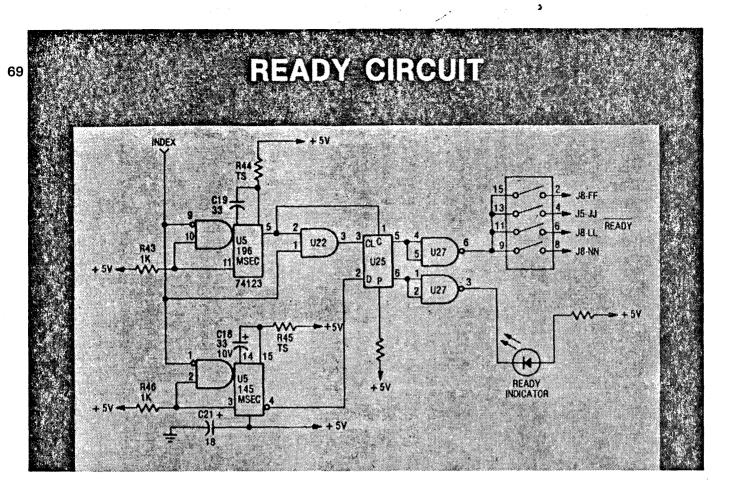

21. The Ready flip flop is set when the diskette is rotating within  $\pm 15\%$  of the normal operating speed of 360 rpm.

#### True/False

- 22. At the nominal speed of 360 rpm, one diskette revolution takes approximately:

- a) 10mS

- b) 25mS

- c) 80mS

- d) 128mS

- e) 170mS

- 23. Refer to the Logic Schematic for the ICMD unit and consider the following failure condition:

The failing unit is one of two mounted in the same cabinet. The other unit works correctly. On the failing unit, a diskette is inserted and the Ready Indicator illuminates. However, when the host system attempts to use the failing unit, it reports that the unit is not Ready. Excluding the Interface cable and components, list the three most likely suspect components.

1.

2.

3.

Give your answers to the Course Supervisor for grading. If any answer is incorrect, review the relevant section of the Lecture before continuing.

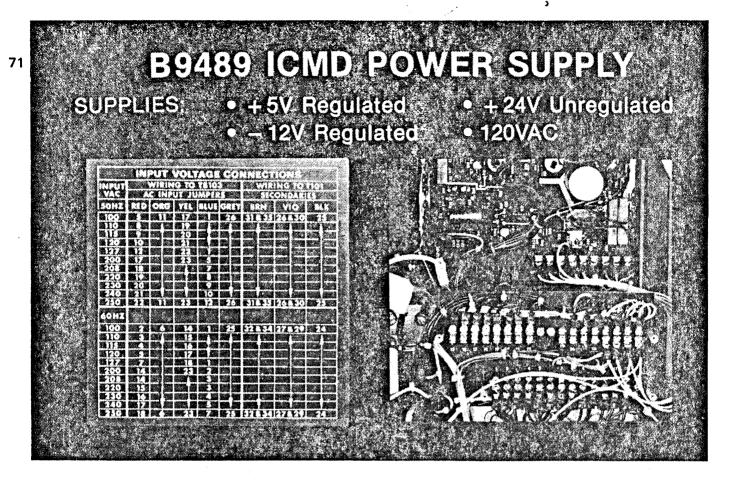

## **READ THE FOLLOWING PRACTICE OBJECTIVES**

#### **PRACTICE OBJECTIVES:**

- 1. Configure the unit power supply for operation at the correct line voltage and frequency.

- 2. Determine the purpose and function of each circuit within the power supply.

- 3. Determine the conditions which cause the power supply protection circuitry to operate.

- 4. Check power supply voltage levels and make any necessary adjustment to correct for variations in component tolerances.

#### **PRACTICE:**

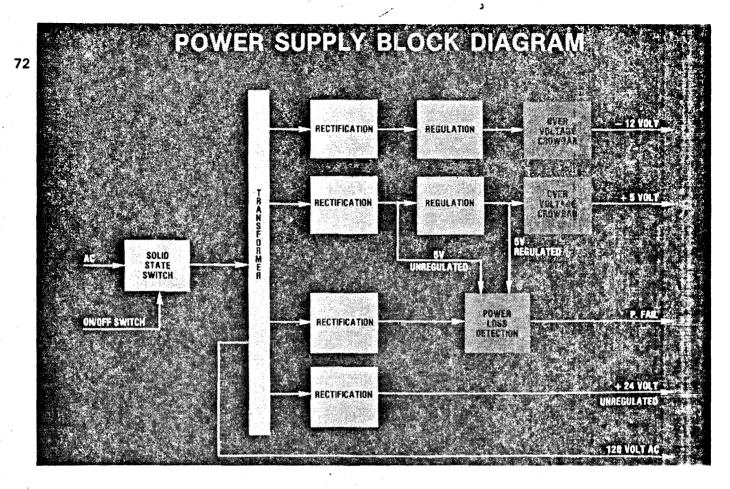

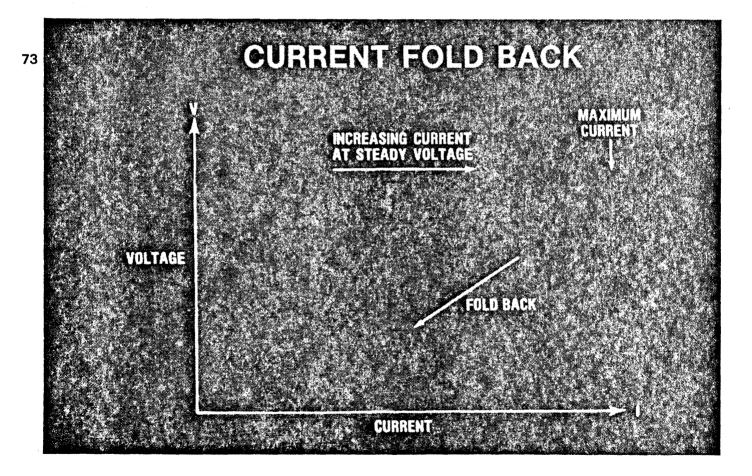

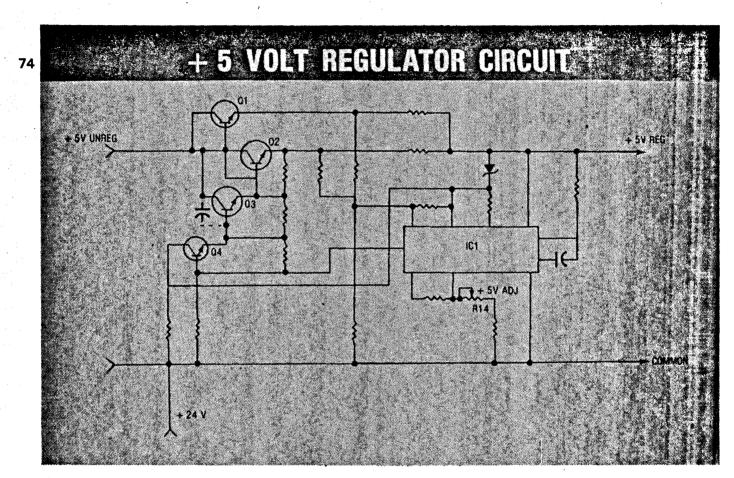

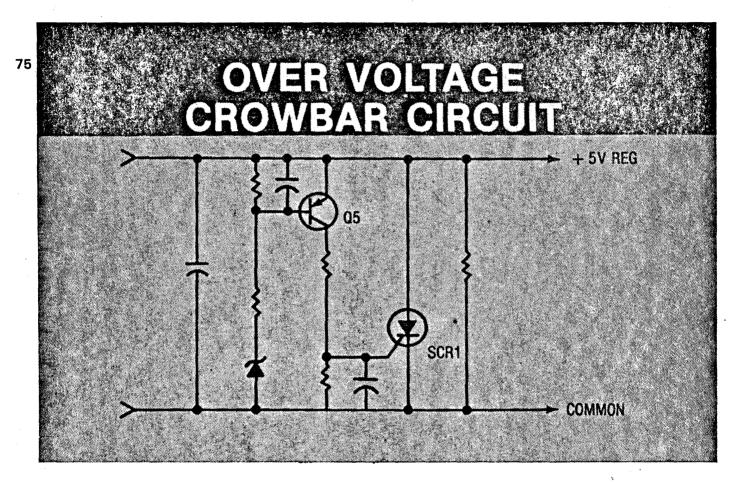

- 1. Continue listening to the cassette for Lecture 2 and view slides 71 to 77.

- 2. Check the transformer tapping for the unit you are working with against the appropriate table for the line voltage used.

- 3. Identify a suitable location to measure each voltage produced by the power supply. Measure each voltage. Locate the two adjustment potentiometers. Note that these adjustments are made during manufacture and should not require attention unless associated components are replaced.

This concludes Lecture 2.

٨

## **LECTURE 3**

#### LECTURE INTRODUCTION:

The third lecture divides into three sections:

- i) The first section describes unit installation for all styles of B 9489 ICMD units.

- ii) The second section details all ICMD unit adjustments describing their purpose and where necessary, the correct sequence. Also included are practice instructions for removal and replacement of each major component.

- iii) The third section covers unit maintenance which includes both fault finding using the MTR procedures and preventative maintenance requirements.

3

## **READ THE FOLLOWING LECTURE OBJECTIVES**

## **LECTURE OBJECTIVES:**

1. Install any style of B 9489 ICMD unit.

Υ.

- 2. Determine the need for and be able to correctly apply all unit adjustments in the correct sequence.

- 3. Remove and replace any component or sub-assembly of the ICMD unit applying all necessary adjustments.

- 4. Use the MTR and knowledge of the unit to detect any given failure and to correct the failure by adjustment or component replacement.

## READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

#### **PRACTICE OBJECTIVES:**

- 1. Correctly configure any style ICMD unit for operation with the local power supply voltage and frequency.

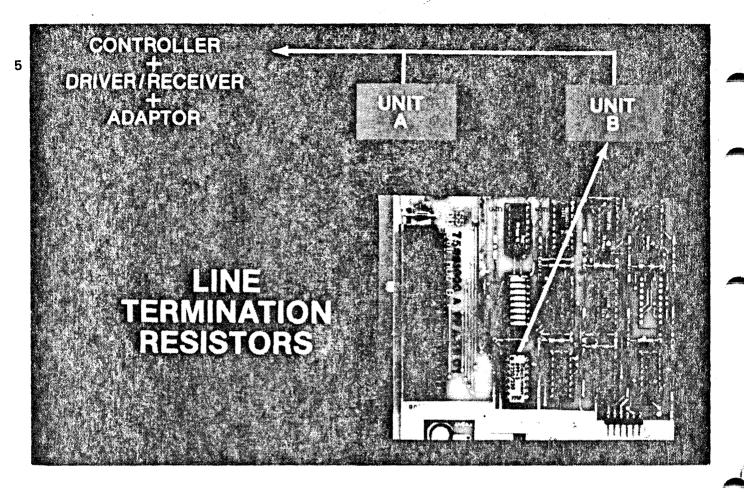

- 2. Install resistor chip terminators as necessary.

- 3. Set the unit designate number for each unit.

- 4. Correctly configure the Unit Select and Unit Ready designations.

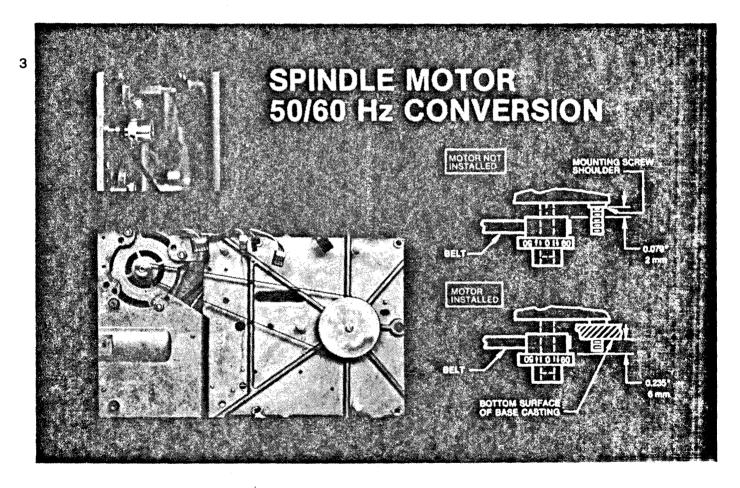

- 1. Listen to the cassette for Lecture 3 and view slides 1 to 11.

- 2. Check the drive belt alignment adjustment on the unit you are working with.

- 3. If you are working with a free standing unit, use the transformer tapping table in the Technical Manual, Volume 1, Section 2 to determine the voltage and frequency for which the unit is configured.

- 4. Review all currently released RIN, LIN and ATI information, determine whether all updates have been applied and apply any which are found to be outstanding.

- 5. Locate and determine the settings of the Unit Select and Unit Ready switches.

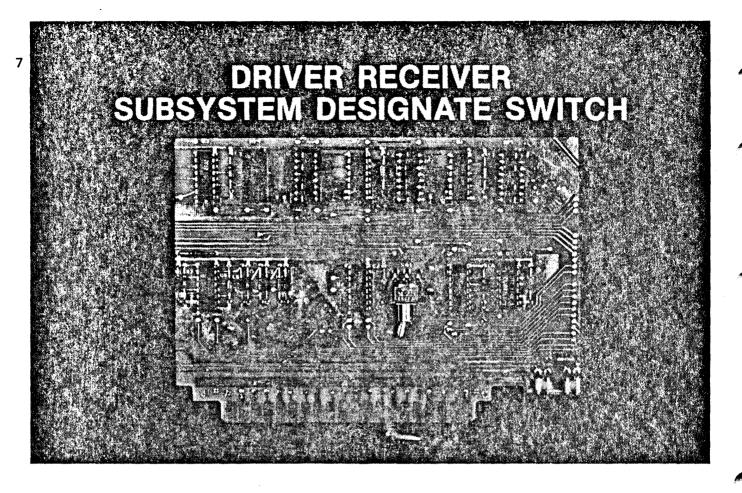

- 6. If you are working with a free standing unit, locate and determine the setting of the Subsystem Designate Switch.

## READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

## PRACTICE OBJECTIVES:

- 1. Determine for each of the following adjustments that the adjustment is correct and the effect of incorrect adjustment. Correctly perform each adjustment;

- a. Registration cone and spindle alignment.

- b. Push rod travel and door interlock switch.

- c. Head load bail.

- 2. Remove and replace any assembly or component associated with the registration cone and spindle, push rod, door interlock and head load bail assemblies.

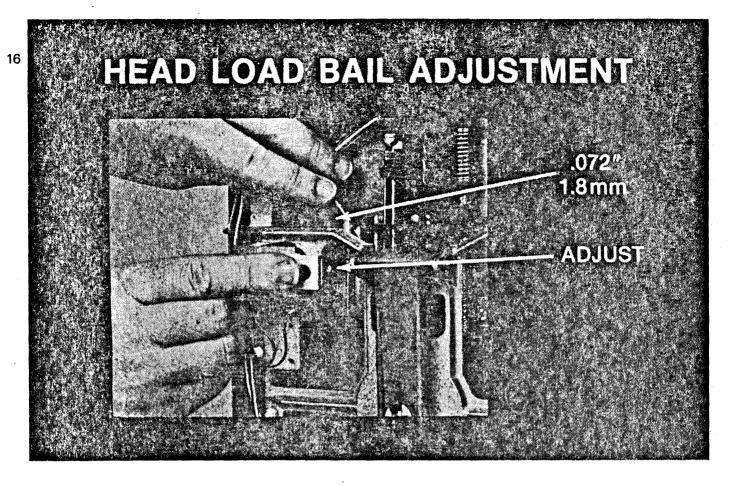

- 1. Listen to the cassette for Lecture 3 and view slides 12 to 17.

- 2. Remove and replace the chassis support assembly referring to the Technical Manual, Volume 1, Page 4-8 for the correct procedure and adjustment sequence.

- 3. Check and if necessary, perform the head load bail adjustment.

.

¢

## READ THE FOLLOWING PRACTICE OBJECTIVE AND COMPLETE THE PRACTICE

## **PRACTICE OBJECTIVE:**

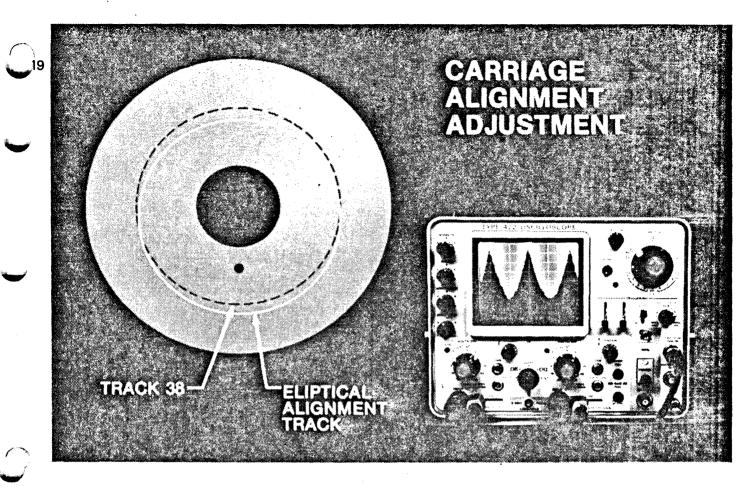

1. Ensure compatability of units by obtaining the correct carriage assembly (track) alignment.

- 1. Listen to the cassette for Lecture 3 and view slides 18 to 23.

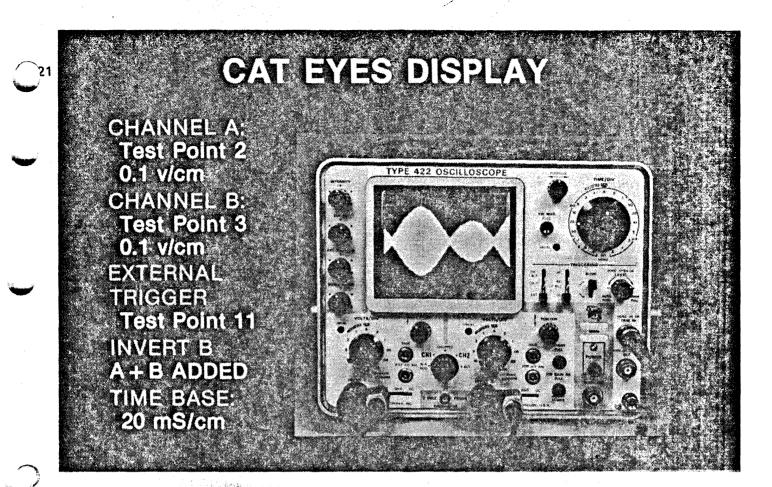

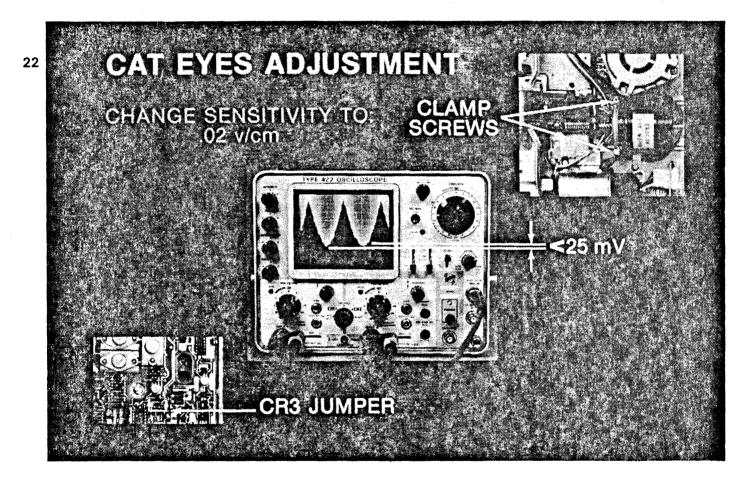

- 2. Referring to the Technical Manual, Volume 1, Page 5-5, check the cateyes alignment pattern using an alignment diskette or oscilloscope. DO NOT adjust the alignment at this time. This adjustment is performed in a later practice.

## READ THE FOLLOWING PRACTICE OBJECTIVE AND COMPLETE THE PRACTICE

## **PRACTICE OBJECTIVE:**

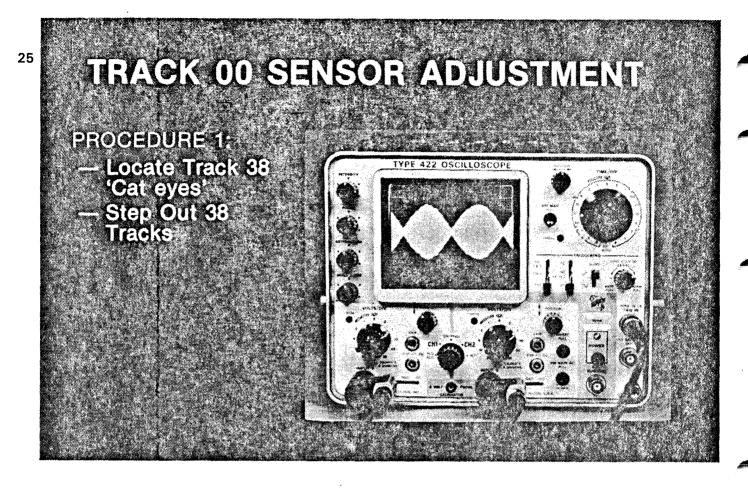

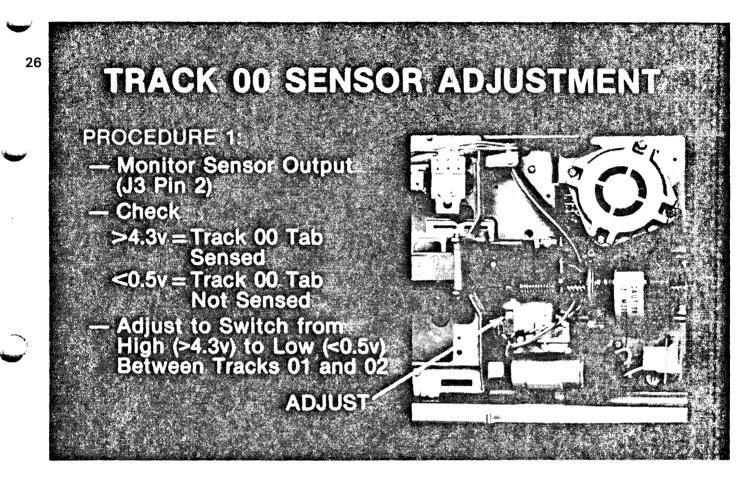

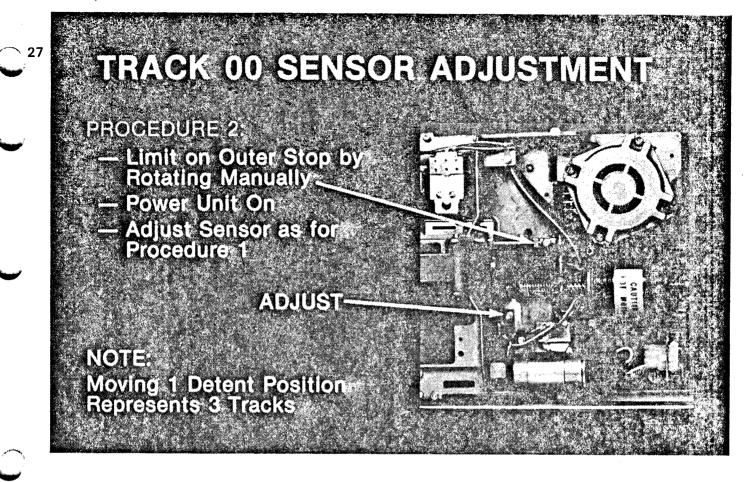

Determine the need for and correctly adjust the optical track 00 sensor using the appropriate adjustment procedure, either referenced to track 38 or to the outer carriage stop.

#### **PRACTICE:**

- 1. Listen to the cassette for Lecture 3 and view slides 23 to 28.

- 2. Referring to the Technical Manual, Volume 1, Page 5-7 through Page 5-9, verify that the adjustment of the track 00 optical sensor is correct using the two procedures described.

NOTE: These adjustments have been revised to ensure that the sensor output switches between tracks 01 and 02, i.e. J3 pin 2 should be high at tracks 00 and 01 but low at track 02. Refer to ATI 54403. DO NOT adjust the optical track 00 sensor at this time. This adjustment is performed in a later practice.

-40-

## READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

#### **PRACTICE OBJECTIVES:**

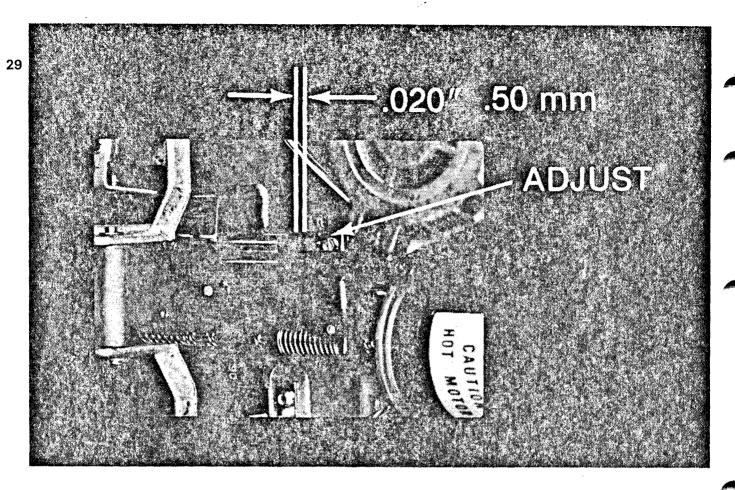

- 1. Determine the need for and correctly adjust the carriage stops.

- 2. Remove and replace any assembly or component associated with the head carriage assembly and stepper motor assembly, ensuring that following replacement, the unit is correctly adjusted for proper unit function and media compatability with other drive units.

#### PRACTICE:

- 1. Listen to the cassette for Lecture 3 and view slides 29 and 30.

- 2. Referring to the Technical Manual, Volume 1, Page 4-7 remove and replace the head carriage assembly, performing the carriage assembly (track) alignment, optical track 00 sensor and carriage stop adjustment.

-41-

## READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

#### **PRACTICE OBJECTIVES:**

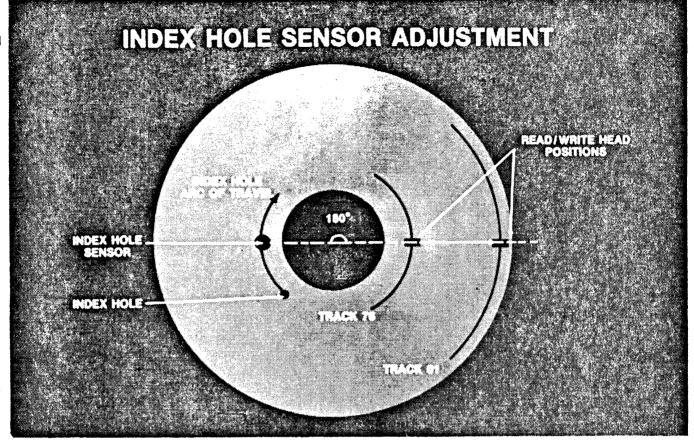

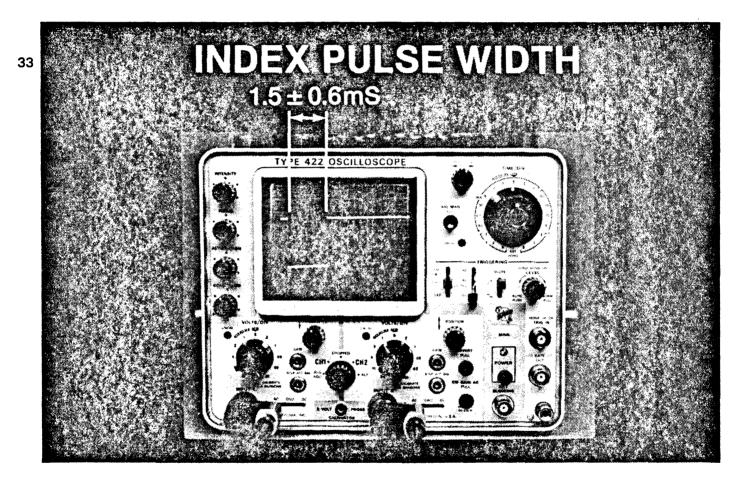

- 1. Ensure correct adjustment of the Index Hole sensor.

- 2. Given the need to replace specific electronic components, associate any related TS (test selected) resistors and determine the need to change the value of any test selected component.

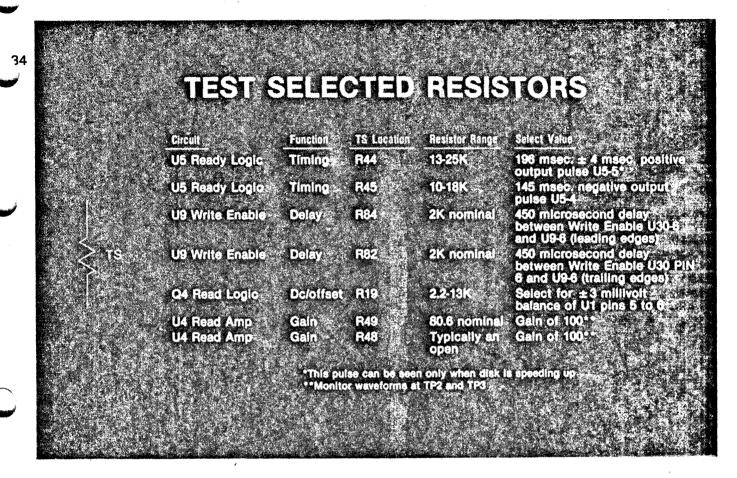

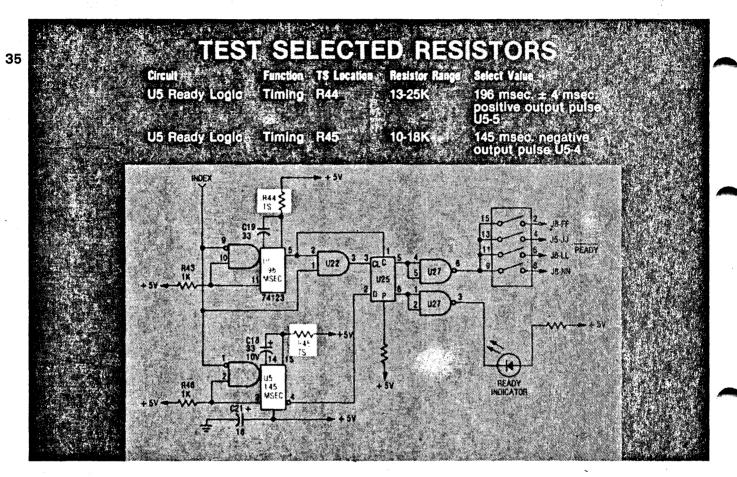

- 1. Listen to the cassette for Lecture 3 and view slides 31 to 36.

- 2. Referring to the Technical Manual, Volume 1, Page 5-11, check the optical Index sensor adjustment. Adjust if necessary.

- 3. Using the Test Selected Resistor table in the Technical Manual, Volume 1, Page 4-12, verify by measurement that the values of each test selected resistor in the unit is within tolerance.

## READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

#### **PRACTICE OBJECTIVES:**

- 1. Identify the Maintenance Philosophy for the ICMD unit.

- 2. Use the MTR, any available host system test procedures and your knowledge of the unit logic to determine that a unit is failure free or to detect and define any failure to the failed component.

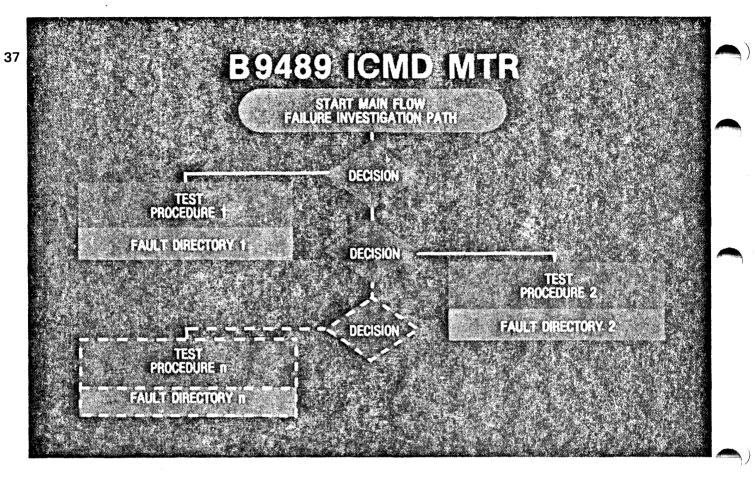

- 1. Listen to the cassette for Lecture 3 and view slides 37 to 45.

- 2. Run any available host system test program and the unit MTR failure investigation path to determine that a unit is failure free. Correct any failures or performance defects.

## READ THE FOLLOWING PRACTICE OBJECTIVES AND COMPLETE THE PRACTICE

## PRACTICE OBJECTIVE:

$S_{\rm eff} = 1$

•

- 1. Complete the preventative maintenance schedule at the prescribed interval.

- 2. Ensure that the unit is correctly adjusted and operates to specification.

#### **PRACTICE:**

- 1. Refer to the Technical Manual, Volume 1, Page 4-1 through 4-3. Read the section headed "Preventative Maintenance Procedures."

- 2. Check all adjustments and test the unit. Correct as necessary. Ask course supervisor to check the unit.

-44-

This concludes the B 9489 ICMD Field Engineering Training Program.

Review any objective which you feel that you have not fully achieved and refer any outstanding questions or problems to your Course Supervisor.

Ensure that the unit is correctly adjusted and performing to specification before asking your Course Supervisor to finally check the unit.

-45-

## **LECTURE 1**

THIS IS THE FIRST LECTURE IN THE BURROUGHS B 9489 INDUSTRY COMPATIBLE MINI DISK (ICMD) TRAINING PROGRAM. THIS FIRST LECTURE GIVES A PRODUCT DESCRIP-TION, DESCRIBING BOTH THE TYPE OF APPLICATION AND OPERATIONAL CHARAC-TERISTICS OF THE ICMD DRIVE AND INCLUDES THE BASIC RULES FOR DISK HANDL-ING AND STORAGE.

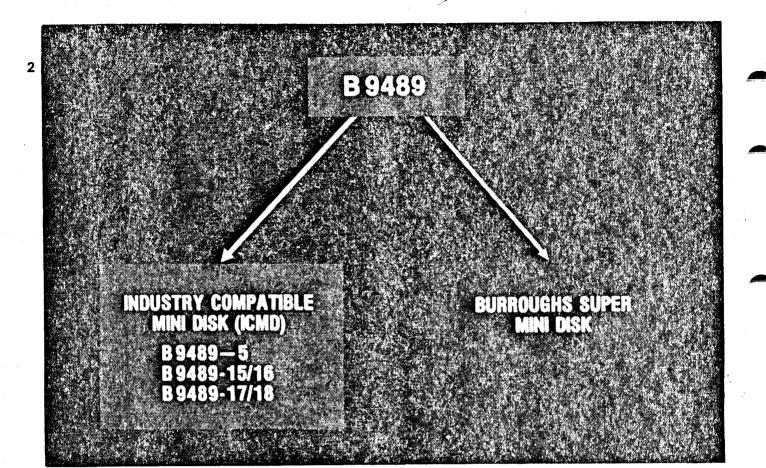

THERE ARE TWO DISTINCT GROUPS OF DISK DRIVES WITHIN THE B 9489 FAMILY WHICH SHOULD NOT BE CONFUSED. FIRST, THERE IS THE INDUSTRY COMPATIBLE MINI DISK GROUP WHICH IS THE SUBJECT OF THIS TRAINING PROGRAM. SECOND, THERE IS THE BURROUGHS SUPER MINI DISK GROUP WHICH IS DIFFERENT, BOTH IN THE HARDWARE OPERATION OF THE DRIVE AND THE FORMAT IN WHICH DATA IS RECORDED. FUTURE DEVELOPMENTS COULD ADD ADDITIONAL GROUPS TO THE FAMILY.

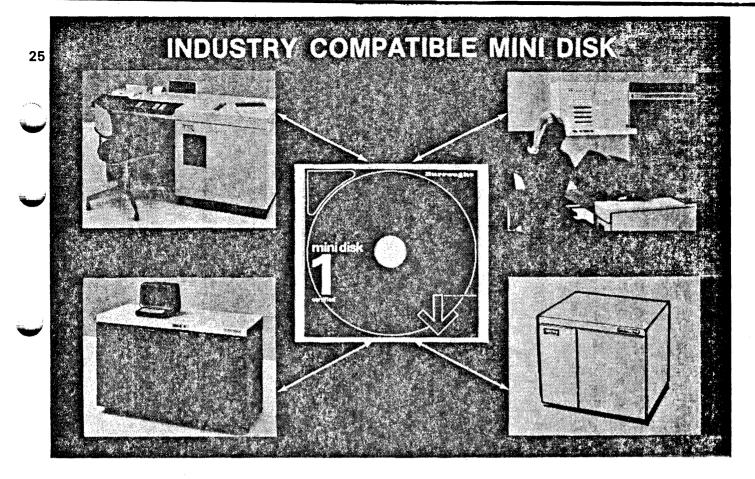

L1-2

THE ICMD FLEXIBLE DISK DRIVE SUBSYSTEMS ARE PERIPHERAL DEVICES USED IN DATA ENTRY AND STORAGE APPLICATIONS. AN INDUSTRY COMPATIBLE REMOV-ABLE MEDIA CALLED A DISKETTE OR FLEXIBLE DISK IS USED. DATA IS STORED ON THE DISKETTES USING MAGNETIC TECHNIQUES IN AN INDUSTRY COMPATIBLE FORMAT, ALLOWING MEDIA INTERCHANGE BETWEEN ANY COMPUTER SYSTEM WITH EQUIVALENT FLEXIBLE DISK DRIVE SUBSYSTEMS, REGARDLESS OF THE MANUFAC-TURER AND VENDOR.

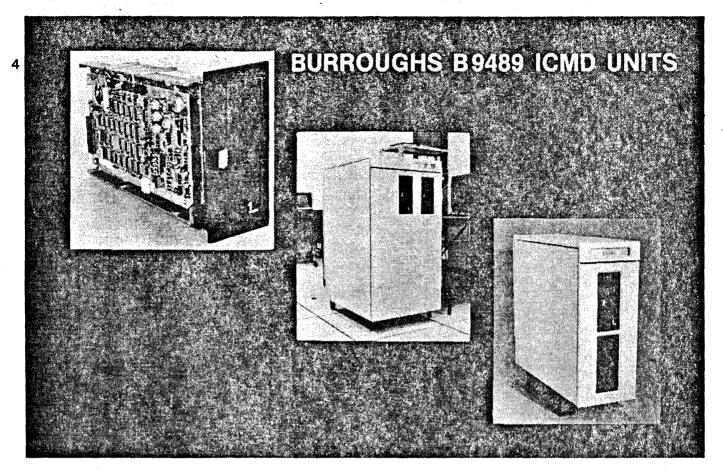

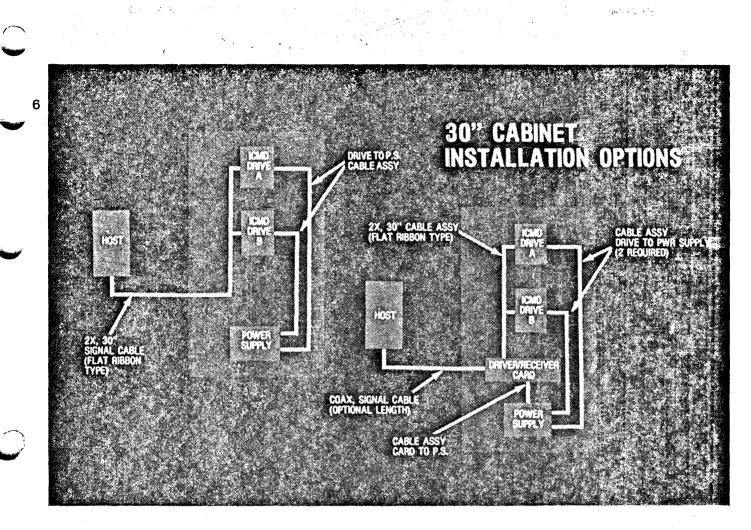

THREE BASIC CONFIGURATIONS OF THE BURROUGHS FDD SUBSYSTEM ARE AVAIL-ABLE FOR USE WITH THE VARIOUS BURROUGHS HOST SYSTEMS. EACH CONFIGU-RATION USES THE SAME BASIC DISK DRIVE. THIS DISK DRIVE MAY BE BUILT INTO THE HOST SYSTEM OR BE FREESTANDING IN EITHER A 30 OR 44 INCH HIGH CABINET. WE WILL LOOK AT EACH CONFIGURATION IN TURN.

L1-4

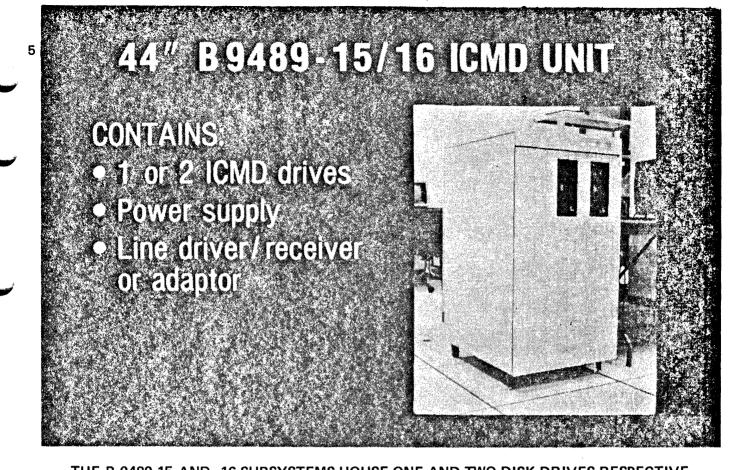

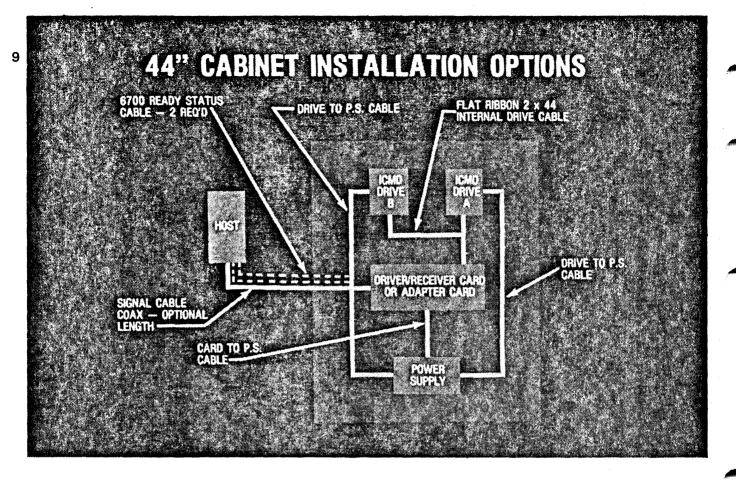

THE B 9489-15 AND -16 SUBSYSTEMS HOUSE ONE AND TWO DISK DRIVES RESPECTIVE-LY IN THE 44 INCH HIGH CABINET. THE UNIT ILLUSTRATED IS THE -16 HOUSING TWO DISK DRIVES. THESE SUBSYSTEMS FUNCTION AS STAND ALONE PERIPHERAL UNITS THAT CONTAIN ALL NECESSARY POWER SUPPLIES, INTERNAL CABLING AND EITHER A LINE DRIVER/RECEIVER CARD OR AN ADAPTOR CARD TO INTERFACE TO THE BURROUGHS HOST SYSTEM.

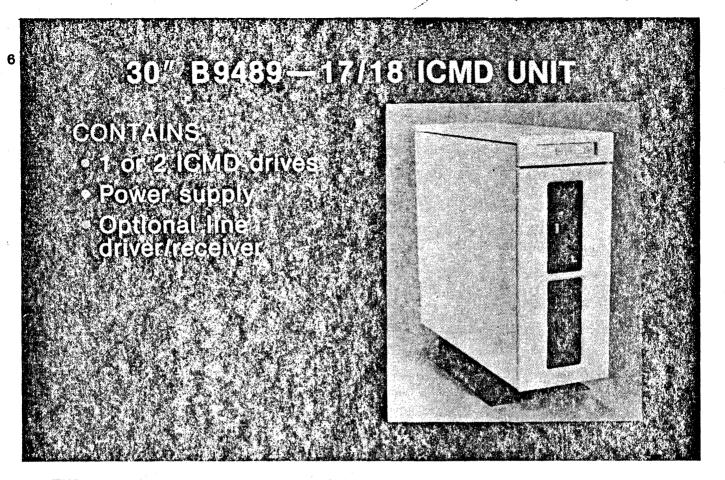

THE B 9489-17 AND -18 SUBSYSTEMS AGAIN HOUSE ONE AND TWO DISK DRIVES RESPECTIVELY, BUT IN THE 30 INCH HEIGHT CABINET. THE UNIT ILLUSTRATED IS THE -17 HOUSING ONE DISK DRIVE. LIKE THE -15 AND -16 VERSIONS, THESE SUB-SYSTEMS CONTAIN THE POWER SUPPLY AND INTERNAL CABLING. HOWEVER, THE UNIT DOES NOT HAVE THE OPTION OF AN ADAPTOR CARD AND DEPENDING ON THE REQUIREMENTS OF THE HOST SYSTEM THE DRIVER/RECEIVER CARD IS OPTIONAL.

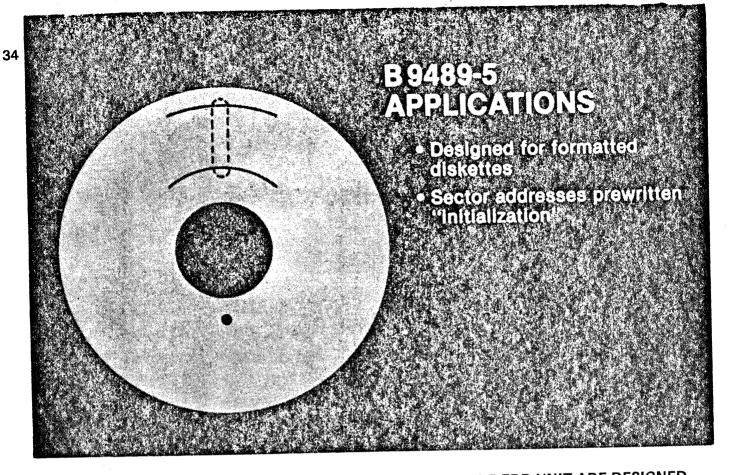

THE B 9489-5 UNIT IS THE SAME BASIC FLEXIBLE DISK DRIVE AS USED IN BOTH THE FREESTANDING CABINET SUBSYSTEMS, BUT WITHOUT THE POWER SUPPLY AND CABLING. THIS UNIT IS DESIGNED FOR MOUNTING IN THE HOST SYSTEM CABINETRY AND POWER MUST BE PROVIDED BY THE HOST SYSTEM.

THESE THREE BASIC CONFIGURATIONS OF THE BURROUGHS FDD SUBSYSTEM ALLOW THE INDUSTRY COMPATIBLE MINI DISK TO BE USED WITH A WIDE RANGE OF BURROUGHS PRODUCTS FROM SMALL SYSTEMS SUCH AS THE B 80 THROUGH TO VERY LARGE SYSTEMS SUCH AS THE B 7700.

LET US LOOK AT THE MINI DISK OR DISKETTE MEDIA ITSELF IN MORE DETAIL AND CONSIDER SOME OF THE HANDLING AND STORAGE PROCEDURES WHICH SHOULD BE FOLLOWED TO MINIMIZE THE RISK OF MEDIA DAMAGE.

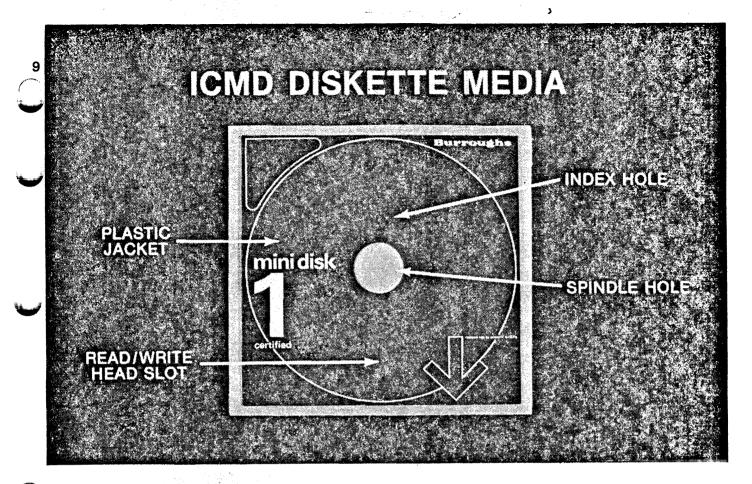

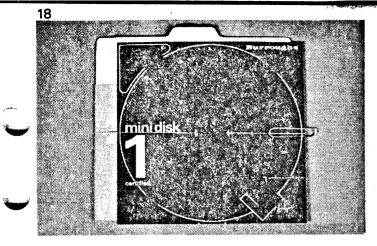

THE DISKETTE IS CONTAINED IN A FLEXIBLE PLASTIC JACKET FROM WHICH IT IS NEVER REMOVED. THE DISK IS COATED ON ONE SIDE WITH A MAGNETIC OXIDE SIMILAR TO THAT USED ON AUDIO RECORDING TAPE.

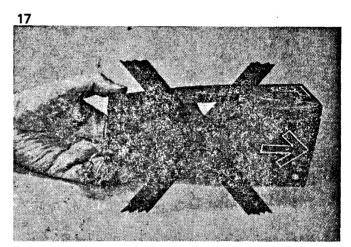

THE CENTRAL SPINDLE HOLE IS USED TO BOTH REGISTER -- THAT IS CORRECTLY ALIGN -- AND ROTATE THE DISK.

A SMALL HOLE, CALLED THE INDEX HOLE, IS LOCATED CLOSE TO THE SPINDLE

L1—9

HOLE. THE INDEX HOLE IS SENSED AS IT PASSES AN OPTICAL SENSOR IN THE FDD TO GENERATE A TIMING PULSE CALLED "INDEX" WHICH OCCURS ONCE PER DISK-ETTE REVOLUTION.

DURING A READ OR WRITE OPERATION, THE FDD READ/WRITE HEAD CONTACTS THE DISKETTE SURFACE THROUGH AN OPEN SLOT IN THE PLASTIC JACKET.

10

# DISKETTE MEDIA CARE AND HANDLING

Improper care and handling of Diskette Media can result in: • Physical Damage • Contamination • Loss of Recorded Data

PROPER CARE AND HANDLING OF THE DISKETTE IS ESSENTIAL TO ENSURE LONG DISKETTE LIFE AND TO MINIMIZE THE POSSIBILITY OF MEDIA ERRORS. IMPROPER CARE AND HANDLING CAN RESULT IN THREE MAIN TYPES OF DAMAGE. THESE ARE PHYSICAL DAMAGE, CONTAMINATION AND LOSS OF RECORDED DATA.

L1 – 10

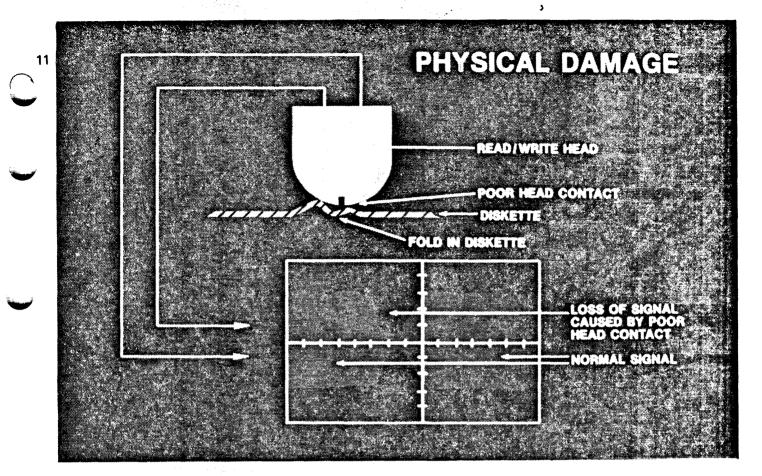

THE FIRST TYPE OF DAMAGE, PHYSICAL DAMAGE SUCH AS FOLDS, SCRATCHES OR DISTORTION OF THE DISK, CAUSES ERRORS BECAUSE THE READ/WRITE HEAD IS UNABLE TO MAINTAIN CLOSE CONTACT WITH THE MAGNETIC OXIDE RECORDING SURFACE OF THE DISK RESULTING IN A LOSS OF SIGNAL DURING A READ OPERA-TION OR BADLY RECORDED DATA DURING A WRITE OPERATION. IN SERIOUS CASES, DAMAGE TO THE READ/WRITE HEAD ITSELF MAY OCCUR.

L1-11

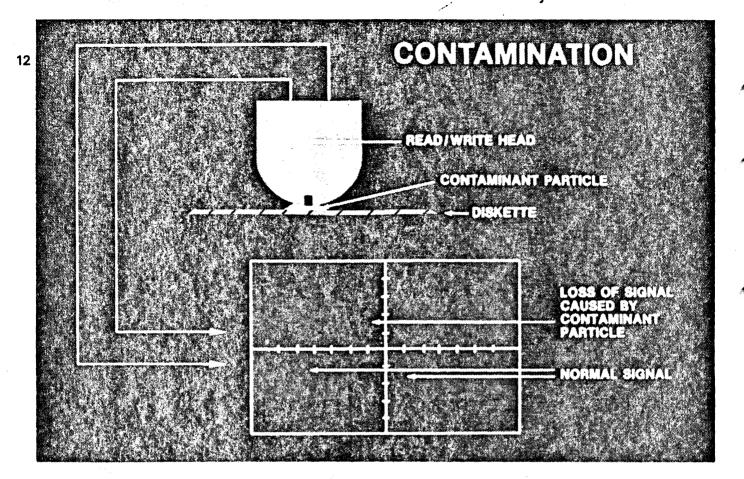

THE SECOND TYPE OF DAMAGE, CONTAMINATION, IS CAUSED BY PARTICLES OF DIRT ON THE MAGNETIC OXIDE SURFACE OF THE DISKETTE. AS WITH PHYSICAL DAMAGE, CONTAMINATION CAN CAUSE THE READ/WRITE HEAD TO LOOSE CLOSE CONTACT WITH THE MAGNETIC OXIDE RECORDING SURFACE OF THE DISK RESULTING IN A LOSS OF SIGNAL DURING A READ OPERATION OR, BADLY RECORDED DATA DURING A WRITE OPERATION.

TYPICAL CONTAMINANTS ARE DUST, FOOD PARTICLES AND CIGARETTE ASH. CON-TAMINANTS CAN CAUSE SCRATCHES IN BOTH THE DISKETTE SURFACE AND READ/ WRITE HEAD AND CAN BUILD UP ON THE READ/WRITE HEAD TO BE TRANSFERRED FROM DISKETTE TO DISKETTE.

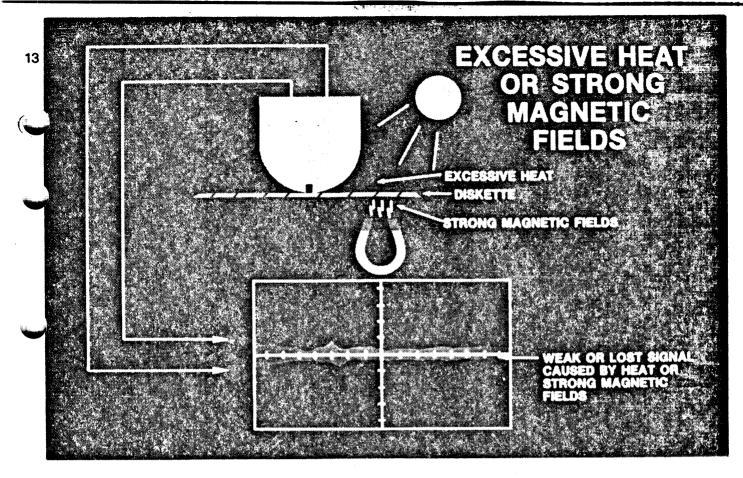

THE THIRD TYPE OF DAMAGE IS LOSS OF DATA RECORDED ON THE MAGNETIC OXIDE CAUSED BY EXPOSURE TO STRONG MAGNETIC FIELDS OR EXCESSIVE HEAT. STRONG MAGNETIC FIELDS CAN ERASE THE MAGNETICALLY RECORDED DATA ON THE DISK-ETTE CAUSING LOSS OF SIGNAL DURING A READ OPERATION. EXCESSIVE HEAT CAN BOTH ERASE MAGNETICALLY RECORDED DATA AND CAUSE PHYSICAL DISTORTION OF THE DISK.

TO AVOID SUCH HAZARDS, REMEMBER THE FOLLOWING RULES WHEN HANDLING DISKETTES.

DO NOT TOUCH THE DISKETTE SURFACE EXPOSED BY THE JACKET SLOT.

DO NOT LEAVE DISKETTE WITHOUT PROTECTIVE ENVELOPE WHEN NOT IN USE.

DO NOT WRITE ON THE JACKET LABEL WITH A LEAD PENCIL OR BALL POINT PEN SURFACE DAMAGE OR CONTAMINATION CAN RESULT. A FELT TIP PEN IS RECOM-MENDED.

DO NOT FOLD OR BEND THE DISKETTE.

DO NOT USE RUBBER BANDS OR PAPER CLIPS ON DISKETTES.

DO NOT PLACE HEAVY OBJECTS ON DISKETTES.

DO NOT SMOKE, EAT OR DRINK WHILE HANDLING DISKETTES.

DO NOT ATTEMPT TO CLEAN THE MAGNETIC OXIDE SURFACE. SUBSTANCES SPILLED ON THE DISKETTE JACKET CAN BE REMOVED AND DATA RECOVERED ONLY IF THE CONTAMINANT DOES NOT REACH THE RECORDING SURFACE.

## **DISKETTE STORAGE**

- Store in protective envelope

- Store envelopes vertically in box or cabinet

- Keep away from magnetic fields

- Protect from excessive heat, moisture and direct sunlight

- Replace worn, cracked and distorted envelopes

Replace damaged and contaminated diskettes

AS WITH DISKETTE HANDLING, CERTAIN RULES SHOULD BE APPLIED TO DISKETTE STORAGE:

- ALWAYS STORE THE DISKETTE IN THE PROTECTIVE ENVELOPE WHEN NOT IN USE.

- STORE THE PROTECTED DISKETTE IN THE BOX OR A CABINET IN A VERTICAL POSITION.

- KEEP THE DISKETTE AWAY FROM MAGNETIC FIELDS OR MATERIALS WHICH MAY BE MAGNETIZED.

- PROTECT THE DISKETTE FROM EXCESSIVE HEAT, MOISTURE AND DIRECT SUNLIGHT. ENVIRONMENTAL LIMITS ARE SPECIFIED IN THE TECHNICAL MANUAL.

- REPLACE STORAGE ENVELOPES THAT HAVE BECOME WORN, CRACKED OR

**DISTORTED.**

• REPLACE DAMAGED OR CONTAMINATED DISKETTES AND REMEMBER, A DAM-AGED OR CONTAMINATED DISKETTE CAN CAUSE DAMAGE TO THE DISK DRIVE

ITSELF AND SUBSEQUENTLY TO OTHER DISKETTES.

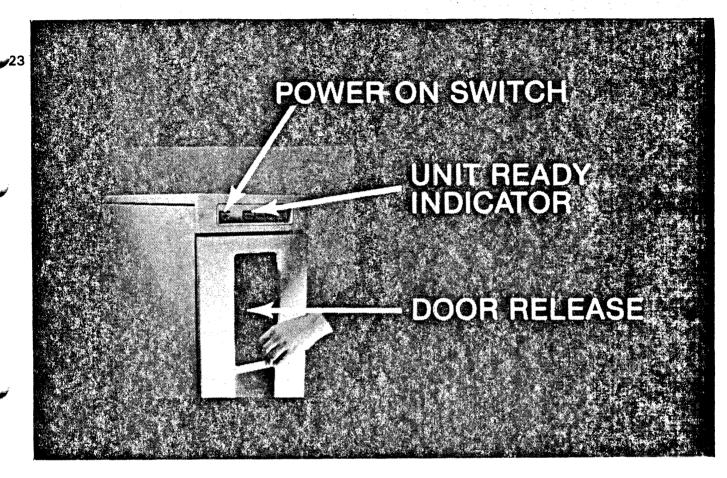

TO OPERATE THE B 9489 ICMD DRIVE, THE OPERATOR IS REQUIRED TO OPEN THE SPRING LOADED DOOR, INSERT THE DISKETTE FULLY INTO THE DRIVE MECHANISM AND CLOSE THE DOOR. ALL SUBSEQUENT OPERATIONS ARE CONTROLLED BY THE HOST SYSTEM.

A UNIT READY INDICATOR IS PROVIDED ON BOTH THE FREESTANDING CABINET AND HOST SYSTEM MOUNTED VERSIONS. THE UNIT READY INDICATOR INDICATES THAT THE DISKETTE IS INSERTED CORRECTLY, THE DOOR IS CLOSED AND THE DISKETTE IS ROTATING AT THE CORRECT SPEED.

A POWER ON SWITCH IS PROVIDED ON FREE STANDING UNITS WHICH CONTAIN AN

INTERNAL POWER SUPPLY, INDEPENDENT OF THE HOST SYSTEM.

**STOP THE LECTURE AT THIS POINT AND RETURN TO YOUR WORKBOOK. COMPLETE THE PRACTICE FOR THIS SECTION BEFORE CONTINUING.**

CONTINUING WITH THIS FIRST LECTURE, YOU WILL REMEMBER THAT WE SAID THE MEDIA IS INDUSTRY COMPATIBLE, MEANING THAT THE DATA FORMATS AND ENCOD-ING METHODS USED ON THE DISKETTE ARE THE SAME AS THOSE USED BY OTHER MANUFACTURERS TO ALLOW MEDIA INTERCHANGE BETWEEN DIFFERENT MANU-FACTURERS COMPUTER SYSTEMS.

LET US LOOK FIRST AT THE DISKETTE FORMAT AND SECOND, AT THE ENCODING METHOD. BOTH ARE USED TO MAKE THIS MEDIA INTERCHANGE POSSIBLE.

THE DISKETTE HAS A TOTAL OF 77 TRACKS. 73 OF THESE TRACKS ARE USED TO STORE DATA. TWO OF THE REMAINING FOUR TRACKS ARE RESERVED FOR USE AS ALTERNATIVE DATA TRACKS IF ANY OF THE NORMAL 73 TRACKS ARE FOUND TO CONTAIN MEDIA FLAWS AND CONSEQUENTLY CANNOT BE USED.

ONE OF THE REMAINING TWO TRACKS IS RESERVED FOR MAINTENANCE PURPOSES AND IS NOT NORMALLY USED BY BURROUGHS.

THE REMAINING TRACK IS THE FIRST PHYSICAL TRACK ON THE DISK, TRACK 00, WHICH CONTAINS DESCRIPTIVE INFORMATION ABOUT THE DATA RECORDED ON THE DISKETTE. THIS INFORMATION INCLUDES THE LABEL NAMES OF FILES WRITTEN ON THE DISKETTE, THE DISKETTE ADDRESSES TO INDICATE WHERE THE FILES ARE LOCATED, THE ERROR DIRECTORY, ETC. YOU CAN FIND A DETAILED DESCRIPTION OF THE CONTENT OF THE INDEX TRACK IN SECTION 1 OF THE FIELD ENGINEERING TECHNICAL MANUAL.

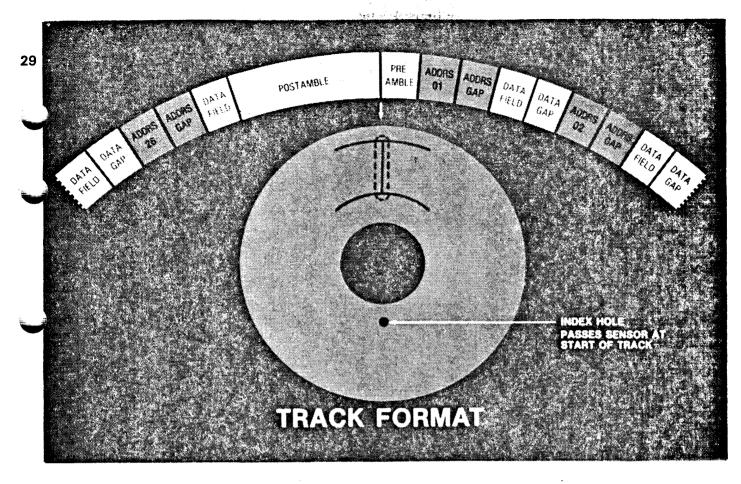

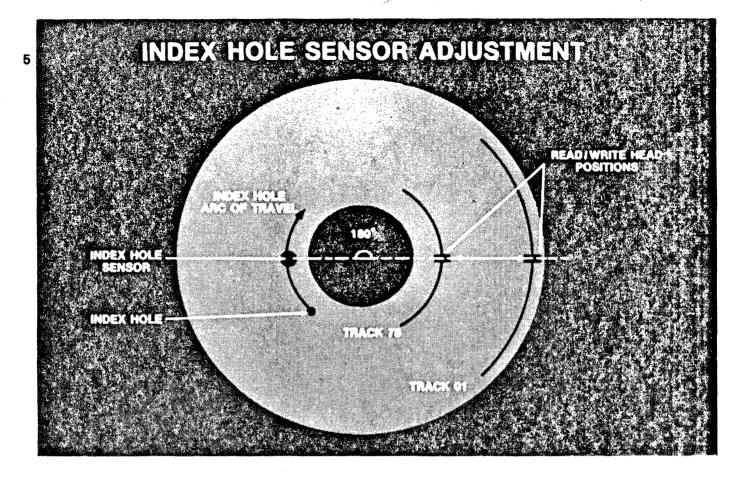

THE START OF A TRACK IS INDICATED TO THE MINI DISK CONTROLLER IN THE HOST SYSTEM BY THE SIGNAL "INDEX" AS THE INDEX HOLE PASSES THE OPTICAL SENSOR, WHICH IS 180 DEGREES FROM THE READ/WRITE HEAD.

STARTING OPPOSITE THE INDEX HOLE, AT THE START OF A TRACK, THE TRACK CON-SISTS OF A SINGLE PREAMBLE FIELD FOLLOWED BY AN ADDRESS FIELD AND AN ADDRESS GAP FIELD. THE ADDRESS GAP FIELD IS FOLLOWED BY A DATA FIELD, SOMETIMES CALLED A SECTOR, AND A DATA GAP FIELD. WITH THE EXCEPTION OF THE PREAMBLE FIELD, THIS SEQUENCE IS REPEATED 26 TIMES WITH THE 26TH DATA FIELD FOLLOWED BY A POSTAMBLE FIELD SIGNIFYING THE END OF THE TRACK.

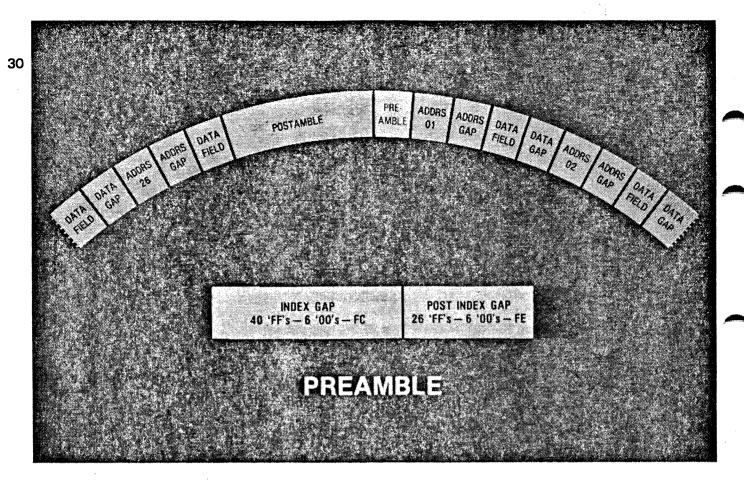

TAKING EACH FIELD IN TURN, THE PREAMBLE FIELD DIVIDES INTO TWO PARTS, THE INDEX GAP AND THE POST INDEX GAP.

THE INDEX GAP CONTAINS 40 "FF" CHARACTERS FOLLOWED BY SIX "00" CHARAC-TERS. THESE ARE FOLLOWED BY THE HEXADECIMAL CHARACTERS "FC" WHICH ARE THE INDEX SYNC MARK BYTE.

SYNC MARK BYTES ARE USED TO IDENTIFY THE BEGINNING OF FIELDS AND TO SYNCHRONIZE THE READ LOGIC IN THE CONTROLLER.

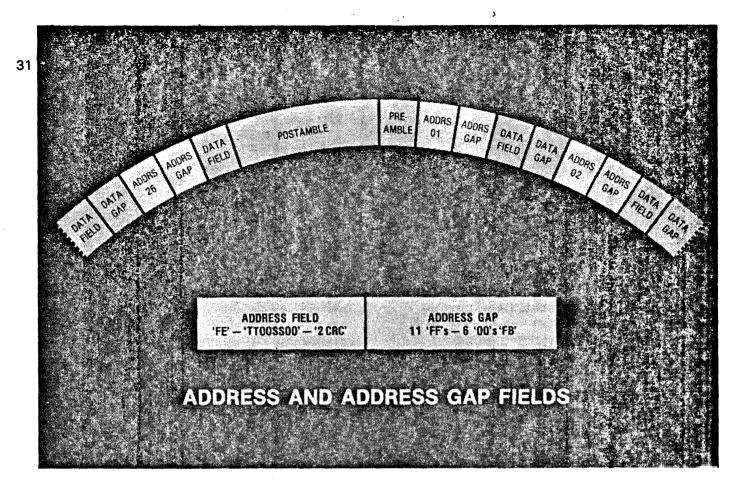

THE POST INDEX GAP FOLLOWS IMMEDIATELY CONTAINING 26 "FF" CHARACTERS FOLLOWED BY SIX "00" CHARACTERS AND THE ADDRESS SYNC MARK BYTE. THE ADDRESS SYNC MARK BYTE IS THE HEXADECIMAL CHARACTER "FE" TO IDENTIFY THE FOLLOWING FIELD AS AN ADDRESS FIELD.

THE FIRST ADDRESS FIELD FOLLOWS THE PREAMBLE AND CONTAINS THE ADDRESS OF THE FIRST DATA FIELD. IN THE FORMAT SHOWN IN THE DIAGRAM, "TT" RE-PRESENTS THE TRACK ADDRESS IN THE RANGE 00 THROUGH 76, "00" IS A SEPARA-TOR "SS" REPRESENTS THE SECTOR, THAT IS DATA FIELD ADDRESS, "00" IS AN-OTHER SEPARATOR FOLLOWED BY TWO CYCLIC REDUNDANCY CHECK (CRC) CHARACTERS.

TWO CRC CHARACTERS ARE USED AT THE END OF THE ADDRESS FIELD TO ENSURE THAT DATA IS READ BACK CORRECTLY FROM THE DISKETTE.

AN ADDRESS GAP FIELD FOLLOWS EACH ADDRESS FIELD. THIS FIELD CONTAINS NO DATA AND IS USED TO ALLOW TIME FOR THE WRITE LOGIC TO TURN ON, DURING A WRITE OPERATION, AFTER THE ADDRESS HAS BEEN READ. THE ADDRESS GAP FIELD CONTAINS 11 "FF" CHARACTERS FOLLOWED BY SIX "00" CHARACTERS AND THE DATA SYNCH MARK CHARACTER "FB". NOTE THAT ALTHOUGH THE FIRST 11 CHARACTERS ARE PREFERABLY "FF"S, "00" CHARACTERS ARE PERMISSIBLE AND MAY BE USED BY SOME SYSTEMS.

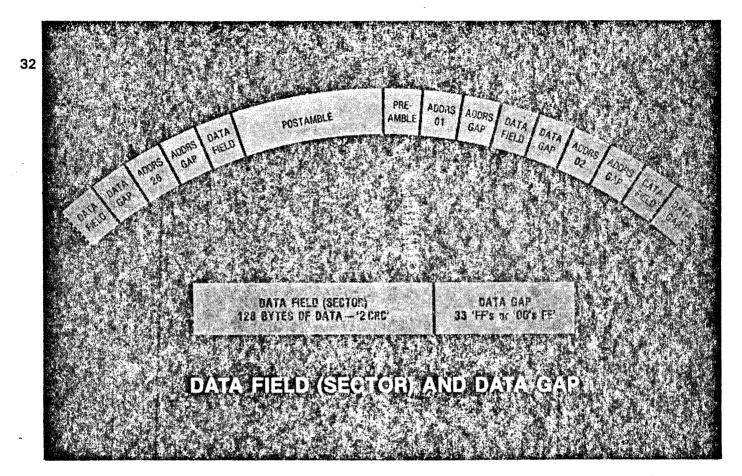

AFTER THE DATA SYNCH MARK CHARACTER "FB" IN THE ADDRESS GAP FIELD COMES THE DATA FIELD OR SECTOR. THIS CONSISTS OF 128 BYTES OF DATA FOLLOWED BY TWO CRC CHARACTERS TO CHECK THAT DATA READ BACK FROM THE DATA FIELD IS CORRECT.

THE DATA FIELD IS FOLLOWED BY A DATA GAP FIELD WHICH LIKE THE ADDRESS FIELD GAP CONTAINS NO DATA. THE DATA GAP FIELD CONTAINS 33 "FF" OR "00"

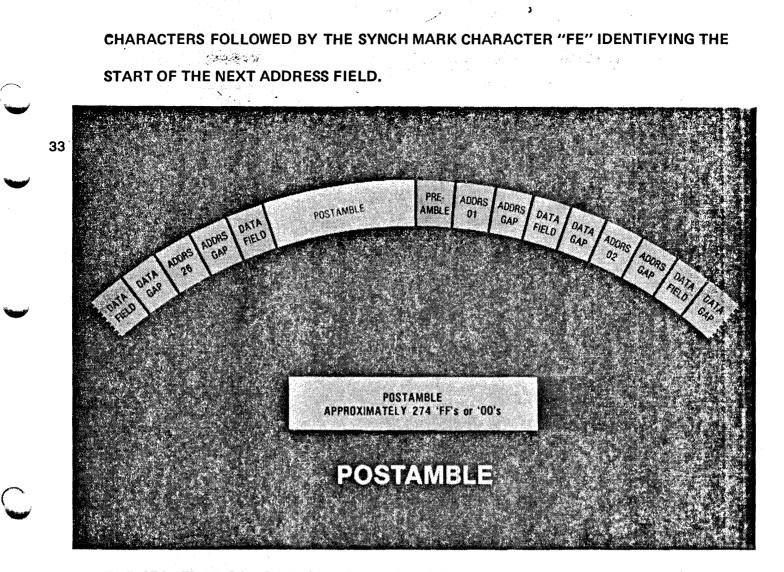

THE SEQUENCE OF ADDRESS FIELD, ADDRESS GAP FIELD, DATA FIELD AND DATA GAP FIELD REPEATS UNTIL THE 26TH SECTOR WHICH IS THE LAST SECTOR ON THE TRACK. THIS IS FOLLOWED IMMEDIATELY BY THE POSTAMBLE FIELD. THE POST-AMBLE FIELD CONSISTS OF "FF" OR "00" CHARACTERS WHICH FILL THE AREA OF TRACK BETWEEN THE END OF THE LAST DATA FIELD AND THE INDEX HOLE. RE-MEMBER, THE INDEX HOLE INDICATES THE START OF THE TRACK PREAMBLE. THE POSTAMBLE IS NOMINALLY ABOUT 274 CHARACTERS LONG BUT THIS NUMBER WILL VARY DEPENDING ON WRITE FREQUENCY AND DISK SPEED TOLERANCES.

APPLICATIONS FOR WHICH BURROUGHS USES THE B 9489-5 FDD UNIT ARE DESIGNED FOR FORMATTED DISKETTES. FORMATTED DISKETTES HAVE THE SECTOR AD-DRESSES PREWRITTEN ON THEM. THE PROCESS OF WRITING THESE ADDRESSES IS CALLED DISK INITIALIZATION.

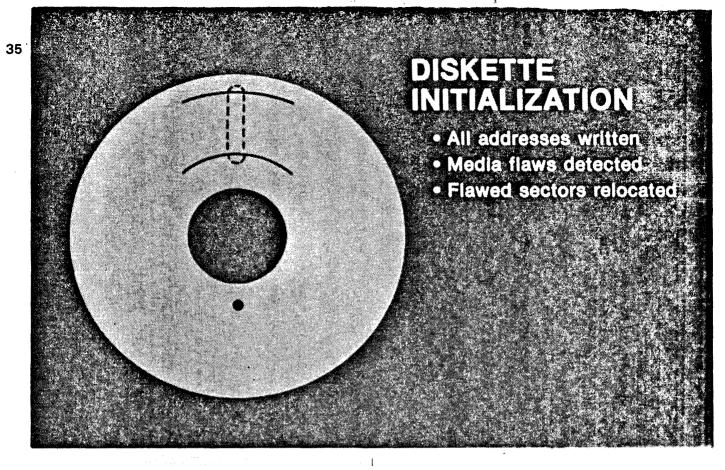

WHEN A DISKETTE IS INITIALIZED, EVERY TRACK IS WRITTEN FROM BEGINNING TO END WITHOUT INTERRUPTION TO ENSURE READABILITY FROM FDD TO FDD. AN-OTHER PART OF THE DISKETTE INITIALIZATION SEQUENCE DETERMINES THE PRE-SENCE OF POSSIBLE MEDIA FLAWS IN EACH TRACK. WHEN A MEDIA FLAW IS EN-COUNTERED IN A TRACK, THE HOST SYSTEM WRITES A SPECIAL DELETED DATA SYNC MARK CHARACTER "F8" IN PLACE OF THE NORMAL "FB" DATA SYNC MARK CHARACTER. THE TRACK AND SECTOR ADDRESS IN WHICH THE MEDIA FLAW IS DETECTED ARE STORED IN THE INDEX TRACK 00 ERROR TRACK DIRECTORY AND AN ALTERNATIVE RECORD LOCATION GIVEN UTILIZING THE TWO SPARE TRACKS.

## DOUBLE FREQUENCY ENCODINC

# Clock and data written serially Clock bit precedes data bit

INFORMATION IS WRITTEN ON THE DISKETTE USING A DOUBLE FREQUENCY EN-CODING METHOD IN WHICH CLOCK AND DATA BITS ARE WRITTEN SERIALLY WITH EACH DATA BIT PRECEDED BY A CLOCK BIT.

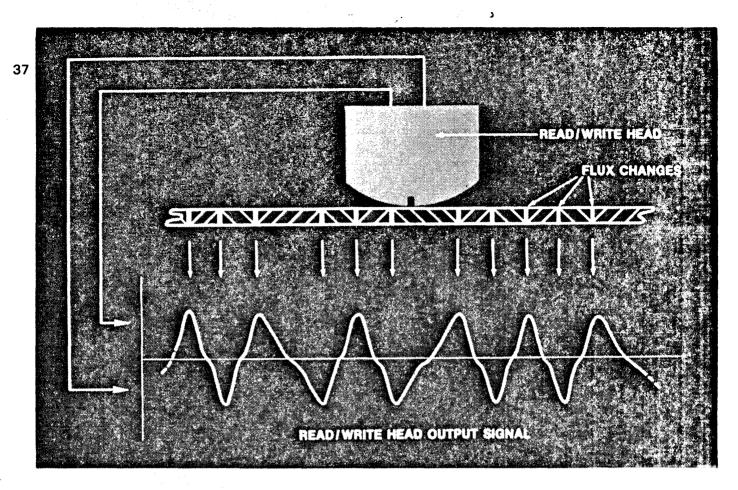

ONE BITS AND CLOCK BITS ARE REPRESENTED BY A CHANGE IN DIRECTION OF MAGNETIC FLUX RECORDED IN THE OXIDE COATING ON THE DISKETTE. WHEN THE DISKETTE ROTATES UNDER THE READ/WRITE HEAD DURING A READ OPERATION, THESE FLUX CHANGES PRODUCE EITHER POSITIVE OR NEGATIVE GOING PEAKS IN THE OUTPUT FROM THE READ/WRITE HEAD DEPENDING ON THE DIRECTION OF THE FLUX CHANGE.

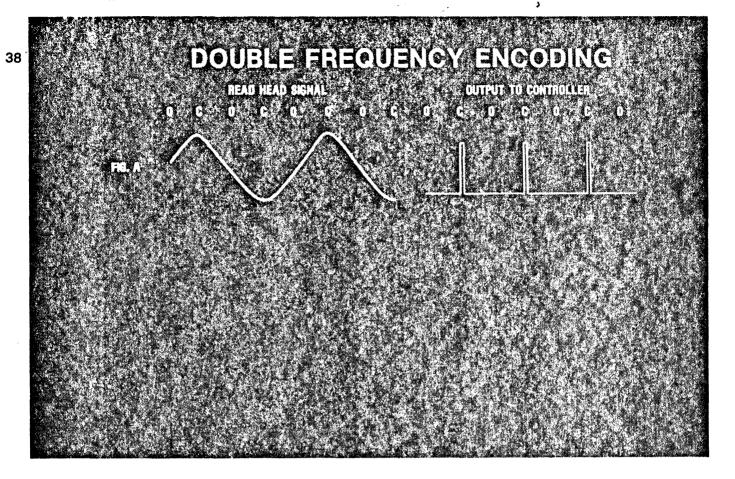

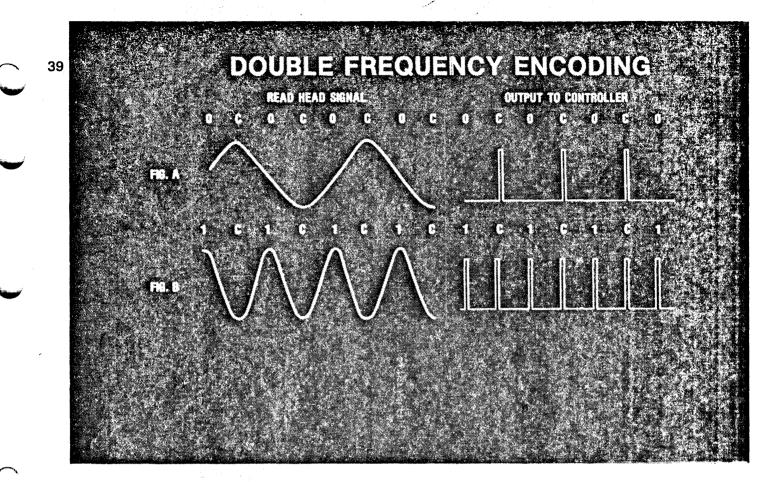

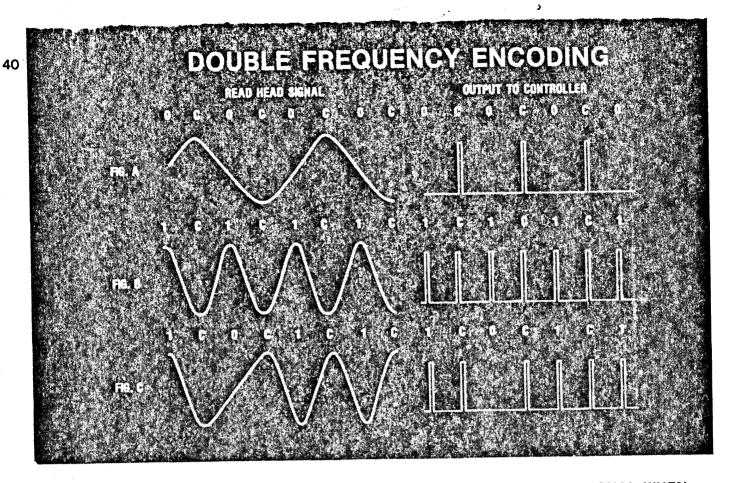

THE CLOCKS ACT AS DATA WINDOWS. IF THERE IS NO PEAK BETWEEN CLOCKS, THE DATA BIT IS A ZERO. FIGURE "A" REPRESENTS THE DIFFERENTIAL READ HEAD OUT-PUT SIGNAL FOR ALL ZERO BITS. ALL THE PEAKS SHOWN, BOTH POSITIVE AND NEGA-TIVE GOING, ARE CLOCK BITS. THE READ LOGIC WITHIN THE FDD UNIT PRODUCES A COMPOSITE DIGITAL READ DATA SIGNAL WHICH IS OUTPUT TO THE HOST SYSTEM CONTROLLER. THIS DIGITAL SIGNAL IS REPRESENTED ON THE RIGHT HAND SIDE OF FIGURE "A".

IF THERE IS A PEAK BETWEEN CLOCKS THE DATA BIT IS A ONE. FIGURE "B" SHOWS THE DIFFERENTIAL READ HEAD OUTPUT SIGNAL FOR ALL ONE BITS. ALTERNATE PEAKS REPRESENT CLOCK AND ONE BITS, WITH THE COMPOSITE DIGITAL READ SIGNAL OUTPUT TO THE CONTROLLER SHOWN TO THE RIGHT OF THE FIGURE.

FIGURE "C" REPRESENTS THE DIFFERENTIAL READ HEAD OUTPUT SIGNAL WHEN ONES AND ZEROES ARE MIXED. THE SIGNAL APPEARS MORE COMPLEX BUT THE SAME PRINCIPLE APPLIES. A PEAK, EITHER NEGATIVE OR POSITIVE GOING, RE-PRESENTS A ONE BIT OR A CLOCK BIT. AGAIN THE DIGITAL READ SIGNAL OUTPUT IS SHOWN TO THE RIGHT OF THE FIGURE.

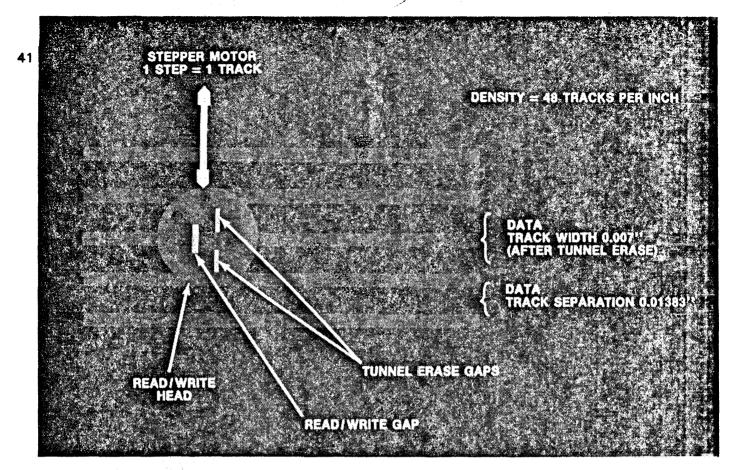

THE B 9489-5 ICMD UNIT CONTAINS A SINGLE GAP READ/WRITE HEAD WHICH STEPS BETWEEN TRACKS UNDER THE CONTROL OF A STEPPER MOTOR. BECAUSE HEAD POSITIONING IS FIXED, THE POSITIONING OF THE HEAD RELATIVE TO THE SPINDLE AND THE CORRECT REGISTRATION OF THE DISKETTE ON THE SPINDLE IS CRITICAL. THE TRACK DENSITY IS 48 TRACKS PER INCH, WITH A TRACK WIDTH OF 0.007 INCH.

TO TRIM THE INTER TRACK SPACE DURING A WRITE OPERATION, THE READ/WRITE HEAD PERFORMS A "TUNNEL ERASE" DURING THE WRITE. THIS ERASES 0.01383 OF AN INCH OF THE MAGNETIC OXIDE ON BOTH SIDES OF THE TRACK, MINIMIZING POSSIBLE NOISE FROM OLD DATA CAUSED BY TOLERANCES IN HEAD ALIGNMENT WITH EACH TRACK.

### B9489 ICMD PERFORMANCE AND CAPABILITIES

Rotates at 360 RPM

Average latency 83 mS

Track to track step time 10 mS

Density 1,836 to 3,268 BPi

Maximum transfer rate 31 K bits per second

Total capacity

Data 242,944 bytes

(73 tracks X 26 sectors X 128 bytes)

All 401.016 bytes

THIS IS A SUMMARY OF THE PERFORMANCE CHARACTERISTICS AND CAPACITIES OF THE ICMD FLEXIBLE DISK DRIVE UNIT. THE DISKETTE IS ROTATED BY THE SPINDLE AT 360 REVOLUTIONS PER MINUTE, GIVING AN AVERAGE LATENCY, THAT IS THE AVERAGE TIME TO REACH A GIVEN ADDRESS ON A TRACK WITHOUT HEAD MOVE-MENT, OF 83 MILLISECONDS. THE TIME TAKEN FOR THE READ/WRITE HEAD TO

STEP BETWEEN TRACKS IS 10 MILLISECONDS PER TRACK.

THE RECORDING DENSITY INCREASES TOWARD THE INNER TRACKS FROM 1,836 BITS PER INCH ON THE OUTER TRACK TO 3,268 BITS PER INCH ON THE INNER TRACK.

DURING A WRITE OR READ OPERATION, DATA IS TRANSFERRED TO OR FROM THE DISKETTE AT A RATE OF 31 KILOBYTES PER SECOND.

42

THE DATA CAPACITY OF THE DISKETTE IS A TOTAL OF 242,944 DATA BYTES, BEING 73 TRACKS OF 26 SECTORS EACH CONTAINING 128 BYTES. THE TOTAL CAPACITY OF THE DISK INCLUDING ALL ADDRESS FIELD, GAP FIELDS AND THE INDEX TRACK IS 401,016 BYTES.

THE SUMMARY OF PERFORMANCE CHARACTERISTICS AND CAPACITIES OF THE UNIT COMPLETES THIS FIRST LECTURE IN THE BURROUGHS B 9489 ICMD TRAINING PROGRAM. RETURN TO YOUR WORKBOOK AND COMPLETE THE PRACTICE FOR THIS SECTION BEFORE CONTINUING.

THIS IS THE SECOND LECTURE IN THE BURROUGHS B 9489 INDUSTRY COMPATABLE MINI DISK (ICMD) TRAINING PROGRAM. THE LECTURE IS DIVIDED INTO TWO SEC-TIONS. THE FIRST SECTION IDENTIFIES THE PHYSICAL LOCATIONS AND FUNCTIONS OF THE MAJOR SUBASSEMBLIES IN THE UNIT. THE SECOND SECTION DESCRIBES THE THEORY OF OPERATION OF THE UNIT.

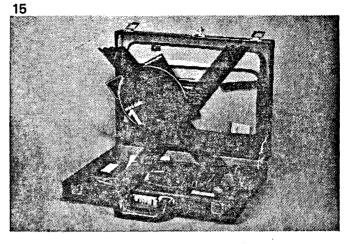

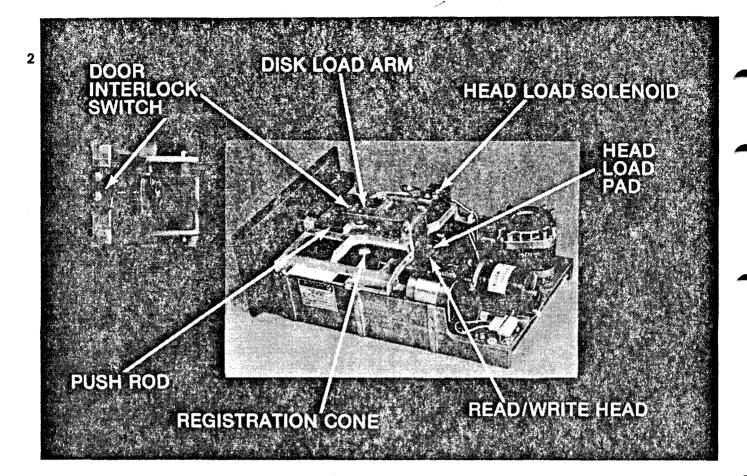

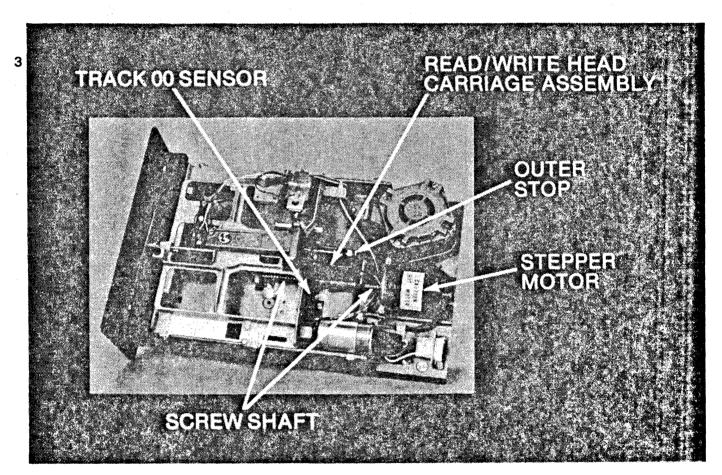

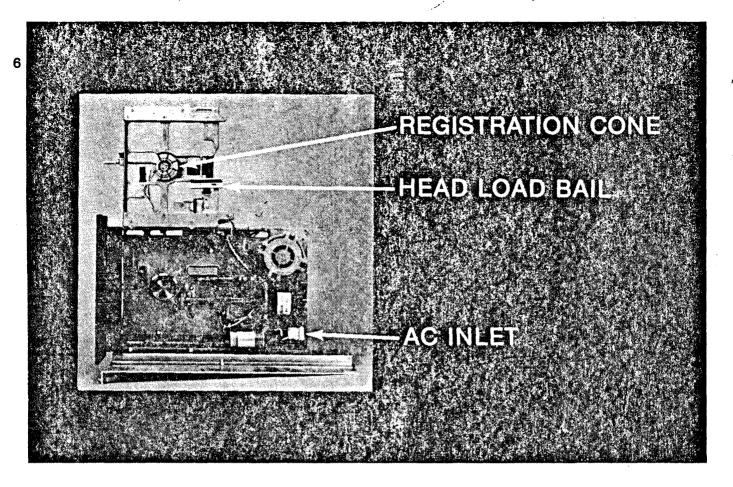

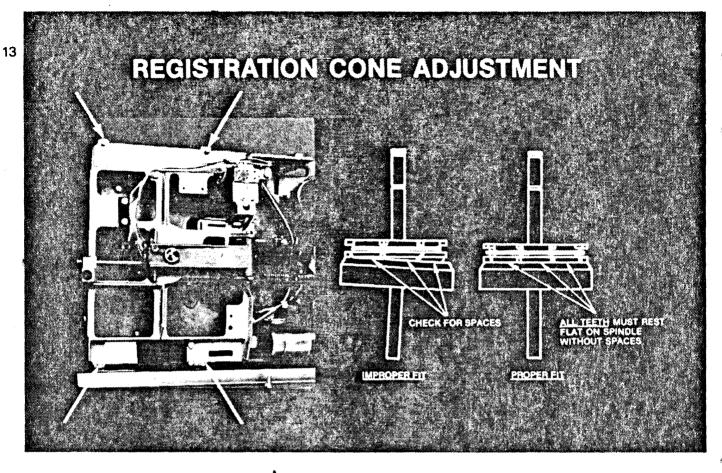

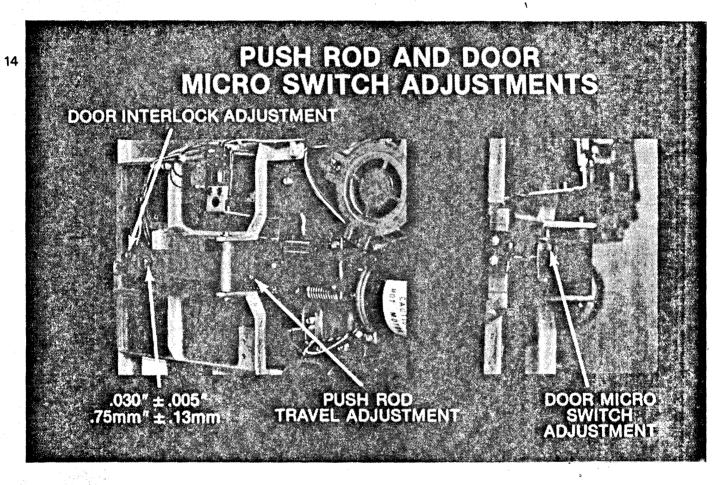

THE PICTURE SHOWS A B 9489-5 UNIT, REMOVED FROM THE HOST SYSTEM AND IDEN-TIFIES SOME OF THE MAJOR SUBASSEMBLIES. CLOSING THE DOOR MOVES THE PUSHROD WHICH ENGAGES THE DISK LOAD ARM. THE DISK LOAD ARM MOVES THE REGISTRATION CONE TO CLAMP THE DISKETTE TO THE SPINDLE.

THE REGISTRATION CONE IS NOT CLEARLY VISIBLE IN THIS PICTURE BUT IS SHOWN LATER WITH THE UNIT PARTIALLY DISASSEMBLED.

THE DISK LOAD ARM ALSO ACTIVATES THE DOOR INTERLOCK SWITCH. CLOSING THE DOOR INTERLOCK SWITCH ENABLES THE HOST SYSTEM CONTROLLER TO LOAD THE READ/WRITE HEAD BY ENERGIZING THE HEAD LOAD SOLENOID. WHEN THE HEAD LOAD SOLENOID IS ENERGIZED, THE HEAD LOAD BAIL MOVES FORWARD ALLOWING THE SPRING LOADED HEAD LOAD PAD TO CONTACT THE BACK SURFACE OF THE DISKETTE. THE PRESSURE FROM THIS PAD MAINTAINS CLOSE CONTACT BETWEEN THE READ/WRITE HEAD AND THE MAGNETIC OXIDE SURFACE OF THE FLEXIBLE DISKETTE.

THE READ/WRITE HEAD IS MOUNTED ON THE CARRIAGE ASSEMBLY WHICH IS MOVED BETWEEN TRACKS BY THE STEPPER MOTOR THROUGH THE SCREW SHAFT. CARRIAGE MOVEMENT ON THE SHAFT IS LIMITED BY THE INNER STOP AND THE OUTER STOP. EACH STEP OF THE STEPPER MOTOR ROTATES THE SCREW SHAFT THROUGH 15 DEGREES WHICH MOVES THE HEAD BY ONE TRACK.

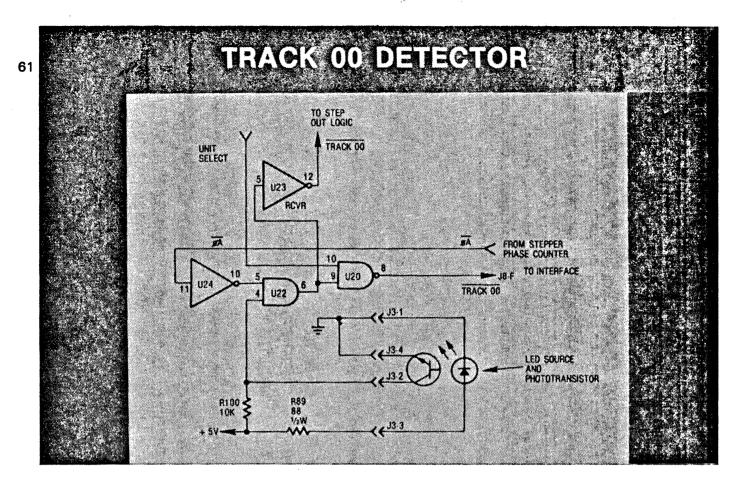

#### THE TRACK 00 SENSOR IS AN OPTICAL SENSOR WHICH DETERMINES WHETHER THE

READ/WRITE HEAD IS POSITIONED TO TRACK 00.

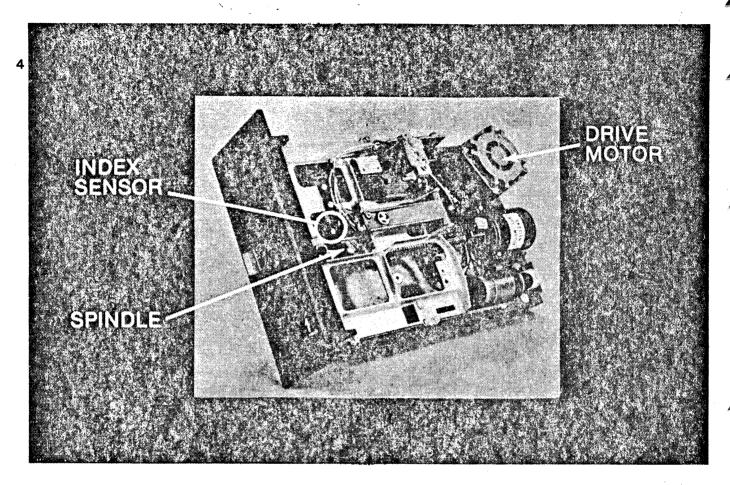

THE DISK DRIVE MOTOR IS CONNECTED TO THE SPINDLE BY A BELT AND PULLEY WHICH ARE GEARED TO ROTATE THE SPINDLE AT 360 RPM. THE OPTICAL INDEX SENSOR SENSES THE INDEX HOLE IN THE DISK TO PROVIDE THE TIMING REFER-ENCE SIGNAL "INDEX".

L2-4

REMEMBER THAT THE INDEX HOLE DETERMINES THE POINT IN THE CIRCUMFER-ENCE OF THE DISKETTE THAT EACH TRACK STARTS. NOTICE THAT BECAUSE THE OPTICAL INDEX SENSOR IS ON THE OPPOSITE SIDE OF THE SPINDLE TO THE READ/ WRITE HEAD, THE INDEX HOLE IS PHYSICALLY 180 DEGREES AROUND THE SURFACE OF THE DISKETTE FROM THE START OF EACH TRACK. THIS IS ALSO THE POINT DURING THE ROTATION OF THE DISKETTE AT WHICH THE READ/WRITE HEAD IS LOADED.

THE AC POWER INLET IS SHOWN TO THE BOTTOM RIGHT. THIS INLET CONNECTS AN EXTERNAL 120V AC SUPPLY TO THE DISK DRIVE MOTOR.

THE DISK LOAD ARM CASTING IS DISASSEMBLED FROM THE UNIT IN THIS ILLUS-TRATION TO SHOW THE REGISTRATION CONE WHICH CENTERS AND CLAMPS THE DISKETTE TO THE SPINDLE. ALSO VISIBLE IS THE HEAD LOAD BAIL WHICH HELPS TO KEEP THE DISK FLAT AS WELL AS ENGAGING AND DISENGAGING THE HEAD LOAD PAD.

L2-6

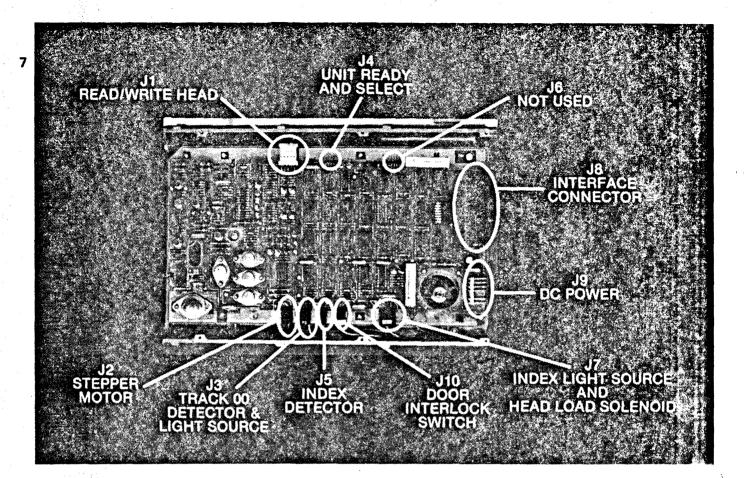

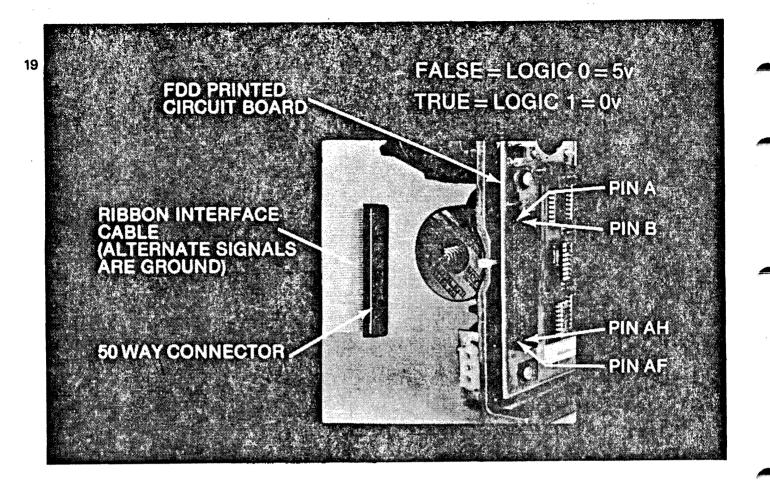

A VIEW OF THE OTHER SIDE OF THE UNIT SHOWS THE LOGIC PRINTED CIRCUIT BOARD. THE LOGIC BOARD MAY BE INTERFACED DIRECTLY TO THE HOST SYSTEM, THROUGH THE OPTIONAL LINE DRIVER/RECEIVER OR THROUGH THE OPTIONAL ADAPTOR CARD.

THE INTERFACE IS VIA A 50 WAY CONNECTOR, J8. THE CONNECTOR BELOW J8, J9 CONNECTS THE UNIT TO THE HOST SYSTEM OR OPTIONAL INTERNAL UNIT DC POWER SUPPLY.

MOVING CLOCKWISE AROUND THE PCB, J7 CONNECTS TO THE DIODE LIGHT SOURCE FOR THE OPTICAL INDEX HOLE DETECTOR AND THE HEAD LOAD SOLENOID. J10 CONNECTS WITH THE DOOR INTERLOCK SWITCH. J5 CONNECTS THE OPTICAL INDEX HOLE DETECTOR TO THE LOGIC. J3 CONNECTS THE OPTICAL TRACK 00 DIODE LIGHT SOURCE AND DETECTOR TO THE LOGIC.

J2 CONNECTS THE STEPPER MOTOR TO THE STEPPER MOTOR DRIVER CIRCUITRY ON THE LOGIC PCB. J1 IS CONNECTED TO THE READ/WRITE HEAD. THE OPTIONAL UNIT READY AND SELECT INDICATORS CONNECT TO J4. J6 IS NOT USED.

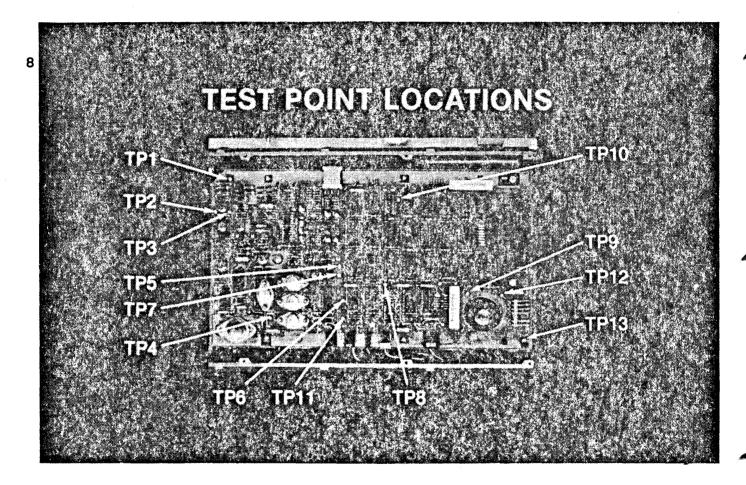

THIRTEEN TEST POINTS ARE PROVIDED ON THE PCB FOR TEST AND MAINTENANCE PURPOSES. LIKE MOST OTHER COMPONENTS, THEIR REFERENCE IDENTIFICATION IS PRINTED BESIDE THEM ON THE PCB. A DIAGRAM SHOWING THE LOCATION OF EACH OF THESE TEST POINTS CAN BE FOUND IN THE TECHNICAL MANUAL.

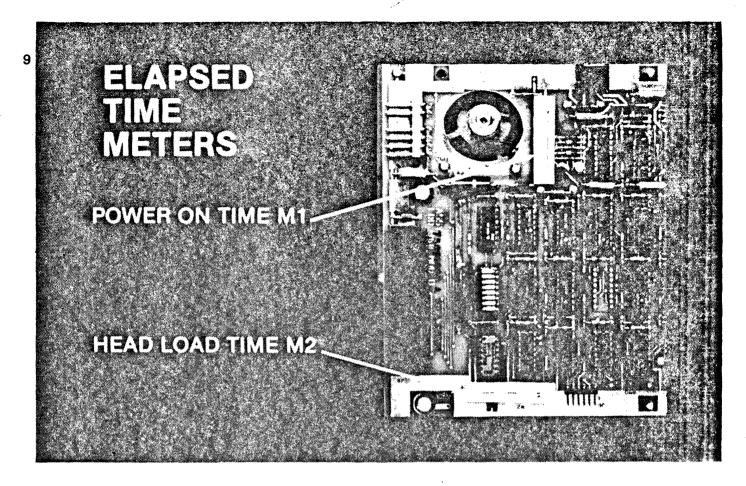

THE UNIT IS EQUIPPED WITH TWO ELAPSED TIME METERS. THE ELAPSED TIME METERS ARE OF THE MERCURY MIGRATION TYPE. M1, RECORDS THE TOTAL POWER ON HOURS FOR THE UNIT. M2, RECORDS THE NUMBER OF HOURS THE READ/WRITE HEAD HAS BEEN LOADED. THIS INFORMATION IS USED TO DETERMINE PREVEN-TATIVE MAINTENANCE REQUIREMENTS WHICH ARE DESCRIBED LATER.

STOP AT THIS POINT AND RETURN TO YOUR WORKBOOK. COMPLETE THE PRACTICE FOR THIS SECTION BEFORE CONTINUING.

A CLEAR COMPREHENSION OF THE FUNCTION AND OPERATION OF EACH CIRCUIT IN THE RELATIVELY SIMPLE LOGIC OF THE B 9489-5 UNIT WILL BE OF CONSIDER-ABLE ASSISTANCE WHEN USING THE MTR GUIDED PROCEDURES LATER AND SHOULD ENABLE YOU TO REDUCE THE NUMBER OF SUSPECTS FOR ANY GIVEN FAULT DIAG-NOSIS.

THIS SECTION OF THE LECTURE DETAILS THE THEORY OF OPERATION OF THE B 9489 UNIT. THE FIRST PART INTRODUCES A BLOCK DIAGRAM OF THE LOGIC TO GIVE AN OVERALL DESCRIPTION OF THE UNIT BEFORE A MORE DETAILED FUNCTIONAL DESCRIPTION OF EACH SECTION.

## B9489 ICMD UNIT LOGIC FUNCTIONS

Receive and respond to controller commands

Generate control signals for drive status

Position Read/Write head to selected track

Read and write serial data

YOU ALREADY HAVE A GOOD APPRECIATION OF THE BASIC OPERATING FUNCTIONS AND CAPABILITIES OF THE B 9489-5 UNIT.

THE FUNCTIONS OF THE UNIT CAN BE SUMMARIZED INTO FOUR BASIC AREAS:

- FIRST, TO RECEIVE COMMAND SIGNALS FROM THE CONTROLLER AND RESPOND TO THE COMMANDS.

- SECOND, TO GENERATE CONTROL SIGNALS FOR USE BY BOTH THE DRIVE AND THE CONTROLLER TO DETERMINE THE STATUS OF THE DRIVE.

- THIRD, TO POSITION THE READ/WRITE HEAD TO THE SELECTED TRACK.

- AND FOURTH, TO READ OR WRITE DATA IN SERIAL BIT FORM FROM OR TO THE CONTROLLER.

ALL OPERATIONS OF THE UNIT ARE DEPENDENT UPON COMMANDS RECEIVED FROM THE CONTROLLER.

L2-12

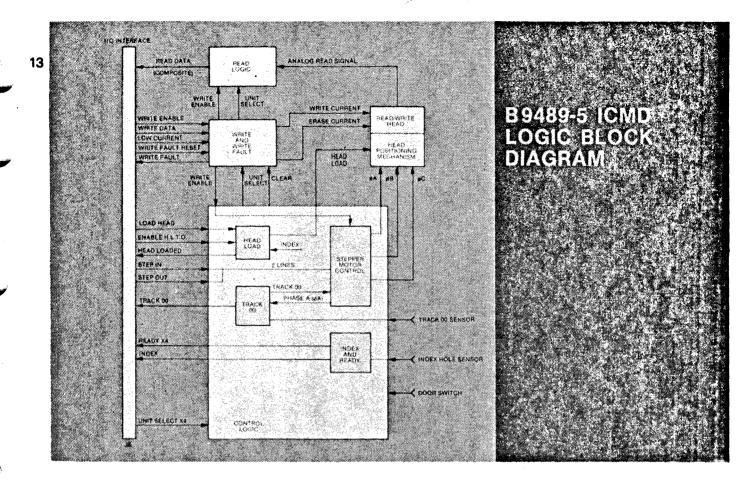

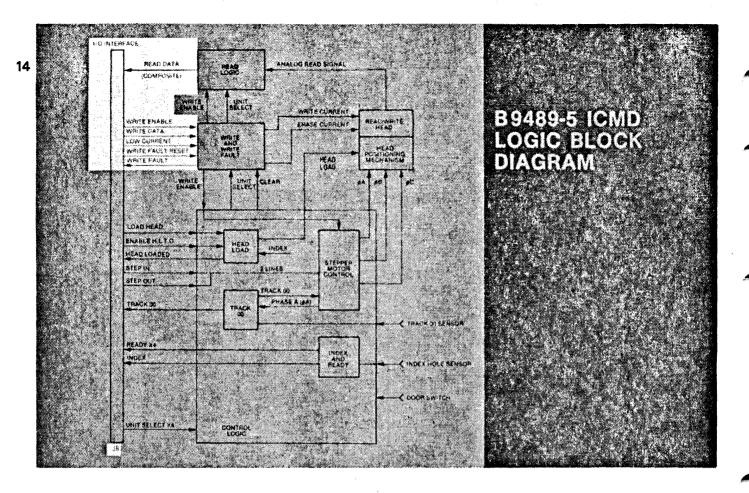

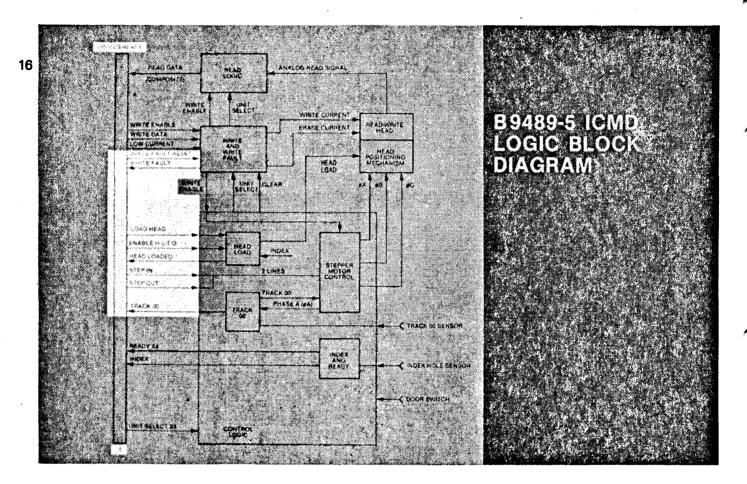

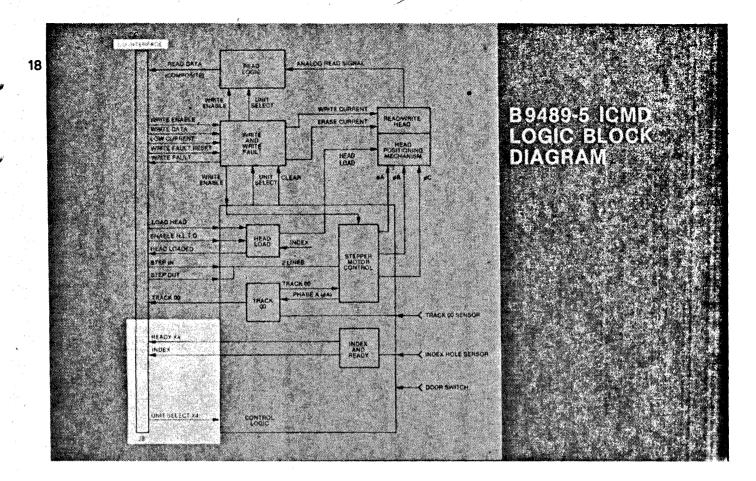

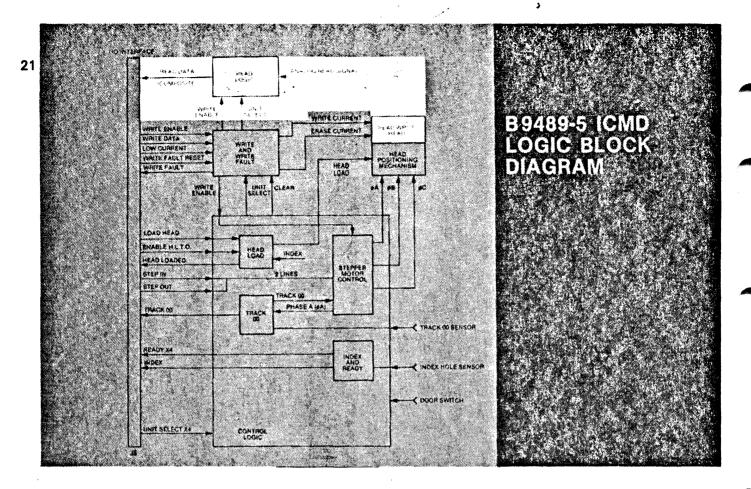

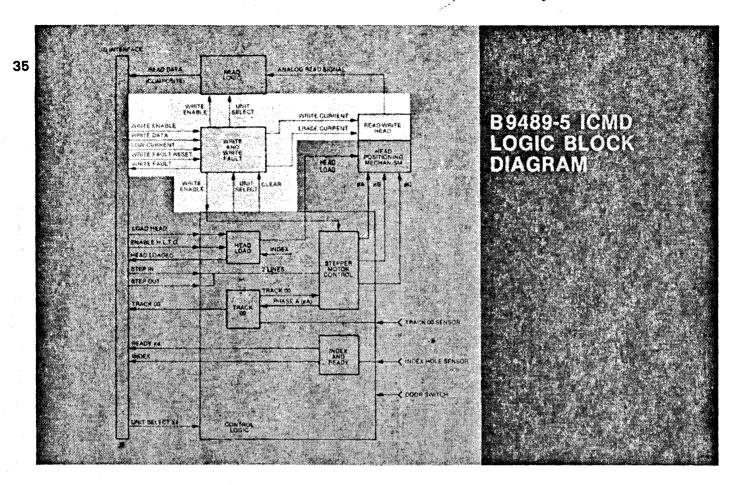

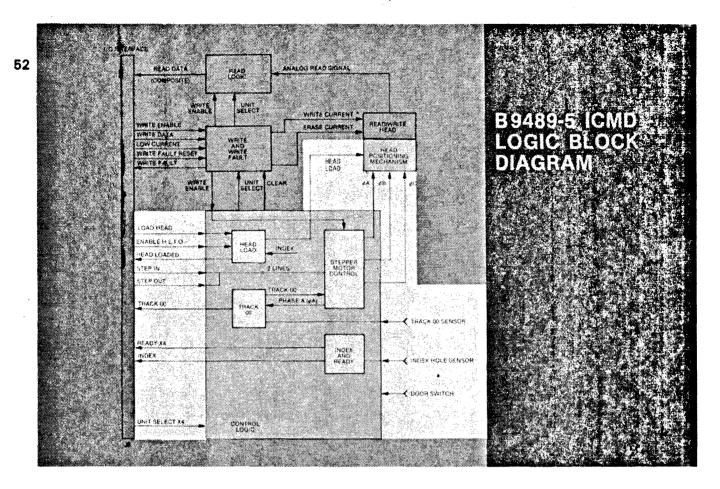

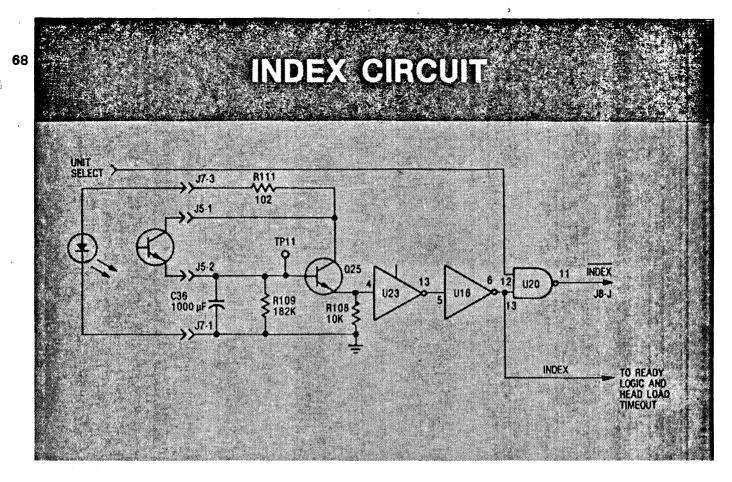

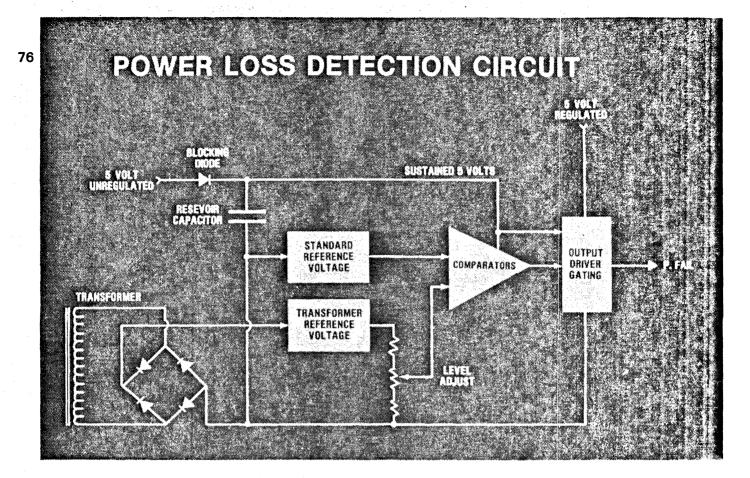

THIS DIAGRAM REPRESENTS THE COMPLETE LOGIC OF THE UNIT, DIVIDED INTO FIVE MAIN SECTIONS; THE I/O INTERFACE, THE READ LOGIC, THE WRITE AND WRITE FAULT LOGIC, THE HEAD POSITIONING MECHANISM WITH THE READ/WRITE HEAD ITSELF AND FINALLY THE CONTROL LOGIC, INCLUDING THE HEAD LOAD, TRACK 00, STEPPER MOTOR CONTROL AND INDEX AND READY LOGIC.

L2—13

THE SIGNAL INTERFACE WITH THE HOST SYSTEM CONTROLLER OR POSSIBLY THE OPTIONAL ADAPTOR FOR MEDIUM AND LARGE SYSTEMS, IS VIA THE 50 WAY CON-NECTOR, J8.

EXPLAINING EACH SIGNAL IN TURN, READ DATA IS THE DIGITAL SIGNAL FROM THE UNIT, CONSISTING OF THE COMPOSITE CLOCK AND DATA BITS READ FROM THE DISKETTE.

WRITE ENABLE, AS THE NAME IMPLIES, ENABLES THE WRITE LOGIC AND DISABLES THE READ LOGIC WHEN THE SIGNAL IS AT A LOGIC 1 LEVEL.

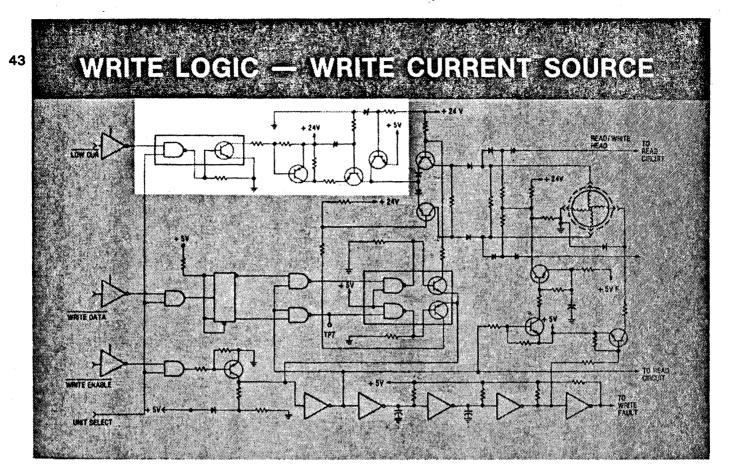

WRITE DATA RECEIVES THE COMPOSITE CLOCK AND DATA FROM THE CONTROLLER WHICH ARE TO BE WRITTEN TO THE DISKETTE. LOW CURRENT IS A SIGNAL FROM THE CONTROLLER WHICH REDUCES THE CURRENT TO THE WRITE HEAD WHEN THE WRITE IS TAKING PLACE ON A TRACK ABOVE TRACK 43. THE LOWER WRITE CURRENT IS REQUIRED ABOVE TRACK 43 BECAUSE OF THE EFFECTS OF THE INCREASED PACKING DENSITY ON THE TRACKS TOWARDS THE CENTER OF THE DISKETTE.

THE WRITE FAULT SIGNAL INDICATES A WRITE FAULT CONDITION TO THE CON-TROLLER.

INDICATES:

15

A write enable issued when head is not loaded

Write data sent at wrong clock rate

Write command issued but no data received in 450 µS

Does not indicate write data error

A WRITE FAULT INDICATES ONE OR MORE OF THESE CONDITIONS; A WRITE ENABLE IS ISSUED WHEN THE HEAD IS NOT LOADED, WRITE DATA ARE SENT AT THE WRONG CLOCK RATE OR A WRITE IS ISSUED AND DATA ARE NOT RECEIVED WITHIN A 450 MICROSECOND TIME PERIOD. BECAUSE THE READ/WRITE HEAD IS A SINGLE GAP HEAD, THE DATA WRITTEN TO THE DISKETTE CANNOT BE CHECKED DURING A WRITE OPERATION. DATA CAN ONLY BE CHECKED BY THE HOST SYSTEM PERFORMING A READ IMMEDIATELY AFTER THE WRITE AND COMPARING DATA.

THE SIGNAL WRITE FAULT RESET CLEARS THE WRITE FAULT LATCH IN THE WRITE FAULT LOGIC.

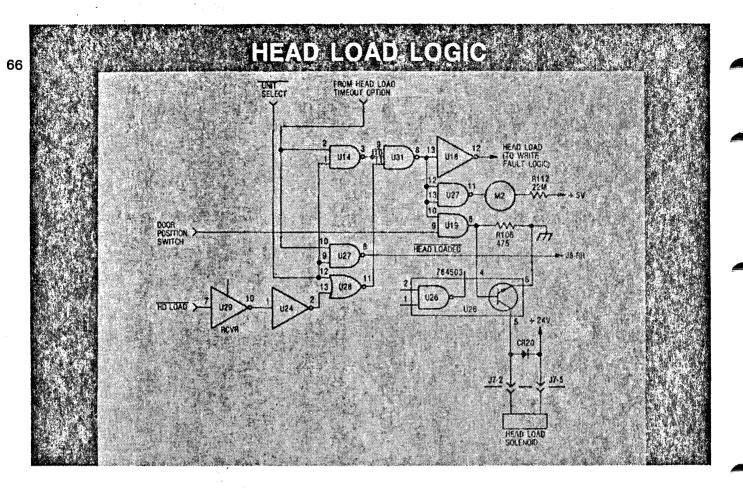

LOAD HEAD IS A COMMAND FROM THE CONTROLLER WHICH CAUSES THE HEAD LOAD SOLENOID TO ENERGIZE. LOAD HEAD IS A LOGIC 1 LEVEL WHICH MUST BE INITIATED 60 MILLISECONDS BEFORE INITIATING A READ OR WRITE OPERATION TO ALLOW FOR HEAD LOAD SETTLING TIME. TO ENSURE INCREASED HEAD AND DISKETTE LIFE THIS SIGNAL SHOULD BE AT A LOGIC ZERO WHENEVER A DATA TRANSFER OPERATION IS NOT IN PROCESS OR PENDING.

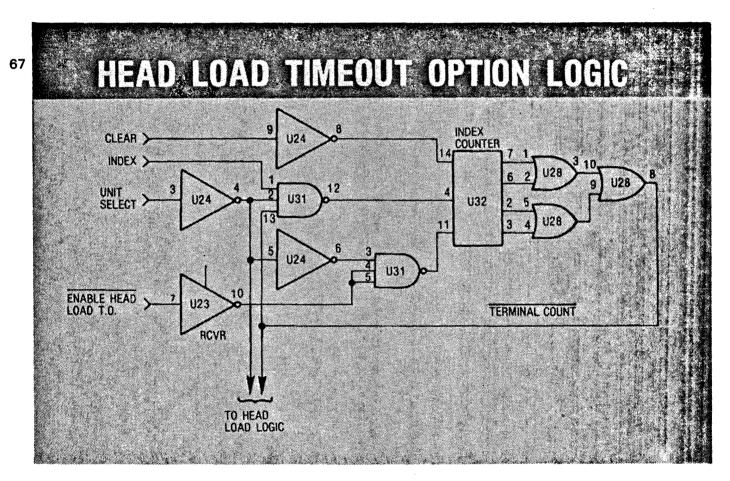

ENABLE HEAD LOAD TIME OUT, (HLTO), IS USED ON UNITS WITH THE HEAD LOAD TIME-OUT OPTION. THIS OPTION USES A TIME-OUT COUNTER WITHIN THE DRIVE TO KEEP THE READ/WRITE HEAD LOADED FOR EIGHT INDEX PULSES AFTER THE DRIVE IS DESELECTED.

THE SIGNALS "STEP IN" AND "STEP OUT" CAUSE THE READ/WRITE HEAD TO STEP IN OR OUT BY ONE TRACK.

TRACK 00 IS AN OUTPUT SIGNAL TO THE CONTROLLER TO INDICATE THAT THE READ/WRITE HEAD CARRIAGE ASSEMBLY IS POSITIONED OVER TRACK 00.

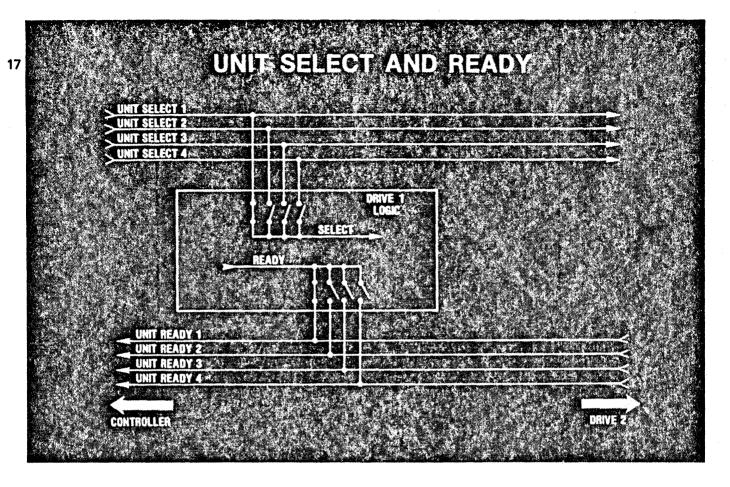

THE B 9489-5 UNIT IS DESIGNED SO THAT A MAXIMUM OF FOUR UNITS COULD BE CONNECTED TO A SINGLE CONTROLLER. ALTHOUGH PRESENTLY A MAXIMUM OF TWO DRIVES ARE USED, THE UNIT INTERFACES TO FOUR SELECT SIGNALS AND FOUR READY SIGNALS. EACH UNIT IS ASSIGNED A CORRESPONDING DRIVE NUMBER BETWEEN ONE AND FOUR. ONCE THIS NUMBER IS ASSIGNED, THE CONTROL LOGIC IS CONNECTED TO THE ASSIGNED UNIT "SELECT" AND "READY" SIGNALS USING SWITCHES MOUNTED IN A DUAL IN LINE PACKAGE ON THE LOGIC PCB.

THE UNIT SELECT SIGNAL ENABLES ALL CONTROL AND STATUS COMMUNICATION, EXCEPT READ STATUS BETWEEN DRIVE 1 AND THE HOST SYSTEM CONTROLLER. A LOGIC 1 ON THE ASSIGNED SELECT LINE SELECTS THE DRIVE, A LOGIC 0 DE-COUPLES THE DRIVE FROM THE CONTROLLER.

THE UNIT READY SIGNAL INDICATES THAT THE DISKETTE IS CORRECTLY INSERTED, THE DOOR IS CLOSED AND THE DISKETTE IS UP-TO-SPEED.

THE INDEX SIGNAL, AS PREVIOUSLY MENTIONED IS A TIMING SIGNAL TO THE HOST SYSTEM CONTROLLER INDICATING THE RELATIVE POSITION OF THE DISKETTE FROM THE OPTICAL SENSOR ONCE PER DISKETTE REVOLUTION.

THE REMAINING SIGNALS IN THE FIFTY WAY INTERFACE ARE GROUND SIGNALS WHICH ARE USED IN THE FLAT INTERFACE CABLE TO PROVIDE ISOLATION BETWEEN ACTIVE SIGNAL PATHS.

THE CONVENTION USED ON THE INTERFACE FOR THE UNIT IS THAT A FALSE OR LOGIC 0 IS REPRESENTED BY A 5V SIGNAL LEVEL. A TRUE OR LOGIC 1 IS REPRESENT-ED BY A 0V SIGNAL LEVEL.

STOP THE LECTURE AT THIS POINT AND RETURN TO YOUR WORKBOOK, COMPLETE THE PRACTICE FOR THIS SECTION BEFORE CONTINUING.

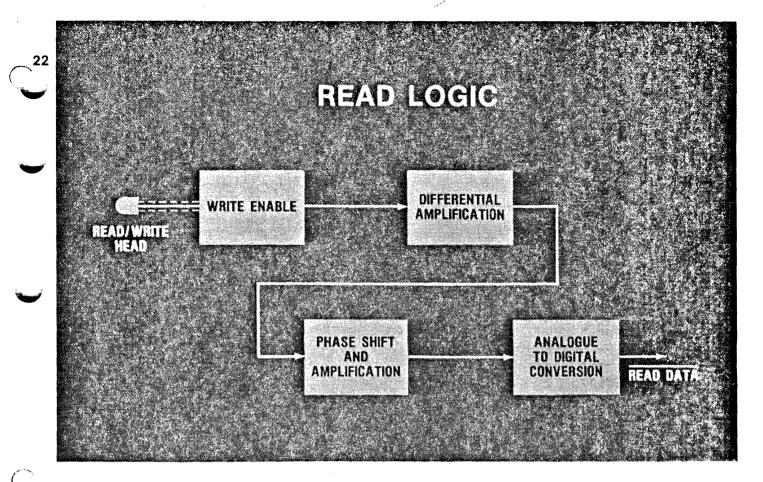

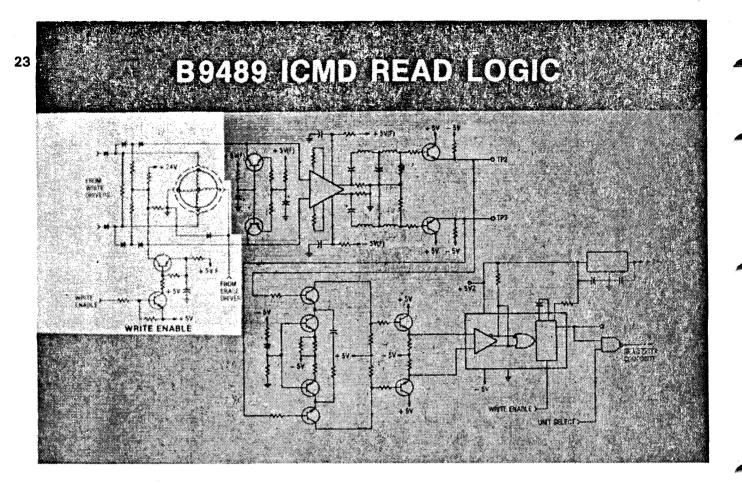

THE NEXT FUNCTIONAL BLOCK IN THE ICMD UNIT TO BE EXAMINED IS THE READ LOGIC. THE READ LOGIC TAKES THE ANALOGUE OUTPUT SIGNAL FROM THE READ HEAD AND CONVERTS IT INTO THE DIGITAL SIGNAL REQUIRED BY THE HOST SYS-TEM CONTROLLER.

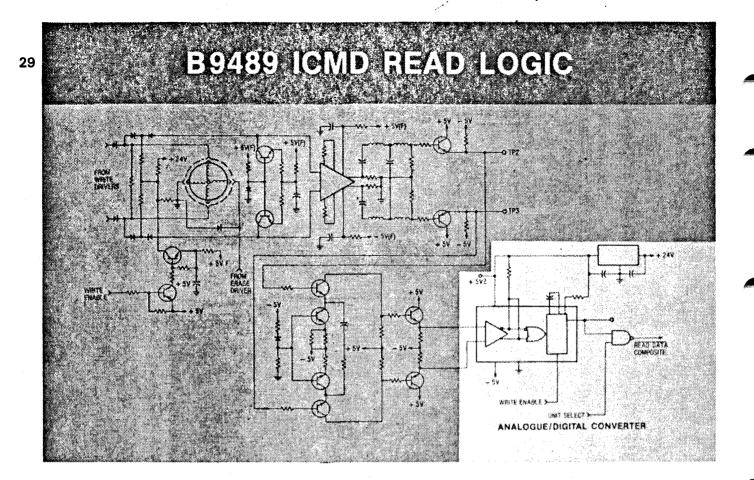

THE READ LOGIC CONSISTS OF FOUR MAIN FUNCTIONAL BLOCKS, WRITE ENABLE; DIFFERENTIAL AMPLIFICATION; PHASE SHIFT AND AMPLIFICATION; AND ANALOGUE TO DIGITAL CONVERSION. WE WILL HIGHLIGHT AND DESCRIBE EACH OF THESE FOUR FUNCTIONAL BLOCKS TO EXPLAIN THE OPERATION OF THE READ LOGIC IN DETAIL.

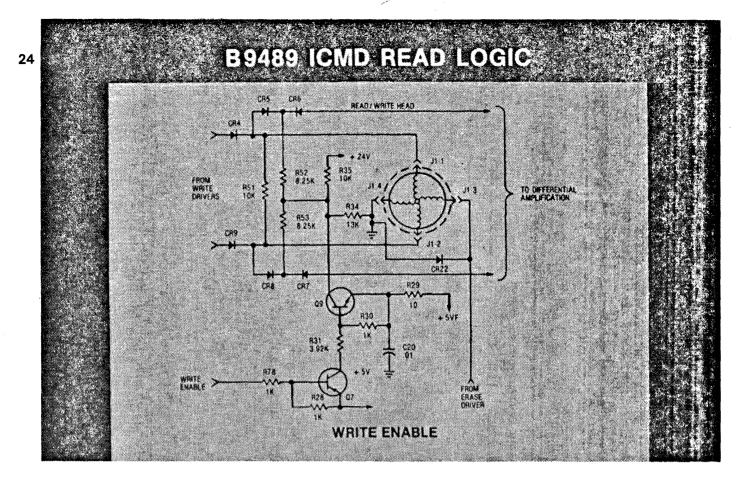

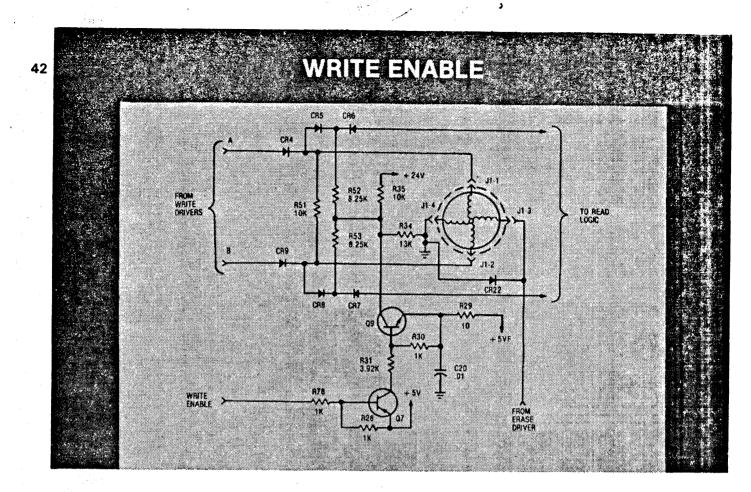

THIS DRAWING SHOWS THE COMPLETE READ LOGIC CIRCUIT. THE FUNCTIONAL BLOCK HIGHLIGHTED IN THIS DIAGRAM IS THE WRITE ENABLE CIRCUITRY. THE WRITE ENABLE CIRCUITRY DETERMINES WHETHER THE READ/WRITE HEAD IS WRITE ENABLED. IF THE READ/WRITE HEAD IS NOT WRITE ENABLED, THEN BY DEFAULT IT IS READ ENABLED.

THE DETAIL IS CLARIFIED BY ENLARGING THE FUNCTIONAL BLOCK. THE SIGNAL SHOWN AT THE BOTTOM LEFT OF THE DRAWING IS WRITE ENABLE, DERIVED FROM THE INTERFACE SIGNAL. WRITE ENABLE IS A LOGICAL 1, THAT IS 5 VOLTS OR HIGH, TO ENABLE THE WRITE DRIVERS. WHEN WRITE ENABLE IS A LOGICAL 0, THAT IS 0 VOLTS OR LOW, THE WRITE DRIVERS ARE DISABLED AND CONSEQUENTLY THE READ LOGIC IS ENABLED.

WHEN WRITE ENABLE IS LOW, THE BLOCKING DIODES CR5 AND CR8 ARE FORWARD BIASED THROUGH THE ACTION OF Q7 AND Q9. THIS ALLOWS THE ANALOGUE SIGNAL FROM THE READ/WRITE HEAD TO PASS TO THE NEXT STAGE IN THE READ LOGIC, DIFFERENTIAL AMPLIFICATION.

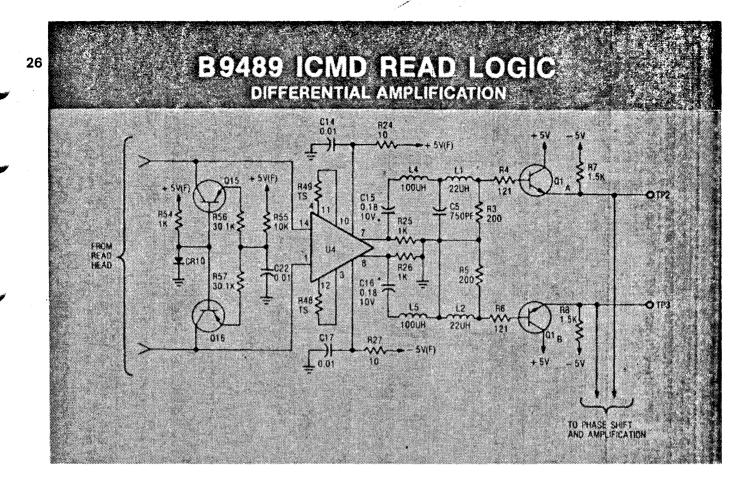

THE DIFFERENTIAL AMPLIFICATION CIRCUIT AMPLIFIES THE DIFFERENCE BETWEEN THE TWO 180 DEGREE OUT-OF-PHASE READ DATA SIGNALS OUTPUT FROM THE READ HEAD.

THE DIFFERENTIAL AMPLIFIER IS A MULTI-STAGE CIRCUIT THAT CONSISTS OF A DIFFERENTIAL VIDEO AMPLIFIER U4 AND THE DUAL PACKAGED TRANSISTORS Q1A AND Q1B. THE GAIN OF THE AMPLIFIER IS PRESET BY THE VALUE OF THE RE-SISTORS R49 AND R48. NOTICE THAT THE VALUE OF THESE RESISTORS IS INDICAT-ED BY THE LETTERS "TS." TS MEANS THE VALUES ARE TEST SELECTED. DETAILED PROCEDURES FOR ESTABLISHING THE CORRECT VALUES FOR THESE COMPONENTS, IN CASE REPLACEMENT IS NECESSARY, ARE DESCRIBED IN A LATER LECTURE.

TWO TEST POINTS, TP2 AND TP3, ARE PROVIDED SO THAT THE SIGNAL OUTPUT FROM A1A AND Q1B CAN BE MEASURED FOR TEST PURPOSES.

THE OUTPUT FROM THE DIFFERENTIAL AMPLIFIER CIRCUIT IS THEN INPUT TO THE NEXT STAGE IN THE READ LOGIC, THE PHASE SHIFT AND AMPLIFICATION CIRCUIT.

THE PHASE SHIFT AND AMPLIFICATION CIRCUIT, PHASE SHIFTS ONE OF THE SIGNALS FROM THE DIFFERENTIAL AMPLIFICATION CIRCUIT BY 90 DEGREES RELATIVE TO THE OTHER ONE.

THIS PHASE SHIFT, TOGETHER WITH A FURTHER STAGE OF AMPLIFICATION, IS THE FIRST STAGE IN THE CONVERSION FROM THE ANALOGUE SIGNAL, READ FROM THE DISKETTE, TO THE DIGITAL SIGNAL REQUIRED BY THE HOST SYSTEM CONTROLLER.

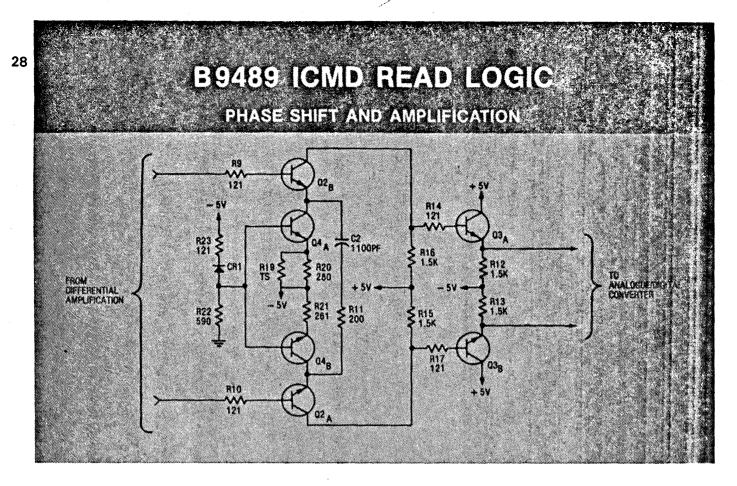

THE PHASE SHIFT CIRCUIT IS COMPRISED OF THE DUAL PACKAGED TRANSISTORS 02A AND 02B TOGETHER WITH THE RESISTANCE/CAPACITANCE NETWORK OF C2 AND R11, TO PHASE SHIFT THE TWO ANALOGUE READ SIGNALS, SO THAT THEY ARE 90 DEGREES OUT-OF-PHASE.

TRANSISTORS Q4A AND Q4B ARE THE CURRENT SOURCES FOR Q2A AND Q2B. THE RESISTOR R19 IS ANOTHER TEST SELECTED VALUE RESISTOR. R19 IS SELECTED TO CONTROL THE DC BALANCE OF THE TWO 90 DEGREE PHASE SHIFTED SIGNALS BEFORE THEY ARE APPLIED TO THE NEXT STAGE IN THE READ LOGIC CIRCUITRY. ADDITIONAL AMPLIFICATION OF THESE SIGNALS IS PROVIDED BY TRANSISTORS Q3A AND Q3B. THE NEXT STAGE IS ANALOGUE TO DIGITAL CONVERSION.

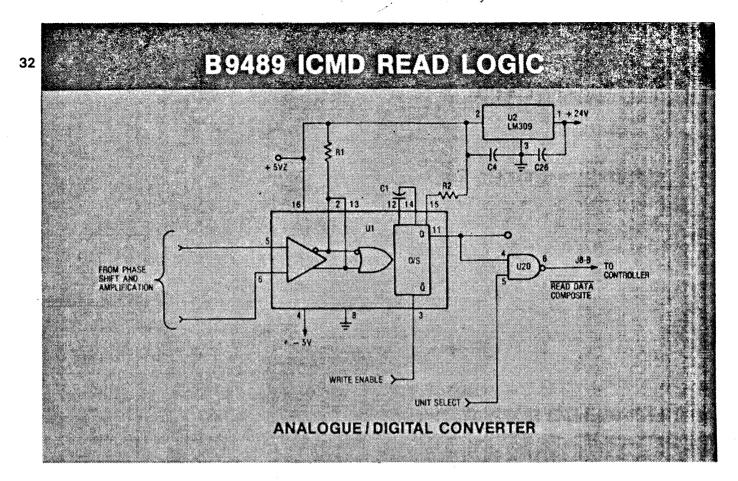

ANALOGUE TO DIGITAL CONVERSION IS THE FINAL STAGE IN THE READ LOGIC BEFORE THE RESULTING SERIAL DATA CAN BE TRANSFERRED TO THE HOST SYSTEM CONTROLLER. THE ANALOGUE TO DIGITAL CONVERTER USES THE TWO 90 DEGREE OUT-OF-PHASE SIGNALS TO PRODUCE A COMPOSITE READ DATA SIGNAL CONTAIN-ING THE SERIAL CLOCK AND DATA PULSES AT NORMAL LOGIC LEVELS.

3

BEFORE EXAMINING THE CIRCUIT OF THE DIGITAL TO ANALOGUE CONVERTER IN DETAIL, LET US LOOK MORE CLOSELY AT TWO SIGNALS INPUT TO THE FIRST STAGE OF THE ANALOGUE TO DIGITAL CONVERTER.

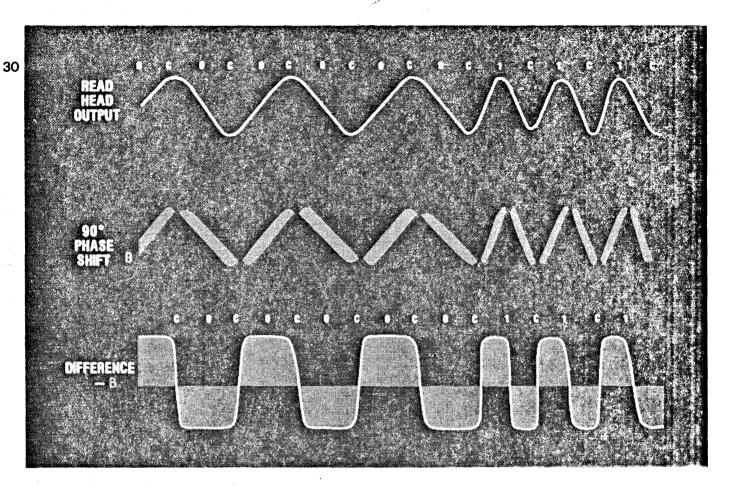

THE UPPER PART OF THE DIAGRAM SHOWS A TYPICAL READ HEAD OUTPUT SIGNAL "A", WITH THE 90 DEGREE PHASE SHIFTED SIGNAL "B".

WHEN THESE TWO SIGNALS ARE SUPERIMPOSED AS SHOWN IN THE CENTER OF THE DIAGRAM, THE DIFFERENCE BETWEEN THE TWO AREAS CAN BE CLEARLY SEEN. INITIALLY, "A" IS MORE POSITIVE THAN "B", THEN "B" BECOMES MORE POSITIVE THAN "A" AND SO ON. THE LOWER PART OF THE DIAGRAM REPRESENTS THE DIFFERENCE SIGNAL WHICH APPROXIMATES TO A SQUARE WAVE. IN THIS SIGNAL, BOTH CLOCK AND ONE BITS ARE REPRESENTED BY TRANSITIONS, EITHER POSITIVE OR NEGATIVE GOING, NOT THE LEVEL. THESE TRANSITIONS CORRESPOND TO THE PEAKS IN THE ORIGINAL READ HEAD OUTPUT SIGNAL.

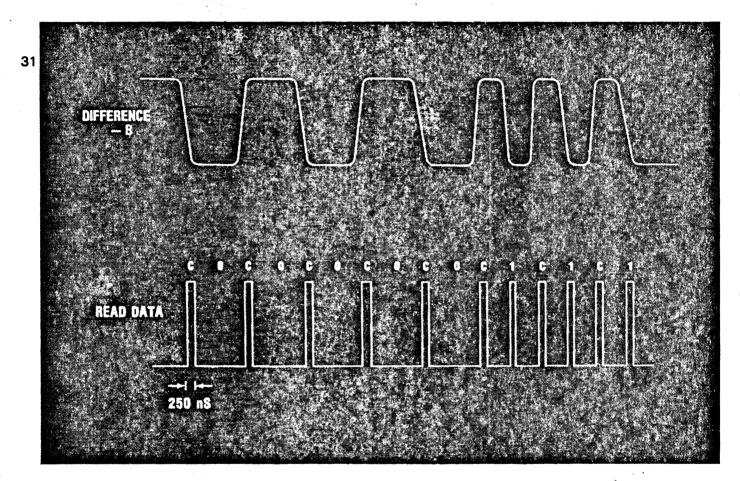

THE DIFFERENCE SIGNAL, IN WHICH BOTH CLOCK AND ONE BITS ARE REPRESENTED BY TRANSITIONS, IS INPUT TO A ONE SHOT MULTIVIBRATOR WHICH IS TRIGGERED TO PRODUCE A POSITIVE OUTPUT PULSE FOR BOTH NEGATIVE AND POSITIVE GOING INPUT PULSES. THESE 250 NANOSECOND OUTPUT PULSES BECOME THE DIGITAL INTERFACE SIGNAL, "READ DATA."

THE ANALOGUE TO DIGITAL CONVERSION IS ACCOMPLISHED BY ONE INTEGRATED CIRCUIT U1, WHICH IS A COMBINATION DIFFERENTIAL VOLTAGE COMPARATOR AND ONE SHOT MULTIVIBRATOR. THE 250 NANOSECOND PULSE DURATION IS DE-TERMINED BY THE TIMING CAPACITOR C1. U2 IS A VOLTAGE REGULATOR PROVID-ING A WELL REGULATED 5 VOLTS FOR U1.

BEFORE THE READ DATA SIGNAL IS OUTPUT TO THE CONTROLLER, IT IS GATED WITH THE SIGNAL UNIT SELECT BY U20. U20 INVERTS THE SIGNAL AND UNIT SELECT PREVENTS ANY ERRONEOUS DATA SIGNALS FROM REACHING THE CONTROLLER WHEN THE UNIT IS NOT SELECTED.

TO SUMMARIZE, THE WRITE ENABLE BLOCK DETERMINES WHETHER THE READ/ WRITE HEAD IS READ OR WRITE ENABLED. THE OUTPUT SIGNAL PASSES THROUGH A DIFFERENTIAL AMPLIFIER. THE AMPLIFIED SIGNALS ARE PHASE SHIFTED TO PRODUCE TWO SIGNALS WITH A PHASE DIFFERENCE OF 90 DEGREES BEFORE BEING CONVERTED TO A DIGITAL SIGNAL, "READ DATA."

STOP THE LECTURE AT THIS POINT AND RETURN TO YOUR WORKBOOK. COMPLETE THE PRACTICE FOR THIS SECTION BEFORE CONTINUING.

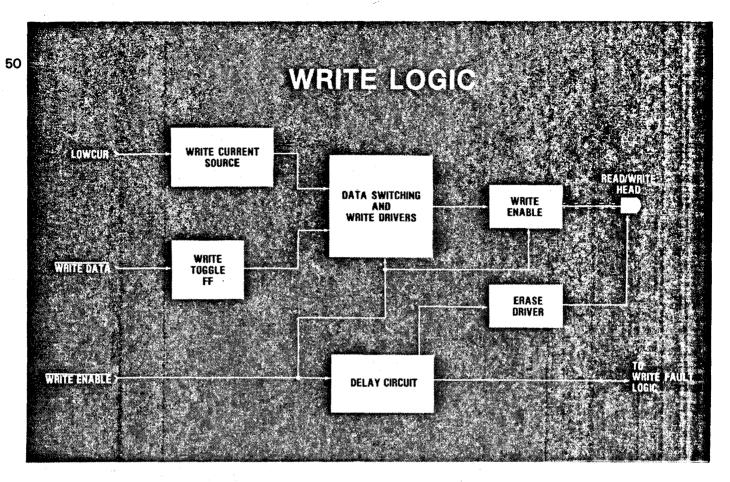

RETURNING TO THE LOGIC BLOCK DIAGRAM OF THE ICMD UNIT, THE NEXT FUNC-TIONAL BLOCK IS THE WRITE AND WRITE FAULT LOGIC.

THE WRITE AND WRITE FAULT LOGIC USES THE SERIAL CLOCK AND DATA SIGNAL "WRITE DATA" FROM THE HOST SYSTEM CONTROLLER TO PRODUCE THE SIGNAL USED TO WRITE TO THE DISKETTE.

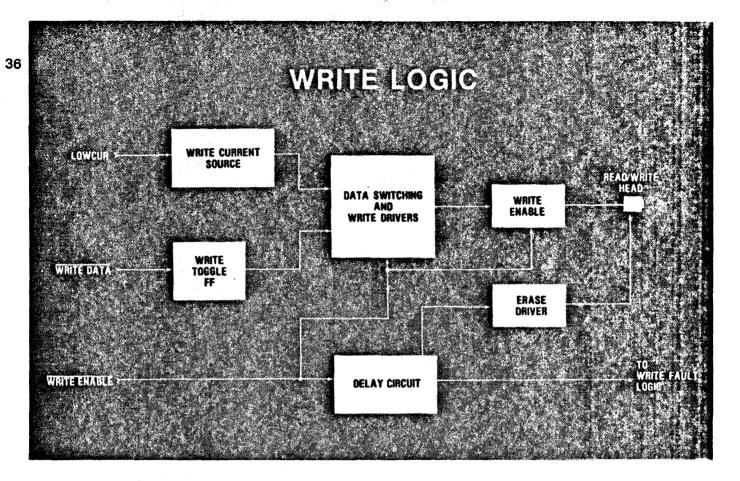

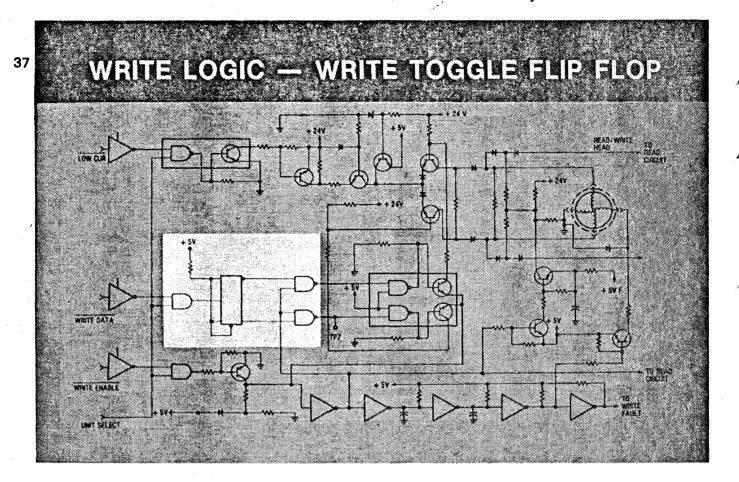

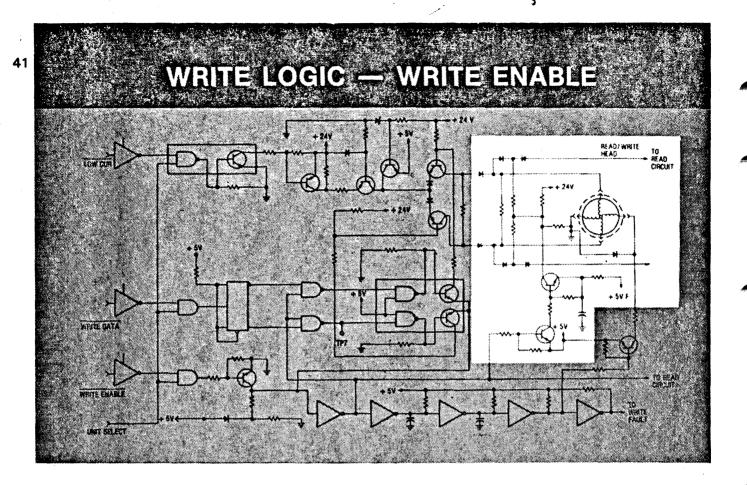

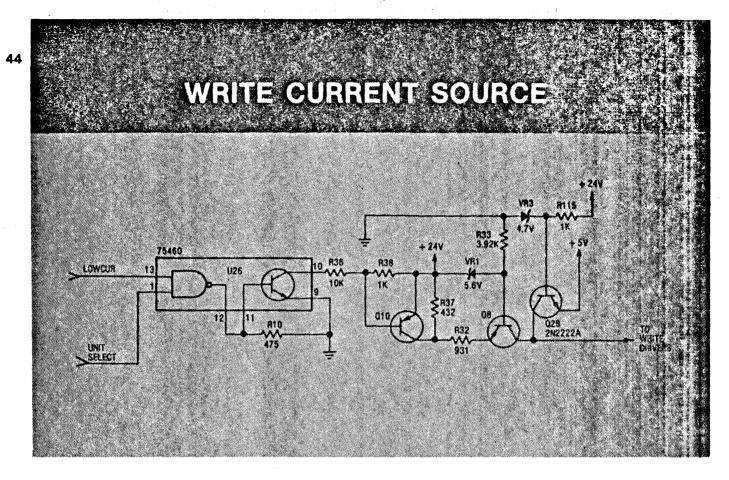

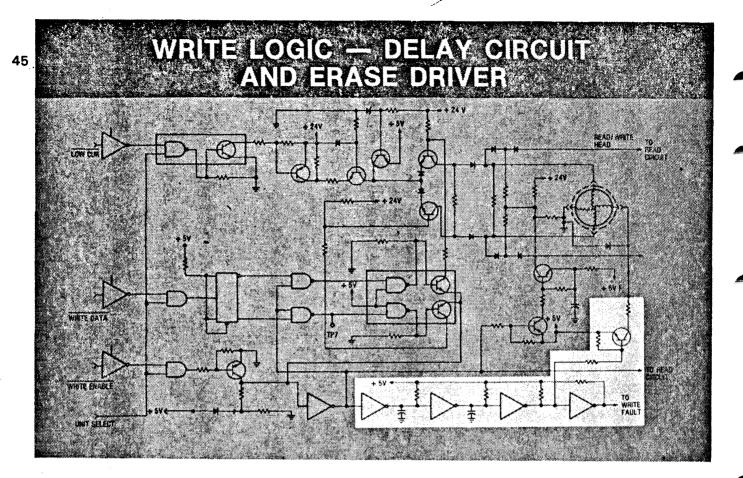

THE WRITE LOGIC CONSISTS OF SIX MAIN FUNCTIONAL AREAS. THESE ARE THE WRITE TOGGLE FLIP FLOP; DATA SWITCHING AND WRITE DRIVERS; THE WRITE CURRENT SOURCE; THE WRITE ENABLE LOGIC; A DELAY CIRCUIT; AND THE ERASE DRIVER.

THE WRITE FAULT LOGIC IS NOT SHOWN IN THIS DIAGRAM, BUT IS EXPLAINED LATER.

AS WITH THE READ LOGIC, EACH BLOCK IN THE DIAGRAM IS RELATED TO THE SCHE-MATIC AND EXPLAINED INDIVIDUALLY, STARTING WITH THE WRITE TOGGLE FLIP FLOP.

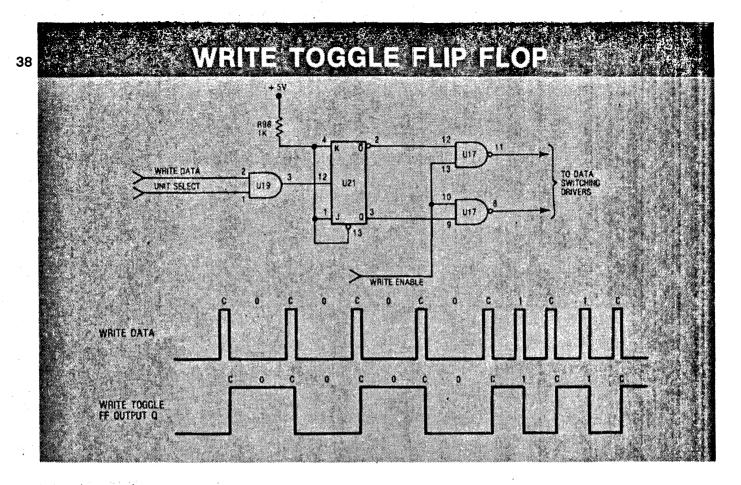

THE WRITE TOGGLE FLIP FLOP IS THE FIRST STAGE IN CONVERSION OF THE COM-POSITE CLOCK AND DATA BIT SERIAL DATA SIGNAL FROM THE HOST SYSTEM CON-TROLLER TO THE SIGNAL USED BY THE WRITE HEAD.

WRITE DATA IS FIRST GATED WITH THE UNIT SELECT TO ENSURE THAT THE DATA IS FOR THIS UNIT. THE WRITE TOGGLE FLIP FLOP U21, IS A JK FLIP FLOP WITH BOTH THE SET AND RESET INPUTS HELD HIGH AND WRITE DATA/ CONNECTED TO THE CLOCK INPUT. IN THIS CONDITION, THE JK FLIP FLOP COMPLIMENTS ON THE TRAIL-ING EDGE OF EACH INPUT DATA PULSE AS SHOWN IN THE LOWER PART OF THE DIA-GRAM.

THIS ACTION PRODUCES THE COMPOSITE SIGNAL, SHOWN BELOW THE WRITE DATA SIGNAL, IN WHICH EACH CLOCK AND DATA ONE BIT IS REPRESENTED BY A LEVEL CHANGE AND NOT THE SIGNAL LEVEL.

THE SET AND RESET OUTPUTS OF THE JK FLIP FLOP ARE GATED IN U17 WITH WRITE ENABLE BEFORE BEING OUTPUT TO THE DATA SWITCHING DRIVERS.

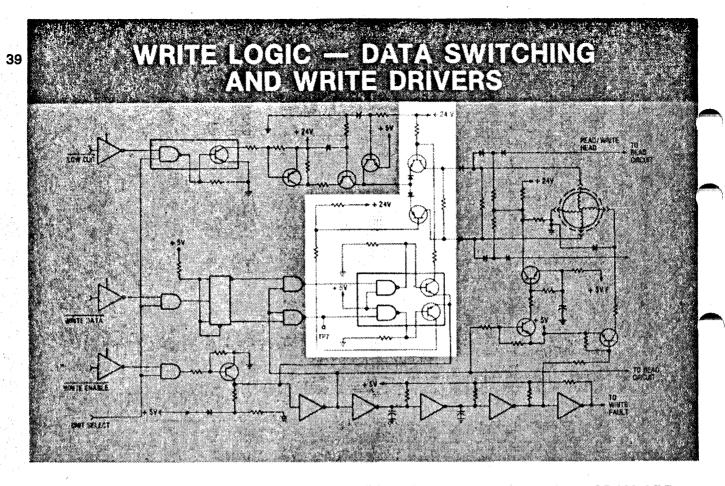

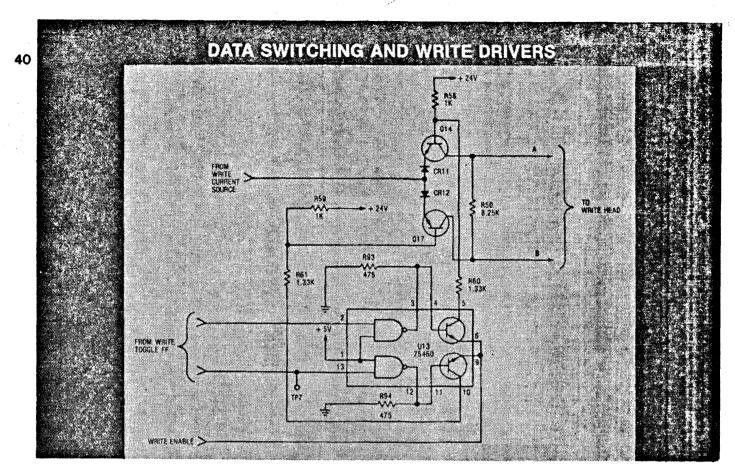

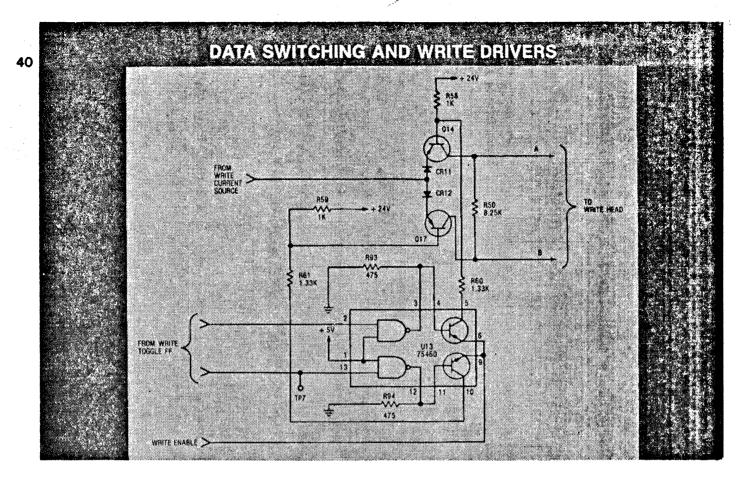

THE DATA SWITCHING AND WRITE DRIVERS, HIGHLIGHTED IN THIS DIAGRAM ARE THE NEXT STAGE IN THE WRITE LOGIC. THE DATA SWITCHING DRIVERS CONTROL THE CONDUCTION OF THE WRITE DRIVERS WHICH IN TURN PROVIDE CURRENT TO THE WRITE HEAD.

THE TWO DATA SWITCHING DRIVERS ARE LOCATED IN A SINGLE IC PACKAGE U13. BECAUSE THE TWO INPUTS TO U13 ARE THE SET AND RESET OUTPUTS OF THE WRITE TOGGLE FLIP FLOP, ONLY ONE DRIVER CAN CONDUCT AT A TIME. Q14 AND Q17 ARE THE WRITE DRIVER TRANSISTORS. AS ONLY ONE OF THEM CAN CONDUCT AT ANY TIME, Q14 AND Q17 ARE USED TO DETERMINE THE DIRECTION OF CURRENT FLOW THROUGH THE WRITE HEAD. WITH Q14 CONDUCTING, CURRENT FLOWS TO THE WRITE HEAD THROUGH "A" AND NOT "B." WITH Q17 CONDUCTING CURRENT FLOWS TO THE WRITE HEAD THROUGH "B" AND NOT "A."

THE CURRENT FOR THE WRITE DRIVERS IS SUPPLIED FROM THE WRITE CURRENT SOURCE WHICH IS DETAILED LATER. THE DELAYED WRITE ENABLE SIGNAL IS ALSO USED BY THE WRITE FAULT LOGIC WHICH IS EXPLAINED LATER.

## WRITE FAULT

47

A write enable is issued when the head is not loaded Write data are sent at the wrong clock rate A write is issued and data not received within 450 µS

A WRITE FAULT IS DEFINED WHEN ONE OR MORE OF THESE CONDITIONS EXIST; A WRITE ENABLE IS ISSUED WHEN THE HEAD IS NOT LOADED; WRITE DATA ARE SENT AT THE WRONG CLOCK RATE; AND/OR A WRITE IS ISSUED AND DATA ARE NOT RECEIVED WITHIN A 450 MICROSECOND TIME PERIOD.

THE THREE POSSIBLE WRITE FAULT CONDITIONS ARE DETERMINED BY THE WRITE FAULT LOGIC. WHEN A WRITE FAULT OCCURS, THE WRITE FAULT LATCH IS SET TO INDICATE THE CONDITION TO THE HOST SYSTEM CONTROLLER.

THE WRITE FAULT LATCH CONSISTS OF TWO ELEMENTS OF U12.

THE INPUT SIGNAL, HEAD LOAD, IS GATED WITH WRITE ENABLE IN U17 AND THE OUTPUT IS APPLIED TO ONE OF THE SET INPUTS OF THE LATCH. THIS CAUSES THE LATCH TO SET IF WRITE ENABLE IS RECEIVED BEFORE HEAD LOAD.

THE OTHER SET INPUT IS THE OUTPUT OF A THREE INPUT "NAND" GATE, ALSO AN ELEMENT OF U12. THE INPUTS TO THIS "NAND" GATE ARE WRITE ENABLE, WRITE ENABLE DELAYED AND THE INVERTED OUTPUT OF THE DATA RATE ONE SHOT, U16.

U16, IS A RETRIGGERABLE ONE SHOT MULTIVIBRATOR THAT IS TRIGGERED BY THE DATA INPUT. THE FIRST DATA BIT MUST BE RECEIVED BEFORE WRITE ENABLE DELAYED, FROM THE 450 MICROSECOND DELAY CIRCUIT, APPLIES A HIGH TO THE THREE INPUT "NAND" GATE. THE FIRST DATA BIT CAUSES THE INVERTED OUTPUT OF THE ONE SHOT TO GO LOW AND STAY LOW IF THE NEXT DATA BIT IS RECEIVED BEFORE THE ONE SHOT TIMES OUT. IF NO DATA ARE RECEIVED TO TRIGGER THE ONE SHOT OR, IF THE DATA BITS ARE NOT RECEIVED AT A RATE WHICH KEEPS THE ONE SHOT FROM TIMING OUT, THE WRITE FAULT LATCH IS SET.

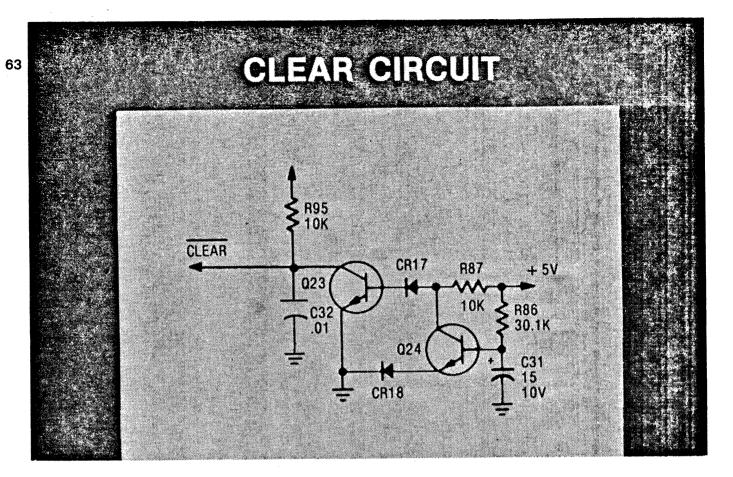

ONCE THE WRITE FAULT LATCH IS SET, IT CAN ONLY BE RESET BY A WRITE FAULT RESET FROM THE HOST SYSTEM CONTROLLER OR THE CLEAR SIGNAL.

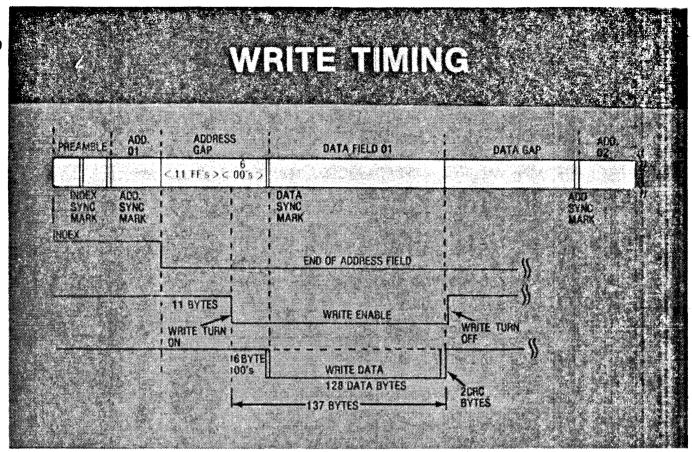

THE TIMING OF A WRITE OPERATION IS DETERMINED BY THE HOST SYSTEM CON-TROLLER. THIS TIMING DIAGRAM SHOWS THE WRITE SEQUENCE FOR SECTOR ONE WHICH IS BASICALLY THE SAME FOR ALL OTHER SECTORS.

REMEMBER THAT THE DISKETTE IS FORMATTED, MEANING THAT THE ADDRESS FIELDS ARE PREVIOUSLY ENCODED ON THE DISKETTE. THE TOP PART OF THE DIA-GRAM SHOWS THE FORMAT AT THE START OF A TRACK ON THE DISKETTE. THE FORMATTED DISKETTE ALLOWS DATA TO BE WRITTEN BY A "WRITE SPLICE" OPER-ATION IN WHICH THE WRITE STARTS DURING THE ADDRESS GAP AND FINISHES IN THE DATA GAP IMMEDIATELY FOLLOWING THE DATA FIELD.

BEFORE A WRITE OPERATION COMMENCES, THE HOST SYSTEM CONTROLLER

· 49

PERFORMS A "SEEK" OPERATION TO FIRST LOCATE THE CORRECT TRACK AND SECOND TO LOCATE THE CORRECT ADDRESS ON THAT TRACK.

WRITE TURN ON OCCURS WHEN WRITE ENABLE GOES LOW, 11 BYTES AFTER COM-PLETING THE READ OF THE ADDRESS FIELD. THIS IS FOLLOWED BY THE GENERA-TION OF SIX BYTES OF ZEROES WHICH PROVIDE A BUFFER ZONE TO ALLOW THE WRITE CIRCUITRY TIME TO TURN ON BEFORE ACTUAL DATA ARE RECEIVED. AFTER THE SIX BYTES OF ZEROES, THE UNIT WRITES A DATA SYNC MARK FOLLOWED BY 128 BYTES OF DATA AND TWO CRC CHARACTERS.

WRITE TURN OFF OCCURS WHEN WRITE ENABLE GOES HIGH TWO BIT TIMES AFTER WRITING THE SECOND CRC BYTE. AFTER WRITING THE LAST BIT OF THE SECOND CRC BYTE, TWO CLOCK BITS WITH ZERO DATA BITS ARE WRITTEN IN THE DATA GAP FIELD.

WRITE ENABLE IS THEN TURNED OFF ON THE THIRD CLOCK BIT TRANSITION. THE REMAINDER OF THE DATA GAP PROVIDES TIME FOR THE WRITE CIRCUITRY TO TURN OFF BEFORE THE READ/WRITE HEAD REACHES THE NEXT ADDRESS FIELD.

TO SUMMARIZE THE WRITE LOGIC, WRITE DATA/ IS INPUT TO THE WRITE TOGGLE FLIP FLOP WHICH COMPLIMENTS FOR EACH CLOCK OR DATA BIT. THE SET AND RE-SET OUTPUTS OF THE WRITE TOGGLE FLIP FLOP TOGGLE THE TWO WRITE DRIVERS THROUGH THE DATA SWITCHING DRIVERS WHICH CAUSES THE DIRECTION OF MAG-NETIC FLUX IN THE WRITE HEAD TO CHANGE FOR EACH CLOCK OR DATA BIT. THE CURRENT FOR THE WRITE DRIVERS IS PROVIDED THROUGH THE WRITE CURRENT SOURCE WHICH REDUCES THE CURRENT WHEN WRITING TO TRACKS OVER TRACK 43.

THE DELAY CIRCUIT DELAYS THE WRITE ENABLE SIGNAL BY 450 MICROSECONDS BEFORE ENABLING THE ERASE DRIVER FOR THE TUNNEL ERASE.

THE DELAYED WRITE ENABLE SIGNAL IS ALSO USED BY THE WRITE FAULT LOGIC.

THE WRITE FAULT LOGIC DETECTS POSSIBLE WRITE ERROR CONDITIONS WHICH CAUSE THE WRITE ERROR FLIP FLOP TO LATCH UNTIL IT IS RESET BY THE CON-TROLLER.

STOP THE LECTURE AT THIS POINT AND RETURN TO YOUR WORKBOOK. COMPLETE THE PRACTICE FOR THIS SECTION BEFORE CONTINUING.

٤

THE FINAL SECTION OF LOGIC TO BE DESCRIBED IN THE BLOCK DIAGRAM IS THE CONTROL LOGIC.

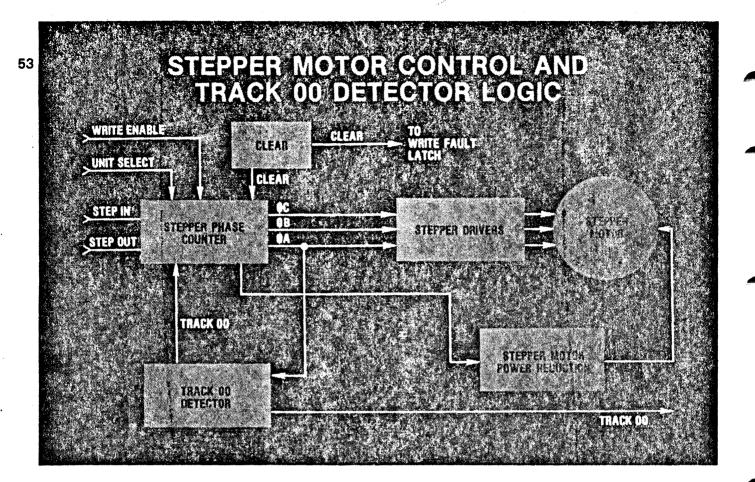

THERE ARE FOUR MAIN SECTIONS WITHIN THE CONTROL LOGIC, STEPPER MOTOR CONTROL; TRACK 00 DETECTION; HEAD LOAD; AND INDEX AND READY.

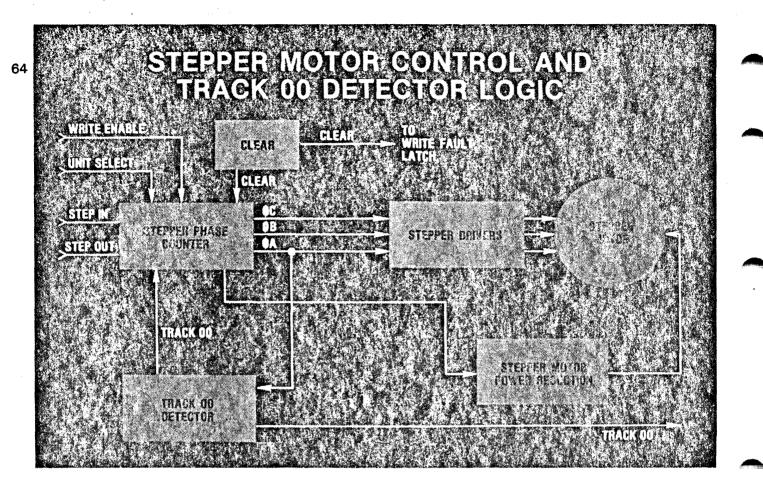

THE FIRST OF THESE SECTIONS DESCRIBED IS THE STEPPER MOTOR CONTROL AND TRACK 00 DETECTION LOGIC.

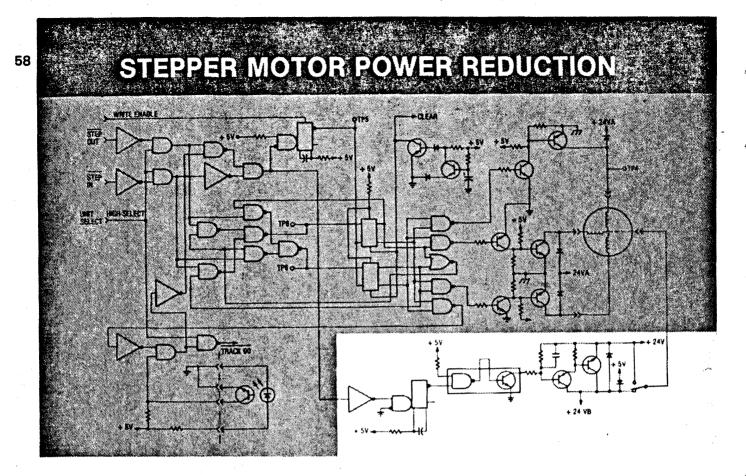

THE STEPPER MOTOR CONTROL LOGIC CONSISTS OF THE STEPPER PHASE COUNTER WHICH IS INCREMENTED BY THE STEP IN INPUT SIGNAL AND DECREMENTED BY THE STEP OUT INPUT SIGNAL. THE THREE OUTPUTS, PHASE "C", "B" AND "A" DRIVE THE STEPPER MOTOR THROUGH THE STEPPER DRIVERS.

THE STEPPER MOTOR POWER REDUCTION LOGIC REDUCES THE CURRENT SUPPLIED TO THE ACTIVE PHASE WITHIN THE STEPPER MOTOR WHEN THE MOTOR IS NOT MOV-ING. THE REDUCTION IN CURRENT IS REQUIRED TO PREVENT OVERHEATING. A SMALL CURRENT CONTINUES TO BE SUPPLIED TO THE ACTIVE PHASE IN THE MOTOR WHEN IT IS NOT MOVING TO ELECTRICALLY DETENT THE MOTOR.

THE TRACK 00 DETECTOR DETERMINES THAT THE READ/WRITE HEAD IS AT TRACK

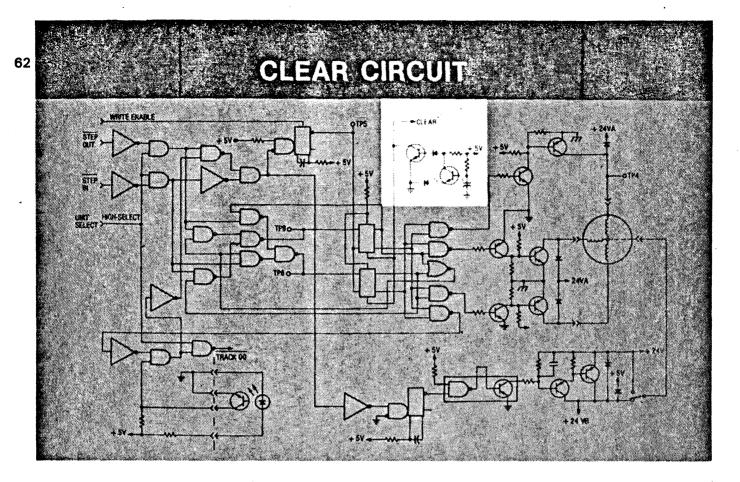

00 USING BOTH THE OPTICAL DETECTOR AND THE PHASE "A" SIGNAL. THE CLEAR LOGIC SHOWN AT THE TOP OF THE DIAGRAM RESETS THE STEPPER PHASE COUNTER ON POWER ON, AND AS MENTIONED IN AN EARLIER PART OF THE LECTURE, THE CLEAR LOGIC ALSO RESETS THE WRITE FAULT LATCH.

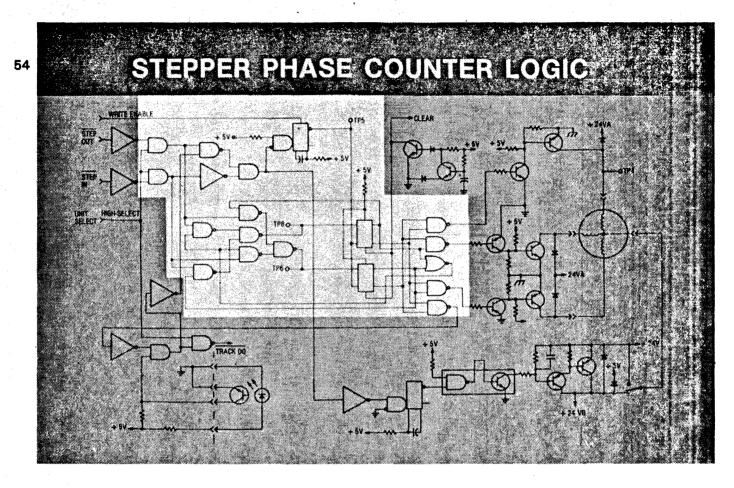

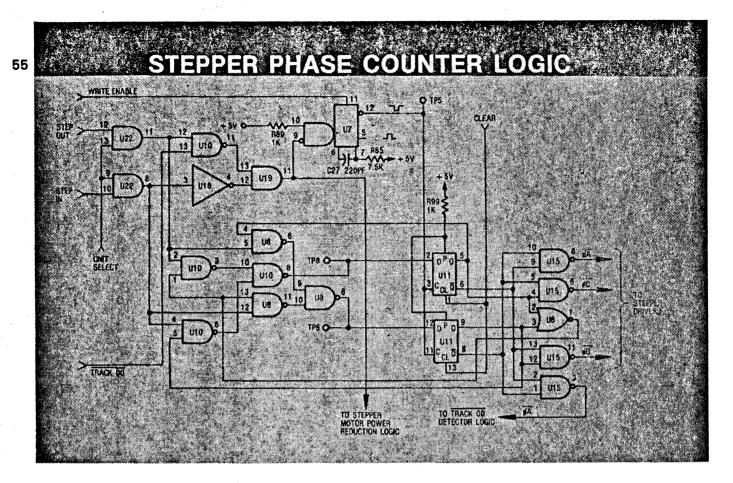

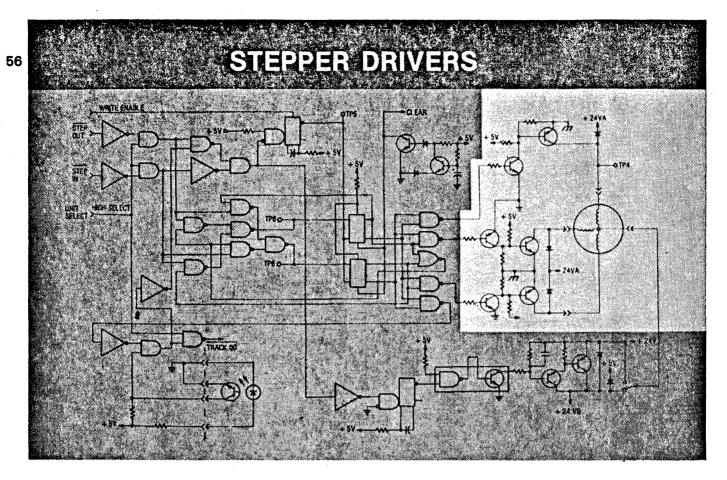

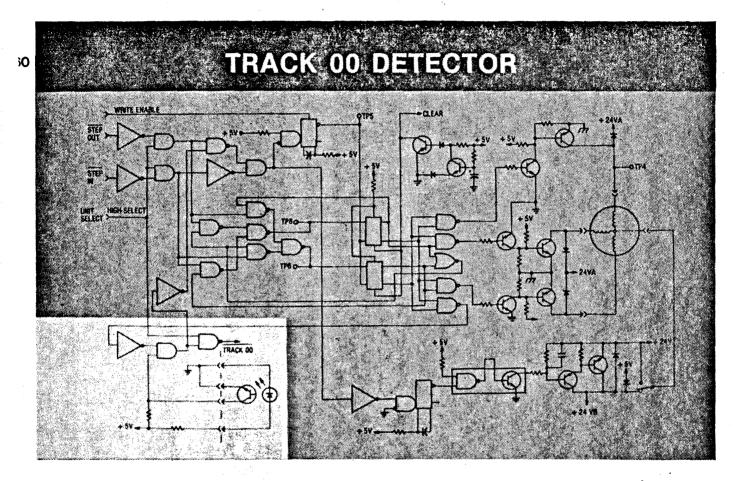

THIS DIAGRAM HIGHLIGHTS THE STEPPER PHASE COUNTER LOGIC WHICH SEQUEN-CES THE ACTIVE PHASES TO THE STEPPER MOTOR ACCORDING TO THE INPUT SIG-NALS STEP OUT AND STEP IN.

THE STEPPER PHASE COUNTER ITSELF CONSISTS OF TWO "D" TYPE FLIP FLOPS, U11, SHOWN CLOSE TO THE CENTER OF THE DIAGRAM. THE OUTPUTS OF THE TWO "D" TYPE FLIP FLOPS ARE DECODED TO GIVE THE THREE PHASES "A", "B" AND "C" BY U15. THE SIGNALS PHASE "A", "B" AND "C" CONTROL THE STEPPER DRIVERS.

THE COUNT OUTPUT FROM THE TWO FLIP FLOPS IS INCREMENTED OR DECREMENTED UNDER THE CONTROL OF THE STEP OUT AND STEP IN SIGNALS, BY THE LOGIC GAT-ING COMPRISING U8 AND U10.

NOTICE THAT THE "D" TYPE FLIP FLOPS ARE CLOCKED ON THE "C" INPUT BY THE RESET OUTPUT OF A RETRIGGERABLE ONE SHOT MULTIVIBRATOR, U7 SHOWN TOP CENTER. THE "D" TYPE FLIP FLOPS ARE CLOCKED BY THE POSITIVE GOING EDGE

OF THE CLOCK SIGNAL. THIS ACTION DELAYS THE CLOCK SIGNAL BY 0.6 MICRO-SECONDS FROM THE ACTUAL STEP COMMAND TO ALLOW TIME FOR THE INPUTS TO THE "D" TYPE FLIP FLOPS TO BE CORRECTLY CONDITIONED BY THE INPUT LOGIC. THE STEP COMMAND SIGNALS HAVE A MINIMUM DURATION OF 1 MICROSECOND TO ENSURE CORRECT OPERATION.

GATING STEP OUT AND STEP IN WITH UNIT SELECT IN U22 ENSURES THAT ONLY THE STEPPER LOGIC IN THE SELECTED UNIT IS ACTIVATED.

THE TRACK 00/ SIGNAL IS GATED IN THE ELEMENT OF U10 SHOWN TOWARDS THE TOP LEFT OF THE DRAWING, TO DISABLE FURTHER STEP OUT COMMANDS ONCE THE READ/WRITE HEAD HAS REACHED TRACK 00.

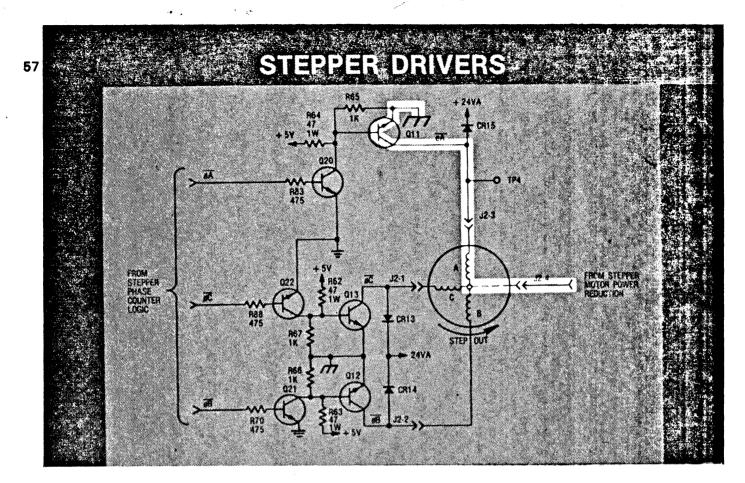

THE THREE STEPPER DRIVERS, HIGHLIGHTED IN THIS DRAWING WITH THE STEPPER MOTOR ITSELF, DRIVE EACH OF THE THREE STEPPER MOTOR PHASE WINDINGS IN SEQUENCE BY PROVIDING A CURRENT RETURN TO GROUND.

EACH OF THE THREE DRIVER CIRCUITS IS IDENTICAL, CONSISTING OF A PAIR OF TRANSISTORS. FOR EXAMPLE, PHASE A/ IS ACTIVE WHEN LOW. THIS SWITCHES Q20 ON WHICH SWITCHES Q11 ON PROVIDING THE CURRENT PATH SHOWN FROM THE CURRENT INPUT VIA THE STEPPER MOTOR POWER REDUCTION CIRCUIT THROUGH THE PHASE "A" MOTOR WINDING TO GROUND.

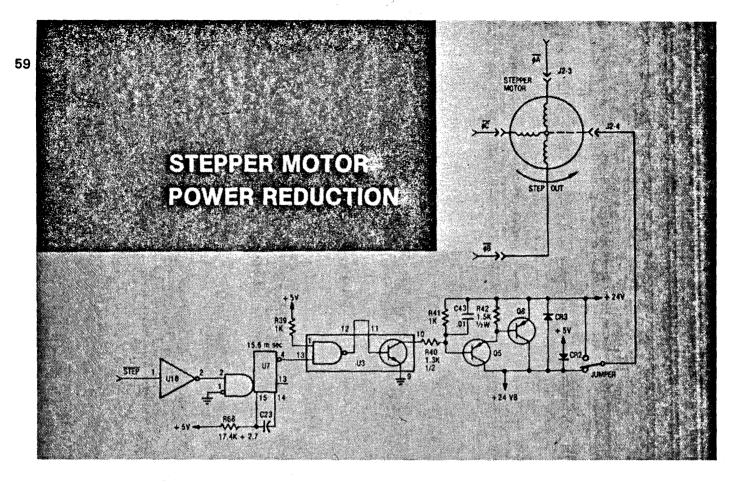

THE POWER SUPPLIED TO THE STEPPER MOTOR IS CONTROLLED BY THE STEPPER MOTOR POWER REDUCTION LOGIC. AS MENTIONED EARLIER, THE POWER SUPPLIED TO THE MOTOR WHEN IT IS NOT MOVING MUST BE REDUCED TO AVOID OVERHEAT-ING.

WHENEVER A STEP COMMAND IS RECEIVED, THE SIGNAL STEP/ FROM THE STEPPER PHASE COUNTER LOGIC GOES LOW. THROUGH INVERTER U18, THIS TRIGGERS AN-OTHER RETRIGGERABLE ONE SHOT MULTIVIBRATOR U7 WHICH PROVIDES A 15.6 MILLISECOND PULSE TO THE DRIVER IC U3. THIS SWITCHES ON THE DARLINGTON PAIR Q5 AND Q8 TO CONNECT THE STEPPER MOTOR TO +24 VOLTS FOR 15.6 MILLI-SECONDS. AS THE NEXT STEPPER MOTOR PHASE IS SELECTED THE MOTOR SHAFT ROTATES BY ONE STEP OR 15 DEGREES.

IF ADDITIONAL STEP COMMANDS ARE RECEIVED, WITHIN THE 15.6 MILLISECOND TIME PERIOD, THE MULTIVIBRATOR U7 IS RETRIGGERED TO HOLD Q5 AND Q8 ON UNTIL 15.6 MILLISECONDS AFTER THE LAST STEP COMMAND.

WHEN THE MULTIVIBRATOR TIMES OUT, Q5 AND Q8 TURN OFF TO DISCONNECT THE +24 VOLT SOURCE. A REDUCED CURRENT PATH IS NOW PROVIDED TO THE STEPPER MOTOR FROM THE +5 VOLT SUPPLY THROUGH THE BLOCKING DIODE CR2. THE REDUCED CURRENT ELECTRICALLY DETENTS THE STEPPER MOTOR IN THE ACTIVE PHASE POSITION.