# Burroughs MEDIUM SYSTEMS B 2500/B 3500/B 2700 CENTRAL PROCESSOR and MEMORY

**REFERENCE MANUAL**

COPYRIGHT© 1966, 1968, 1969, 1972 AA828689 AA995115 AA120798 **Burroughs Corporation**

Detroit, Michigan 48232

\$2.00

# TABLE OF CONTENTS

| TITLE                          | PAGE              |

|--------------------------------|-------------------|

| INTRODUCTION                   | vi                |

| CORE MEMORY                    | 1-1               |

| General                        | 1-1               |

| General                        | 1-1               |

| Memory Base B Cabinet          | 1-2               |

| Memory Stacks                  | 1-2               |

| Stack Configuration            | 1-2               |

| Memory Control                 | 1-2               |

| Cabinet Addressing             | 1-4               |

| Stack Addressing               | 1-4               |

| Sextant Addressing             | 1-5               |

| Location                       | 1-5               |

| Parity                         | 1-11              |

| Memory Timing                  | 1-11              |

| Stack Timing                   | 1-11              |

| Read Operation                 | 1-11              |

| Write Operation                | 1-11              |

| CENTRAL PROCESSOR              | 2-1               |

| General                        | 2-1<br>2-1        |

| Processor Operating Modes      | 2-1 2-1           |

| Control State, Zero Base       | 2-1<br>2-1        |

| Control State, Non-Zero Base   | $2^{-1}$<br>2-1   |

| Normal State, Zero Base        | $2^{-1}$<br>2-1   |

| Normal State, Non-Zero Base    | $2^{-1}$<br>2-1   |

| Logical Units                  | $2^{-1}$<br>2-1   |

| Overflow Flip-Flop             | $2^{-1}$<br>2-1   |

| Comparison Flip-Flops          | 2-1<br>2-2        |

| EBCDIC/USASCII Mode Flip-Flop  | 2-2               |

| INTERRUPT Flip-Flop            | 2-2               |

| Normal/Control State Flip-Flop | 2-3<br>2-3        |

| Timer                          | 2-3               |

| Base Register                  |                   |

| Limit Register                 | 2-4               |

| Index Registers                | 2-4               |

| Data Modes                     | 2-4               |

| Four-Bit Mode                  | 2-4               |

| Eight-Bit Mode                 | 2-5               |

| Instruction Format             | 2-5               |

| Address Index                  | 2-6               |

| Address Controller             | 2-7               |

| Address Digits                 | 2-7               |

| Operator Code                  | 2-7               |

|                                | 2-7               |

| Literal Specification          | 2-8               |

| Read-Only Memory               | 2-8<br>2-8        |

| Hardware Instructions          | $\frac{2-8}{2-8}$ |

| Data Movement Operation Codes  | 2-8               |

SECTION

1

For Form 1063781

# TABLE OF CONTENTS (Cont)

# SECTION

2 (Cont)

# TITLE

| P | Δ | G | F  |

|---|---|---|----|

| г | м | 0 | E. |

| Move Alphanumeric (MVA)                                                                                                                       | 2-9                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Move Numeric (MVN)                                                                                                                            | 2-9                 |

| $Move \operatorname{Repeat}(MVR)  .  .  .  .  .  .  .  .  .  $                                                                                | 2-9                 |

| Move Words (MVW)                                                                                                                              | 2-9                 |

| Move Words and Clear (MVC)                                                                                                                    | 2-9                 |

| Move Links (MVL)                                                                                                                              | 2-9                 |

| Arithmetic Operation Codes                                                                                                                    | 2-10                |

| Two Address Add (INC)                                                                                                                         | $\frac{2}{2}$ -10   |

| Three Address Add $(ADD)$                                                                                                                     | $\frac{2}{2}$ -10   |

| Two Address Subtract (DEC)                                                                                                                    | $\frac{2}{2}$ -10   |

| Three Address Subtract (SUB)                                                                                                                  | $\frac{2}{2-10}$    |

| $Multiply (MPY) \qquad \dots \qquad $ | $\frac{2-10}{2-10}$ |

| Divide (DIV)                                                                                                                                  | 2-10<br>2-10        |

| Floating Point Arithmetic Operation Codes                                                                                                     | 2-10<br>2-10        |

| Floating Point Add $(FAD)$                                                                                                                    |                     |

| Floating Point Add (FAD)                                                                                                                      | 2-10                |

| Floating Point Multiply (FMP)                                                                                                                 | 2-11                |

| Floating Point Divide (FDV)                                                                                                                   | 2-11                |

|                                                                                                                                               | 2-11                |

| Logical Operation Codes                                                                                                                       | 2 - 11              |

| Translate (TRN)                                                                                                                               | 2-11                |

| Scan to Delimiter-Equal (SDE)                                                                                                                 | 2-11                |

| Scan to Delimiter-Unequal (SDU)                                                                                                               | 2 - 11              |

| Scan to Delimiter-Zone Equal (SZE)                                                                                                            | 2 - 12              |

| Scan to Delimiter-Zone Unequal $(SZU)$                                                                                                        | 2-12                |

| Bit Zero Test (BZT)                                                                                                                           | 2 - 12              |

| Bit One Test (BOT)                                                                                                                            | 2 - 12              |

| AND (AND)                                                                                                                                     | 2-12                |

| OR(ORR)                                                                                                                                       | 2-12                |

| $\operatorname{NOT}(\operatorname{NOT})$                                                                                                      | 2-13                |

| $\underline{SEARCH}(\underline{SEA})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                        | $\frac{-10}{2-13}$  |

| Compare Alphanumeric (CPA)                                                                                                                    | $\frac{2}{2}$ -13   |

| Compare Numeric (CPN)                                                                                                                         | 2-13<br>2-13        |

| $EDIT (EDT) \qquad \dots \qquad $     | 2-13<br>2-14        |

| Address Branching                                                                                                                             | 2-14<br>2-14        |

| No Operation (NOP)                                                                                                                            | $\frac{2-14}{2-14}$ |

| Branch on Less Than (LSS)                                                                                                                     | $\frac{2-14}{2-14}$ |

| Branch on Equal (EQL)                                                                                                                         |                     |

| Dranch on Equal (Eq. ) $\cdot \cdot $         | 2-14                |

| Branch on Equal or Less than Equal (LEQ)                                                                                                      | 2-14                |

| Branch on Greater (GTR)                                                                                                                       | 2-14                |

| Branch on Not Equal (NEQ)                                                                                                                     | 2-14                |

| Branch on Greater than or Equal (GEQ)                                                                                                         | 2-14                |

| Branch Unconditionally (BUN)                                                                                                                  | 2 - 15              |

| Branch on Overflow (OFL)                                                                                                                      | 2 - 15              |

| Branching Operator Codes                                                                                                                      | 2 - 15              |

| $Enter (NTR)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                | 2 - 15              |

| EXIT (EXT)                                                                                                                                    | 2 - 15              |

| Branch Communicate (BCT)                                                                                                                      | 2 - 15              |

| Privileged Operation Codes                                                                                                                    | 2 - 15              |

| Branch Reinstate (BRE)                                                                                                                        | 2 - 15              |

| Initiate (IIO)                                                                                                                                | 2 - 16              |

|                                                                                                                                               |                     |

# TABLE OF CONTENTS (Cont)

# SECTION

2 (Cont)

### TITLE

| Read Address (RAD)                           |         | •••           |       |       | • • | • | 2 - 16                    |

|----------------------------------------------|---------|---------------|-------|-------|-----|---|---------------------------|

| Read and Clear Timer (RCT)                   |         | • • •         |       |       | • • | • | 2 - 16                    |

| Reader Timer (RDT)                           |         | • • •         |       |       | ••• | • | 2 - 17                    |

| Set Timer $(STT)$                            |         |               |       |       | • • |   | 2 - 17                    |

| Scan Result Descriptor (SRD)                 |         |               |       | ·     |     |   | 2-17                      |

| Miscellaneous Operator Codes                 |         |               |       |       |     |   | 2 - 17                    |

| Set Mode (SMF)                               |         |               |       |       |     |   | 2 - 17                    |

| Set Mode (SMF)<br>Halt, Branch (HBR)         |         |               |       |       |     |   | 2 - 17                    |

| Halt, Breakpoint (HBK) .                     |         |               |       |       |     |   | 2-18                      |

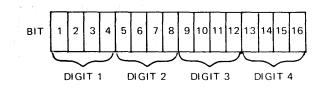

| Processor Result Descriptors                 |         |               |       |       |     |   | 2-18                      |

| Normal State Interrupts                      |         |               |       | • • • |     |   | $\frac{-10}{2-18}$        |

| Memory Parity Error                          |         |               |       |       |     |   | $\bar{2}-19$              |

| Address Error                                |         |               |       |       |     |   | $\frac{-10}{2-19}$        |

| Instruction Time-Out                         | • • • • | • • •         | • • • |       | • • | • | $\frac{1}{2}$ -19         |

| Invalid Instructions                         | • • • • |               |       |       |     | • | 2-20                      |

| Privileged Instructions                      |         |               |       |       |     |   | $\frac{1}{2}$ -20         |

| Clock Interrupt                              |         |               |       |       |     |   | 2-20                      |

| Control State Interrupts                     |         |               |       |       |     |   | 2-20                      |

| Invalid I/O Operation                        |         |               |       |       |     |   | 2-20                      |

| Stack                                        |         |               |       |       |     |   | $\frac{2}{2}-20$          |

| Adder                                        |         |               |       |       |     |   | 2-21                      |

| Floating Point Representation                |         |               |       |       |     |   | 2-21<br>2-21              |

| Load Function                                |         |               |       |       |     |   | $\frac{2}{2}-\frac{2}{2}$ |

| Normal Load                                  |         |               |       |       |     |   | 2-23                      |

| Universal Load                               |         |               |       |       |     |   | 2-24                      |

| Console                                      |         |               |       |       |     |   | $\frac{2}{2}-24$          |

| Display Panel                                |         |               |       |       |     |   | 2-24<br>2-24              |

| Control Panel                                |         |               |       |       |     |   | 2-24<br>2-26              |

| CL (Clear) Key                               |         |               |       |       |     |   | 2-20<br>2-26              |

| LD (Load) Key                                |         |               |       |       |     |   | 2-26                      |

| STOP/RUN Key                                 |         |               |       |       |     |   | 2-26                      |

| SI (Single Instruction) Key                  |         |               |       |       |     |   | 2-20<br>2-26              |

| OI (Operator Interrupt) Key                  |         |               |       |       |     |   | 2-20<br>2-27              |

| OP Key                                       |         |               |       |       |     |   | 2-27                      |

| A, B, and C (Field Address) Ke               | evs     |               |       |       | • • | • | 2-27<br>2-27              |

| PA (Program Address) Key                     |         |               |       | •••   | • • | • | 2-21                      |

| AD (Address) Key                             |         |               |       | •••   | • • | • | 2-27                      |

| $\frac{110}{\text{WR}}$ (Write) Key $\ldots$ | • • • • |               | •••   | •••   | • • | • | 2-27                      |

| SKIP Key                                     |         |               |       |       |     |   | 2-27                      |

| READ Key                                     |         |               |       |       |     |   | 2-27                      |

| BM (Base Memory) Key                         |         |               |       |       |     |   | 2-21                      |

| CS (Control State) Key                       | ••••    | •••           | •••   | • • • | ••• | • | 2-27                      |

| TERM (Terminate) Key                         |         |               |       |       |     |   | 2-21                      |

| DIGIT Keys                                   |         |               |       |       |     |   | 2-28<br>2-28              |

| EMERG PULL OFF (Emerger                      |         |               |       |       |     |   | 2-28<br>2-28              |

| PWR ON Key                                   |         | ., <u>.</u> y | •••   | • • • | ••• | • | 2-28<br>2-28              |

| PWR OFF Key                                  | • • • • | • • •         |       | •••   | ••• | • | 2-28<br>2-28              |

| 1 1110 01 1 120 y                            | • • • • | • • •         | • • • | • • • | • • | • | 2-20                      |

# TABLE OF CONTENTS (Cont)

# SECTION

3

# TITLE CONTRACTOR CONTRACTOR

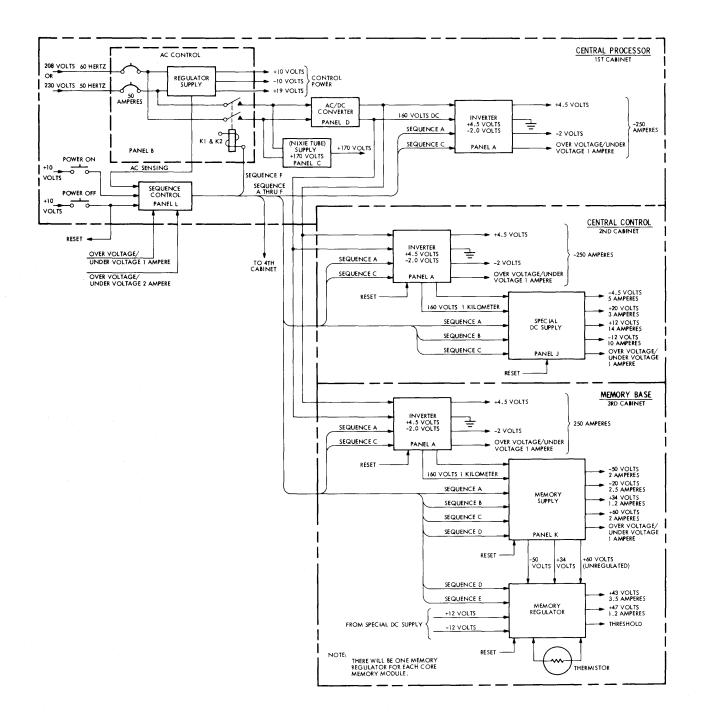

| SYSTEM POWER CONFIGURATION           |  |   |   |   |   |   |   |   | • |   |   |   | 3-1 |

|--------------------------------------|--|---|---|---|---|---|---|---|---|---|---|---|-----|

| General                              |  |   |   | • | • |   |   | • |   | • | • | • | 3-1 |

| Overvoltage and Undervoltage Sensing |  | • | • | • | • | • | • | • | • | • | • | • | 3-1 |

# LIST OF ILLUSTRATIONS

| FIGURE                         | TITLE                                            | PAGE       |

|--------------------------------|--------------------------------------------------|------------|

| 1-1.                           | Memory Cabinet                                   | 1-1        |

| 1-2.                           | Central Control and Memory Base A Cabinet Layout | 1-1        |

| 1-3.                           | Central Control and Memory Base A Cabinet        | 1-2        |

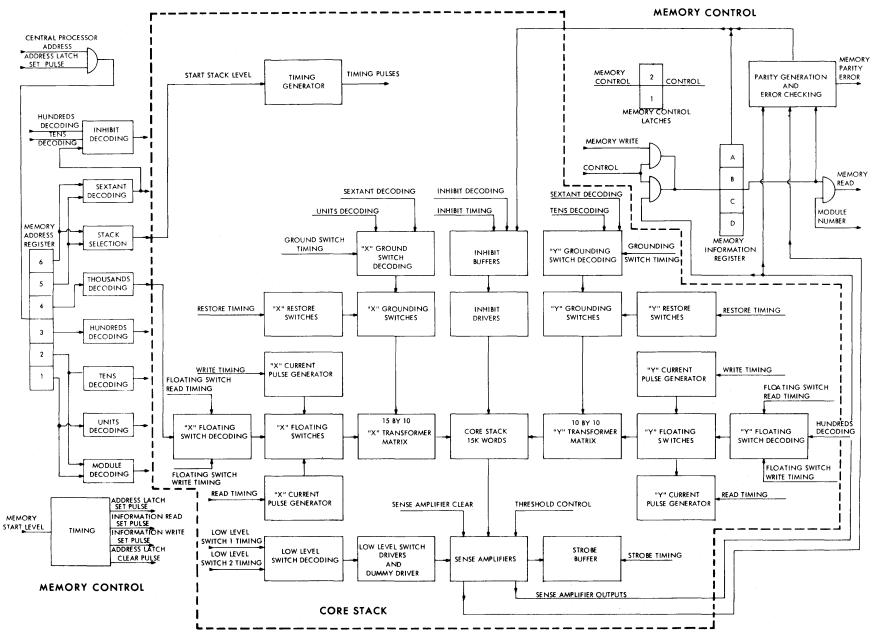

| 1-4.                           | Momony Block Diagram                             | 1-3        |

| 1-5.                           | Memory Base B Cabinet Layout                     | 1-4        |

| 1-6.                           | Memory Base B Cabinet                            | 1-4        |

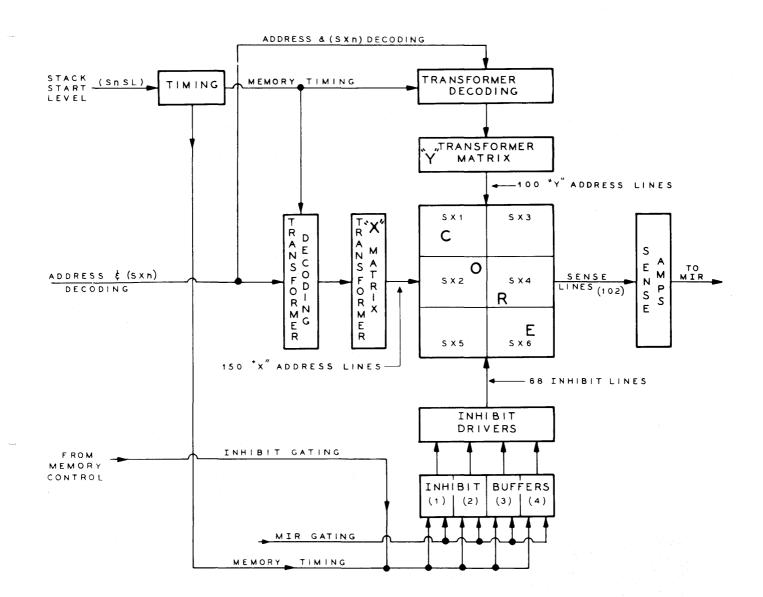

| 1-7.                           | Stack Block Diagram                              | 1-5        |

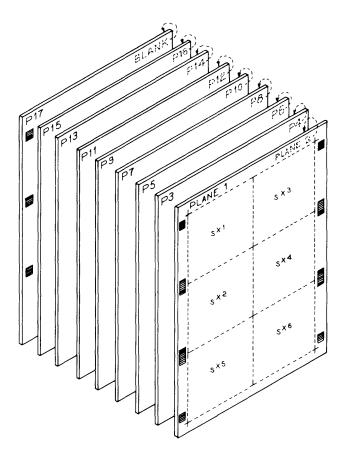

| 1-8.                           | Memory Planes                                    | 1-6        |

| 1-9.                           | Address Lines Through Sextants                   | 1-7        |

| 1-10.                          | Memory Control Interface                         | 1-8        |

| 1-11.                          | Memory Control/Stack Interface                   | 1-9        |

| 1-12.                          | Addressing Sequence                              | 1-10       |

| 1-13.                          | Sextant Gating of Transformers                   | 1-10       |

| 1-14.                          | 15 x 10 "X" Transfer Array                       | 1-11       |

| 1-15.                          | "X" Transformer Decoding Lines                   | 1-12       |

| 1-16.                          | "Y" Transformer Decoding Lines                   | 1-13       |

| 2-1.                           | Index Register Format                            | 2-4        |

| 2-2.                           | Six-Digit Instruction Format                     | 2-6        |

| 2-3.                           | Eight-Digit Instruction Format                   | 2-6        |

| <u>2</u> -4.                   | Field Length Digits                              | 2-8        |

| 2-5.                           | Literal Specification Control                    | 2-8        |

| <b>2</b> -6.                   | "AND" Truth Table                                | 2-12       |

| <b>2</b> -7.                   | "ORR" Truth Table                                | 2-13       |

| 2-8.                           | "NOT" Truth Table                                | 2-13       |

| <b>2</b> -9.                   | Processor Result Descriptor                      | 2-18       |

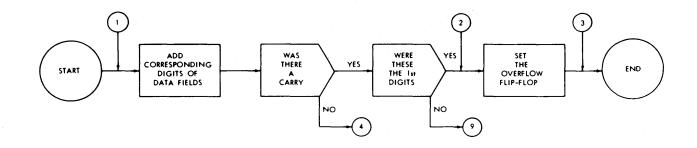

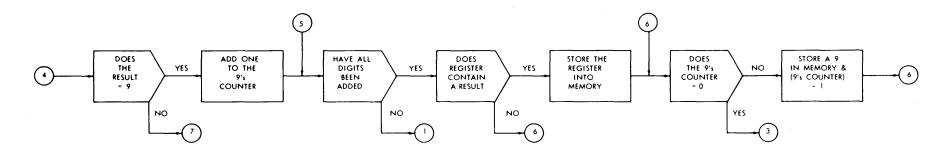

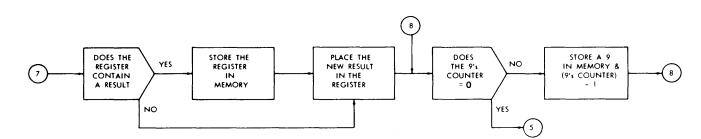

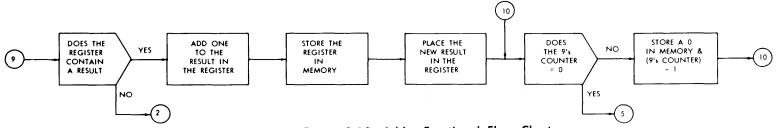

| <b>2-10</b> .                  | Adder Functional Flow Chart                      | 2-22       |

| <b>2</b> -10.<br><b>2-11</b> . | Adder Examples                                   | 2-23       |

| <b>2-11</b> .<br><b>2-12</b> . | Floating Point Data Format                       | 2-23       |

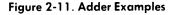

| 2-13.                          | Operator's Console                               | 2-25       |

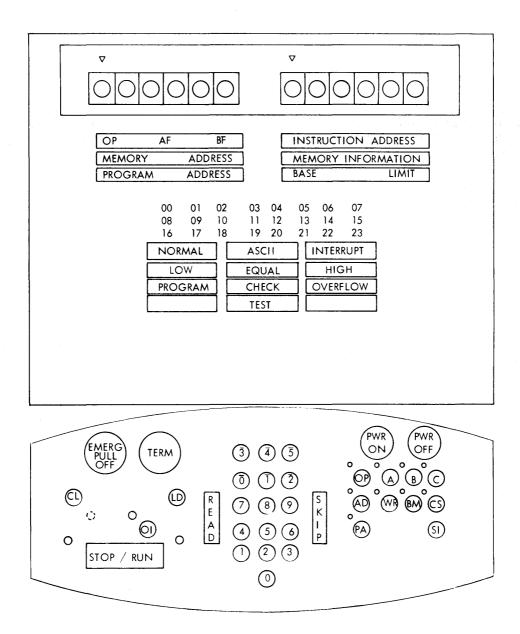

| 3-1.                           | General Power Interface Block Diagram            | 3-1        |

| 3 <b>-</b> 2.                  | Power Distribution Layout                        | 3-1<br>3-2 |

|                                | LIST OF TABLES                                   |            |

# TABLE

# TITLE

PAGE

PAGE

| 1-1 | Examples of Address Breakdown                | 1-8  |

|-----|----------------------------------------------|------|

| 2-1 | Bit Functions of Processor Result Descriptor | 2-18 |

| 2-2 | Floating Point Representation                | 2-23 |

The Burroughs B 2500, B 3500, and B 2700 memories and central processors offer a totally integrated design that incorporates monolitic, solid-state circuitry.

#### CORE MEMORY

The core memory, being extremely modular, allows for configurations that easily provide for most user requirements. Base and limit registers are designed within the memory logic to allow the system to utilize dynamic storage allocation and, perhaps of greatest importance, is that all memory addresses are digit addressable and the memory itself is easily incrementable.

#### CENTRAL PROCESSOR

The central processor contains the circuitry to perform the instruction set. The instructions are capable of performing operations on digit, byte, or word formatted fields. The internal 8bit code may be either EBCDIC or USASCII code and is programmatically selectable. In addition to executing the instruction set, the processor has an automatic interrupt system.

# SECTION 1

# GENERAL

The main memory utilized is a four-wire coincident current core memory with a minimum cycle time of one microsecond. Depending on the system storage, memory is variable in size from 10,000 characters up to a maximum of 500,000 characters.

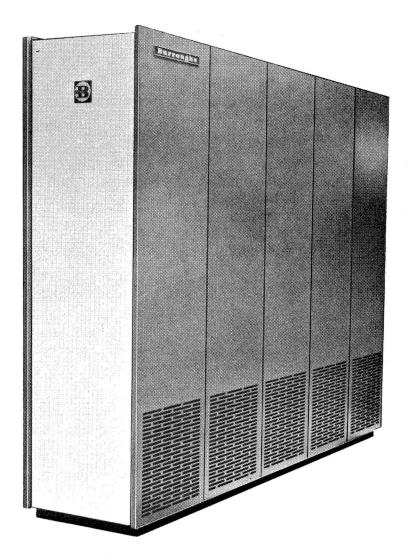

A typical memory cabinet is shown in figure 1-1. Two types of core memory cabinets are available: Central Control and Memory Base A cabinet and the Memory Base B cabinet.

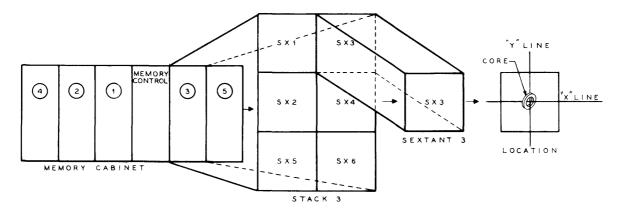

Figure 1-4 is a block diagram of the entire memory system.

Individual core modules, referred to as stacks, are available in 10,000 (10K) character, 20K character, and 30K character sizes. Each of these stacks is completely independent, containing all necessary drivers, sense amplifiers, and core.

# CENTRAL CONTROL AND MEMORY BASE A CABINET

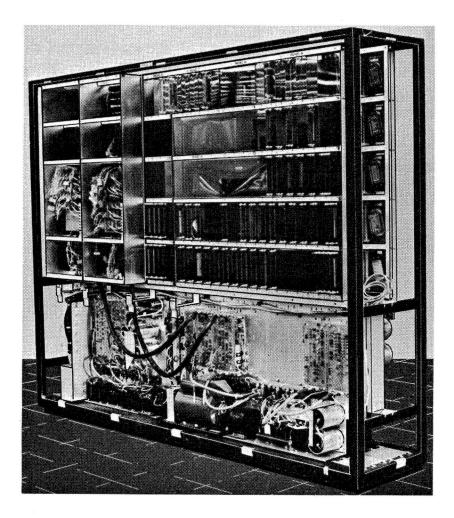

The Central Control and Memory Base A cabinet is used in the Two Cabinet System. Within this cabinet there is space allocated for up to two memory stacks and since the largest stack contains 30,000 characters, the Two Cabinet System is limited in core storage to 60,000 characters. Figure 1-2 shows a layout diagram of the Central Control and Memory Base A cabinet, and figure 1-3 shows the internal hardware of the cabinet.

Figure 1-2. Central Control and Memory Base A Cabinet Layout

Figure 1-3. Central Control and Memory Base A Cabinet

# MEMORY BASE B CABINET

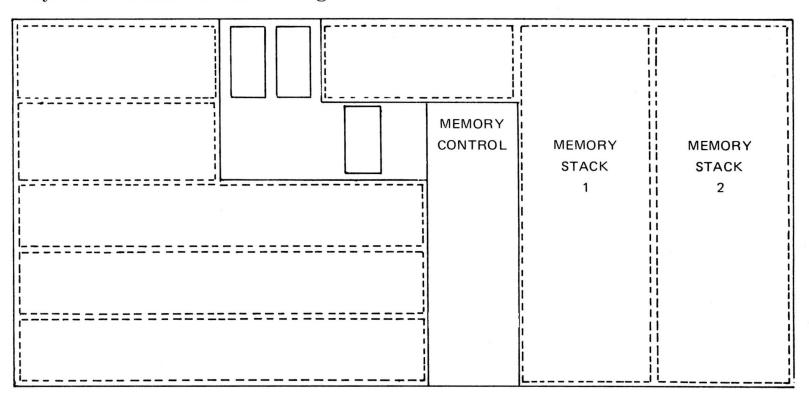

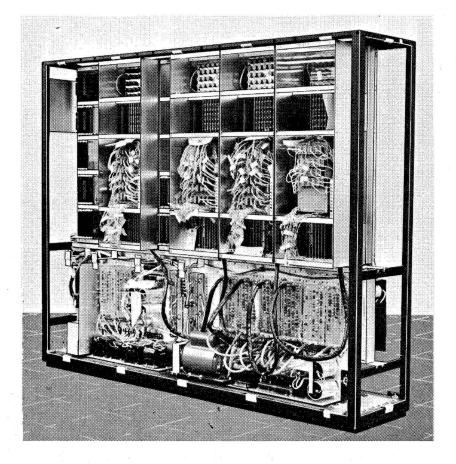

The Memory Base B cabinet houses up to five memory stacks and provides these systems with measurably more storage. Figure 1-5 is a layout diagram of the Memory Base B cabinet and figure 1-6 shows the internal hardware of the cabinet.

Certain Models of the B 2500 and B 2700 are configured into three cabinet systems (CPU, Peripheral Controls, and Memory Base). These Systems operate with one Memory Base B cabinet, with a maximum core storage of 120K characters (four 30K stacks).

Additional models of the B 2700 and B 3500 Systems can each utilize up to four Memory Base B cabinets. The first three cabinets, each containing five 30K stacks, provide these systems with storage for up to 450K characters. The fourth cabinet can house only up to 50K characters, giving the system a total memory storage capacity of 500K characters. The memory stacks are placed in specific locations within the cabinet as shown in the layout diagram, figure 1-5. Each consecutive stack area must contain a full 30K characters before the next location can be utilized.

# **MEMORY STACKS**

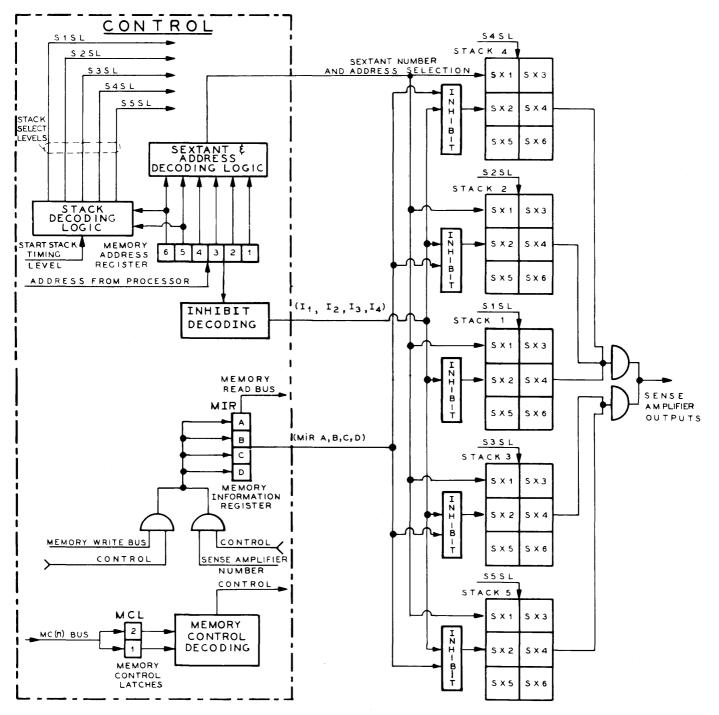

Figure 1-7 is a detailed block diagram of a core memory stack with associated control circuits. Each stack is self-sufficient in that it contains all necessary timing circuits, drivers, and sense amplifiers to be totally independent of all other stacks. However, if the storage size of the core memory is changed, the memory-size card, located in the central processor, must be changed.

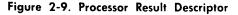

# Stack Configuration

Each core stack is 17 planes deep (figure 1-8), with each word containing one bit from each plane. This results in a 16-bit (four digit) word with one parity bit.

Each plane has its own sense and inhibits lines. They share addressing lines for associated locations on the other planes.

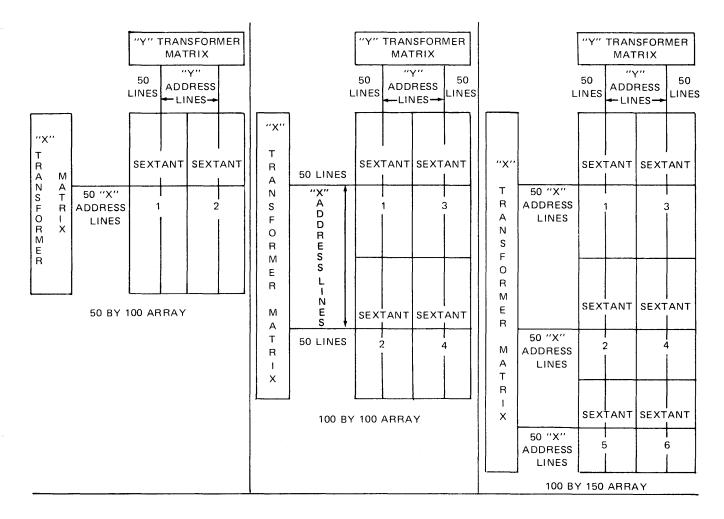

Array positioning provides for coordinate addressing of the desired core position. Figure 1-9 is a block diagram showing the three types of arrays: the 50 x 100 array for the 10,000 character stack, the 100 x 100 array for the 20,000 character stack, and the 100 x 150 array for the 30,000 character stack.

For addressing purposes, each stack is divided into 5,000 character sections referred to as sextants. The 30,000 character stack (figure 1-9) contains six sextants, the 20,000 character stack contains four sextants, and the 10,000 character stack contains two sextants.

# MEMORY CONTROL

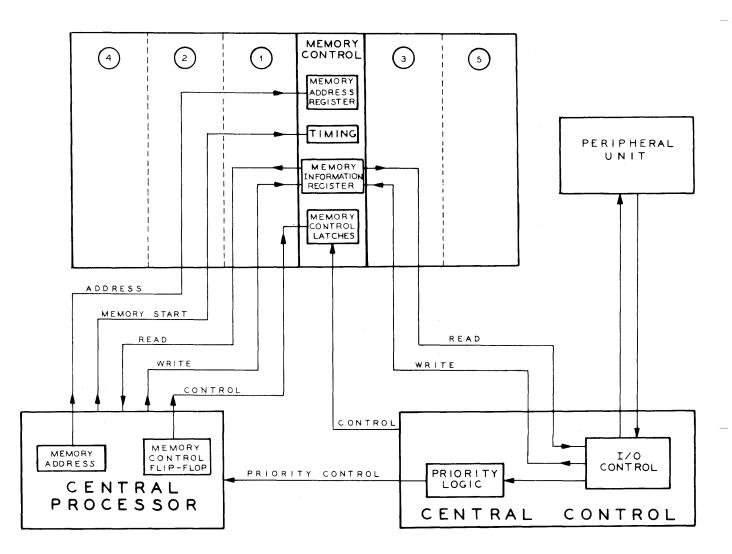

The interface between memory control, central processor and central control is shown in figure 1-10. Figure 1-11 is a detailed block diagram of the memory control logic and the interfacing of this logic to the memory stacks.

The memory cycle begins when either the central processor or an I/O channel request is granted access to memory. When the access is

Figure 1-4. Memory Block Diagram

---ω

| ٩ | 2   | Ū               | MEMORY<br>CONTROL | 3 | 5 |

|---|-----|-----------------|-------------------|---|---|

|   |     | n<br>B<br>Haine | ×1 11             |   |   |

| 2 | с ç | ~               | 2.                |   |   |

Figure 1-5. Memory Base B Cabinet Layout

Figure 1-6. Memory Base B Cabinet

granted, a series of address decoding procedures are initiated. This addressing is performed in the following sequence:

- a. Cabinet addressing.

- b. Stack addressing.

- c. Sextant addressing.

- d. Location.

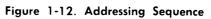

Figure 1-12 shows an exploded view of the complete memory scheme. The first breakdown is from the address in the address register (ADR), located within the central processor, into cabinet selection. Once the cabinet is located, the stack within the cabinet is determined from the address in the memory address register (MAR). Next, the proper sextant is selected and, with the last four digits in the MAR, two transformers lines are selected: one "X" and one "Y."

### **Cabinet Addressing**

Cabinet addressing is determined by the decoding of the most significant digit (MSD) of the address within the address register of the processor (ADR) when a memory access has been granted. As the access is granted to either an I/O channel or the central processor, a term called memory start (MST) is gated with the MSD in the ADR, which then sends the start level to the proper cabinet.

# Stack Addressing

Stack addressing is accomplished by gating digits 5 and 6 of the memory address register with the start stack timing level (SSTL). Since a stack can contain up to 60,000 digits, stack number one is selected when the MAR is from 000,000 up to 059,999; stack number two is selected when the MAR is from 060,000 up to 119,999, etc. The MAR values and address of stacks are as follows:

| Value of MAR                           | Addressed Stack |

|----------------------------------------|-----------------|

|                                        |                 |

| 000,000 - 059,999<br>060,000 - 119,999 | $\frac{1}{2}$   |

| 120,000 - 179,999                      | 2               |

| 120,000 - 239,999                      | 4               |

| 240,000 - 299,999                      | $\overline{5}$  |

Figure 1-7. Stack Block Diagram

#### Sextant Addressing

As previously mentioned, a sextant is a 5,000 character section of a stack with six sextants in a 30,000 character stack, four sextants in a 20,000 character stack, and two sextants in a 10,000 character stack. The sextants are designated 1 through 6, depending on the stack size, as shown in figure 1-9. Since each of the five stacks have sextants 1 through 6, there are five groups of stack addresses which could select each sextant term. The proper sextant is determined by digits 5 and 6 of the memory address register. Sextant one is selected by the term sextant 1 (SX1). This term is used to select the group of transformers that drives current through the selected sextant. Sextants 2 through 6 are selected in a similar manner by terms SX2 through SX6.

#### Location

As shown in figure 1-9, a full stack contains six sextants, with each sextant occupying a specific location within the stack. The stack is addressed by 150 "X" address lines and 100 "Y" address lines with each sextant having 50 intersecting "X" and "Y" lines.

Figure 1-8. Memory Planes

Each of these addressing lines is connected to the secondary of a transformer with a single transformer for each line. The selection of one "X" transformer and one "Y" transformer completes the coordinate addressing of a specific location.

The selection of the proper transformer is accomplished with the last four digits of the MAR and the sextant decoding described earlier. The sextant information divides the transformers into groups of 50. However, the "X" address line that intersects sextant 1 (SX1) also passes through SX3, as shown in figure 1-9. Similarly, the "X" address lines that intersect sextants 2 and 3 also pass through sextants 4 and 6, respectively. The "Y" address that intersects sextants 1 and 3 also passes through sextants 2 and 5, and 4 and 6, respectively.

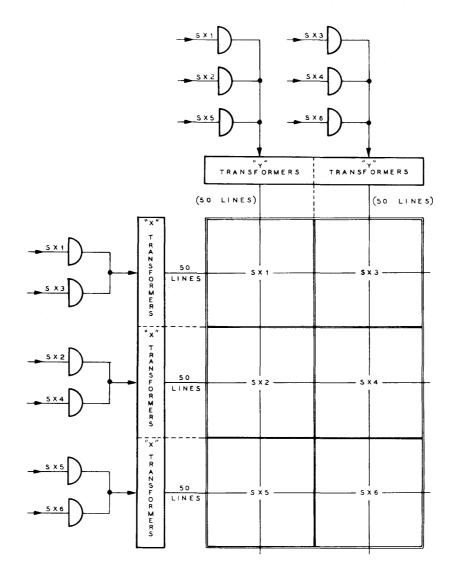

Figure 1-13 shows that if the address in the MAR selects SX1, only the group of transformers whose output lines pass through SX1 and SX3 for the "X" transformer matrix and through SX1, SX2 and SX5 for the "Y" transformer matrix are enabled. However, only SX1 experiences coordinate intersection, which means that only sextant 1 is provided with both "X" and "Y" half-current.

The summation of these two half-currents provides full current (2 times one-half), which is required to fully change the state of the core. The other sextants included with the transformers that intersect SX1 only receive half of the required current, either from the "X" or "Y" transformer matrix.

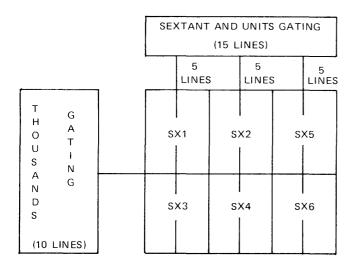

The transformers are selected by the intersection of two address decoding lines. The "X" address lines are decoded from sextant MAR thousands and MAR units gating, whereas the "Y" address lines are decoded from the sextant, MAR hundreds, and MAR tens. Refer to figure 1-14. One group of address decoding lines is composed of the thousands position, digit 4 of MAR. Since digit 4 can contain ten different configurations (0 through 9), it is decoded into ten different address decoding lines directly from the binary count in the MAR digit 4 position. These lines are designated K0, K1, K2 through K9.

The other group of 15 lines is composed of the unit sextant gating. The "X" transformers must address through different pairs of sextants.

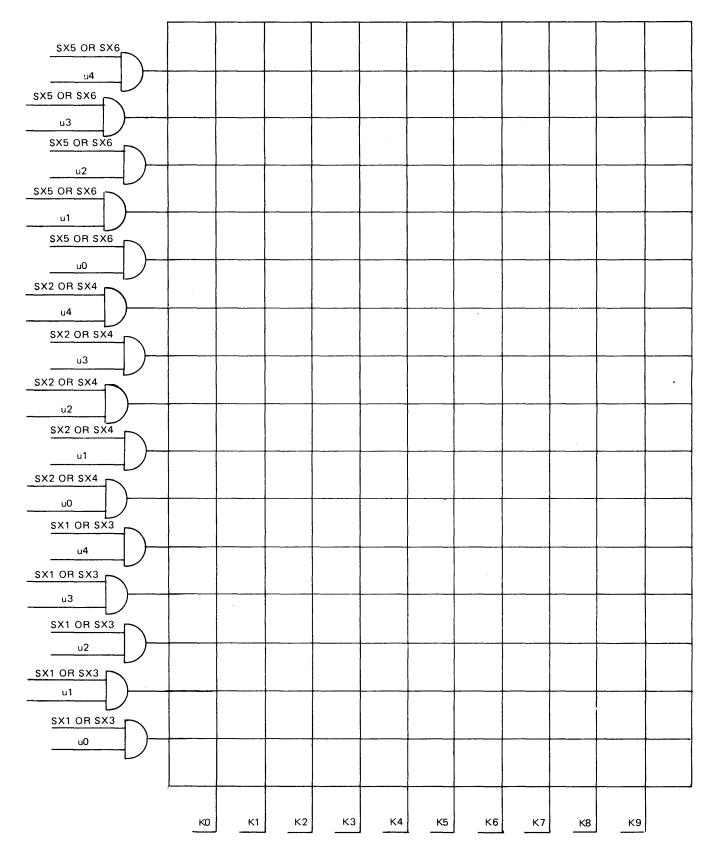

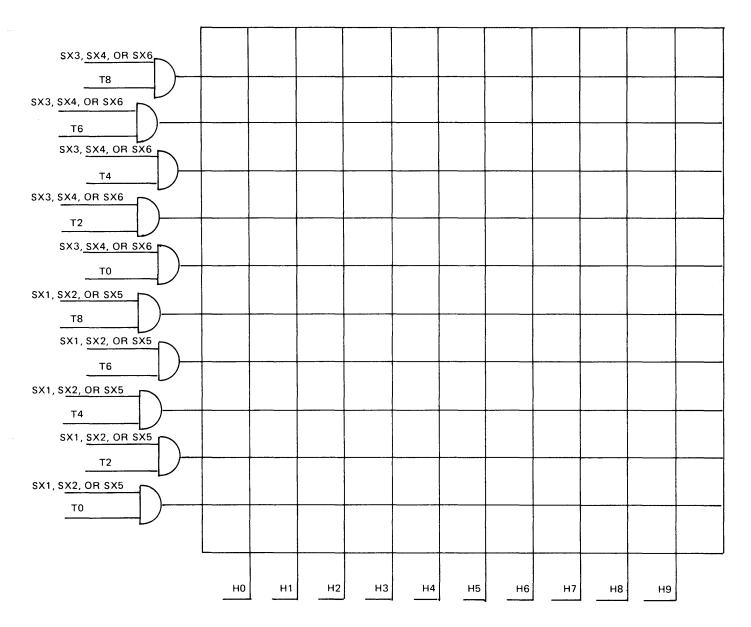

These five unit terms U0 through U5, combined with the three sextant terms, gates the group of 15 lines to the transformer matrix. A complete block diagram of these lines and associated gating is shown in figure 1-15. At the point of intersection of the decoding lines, a transformer is selected. Only one horizontal line and one vertical line can be enabled during a memory access; therefore, only one transformer is enabled. This drives current through one "X" address line of the core stack.

The selection of the "Y" transformer is accomplished in the same identical manner as the selection of the "X" transformer. The "Y" transformers are arranged in a 10 x 10 array, as shown in figure 1-16. This array is addressed by two groups of ten lines. One group of ten lines is decoded from the hundreds position (digit 3 of the MAR), while the other group of ten lines is decoded from the even tens position (digit 2 of the MAR) and the sextant gating.

Figure 1-9. Address Lines Through Sextants

The tens and units positions of MAR can describe 100 different digit addresses. There are five word addresses in each 20 consecutive digit addresses starting with 000,000.

The first word of each 20 addresses contains an even digit (MAR tens equal to 0, 2, 4, 6 and 8). The odd MAR digits have a value of 0 through 3 for any digit address in the first word. The address of any digit in the first word is designated by the term U0.

The second word of each 20 addresses contains an even (MAR 2, and MAR 1) digit value of 4 through 7. The term for this decoding is U1.

The three remaining unit terms (2 through 5) are decoded in the same manner, generating the terms U2 through U4.

The hundreds lines are decoded from the binary count in the hundreds position of the MAR. This count can be from 0 through 9, with each count being designated H0 through H9.

The output of the "Y" transformers passes through two groups of three sextants, as shown in figure 1-9. These groups form the terms SX1, SX2, or SX5 and SX3, SX4, or SX6, with each gate having five even tens terms to achieve the ten gating lines to the matrix. The even tens terms are decoded directly from the ten positions of MAR minus the one bit used in the units gating. The terms T0, T2, T4, T6 and T8 are derived from this count. Refer to figure 1-9. Addressing is now complete. (The transformers drive the address lines which select one specific location which contains one word or four digits, plus a parity bit. Examples of address breakdown are given in table 1-1.

Figure 1-10. Memory Control Interface

| Table 1-1. Examples of Address Breakdow |

|-----------------------------------------|

|-----------------------------------------|

| Address<br>in ADR | Cabinet<br>Location | Address<br>in MAR | Stack<br>Location | Sextant<br>Location |    | MAR<br>Digit 3<br>(Hundreds<br>Term) | MAR<br>Digit 2<br>(Tens<br>Terms) | Unit<br>Term |

|-------------------|---------------------|-------------------|-------------------|---------------------|----|--------------------------------------|-----------------------------------|--------------|

| 183620            | 1                   | 183620            | 4                 | 1                   | K3 | H6                                   | T2                                | U0           |

| 382195            | 2                   | 082195            | 2                 | 3                   | K2 | H1                                   | T8                                | U3           |

| 491835            | 2                   | 191835            | 4                 | 2                   | K1 | H8                                   | T2                                | U3           |

| 604171            | 3                   | 004171            | 1                 | 1                   | K4 | H1                                   | <b>T</b> 6                        | U2           |

| 895952            | 3                   | 295952            | 5                 | 6                   | K5 | H9                                   | T4                                | U3           |

| 962111            | 4                   | 062111            | 2                 | 1                   | K2 | H1                                   | <b>T</b> 0                        | U2           |

Figure 1-11. Memory Control/Stack Interface

Figure 1-13. Sextant Gating of Transformers

Figure 1-14. 15 x 10 "X" Transfer Array

#### PARITY

The memory system operates with odd parity. This stipulates that an odd number of bits is set for each word location. That is, if a word is placed in the memory information register (MIR), which contains an even number of bits set, the parity bit must also be set at the time the word is written. If the word within the MIR contains an odd number of bits, the parity bit need not be utilized.

#### MEMORY TIMING

The memory cycle is one microsecond in duration. Logic generated within the central control, and which is then called to memory, synchronizes timing pulses between memory, the central control, and the central processor. The time duration between clock pulses is 560 nanoseconds.

Memory timing is generated in both memory control and the stack. When a memory cycle is required by the central processor or an I/Ochannel, the central processor triggers the timing circuits located within memory control. The appropriate stack is selected by address decoding and its timing circuits enabled by a Start Stack Level (SnSL). This logic produces timing pulses required to control the stack function.

#### STACK TIMING

The timing generated by the stack timing logic is used to control the sequence of operations that causes read and write current to flow within the stack.

#### READ OPERATION

The address to be used during the read operation is received from the address register within the central processor and is stored in the memory address register (MAR). The MAR is decoded by the stack decoding logic and gated to produce one of five SnSL levels. This level, in turn, determines the stack to be used. The MAR is also utilized by the address and sextant decoding logic to determine the location within the stack that is to be utilized. This information is gated to all stacks within the memory cabinet, but it is usable only in the stack receiving the SnSL level. After the stack is triggered by SnSL, the output from the sense amplifiers is sent to the memory information register (MIR). The sense amplifier senses the status of the cores within the stack. The type of operation to be performed is stored in the mempry control latches (MCL), which is then decoded and controls the input to the MIR. In the case of a read operation, the outputs from the sense amplifiers are gated to the MIR where they are then sent to the central control or central processor for usage.

#### WRITE OPERATION

For a write operation, the logic utilized for the read operation is valid, except that the MCL now contains codes for a write operation. The outputs of the sense amplifiers are inhibited and only the new information from the central control or central processor is latched in the MIR. The inhibit gating, in turn, controls the writing of the information within the MIR into a memory location addressed by the MAR.

Figure 1-16. "Y" Transformer Decoding Lines

# SECTION 2

#### GENERAL

The Central Processors contain the circuitry and logic required to perform the instruction set utilized by their associated systems. These instruction sets are capable of performing operations on digit-, byte-, or word-formatted data fields. The internal working code utilized by the central processors is 8-bit EBCDIC or 8-bit USASCII, both of which are programmatically selectable. Integrated into the hardware is an automatic interrupt system capable of informing the processor of any condition experienced by any portion of the system.

The B 2500/B 3500 and the B 2700 Central Processor speeds are as follows:

| Model                                                       | Processor<br>Speed |

|-------------------------------------------------------------|--------------------|

| B 2510/B 2520                                               | 0.5 MHz            |

| B 2731                                                      | 0.67 MHz           |

| B 2501/B 2502/B 2741/B 2761/<br>B 2540/B 2765               | 1.0 MHz            |

| B 2751/B 2771/B 2772/B 3501/<br>B 3506/B 3508/B 3510/B 3514 | 2.0 MHz            |

#### PROCESSOR OPERATING MODES

The Central Processors can operate in one of four modes: control state, zero base; control state, non-zero base; normal state, zero base; and normal state, non-zero base.

#### Control State, Zero Base

In this mode, the interrupt flip-flop can be set, but the interrupt branch is not executed until the return to normal state. Any privileged instructions are allowed.

#### Control State, Non-Zero Base

In this mode, the interrupt flip-flop can be set, but the interrupt branch is not executed until the return to normal state. Any privileged instructions are disallowed.

#### Normal State, Zero Base

In this mode, the interrupt branch is allowed to be executed and privileged instructions are allowed.

#### Normal State, Non-Zero Base

In this mode, the interrupt branch is allowed to be executed and privileged instructions are disallowed.

Object program, assemblers, compilers, and generators are executed in the normal state, non-zero base, whereas the greater majority of the Master Control Program (MCP) is executed in the control state, zero base. A small number of privileged instructions, used exclusively by the MCP, can be executed only in zero base. These priviledged instructions include operations such as initiate output and read timer.

#### LOGICAL UNITS

There are several logical units contained within the central processor that directly or indirectly affect its operation. These logical units control the execution of specific instructions and are, themselves, set or changed by other instructions.

#### **OVERFLOW** Flip-Flop

The OVERFLOW flip-flop is a hardware logical unit that indicates the data field of a move or arithmetic instruction is exceeded. If an overflow condition is detected, the command is executed but the data is not affected. The OVERFLOW flip-flop is not cleared at the beginning of an arithmetic operation but is preserved; therefore, it indicates overflow that has occurred any time before or during a series of arithmetic operations or other interjected nonarithmetic operations. Instructions that can create an overflow condition are:

- a. Arithmetic instructions except multiply.

- b. Floating point arithmetic instructions.

- c. Move Numeric.

- d. Move Alphanumeric.

Overflow cannot occur during a multiply instruction, since the receiving field is always large enough to contain the product. In all cases except the floating point instructions, overflow results when the receiving field cannot contain the sending field. With floating point instructions, the overflow can also be caused by an out-of-range exponent. The OVERFLOW flipflop is reset by the Branch-On-Overflow instruction. Once cleared, it can be set if the conditions arise while executing those instructions that may cause it to be set. There are two ways in which the present setting of the OVERFLOW flip-flop may be stored in the four-bits of reserved address memory and then cleared, as shown below.

- a. Branch Communicate.

- b. Automatic interrupt feature.

The OVERFLOW flip-flop is restored from the reserved memory location by the Branch Reinstate instruction. In addition, the object program may branch to some subroutine and the OVERFLOW flip-flop setting must be retained and restored at the conclusion of the subroutine execution, prior to continuing in the object program. The Enter instruction stores the flip-flop setting into the four bits of the reserved character location in the memory stack, and then clears the OVERFLOW flip-flop. The Exit instruction restores the OVERFLOW flipflop setting from this reserved location.

#### **COMPARISON Flip-Flops**

Two hardware flip-flops make up the comparison logical unit. These two flip-flops have the following four combinations (0 = reset, 1 = set):

- a. 00 cleared.

- b. 01 greater or high comparison result.

- c. 10 less or low comparison result.

- d. 11 zero or equal comparison result.

These four states represent the result of executing an instruction that affects these logical units. The cleared state actually indicates that there is no comparison result existing. The instructions that set a result into the COMPARISON flip-flops and are reflected on the appropriate console indicators are as follows:

- a. All arithmetic instructions.

- b. All floating point instructions.

- c. Compare instructions.

- d. Move Numeric instruction.

- e. Move Alphanumeric instruction.

- f. The bit test instruction.

- g. The logical instructions.

- h. The scan instructions.

- i. The Edit instruction.

- j. The Scan Result Descriptor instruction.

- k. Search instruction.

Any branching that is done on the basis of the comparison will not change the status of the flip-flops. Only another instruction that affects them can change their status. When entering control state by means of the Branch Communicate instruction or the automatic interrupt system, the status of the comparison flip-flops is stored. The 2-bit and 1-bit of the same character that stores the OVERFLOW flip-flop status will contain the status of the COMPARISON flip-flops. The flip-flops are then cleared before branching to control state. When return is made to the normal state, the Branch Reinstate instruction will restore the comparison flipflops from the character in reserved address memory. Similarly, when entering a subroutine, the Enter instruction stores the COMPAR-ISON flip-flops in the 2-bit and 1-bit of the specified character in the memory stack. This same character contains the OVERFLOW flipflops status. When leaving the subroutine with the Exit instruction, the COMPARISON flipflops are restored from this character in the stack.

#### EBCDIC/USASCII Mode Flip-Flop

This flip-flop determines whether the processor is operating on EBCDIC or USASCII internally coded data. The reset state of the flip-flop indicates that the processor is using the EBCDIC code. The flip-flop can be programmatically set to indicate that the processor is to use USASCII code. The Set Mode instruction sets or resets this flip-flop, as desired by the programmer. The following instructions are sensitive to the setting of the EBCDIC/USASCII mode flipflop:

a. All Arithmetic instructions.

b. All Floating Point instructions.

c. Move Numeric instruction.

d. Move Alphanumeric instruction.

e. Move Repeat instruction.

f. Translate instruction.

g. Scan Delimiter Equal instruction.

h. Scan Delimiter Unequal instruction.

i. Edit instruction.

When branching to the control state, the setting of the EBCDIC/USASCII MODE flip-flop is also stored in the 8-bit of the same character containing the settings of the OVERFLOW and COMPARISON flip-flops. It is then cleared prior to entering the control state. This is done by either of the following instructions:

a. Branch Communicate.

b. Automatic interrupt branch.

When returning to normal state, the Branch Reinstate instruction will restore the EBCDIC/ USASCII mode flip-flop from the character in reserved address memory. When entering a subroutine, the Enter instruction will store the status of the MODE flip-flop in the 8-bit of the specific character in the stack which also contains the OVERFLOW and COMPARISON flipflop settings. The Exit instruction will restore the EBCDIC/USASCII MODE flip-flop from the character in the stack when leaving the subroutine. This is necessary in the event that the flip-flop is changed by the subroutine. The special character in reserved memory or the stack contains the setting of the EBCDIC/USASCII mode flip-flop in the 8-bit, the setting of the OVERFLOW flip-flop in the 4-bit, and the settings of the COMPARISON flip-flops in the 2bit and 1-bit.

#### INTERRUPT Flip-Flop

The INTERRUPT flip-flop is a hardware logical unit that indicates the presence of an interrupt. This flip-flop controls the automatic interrupt circuitry when the processor is operating in normal state. If the flip-flop is reset (no interrupt condition), execution continues in sequence from instruction to instruction. If an interrupt occurs, the flip-flop is set. If the flip-flop is set at the completion of an instruction execution cycle, the automatic interrupt branch to control state, base zero occurs. The flip-flop is set by the detection of any I/O complete interrupt. The Scan Result Descriptor instruction will reset the INTERRUPT flip-flop while executing the interrupt handling routine.

#### Normal/Control State Flip-Flop

This flip-flop can be set only by the Branch Reinstate instruction which is executed by the Operating System. It is reset by either the Branch Communicate instruction or the automatic interrupt branch. When the flip-flop is set, the processor is operating in the control state which inhibits the automatic interrupt circuitry.

The setting of this flip-flop dictates the state of operation of the processor. When it is set, the processor is operating in normal state and allows the execution of the automatic interrupt branching.

#### Timer

The timer consists of two words in address memory. The first timer word is counted at a one KiloHertz rate. This word is compared with the value of the second word which is placed there by the Operating System. When the first word is equal to or greater than the second word, a clock interrupt occurs. The timer will continue to count after the interrupt and requires the Operating System to read and clear the first word of the timer. The value read from the timer word is used by the Operating System for logging functions and updating the realtime clock.

#### **Base Register**

The base register in the processor is a three-digit register. These three digits are always added to the two high-order digits of the five-digit program and instruction address to form a sixdigit absolute address. This makes the base register modulo 1000, that is, a base register value of 137 is actually 137,000. This base register value is always added to the base relative address contained in the instructions. This computation takes place during the fetch cycle, prior to storing the absolute address generated into address memory. For any program, the base register value is created by the Operating System and stored in reserved memory location 000070 (table 2-1) prior to initiating the program. When the Branch Reinstate instruction is executed, the base register is set to the value contained in reserved memory, establishing the base register of the normal state program. If a Branch Communicate instruction or an automatic interrupt branch is executed, the base register value is stored in the reserved address memory location prior to entering control state and the base register is also cleared to zero.

#### Limit Register

The limit register within the processor is a three-digit register. The purpose of the limit register is to provide memory protection. Memory protection is accomplished by comparing the high-order three digits of the absolute address generated for instructions with the base and limit registers. The base register provides the lower limit and the limit register provides the upper limit. The value of the limit register is provided by the Operating System and stored in reserved memory location 000073. The Branch Reinstate instruction sets the limit register to the value contained in reserved memory. When the Branch Communicate instruction or automatic interrupt branch is executed, the limit register value is stored in reserved memory prior to entering control state and the limit register is set to the system memory size. This allows the Operating System to access all memory.

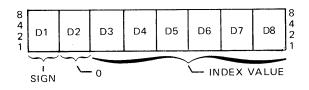

#### Index Registers

The index registers used in the processors are not hardware registers as are the base and limit registers. Three index registers are contained in reserved locations of an object program and are always assigned the same base relative address. The format of the index register is shown in figure 2-1.

Figure 2-1. Index Register Format

Each index register consists of eight digit positions. The most significant digit (D1) is the sign of the index value. The second digit position is not used when indexing. The value of the index is the decimal value contained in the remaining six digit positions (D3 through D8). If an instruction address specifies indexing, the value of the specified index register is added algebraically to the base register, plus the base relative address prior to storing the generated address in address memory. The index register value can be changed by any instruction that addresses memory. In addition, the Enter and Exit instructions use and alter the setting of Index Register 3 (IX3); however, the settings are saved and restored. In the zero-base state, the Scan Result Descriptor instruction and the Search instruction use IX1 in their execution.

#### DATA MODES

Two data modes are utilized in the Processors to represent internal data: the 4-bit mode and the 8-bit mode.

#### Four-Bit Mode

In the 4-bit mode, data is interpreted in units of 4-bits and, where a sign is expected, the sign is interpreted as a separate and leading 4-bit unit. The internal code in 4-bit mode is interpreted by the arithmetic unit in the processor as follows:

| Binary<br>Code | Sign Code                  | Decimal<br>Equivalent       |

|----------------|----------------------------|-----------------------------|

| 0000           | +                          | 0                           |

| 0001           | +                          | 1                           |

| 0010           | +                          | 2                           |

| 0011           | +                          | 3                           |

| 0100           | +                          | 4                           |

| 0101           | +                          | 5                           |

| 0110           | +                          | 6                           |

| 0111           | +                          | 7                           |

| 1000           | +                          | 8                           |

| 1001           | +                          | 9                           |

| 1010           | +                          | $\mathcal{N}$ (undigit 0) * |

| 1011           | +                          | arrow (undigit 1) *         |

| 1100           | +                          | $\mathcal{Z}$ (undigit 2) * |

| 1101           | -                          | X (undigit 3) *             |

| 1110           | +                          | $\mathcal{A}$ (undigit 4) * |

| 1111           | +                          | $\mathcal{F}$ (undigit 5) * |

| *              | These units<br>accepted by | the                         |

accepted by the arithmetic unit but they will result in unspecified results.

When a signal 4-bit format is specified in the receiving field for any operation, a plus sign compares higher than a minus sign in the system's collating sequence, as shown below:

| USASCII Code | EBCDIC Code |

|--------------|-------------|

| + = 1011     | + = 1100    |

| - = 1101     | - = 1101    |

#### Eight-Bit Mode

In an 8-bit mode, data is interpreted in units of 8-bits (one byte). Any required conversion between 4-bit and 8-bit mode is accomplished automatically during the execution of instructions with no timing costs absorbed by the program being operated. For code sensitive instructions including the manipulation of 4-bit numeric data, the most significant fours bits of a 2-byte receiving field are automatically set to the code indicating the numeric subset of the selected 8-bit code. The four bits are 1111 (undigit 5) in EBCDIC code and 0101 (binary 5) is USASCII code.

Except in the move alphanumeric, move numeric and edit instructions, 8-bit data is considered unsigned.

Alphanumeric comparisons are performed in binary code. The collating sequence for EBCDIC code is special characters, alphabetical characters, and then digits. The collating sequence for USASCII is special characters, digits, and then alphabetical characters.

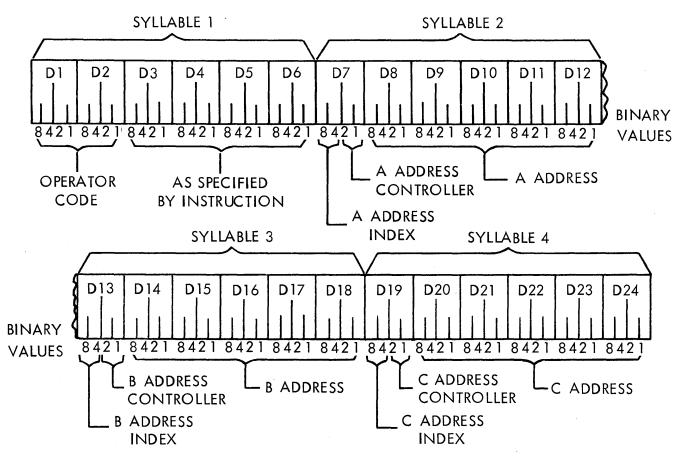

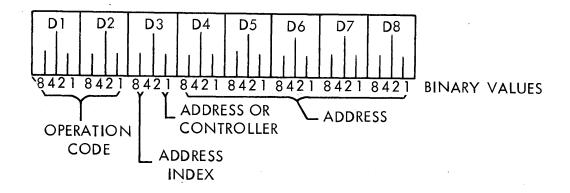

#### INSTRUCTION FORMAT

The two instruction formats used by the processors are format A, which is variable in length from one to four syllables, or format B, which is a fixed length of eight digits. Most instructions consist of from one to four syllables, depending on the particular instruction. An instruction syllable consists of six digits as shown in figure 2-2.

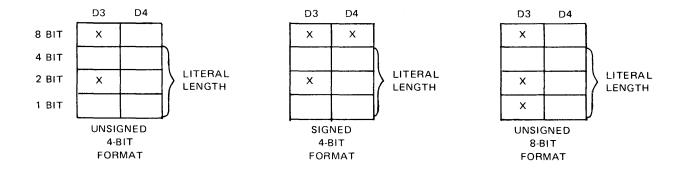

The first syllable of every instruction contains the operation code in digits D1 and D2. Digit positions D3 through D6 have various functions as specified by each instruction. Generally, D3 and D4 specify the length of the A field, whereas D5 and D6 specify the length of the B field. Several instructions consist of a single syllable. In multiple syllable instructions, the second, third, and fourth syllables are the A field, B field, and C field addresses, respectively. The addresses always address the most significant digit of the field. Digits D7, D13, and D19 specify various control functions with respect to the A, B, and C field addresses, respectively. The two address-index bits determine which index register, if specified, to use in generating the absolute address. The two address-controller bits specify whether signed or unsigned 4bit or 8-bit formatted information is in the data field. The address controller bits may also specify indirect addressing. Digits D3 and D4 of the first syllable can specify that the second syllable (D7 through D12) is a literal value and not an address. The format of the literal is given in digits D3 and D4.

Figure 2-2. Six-Digit Instruction Format

The 8-digit format is used only when an operation code and address are necessary, such as in a Branch instruction. The 8-digit instruction format is shown in figure 2-3.

#### **Address Index**

The two most significant bits (8 and 4) of the first digit in the address field is the address index control. The bit configuration of the address

index signifies which of three index registers is to be used while generating an absolute address. The eight-bit and four-bit configuration is as follows:

- a. 00 no indexing.

- b. 01 index register 1 (IX1).

- c. 10 index register 2 (IX2).

- d. 11 index register 3 (IX3).

#### Figure 2-3. Eight-Digit Instruction Format

There is an address index controller for the A, B, and C address fields, and also for the address field of the eight-digit instruction. If indexing is specified, the designated index register value contained in reserved locations within an object program is added algebraically to the address field and base register during the fetch cycle, prior to storage in its reserved address memory location.

#### Address Controller

The two low-order bits (2 and 1) of the first digit in the address field specify the data field format. The address controller bits and address index bits comprise the entire first-digit position of the address field. Four different two-bit and one-bit combinations can be specified by the two address controller bits as follows:

| a. 00 — unsigned four-bit<br>format.  | Most signifi-                                                |

|---------------------------------------|--------------------------------------------------------------|

| b. 01 — signed four-bit<br>format.    | Most signifi-<br>cant address<br>digit for the<br>branch in- |

| c. 10 — unsigned eight-bit<br>format. | structions                                                   |

d. 11 — indirect address.

Any combination may be used except where prohibited by a specific instruction. The unsigned 4-bit format means that the data field consists of digits of information without a sign digit. The signed four-bit format specifies a digit data field with a sign digit preceding the most significant digit of the field. The field length does not include the sign digit position when a signed data field is specified. A bit configuration of 1101 is always treated as a minus sign (-), whereas any other bit configuration is considered as a plus sign (+). The unsigned eight-bit (character/byte) format specifies that the data field is in an internal eight-bit alphanumeric code. The indirect address bit configuration specifies that the data field address is located at the specified base relative location. During the fetch cycle, another access must be made to obtain the specified field address.

An indirect address must be even and is checked after indexing, if any. An odd indirect address is considered to be a non-synchronized address contained in an instruction and causes a processor interrupt.

#### **Address Digits**

Since the first digit of the address field comprises the address index and controller bits, five digits remain for use as the data field address; however, addresses may generate beyond this seemingly maximum address of 099,999 by utilizing the address controller bits at binary values up to a 2, thus creating an actual maximum address range per program of 000000 to 299,999. Programs exceeding the address of 099,999 cannot contain referenced data areas in excess of the 099,999 address. This address is always base relative and is added to the base register value during the fetch cycle. The absolute address stored in address memory is comprised of the value in the address field added to the base register. It can also be indexed by an index register when specified. The address digits are limited to the decimal digits zero through nine, thus creating a completely decimal addressing scheme for a beneficial system/programmer/ operator interface.

#### **Operator Code**

The first two digits of the first syllable represent the operator code. This operator code is a decimal value ranging from 00 through 99, but all values are not used. All unassigned codes are reserved for expansion. If the processor receives any operator code that has not been assigned, an invalid instruction interrupt is generated. The operator code itself determines the number of syllables that must be fetched.

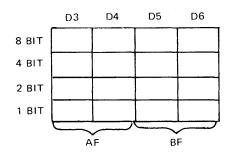

#### Field Length

For a majority of the instructions, the third, fourth, fifth, and sixth digits (D3 through D6) of the first syllable control the field lengths of the data fields (see figure 2-4). Digits D3 and D4 determine the A field length (AF), whereas digits D5 and D6 determine the B field length (BF).

The field length values can range between 00 and 99, inclusively. If a field length of 00 is specified, the field length is 100. The digits D3 and D5 may also specify an indirect field length. This is accomplished by making the D3/ D5 8-bit and 4-bit both equal to a 1. The base relative indirect address of the field length is obtained from the two low-order bits of D3/D5 and the even values of the D4/D6 digit. Thus, the indirect field-length base relative address can be any even value from 00 through 38 for a total of 20 base relative addresses.

Figure 2-4. Field Length Digits

#### **Literal Specifications**

Some of the instructions allow the A field length digits to specify that the A address syllble contains a literal value and not the address of a data field. Figure 2-5 shows the bit configuration for the various literals that the A address syllable can contain.

When D3 has the 8-bit and 2-bit ON with the 4-bit OFF, the A address is a literal. The D3 1-bit and D4 8-bit specify the format of the literal. When the literal specification is an unsigned four-bit format, the literal length can be one through six — the total number of digits in the address field. When the signed four-bit format is specified, the literal length can be one through five since the most significant digit is the sign digit.

When the eight-bit format is specified, the literal length can have a value of one through three. If the literal length is less than the maximum length for the specified format, the literal is always assumed to be left-justified.

#### **Read-Only Memory**

The read-only memory (ROM) within the processor is a resistive-type of storage. It contains a set of microprograms that controls most of the actions taken by the processor. The microprograms are initiated by the operation codes of program instructions after they are fetched from memory. The microprograms utilize the addresses stored in address memory during the execution of the instruction.

#### HARDWARE INSTRUCTIONS

The following list is a composite of all mnemonic operation codes used by the systems processor. Assemblage of this list is only by general classification of the individual codes.

Each operation code will be broken down into its associated descriptor.

#### **Data Movement Operation Codes**

The following operator codes are utilized to manipulate data to and from different areas within the system.

Figure 2-5. Literal Specification Control

#### MOVE ALPHANUMERIC (MVA)

OP

The number of syllables is equal to two. The descriptor for the MVA operation is shown below:

| Code | AF                      | BF                                | A Address                | B Address                          |

|------|-------------------------|-----------------------------------|--------------------------|------------------------------------|

| 10   | Length of<br>data field | Length of<br>destination<br>field | Address of<br>data field | Address of<br>destination<br>field |

This instruction moves digits or characters from the A field (AF) and stores them at the location specified by the B address. The count in AF and BF specifies the length of the A and B fields, respectively. Up to 100 digits or characters may be moved, with the one-hundredth character specified by the count 00 in either length field.

#### MOVE NUMERIC (MVN)

The number of syllables is equal to two. The descriptor for the MVN operation is shown below:

| Code | AF                      | BF                                | A Address                | B Address                          |

|------|-------------------------|-----------------------------------|--------------------------|------------------------------------|

| 11   | Length of<br>data field | Length of<br>destination<br>field | Address of<br>data field | Address of<br>destination<br>field |

This instruction moves digits or the numeric portion of characters from a location specified by the A address to a location specified by the B address. The value within AF specifies the number of digits to be moved. The length of the destination field is contained in BF.

#### MOVE REPEAT (MVR)

The number of syllables is equal to two. The descriptor for the MVR operation is shown below:

| OP<br>Code | AF                           | BF                                                                     | A Address                                                           | B Address                                                       |

|------------|------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|

| 14         | Length of<br>A field<br>data | Number of<br>times that<br>data is to<br>be moved<br>to the B<br>field | Most<br>significant<br>digit<br>(MSD) of<br>the data to<br>be moved | Most<br>significant<br>digit<br>(MSD) of<br>the result<br>field |

This instruction moves data from a location specified by the A address to a location specified by the B address. AF contains the number of digits or characters in the A field. BF specifies the number of times the entire A field is to be moved to the B field. The length of the B field is the product of AF times BF.

#### MOVE WORDS (MVW)

The number of syllables is equal to two. The descriptor for the MVW operation is shown below:

| Code | AF                                | $\mathbf{BF}$ | A Address                         | B Address                          |

|------|-----------------------------------|---------------|-----------------------------------|------------------------------------|

| 12   | Number of<br>words to<br>be moved |               | Address of<br>data to be<br>moved | Address of<br>designation<br>field |

This instruction moves words from a location specified by the A address and stores them in a location specified by the B address. At the completion of the instruction, both the A and B fields (AF and BF) contain identical information.

#### MOVE WORDS AND CLEAR (MVC)

The number of syllables is equal to two. This descriptor is identical to that of the MVW operation, except for the following:

a. The OP code is equal to 13.

b. Zeros are written into the A location after each word has been moved.

#### MOVE LINKS (MVL)

The number of syllables is equal to three. The descriptor for the MVL operation is shown below:

| OP<br>Code | AF                                            | BF     | A<br>Address | B<br>Address | C<br>Address |

|------------|-----------------------------------------------|--------|--------------|--------------|--------------|

| 09         | Length of<br>all fields<br>(1 through<br>100) | Unused | Inst         | ruction A    | ddressed     |

This instruction is comprised of four syllables: the OP code, the AF variant, the BF variants, and three addresses. The AF variant specifies allowable data field lengths. These lengths are from 1 to 100 digits or characters. The final address controllers for all three addresses must be alike and can indicate unsigned numeric, signed numeric, or unsigned alpha information.

During the execution of this instruction, the processor ignores the A and B controllers and uses the C controller to control all of the information fields.

#### **Arithmetic Operation Codes**

The following operator codes are utilized to perform arithmetic calculations.

#### TWO ADDRESS ADD (INC)

The number of syllables is equal to two. The descriptor for the INC operation is shown below:

| OP<br>Code | AF                     | BF                  | A<br>Address                             | B<br>Address                             | C<br>Address                     |

|------------|------------------------|---------------------|------------------------------------------|------------------------------------------|----------------------------------|

| 01         | "A"<br>field<br>length | "B" field<br>length | Address<br>of addend<br>or<br>subtrahend | Address<br>of<br>augend<br>or<br>minuend | Address<br>of<br>result<br>field |

This instruction algebraically adds the contents of the A field to the contents of the B field. The sum is stored in the B address.

#### THREE ADDRESS ADD (ADD)

The number of syllables equals three. The ADD instruction is identical to the two address add instruction except for the following:

- a. The OP code is equal to 02.

- b. The sum is stored in the C address.

#### TWO ADDRESS SUBTRACT (DEC)

The number of syllables equals two. The DEC instruction is identical to the two address add instruction except for the following:

- a. The OP code is equal to 03.

- b. The difference is stored in the B address.

#### THREE ADDRESS SUBTRACT (SUB)

The number of syllables equals three. The SUB instruction is identical to the two address add instruction except for the following:

a. The OP code is equal to 04.

b. The difference is stored in the C address.

#### MULTIPLY (MPY)

The number of syllables equals three. The descriptor for the MPY operation is shown below:

| OP<br>Code | AF                     | BF                  | A<br>Address                | B<br>Address                  | C<br>Address             |

|------------|------------------------|---------------------|-----------------------------|-------------------------------|--------------------------|

| 05         | "A"<br>field<br>length | "B" field<br>length | Address<br>of<br>multiplier | Address<br>of<br>multiplicand | Address<br>of<br>product |

This instruction algebraically multiplies the multiplicand specified by the B address by the multiplier specified by the A address and places the product into the address specified by C.

AF and BF in this instruction specify the length of the A field and B field, respectively. These fields may specify from 1 to 100 digits, with the value of 00 representing a length of 100. The length of the C field will be the sum of AF and BF.

#### DIVIDE (DIV)

The number of syllables equals three. The descriptor for the DIV operation is shown below:

| OP<br>Code | AF                | BF                | A<br>Address          | B<br>Address                                 | C<br>Address              |

|------------|-------------------|-------------------|-----------------------|----------------------------------------------|---------------------------|

| 06         | A field<br>length | B field<br>length | Address<br>of divisor | Address<br>of<br>dividend<br>or<br>remainder | Address<br>of<br>quotient |

This instruction algebraically divides the contents of the B field by the contents of the A field and places the quotient in the C field. Any remainder as a result of the division will be found in the B field.

#### Floating Point Arithmetic Operation Codes

The following operation codes enhance the arithmetics of the system by allowing floating-point operation.

#### FLOATING POINT ADD (FAD)

The number of syllables is equal to three. The descriptor for the FAD operation is shown below:

| OP<br>Code | AF   | BF                                                       | A<br>Address          | B<br>Address             | C<br>Address             |

|------------|------|----------------------------------------------------------|-----------------------|--------------------------|--------------------------|

| 80         | (not | Length<br>of B<br>mantissa<br>(not<br>including<br>sign) | Address<br>of A field | Address<br>of B<br>field | Address<br>of C<br>field |

In floating point addition, the exponents of A and B must be made equal before algebraically adding the mantissa. Equalizing the exponents is accomplished by incrementing or decrementing the exponents of A or B addresses, while effectively shifting the decimal point in the mantissa.

#### FLOATING POINT SUBTRACT (FSU)

The number of syllables equals three. The descriptor for the FSU operation is identical to that of the floating point add operation, except that the OP code is equal to 81.

#### FLOATING POINT MULTIPLY (FMP)

The number of syllables equals three. The descriptor for the FMP operation is shown below:

| OP<br>Code | AF                                                       | BF                                                       | A<br>Address                | B<br>Address                       | C<br>Address             |

|------------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------|------------------------------------|--------------------------|

| 82         | Length<br>of A<br>mantissa<br>(not<br>including<br>sign) | Length<br>of B<br>mantissa<br>(not<br>including<br>sign) | Address<br>of<br>multiplier | Address<br>of<br>multipli-<br>cand | Address<br>of<br>product |

This instruction algebraically multiplies the contents of the B address by the contents of the A address and places the product into the location specified by the C address.

#### FLOATING POINT DIVIDE (FDV)

The number of syllables equals three. The descriptor for the FDV operation is shown below: