# B 1700

# FIELD CARD TESTER

INTRODUCTION AND OPERATION

FUNCTIONAL DETAIL

# Burroughs

FIELD ENGINEERING

# TECHNICAL MANUAL

#### FIELD ENGINEERING PROPRIETARY DATA

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown, or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished for Burroughs Field Engineering Personnel, and is not furnished to customers except under spocial License Agreement.

THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

CIRCUIT DETAIL

**ADJUSTMENTS**

MAINTENANCE PROCEDURES

INSTALLATIO

RELIABILITY IMPROVEMENT NOTICES

OPTIONAL FEATURES

# LIST OF EFFECTIVE PAGES

NOTE: Insert latest changed page; dispose of superseded pages.

#### TOTAL NUMBER OF PAGES IN THIS MANUAL IS 64 CONSISTING OF THE FOLLOWING:

| Page | No. |

|------|-----|

|      |     |

Issue

| Title           | Original |

|-----------------|----------|

| A               | Original |

| i thru iv       | Original |

| 1-1 thru $1-22$ | Original |

| 2–1 thru 2–19   | Original |

| 2–20 Blank      | Original |

| 3–1 thru 3–6    | Original |

| 5–1 thru 5–10   | Original |

A PAGE

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

# TABLE OF CONTENTS

| Section |                                      | Page       |

|---------|--------------------------------------|------------|

| 1       | INTRODUCTION AND OPERATION           |            |

|         | General Information                  | 1-1        |

|         | Maintenance Philosophy               | 1-1        |

|         | Memory Cards                         | 1 - 1      |

|         | Field Card Tester                    | 1 - 1      |

|         | Logic Power                          | 1 - 1      |

|         | Main Test Logic                      | 1 - 1      |

|         | Operating Panel                      | 1-4        |

|         | Lamp Display                         | 1 - 4      |

|         | Card Connectors                      | 1-4        |

|         | Signature                            | 1-4        |

|         | Node Count                           | 1-4        |

|         | Test Cycle Theory                    | 1-4        |

|         | Connector Pins                       | 1-4        |

|         | Word Register                        | 1-4        |

|         | Clear Phase                          | 1-4        |

|         | Test Phase                           | 1-4<br>1-5 |

|         | Clock Control                        | 1-3<br>1-5 |

|         | Display                              | 1-5<br>1-5 |

|         | Self Check Feature                   | 1-5<br>1-5 |

|         | Revision History Sheet               | 1 - 5      |

|         | Card Description                     | 1-5        |

|         | Test Flow Diagram                    | 1-5        |

|         | Card Block Diagram                   | 1-5        |

|         | Operating Instructions and Signature | 1-5        |

|         | Node Count                           | 1 - 5      |

|         | Node Count Values                    | 1-5        |

|         | Card History Sheet                   | 1-6        |

|         | Operating Panel Details              | 1–10       |

|         | FCT Operating Procedures             | 1-14       |

|         | Accessories – Description and Use    | 1-17       |

|         | Logic Signal Glossary                | 1-18       |

|         | CL Card                              | 1-18       |

|         | YO Card                              | 1-21       |

| 2       | FUNCTIONAL DETAIL                    |            |

|         | Basic Test Method                    | 2-1        |

|         | Signature                            | 2 - 2      |

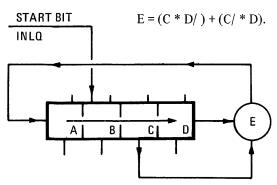

|         | Simple Shift Register                | 2-2        |

|         | Bit Pattern Generator                | 2 - 2      |

|         | Feedback Principle                   | 2-2        |

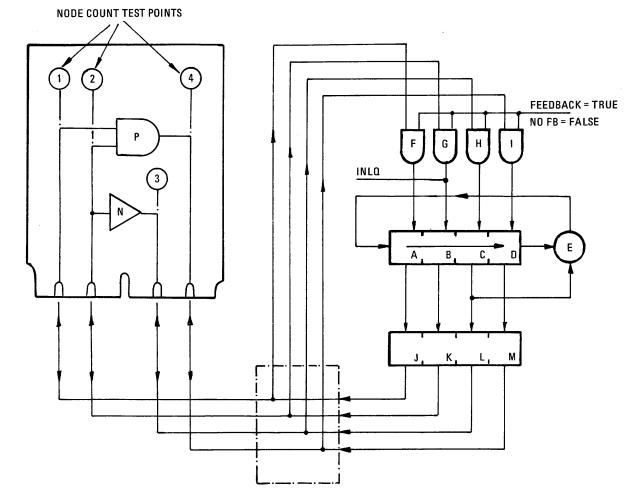

|         | Signature/Node Count                 | 2-3        |

|         | General                              | 2-3        |

|         | Good Signature (with FB)             | 2-4        |

|         | Bad Signature (Fault P with FB)      | 2-4        |

|         | Bad Signature (Fault N with FB).     | 2-4        |

|         | Good Node Count (No FB)              | 2-4        |

|         | Bad Node Count (Fault P and no FB)   | 2-5<br>2-5 |

|         | Bad Node Count (Fault N and no FB)   | 2-3        |

i

~

| Sectior | 1                             | Page  |

|---------|-------------------------------|-------|

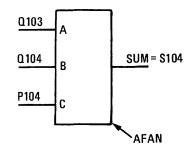

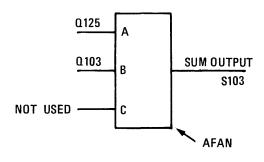

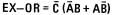

| 2       | Sum/Shift Logic               | 2-5   |

|         | Exclusive-Or and Return Loop  | 2-5   |

|         | Register Storage Logic        | 2-5   |

|         | Output Buffer Logic           | 2-6   |

|         | Backplane Wired-or Connection | 2 - 6 |

|         | Feedback Gating               | 2-6   |

|         | Led Display Gating            | 26    |

|         | Start Bit Logic               | 2-6   |

|         | Disconnect Input Gating       | 2-6   |

|         | LFAN Clock Logic              | 2-6   |

|         | Disconnect Latch Logic.       | 2-6   |

|         | Pin Disconnect Procedure      | 2-8   |

|         | Pin Select Procedure          | 2-8   |

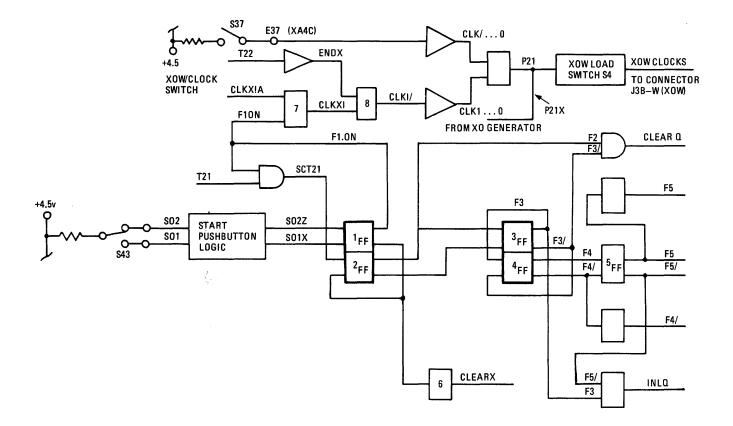

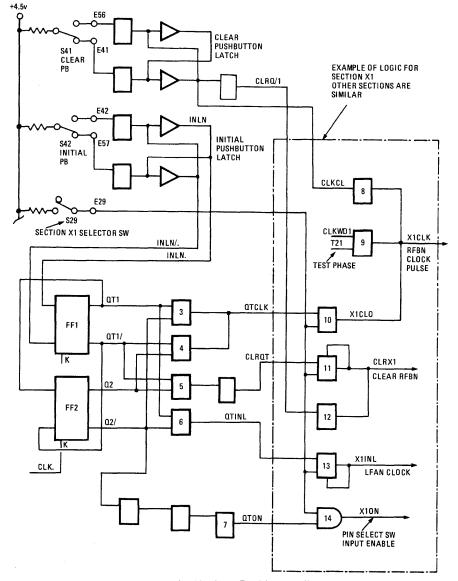

|         | Start Pushbutton Logic        | 2-8   |

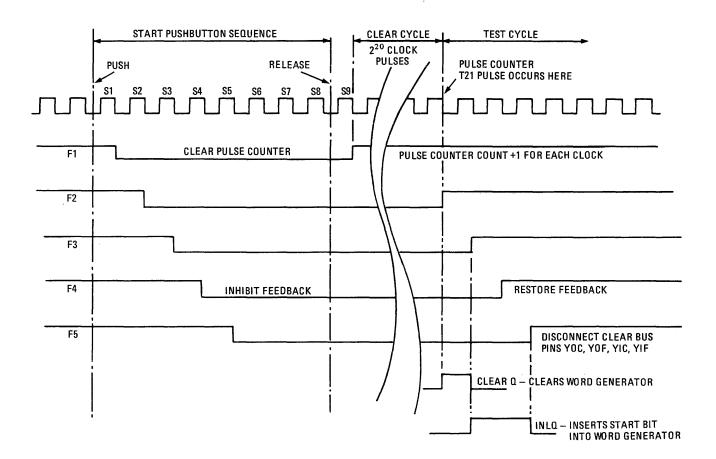

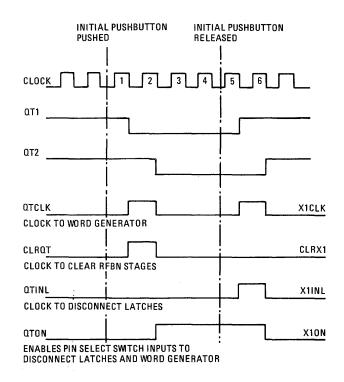

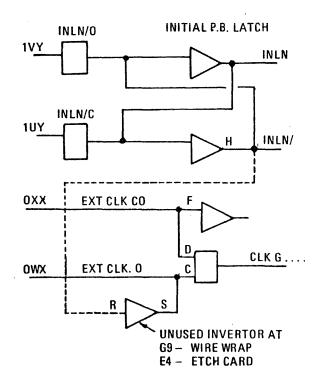

|         | Initial Pushbutton Logic      | 2-10  |

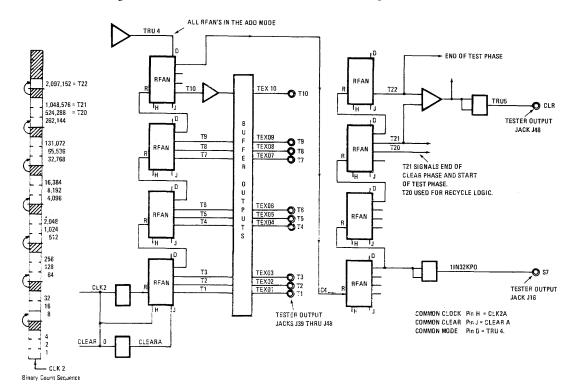

|         | Word Section Generator.       | 2-11  |

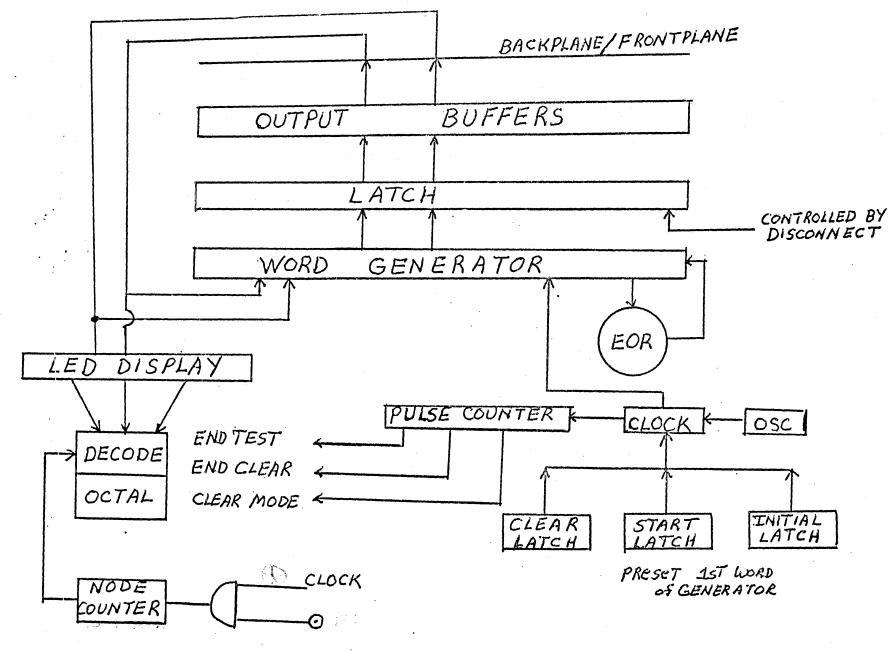

|         | Word Generator Block Diagram  | 2-11  |

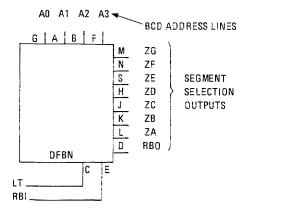

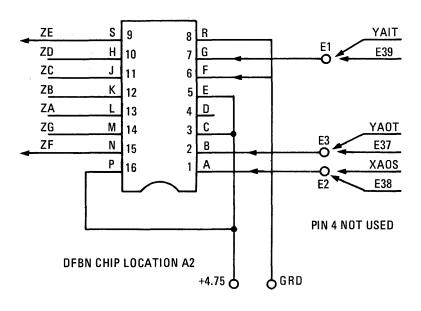

|         | Pulse Counter Probe Logic     | 2-11  |

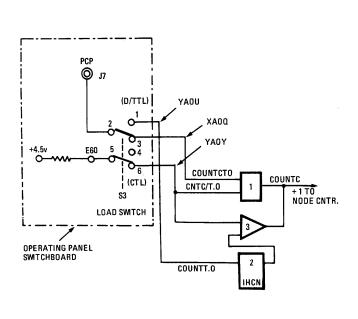

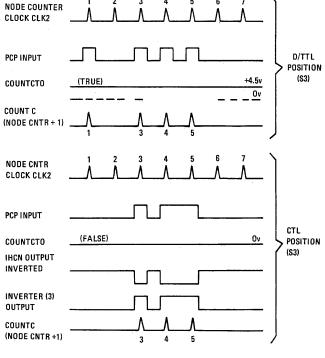

|         | Node Counter Logic            | 2-14  |

|         | Pulse Counter Logic           | 2-15  |

|         | Pulse Counter Decoder Logic   | 2-15  |

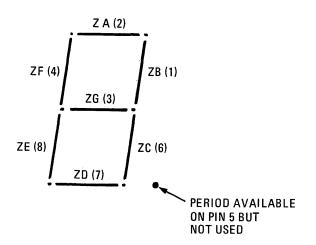

|         | Numeric Display Logic         | 2-16  |

|         | Interlock Relay $\pm 12$ Volt | 2-17  |

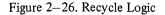

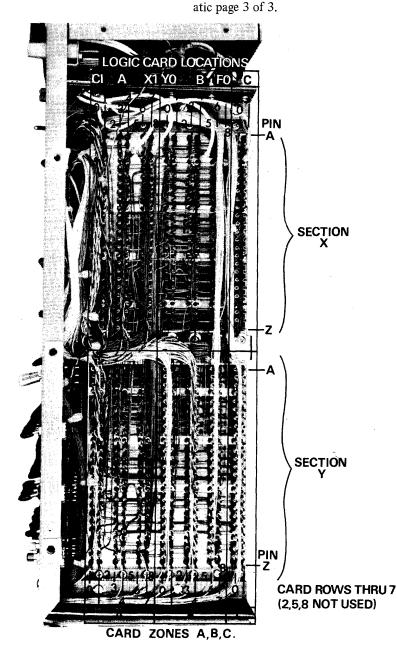

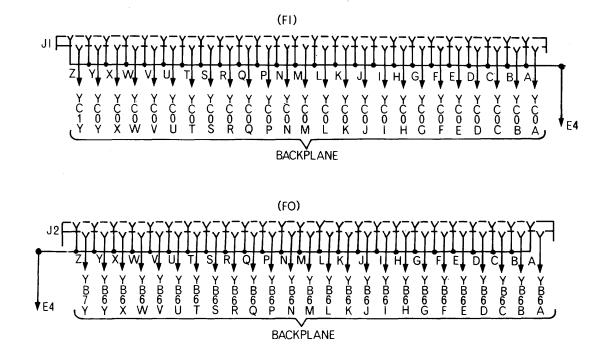

|         | Recycle Logic                 | 2-18  |

|         | Backplane Pin Location.       | 2-19  |

|         | Initial Pushbutton.           | 2-19  |

|         | Selector Switch               | 2-19  |

|         |                               |       |

| 3       | CIRCUIT DETAIL                |       |

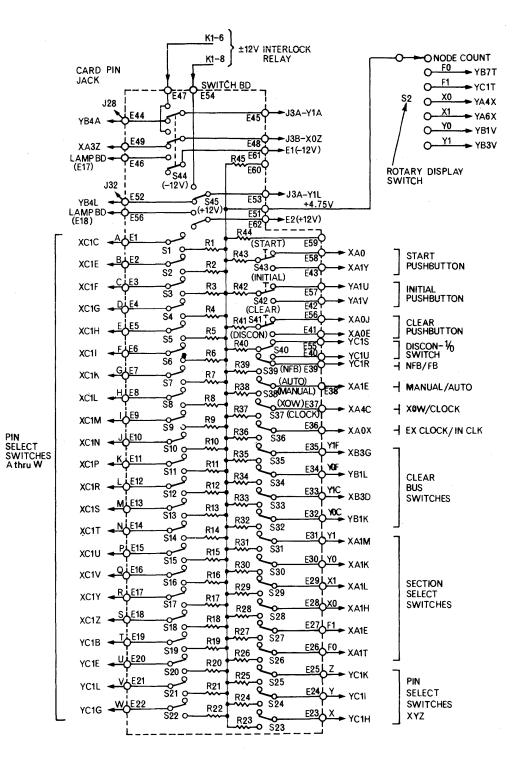

|         | Card Tester Schematic         | 3-1   |

|         | Frontplane Connectors         | 3-1   |

|         | Backplane Connectors          | 3-2   |

|         | Tester Output Jacks           | 3-3   |

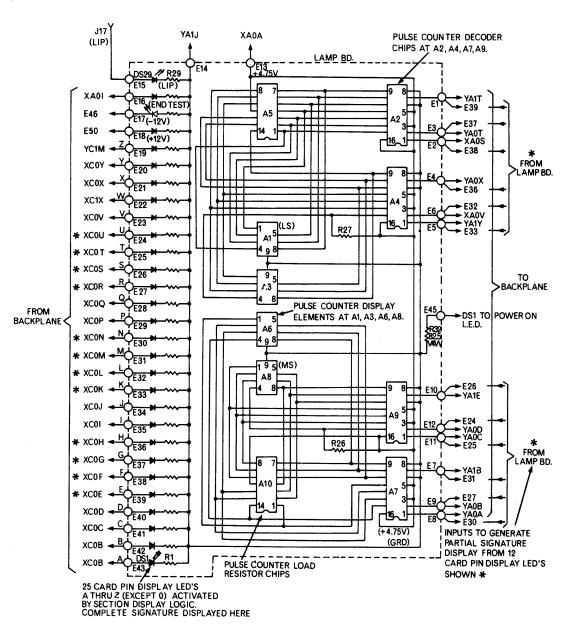

|         | Lamp Display Board            | 3-4   |

|         | Switchboard                   | 3-5   |

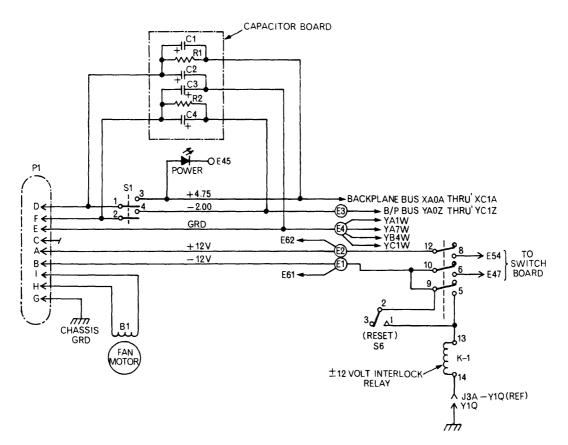

|         | Logic Voltage Distributor     | 3–6   |

|         | Test Field Documents          | 3-6   |

|         |                               |       |

| 5       | MAINTENANCE PROCEDURE         |       |

|         | General                       | 5-1   |

|         | Maintenance Guide             | 5 - 1 |

|         | Cooling Fan                   | 5 - 1 |

|         | Internal Clock Frequency      | 5 - 1 |

|         | Trouble Shooting Guide        | 5-2   |

|         | General                       | 5 - 2 |

|         | Clock Card Waveforms          | 5-2   |

|         | Pulse Counter Test            | 5-2   |

|         | Node Counter Test             | 5-2   |

|         | Self Check Signature          | 5-2   |

|         | Disconnect Logic Test         | 5-2   |

|         | Pin Select Logic Test         | 5-2   |

|         | Pulse Counter Test            | 5-4   |

|         |                               |       |

iii

# TABLE OF CONTENTS (continued)

| Section | •                            | Page |

|---------|------------------------------|------|

| 5       | Self Check Node Counts       | 5-4  |

|         | Operating Procedure          | 54   |

|         | Backplane Section X0         | 5-5  |

|         | Backplane Section X1         | 5-5  |

|         | Backplane Section Y0         | 55   |

|         | Backplane Section Y1         | 5-5  |

|         | Frontplane Section F0 and F1 | 5-6  |

|         | Output Buffer Check          | 5-6  |

|         | Single Shot Clock            | 56   |

|         | Modification Procedure       | 5-6  |

|         | Operating Procedure          | 56   |

|         | Start Bit Modification INLQ  | 5-7  |

|         | Operating Procedure          | 5-7  |

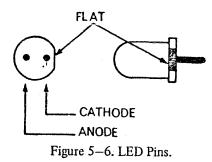

|         | Led Pin Polarity             | 5-7  |

|         | RIN/LIN's                    | 5–7  |

|         | Location/Access Instructions | 57   |

|         | Electronic Assembly          | 5-7  |

|         | Logic Card                   | 5-7  |

|         | Switch Assembly              | 5-7  |

|         | Lamp Board Assembly          | 57   |

|         | End Panel Assembly           | 5-7  |

| (       | Component Part Numbers       | 5-10 |

# LIST OF ILLUSTRATIONS

# Figure

ţ

| Typical B1700 Logic Card Prepared for Testing            | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field Card Tester                                        | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Card Block Diagram (Card J)                              | 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Card Test Flow Diagram                                   | 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FCT Conditions Lamp and Signature Display (For Card J.). | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Typical Node Count Listing                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Logic Card History Sheet                                 | 1–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Upper Operating Panel Details                            | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Lower Operating Panel Details                            | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Reserved Backplane Pins                                  | 1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Card Test Data Page 1                                    | 1-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Card Test Data Page 1                                    | 1-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

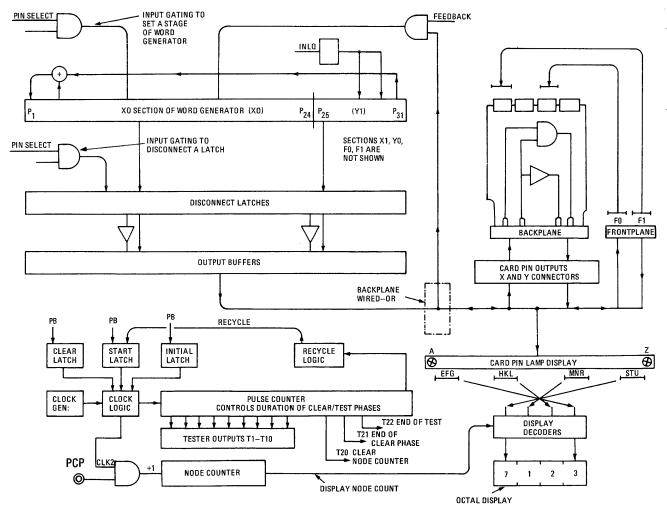

| FCT Block Diagram                                        | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -                                                        | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                          | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                          | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| •                                                        | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -                                                        | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                          | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Sum/Shift/Display Logic                                  | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                          | 2–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Start Pushbutton Logic                                   | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                          | Field Card Tester .Card Block Diagram (Card J)Card Test Flow Diagram .FCT Conditions Lamp and Signature Display .(For Card J.).Typical Node Count ListingLogic Card History Sheet .Upper Operating Panel Details .Lower Operating Panel Details .Lower Operating Panel Details .Card Test Data Page 1Card Test Data Page 1Card Test Data Page 1Simple Shift Register .Signature/Node Count Examples .Sum/Shift AFAN Element .Exclusive-OR AFAN .Sum/Shift/Display Logic .Disconnect Logic . |

# PCN-21U2380-002

# LIST OF ILLUSTRATIONS (continued)

# Figure

| Page |

|------|

|------|

| 2-11      | Start Pushbutton Logic Timing           | 2–9  |

|-----------|-----------------------------------------|------|

| 2-12      | Initial Pushbutton Logic                | 2-10 |

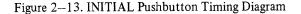

| 2-13.     | Initial Pushbutton Timing               | 2-11 |

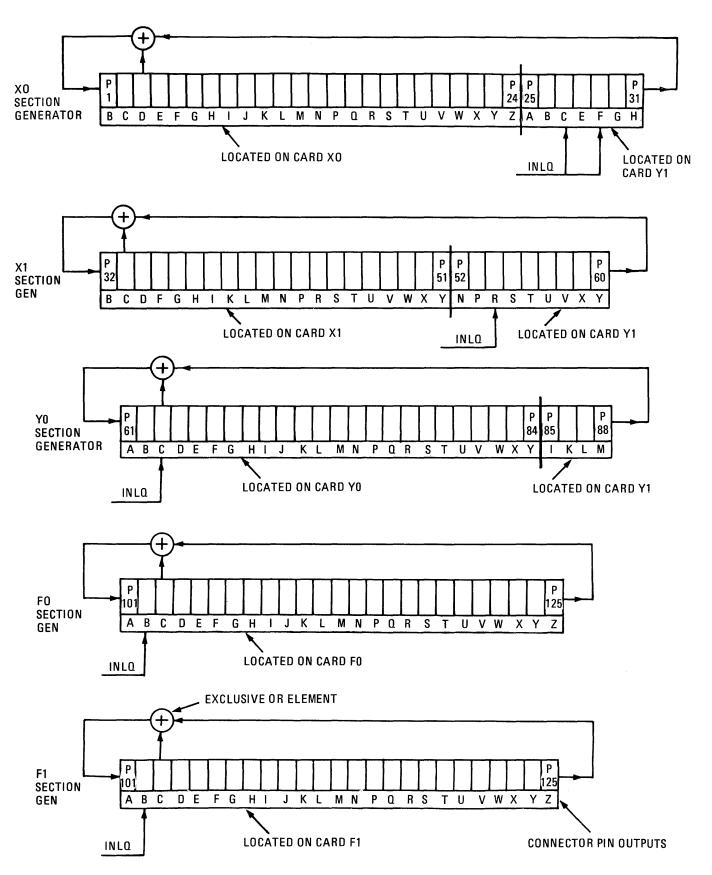

| 2-14      | Word Generator Sections                 | 2-12 |

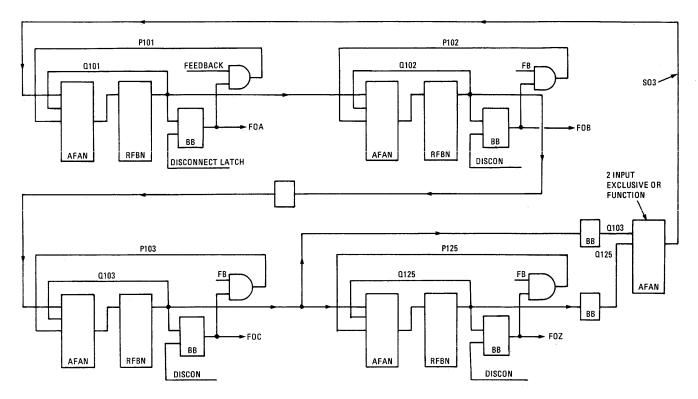

| 2-15      | Word Generator Block Diagram (FO)       | 2-13 |

| 2-16      | Pulse Counter Probe Logic               | 2-13 |

| 2 - 17    | PCP Logic Timing.                       | 2-13 |

| 2-18      | Node Counter Logic                      | 2-14 |

| 2-19      | Pulse Counter Logic                     | 2-15 |

| 2-20      | Seven Segment Decoder.                  | 2-15 |

| 2 - 21    | DFBN Truth Table                        | 2-15 |

| 2-22      | Decoder Input/Outputs                   | 2-16 |

| 2-23      | LED Display Bar Layout                  | 2-16 |

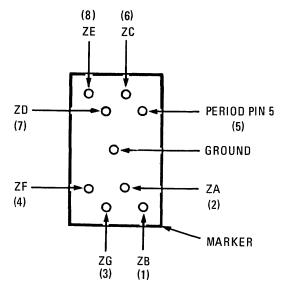

| 2-24      | Display Element Pin Layout              | 2-16 |

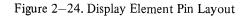

| 2-25      | Interlock Relay $\pm 12v$               | 2-17 |

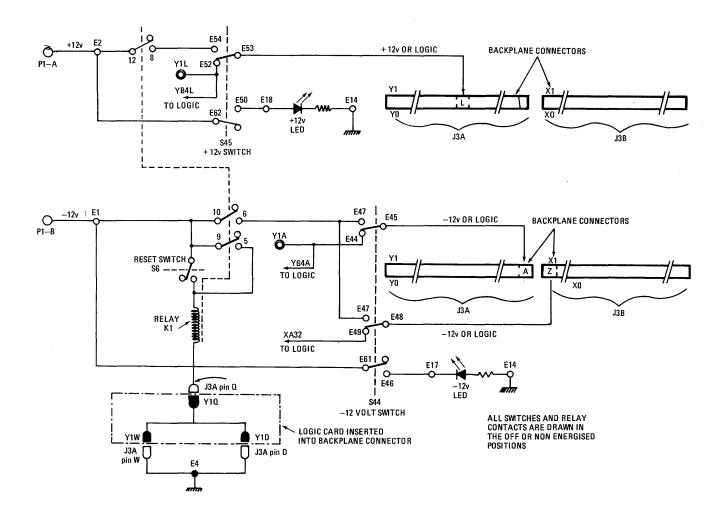

| 2-26      | Recycle Logic                           | 2-18 |

| 2-27      | Recycle Logic Timing                    | 2-18 |

| 2-28      | Backplane Pin Co-ordinates              | 2-19 |

|           |                                         |      |

| 3-1       | Frontplane Connectors                   | 3-1  |

| 3-2       | Backplane Connectors                    | 3-2  |

| 3–3       | Tester Output Jacks                     | 3-3  |

| 3-4       | Card Pin Jacks                          | 3-3  |

| 3-5       | Lamp Display Board                      | 3-4  |

| 36        | Switch Board                            | 3-5  |

| 3–7       | Logic Voltage Distribution              | 3–6  |

| 5-1       | FCT Clock Waveforms                     | 5-1  |

| 5-2       | Pulse Counter Signals                   | 5-3  |

| 5-3       | Node Counter Signals                    | 5-3  |

| 5-4       | Relation Between Logic Card & Signature | 5-3  |

| 5—5       | Single Shot Clock Modification          | 5-6  |

| 5-6       | LED Pins                                | 5-7  |

| 5-0<br>57 | Electronic Assembly                     | 5-8  |

| 5-9       | Switch Board Assembly                   | 5-9  |

# SECTION 1 INTRODUCTION AND OPERATION

#### GENERAL INFORMATION

#### MAINTENANCE PHILOSOPHY

The maintenance philosophy of the Burroughs B1700 computer is based upon the on-site use of a portable Field Card Tester, referred to as an FCT.

Central system faults, either on processor cards or input-output cards, may be confirmed by exercising a suite of MTR/Diagnostic test routines. These test routines are supplied with each system. Each test routine is encoded on a 0.25 inch wide magnetic tape enclosed in a plastic cassette.

The tape drive and its electronic control unit is a plugin module mounted on the front console. The tape drive control logic interfaces directly with the processor and is independant of all other input-output controls. These test routines may be executed directly from cassette or entered into main memory prior to execution. All test routines are supported by documentation containing loading procedures, error halts, options and console key instructions. Error halts are signalled by observing the console lamp display or the Console Printer (SPO). For each processor error halt, the supporting test documents will advise the Field Engineer (FE) of the failing logic card. Some complex logic functions are located on more than one card. In this case, the error halts will define a small group of cards rather than one logic card. The suggested group of logic cards are then tested in the FCT, one by one, to identify the failing card. With the diagnostic ability of the FCT, the FE can isolate the failing circuit or chip. After replacing the faulty circuit, the card must be tested again by the FCT to ensure that the fault has been repaired. Also, the MTR/Diagnostic test routines must be repeated to ensure that the overall system is functioning correctly.

#### MEMORY CARDS

The dynamic S-memory and M-string memory cards are not test-compatible with the FCT.

NEVER INSERT MEMORY CARDS INTO THE FIELD

Fault diagnosis of memory problems are determined by executing special memory test routines that assist the FE in isolating the failure to a component or a small group of components. Fault location is simplified by memory logic design and that memory cards are interchangeable.

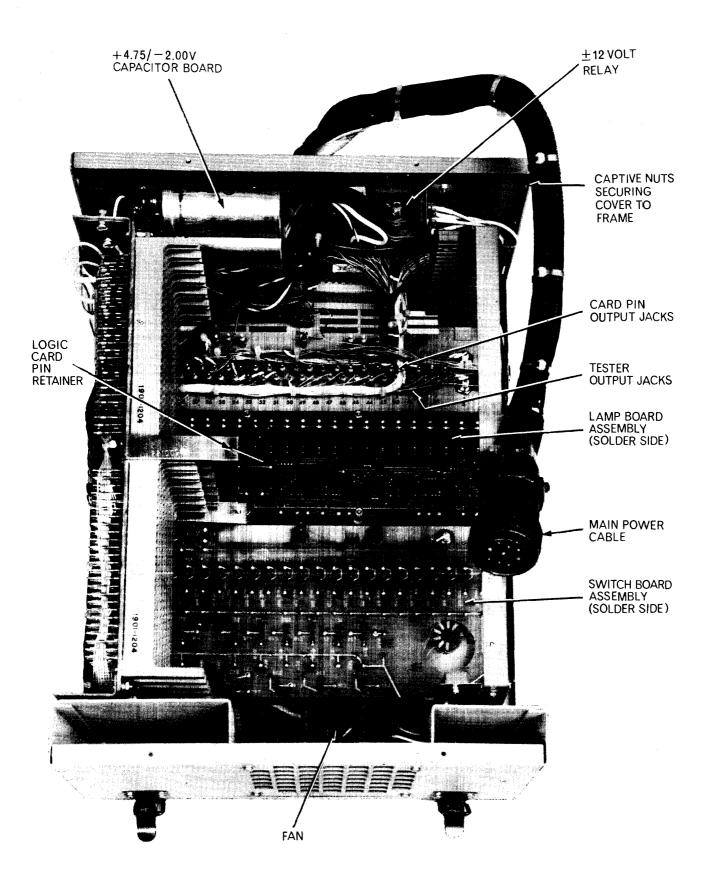

#### FIELD CARD TESTER

The Burroughs B1700 FCT as shown in Figure 1–1, is designed for field service and operated by FE's trained in its use. The B1700 maintenance philosophy states that logic cards must be repaired on-site. The FCT is specifically designed to be used as the primary diagnostic tool to detect and isolate defective logic components. The FCT electronics and metal case surrounding it, weighs approximately 27 pounds (13 Kg) and measures  $19 \times 14 \times 7$  inches ( $49 \times 36 \times 18$  cm) overall. Storage space for tester accessories are included within the case.

The basic areas of the FCT are as follows:

- 1. Logic Power

- 2. Main Test Logic

- 3. Operating Panel

- 4. Lamp Display

- 5. Card Connectors.

#### Logic Power

I cardo une

The four logic voltages  $\pm 4.75$ , -2,  $\pm 12$ , -12 olts and mains A.C. power are obtained from the processor via a flexible cable. A cable socket on the processor mainframe (card side), allows the FCT to be operated on the SPO table.

#### Main Test Logic

The test logic is mounted on seven logic cards. All logic I.C. chips and discrete components are common B1700 parts, mounted on three quarter sized B1700 double edge connector cards. The wire wrapped logic cards on early FCT's have been superseded and replaced by etched cards. The FCT circuits and logic functions are identical for wirewrap or etched FCT cards.Only the chip locations are different. Section 2 of this manual will refer to etched card chip locations for explanation purposes.

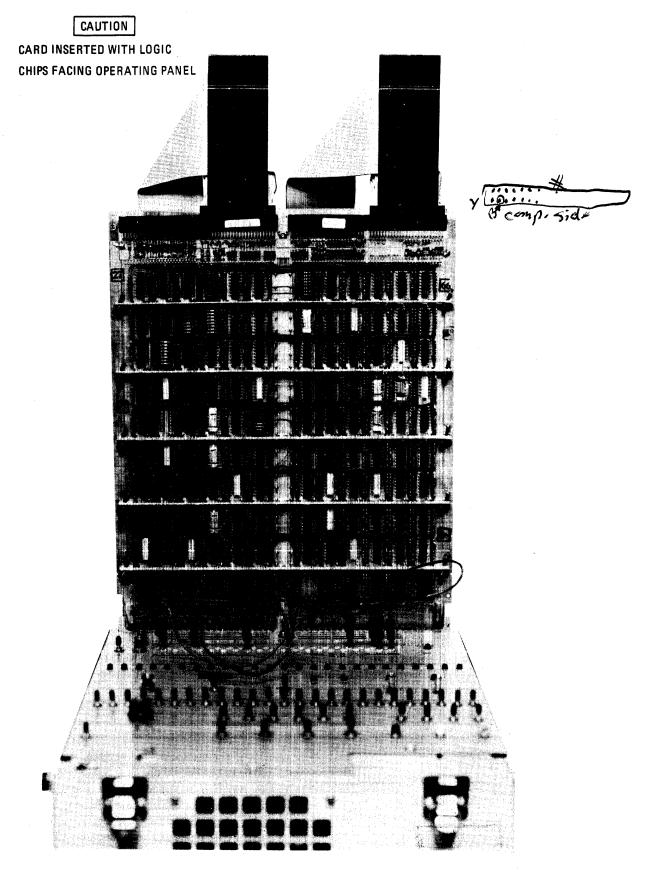

Figure 1-1. Typical B1700 Logic Card Prepared for Testing.

Figure 1–2. Field Card Tester

#### **Operating Panel**

The operator's switch panel comprises 43 switches, providing sufficient flexibility to diagnose and locate logic card faults. The main function of the switch panel is to precondition the FCT logic via the Section Select, Pin Select and DISCON-1/0 switches. Panel controls will also select the front plane or backplane connector pins or Node Count for display purposes. Special loading resistor networks for internal clock and type of logic under test are switchable. Remaining switches include Manual/Auto, Feedback/No Feedback, Internal/External Clock,  $\pm 12$ volts and Master Power on/off.

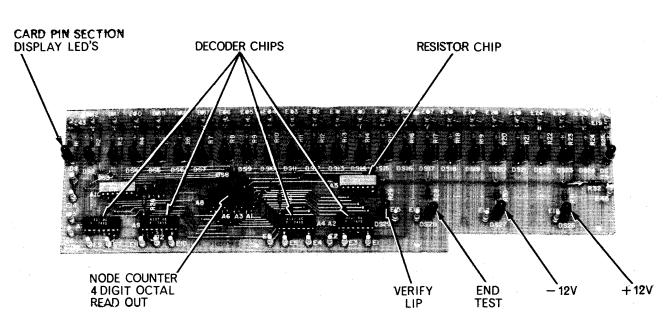

#### Lamp Display

The lamp display is composed of 30 light emitting diodes (LED's). The display is divided into a 25 card pin display, a 4 digit LED octal pulse counter display and other indicators for power, end of test,  $\pm 12$  volts etc. The LED's are illuminated by true logic voltage levels from each card pin selected by the rotary selector switch.

#### Card Connectors

The FCT includes two 50 socket backplane connectors marked X0, X1, Y0, Y1 and two 50 pin frontplane connectors marked F0, F1. Three 50 way flat ribbon cables are provided with the accessories to connect and test all card frontplane connectors.

#### SIGNATURE

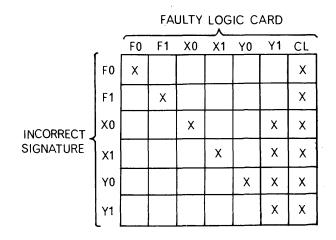

The true complete signature for any B1700 testcompatible logic card is contained in the 25 pin card pin display at the end of the Test Sequence. A quick visual check of a card signature is displayed by the Pulse Counter. This four digit readout is a partial signature, obtained by sampling 12 logic levels of a card pin connector at the end of a Test sequence. Each card that is test-compatible with the FCT, will exhibit its own unique signature. The signatures of good, correctly functioning cards are recorded in the Card Test Documents which are distributed with each FCT. Therefore the signature of any card under test is compared to the correct signature indicated in the Card Test Documents. If the signatures do not compare, then the FCT has correctly identified the faulty logic card. An incorrect signature however, will not indicate the cause or location of the fault on that card.

#### NODE COUNT

Faulty components are located by a supplementary test procedure known as the Node Count. In this test, points within the logic circuit are checked and displayed on the Pulse Counter. The card test documents provide detailed instructions for Node Count procedures and lists the correct Node Count values expected for logic signals on the card. The Node Count is displayed at the end of the Test Sequence with no feedback. By starting with a correct node count it is possible to follow and check each count along any logic signal path. By this signal path count method, the incorrect count will be associated with the faulty component.

#### TEST CYCLE THEORY

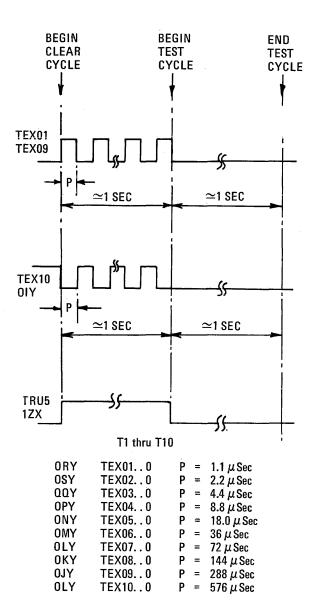

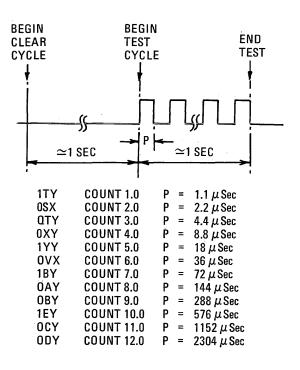

The test cycle will generate a repeatable series of logic signals or bit patterns to a logic card at a clock speed of 1 Megahertz. Higher clock speeds may be employed using an external clock generator connected to the FCT. These bit patterns are referred to as words, which are applied to the card via the backplane and frontplane connector pins. The complete test cycle is divided into 2 phases, beginning with the Clear phase and ending with the Test phase.

#### CONNECTOR PINS

The total number of card connector pins varies from a maximum of 200 to a minimum of 100. The FCT is designed to test 138 connector pins at a time which includes the complete backplane and 2 frontplane connectors. Also, the card test procedures are divided into sequential steps where each step will test the additional frontplane connectors.

#### WORD REGISTER

Each FCT connector pin is connected to one stage of a word generator register, therefore making a total of 138 stages. The word register is split into 6 sections for logical reasons and will generate bit patterns or words and apply them to the card. Each section is composed of a shift register with the last stage output connected to the first stage input. One stage in each section includes a logical Exclusive—Or element which will modify the next word in sequence.

#### CLEAR PHASE

The Clear phase ensures that both the FCT Logic and card under test are cleared to a known state before the Test phase.

#### TEST PHASE

During the Test phase, the word generator register automatically generates the first word by INLQ. Each word and clock pulse are applied sequentially to the card to logically activate the logic chips and discrete components. The activated logic chip outputs are connected as feedback to the word register inputs to generate the next word in sequence. This process of generating bit patterns or words by the method of the Exclusive—or element and feedback, continues throughout the Test phase. Any logic malfunction however small will modify the final signature, due to the feedback principle.

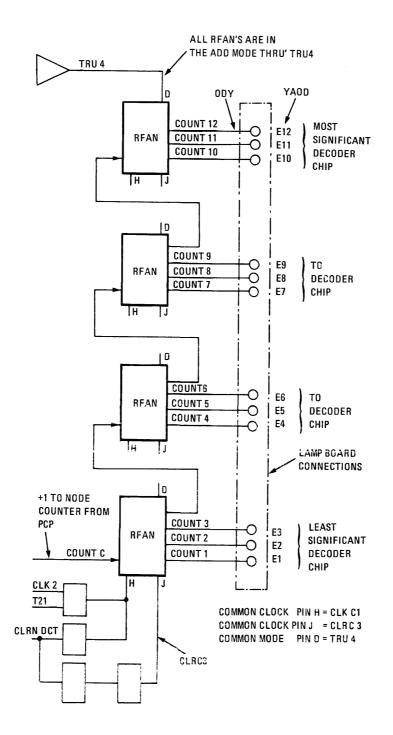

#### CLOCK CONTROL

An exact number of clock pulses are issued for each Clear and Test phase, controlled by a pulse counter. One word is generated for each clock pulse. The precise number of words applied to a card during the Test phase will be 1,048,576. The complete test cycle duration is 2.1 seconds when operating at a clock speed of 1 Megahertz.

#### DISPLAY

The logical state of each connector pin may be displayed on the operating panel. At completion of the Test phase, the card pin lamp display pattern is known as the complete Card Signature. A sample of the card pin display is decoded and displayed on a 4 digit octal readout. A value can be displayed for each FCT connector, enabling the FE to quickly determine that the card is functioning correctly.

#### SELF CHECK FEATURE

Since the FCT is to be used as the primary tool for testing and locating logic faults, the FCT itself must be tested. Therefore a self check feature is incorporated into the FCT logic that enables the FE to verify the FCT is operating correctly. The internal logic is subjected to the same Clear and Test phases and number of words as generated for any B1700 card under test. The final card pin display signature and octal readout display value is compared to the correct values contained in the Card Test Documents.

Card test data documents are provided for all B1700 logic cards that are test-compatible with the FCT. For each card the information contained in these documents is as follows.

#### **Revision History Sheet**

The history sheet lists a description of the revision, its revision suffix, revision date and lists the EI/ECN's relevant to that card.

#### Card Description

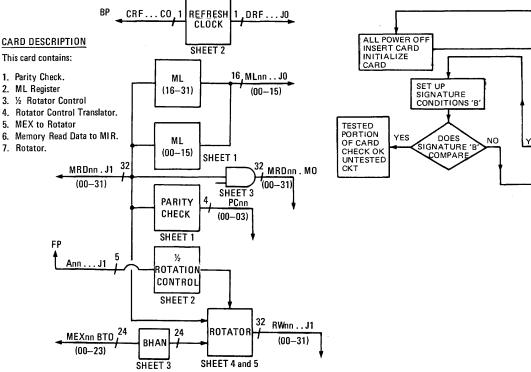

Briefly describes the logic and control function contained on that card, as shown in Figure 1-3.

#### Test Flow Diagram

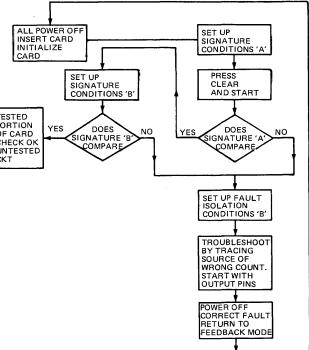

Indicates, step by step as shown in Figure 1-4, the fault procedure to be followed to isolate the faulty logic component on the card.

#### Card Block Diagram

Illustrates a simplified logic block diagram showing important logic signals. The block diagrams are partitioned and relate the logic schematic page number to the block diagram, also shown in Figure 1-3.

Figure 1-3. Card Block Diagram (Card J).

Figure 1-4. Card Test Flow Diagram.

#### Operating Instructions and Signature

Provides operating instructions necessary to precondition the FCT. A typical signature and card pin lamp display is shown in Figure 1-5.

#### Node Count

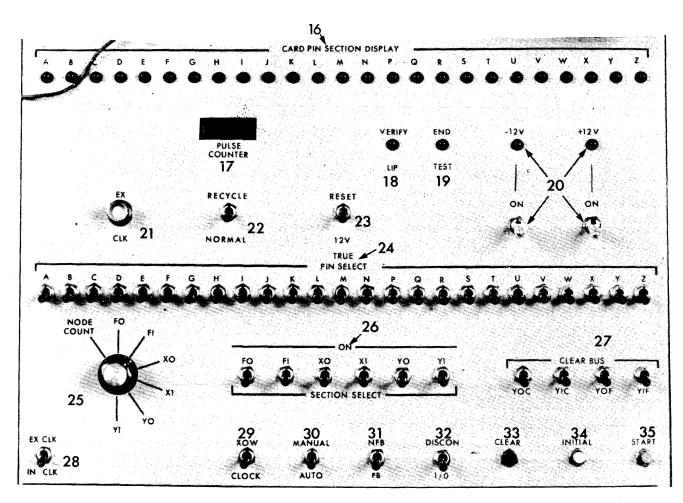

Provides additional instructions for FCT preconditioning for Node Counting, and lists untested circuits. A typical Node Count listing is shown in Figure 1-6.

#### Node Count Values

Lists in alphabetical order all logic signals, pin location and correct Node Count values.

Early node count listings were alphabetic only. Recent editions are composed of the following:

A – CONDITIONS DISCONNECT : YOC

1. A chip pin-sort list.

2. Input-output card pin list.

3. Alphabetic signal name listing.

#### CARD HISTORY SHEET

Before beginning a signature or node count test, the FE must ensure that the card under test and card test data documents correspond. The card history sheet must be used to check that card and test documents are related.Each logic card has its own history sheet as shown in Figure 1-7, which records the following information:

- 1. Engineering changes.

- 2. Card Order Number.

- 3. Card Test Data.

- 4. Logic Card Schematics.

- 5. Card Citcuit Lists.

Card order numbers are changed to show engineering changes and are stamped on the solder side of the card in black eight digit numbers. Caution: the smaller eight digit number, also stamped in black, represents the card assembly number. Each page of the card test documents also shows an eight digit document number. By reference to the card history sheet, the FE can quickly check that the card order number and its related card test document package, do correspond.

|                                                                                   |           |   | IN | SE | RT |   |   |    | to<br>to |      | <i>.</i> |   |    |   |                           | to Y |   |   |   |   |   |    |   |   |   |         |      |

|-----------------------------------------------------------------------------------|-----------|---|----|----|----|---|---|----|----------|------|----------|---|----|---|---------------------------|------|---|---|---|---|---|----|---|---|---|---------|------|

|                                                                                   |           |   |    | SF | ΤΞ |   | : | LO | AĽ       | ) S' | W        |   | 18 |   |                           |      |   |   |   |   |   |    |   |   |   |         |      |

| Display Complete Signature<br>Select or<br>Switch Card Pin Section Lamp Display p |           |   |    |    |    |   |   |    |          |      |          |   |    |   | Pulse<br>Counter<br>Value |      |   |   |   |   |   |    |   |   |   |         |      |

|                                                                                   |           | A | В  | C  | D  | E | F | G  | н        | 1    | J        | K | L  | м | N                         | P    | a | R | s | т | U | ١v | w | х | Y | ار<br>Z | 1    |

|                                                                                   | FO        |   | 1  | 1  | 1  | 1 | 1 |    | 1        | 1    | 1        | 1 |    |   |                           | 1    | 1 |   | 1 | 1 |   | 1  |   | 1 | 1 |         | 3033 |

| M                                                                                 | F1        | 1 |    |    |    | 1 |   | 1  |          |      |          |   |    | 1 | 1                         |      |   |   |   | 1 | 1 | 1  | 1 | 1 |   | 1       | 6305 |

| 1                                                                                 | X0        |   | 1  |    | 1  | 1 |   | 1  | 1        |      |          | 1 | 1  | 1 |                           | 1    |   | 1 |   |   | 1 |    |   | 1 |   |         | 4575 |

|                                                                                   | X1        |   | 1  |    |    |   | 1 | 1  | 1        | ľ    |          | 1 | 1  |   |                           |      |   | 1 |   |   |   | 1  |   | 1 |   | 1       | 4476 |

|                                                                                   | Y0        |   |    |    | 1  | 1 |   | 1  | 1        | 1    |          |   |    |   | 1                         |      |   |   |   |   |   | 1  | 1 | 1 |   |         | 0215 |

| L                                                                                 | <u>Y1</u> |   |    |    |    |   |   |    | 1        | 1    | L        |   | 1  | 1 | 1                         | 1    |   |   |   |   |   |    |   | 1 |   |         | 0350 |

| Figure 1–5. FCT Conditions | Lamp and Signature Display |

|----------------------------|----------------------------|

| (For Card.)                | J)                         |

|   |   | CI | RC | UI | Т |   |   | PIN | I | COUNT |   |   |   |   |  |  |

|---|---|----|----|----|---|---|---|-----|---|-------|---|---|---|---|--|--|

| M | Ε | Х  | 2  | 2  | В | Т | 0 | 0   | U | Y     | 0 | 6 | 2 | 6 |  |  |

| M | Ε | Х  | 2  | 3  | • | J |   | К   | 9 | Ρ     | 7 | 7 | 2 | 1 |  |  |

| M | F | Е  | Т  | C  | н | F | 0 | 1   | Α | Y     | 6 | 3 | 2 | 2 |  |  |

| M | L | С  | 0  | Ν  | 1 | J |   | F   | 8 | D     | 0 | 4 | 3 | 5 |  |  |

| M | L | С  | 0  | Ν  | т | Н | 0 | 1   | C | Υ     | 7 | 3 | 4 | 3 |  |  |

|                             |          | CONTF<br>C NO.      | 10 | ORDER<br>NUMBER (ON) | CIRCUIT LIST | REV   | SCHEMATIC   | REV    | CARD TEST<br>DATA | REV       | REMARKS OR<br>RELATED B P & CARD CHANGES             | MFG<br>DASH |

|-----------------------------|----------|---------------------|----|----------------------|--------------|-------|-------------|--------|-------------------|-----------|------------------------------------------------------|-------------|

|                             | ECN      | 1925                | A  | 2214 2871            | T–2203 9325  | AI    | D-2200 3644 | В      | B-2207 1757       | С         | INCORPORATED PIROR EI'S<br>EXCEPT SPCL ASSY INSTR.   |             |

|                             | EI       | 1900                | A  | 2214 2889            | T-2203 9325  | AJ    |             |        |                   |           | TO REDUCE RC NETWORK IN-<br>DUCTANCE.                |             |

|                             | ECN      | 2077                | Α  |                      |              |       |             |        |                   |           | UPDATED SPCL ASSY INSTR<br>COORD WITH ECN 1925.      |             |

|                             | EI       | 2052                | Α  | 2214 2897            | T-2203 9325  | AK    |             |        |                   |           | WIRE CHANGE REQUIRE IF CARDS<br>W/W WITH CD DECK AH. |             |

| Figure                      | ECN      | 3089                | A  |                      | T-2203 9325  | AK    | D-2200 3644 | В      | B—2209 7588       | A         | INCORPORATED EI'S CHANGED<br>P/N CD TEST DATA.       |             |

| $\frac{1}{1}$               | EI       | 3447                | A  | 2214 2905            |              |       |             |        |                   |           | ADDED (116) 16 PIN SOCKETS<br>TO CD ASSY.            |             |

| Logic                       | El       | 3375                | A  | 2214 2913            |              |       |             |        |                   |           | CHANGE CAP VALUE AND<br>QUANTITY.                    |             |

| Card I                      | EI       | EI 3377 A 2214 2921 |    |                      |              |       |             |        |                   |           | CHANGE CAP VALUE AND<br>QUANTITY.                    |             |

| listory                     | ECN      | 3673                | A  |                      | T-2203 9325  | AK    | D-2200 3644 | В      | B—2209 7588       | A         | INCORPORATED EI's.                                   |             |

| 7. Logic Card History Sheet | ECN      | 3669                |    |                      | DELETEI      | ) WIF | E WRAPPED   | CAR    | D AND             | T<br>REPL | ACED                                                 |             |

| ť                           |          |                     |    |                      | WITH E       | TCHEE | ) CARD, P   | /N<br> | 2208 0972,        | CD        | J ASSY–S PROG.                                       |             |

|                             | EI       | 3699                | Α  | 2214 2921            | T-2203 9325  | AK    | D-2200 3644 | В      | B—2209 7588       | A         | RLSD HISTORY SHEET                                   |             |

|                             | EI<br>13 | 4448<br>74          | Α  |                      |              |       |             |        | B-2209 7588       | В         | ADDED ADDITIONAL INCOMPATIBLE<br>NODE COUNTS.        |             |

|                             |          |                     |    |                      |              |       |             |        |                   |           |                                                      |             |

|                             |          |                     |    |                      |              |       |             |        |                   |           |                                                      |             |

|                             |          |                     |    |                      | L,           |       |             |        |                   |           |                                                      |             |

Burroughs - B1700 Field Card Tester Technical Manual Introduction and Operation

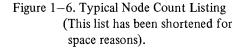

- 1. Frontplane cable connectors F0, F1.

- 2. Backplane connectors.

- 3. Load Switch.

- 4. Auxiliary logic grounding.

- 5. Test Jacks S7 = 11N32KPO S1 through S6 not used.

- 6. XOW Clock Jack.

- 7. Logic Input Probe Jack (LIP).

- 8. Pulse Count Probe Jack (PCP).

- 9. Coaxial Clock Output.

- 10. Logic Load Switch D/TTL-CTL.

- 11. Coaxial FCT Clock Output.

- 12. Card Pin Jacks (X and Y).

- 13. Tester Output Jacks.

- 14. Power on Indicator (+4.75v).

- 15. Main Power on/off switch.

Figure 1-8. Upper Operating Panel Detail.

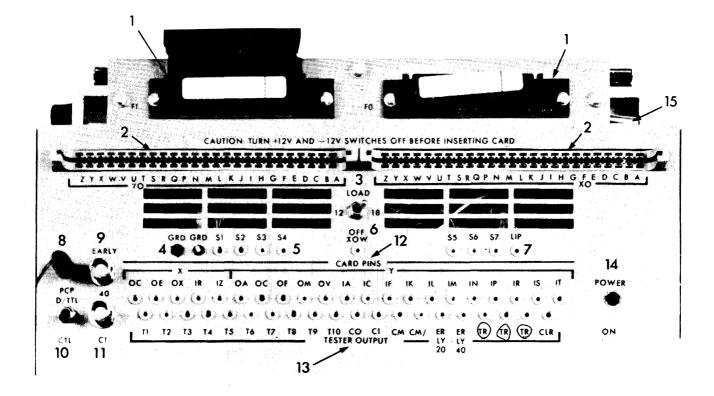

- 16. Card Pin Section Display

- 17. Pulse Counter

- 18. Verify LIP Indicator

- 19. End of Test Indicator

- 20.  $\pm 12v$  Switches and LED's

- 21. External Clock Coaxial Connector

- 22. Recycle/Normal Switch

- 23. Reset Switch for  $\pm 12v$  Relay.

- 24. Pin Select Switches.

- 25. Rotary Display Switch.

- 26. Section Select Switches.

- 27. Clear Bus Switches.

- 28. External/Internal Switch.

- 29. XOW/CLOCK Switch.

- 30. MANUAL/AUTO Switch.

- 31. NO FEEDBACK/FEEDBACK Switch.

- 32. DISCONNECT/1–0 Switch.

- 33. Clear Pushbutton.

- 34. Initial Pushbutton.

- 35. Start Pushbutton.

Figure 1–9. Lower Operating Panel Detail.

#### **OPERATING PANEL DETAILS**

The upper and lower operating panel details are shown in Figure 1-8 and Figure 1-9 respectively.

#### MASTER POWER ON/OFF

This switch controls the application of the +4.75vand -2.00v logic voltage supply from the processor to the FCT. The power on indicator (LED) is illuminated by +4.75 volts supplied through this switch.

#### FRONT PLANE CONNECTOR

Two 25 pin connectors, labelled F0 and F1, are used to connect and test logic cards fitted with frontplane connectors. Flat ribbon cables are provided with the FCT accessories for mating the frontplane connectors to the FCT. For cards with more than two frontplane connectors, then the card test instructions will specify more than one test sequence. Each test sequence will use a different frontplane connector configuration to test all connectors.

#### BACKPLANE CONNECTOR

Two 50 pin backplane connectors are provided, into which the card under test is inserted.

#### CAUTION

The card must be inserted with the logic chips facing the operating panel, as shown in Figure 1–1. Failure to observe this precaution will severely damage the card.

The usual device, ensuring correct card insertion has been removed to allow the FCT cover to fit. Connector designations and card pin identities as shown on the operating panel corresponding to the processor backplane.

#### LOAD SWITCH

A three position switch for selecting the correct loading resistor network for the clock line. Manually set according to instructions contained in the card test data for that card under test. The clock resistor network provides for:-

- 1. 12 clock loads.

- 2. No clock loading.

- 3. 18 clock loads.

#### CARD PIN SOCKETS

These sockets are directly connected to card pins on the backplane connector of the FCT. All 21 card pin sockets are designated by connector (X or Y) and by card pin location (OC thru' IT). Patch cards are inserted into these sockets during a Signature or Node Count test sequence, according to card test data instructions.

#### **TESTER OUTPUT SOCKETS**

The FCT logic generates special signals which are distributed from these tester output sockets through patch cards to the card pin sockets. Cards which require special signals for logic clearing purposes, must use these sockets. Signals generated and distributed from the tester output sockets are described in the following text.

#### T1 thru T10.

These signals are clock signals, active only during the clear phase. Signal T1 frequency is 500 KHZ if the internal clock is used or half the external clock rate. Signals T2 thru' T10, are generated by a series of divide-by-two circuits, using T1 as the basic input signal. These signals switch on the trailing edge of the clock signal at XOW.

#### TRUE

A true signal, shown as TR, provides a constant true logic level. There are three sockets that distribute a true (TR) signal.

#### CLEAR

A clear signal, shown as CLR, provides a constant logical true output during the clear phase only of a test cycle. The clear (CLR) socket completes the series of tester output sockets.

#### LOGIC INPUT PROBE

The logic input probe is inserted into the socket marked LIP and in conjunction with its LED indicator, are used to indicate the logic state of any card signal. The LIP indicator will be ON for a true and be OFF for a false logic level.

#### PULSE COUNT PROBE

The pulse count probe is inserted into the socket marked PCP, when checking node counts on a logic card. The PCP socket is connected to the pulse counter logic which will display the card pin node count at the end of the test sequence.

#### D/TTL - CTL switch

Selects the correct loading network to match the type of logic being checked by the node count method. The switch position will vary according to instructions contained in the card test documents.

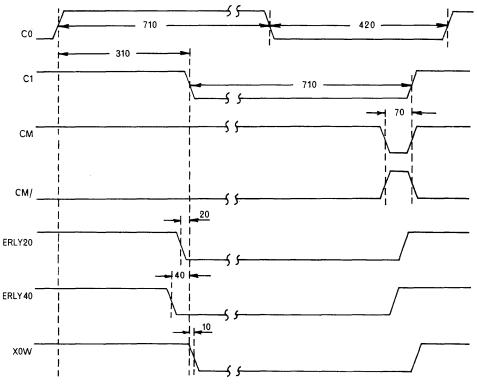

#### CLK 0 (Clock 0)

This signal is essentially the FCT system clock. When the internal FCT clock is used then CLK 0 will have a frequency of one megacycle, with a mark to space ratio of

710 nanoseconds to 420 nanoseconds. This clock signal is active at all times even when the FCT is in the manual mode. The socket CLK 0 provides a convenient external point for checking the FCT clock pulse wave form and frequency.

#### CLK 1 (XOW CLOCK)

This clock signal output is identical to that distributed at XOW when the switch XOW/CLOCK is in the clock position. However, CLK 1 is generated independently to the setting of this XOW/CLOCK switch. Also connected to a coaxial connector.

#### CM and CM/ (Write Enable)

These two clock signals occur slightly earlier than the FCT clock and are used for writing into and reading from 64 bit RFCN's and 256 bit RFDN memory chips. Both CM and CM/ are active for the complete period between start button release and end of the test cycle.

#### EARLY 20/40 CLOCKS

These signals, abbreviated to ERLY, are similar to the XOW clock signal, except that they occur 20 or 40 nanoseconds earlier. These signals are active for the complete period between start button action and end of the test cycle. Early 40 is also connected to the coaxial connector.

#### CARD PIN DISPLAY

The card pin section display is composed of 25 light emitting diodes (LED's), marked A thru' Z, except O. Each LED displays the logic state (true or false) of its corresponding card pin of the card connector selected by the rotary Section Display Selector. For design reasons, the outputs of the card under test and the FCT word generator output buffer stages are strapped together, effectively making an OR-GATE. Therefore the card pin display LED's are illuminated by either (or both) of the following conditions:

- 1. The card under test supplies a positive voltage to that pin.

- 2. The corresponding word generator buffer stage is set and its Disconnect Latch was not set.

Due to this OR-GATE the pin display LED's will indicate the state of the word generator and card if the following conditions are followed. Display the word generator by either (or both) of the following conditions:

- 1) Disconnect Latches not set.

- 2) No card inserted into FCT.

Display the card outputs only if:-

- 1) The corresponding word generator stage was set to zero.

- 2) The corresponding Disconnect Latch was set.

Some backplane pins are permanently reserved for distributing +4.75 and -2.00 volts and logic ground to the card. Therefore the corresponding LED's will not illuminate when selected for display. These reserved backplane pins are shown in Figure 1–10.

| + 4.75v | -2.00v | GROUND |

|---------|--------|--------|

| XOA     | YOZ    | XID    |

| X1A     | Y1Z    | XIJ    |

|         |        | XIW    |

|         |        | XIO    |

|         |        | YID    |

|         |        | YIJ    |

|         |        | YIW    |

Figure 1–10. Reserved Backplane Pins.

To supply  $\pm 12$  volts to specific logic cards, three backplane pins are used, designated YIA, YIL and XOZ.

#### PULSE COUNTER DISPLAY

The display is composed of a four digit LED read out, counting in octal from 0000 to 7777. When tracing and locating logic faults the pulse counter displays the node count of the logic pin being tested. When the start pushbutton is released the display remains at a value of 0000 during the Clear phase and counts during the Test phase. The final count is then compared with the correct node count shown in the Card Test Documentation. For convenience, a selected portion of the card pin display bit patterns are also displayed by the pulse counter for quickly checking the overall logic condition of a card.

#### END OF TEST INDICATOR

Indicates completion of test. Goes off when the start pushbutton is pressed, and is illuminated at the end of the Test Phase.

#### ± 12v SWITCH AND INDICATORS

Two LED indicators, one marked +12 volts and the other marked -12 volts are illuminated when their respective switch is ON. The switches fitted below each voltage indicator distribute  $\pm 12$  volts to specific FCT backplane pins. The -12v feeds pins YIA and XOZ, whilst + 12v feeds pin YIL. Some B1700 logic cards do not require  $\pm 12$  volts for testing purposes. Therefore, FE's must conform to Card Test Data instructions regarding the  $\pm 12$  volt application to the card under test.

INCORRECT APPLICATION OF  $\pm 12$  VOLTS WILL DAMAGE THE LOGIC CARD.

#### 12v/RESET SWITCH

This spring return switch (S6) and associated relay (K1) is fitted to recent FCT models to prevent  $\pm 12$  volts being applied by mistake, to the card. Relay K1 will energise when a card is inserted and the 12v/Reset Switch selected towards the reset position. The required  $\pm 12v$  may then be applied by selecting the appropriate  $\pm 12v$  switch.

#### NORMAL/RECYCLE SWITCH

In the normal position, this switch permits one complete test sequence to occur. Normally used for Signature testing. Whilst the recycle position will permit an automatic repetition of complete test sequences to occur. The recycle function is used during node count testing.

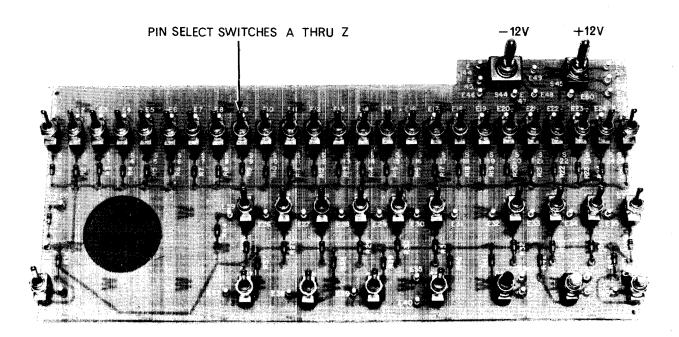

#### PIN SELECT SWITCHES

There are 25 pin select switches marked A thru' Z, except O. Each switch position corresponds to one stage of the word generator section as determined by the Section Select switches. The pin select switches are used to set a stage or to set a Disconnect Latch of any stage and in any section of the word generator register. The type of operation on the word generator depends upon the DISCON/1–0 switch position.

#### EXT: CLOCK CONNECTOR

The coaxial connector, marked EX CLK, provides the possibility of connecting the FCT to an external clock signal.

#### SECTION DISPLAY SELECTOR

This display selector is a seven position rotary switch which controls the card pin section display and pulse counter. The switch positions are marked as follows: (1) Node Count (2) FO (3) F1 (4) XO (5) X1 (6) YO (7) Y1. Functions of the display selector are as follows:

- 1. Node Count In this position the pulse counter displays the node count value obtained by circuit sampling, using the pulse counter probe.

- Switch positions F0 thru Y1 From any one of these six positions the FCT will display the complete bit pattern (or signature) on the card pin section display. The switch also decodes a selected portion of the bit patterns into a four digit octal readout for pulse counter display.

- 3. Frontplane Connector F0, F1. The chip clip may also be inserted into either of these two connectors when testing individual chips or small circuit strings.

#### SECTION SELECT SWITCHES

There are six section select switches, marked (1) X0,

(2) X1, (3) Y0, (4) Y1, (5) F0, (6) F1. These switches select the required section of the FCT word generator. These switches are selected in combination with the Pin Select and Discon/1-0 switches to modify the word generator register, according to Card Test Data instructions.

#### CLEAR BUS SWITCHES

Four switches, marked YOC, Y1C, YOF and Y1F are logically connected to their corresponding pins on the backplane connector. Early in the test cycle, automatic clear signals are applied to these four pins regardless of clear switch settings. Normally the clear bus switches are OFF during the test cycle unless instructed otherwise in the Card Test Documents. Any clear bus switch in the ON position, logically disconnects the pin from the word generator and the pin remains at zero throughout the test cycle. This will reduce the effectiveness of the FCT diagnostic ability.

#### INTERNAL/EXTERNAL CLOCK

This switch, marked in CLK/EX CLK, selects the required clock for the FCT electronics and the card under test.

#### XOW/CLOCK

This switch selects the signal to be connected to pin XOW of the card under test. Certain B1700 logic cards use pin XOW as a clock input, whilst others use XOW as a normal logic signal. In the XOW position, the word generator stage is connected to pin XOW. When in the CLOCK position the clock signal is connected to pin XOW. No feedback will occur from pin XOW, in the CLOCK position, even though the corresponding word generator remains active.

#### MANUAL/AUTO SWITCH

When in MANUAL, one clock pulse will occur for each start pushbutton action. While in AUTO the FCT will perform the complete card test sequence for each Start pushbutton action. The complete card test sequence begins with the Clear cycle automatically followed by the Test cycle. During each cycle  $2^{20}$  clock pulses will occur. The duration of each cycle is controlled by a clock counter, which indicates the end of the Clear cycle by the signal T21 and the end of Test cycle by T22.

#### FEEDBACK/NO FEEDBACK

This switch, marked FB (feedback) and NFB (no feedback), determines whether the card outputs are to be used as feedback to the word generator register. Feedback from the card outputs are used to contribute in the determination of the next bit pattern in the word generator. This switch is

set to feedback (FB) for card signature (GO/NO GO) testing. The no feedback (NFB) position is used for fault location and node counting. No feedback must be used for fault location. Because a faulty logic circuit in one logic area will modify the node count of its adjacent logic circuit that is functioning correctly, therefore making fault location impossible. Instructions specifying the required switch position will be found in the Card Test Data.

#### DISCON-1/0 SWITCH

This switch marked DISCON and 1/0, determines the type of operation performed by the Pin Select switches. The DISCON-1/0 switch is used in conjunction with the following switches:

- 1. Pin Select switches

- 2. Section Select switches

- 3. Initialize pushbutton

These switches are used to pre-condition or initialize the FCT. Complete instructions for-these switch-positions are contained in the Card Test Data documents.

#### DISCON

This position will set a DISCONNECT Latch of the word generator stage if the corresponding Pin Select switch is in the ON position. The choice and number of Disconnect Latches to be set depends upon the Pin Select switches that are selected. A Disconnect Latch when set, will logically disconnect a word generator stage output from the card pin under test. The Card outputs of disconnected stages are connected to word generator inputs as feedback in the usual way, if the Feedback switch is switched to FB. A Disconnect Latch can only be reset by the following procedure:

- 1. Set Pin Select switch to OFF.

- 2. Set DISCON-1/0 to DISCON.

- 3. Depress the Initialize pushbutton.

#### 1/0

This position is marked 1/0 representing one/zero, will store the Pin Select switch positions into the corresponding stage of the word generator register during the clear phase. The Pin Select switches in the ON positon will store a one (1) whilst in the OFF position stores a zero (0). The patterns of 1's and 0's are referred to as a word, which will vary according to the card under test. The contents of the word register are changed during the Test phase therefore this Initialization process of pre-conditioning the FCT must be repeated for each test. Those cards that are completely cleared by a single pulse on pins YOF, Y1F, YOC and Y1C can use any word because the card is cleared early in the Test phase.

#### CLEAR SWITCH

When actuated, the clear pushbutton will clear all FCT registers to zero.

#### INITIALIZE SWITCH

When actuated, the initialize pushbutton will perform the operation indicated by the DISCON-1/0 switch on the word generator register stages selected by the Section Select and Pin Select switches. Used to load the selected word into the word generators register or to set the Disconnect Latches.

#### START PUSHBUTTON

The release of the Start pushbutton will start the complete test sequence. The test sequence begins with the Clear phase followed automatically by the Test phase. A counter controls the duration of each phase with the signal T21 terminating the Clear and signal T22 terminating the Test phase. In the manual mode, one clock pulse is generated for each Start pushbutton release.

#### FCT OPERATING PROCEDURES

An example of FCT operating procedures (page 1) is reproduced in Figure 1–11 and 1–12. Information contained on page 1, shows the precautions and preliminary checks to be followed before card insertion. The FCT selfchecking test sequence and signature is outlined in Figure

The second se

1-12, step 12.

It is impractical to provide complete FCT operating instructions in this manual for all B1700 FCT compatible logic cards. Therefore, the FE must read and conform to the operating instructions detailed in the Card Test Documents.

|                         | THE           | NORMAL POSITION OF                             | ALL SWITCHES WILL BE DOWN OR OFF UNLESS OTHERWISE SPECIFIED.                                                                                                                                                                              |

|-------------------------|---------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10katt                  | CHE           | CK FOR:                                        |                                                                                                                                                                                                                                           |

| Carl.                   |               | MAIN POWER OFF<br>– 12v SW OFF<br>+ 12v SW OFF | CAUTION – ± 12V APPLIED IMPROPERLY CAN<br>RESULT IN DAMAGED PLUG-IN CARDS. MODELS WITH THE 12V<br>RESET SW HAVE THESE VOLTAGES INTERLOCKED.                                                                                               |

| President               |               | PERATING CONDITION<br>TRUCTIONS ITEM 12.       | OF THE TESTER IS IN DOUBT. CONSULT THE SELF-CHECKING FEATURE                                                                                                                                                                              |

| at rel                  | 6)            | INSERT CARD                                    | THIS COMPLETES THE GND TO THE 12V INTERLOCK AND ACTIVATES<br>THE 12V RESET SWITCH. WHEN + OR $-12V$ IS CALLED FOR IN THE                                                                                                                  |

| 5 g                     | <b>.</b><br>5 | MAIN POWER ON                                  | THE 12V RESET SWITCH. WHEN + OR -12V IS CALLED FOR IN THE<br>CARD TEST INSTRUCTIONS, THE APPROPRIATE SW MUST BE ACTI-<br>VATED FOLLOWED BY "RESET" BEFORE THE VOLTAGE WILL BE<br>PRESENT<br>ESS CLEAR SWITCH<br>ELECT SWITCHES DOWN (A-Z) |

| 2.5                     |               | INITIALIZE TESTER                              | PRESENT                                                                                                                                                                                                                                   |

| $\frac{cL}{alls\omega}$ | ton           |                                                | ESS CLEAR SWITCH<br>ELECT SWITCHES DOWN (A->Z)                                                                                                                                                                                            |

|                         |               | SECTI                                          | ON SELECT SWITCHES UP (FO->Y1)                                                                                                                                                                                                            |

| 1h, 7,                  | al So         | - / /                                          | ATCH TO DISCONNECT<br>ESS INITIAL SWITCH                                                                                                                                                                                                  |

|                         | start         |                                                |                                                                                                                                                                                                                                           |

| 0125<br>0125            | 4.            |                                                | ON SELECT SWITCHES DOWN (F0 $\rightarrow$ Y1) $T = \frac{12}{12}$<br>L CARD TEST INSTRUCTIONS $\frac{12}{12}$                                                                                                                             |

| 7772                    | 5.            | TO DISCONNECT A PIN                            | VOR GROUP OF PINS                                                                                                                                                                                                                         |

| 2400                    |               | MOVE<br>MOVE<br>DEPRI<br>(ANY                  | ITCH TO DISCONNECT<br>THE APPROPRIATE SECTION SELECT SW UP (ON)<br>THE APPROPRIATE PIN SELECT SW OR SWITCHES UP (TRUE)<br>SS INITIAL SWITCH<br>PIN SELECT SWITCHES LEFT IN THE DOWN POSITION DURING THIS<br>ATION ARE CONNECTED)          |

| 2                       | 6.            |                                                | LS IS ACCOMPLISHED THROUGH USE OF THE JUMPER WIRES AND CARD<br>ER OUTPUT PIN JACKS.                                                                                                                                                       |

| į                       | 7.            |                                                | DBE (LIP) IS USED IN VERIFYING LOGIC LEVELS. LOGIC LEVELS<br>AYED IN THE "VERIFY LIP" INDICATOR.                                                                                                                                          |

| :<br>.3                 | 8.            | THE LOAD SWITCH (TH<br>AT THE CLOCK LINE X     | TREE POSITIONS) PROVIDES NO LOAD. 12 LOADS OR 18 LOADS<br>KOW.                                                                                                                                                                            |

|                         | 9.<br>        | BY DEPRESSING CLEA                             | STAINED, AFTER THE SET-UP DESCRIBED FOR THE INDIVIDUAL CARD,<br>R AND START, THE COMPLETE SIGNATURE IS IN THE BIT PATTERNS<br>TION DISPLAY AS THE SELECTOR IS ROTATED THROUGH THE<br>NS.                                                  |

|                         |               | A SELECTED PORTION<br>DISPLAY FOR CONVE        | I OF THE BIT PATTERNS ARE DISPLAYED IN THE PULSE COUNTER<br>NIENCE.                                                                                                                                                                       |

|                         |               |                                                | Figure $1-11$ . Card Test Data Page 1                                                                                                                                                                                                     |

- 10. <u>THE NODE COUNTS ARE OBTAINED BY INSERTING THE TEST PROBE INTO JACK</u> <u>PCP AND CONNECTING TO THE APPROPRIATE PIN.</u> THE SELECTOR SWITCH MUST BE SET TO OFF OR NODE COUNT AND THE PB SWITCH TO NO/FB. CLEAR AND START WILL RESULT IN A DISPLAY OF THE NODE COUNT NUMBER IN THE PULSE COUNTER DISPLAY. (SEE NOTE 1) <u>THE RECYCLE SW ALLOWS CONTINUOUS CYCLES</u>.

- 11. TO FACILITATE STATIC TESTING OF INDIVIDUAL CHIPS OR SMALL CIRCUIT STRINGS, A CHIP CLIP IS PROVIDED. THE CLIP CABLE IS PLUGCED INTO FOOR FLOF THE TESTER AND THE SELECTOR SWITCHED TO THE SAME POSITION IF THE CLIP IS THEN ATTACHED TO A CHIP, THE STATE OF EACH CHIP PIN (EXCEPT E, M AND L) WILL BE DISPLAYED IN THE CORRESPONDING CARD PIN DISPLAY INDICATOR. IN ADDITION, A TRUE LEVEL CAN BE PLACED ON EACH PIN BY MOVING THE APPROPRIATE PIN SELECT SWITCH TO TRUE (UP) AND DEPRESSING THE INITIAL SWITCH. (THE CHIP CLIP MUST BE ORIENTATED WITH THE CABLE EXITING DOWNWARD.)

- **3.** THE TESTER SELF-CHECKING FEATURE IS PERFORMED WITH NO CARD INSERTED, ALL SWITCHES IN NORMAL. <u>CLEAR AND START</u> SHOULD RESULT IN THE SIGNATURE DISPLAYED BELOW IF THE TESTER HAS BEEN PROPERLY INITIALIZED AS DESCRIBED IN ITEM 3. (THIS TEST IS DONE IN THE FB MODE).

| Figure | 1 - 11. | Card | Test | Data | Page | 1 ( | (cont'd). |  |

|--------|---------|------|------|------|------|-----|-----------|--|

|--------|---------|------|------|------|------|-----|-----------|--|

|    | Α | В | С | D | E  | F | G | Н | Ι                     | J | K                  | L | М | N   | Р | Q | R  | S        | Т     | U  | V          | W | Х | Y | Z  |      |

|----|---|---|---|---|----|---|---|---|-----------------------|---|--------------------|---|---|-----|---|---|----|----------|-------|----|------------|---|---|---|----|------|

| FO |   |   |   |   | ŁŞ |   |   |   |                       |   | inne line          |   |   | 1   |   |   | °. |          |       |    | 1          |   |   | ł |    | 0725 |

| F1 |   |   |   |   |    |   | 1 |   |                       |   | 1                  |   |   |     |   |   | 1  |          |       |    |            |   |   | 1 |    | 0725 |

| X0 |   | 1 | 1 |   |    |   | . | 1 |                       |   |                    |   |   |     | 1 |   | 1  | 1.25<br> | 1     | 1. | : <b>]</b> |   | 1 | 1 | 1  | 7777 |

| X1 |   |   |   |   |    |   |   | ĺ |                       |   | - 1 <sup>° -</sup> |   | t | , ŝ |   |   |    |          | 1     |    | 12         |   |   |   | ÷. | 2330 |

| Y0 |   | 1 |   | 1 |    |   |   |   |                       |   |                    |   |   |     |   |   |    |          | :   · |    |            |   |   |   |    | 2400 |

| Y1 |   |   | - |   |    |   |   |   | (1)<br>국가<br>국가<br>14 |   |                    |   |   |     |   |   | 4  |          | I.    | 1  |            |   |   | 1 |    | 7577 |

- \* THE TESTER MUST HAVE BEEN INITIALIZED AND CLEARED. IF THE NODE COUNTER IS HOLDING INFORMATION THIS MUST BE CLEARED BY REMOVING THE NODE COUNT PROBE FROM ANY CIRCUITRY AND CYCLING THE TESTER.

- NOTE 1.ZERO COUNTS ON THE NODE COUNT LISTINGS CAN BE EXPRESSED IN SEVERAL WAYS AS FOLLOWS:

- [ TRUE ] ZERO COUNT RESULTING FROM A CONSTANT TRUE [CTR. CYCLES DURING TEST] \$\$

- [FALSE] ZERO COUNT RESULTING FROM A CONSTANT FALSE [CTR. DOES NOT CYCLE] 0000

- [CLOCK] ZERO COUNT RESULTING FROM A CLOCK SIGNAL OR SYNCHRONISM BETWEEN THE FALSE GOING SIGNAL AND THE TESTER CLOCK.

- [0000] ZERO COUNT RESULTING FROM AN EVEN MULTIPLE OF 7777 (OCTAL) + 1.

- [INCOM] ZERO COUNT RESULTING FROM INCOMPATIBLE LOGIC LEVELS.

- NOTE: WHERE MULTIPLE NODE COUNTS ARE LISTED, ZEROS ARE NOT SIGNIFICANT.

7.

8.

#### ACCESSORIES

#### DESCRIPTION and USE

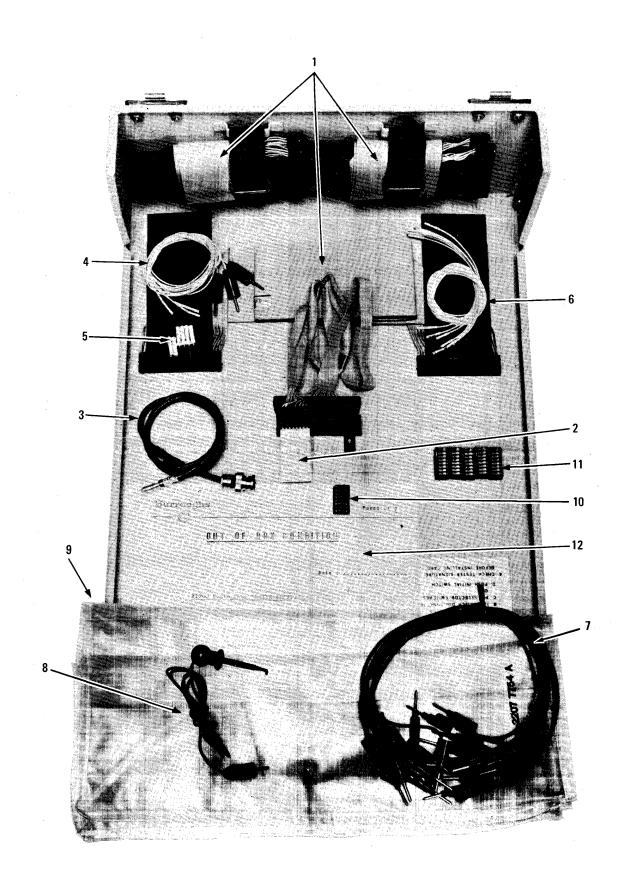

All FCT accessories as shown in Figure 1-13, are identified by a number which is referenced to the following text.

1. Frontplane Cables

PN 2207 5402 Quantity: 3.

- These flat ribbon cables are used to connect the FCT frontplane connectors F0, F1 to any card frontplane connector.

- 2. Chip Clip

PN 2207 7689 Quantity: 1.

The chip clip can be used to statically test any logic chip soldered to the card. The clip is connected to the chip required and the cable end inserted into either frontplane connector F0, F1. Various logic levels can be applied to the chip thru the operating panel. The card pin section display will indicate the logic state of each chip pin.

3. Coaxial Clock Cable

PN 2206 5197 Quantity: 1. Used to connect the FCT to an external clock generator.

4. Tester to Card Jumpers

PN 2207 7713 Quantity: 3.

Used in special cases to apply a true level or signal from the tester output jacks to specific card pins. Alternatively connected to the PCP jack and used as a card pin probe whilst Node Counting any card pin.

#### 5. Insulated Jumper Pins

PN 2207 7747 Quantity: 6.

These are used to connect card pins with two wire wrap levels to standard point to point card pin jumpers.

#### 6. Point to Point Card Jumpers

PN 2207 7705 Quantity: 8. Specifically used to re-route logic signals between card pins when locating logic faults.

#### Point to Point Jumpers

PN 2206 0644 Quantity: 10. Commonly used to connect card pin jacks and tester output jacks together according to Card Test Data instructions.

Pulse Counting Probe

PN 2206 9116 Quantity: 1.

Specifically used when node counting, to connect any logic point to the PCP jack. The probe is composed of spring loaded expanding clip to connect to any logic pin or discrete component.

9. Plastic Cover.

PN 2207 7754 Quantity: 1 A waterproof plastic cover is provided to protect the FCT electronics from water during transportation in bad weather.

10. Jumper Chip

PN 2210 7437 Quantity: 1 A standard 16 pin jumper chip.

11. DIP Switch

PN 2210 1778 | Quantity: 5

These dual-in-line package switches (DIP) are inserted into specific DIP sockets on logic cards during the testing procedure.

12. Check List

This check list is not an accessory. The "out of box" check list is applicable to new Liege manufactured FCT s. Details of transportation damage and FCT self checking tests must be reported on this list and returned using the pre-addressed envelope.

Figure 1–13. Field Card Tester Accessories.

## LOGIC SIGNAL GLOSSARY

CL Card.

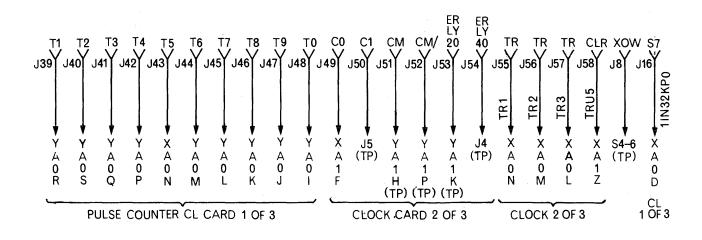

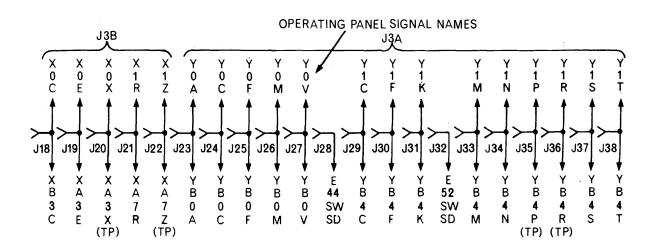

Page 1 of 3

| LOGIC FUNCTION AND LOCATION                                                                                   | LOGIC SIGNAL, INPUT/OUTPUT PIN(S).                                                                     |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| CLEAR ALL SECTION REGISTERS<br>F0,F1,X0,X1,Y0,Y1                                                              | Output term CLEARQ - CLRQ/1                                                                            |

| CLEAR CLOCK COUNTER                                                                                           | CLEAR A<br>True during Start Sequence                                                                  |