# **Bolt Beranek and Newman Inc.**

**Technical Information Report No. 99**

## The ARPANET Pluribus IMP Program

Volume I: Introduction, the IMP Algorithm, the STAGE System

May 1978

Prepared for: Defense Communications Agency

t

Bolt Beranek and Newman Inc.

Technical Information Report No. 99

THE ARPANET PLURIBUS IMP PROGRAM

Volume I

Introduction, The IMP Algorithm, The STAGE System

May 1978

#### Volume I

## TABLE OF CONTENTS

| Chapter | l Int          | r od uc t | tion           | •     | •   | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 1  |

|---------|----------------|-----------|----------------|-------|-----|-------|--------------|-----|-----|-----|----|---|-----|-----|----|---|---|---|---|---|---|----|

| Chapter | 2 The          | IMP .     |                | • •   | •   | •     | •            | •   | • . | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 4  |

| 2•1 T   | he IMP         | Algon     | rithn          | a : . | Int | tro   | du           | ct  | io  | n   | an | d | 0 v | erv | ie | w | • | • | • | • | • | 9  |

| 2.1.    |                | s and     |                |       |     | •     |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 13 |

| 2.1.    | 2 Net          | work l    | Flow           | Co    | ntı | r o 1 |              | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 15 |

| 2.1.    | 3 End          | to Er     |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 16 |

| 2.      | 1.3.1          | Erroi     | r Red          | ov    | ery | y     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 20 |

| 2.      | 1.3.2          | Raw 1     | Packe          | ets   | •   | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | ٠ | • | ٠ | • | • | 21 |

| 2.1.    |                | to IN     |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 21 |

| 2.1.    | 5 Rou<br>6 IMP | ting .    | • • •          | •     | •   | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 25 |

| 2.1.    | 6 IMP          | Relia     | ab il :        | ity   | •   | •     | •            | •   | •   | • ' | •  | • | •   | • • | •  | • | ٠ | • | • | • | • | 25 |

| 2.1.    | 7 Tim          | eout a    | • • •          | •     | •   | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 29 |

| 2.2 0   | rganiz         | ation     | of 1           | la j  | or  | Mo    | du           | 1 e | s   | •   | •  | • | •   | • • | •  | • | • | ٠ | • | • | • | 29 |

| 2.2.    | 1 Mod          | em Ing    | out/(          | Jut   | put | t     | •            | •   | •   | •   | •  | • | •   | •   | •  | • | • | • | • |   | • | 30 |

| 2.2.    | 2 Hos          | t Inpi    | ut/01          | ıtp   | ut  | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 34 |

| 2.2.    |                | к .       |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 38 |

| 2.      | 2.3.1          | Store     | e-and          | 1 – F | orv | var   | d            | •   | •   | •   | •  | • | •   | •   | •  | • | • | • | • | • | • | 38 |

| 2.      | 2.3.2          | FORUS     | S .            | • •   | •   | •     | •            | •   | •   | •   | •  | • | •   | •   | •  | • | • | • |   | • | • | 39 |

| 2.2.    | 4 Rou          | ting A    | Algon          | rit   | hm  | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | • | • | • | • | • | 43 |

| 2.2.    |                | kgroui    |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

|         | 2.5.1          |           |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

|         | 2.5.2          | Backs     | rour           | nd    | Ноя | st    | 6            |     |     |     | •  |   |     |     |    |   |   | • |   |   |   | 47 |

| 2.      | 2.5.3          | Back      | 2 ° 0 111      | n d   | Ho  | st    | 7            |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

|         | 2.5.4          | Backg     | , <b>r</b> our | nd i  | НО  | et.   | à            | •   |     | •   | •  | • |     |     |    |   | • | • | • | • |   | 49 |

| 2.2.    |                | e Host    |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

|         | 2.6.1          | Fake      |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 50 |

|         | 2.6.2          | Fake      |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 50 |

|         |                | Fake      |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

|         | 2.6.4          | Fake      |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

|         | 7 Ver          |           |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   | • |   |   | 52 |

| 2•2•    |                | iabil:    |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   | 52 |

|         |                |           |                |       |     |       |              |     |     |     |    |   |     |     |    |   |   |   |   |   |   |    |

| 2•      | 2.8.1          | BUIIC     | er Ke          | 911   | aD  | 111   | . <b>t</b> y |     | •   | •   | •  | • | •   | •   | •  | • | • | • | • | • | • | 55 |

|         |                | Coun      | ters           | •     | •   | •     | •            | •   | •   | •   | •  | • | •   | • • | •  | • | ٠ | • | • | • | • | 54 |

| 2.      | 2.8.3          | Cros      | sed            | or    | LO  | ope   | ed .         | Qu  | еu  | les |    | • | •   | • • | •  | • | • | • | • | • | • | 55 |

| Chapter | 3 The          | STAG      | E Svs          | ste   | m   | •     | •            | •   | •   | •   | •  | • | •   | •   |    | • |   | • |   |   | • | 57 |

| 3.1 I   | Introdu        | ction     | and            | 0v    | er  | vie   | W            | •   | •   | •   | •  | • | •   | • • | •  |   | • | • | • | • | • | 57 |

|         | interco        |           |                |       |     |       |              |     |     |     |    |   |     | •   |    |   |   | • | • | • | • | 58 |

|    | 1   | 3. | 2  | 1     | 5  | Se  | qu  | e | nc | iı  | ng  | t   | he  | : | ST. | A G | ξE | М  | o d | u. | 1 e | s  | •   |   | • | •   | •  | •  | • | • | • | • | • | • | 58 |

|----|-----|----|----|-------|----|-----|-----|---|----|-----|-----|-----|-----|---|-----|-----|----|----|-----|----|-----|----|-----|---|---|-----|----|----|---|---|---|---|---|---|----|

|    | 1   | 3. | 2  | 2     | 2  | [ n | te  | r | pr | 0 0 | сe  | s s | o r |   | Co  | n t | r  | o1 | а   | no | ł   | St | r i | p | Ί | 'im | ir | ıg | • | • | • | • | • | • | 58 |

|    | -   | 3. | 2  | . 3   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 59 |

|    |     | 3. | 2  | . 4   | ]  | FI  | XI  | Т | W  | 0 1 | rd  | s   | •   | • | •   |     | ,  | •  | •   | •  | •   | •  |     |   | • | •   | •  | •  | • | • | • | • | • | • | 60 |

| 3  | 3.: | 3  | I  | ) a t | :a | В   | a s | e | s  |     | •   | •   | •   | • | •   | •   |    | •  | •   | •  | •   | •  |     |   | • | •   | •  | •  | • | • | • | • | • | • | 61 |

|    |     | 3. | 3. | 1     | ]  | Pa  | g e |   | Гу | pe  | e s |     | •   | • | •   |     | ,  | •  | •   | •  | •   | •  |     |   | • | •   | •  | •  | • | • | • | • | • | • | 61 |

|    |     | 3. | 3  | 2     | ]  | Pa  | g e |   | Fo | r   | na  | t   | •   | • | •   |     | ,  | •  | •   | •  | •   | •  |     | , | • | •   | •  | •  | • | • | • | • | • | • | 62 |

| .3 | 3.2 | Ύ  | ]  | [ n t |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 65 |

|    |     |    |    | • 1   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 65 |

|    | 2   | 3. | 4. | • 2   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 66 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 67 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 67 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 67 |

| 3  |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 68 |

|    |     |    |    | 1     |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 68 |

|    | 2   | 3. | 5  | • 2   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 69 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 70 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 72 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 72 |

|    |     |    |    | • 4   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 73 |

|    |     | 3. | 5  | • 5   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 74 |

|    |     |    |    | • 6   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 75 |

|    |     |    |    | • 7   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 75 |

|    |     |    | -  | • 8   |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 75 |

|    |     |    |    | .9    |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 76 |

|    |     |    | -  |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 79 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 80 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 81 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   | 83 |

|    |     |    |    |       |    |     |     |   |    |     |     |     |     |   |     |     |    |    |     |    |     |    |     |   |   |     |    |    |   |   |   |   |   |   |    |

5/78

.

### Volume II

## Table of Contents

| Foreword  |                                                 | • | • | • | • | • | vii |

|-----------|-------------------------------------------------|---|---|---|---|---|-----|

| Chapter 4 | The Debugging System DDT                        |   | • | • |   |   | 1   |

| •         | Command Summaries                               |   |   |   |   |   | 2   |

| 4.1.1     | Addresses, Opening and Closing                  |   |   |   |   |   | 2   |

| 4.1.2     | Type Out Modes                                  |   |   |   |   |   | 3   |

| 4.1.3     | Other Type Out Commands                         | • | • | • | • | • | 4   |

| 4.1.4     | Type In                                         |   |   |   |   |   | 5   |

| 4.1.5     | Address Spaces                                  |   |   |   |   |   |     |

|           | Control                                         | • | • | • | • | • | 7   |

|           | IMP Version Features                            |   |   |   |   |   |     |

| 4.1.8     |                                                 |   |   |   |   |   | 9   |

| 4.2 Cont  | crol Structure of DDT                           |   |   |   |   |   | 9   |

|           | cection, Override                               |   |   |   |   |   | -   |

| 4.4 Debi  | agging Environment of DDT                       |   |   |   |   |   | 11  |

| 4.5 Debu  | 1gging Mode • • • • • • • • • • • • • • •       |   | • |   |   | • | 13  |

|           |                                                 | - | - | - | - | - |     |

| Chapter 5 | Detailed Program Descriptions                   | • |   | • | • |   | 15  |

|           | ge System • • • • • • • • • • • • • • • • • • • |   |   |   |   |   |     |

| 5.1.1     | Stage LK - Local Kernel Checks • • • • •        |   |   |   |   |   |     |

| 5.1.2     | Stage MD - Common Memory Discovery              |   |   |   |   |   |     |

| 5.1.3     | Stage RK - Reliability Page Kernel Check        |   |   | • |   |   | 22  |

| 5.1.4     | Stage BD - Common Bus Discovery                 |   |   |   |   |   |     |

| 5.1.5     | Stage CD - Bus Coupler Discovery                |   |   |   |   |   |     |

| 5.1.6     | Stage RC - Reliability Page Check               |   |   |   |   |   |     |

| 5.1.7     | Stage LC - Local Page Checksum • • • • •        |   |   |   |   |   |     |

| 5.1.8     | Stage MC - Common Memory Checksums              |   |   |   |   |   |     |

| 5.1.9     | Stage MM - Common Memory Management             |   |   |   |   |   |     |

| 5.1.10    |                                                 |   |   |   |   |   |     |

|           |                                                 |   |   |   |   |   |     |

| 5.1.11    |                                                 |   |   |   |   |   |     |

| 5.1.12    |                                                 |   |   |   |   |   |     |

| 5.1.13    |                                                 |   |   |   |   |   |     |

|           | Illegal Instruction Interrupt Handler .         |   |   |   |   |   |     |

|           | Level 1 Interrupt Handler                       | • | • | ٠ | ٠ | ٠ | 43  |

| 5.1.16    |                                                 | ٠ | • | • | • | ٠ | 44  |

| 5.2 IMP   | System Central Dispatch                         | ٠ | • | • | ٠ | • | 46  |

|           | em to IMP • • • • • • • • • • • • • • • • • • • |   |   |   |   |   |     |

|           | to Modem                                        |   |   |   |   |   |     |

|           | t to IMP • • • • • • • • • • • • • • • • • • •  |   |   |   |   |   |     |

| 5.6 IMP   | to Host                                         | • |   |   |   |   | 56  |

4

iii

Bolt Beranek and Newman Inc.

| 5.7 | Tas     | sk .   |      | •   | •   | •     |         |      |      |    | •     |              |    | •  |    |    |   |   |   |    |    |   |   | _ |   | 59       |

|-----|---------|--------|------|-----|-----|-------|---------|------|------|----|-------|--------------|----|----|----|----|---|---|---|----|----|---|---|---|---|----------|

|     | .7.1    | Tasl   |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    | • | • |   |   |          |

|     | -       | Bacl   |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

| -   |         | 2.1    | Bac  |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     |         | 2.2    |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     |         | 2.3    |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     |         | 2.4    |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 73       |

| 5.8 |         | iting  |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 75       |

|     |         | ce Hos |      |     |     | •     |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     | •9•1    | TTY    |      |     |     |       |         |      |      |    |       |              |    | •  |    |    |   |   |   |    |    |   |   |   |   | 78       |

|     | • 9 • 2 | TTY    |      |     |     |       | -       |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 78<br>79 |

|     | • 9 • 2 | DDT    |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     |         |        |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   | -  |    | - | - | - | - | 80       |

|     | •9•4    |        |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     | •9•5    |        |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     | • 9 • 6 |        |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     |         | Sta    |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     | • 9 • 8 |        |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

|     |         | ery D  |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

| 5   | .10.    | 1 VD   | H Li | ne  | II  | nit   | ia      | 11 i | za   | ti | . o n | ı S          | ub | ro | ut | in | е | • | ٠ | •  | ٠  | • | • | • | ٠ | 91       |

| 5   | .10.2   |        | H Ez |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

| 5   | .10.1   |        | dem  |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   |          |

| . 5 | .10.4   | 4 VD   | H to | ) H | os  | t-c   | od      | le   | Co   | rc | ut    | in           | e  | •  | •  | •  | • | • | • | •  | ۰. | • | • | • | • | 96       |

| 5   | .10.    | 5 Ho   | st-d | cod | e   | to    | VD      | H    | Сc   | rc | ut    | :in          | e  | •  | •  | •  | • | • | • | •  | •  | • | • | • | • | 97       |

| 5   | .10.    | 6 VD   | Hto  | o M | od  | em .  | Co      | ro   | ut   | ir | ıe    | •            | •  | •  |    | •  | • | • |   | •  | •  |   | • | • | • | 98       |

| 5.1 | 1 T:    | imeou  |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 100      |

| 5   | .11.    | 1 Ho   |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 102      |

| 5   | .11.    | 2 Ba   | ck I | los | t ' | Tin   | iec     | ut   |      | •  | •     |              | •  | •  | •  | •  | • | • | • |    |    |   |   |   |   | 103      |

|     | .11.    |        | ow ! |     |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 104      |

| -   |         | 1.3.1  |      | ele |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 105      |

|     |         | 1.3.2  | R    | eas | sei | mb]   | Lv      | B1   | . 00 | k  | Ch    | iec          | k  | •  | •  | •  | • | • | - |    | •  | • | • | • |   | 106      |

|     |         | 1.3.3  | H    | bst | A   | с с е |         | <br> | h e  |    | sr    | . – -<br>1 m |    |    |    |    |   |   |   |    |    |   |   |   |   | 107      |

|     |         | 1.3.4  |      | Lne |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 108      |

|     |         | 1.3.5  |      | 4 P |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 110      |

|     |         | 1.3.6  |      | ent |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 111      |

|     |         | 1.3.7  |      | ran |     |       |         | -    |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 112      |

|     |         | 1.3.8  |      | eal |     |       |         |      |      |    |       |              |    |    |    |    |   |   |   |    |    |   |   |   |   | 114      |

|     |         | 1.3.9  |      | out | in  | о П   | <br>Гіп |      |      |    |       |              |    |    |    |    |   | • | • |    | •  | • |   |   |   | 115      |

|     |         | 1.3.1  |      | Inc |     |       |         |      |      |    |       |              |    |    |    |    |   | • |   |    |    | • | • |   |   | 117      |

|     |         | 1.3.1  |      | Rou |     |       |         |      |      |    |       |              |    |    |    | •  |   | • | • | •  | •  | • | • | • |   | 118      |

|     |         | 1.3.1  |      | Buf |     | -     |         |      |      |    |       |              |    |    |    |    |   | • | • | .• | •  | • | • | • |   | 119      |

|     |         |        |      |     |     |       |         |      |      |    |       |              |    |    |    |    |   | • | • | •  | •  | • | • | • |   |          |

|     |         | 1.3.1  |      | A11 |     |       |         |      |      |    |       |              |    |    |    |    | • | • | • | •  | •  | • | • | • |   | 121      |

|     |         | 1.3.1  |      | Mod |     | -     |         |      |      |    |       |              |    |    |    |    | • | • | ٠ | •  | •  | • | • | • |   | 122      |

|     |         | 1.3.1  |      | Buf |     |       |         |      |      |    |       | •            |    |    |    | ٠  | ٠ | ٠ | ٠ | ٠  | •  | ٠ | • | • |   | 124      |

|     |         | 1.3.1  |      | Tra |     |       |         |      |      |    |       |              |    |    |    | ٠  | ٠ | ٠ | • | ٠  | ٠  | • | ٠ | ٠ |   | 126      |

|     | 5.1     | 1.3.1  | .7.  | Age | e M | es    | sag     | gе   | B.   | LO | ck    | 5            | ٠  | ٠  | ٠  | ٠  | ٠ | ٠ | ٠ | ٠  | ٠  | ٠ | ٠ | ٠ |   | 127      |

5/78

8

|    |     |     | 5. | . 1 | 1.  | 3. | • 1 | 8   |     | IN          | 1 P | '-1 | gо  | 1  | ng  | -   | do  | ) W | n  | M  | es  | 3 5 | aş | зe      | С   | h e | ck |     | • | • | • | • | • | • | • | 129 |

|----|-----|-----|----|-----|-----|----|-----|-----|-----|-------------|-----|-----|-----|----|-----|-----|-----|-----|----|----|-----|-----|----|---------|-----|-----|----|-----|---|---|---|---|---|---|---|-----|

|    |     |     | 5. | . 1 | 1.  | 3. | . 1 | 9   |     | St          | t a | t   | i s | t  | ic  | : S | (   | Ch  | e  | ck |     | •   |    | •       | •   | •   | •  | •   | • | • | • | • | • | • | • | 130 |

|    |     |     | 5  | . 1 | 1.  | 3  | • 2 | 0   |     | Re          | e s | ti  | ar  | t  | E   | Bu  | fí  | Еe  | r  | С  | h e | e c | k  |         | •   | •   | •  | •   | • | • | • | • | • | • | • | 131 |

|    |     |     | 5  | • 1 | 1.  | 3  | • 2 | 1   |     | Fa          | a k | :e  | H   | lo | st  | :   | Sc  | ) f | t  | wa | re  | 3   | Cł | n e     | ck  |     | •  | •   | • | • | • | • | • | • | • | 132 |

|    |     |     | 5  | • 1 | 1.  | 3  | • 2 | 2   |     | Ba          | a c | k   | H   | lo | s t |     | Sc  | o f | t١ | wa | re  | e   | Cł | n e     | ck  |     | •  | •   | • | • | • | • | • | • | • | 133 |

|    |     |     | 5. | • 1 | 1.  | 3  | • 2 | 3   |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 134 |

|    |     |     | 5  | . 1 | 1.  | 3  | • 2 | 4   |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 135 |

|    |     |     |    | • 1 |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 136 |

|    | 5.  | 12  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 138 |

|    |     |     |    | 2.  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 142 |

|    |     | -   |    | 2.  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 143 |

|    | 5.  | 13  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 145 |

|    |     | 14  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 147 |

|    | -   |     |    | 4.  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 147 |

|    |     | 5.  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 149 |

|    |     | 5.  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 150 |

|    |     | 5.  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 151 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 152 |

|    |     | 5.  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 153 |

|    |     |     |    |     | -   |    |     | - 1 | . – |             |     | -   |     | -  |     | -   |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   |   |   |     |

| Ch | hap | te  | r  | 6   |     | Da | a t | a   | F   | <b>'o</b> 1 | rm  | ıa  | ts  | 3  |     |     | •   | •   |    | •  | • - | •   |    | •       | •   | •   | •  | •   | • | • | • | • | • | • | • | 155 |

|    | 6.  | 1   | (  | 01  | d – | S  | ty  | 16  | Э   | Le          | e a | ld  | er  |    | Fc  | r   | m a | at  |    | •  | •   | •   |    | •       | •   | •   | •  | •   | • | • | • | • | • | • | • | 155 |

|    |     |     |    |     |     |    | -   |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 156 |

|    |     | 3   |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 158 |

|    | 6.  | 4   | ]  | Ba  | si  | c  | P   | аc  | : k | e           | t   | S   | tr  | u  | c t | tu  | re  | e   |    | •  | •   | •   |    | •       | •   | •   | •  | •   | • | • | • | • | • | • | • | 159 |

|    |     | 6.  |    | • 1 |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 161 |

|    |     |     | 6  | • 4 |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 162 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 163 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 164 |

|    |     | 6.  |    | • 2 |     |    |     |     | -   | -           |     |     | -   |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     | - |   |   |   |   | • |   | 165 |

|    |     |     | 6  | • 4 |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 166 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 167 |

|    |     | 6.  | 4  | • 3 |     | Pa | аc  | ke  | e t | : 1         | t y | p p | е   | 2  | :   | R   | 01  | ut  | 1  | ng | ł   | an  | d  | n       | u1  | 1   | •  | •   | • | • | • | • | • | • | • | 168 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 170 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 170 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   |   |   |   | • |   | 170 |

|    |     |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         |     |     |    |     |   |   | • |   |   |   |   | 171 |

|    |     |     | Ť  | 6   | . 4 |    | 4.  | 3   | . 1 |             | D   | )a  | t a | Ì  | fc  | ) r | Ē   | S E | т  | ΠP | · . | ne  | S  | -<br>sa | ige | , Č |    |     |   |   |   |   |   |   |   | 172 |

|    | ·   |     |    |     |     |    | 4.  |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         | e e |     |    |     |   |   |   |   |   |   |   | 173 |

|    | 6.  | 5   | 1  | Mo  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    | •  |     |     |    | • 5     |     | -   | -  | -   |   |   | - | - | - |   | • | 174 |

|    | 6.  |     |    | Но  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    | -       |     |     | -  | -   | - |   | - |   | - |   | - | 177 |

|    | 6.  |     |    | Ba  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    | •       | -   |     | -  | •   | - |   | • | • | • | • | • | 180 |

|    | 6.  |     |    | Fa  |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    | •       | -   | -   | -  | •   | • |   | • | • | • | • | • | 181 |

|    | 6.  |     |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         | r   | B1  | -  | k s | - |   |   | - | • |   | - | 183 |

|    |     | 10  |    |     |     |    |     |     |     |             |     |     |     |    |     |     |     |     |    |    |     |     |    |         | •   |     |    |     |   |   |   | - | - |   | - | 185 |

|    | -   | _ • |    | -   |     |    |     |     | -   |             |     |     | - 0 |    |     | -   |     | •   |    |    |     |     |    | -       | -   | -   | -  | -   | - |   | - | - | - | - | - |     |

v

#### Bolt Beranek and Newman Inc.

6.11 Receive Message Block Table . . . . 187 • 6.12 Transaction Block Table . . . . . . • • • 189 . 6.12.1 Reserved Transaction Block Format . . . 189 . 6.12.2 Outstanding Message Transaction Block Format . 190 • 6.12.3 Control Message Transaction Block Format . . . 191 ٠ 192 • • 194 • ٠ • • • •

## Volume I

Table of Figures

| Figure | 1)  | Network Message Flow                                                                                                                                      |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 2)  | Network Protocols                                                                                                                                         |

| Figure | 3)  | Packet Flow and Processing 10                                                                                                                             |

| Figure | 4)  | Basic Loop in HI 17                                                                                                                                       |

| Figure | 5)  | Format of a Packet $\ldots \ldots \ldots$ |

| Figure | 6)  | Reliability Software                                                                                                                                      |

| Figure | 7)  | States of Module HI                                                                                                                                       |

| Figure | 8)  | States of FORUS                                                                                                                                           |

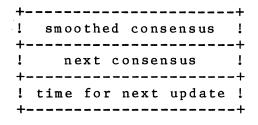

| Figure | 9)  | Consensus Words                                                                                                                                           |

| Figure | 10) | Organization of Common Memory • • • • • • • • • • 7                                                                                                       |

#### Volume I

## Table of Tables

Table 1) Half-count Values for Various Line Speeds . . . . . 33

.

#### Volume II

#### Table of Tables

| Table | 1) | DDT Error | Type-Outs. |            | • | ٠ | ٠ | • | ٠ | • | • | • | • | • | • | 10 |

|-------|----|-----------|------------|------------|---|---|---|---|---|---|---|---|---|---|---|----|

| Table | 2) | Simulated | Processor  | Registers. | • | • | ٠ | • | • | • | • | • | • | • | • | 12 |

| Table | 3) | Debugging | Mode Halt  | Type-Outs. | • | • | • | • | • | • | ٠ | • | • | • | • | 14 |

#### Chapter 1 Introduction

During the past decade, the technology of packet-switching has come into increasing use in the design and construction of computer networks. Networks using this technology are generally characterized by:

- A subnetwork of communications processors to which the host computers are connected.

- 2. A high degree of connectivity among the communications processors forming the nodes of this subnetwork.

- 3. The division of messages into packets, typically 1000 bits in length, by the communications processor to which the originating host is connected.

- 4. The dynamic routing of packets to the destination communications processor for reassembly and delivery to the host to which the message is addressed.

The pioneering, largest, and most advanced of these networks is the ARPANET(1) whose approximately 60 nodes currently net over 120 host computers; it has been in operation since 1969. Its basic technology has been adopted by computer networks in government and industry, both here and abroad, e.g., AUTODIN II, CTNE, CYCLADES, DATAPAC, DDX, EIN, EPSS, NPL, TELENET, TRANSPAC.

Some networks, e.g., EDN, COINS, PLATFORM, PWIN, use the same (or substantially the same) equipment and terminology as the ARPANET, including the communications processor which, for these networks, is called the Interface Message Processor (IMP). Two kinds of IMPs are in use: the Honeywell H-316(2) and the Bolt Beranek and Newman (BBN) Pluribus.(3)

"Selected Bibliography and Index to Publications about ARPANET," Becker and Hayes, Inc., Los Angeles, California, 1976.

NTIS AD-A026900.

(2) F.E. Heart, et al., "The Interface Message Processor for the ARPA Computer Network," AFIPS Conference Proceedings, Vol. 36, 1970, pp. 551-567.

(3) F.E. Heart, et al., "A New Minicomputer/Multiprocessor for the ARPA Network," AFIPS Conference Proceedings, Vol. 42, 1973, pp. 529-537. The message packet processing functions performed by a Pluribus IMP are the same as those of a H-316 IMP, but there are significant differences in the manner in which their programs are designed and implemented. These differences are dictated by the architectural differences between the two types of computers. The H-316 is a single-processor, interrupt-driven machine while the Pluribus is a multiprocessor which uses parallel processing and a priority ordered Pseudo Interrupt Device (PID) to control the sequence of execution of all program tasks and the servicing of I/O devices to achieve real-time response.

The Pluribus consists of processors, memory modules, I/Odevices, buses over which these communicate, and bus couplers to interconnect the individual buses. Within this framework, a wide variety of systems can be configured, ranging from small single-bus machines to large multibus systems with tens of processors, up to 1024K bytes of main memory, and many diverse devices. I/0 Pluribus A11 processors are functionally equivalent; any processor can perform any system task and control any device.

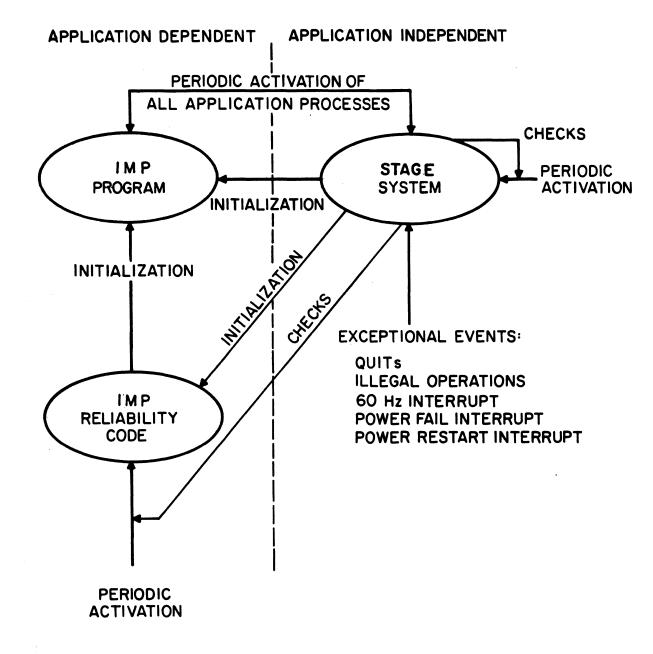

The principal responsibility for maintaining reliability in the Pluribus is placed on its software. The Pluribus hardware was designed to provide an appropriate vehicle for the software reliability mechanism. When hardware errors are detected, the software exploits the redundancy of the hardware by constructing a new logical system configuration which excludes the failing resource, using redundant counterparts in its place. A small hierarchical operating system called STAGE(4) coordinates the software reliability mechanisms involved.

The H-316 IMP program has been documented in BBN Technical Information Report No. 89, The Interface Message Processor Program, March 1977 (periodically updated). The purpose of the present report is to document the Pluribus IMP program. The report is divided into two volumes. Volume I contains, in addition to this introduction, descriptions of the IMP and STAGE system programs; the debugging system DDT, detailed program descriptions, and data formats are included in Volume II. Α general familiarity with packet switching and with the Pluribus architecture, e.g., as described in Pluribus Document 2, System Handbook, (BBN Report No. 2930), will be helpful in using and understanding the present report. Unless otherwise stated, a11

(4) J.G. Robinson and E.S. Roberts, "Software Fault-Tolerance in the Pluribus," AFIPS Conference Proceedings, Vol. 47, June 1978. 5/78

numbers are decimal; where hexadecimal numbers are used, they are followed by a "!".

As a final note, it is pointed out that some networks, e.g., Platform, use Pluribus IMPs with memory and I/O devices on the same bus, called an M/I bus. The Pluribus program treats these buses as if they were separate I/O and memory buses. In line with this approach, the discussion in the body of this document is functionally oriented and the reader should keep in mind that, for machines with M/I buses, all references to memory or I/O buses actually refer to the memory or I/O space of the M/I bus. The single instance involving a routine that deals specifically with the M/I bus structure is discussed in Section 3.5 (Stage CD).

#### Chapter 2 The IMP

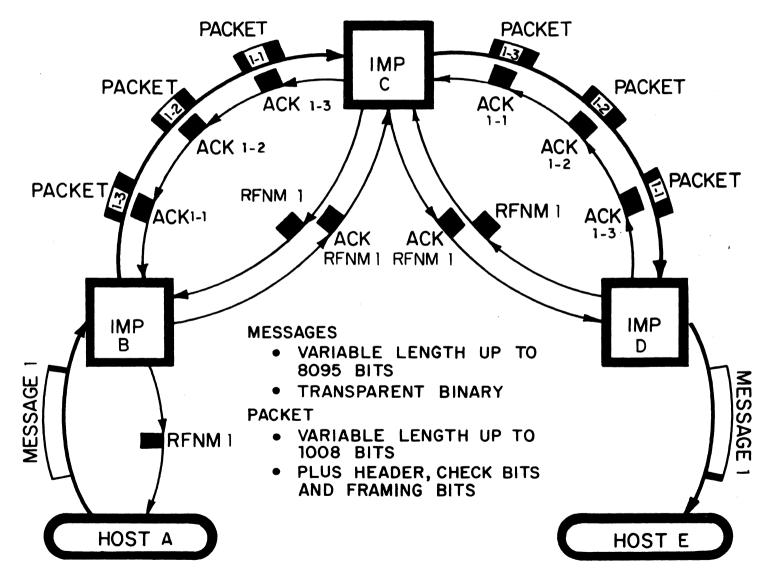

This chapter describes the algorithms that the IMP uses in performing its functions as a network communications processor. The flow of messages through the network is illustrated in Figure The host sends the IMP a <u>message</u> up to long, 1. 8063 bits preceded by a leader which specifies its destination. The source IMP accepts the message in <u>packets</u> up to 1008 bits long. Each packet has a header to allow for the transmission from IMP to IMP.(5) Figure 1 demonstrates how message 1 is transferred from IMP to IMP in three packets, numbered 1-1, 1-2, and 1-3. When a packet is successfully received at each IMP, an acknowledgement or ack is sent back to the previous IMP. Inter-IMP acks are shown returning for each packet. Finally the message arrives at the destination IMP where it is reassembled: that is, the packets are recombined into the original message. The message is sent to the destination host and a <u>Ready for Next Message</u> (RFNM) sent back to the source host. A RFNM is a unique, one-packet is message and it is acknowledged at each IMP to IMP hop on its return path.

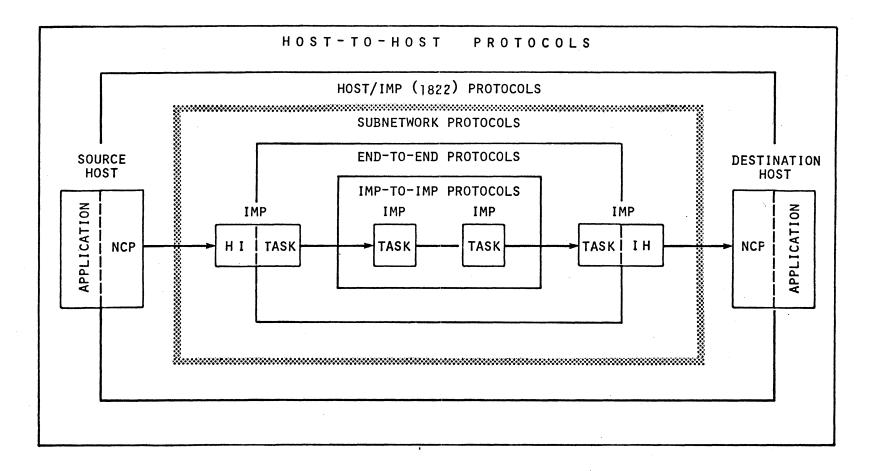

As shown in Figure 2, several layers of nested protocols are involved in transmitting a message between application programs in different hosts, as follows:

- <u>Host-to-Host</u>. Protocols between source and destination hosts.

- 2. Host/IMP. Protocols between a host and its local IMP.

- 3. Subnetwork. Protocols between IMPs.

- 4. <u>End-to-End</u>. Protocols between source and destination IMPs.

- 5. <u>IMP-to-IMP</u>. Protocols between adjacent IMPs serving as store-and-forward nodes.

(5) Note the distinction between the leader, which appears at the beginning of a message as it passes between a host and an IMP, and a header, which appears in front of a packet in an IMP or in transit between IMPs.

Figure 1. Network Message Flow

Page 5

Page 6

5/78

5/78

The highest level of protocol in the network is the host-to-host protocol governing the transmission of messages from a source to a destination host. A message originating in a host's application program is passed to that host's Network Control Program (NCP) which performs all communication between its host and the network. The host-to-host protocols are implemented in the NCP. They establish the rules by which the conversation between the source and destination hosts will be held. This permits two architecturally different hosts to communicate.

The next protocol level is the host/IMP protocols which enables the host's NCP to pass a message on to the local IMP. This is accomplished by following the so-called "1822" protocol "Specifications for described in BBN Report No. 1822, the Interconnection of a Host and an IMP." That document defines the hardware interface between a host and an IMP and specifies the protocol to be followed in transmitting messages between them. The host's NCP casts the message into the proper format and precedes it by a leader which specifies such data as the destination host's network address, the message's priority, etc. It then takes the appropriate hardware actions to transmit the and message to the IMP. At some subsequent time, the IMP leader to which the receiving host is connected receives the message and passes it to the host through its own 1822 interface.

The remaining lower protocols are implemented between the IMPs of the subnetwork and no longer concern the participating hosts. This is indicated in Figure 2 by the shaded box.

The next protocol level is the <u>end-to-end</u> message protocol. source IMP receives the message through the 1822 interface The and passes it to the host-to-IMP (HI) module. The information from the leader is stored in a transaction block, a data area reserved for the purpose, and the leader is examined to determine the addressee. For data to flow in the network, a conversation initiated with the destination IMP must be unless such a conversation already exists. A series of protocol messages is transmitted back and forth between the source IMP and the destination IMP, resulting in a transmit message (TM) block in the source IMP and a receive message (RM) block in the destination IMP. When each IMP knows of the existence and identity of the relevant block in the other, the conversation has Note that "conversation" is a technical term initiated. been referring to a one-way transmission of data. Although control messages pass in both directions in a conversation, data move in one direction only. (A two-way exchange between hosts actually involves two conversations in the IMP subnetwork.) Once a conversation has been initiated, it may be used for many messages; it is terminated automatically by the IMP subnetwork when it falls into disuse.

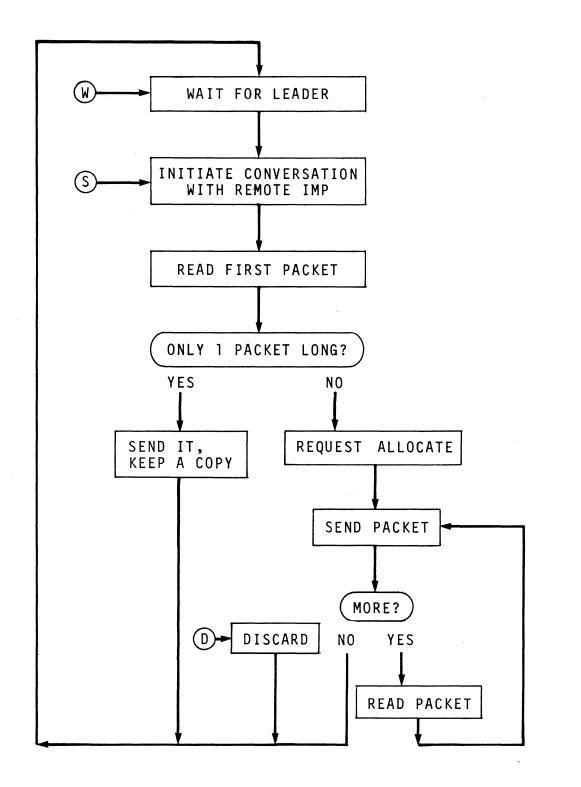

Having initiated the conversation, the host-to-IMP module (HI) in the source IMP breaks the message into packets up to 1008 bits long and invokes the basic store-and-forward module TASK to send each packet to the destination IMP. TASK is called upon to transmit only one packet at a time. Once the message has been received at the destination IMP, the module TASK in the destination IMP invokes the IMP-to-host module (IH) to transmit the message to the destination host. Notice that this level of discussion starts with a message received in the IMP through HI which is passed off to TASK in that IMP, and that TASK in the destination IMP passes the message through IH to the receiving host. All processing just described takes place even if both hosts are connected to the same IMP.

The next level of discussion involves the transmission of a single packet from one IMP to another. TASK is invoked by handing it a packet which it is to move towards its ultimate destination. Such packets may arise from either of two sources: from HI as just described, or from an adjacent IMP. The effect is the same in either case.

When an IMP receives a packet, that packet is either to a host connected to this IMP or to a host connected addressed to some other IMP. In the latter case TASK must determine the the packet's route. IMP has several Each next 1eg of communication links connecting it to adjacent IMPs, and TASK must determine which of these links is the best one to the destination, given the present state of the network. The routing algorithm gathers data about the current status of network traffic and transmits these data periodically from one IMP to The results of this data gathering operation are used another. to create tables which TASK can interrogate to determine, for any given destination IMP, the best line over which to transmit the packet. Since routing messages are received periodically by each IMP, successive packets of a message may be transmitted via different routes, leading to the possibility that the packets are received at the destination IMP out of order. (New routing information may reveal a less busy route, so that a subsequent packet may travel more rapidly than an earlier one.) For this reason, the IMP algorithms are designed to reassemble the packets of a multi-packet message in the proper order.

5/78

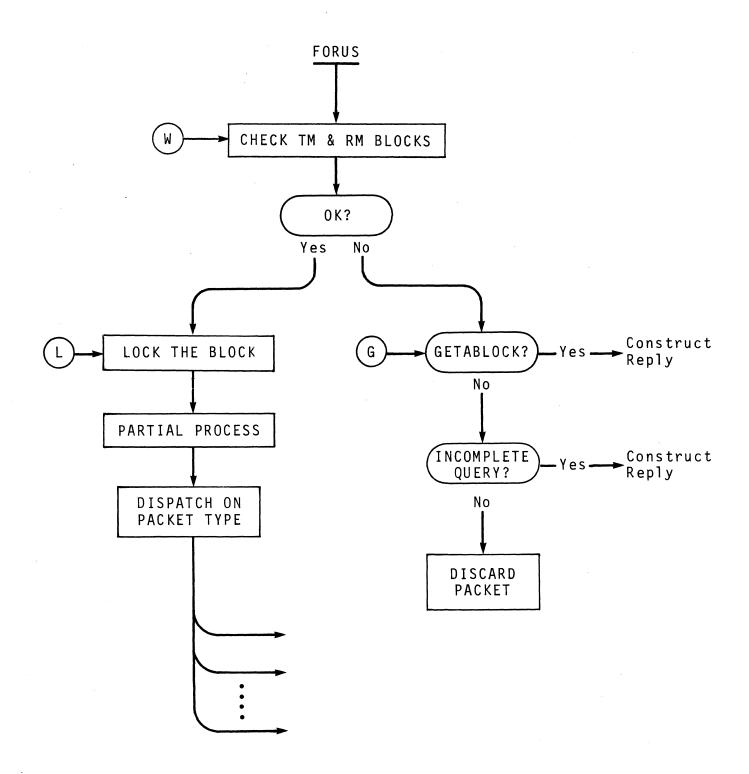

Having determined the line over which to transmit the packet, TASK then transmits it to an adjacent IMP (which may or may not be the destination IMP). TASK in that IMP goes through an identical process. This process continues until the packet arrives at the destination IMP, at which time TASK passes it to the module FORUS which performs the necessary reassembly of the packets into a message. FORUS also insures that messages are passed to the host in proper order.

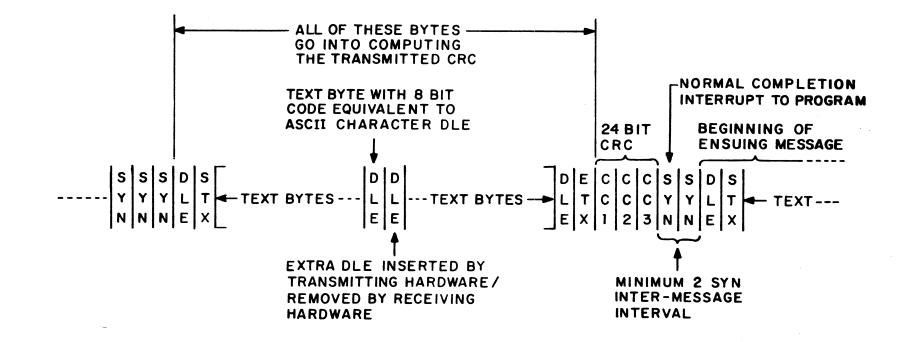

A final protocol is the low-level IMP-to-IMP protocol, which governs usage of the communication links between IMPs. Each physical link between IMPs is divided (by the software) into up to 128 logical channels, so that up to 128 packets at a time may be in transit in each direction between each pair of IMPs. The channel concept permits each IMP to initiate transmission of subsequent packets over a link before receiving acknowledgement of the successful transmission of the first. Note the distinction between the end-to-end protocol and the low-level IMP-to-IMP protocol. The former is concerned with the concept of the conversation, the latter with channels.

#### 2.1 The IMP Algorithm: Introduction and Overview

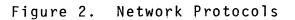

The data flow through the IMP is shown in Figure 3, a schematic drawing of packet processing. The processing programs are described below.

The host-to-IMP routine (HI, shown in the lower left corner οf the figure) handles messages being transmitted into the IMP from a local host. The routine first accepts the leader to construct a header that is prefixed to each packet of the message. It then accepts the first packet and, if no allocation of space exists for the destination IMP, constructs a request for buffer allocation which it places on TASK's queue. A single-packet message is placed directly on the task queue regardless of allocation status and a copy is held in the transaction block until either a RFNM or allocation is returned. Α returned RFNM causes the packet to be released (since the message has been received), while a returned allocation for the single-packet message causes retransmission by TASK. Requests for multi-packet allocation are sent without actual message data. The request is recorded at the destination IMP and an allocation message is returned by a background process as soon as space is available. A returned allocation causes HI to place the first packet with header on TASK's queue. Input of the rest of the message is then accepted from the host. HI also verifies the

Figure 3. Packet Flow and Processing

Page 10

5/78

message format. The routine is reentrant and services all hosts connected to the IMP.

The modem-to-IMP routine (M2I, shown in the upper right corner of the figure) handles inputs from the modems through which the IMP is connected to the communication links. This routine first sets up a new input buffer, previously obtained from the free list. (That is, M2I performs double buffering.) a buffer cannot be obtained, the received packet is not If acknowledged and the buffer is reused immediately to read in the next packet. The discarded packet is retransmitted later by the distant IMP as soon as a timer runs out. M2I processes returning acknowledgements for previously transmitted packets and either releases the packets to the free list or signals their subsequent release to the IMP-to-modem routine. M2I then places the buffer on the end of TASK's queue.

TASK uses the header information to direct packets to their proper destination. It routes packets from the task queue either to a local host queue or onto an output modem determined from the tables. If the packet is for non-local delivery, TASK routing determines whether sufficient store-and-forward buffer space is available. If not, buffers from modem lines are flushed and no subsequent acknowledgement is returned by I2M. (Normally, an acknowledgement is returned with the next outgoing packet over Packets from hosts that modem line.) which cannot get store-and-forward space are freed by TASK and requeued at a later time by HI.

If a packet from a modem line is addressed for local delivery, its message number is checked to see whether a duplicate packet has been received. Each IMP maintains for each connection a window of contiguous message numbers which it will accept from the other end of the connection. Packets with out-of-range numbers are considered duplicates and are discarded. The receipt of a RFNM for the oldest message at the source IMP permits the window to be moved up by one number.

Replies such as RFNMs or Dead Host messages are placed in transaction blocks. TASK then pokes IH to initiate output to the host.

Message packets for local delivery are linked together with other packets of the same message number in a reassembly block. When a message is completely reassembled, the leading packet is linked to the appropriate host output queue for processing by IH. Incoming routing messages are processed by the routing program with high priority so that outgoing routing messages and the routing directory immediately reflect any new information received. M2I generates I-heard-you messages to indicate to the neighbor receipt of the routing message.

The <u>IMP-to-modem</u> routine (I2M) transmits successive packets from the modem output queues and sends piggybacked acknowledgements for packets correctly received by M2I and accepted by TASK.

The <u>IMP-to-host</u> routine (IH) passes messages to local hosts and informs a background process when a RFNM should be returned to the source host.

A <u>fake</u> host is a program in the IMP which acts like a real host in many ways, including being the source or destination of network traffic. The four fake hosts are:

- 1. Fake Host 0--The terminal connected to the Pluribus IMP.

- 2. Fake Host 1--The debugging process DDT.

- 3. Fake Host 2--The packet core process used to reload part of the memory should it be found to be incorrect.

- 4. Fake Host 3--Used for miscellaneous purposes such as reports to the NCC, message generation, etc.

Selected hosts and IMPs, particularly the Network Control Center (NCC), find it necessary or useful to communicate with one or more of these fake hosts.

The ΤΤΥ fake host assembles characters from the terminal into network messages and decodes network messages into TTY's characters for the terminal. default message ("crosspatch") destination is the DDT fake host at its own IMP. It can, however, be connected to any other IMP terminal, any other IMP's DDT fake host, or to any host program with compatible format.

DDT permits the operational program and its data to be inspected and changed. Although its normal message source is the TTY fake host at its own IMP, DDT responds to a message of the correct format from any source. This program is normally inhibited from changing the operational IMP program; NCC intervention is required to activate the program's full power.

5/78

The STATISTICS fake host collects measurements about network operation and periodically transmits them to a designated host. This program sends but does not receive messages.

The PACKET CORE fake host loads and dumps portions of its own IMP's memory, or acts as an intermediary in loading and dumping portions of the memory belonging to a neighbor who is unable to communicate via the normal IMP-to-IMP protocol. The PACKET CORE facility allows for dissimilar machines to coexist as IMPs on the network; reloading and diagnostic dumping of a malfunctioning IMP can be done without the requirement that one of its neighbors be of the same machine type.

<u>Background Hosts</u>. These are modules which are run periodically and search the IMP's data bases for certain tasks to perform. They send connection protocol messages, incomplete transmission messages, allocations, and RFNMs, as well as returning GIVEBACKs closing unused connections. The background hosts run in a slightly different manner than the fake hosts in that they do not simulate the host/IMP channel hardware. They do not go through the host/IMP code at all, but put their messages directly on the task queue. Nonetheless, the principle is the same.

#### 2.1.1 IMPs and Hosts

The software interface between an IMP and a host will now be defined; the details of the hardware interface are to be found in BBN Report No. 1822. Each IMP serves hosts whose cable distances from the IMP are less than 2000 feet. A modem channel must be used for greater distances; this latter type of host connection is termed a Very Distant Host (VDH) and is also discussed in BBN Report No. 1822.

Connecting an IMP to a wide variety of different local hosts requires a hardware interface, some part of which must be custom tailored to each host. The interface is therefore partitioned so that a standard portion can be built into the IMP which is identical for all hosts, while a special portion of the interface is unique to each host. The interface is designed to allow messages to flow in both directions at once; a bit-serial interface is used.

The host interface operates asynchronously, each data bit being passed across the interface via a four-way Ready-for-Next-Bit/There's-Your-Bit handshake procedure. This technique permits the bit rate to adjust to the rate of the slower member of the pair and allows necessary interruptions when words must be stored into or retrieved from memory.

A message from a host consists of a leader followed by data bits. The leader format was changed in late 1976 to accommodate more than 63 IMPs in the network and more than 4 hosts per IMP. Since some hosts have yet to be reprogrammed for the new format, the IMPs support either format although all internal processing in the IMP assumes new format. Any leader in old format is translated to new format immediately upon receipt by HI, and the format is changed just before transmission of a message by IH to a host using old format.

The format of the message leader provides a 16-bit field for IMP numbers, so that in principle there can be as many as 2\*\*16 IMPS. In practice, other restrictions limit the IMPs to being numbered between 1 and 67.(6) Host numbers are in an 8-bit field and may range from 0 to 255. Because of storage limitations, 26 (including fake hosts) is the maximum possible number of hosts. Four of these host numbers are reserved permanently for fake hosts, numbered 252 through 255, as follows:

252 local terminal 253 DDT, the debugging process 254 packet core 255 statistics, message generation/discard

The software for the fake host simulates 1822 hardware.

Messages intended for dead hosts (which are not the same as dead IMPs) cannot be delivered; they require special handling to avoid indefinite circulation in the network and spurious arrival at a later time. Such messages are purged from the network at the destination IMP. A host computer is notified about a dead host only when it attempts to send a message to it.

(6) IMP number 0 is not usable because of certain conventions in message fields, and 67 is the maximum number of fields transmittable in certain parts of routing information.

#### 2.1.2 Network Flow Control

A major hazard in a message-switching network is congestion, which can arise either from system failures or from peak traffic flow. Congestion typically occurs when a destination IMP becomes flooded with incoming messages for one or more of its hosts. If the flow of messages to this destination is not regulated, the congestion backs up into the network, affecting other IMPs and degrading or even completely clogging the communication service. To avoid this problem, the IMPs incorporate a quenching scheme that limits the flow of messages to a given destination before congestion begins to occur.

This quenching scheme requires that buffer space be allocated where it will be needed before a message may enter the system. If buffering is provided in the source IMP, one can optimize for low delay transmissions; while if the buffering is provided at the destination IMP, one can optimize for high bandwidth transmissions. To be consistent with the goal of a balanced communications system, the approach used utilizes some buffer storage at both the source and the destination as well as a request mechanism from source IMP to destination IMP.

Specifically, no multi-packet message is allowed to enter network until enough storage for the message has been the allocated at the destination IMP. As soon as the source IMP realizes that a message is multi-packet, it sends a control message to the destination IMP requesting that reassembly storage be reserved at the destination for this message. It does not take in further packets from the host until it receives an allocation message in reply.(7) The destination IMP queues the request and sends the allocation message to the source IMP when enough reassembly storage is free; at this point the source IMP accepts the (rest of the) message from the host and starts to send it to the destination.

Effective bandwidth is maximized for sequences of long messages by permitting all but the first message to bypass the request mechanism. When the message itself arrives at the destination and the destination IMP is about to return the Ready For Next Message (RFNM), the destination IMP waits until it has

(7) This is not completely accurate, since the double buffering scheme employed in HI permits two packets to be read in while waiting for the allocation. In the usual case, the allocation arives before the host interface must be blocked. adequate buffer and reassembly space for an additional multi-packet message and then piggybacks a storage allocation onto the RFNM. If the source host is prompt in answering the RFNM with its next message, an allocation is ready and the message can be transmitted at once. If the source host delays too long, or if the data transfer is complete, the source IMP returns the unused allocation to the destination. With this mechanism, the inter-message delay has been minimized and the hosts can obtain the full bandwidth of the network.

delay for a short message has been minimized by The transmitting it to the destination immediately upon its receipt from the host, retaining a copy in the source IMP. If there is space at the destination, the message is accepted at once and passed on to a host and a RFNM is returned, the source IMP discarding the message when it receives the RFNM. If there is not enough space, the destination IMP discards the message and queues within itself a request for allocation. (Effectively, it treats it as a request for space.) When space becomes available, the source IMP is notified that the message may now Ъе retransmitted. Thus, there is no setup delay at all in the vast majority of cases in which storage is available the at destination.

These mechanisms make the IMP network fairly insensitive to unresponsive hosts, since holding the source host to a transmission rate equal to the reception rate of the destination host prevents clogging the network with messages. Further, reassembly lockup is prevented because the destination IMP never has to turn away a multi-packet message destined for one of its hosts; reassembly storage has been allocated for each such message prior to its entry into the network.

#### 2.1.3 End to End Communications

To communicate, both source and destination IMPs must establish a record of the connection between them. This simplex connection, consisting of a Transmit Message (TM) block at the source, and a corresponding Receive Message (RM) block at the destination, is created and later removed using a special protocol which detects duplicate or missing messages. Each message transmitted as part of a conversation contains the index of the relevant block (TM or RM) at the far end. The connection is disallowed if the host/host access control mechanism does not permit that host pair to communicate. Every IMP maintains for each of its hosts a pair of Host Access Control (HAC) words in which each of the 16 bits represents one of sixteen logical subnetworks. The bits in one word signify membership in, and in the other word signify permission to communicate with, the subnetworks. A pair of hosts may communicate with each other only if they are members of the same logical subnetwork or if one is allowed to communicate with hosts in a subnetwork of which the other is a member.

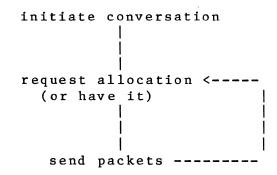

A conversation is a one-way message path from a source IMP to a destination IMP, where "one-way" means that data are transmitted in only one direction although control messages move in both directions. The basic control loop in HI that deals with conversations is shown in Figure 4. After going through some

Figure 4 Basic Loop in HI

initial protocol to set up the conversation, the two remaining steps are to request an allocation and to send packets. The action of requesting an allocate can be by-passed in the event that an allocation is available. (It may have been provided on the RFNM returned for the previous message.)

The message sent to the remote IMP to initiate a conversation is GETABLOCK, which asks that an RM block be set up. The receiving IMP replies either GOTABLOCK or CANT, depending

upon whether or not there is an available RM block which it can allocate for this conversation. If it finds such a block, then a conversation has been successfully initiated.

For each conversation, an independent message number sequence is maintained by each of the two participating IMPs, originating IMP maintaining it in the TM block and the the destination IMP in the RM block. The counter is incremented Ъv onė for each message sent over the conversation. The transmitting IMP assigns the message numbers in sequence, and the receiving IMP uses the same message number as part of the Since it is an inherent acknowledgement. property of the store-and-forward protocol that messages may arrive the at destination out of order, a window of eight messages is maintained, and the reassembly process is willing to accept any message within that window. (FORUS assures that messages are delivered to the host in proper order.) As it receives a message and acknowledges it to the source (by a RFNM), the transmitting moves the window up past each successfully acknowledged IMP message. The end-to-end protocol permits up to eight messages per conversation to be in the network at any time, thus allowing a host to send messages rapidly accross the network despite delays in returning RFNMs. If a host tries to get ahead by more than eight messages, the transmitting IMP blocks it. Messages arriving at a destination IMP with message numbers outside of the current window or with message numbers already marked as received are duplicates to be discarded. The message number concept two purposes: it orders the messages for delivery to the serves destination host, and it provides for the detection of duplicate missing messages. The message number is internal to the IMP and subnetwork and invisible to the hosts.

Α sequence control system based on а single source/destination connection, however, does not permit priority traffic to go ahead of other traffic. More generally, a host may request special treatment for a message; wish to thus, a is created for each "handling tvpe." separate connection Currently, there are two possible handling types: regular (for high bandwidth) and priority (for low delay).

When a request for an allocate comes in to an IMP with an associated message number, that message number should be in an idle state. (If the message number is busy, the allocation is a duplicate and is discarded.) FORUS puts this conversation in the state "need an allocate."

When an allocate is returned, it goes into the TM block. That is, a record is made in the TM block of the amount of space allocated. The originating host is blocked until the allocate is returned. When the source IMP receives the allocate, it starts Because of the double buffering in to send packets. the host-to-IMP interface, the source host may have already sent two packets. However, the IMP cannot receive more than that and does not attempt to do so until it has received word from the destination IMP that the storage allocation is available. It is for this reason that it is important that allocation processing be expedited; therefore, the destination IMP is willing to wait for up to half a second to be able to piggyback the allocation on a RFNM for a previous multi-packet message.

At the destination IMP, the packets are collected as they are received. The reassembly block contains a pointer to the first packet received, and each successive packet is threaded onto this packet list in the proper order for the message. Thus duplicate packets can be discarded as soon as they are received when the attempt to thread them onto the list reveals an already received packet with the same packet number. If a packet is lost, the source IMP sends an Incomplete Query message after 30-45 seconds.

Special processing is provided for single packet messages so that they can be transmitted expeditiously. Upon receiving a single packet message from the host, HI transmits it to the destination IMP as a request for an allocation of one block but also retains a copy in the transaction block. However, all of the data accompanies this request for allocation. The destination IMP attempts to find a buffer for the data and (if it is not the next message to go to the host) a reassembly block. If it is able to find both, then the message is complete; it is sent to the destination host and a RFNM is returned. If there is no available buffer and reassembly block, the message is treated as if it were merely a request for an allocation and the data that accompanied it is discarded. Eventually a reassembly block and a buffer are allocated and an allocation of one is sent to the source IMP.

#### 2.1.3.1 Error Recovery

Since packets are sent between IMPs via potentially unreliable communication links, procedures have been developed to detect and account for a lost packet or message. The IMP algorithm takes various steps to continue smooth operation even if packets or protocol messages are lost in transit. Some of the techniques employed are presented in this section.

The source IMP keeps track of all messages for which a RFNM has not yet been received, and the destination IMP keeps track of the replies it either has yet to send or has already sent. When the RFNM is not received for too long (about 30-45 seconds), the source IMP sends an "Incomplete Query" protocol message (using the same message number) to the destination, a message which inquires in effect, "What is the status of this message number?" If the destination has already received that message (that is, if the acknowledgement was lost in the network), then a duplicate acknowledgement is sent. If some part of the message was lost in transmission, the destination replies, "I've just received an incomplete message." This reply includes enough details about the error so that appropriate corrective action can be taken. At the very least, the originating host can be informed that the message was lost in transit. The source IMP continues inquiring This technique generally insures until it receives a response. that the source and destination IMPs keep their message number sequences synchronized and that any allocated space is released should a message become lost in the subnetwork because of а machine or communication line failure.

A conversation is terminated either after a prolonged period of inactivity, or after a somewhat shorter period of inactivity coupled with the need for the message block by some other connection, or by the need to resynchronize a message number sequence that has been broken. The special termination protocol can be initiated by either the source or the destination in the first two of the cases mentioned above, or by the source in the third case upon the receipt of an "out of range" response to an Incomplete Query. Upon closing a conversation, both source and destination IMPs release all resources held or allocated for that conversation.

#### 2.1.3.2 Raw Packets

The network provides a facility outside of the normal host/host connection mechanism for sending and receiving "raw These messages are identified by a special host-IMP packets." and IMP-host code and bypass the connection mechanism. They are routed normally through the subnetwork, but no sequencing, error control, reassembly, or storage allocation is performed. Thus. they may arrive out of order at the destination host, some packets may be missing or duplicated, or packets may be thrown away by the subnetwork if insufficient resources are available to No RFNMs or other messages are sent back to the handle them. source host about such raw packets. Since there is no flow control, a host can overload the net with raw packets and cause it to fail; therefore, a special privilege bit (in the host access word) is required for a host to be permitted to send them.

#### 2.1.4 IMP to IMP Communication

The preceding section dealt with the end-to-end protocol of sending messages from a source IMP to a destination IMP. At a lower level is the IMP-to-IMP protocol involved in sending individual packets from one IMP to another. This protocol is now discussed.

The mode of operation in connection with IMP-to-IMP transmission of packets is as follows: when a packet is transmitted from one IMP to another, the sending IMP retains a copy. When the IMP at the other end of the link has successfully received the packet, it acknowledges it to the sender. On receipt of that acknowledgement, the sender is able to release the buffer space in which the packet copy is held. If an acknowledgement is not received in time, the sending IMP merely retransmits the packet. The exact length of time an IMP will wait before retransmission depends on the type of line being used (land vs. satellite) as well as the bandwidth of the link (low speed vs. high speed).

A simple acknowledgement discipline applies to a channel,(8) a connection between one IMP and another. Over each channel, each packet is assigned a gender as being either even or odd;

(8) "Channel" is a technical term; a full definition will be found later in this section.

associated with each packet is a single bit which specifies the packet's gender. For a channel from IMP A to IMP B, every data packet or null sent back from B to A contains an acknowledgement (ACK) field specifying for each channel the gender of the last packet received from A. It is this field which provides the acknowledgement required by the IMP-to-IMP protocol. For example, after a packet of gender even has been transmitted from A to B, the ACK field in each packet sent back from B to A is examined. When that field shows that the channel status is even, IMP A knows that the packet has been received correctly and then that it is able to discard its copy and to transmit additional packets over the channel. The next packet it transmits then has gender odd, and again the acknowledgement is detected when the field in any packet from B to A indicates that the gender of ACK the channel is odd. Note that loss of a packet along with its associated ACK bits causes no harm other than a slight delay until the sender notes the acknowledgement, since the gender status is repeated in the next packet.