# **Bolt Beranek and Newman Inc.**

**Technical Information Report No. 99**

## The ARPANET Pluribus IMP Program

Volume II: DDT, Program Descriptions, Data Formats

May 1978

Prepared for: Defense Communications Agency Technical Information Report No. 99

## THE ARPANET PLURIBUS IMP PROGRAM

Volume II

## DDT, Program Descriptions, Data Formats

May 1978

## Volume II

## Table of Contents

| - 1                   |           |             |       |       |      |      |       |      |     |   |   |     |   | vii    |

|-----------------------|-----------|-------------|-------|-------|------|------|-------|------|-----|---|---|-----|---|--------|

| Foreword<br>Chapter 4 | The Debu  | • • •       | ••••  | •••   | •••  | ••   | •••   | •••  | • • | • | • | ••• | - |        |

| 4.1 DDT               | Command   | 18 g 1 ll g | Jyst  | em D. | DI   | • •  | • •   | • •  | • • | • | • | • • | • | 1<br>2 |

| 4•1 DD1<br>4•1•1      |           |             |       |       |      |      |       |      |     |   |   |     |   | 2      |

| 4 • 1 • 1 4 • 1 • 2   | Addresse  |             |       |       |      |      |       |      |     |   |   |     |   |        |

|                       | Type Out  |             |       |       |      |      |       |      |     |   |   |     |   | 3      |

| 4 • 1 • 3             | Other Ty  |             |       |       |      |      |       |      |     |   |   |     |   | 4      |

| 4.1.4                 | Type In   |             |       |       |      |      |       |      |     |   |   |     |   | 5      |

| 4.1.5                 | Address   |             |       |       |      |      |       |      |     |   |   |     |   | 6      |

| 4.1.6                 | Control   |             |       |       |      |      |       |      |     |   |   |     |   | 7      |

|                       | IMP Vers  |             |       |       |      |      |       |      |     |   |   |     |   | 8      |

|                       | Miscella  |             |       |       |      |      |       |      |     |   |   |     |   | 9      |

|                       | rol Stru  |             |       |       |      |      |       |      |     |   |   |     |   | 9      |

| 4.3 Prot              | ection,   | Overr       | ide   | • •   | ••   | • •  | • •   | • •  | • • | • | • | ••  | • | 10     |

| 4.4 Debu              | igging Er | nvironm     | nent  | of D  | DT   | • •  | • •   | • •  | • • | • | • | • • | • |        |

| 4.5 Debu              | igging Mo | ode.        | • •   | • •   | ••   | • •  | • •   | • •  | • • | • | • | ••• | • | 13     |

|                       |           |             |       |       |      |      |       |      |     |   |   |     |   |        |

| Chapter 5             | Detailed  |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1 Stag              | ge System | n ••        | • •   | • •   | ••   | • •  | • . • | • •  | • • | • | • | ••• | • | 16     |

| 5.1.1                 | Stage LI  | K - Loc     | al K  | erne  | 1 Ch | ecks | •     | • •  | • • | • | • | • • | • | 19     |

| 5.1.2                 | Stage MI  | ) - Com     | nmon  | Memo  | ry D | isco | very  |      | • • | • | • |     | • | 20     |

| 5.1.3                 | Stage RI  | K - Rel     | liabi | lity  | Pag  | e Ke | rnel  | . Ch | eck | • | • |     | • | 22     |

| 5.1.4                 | Stage BI  |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.5                 | Stage CI  | ) – Bus     | s Cou | pler  | Dis  | cove | ery   |      |     | • | • |     | • | 26     |

| 5.1.6                 | Stage R(  |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.7                 | Stage L(  |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.8                 | Stage M   |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.9                 | Stage Ml  |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.10                | Stage 1   |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.11                | Stage A   |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.12                | Block 1   |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.1.13                | Quit Ha   |             |       |       |      |      |       |      |     |   |   |     |   |        |

|                       | Illegal   |             |       |       |      |      |       |      |     |   |   |     |   |        |

|                       |           |             |       |       |      |      |       |      |     |   |   |     |   |        |

|                       | Level 1   |             |       |       |      |      |       |      |     |   |   |     |   | 43     |

| 5.1.16                | Level 4   |             |       |       |      |      |       |      |     |   |   | ••• |   | 44     |

|                       | System (  |             |       |       |      |      |       |      |     |   |   |     |   | 46     |

|                       | em to IMI |             |       | • •   |      |      |       |      |     |   |   |     |   |        |

|                       | to Moder  |             |       | • •   |      |      |       |      |     |   |   |     |   |        |

|                       | to IMP    |             |       |       |      |      |       |      |     |   |   |     |   |        |

| 5.6 IMP               | to Host   | • • •       | • •   | • •   | • •  | • •  | • •   | • •  | • • | • | • | • • | ٠ | 56     |

i

| 5 | • 7   | Tas  | k.      | •   | •   |      | •        | •   | •   | •    | •  | •   | •  | •  | •  | • | • | • | • | • | • | • | • | • | • | • | 59       |

|---|-------|------|---------|-----|-----|------|----------|-----|-----|------|----|-----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|----------|

|   | 5.    | 7.1  | Tas     | k F | or  | Us   | •        | •   | •   | •    | •  | •   | •  | •  | •  | • | • | • | • | • | • | • | • | • | • | • | 61       |

|   | 5.    | 7.2  | Bac     | k H | ost | s    | •        | •   | •   | •    | •  | •   | •  | •  | •  | • | • | • | • | • | • | • |   | • | • |   | 66       |

|   |       | 5.7. | 2.1     | Ba  | ck  | Hos  | зt       | 5   | •   | •    | •  | •   | •  | •  | •  | • | • | • | • |   | • |   | • | • |   |   | 67       |

|   |       | 5.7. | 2.2     |     |     | Ho   |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 69       |

|   |       | 5.7. |         |     |     | Ho   |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 71       |

|   |       | 5.7. | -       |     |     | Ho   |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 73       |

| 5 | . 8   |      | ting    |     |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   | • | 75       |

| - |       | Fak  |         |     |     | •••  |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   | • |   | • | 77       |

| 5 |       | 9.1  |         |     |     | Но   |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   | • |   | • |          |

|   |       |      |         |     |     |      |          |     |     |      |    |     |    |    |    |   | • |   | - | - | - | - | - | - | - | • | 78       |

|   |       | 9.2  |         | Fa  |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   | - |   | • | ٠ | ٠ | 79       |

|   |       | 9.3  | DDT     |     |     |      |          |     |     |      |    |     |    |    |    |   | • |   |   |   |   | • |   |   | ٠ | ٠ | 80       |

|   |       | 9•4  | DDT     |     |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   | ٠ | 81       |

|   | 5.    | 9.5  | Pac     |     |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   | ٠ | 82       |

|   | 5.    | 9.6  | Pac     | ket | Сс  | ore  | Fa       | ake | I   | MP   | t  | 0   | Ho | st |    | • | • | • | • | • | • | • | • | • | • | • | 84       |

|   | 5.    | 9.7  | Sta     | tis | tic | cs : | Fal      | кe  | Ho  | st   | ť  | 0   | ΙM | Р  | •  | • | • | • | • | • | • | • | • | ٠ | • | • | 86       |

|   | 5.    | 9.8  | Dis     | car | d 1 | Fak  | e :      | IMP | t   | 0    | Ho | st  |    | •  | •  | • | • | • | • | • | • | • | • | • | • | • | 88       |

| 5 | .10   | ) Ve | ry D    | ist | ant | t He | st       | t ( | V D | H )  | I  | n t | er | fa | сe |   | • | • | • | • | • | • |   | • |   | • | 89       |

|   | 5.    | 10.1 | •       |     |     |      |          | -   |     | -    |    |     |    |    |    |   |   | e |   |   | • | • |   |   | • | • |          |

|   |       | 10.2 |         | ΗE  |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   |          |

|   |       | 10.3 |         | dem |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 94       |

|   |       | 10.4 |         | H t |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | • | • | 96       |

|   |       | 10.5 |         | st- |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | • | • | 90<br>97 |

|   |       | 10.5 |         |     |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | • | • |          |

| F |       |      |         | Ht  |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | • | • | 98       |

| С | • 1 1 |      | meou    |     |     | • •  |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | • |   | 100      |

|   |       | 11.1 |         | st  |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | ٠ |   | 102      |

|   |       | 11.2 |         | ck  |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   | • |   | 103      |

|   | 5.    | 11.3 |         | ow  |     |      |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   | ٠ | ٠ |   | 104      |

|   |       | 5.11 |         |     |     | ety  |          |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   | • | ٠ |   | 105      |

|   |       | 5.11 | • 3 • 2 | ? R | ea  | sse  | mb.      | 1 y | B1  | oc   | k  | Ch  | еc | k  | •  | • | • | • | • | • | ٠ | • | ٠ | ٠ | ٠ |   | 106      |

|   |       | 5.11 | .3.3    | B H | ost | t A  | сс       | ess | ; C | h e  | ck | s u | m  | •  | •  | • | • | • | • | • | • | ٠ | • | • | • |   | 107      |

|   |       | 5.11 | .3.4    | + L | ind | e S  | ta       | te  | Τi  | me   | ou | t   | •  | •  | •  | • | • | • | • | • | • | • | • | • | • |   | 108      |

|   |       | 5.11 | • 3 • 5 | i I | ΜP  | to   | H        | ost | : S | of   | tw | ar  | е  | Ch | еc | k | • | • | • | • | • | • | • | • | • |   | 110      |

|   |       | 5.11 | .3.6    | C C | en  | tra  | 1        | Dis | ра  | tc   | h  | Ch  | еc | k  | •  | • | • | • | • | • | • | • | • | • | • |   | 111      |

|   |       | 5.11 | .3.7    | ′ Т | rai | nsa  | ct       | ion | Ē   | 31o  | ck | Т   | im | eo | ut |   | • | • | • | • | • | • | • | • |   |   | 112      |

|   |       | 5.11 | .3.8    | 3 R | ea  | 1 н  | os       | t F | lea | ıd v | L  | in  | е  | Ch | ec | k |   | • |   | • |   |   |   |   |   |   | 114      |

|   |       | 5.11 |         |     |     | tin  |          |     |     | -    |    |     |    |    |    |   |   |   |   | • |   |   |   |   |   |   | 115      |

|   |       | 5.11 |         |     |     | com  | -        |     |     |      |    |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 117      |

|   |       | 5.11 |         |     |     | uti  |          |     |     |      |    |     |    |    |    | • |   |   | • | • |   | • | • | • | • |   | 118      |

|   |       | 5.11 |         |     |     | ffe  | <u> </u> |     |     |      |    |     |    |    |    |   |   | • | • | • | • | • | • | • | • |   | 119      |

|   |       |      |         |     |     |      |          |     |     |      |    |     |    |    |    |   |   | • | • | • | • | • | • | • | • |   |          |

|   |       | 5.11 |         |     |     | 100  |          |     |     |      |    |     |    |    |    |   | • | • | • | • | • | • | • | • | • |   | 121      |

|   |       | 5.11 |         |     |     | dem  |          |     |     |      |    |     |    |    |    |   | • | • | • | • | • | • | • | • | • |   | 122      |

|   |       |      | • 3• 1  |     |     | ffe  |          |     |     |      |    |     | •  |    |    |   | • |   | • | • | • | • | • | • | • |   | 124      |

|   |       |      | • 3• 1  |     |     | ace  |          |     |     |      |    |     |    | -  | -  |   | • | - |   |   |   | ٠ |   | • | • |   | 126      |

|   |       | 5.11 | 3 . 1   | L 7 | Ag  | e M  | e s      | sag | зe  | B1   | oc | ks  | ;  | •  | •  | • | • | • | • | • | • | • | • | • | ٠ |   | 127      |

ii

| 5.11.3.18 IMP-going-down Message Check                                                                                                  | • • | 129 |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| 5.11.3.19 Statistics Check                                                                                                              |     | 130 |

| 5.11.3.20 Restart Buffer Check                                                                                                          | • • | 131 |

| 5.11.3.21 Fake Host Software Check                                                                                                      |     | 132 |

| 5.11.3.22 Back Host Software Check                                                                                                      |     | 133 |

| 5.11.3.23 Trouble Report Checks                                                                                                         |     | 134 |

| 5.11.3.24 Light Display Check                                                                                                           |     | 135 |

| 5.11.3.25 Nice Stop Check                                                                                                               |     | 136 |

| 5.12 Initialization                                                                                                                     |     | 138 |

| 5.12.1 Buffer Initialization                                                                                                            |     | 142 |

| 5.12.2 DDT Page Initialization                                                                                                          |     | 143 |

| 5.13 Configuration                                                                                                                      |     | 145 |

| 5.14 Miscellaneous Routines                                                                                                             |     | 147 |

| 5.14.1 Packet Core Reload                                                                                                               |     | 147 |

| 5.14.2 Block Transfer Polling Process                                                                                                   |     | 149 |

| $5.14.3$ Restart Process $\cdot \cdot $ |     | 150 |

| 5.14.4 DDT Polling Process                                                                                                              |     | 151 |

| 5.14.5 Teletype Handler Polling Process                                                                                                 |     | 152 |

| $5.14.6$ Display Process $\cdot \cdot $ |     | 153 |

|                                                                                                                                         | ••• | 1)) |

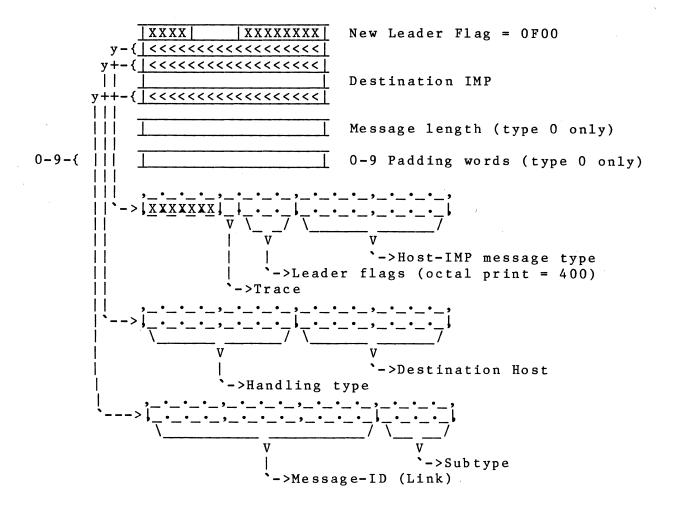

| Chapter 6 Data Formats                                                                                                                  |     | 155 |

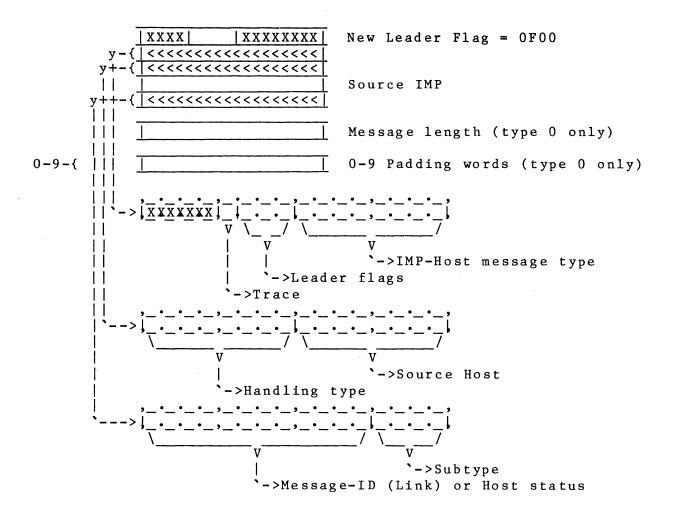

| 6.1 Old-style Leader Format                                                                                                             |     | 155 |

| 6.2 New-style Leader Format                                                                                                             |     | 156 |

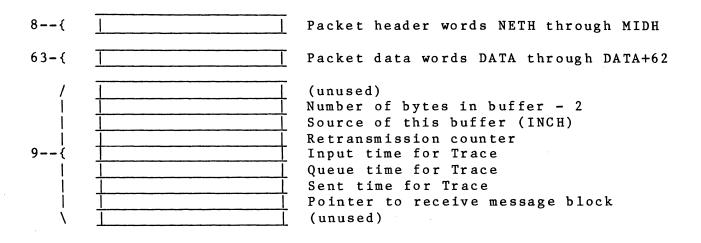

| 6.3 Buffer Format                                                                                                                       |     | 158 |

| 6.4 Basic Packet Structure                                                                                                              |     | 159 |

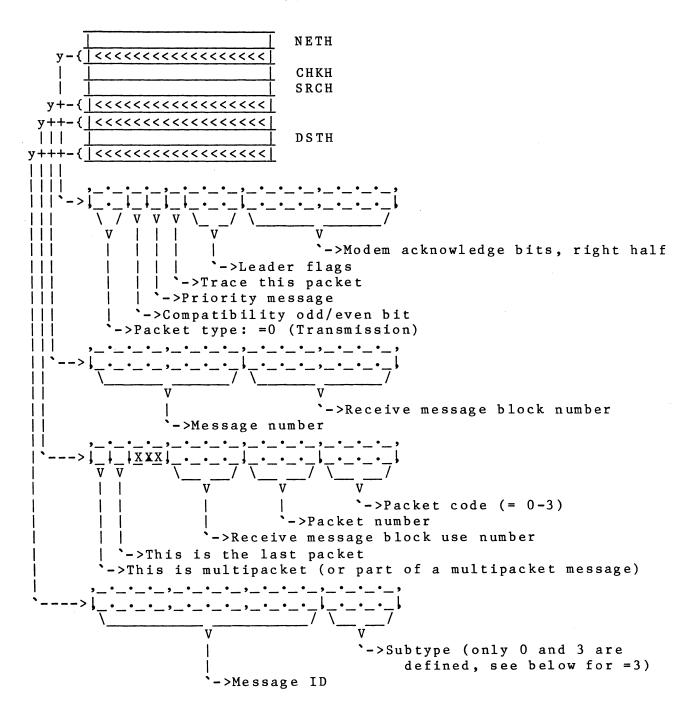

| 6.4.1 Packet Type 0 Formats                                                                                                             |     | 161 |

| 6.4.1.1 Packet format for Type 0, Codes 0-3                                                                                             |     | 162 |

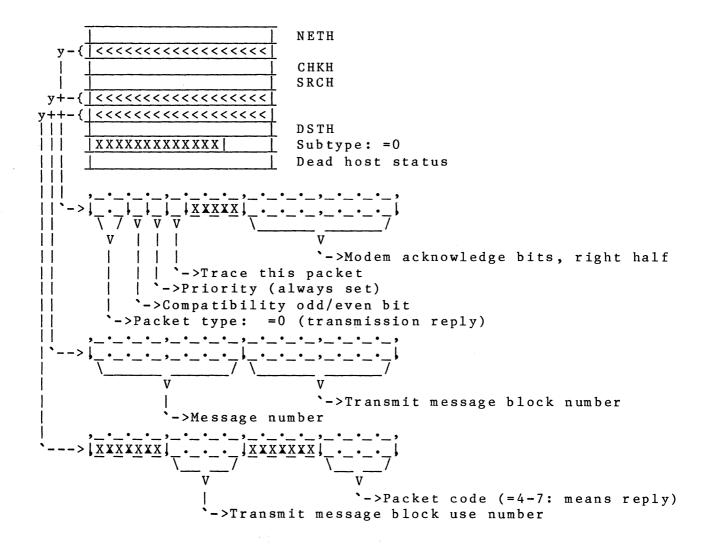

| 6.4.1.2 Type 0, codes 4-7                                                                                                               |     | 163 |

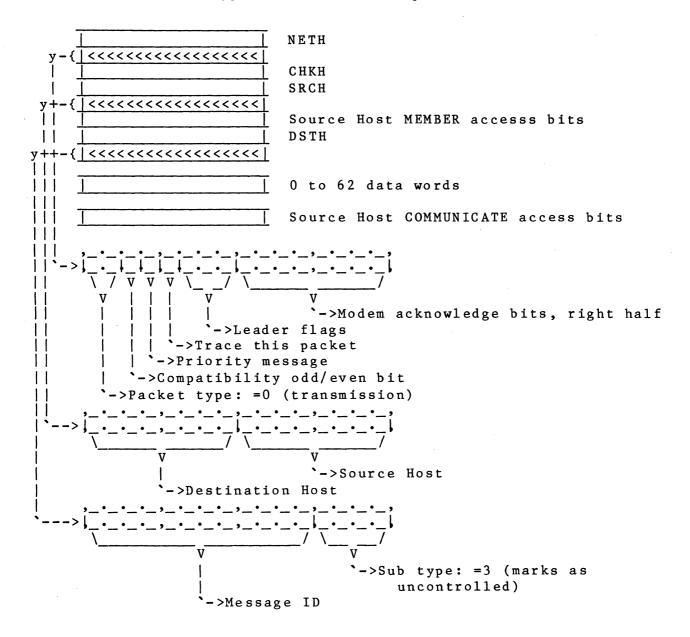

| 6.4.1.3 Type 0, subtype 3: Uncontrolled packet .                                                                                        |     | 164 |

| 6.4.2 Type 1 Packet Formats                                                                                                             |     | 165 |

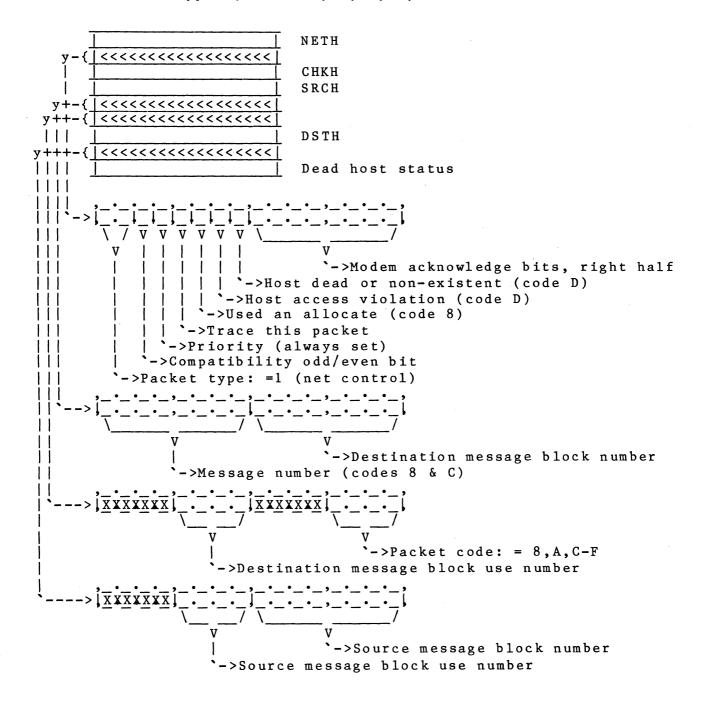

| 6.4.2.1 Packet type 1, codes 8, A, C, D, E and F                                                                                        |     | 166 |

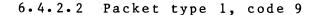

| 6.4.2.2 Packet type 1, code 9                                                                                                           |     | 167 |

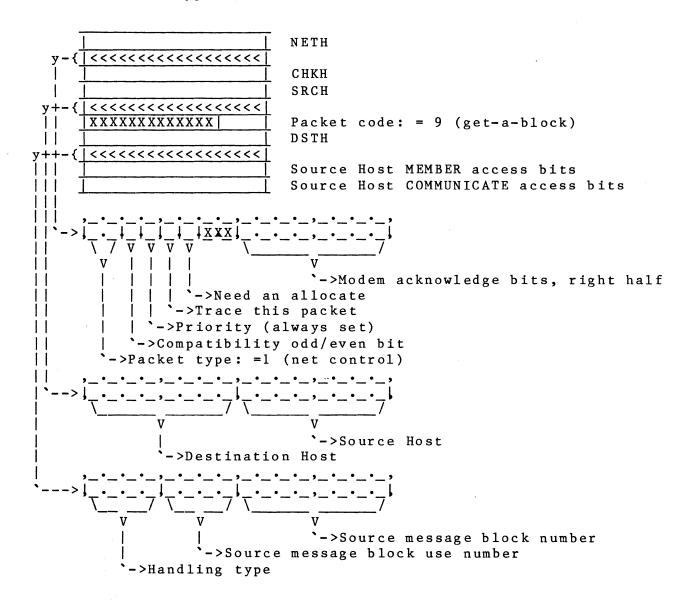

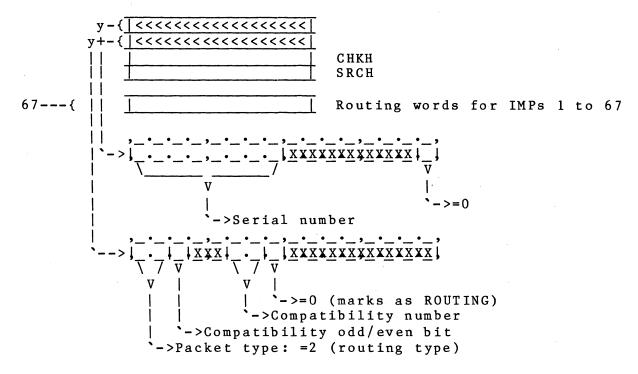

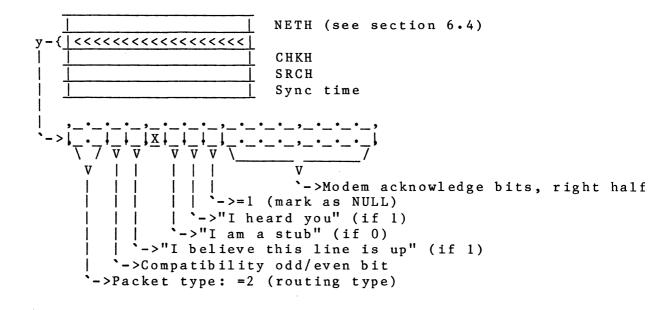

| 6.4.3 Packet type 2: Routing and null                                                                                                   |     | 168 |

| 6.4.4 Packet Type 3                                                                                                                     |     | 170 |

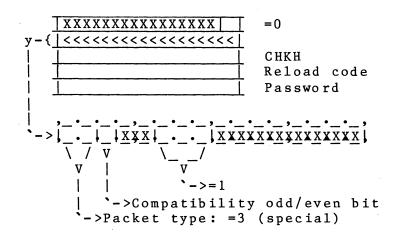

| 6.4.4.1 Demand reload $$                                                                                                                |     | 170 |

| 6.4.4.2 Reload request                                                                                                                  |     | 170 |

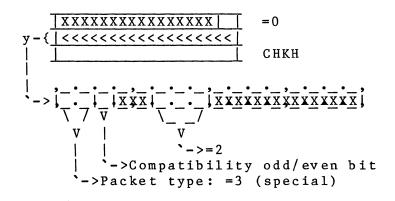

| 6.4.4.3 Packet core $$                                                                                                                  |     | 171 |

|                                                                                                                                         | • • |     |

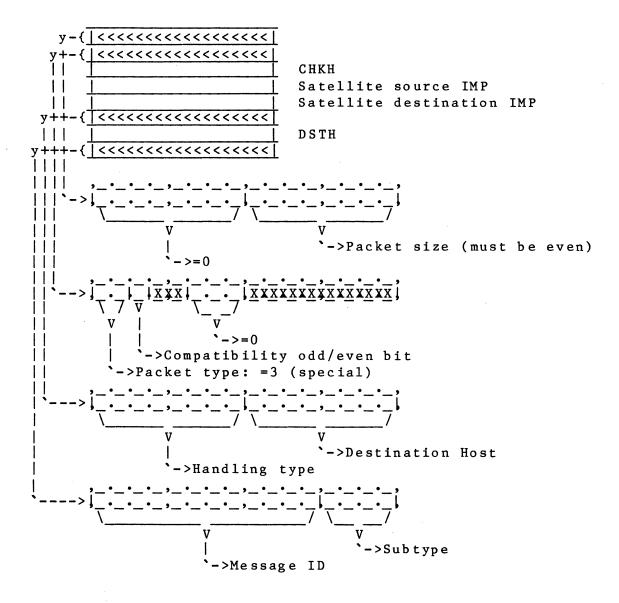

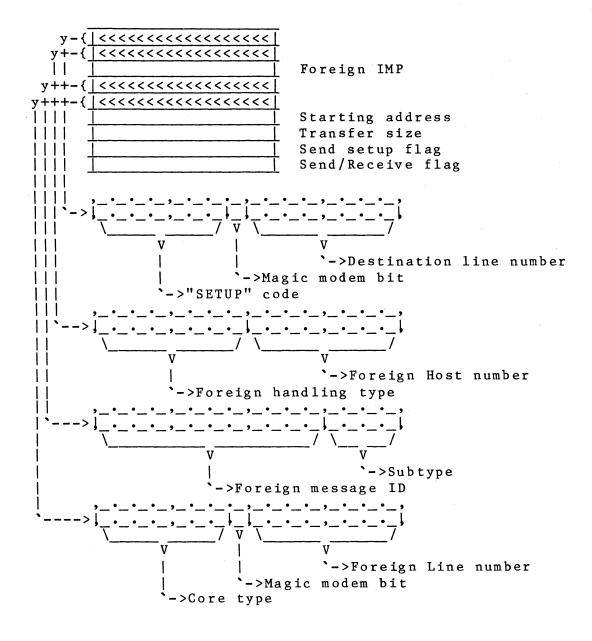

| 6.4.4.3.1 Data for SETUP message                                                                                                        | • • | 172 |

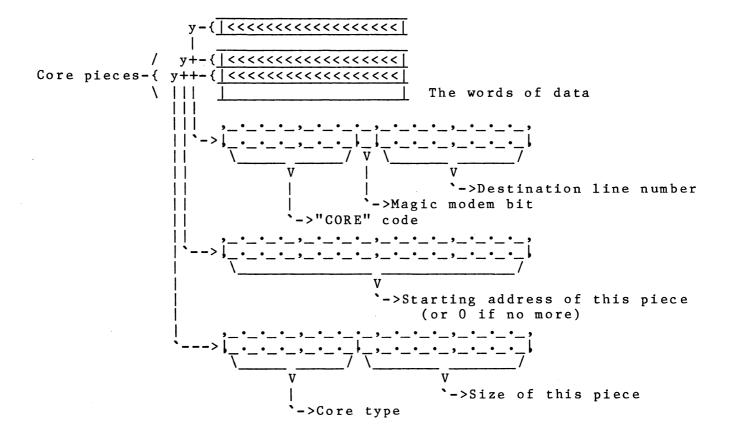

| 6.4.4.3.2 Data for CORE message                                                                                                         | ••  | 173 |

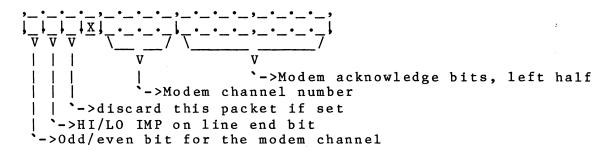

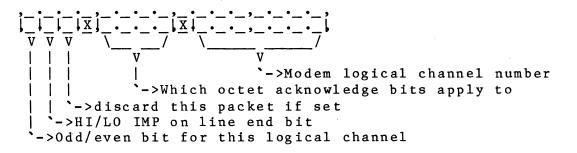

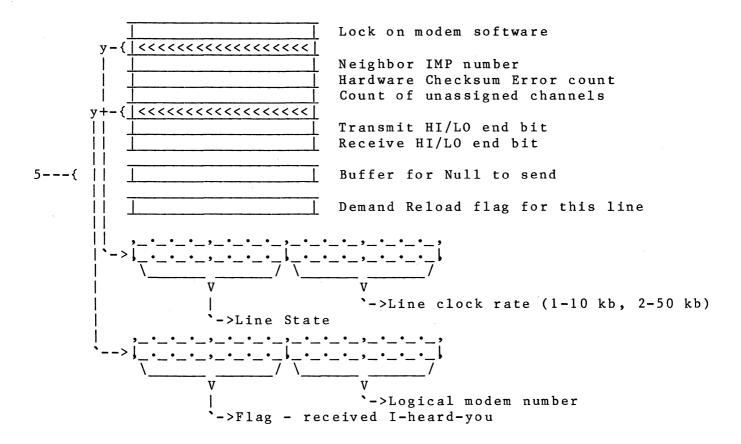

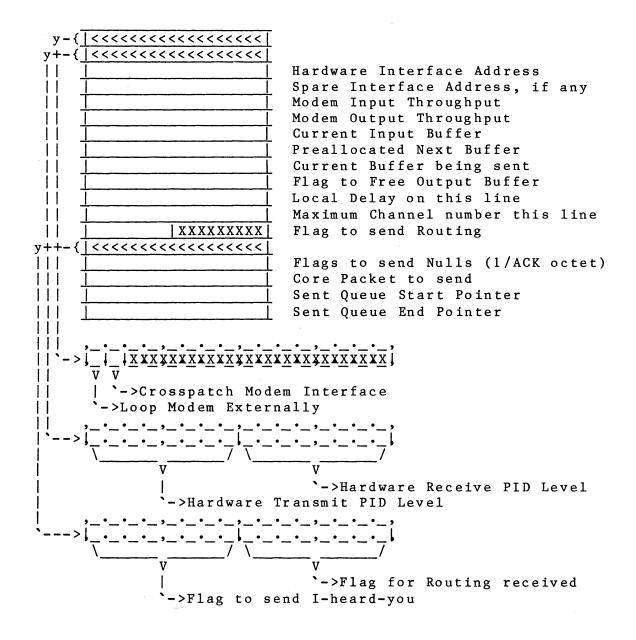

| 6.5 Modem Parameter Blocks                                                                                                              | • • | 174 |

| 6.6 Host Parameter Blocks                                                                                                               | • • | 177 |

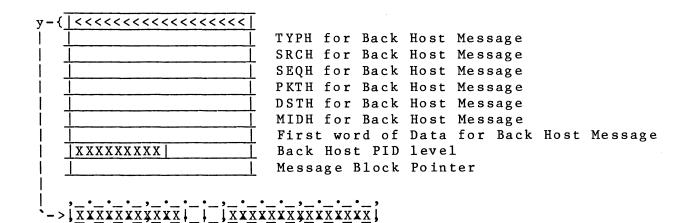

| 6.7 Back Host Parameter Blocks                                                                                                          | • • | 180 |

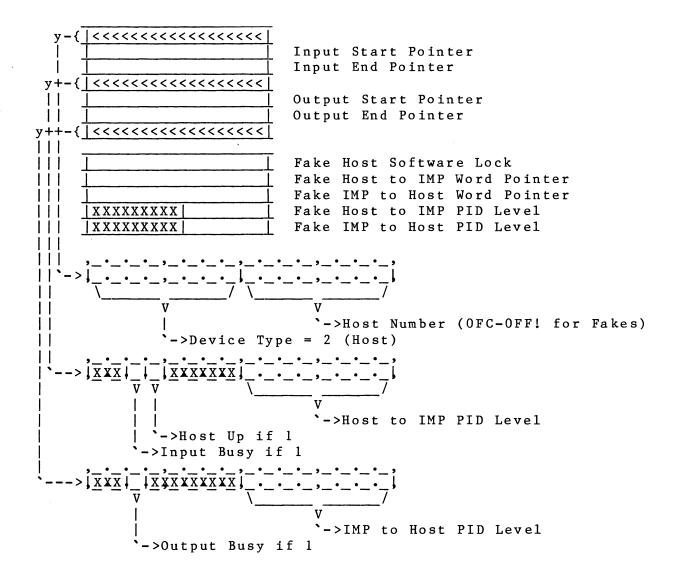

| 6.8 Fake Host Parameter Blocks                                                                                                          | • • | 181 |

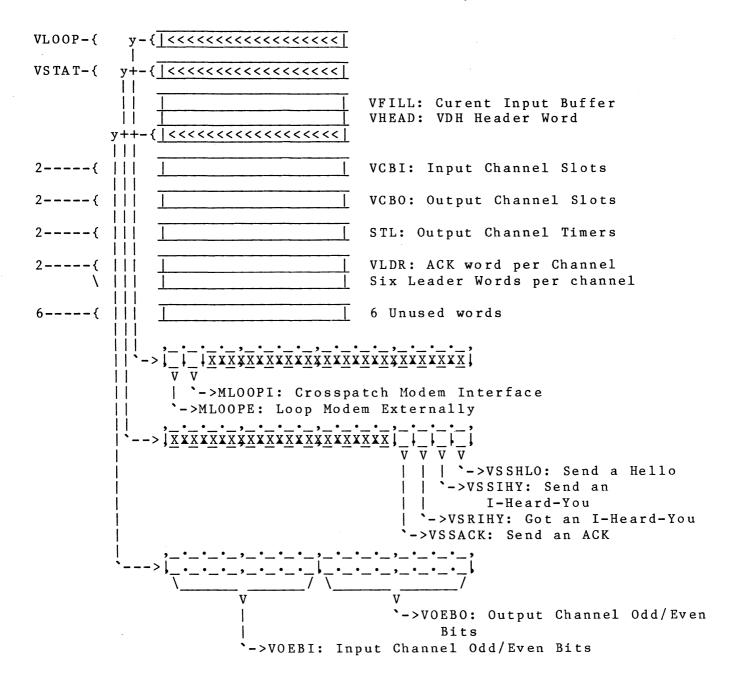

| 6.9 Very Distant Host (VDH) Parameter Blocks                                                                                            | • • | 183 |

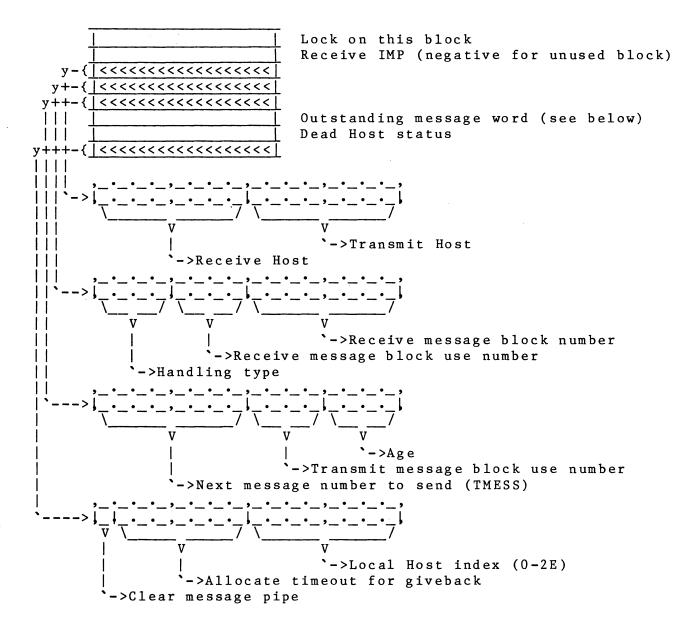

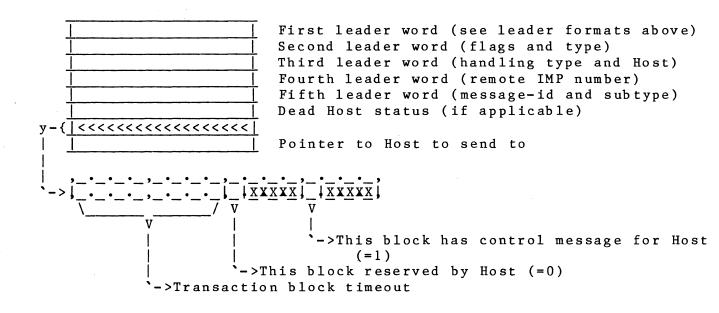

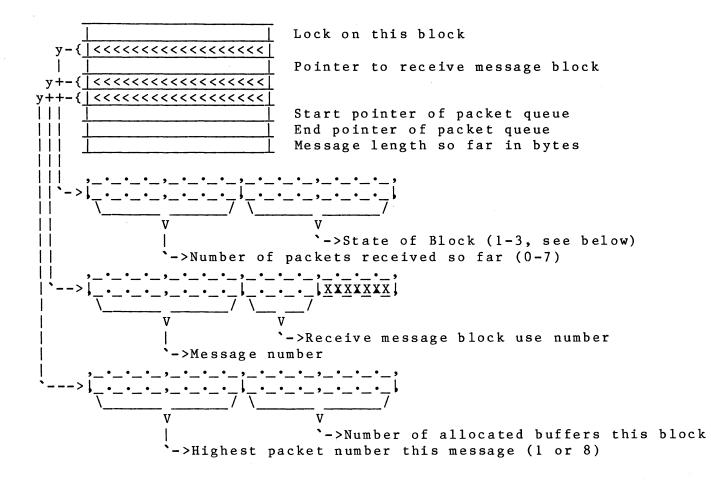

| 6.10 Transmit Message Block Table                                                                                                       | • • | 185 |

6.11 Receive Message Block Table . . . . . . . . 187 . 6.12 Transaction Block Table . . . . . . . . 189 • • • • . 6.12.1 Reserved Transaction Block Format . . . . 189 • ٠ 6.12.2 6.12.2 Outstanding Message Transaction Block Format .6.12.3 Control Message Transaction Block Format . . . 190 • 191 • 192 ٠ ٠ 194

## Volume II

## Table of Tables

| Table | 1) | DDT Error | Type-Outs. | • • • • •  | • | ٠ | • | • | ٠ | • | • | • | • | • | • | 10 |

|-------|----|-----------|------------|------------|---|---|---|---|---|---|---|---|---|---|---|----|

| Table | 2) | Simulated | Processor  | Registers. | • | • | • | • | • | • | • | • | • | • | • | 12 |

| Table | 3) | Debugging | Mode Halt  | Type-Outs. | • | • | • | • | • | • | • | • | • | • | • | 14 |

#### Foreword

This document forms Volume II of a two-volume set which describes the Pluribus IMP program. The first volume contains descriptions of the major routines in the IMP system. Discussions in Volume I are high-level and that volume is Volume II contains detailed intended to be self-contained. descriptions of the programs that comprise the IMP system. Chapter 4 describes the DDT debugging system, Chapter 5 discusses the various program modules of the IMP system in detail, and Chapter 6 contains pictoral descriptions of the data structures Volume II is intended for system implementors, and should used. be read only with a thorough understanding of all the discussions of Volume I and with the IMP program listing handy.

## Chapter 4 The Debugging System DDT

The Pluribus IMP provides within itself the diagnostic debugging system DDT to facilitate dealing with problems that might arise. The implementation makes it possible to debug the Pluribus IMP either from the terminal attached to the IMP or from a remote location. Both the local terminal handler process and the DDT process are implemented as fake Hosts within the IMP. These Hosts are "cross-patched" when the system is initialized, so that characters typed at the terminal are sent to DDT, and DDT responses print on the terminal. DDT commands are provided to reconnect DDT to another Host anywhere in the network to permit remote debugging. Further details about these fake Hosts are in sections 2.2.6.1, 2.2.6.2, and in 5.9.1-5.9.4.

DDT is a program which provides a mechanism for inspecting and changing registers of the machine. In a broader sense, however, it can be viewed as a simple operating system which controls the starting and stopping of processors and handles extraordinary conditions (QUIT and ILLOP). This section is not intended as a tutorial; some knowledge of how other DDTs work (see, for example, "DDT-10 Programmer's Reference Manual," Digital Equipment Corporation, Maynard, Massachusetts, copyright 1968, 1969, 1970) may be helpful.

Pluribus DDT versions have been developed for different configurations and applications; only the IMP version is discussed here. Regardless of the internal structure, a11 versions appear basically the same to the user. DDT requires a controlling device, such as a Teletype or VISTAR. Pluribus IMP DDT runs in conjunction with the STAGE subsystem. As such, it may run only when at least the STAGE Kernel is in operation (i.e. Stages LK through RC are running). DDT makes use of the Block Transfer routine to examine and deposit words in memory. Modifying locations within checksummed code automatically updates the proper checksum to permit patching of the program from DDT.

Following are descriptions of the various commands the user may type. A number is represented by "nn", and <altmode> (or <escape>) is represented by "\$". A dollar-sign character is indicated by "<dollar>". A caret or uparrow "^" followed by a letter indicates a control character. The character caret (or uparrow) is indicated "<uparr>". The underscore or backarrow character is indicated by "<backarr>". The carriage return character is denoted "<cr>", and linefeed "<lf>". The word "register" generally means a location in address space; a "processor register" is just that. Numbers are followed by "!" to indicate that they are hexadecimal (base 16).

4.1 DDT Command Summaries

4.1.1 Addresses, Opening and Closing

Whenever a register is "opened", its contents are typed out in the current mode (except as noted for certain commands). When a register is "closed", the last value typed in while open, if any, is written to that register. If nothing or <delete> is typed in, nothing is written.

- nn/ Opens register nn. The processor in whose address space the reference was made types out as "Pnn" immediately following the /. The contents of the requested register then are typed in the current type out mode.

- nn,nn,nn/ The first two arguments specify a processor or processors to do the reference, and a map setting if needed. The processor(s) may be specified as for the ":" command (see below). A single processor or any set of processors is permissible, and the command has the same effect as if "nn:" or "Pnn:" were typed prior to opening the location. If the address requested is a mapped reference (i.e., the address is in the range 4000-BFFF!), the middle argument is used to set the appropriate DDT pseudo-map. The effect is identical to explicit map-setting using the proper "nn,nn<sup>F</sup>" command (see below). Either of the first two arguments may be the default is to leave the processor omitted; selection and map settings as they were prior to the command.

- Rnn/ Opens processor register nn. For processors running STAGE, simulated processor registers are used, which contain the actual processor register values at the last occurence of a snapshot-triggering trap. Refer to the discussion of the DDT debugging environment below. For processors not running STAGE, the actual processor If the processor is running register is referenced. program, all references to its another processor registers result in QUITs, except for R15. The latter is the processor control register and is always visible, although references to it may cause the processor to halt.

5/78

<cr> Closes current register, if any open.

- Closes current register, if any open, and opens next "instruction"; that is, if type out mode is symbolic (see below) and the current register is a double-word instruction, skip one register.

- \$<lf> Same as <lf> but always opens the next register; that is, a register is never skipped.

- <uparr> Closes current register, if any open, and opens the previous one.

\$<uparr> Like <uparr> but goes up two registers, not one.

- By itself, is the value of the address of the current register, if any open; if none, then the last current register.

- / Types out the contents of the register addressed by the current register but does not open it or change ".". The address used is the "effective" address of the symbolic instruction, if the current type-out was symbolic. For instructions that have no effective address (HLT for example), or for type out in constant or ASCII mode, the actual memory contents are used for the "effective" address.

- \$/ Closes the current register and opens the register addressed by the current register, as in "/".

4.1.2 Type Out Modes

There are two orthogonal type out modes. One controls the radix of type out:

^H Numbers are typed out in hexadecimal (base 16) - the default.

\$^0 Numbers are typed out in octal (base 8).

The other controls how register contents are interpreted:

S Type out symbolically, that is, try to interpret as an instruction, including next word if a two-word instruction code. <sup>K</sup> (Konstant) type out as a number.

^A Type out as two ASCII characters.

4.1.3 Other Type Out Commands

Retypes out the current register in the alternate mode as follows:

currentalternatesymbolicconstantconstantsymbolicASCIIconstant

- \$= Retypes out the current register in the alternate mode, as in "=", and changes the current mode to the alternate mode.

- nn= When preceded by a number or an expression, types out the value of that expression. The result of such expression arithmetic is not considered a value to be written to an open register when closed.

- nn" opens location nn, but does not type out contents; remains in this mode until / or \ is typed.

\$" analogous to \$/

" analogous to /

nn\ opens location nn, but the address type out is suppressed on succeeding lines until / or " is typed.

\$\ analogous to \$/

\ analogous to /

nn[ opens location nn, but types out contents in the

alternate mode (see =, above); does not change current

mode.

\$[ analogous to \$/

[ analogous to /

=

#### 4.1.4 Type In

symbols DDT contains symbols with predefined values to facilitate type in of symbolic data. All of the op codes and other instruction components of the Pluribus assembler are appropriately defined. By using <space> and/or <tab>, instructions may be entered in virtually the same format as the assembler expects. Type in routines correctly interpret displacements in branch instructions. Malformed instructions result in the type out "#", and all current type in is cancelled. There is presently no facility for user defined symbols.

> <u>NOTE</u>: The characters <comma>, "=", "#", "+", "-", "(", and ")" have special meaning within an instruction type in, as do the symbols RO, Rl, ... R7. Refer to BBN Report No. 3001, Pluribus Document 4, Basic Software, Part 2, for a description of the Pluribus assembler format.

- nn

- Typed in numbers are generally interpreted according to the current type out radix, except that numbers containing letters A-F are always hexadecimal. Note that some numbers look just like symbols; e.g., ADD, ADDB, BC, BE, BF1, BF2, and BF3. These are treated as symbols unless they are explicitly denoted as numbers by a leading zero or by an "!" after the number. It is good habit to precede all hexadecimal а numbers beginning with the letters A-F by a leading 0.

- nn. a decimal number

- nn' an octal number

- nn! a hexadecimal number

+ addition

<space> addition

<tab> addition

#### - subtraction

- <backarr> has the value of the last quantity typed out as a

result of examining a register. This would be the

value of second word of a two-word instruction when in

symbolic mode. If the value of the first word is

desired, use "=" followed by <backarr>.

- <comma> is used to input two words at a time. Typing <comma>

after the first value saves that value until the

terminator is typed after the second value, then both

values are written to memory. The value of "." is not

changed. A <delete> typed after the <comma> aborts the

entire input. If nothing is typed before the <comma>,

only the second word is changed.

## 4.1.5 Address Spaces

- Pnn: sets the number of the current processor address space. The processor number is specified according to the Pluribus convention that assigns coupler addresses to indicate the physical processor position in the machine. If the processor doesn't exist, is or inaccessible, subsequent references to its address space produce the "WHO?" diagnostic. No checking is done at the time the ":" is typed.

- selects a set of processors, according to the mask nn: given in nn. Bits correspond to processors in the system, assigned right-to-left in increasing order by processor number. If nn is 0 or the character "-" or not specified at all, the mask is set to be all processors currently running STAGE. Read references go to the first processor that runs the Block Transfer subroutine; if no processor running STAGE is in the then some processor in the mask is accessed by mask, its buddy (if the buddy is running STAGE), or the lowest-numbered processor in the mask is accessed by backwards bus coupling. The identity of the processor in whose address space the location was examined types after the "/" (see above). Write references are performed by all processors in the mask, allowing simultaneous patching of all processor local memories.

- nn,nn<sup>F</sup> sets the map value of the memory page to be referenced when examining addresses in the mappable segments

(4000!-BFFF!) to the second argument. The map setting maintained internally to DDT, but is used for all is subsequent references through the corresponding address window until changed by another ^F or / command. 0n e the four segments is specified by the first of argument, which must be "MO", "M1", "M2" or "M3" to select a particular 4K map window. If the first argument is missing, map 0 is assumed. The map setting is interpreted as follows: (1) even numbers less than 200! select a logical page type, as maintained by Stage (2) even numbers 200! or greater select the MM. physical page with that map setting. (3) 0 selects logical page 0 (the "reliability" page). (4) Any odd number selects a physical page; in particular, 1 selects physical page 0. An argument of -1 causes all four maps to be set to their default values, which are 0,10,12,10 for the reliability, variables, second variables, and variables (logical) pages. The current map settings may be examined by opening locations MO-M3 (i.e., type "MO/" to see the current setting for references to locations 4000-5FFF).

- 4.1.6 Control

- nn<sup>G</sup> starts the selected processor at nn. If the selected processor is running STAGE, nn is copied to its simulated RO and its R15 is set to 2.

- ^G starts the selected processor at the address last specified by a ^G command. If no argument is given and no address has been specified previously, a "#" prints and nothing else happens.

- \*X stops the selected processor if running and types out the contents of the program counter. If not running, types out "HALTED". For processors running in the STAGE system, sets their simulated R15 to a 1, and prints the contents of simulated R0.

- ^P Causes the selected processor to proceed from its current state. If a processor running STAGE is selected, its R15 is set to 2.

- <sup>2</sup> steps the selected processor one instruction and types that instruction. Prcoessors running STAGE set their R15 to 3. In this case, single-stepping is meaningless and should not be tried.

\$^Z like ^Z but does not type the instruction.

nn<sup>2</sup> like <sup>2</sup> but first sets the program counter to nn.

- 4.1.7 IMP Version Features

- nn^L sets up a leader for a "semicolon message". Format is

"<leaderl>, <leader2>, <leader3>, <leader4>,

<leader5>^L". Any field not specified is assumed to be

zero except for <leader1>, which is set to 0F00. Thus,

the command 3,6,^L sets up a normal message leader for

semicolon messages to Host 3 on IMP 6, with no special

leader flags and a message-id of 0.

- <sup>^</sup>L clears the screen and repaints the display in the bottom portion of the screen.

- nn,nn<sup>C</sup> "crosspatches" all subsequent type in. The second argument is the IMP to send to; the first is which Host on that IMP. Host OFD (i.e., the DDT fake Host) is assumed if the first argument is omitted.

- ^@ undoes ^C and directs type in to the local DDT echoes a <cr>, <lf> pair.

- ^T returns as a value in the current radix the number of the last IMP Teletype to "crosspatch" to the local Teletype.

- ^0 complements value of the override switch and echoes "^0N" or "^0F" as appropriate.

- nn^0 same as ^0 for "sense switch" nn (1-4). The Pluribus has no physical sense switches; software sense switches are maintained in this fashion, but currently have no function.

nn<dollar> activates the operator help (OPHELP) command nn.

These commands are various maintenance and debugging

aids which enable day-to-day operation of the IMP

system without detailed knowledge of the program. For

ex

ample, OPHELP commands can loop and unloop modem

lines, or look up the address of a Host parameter

block.

#### 4.1.8 Miscellaneous Commands

nn,nn,nn<sup>B</sup> copies contents of some processor's private memory to the corresponding locations of the private memory of the currently selected processor(s). The first argument selects which processor(s) should be the source of the transfer, where nn is interpreted as in the nn: command (see above). Pnn: may be used to copy from one specific processor. The latter two arguments give the inclusive bounds on the addresses to be copied. Omitting arguments causes the last value previously specified for that field to be used; if none exists, a "#" is echoed and no copy takes place.

#### 4.2 Control Structure of DDT

The Teletype handler process and the DDT process are polled from the operational IMP program when they have work to do (i.e., characters to process). The Teletype process is also called periodically to check for new input characters from the Teletype interface. Since crosspatching allows the local Teletype to send its characters to another IMP, and other IMPs or Hosts may send characters to the DDT process, the two processes must be independent. The ^C and ^@ commands provide control over the crosspatching of the local IMP Teletype.

DDT makes use of the Stage Block Transfer process to perform operations that involve moving data in memory. The various Examine and Deposit functions are such operations, as are the ^X, ^G, ^P, ^Z, and ^B commands. Failures within the Block Transfer process set error codes, which DDT attempts to interpret. Table 1 shows the DDT error type outs and their meanings.

The Teletype and DDT processes communicate only by passing characters through buffers. The Fake Host processes responsible for communicating these characters to and from the network manage the other side of these buffers. When the system is in debugging mode, and the IMP processes stop passing these characters for several seconds, a special mode is entered which permits the characters to be passed directly from Teletype to DDT and back. In this mode, the IMP Fake Host processes are bypassed (since they may have stopped running anyway). Refer to the discussion of debugging mode below.

#### Type-out Meaning

- QUIT Block Transfer got a QUIT trying to complete the last request. If the request was performed by several processors, the mask specifying which processors got the QUIT will print in parentheses. A mask of FFFF indicates that the single processor which was selected could not complete the transfer.

- FAILED Block Transfer couldn't complete the transfer in the requested processor's address space. Again, a mask saying which processor(s) had trouble will be printed.

- WHO? Some non-existant processor was specified to Block Transfer. The mask which prints says which processor; if a single processor is selected, a mask of FFFF will print and that processor doesn't exist.

- TIMEOUT Block Transfer timed out before the requested transfer could complete. This shouldn't happen; if it does, it indicates a program bug or perhaps a very busy machine.

- ??? A Block Transfer error has happened which DDT can't decode. This should never occur; it would indicate a program bug in DDT.

Table 1 DDT Error Type-Outs.

## 4.3 Protection, Override

DDT has the power to change any location in memory in such a way that it cannot be detected (by a failing checksum, for example). As such, it could completely disable the continued operation of the operational IMP system. For this reason, all potentially dangerous actions of DDT are protected by the override mechanism. Normally, the override condition is disabled in a running IMP system. Only certain Hosts (the NCC IMP Teletype Fake Host, for example) may turn on override. Override is always disabled following a system restart. Once override is enabled, all of DDT's features are permitted, so extreme care must be used that incorrect actions are not requested. As soon as the necessary requests to DDT have been completed, override should be immediately disabled. Override is controlled by the ^0 command.

Commands that can modify memory include a direct request to change an open memory location with <lf> or <cr> (although memory may be examined with override off), the <dollar> commands, the processor-control commands (^X, ^P, ^G, and ^Z), the local memory copy command ^B, and the crosspatch command ^C. Examining memory and typing <lf> to progress to the next location is permissible with override off (since nothing was typed in to be deposited).

#### 4.4 Debugging Environment of DDT

DDT attempts to maintain a "logical" debugging environment similar to the environment the programmer is coding in when he/she is writing the program. In particular, DDT assigns special meanings to such hardware features as the memory map registers (and their effects) and the processor registers. The debugger can thus simulate step-by-step the action of a particular routine by changing the contents of these hardware registers in DDT. DDT, of course, does not change the actual registers, since it is using the registers for its own purposes. Instead, the registers and (in the case of the maps) their side-effects are simulated by DDT.

The simulated or pseudo-map registers can be accessed in DDT, either explicitly by opening locations MO, M1, M2, or M3 (or, equivalently, OFCOO!, OFCO2!, OFCO4! or OFCO6!), or implicilty in the nn,nn/ and ^F commands. The current settings in DDT's simulated registers may be examined by opening locations MO-M3. (The hardware map settings cannot be read directly!)

The processor registers can also be examined for processors running in the system. Of course, since the processor is running at the time, these have no meaning. Instead, DDT displays the registers at the time of the last "snapshot". A snapshot is triggered by a extraordinary occurence in the IMP program. An unexpected QUIT is such an occurence. In many places, traps that are not supposed to happen ever, and in particular traps that may indicate some hardware malfunction, are transformed into snapshot traps (see description of illegal instruction interrupt handler, section 5.1.14). The snapshot consists of a complete picture of the processor registers at the time of the snapshot, plus other interesting information that may have some bearing on the problem Snapshots are sent periodically to TENEX by the PLOG at hand. process when debugging mode is disabled, so that a permanent record of them may be kept and the snapshot area may be reused. Table 2 lists the simulated registers and their meanings.

Register Contents

- RO The illegal instruction (ILLOPR) that triggered this snapshot. Refer to the trap listing for the IMP for its meaning.

- R1-R7 The contents of processor registers 1-7 at the time the snapshot trap was executed. Refer to the program listing to discover their meaning at the time of this particular trap.

- R8 The processor status register at the time of the trap.

- R9 The contents of the program counter at the time of the trap. (i.e., the memory location containing the trap instruction)

- R10 The last call to the Stage restart WST, WSTCOM, or WS. Encodes the reason for the last restart of this processor.

- Rll The contents of the program counter the last time a "program in a loop" condition was detected.

- R12 The address being referenced tha last time an unexpected QUIT occured.

- R13 The contents of the status register at the last unexpected QUIT.

- R14 The program counter at the last unexpected QUIT.

- R15 The simulated processor control register. For more discussion, see the section on debugging mode.

- 170 (This location is right after R15; a <1f> after examining R15 will examine this location). The mapO setting at the last snapshot.

- 172-6 Maps 1-3 at the last snapshot. The map settings will always have the 2-bit or'ed in.

Table 2 Simulated Processor Registers.

#### 4.5 Debugging Mode

Debugging mode is a special IMP program feature which should never be required during normal operation. It allows processors to "hang" in the early portions of STAGE under various drastic error conditions, so that the state of a computation can be examined in DDT after the occurence of the error. This facility is much like the notion of a "breakpoint" in many other DDT's. In the Pluribus, however, we have modified the notion somewhat because of the demands of the multiprocessor environment. In particular, DDT may only run when enough of STAGE is running to guarantee proper communication between the processors in the system. In other words, enough of STAGE must be running to ensure proper operation of the Block Transfer process. This comprises the "kernel" of STAGE, or Stages LK through RC.

Once these Stages are enabled, the Stage dispatcher checks debugging mode flag. This is a flag within the local kernel the checksum bit-coded by processor - if the bit corresponding to a processor is set, it is in debugging mode. Processors in debugging mode will hang at Stage RC if their simulated "halt" bit (bit 1 in R15) is set. They continue to poll Block Transfer and the Teletype and DDT processes, however, so that the state of the system may be examined by the programmer. There are known dead states in debugging mode! The DDT code page, for example, is not checked before the Teletype and DDT routines are called, so' a problem in those routines could cause processors to execute a halt or worse. Use of debugging mode is dangerous, and is only intended for checkout of new systems on machines not performing an operational function. In a redundant system, debugging mode could possibly be used selectively to diagnose a failure in only processor or processor bus, but extreme caution is advised. one

In debugging mode, Stage interprets the processor "Halt" bit (i.e., the l-bit in snapshot register R15) to mean "stop running the system and all stages later than stage RC". When all is normal, the "run" bit (the 2-bit) will be set. An occurence of a snapshot trap will turn off the run bit, but not set the halt bit (this is the "half-halted" state). A serious condition (an unexpected QUIT, or the special halt traps OFFFF and OFADE) will set the halt bit, and this processor will cease running the operational system. In addition, extra bits are set to indicate which condition caused the processor to hang in STAGE, and the reason will print out as "Pnn xxxx@yyyy", where xxxx is the error condition and yyyy is the location of the snapshot trap that caused the halt. The conditions and their meanings are listed in Table 3.

#### Type-Out Meaning

- QUIT The processor got an unexpected QUIT at the instruction whose address is typed in the error print out.

- ILOPR The processor executed a OFFFF instruction at the specified location.

- FADE The processor executed the special illegal instruction OFADE at the specified location. This causes a flag to be set in common variables which in turn forces all the other processors also to hang in STAGE. This is useful when debugging a problem requires looking at the global environment of the system. Each processor checks the flag as it completes the strip it was running.

#### Table 3

#### Debugging Mode Halt Type-Outs.

NOTE: In the "halted" state, Stages LK-RC continue to run. This means that debugging those Stages is very touchy with the use of the OFFFF or OFADE traps. Programmers are advised to try to use snapshot traps wherever possible for debugging, and to resort to the halt traps only rarely. In most cases, enough useful data can be loaded into the registers at the time of the snapshot to permit effective debugging of bad conditions.

The snapshot area, once it contains a valid snapshot, will only be overwritten by the serious condition type of snapshot. The serious snapshot will never be overwritten, but the processor must have its "halt" bit turned off before it reenters the system. The overwriting is controlled by looking at the stets of the simulated R15 run and halt bits. Snapshots are permissable which progress from "run" state to "half-

halted" or "halted" state, and from "half-halted" state to "halted" state. Causing processors to leave either "half-halted" or "halted" state is achieved by typing ^P with the appropriate processor(s) selected. This sets their R15 back into "run" state to permit more snapshots. When not in debugging mode, the TLOG process, as it sends off snapshot messages, turns the "run" bit (bit 2) back on to allow more snapshots to take place.

5/78

## Chapter 5 Detailed Program Descriptions

A concise, systematic approach has been taken in presenting details of the IMP programs in the following pages. The approach is reflected by the headings of the outline used in describing the programs:

- Function for complex routines, each function is numbered for reference in subsequent sections. The list of functions contains those which are fundamental to major IMP operations.

- 2. <u>Control Structure</u> A general description of the coding structure and its control flow.

a. Entry points locations and modes by which the program is entered.

b. External calls the names of subroutine or coroutine calls which the program makes.

c. Initialization important settings made during the initialization process.

d. Cleanup actions taken before exiting or during unusual situations.

- 3. Data Structures.

a. Local data - variables and constants which are used only by the program.

b. Shared - tables, variables and locks which are used by other programs as well. Care must be taken to use software locks wisely so as to insure consistency in shared data.

4. <u>I/O Performed</u> - Any actions taken which affect the state of any hardware interface in the IMP. Included are resets as well as input and output operations.

#### 5.1 Stage System

Function

The Stage system is a series of processes which progressively build up a picture of the Pluribus machine configuration. The output is typically in tables which may be used by operational systems (such as the IMP program) to initiate and perform their Each of the processes is described in a tasks. subsection of this section. Dispatch control for initiating these processes is described in this section. Other basic system functions performed by the Stage routines are described in subsections following the individual Stages.

#### Control Structure

The Stage dispatcher polls individual Stages which have been enabled, under control of the WDIS word. In addition, the Block Transfer process is polled and, if in debugging mode, the Teletype and DDT processes. The dispatcher also maintains the Stage timing functions and consensus arrays for each Stage.

#### Entry Points

Stage is the first system entered on start-up or after a drastic system failure. Following are various entries to Stage, and their uses: SETUP: a halt, so pushing RUN on the operator console proceeds at WS.

WS: restart entry, to force total system reinitialization; normal entry following a fresh paper-tape reload. WSTINI: entry for processor that is restarted by another processor; sets up PROCNO and enters WST.

SJ7: entry if this processor believes the communication page has failed.

WSTCOM: entry to force finding of a (possibly new) communication page.

WST: entry following certain drastic local failures, such as unexpected QUITs or program loops.

External Calls

SBAD: routine to disable later Stages; called on initial entry to disable all but the first Stage (Stage LK). STPOLL: entry to poll DDT and Teletype from Stage, for debugging only. BLT: Block Transfer process; provides mechanism for processor reloads and restarts. DDT examine and deposit, and packet core transfers.

#### Initialization

Each Stage, as it succeeds, initializaes the dispatch (WSLA7) for the succeeding Stage.

Cleanup

All hardware configuration data is periodically checked and kept correct by the Stage processes.

#### Data Structures

Local Data

UWST: saved address of last caller to initial entry to Stage. WSTAGE: currently running Stage index.

WTEMP: temporary register save word.

WSLA1-WSLA7: tables (by Stage) of saved register settings.

SVTIME: most recent time read from real time clock Stage is using (LCLOCK).

Shared Data

LCLOCK: address of current real-time clock for Stage to use. run Stage LK (so all Stages run UTIME: time next to occasionally). WDIS: Stage dispatch control; bit-coded by Stage. CONSOL: address of operator console light registers, if any. LTIME: time (from LCLOCK RTC) before which the Stage dispatcher should next be entered. DEBUGM: debugging mode flag. PROCBT: bit for this processor. SNAP: snapshot save area. MAPREL, MAPCOM, MAPVAR: map settings for reliability, communication, and variables pages. STIME: local copy of Stage system time (SYTIME). COMPTR: pointer from each common memory page to the communication page. SYTIME, SYTIM2: time (25.6 ms ticks if IMP system running), controls many Stage timeout functions. COMREL: communication page pointer to reliability (rely) page. SEGCON, STGCON, BUSCON, COUCON, RCKCON, LOCCON, CKSCON, MEMCON, IOCON, INICON: consensus arrays for Stages MD, RK, BD, CD, RC, LC, MC, MM, ID, AR.

## I/O Performed

While Stage is running, WDIS is displayed in the console address lights. If an external reload is in progress, the packet core address (PKCADD) is displayed in the console data lights by BLT.

#### 5.1.1 Stage LK - Local Kernel Checks

Function

This Stage operates on configuration data local to each processor. Upon successful completion, the processor has initialized its interrupt dispatches (for QUITS, power fails and restores, and the 60-hertz ("jiffy") clock interrupts), discovered its operator console (if any), checksummed the local kernel code, and found a system real time clock (RTC) to use for timing Stage.

#### Control Structure

Entered on any Stage restart, and then runs forever as a coroutine with the Stage dispatcher.

#### Entry Points

Restarts enter at SLK00.

External Calls

CKSUBI, CKSUBR to checksum the local kernel code. SLKSLE to dismiss coroutine (special entry to WSLEEP). FNDCLK to search for a real time clock. SOKAY to signal successful completion of this Stage.

Initialization None.

<u>Cleanup</u> None.

Data Structures

Local Data None.

Shared Data

UQUIT: pointer to unexpected QUIT handler. CONSOL: address of operator console, if any. PROCNO: processor number for thie processor. PROCBT: bit assigned to this processor. LCLOCK: address of RTC for Stage to use.

I/O Performed

Processor interrupt vectors are initialized and level 1 and 4 interrupts are enabled.

#### 5.1.2 Stage MD - Common Memory Discovery

#### Function

This Stage searches the common memory space to find usable common memories. In addition, it must maintain the identity of the communication page, which must be the lowest numbered page the processor can see.

#### Control Structure

Searches through all possible memory from map 0 to map 7E00!. Each memory is tested for proper operation with a brief memory test. The lowest page found is used as a communication page.

#### Entry Points

Coroutine, entered from Stage Dispatcher via WSLA7.

#### External Calls

WSLEEP to dismiss coroutine. SFIXIT to reach consensus for modifying MEMSEG. SCLEAR to remove this processor's FIXIT bit. SOKAY to allow next Stage to run. SBAD to disable later Stages.

#### Initialization

WSLA7 is initialized to dispatch to SMD00.

#### Cleanup

None.

## Data Structures

<u>Local Data</u>

MYSEGS: this processor's version of common memory table. WMLOCK: lock on memory test area. SMDFLG: flag for timing COMTST. SMDTIM: timer for COMTST counters. SMDBUC: junk word (bit bucket) to store into to find memory. SMDBLK: memory test area. COMTST: bit-coded (by processor) timers to fix a COMPTR word.

Shared Data

MAPCOM: map setting for communication page. MEMSEG: common memory table (bit-coded). MEMTOT: total number of 4K memory pages found. STIME: Stage time (local copy). SLFPTR: page self-pointer (copy of map setting). COMPTR: pointer from each page to the communication page. PROCBT: processor bit for this processor.

I/O Performed

None.

#### 5.1.3 Stage RK - Reliability Page Kernel Check

#### Function

This Stage searches through common memory for a viable common memory kernel. The kernel, and the whole page, are checksummed. The result is recorded (via consensus) in COMREL on the communication page.

#### Control Structure

Searches through memory pages discovered by Stage MD. Existence of a kernel is denoted by the password OACE! being stored at location RKEPAS. Checksums of the kernel, and the whole (reliability) page are verified.

#### Entry Point

Coroutine, dispatch from Stage dispatcher via WSLA7.

External Calls

SCLROK to pass the Stage and remove fix-it bit. WSLEEP to dismiss the coroutine. MEMTS2 to check for existence of a memory page. CKSUBI, CKSUBR to compute checksums. SFXBAD to hang this Stage and await consensus for modifying COMREL.

#### Initialization

WSLA7 is initialized to dispatch to SRK00.

#### Cleanup

None.

#### Data Structures

#### <u>Local Data</u>

SRKKER: kernel that has been found by this stage, if any. RKEPAS: location of password constant identifying the kernel. RKERCK: checksum and limit words for kernel checksum. SRKREL: copy of COMREL, used to limit search loop.

Shared Data

COMREL: pointer from communication page to reliability page.

CKSUM: checksum and limit words for common code page. TYPE4K: core type word for common code page.

# I/O Performed None.

#### 5.1.4 Stage BD - Common Bus Discovery

#### Function

Check variables area in common memory for this and later Stages for bad parity and currency; reinitialize it if there is bad parity or if the variables are no longer current. Find which common busses exist (for I/O or memmory). Note which I/O busses have real time clocks. Results are recorded in USEBUS.

#### Control Structure

Scans the common variables area for bad parity, which is indicated by the occurrence of a QUIT. Checks for existence of common busses. I/O busses are checked to see if they have a PID and real time clock. Memory busses exist if their lowest-numbered page is in MEMSEG.

#### Entry Points

Coroutine, called from Stage dispatcher via WSLA7.

#### External Calls

SCLROK to pass the Stage and remove fix-it bit. WSLEEP to dismiss the coroutine. SFXBAD to hang this Stage and await fix-it consensus. WST to restart Stage. WSTMEM to remove a failing memory page from usage and restart Stage.

#### Initialization

WSLA7 is initialized to dispatch to SBD00.

#### Cleanup

None.

#### Data Structures

Local Data

STGTIM: timeout on the Stage common variables area.

Shared Data

COMAR: Stage common variables area.

BBCLOK: lock on backwards bus coupling privelege.

BLTLOK: lock on Block Transfer parameters.

BUSCON, COUCON, RCKCON, LOCCON, CKSCON, MEMCON, IOCON, INICON: Consensus arrays for Stages BD, CD, RC, LC, MC, MM, ID, AR. STIME: local copy of system time.

5/78

MEMSEG: table of existing memory pages from Stage MD. PIDGET: local table of PID read addresses. USEBUS: bit-coded table of existing common busses and real time clocks. LKERCK: local kernel code checksum. MAPREL: map for reliability code page.

I/O Performed

None.

#### 5.1.5 Stage CD - Bus Coupler Discovery

#### Function

Search for all couplers in the system (processor to memory, processor to I/0, and I/0 to memory). Search for all processors in the system.

#### Control Structure

Scans all of coupler addresses on I/O and memory busses. Couplers appearing on I/O busses must be from processor busses; if memory busses have couplers that correspond, they are assumed to be from processor busses also. Couplers appearing only on memory busses are assumed to be from I/O busses, and are remembered separately. Processors are assigned numbers based on their coupler addresses (which generally correspond to their physical location in the Pluribus machine).

#### Entry Points

Coroutine, called from Stage dispatcher through WSLA7.

#### External Calls

SFIXIT to achieve consensus for modifying results of this Stage. SCLROK to pass this Stage and remove this processor's fix-it bit. WSLEEP to dismiss coroutine. SFXBAD to hang this Stage and await consensus to fix results. WST to restart Stage if this processor discovers its own number was wrong.

initialization

WSLA7 is initialized to SCDOO.

#### Cleanup

None.

### Data Structures

Local Data

PROCD: accumulates set of existing processors. SCDIOI: current index to non-processor coupler table. SCDBUS: accumulates bits by bus for which common busses this coupler exists on. AMPCOM: table of common bus amputation states. COUBUS: which busses each processor has couplers on. IOCTBL: table of non-processor couplers and which (memory) busses they exist on.

Shared Data

PROCEX: bit-coded table of existing processors. PROCNO: my own processor index in COUTAB. COUTAB: table of processor coupler addresses. MYPROC: my processor number = coupler index (bus address) plus odd bit if I'm the odd processor. PROIOR: bit table of processors that should be removed from system. AMPROC: amputate words by processor coupler. SEGCON: Stage MD consensus. USEBUS: bit-coded table of existing busses. BBCLOK: lock on backwards bus coupling privelege. QUITV: pointer to most recent QUIT vector used.

I/O Performed

None.

## 5.1.6 Stage RC - Reliability Page Check

## Function

Decides (based on result of Stage RK) whether the checksum on all of the reliability page code is good. If it isn't, trigger a reload. If okay, see whether debugging and this processor is in the simulated halt state; if it is, hang in this Stage.

#### Control Structure

Examines COMREL to determine whether reliability page has a good checksum. DEBUGM and BLTMYC (simulated processor control register) control the halted debugging state.

## Entry Points

Coroutine, called by Stage dispatcher via WSLA7.

## External Calls

WSLEEP to dismiss the coroutine. SBAD to hang the Stage pending a reload. STEST to conditionally pass this Stage. RELTRY to initiate a Block Transfer for a reload.

## Initialization

WSLA7 is initialized to SRC00.

## Cleanup

None.

# Data Structures

Local Data None.

# Shared Data

PROCBT: my assigned proessor bit. SNAP: snapshot save area. COMREL: pointer from communication page to reliability code page. TLIMIT: limit of checksummed area on each code page. CKSUM: checksum on a code page. RCKCON: consensus array for this Stage.

## I/O Performed

# 5.1.7 Stage LC - Local Page Checksum

Function

Verifies the checksum on all the local memory code for this processor. If checksum fails in every processor (i.e., consensus is reached), trigger an external reload.

## Contorl Structure

Computes additive checksum on all constant words of local memory, which should be zero. External reload is initiated by setting appropriate Block Transfer parameters.

# Entry Points

Coroutine, called from Stage dispatcher via WSLA7.

## External Calls

SCLROK to pass this Stage and remove fix-it bit for this processor. WSLEEP to dismiss coroutine. CKSUBI, CKSUBR to compute local code checksum. SFXBAD to hang this Stage and reach consensus to reload. RELTRY to initiate an external reload of local memory.

#### Initialization

WSLA7 is initialized to dispatch to SLC00.

# Cleanup

None.

# Data Structures

Local Data None.

## Shared Data

BLTST: Block Transfer state. LOCALC, HOTLIM: local code checksum and limit. LOCCON: consensus for this Stage.

I/O Performed

## 5.1.8 Stage MC - Common Memory Checksums

## Function

For each common page in the system except the reliability page, compute its checksum. Force page with invalid checksum to be empty (signalled by an improper page type) but with a good checksum.

## Control Checksum

Computes additive checksum for each page, using a limit provided on each page. A special checksum value (password) signals that the checksum should be recomputed, for system initialization after paper tape loading.

#### Entry Points

Coroutine, called from Stage dispatcher via WSLA7.

## External Calls

MEMTS2 to see whether a page exists in MEMSEG. CKSUBI, CKSUBR to compute code checksum. WSLEEP to dismiss subroutine. SFXBAD to hang this Stage and reach consensus to reset a page with bad checksum. SCLEAR to clear this processor's bit from a fix-it array. SOKAY to signal successful completion of verifying all checksums. WSTMEM to remove a failing memory page from usage.

## Initialization

WSLA7 is initialized to dispatch to SMCOO.

## Cleanup

Pages with bad checksums are set to be unused (invalid page type). Pages with parity failures that can be fixed are marked to be reinitialized. Pages with solid memory parity failures are removed from usage.

# Data Structures

Local Data

SMCNEX: next page to checksum. SMCLAS: page we checksummed last. CKSMEM: flag to signal a page whose checksum may have failed.

# Shared Data

MAPREL: map setting for reliability page. CKSUM: page checksum word. BLTST: Block Transfer state. INTIME: page initialization flag.

I/O Performed

# 5.1.9 Stage MM - Common Memory Management

## Function

This stage consists of four subparts, each to deal with one class of page type:

- 1) Find and maintain the active code pages. If can't find one with a given type, and haven't found the minimum number of code pages needed to run the system, hang in this stage, awaiting a reload. If a spare of the given type exists, copy a fresh page from it. The code pages are allocated starting on the lowest-numbered end of memory. All other page types will be allocated from the high end downwards.

- Find and maintain the required variables pages. If can't find one with a given type, create one and zero it. If not enough memory for all these pages, hang in this stage.

- 3) Find or construct spares of all the code pages.

- 4) Find or construct optional variables pages, up to the maximum ths system can use.

Pass this stage if we get at least to part 3.

# Control Structure

- Starting at the bottom of common memory, each map is checked to see if it is a) in the MEMSEG table and b) its CMAP and LMAP entries agree with its type. This is repeated for all the required code pages until either the necessary code pages have been checked or until memory runs out. If memory runs out, STAGE will hang here.

- 2) Starting at the top of common, the same checks are repeated for the required variables pages. If a page is missing, another is usually found or made into a vars page.

- 3) The spare code pages are next found and entered into LMAP and CMAP tables. If no spare page exists, the original, if it exists, may be copied and saved.

- 4) The optional variables are now checked and set up, if there is room. If there is enough room to allocate all of the previous pages, then any excess pages are marked free.

Entry Points

Coroutine, called from the Stage dispatcher via WSLA7.

#### External Calls

SMMHTS, SMMLTS to check maps and supply free pages or spares if map wrong. MEMTST to check if a page is in the MEMSEG table. SCLROK to say this stage passed and OK. SMMCOP to copy a page of memory to a new page. SMMCP2 to clear and check a variables page. SFXBAD to set and check the consensus. FIXJIF to cleanly reenable jiffy interrupts. WSLEEP to dismiss the coroutine. WST to restart Stage if too little common memory exists for the system to run.

#### Initialization

WSLA7 is initialized to dispatch to SMM00.

# Cleanup

Pages that the system doesn't need are marked with an invalid page type to indicate that they are unused. If memory runs out first, the remaining entries in CMAP and LMAP are marked empty.

#### Data Structures

#### Local Data

SMMHI: the high limit of unchecked pages. SMMLOW: the low limit of unchecked pages. SMMSPA: a word used to hold the location of the spare page of desired type. SMMFRE: remembers any free page that has been found. SMMTOT: total pages allocated so far, biased by count of desired variables.

Shared Data

LMAP: local copy of CMAP. CMAP: system map table by page type. CKSUM: common page checksum. TLIMIT: common page checksum limit. MAPCOM: map setting for communication page. MEMTOT: total number of memory pages, from Stage MD. INTIME: page initialization flag. BLTST: Block Transfer state. COMREL: communication page pointer to reliability page. TYPE4K: common page type word.

#### I/O Performed

## 5.1.10 Stage ID - I/O Interfaces Discovery

## Function

Search through I/O address space for common I/O interfaces. Results are built as a bit-coded table.

## Control Structure

Devices are checked for whether their device status register exists. Existing interfaces are tabled by bit in USEIO. Majority agreement among processors is required to decide that an interface exists.

#### Entry Point

Coroutine, called from Stage dispatcher via WSLA7.

#### External Calls

WSLEEP to dismiss the coroutine. SCLEAR to remove this processor's fix-it vote. STEST to conditionally pass this Stage. SBAD to hang this Stage.

## Initialization

WSLA7 is initialized to dispatch to SID00.

#### Cleanup

None.

# Data Structures

Local Data

IOFIX: fix-it array for voting to change the USEIO table.

# Shared Data

PIDGET: table of PIDs from Stage BD. USEIO: bit-coded table of existing devices. PROCBT: this processor's bit. IOCON: this Stage's consensus. CONFLG: flag to tell Configuration that USEIO changed. CONPNT: pointer to current Configuration page. CONA7: current Configuration dispatch.

## I/O Performed

## 5.1.11 Stage AR - Application-dependent Checks

Function

- 1) Check for any processors that have failed local memory checksums, and initiate Block Transfer to reload them.

- 2) Check for any processors that should be running and aren't, and initiate Block Transfer to reload and restart them.

- 3) Poll initialization checking routines on each code page, if any.

- 4) Check for occurences of successful QUIT retries or unsuccessful real time clock readings, and report them (via traps). Report if jiffy interrupts have stopped occuring.

- 5) If any traps have been saved in the local buffer, tally them in the common memory trap tables.

Control Structure

Functions are performed in order given. If an initialization check routine indicates that initialization needs to be performed, reach consensus and call the specified initialization routine.

Entry Points

Coroutine, called from Stage dispatcher via WSLA7.

External Calls

1-2) RELTO to initiate Block Transfers.

- FIXJIF to cleanly reenable jiffy interrupts following an initialization.

- WSLEEP to dismiss coroutine.

- 4) SCLROK to pass this stage and remove this processor's fix-it bit.

- RCLOCK to read the Stage real time clock.

5) ILLCNT to tally a trap in common memory tables.

Initialization

WSLA7 is initialized to dispatch to SAR00.

#### Cleanup

- 4) Counters for QUIT retries and unsuccessful real time clock readings are cleared.

- 5) Local trap table is cleared.

Data Structures

Local Data

2) TEMP1: bit-coded set of processors to start.

- TEMP2: index of page being called for initialization check.

- Shared Data

- BLTST: Block Transfer state. LOCFIX: Stage LC fix-it array. LOCALC: local memory code checksum and limit. CKSCON: Stage MC consensus.

- 2) PRTIME: time next to check for processors to start up. STIME: local copy of Stage system time. PROIOR: processors that shouldn't be started. SEGCON: Stage MD consensus. PROCEX: bit-coded array of processors that exist.

- 3) LMAP: local table of page maps by type. PGINIT: pointer to initialization check for common code page.

- MAPREL: map setting for reliability code page. 4) QUITRT: count of successful quit retries.

- CLOKRT: count of unsuccessful real time clock reads. PROCNO: index of this processor name in COUTAB. JTIME: real time clock reading at last jiffy interrupt.

- 5) MAPVAR: variables page map. LOCIPT: pointer into local trap table. LOCILL: local trap table.

I/O Performed

Jiffy interrupts are disabled while initialization is performed.

# 5.1.12 Block Transfer

Function

Performs a variety of functions associated with moving blocks of memory around in the machine. In particular, this process performs reloads from external sources, as in packet core, reloads of individual processors from other processors, dumps of portions of memory for diagnosis or verification, and examine and deposit operations for DDT.

## Control Structure

Block Transfer is a large subroutine. It checks the state of the Block Transfer parameters and performs any indicated actions.

#### Entry Points

BLT, or BLTLKD if BLTLOK is already locked. Called from the Stage dispatcher, and from the operational system if there is a transfer in progress.

# External Calls

BLTPRM, BLTPRS to do some checking for transfers to or from individual processors. BLTRLD is the entry to the external reload (packet core) process.

#### Initialization

None.

## Cleanup

A variety of error conditions will terminate the transfer in progress early.

## Data Structures

<u>Local Data</u>

TEMP1: saved subroutine return. TEMP2: which processors were done this call (bit-coded). TEMP3: index of bus being used for backwards bus coupling. TEMP4: correct bus coupler password to use. BBCRST: processor last started. BBCBAD: processor to which backwards bus coupling last failed.

Shared Data

BLTST: Block Transfer state plus error bits.

5/78

BLTLOK: Block transfer lock. BLTTO: timeout on Block Transfer actvity. BLTADD: current Block Transfer address. BLTSIZ: how many bytes to transfer still. BLTDON: how much was transferred in this piece. BLTBFM: map setting for buffer for Block Transfer. BLTBFA: address for buffer. BLTPRO: number of processor that did the Block Transfer. BLTBMK: bit table of processors that had trouble in Block Transfer. BLTDID: number of processor whose address space last transfer was to or from. BLTPOK: PID level for Block Transfer to poke when it's done. BLTSTY: source core type for transfer. BLTSPM: source bit table of processors. BLTDTY: destination core type for transfer. BLTDPI: destination bit table for processors. BLTDPM: destination bit table for this piece of transfer. BLTBUF: 36 word buffer for doing Block Transfers. RLDDEV: current device to reload from. RLDINI: to signal initialization of reload flag parameters. MYPROC: my processor's coupler number. STIME: local copy of Stage system time. LMAP: local table of map settings by type. PRTIME: time when next to try a processor restart. BLTMYM: simulated maps for Block Transfer. COUTAB: table of coupler addresses for processors. PROCEX: bit table of processors in system. PROCBT: my processor bit. PROCNO: my processor number (index to COUTAB). AMPROC: table of coupler passwords by processor. USEBUS: bit table of busses in system. BBCLOK: lock on backwards bus coupling privelege.

# I/O Performed

#### 5.1.13 Quit Handler

Function

Services Non-existent Memory interrupts, also know as QUITS. Each QUIT is retried once in case it was intermittent. If it is solid, check for a "password", which is a special form of the NOP instruction, at the location following the instruction that got the QUIT, and transfer control to its target branch address if it is there. Otherwise, enter the unexpected QUIT handler, which will restart the system in Stage.

## Control Structure

Obtains control via the processor QUIT vector in low address of local memory. Returns to main program or enters unexpected QUIT handler if the QUIT is solid and there is no password. Instruction fetch QUITs and QUITs within the Quit Handler are always treated as unexpected.

## Entry Points

Q50 if even processor (key 0); Q70 if odd (key 1).

#### External Calls

QSUBR, QSUBO to set up parameters during unexpected QUIT, QUIT on instruction fetch, or QUIT in Quit Handler.

## Initialization

Local memory interrupt vectors are initialized to dispatch to Q50 and Q70. UQUIT is initialized to dispatch to SYSUQ, the system unexpected Quit Handler.

#### Cleanup

Unexpected QUITs, QUITs on instruction fetches, and QUITS in the Quit Handler all cause system restarts via the unexpected QUIT routine.

## Data Structures

Local Data

QX: register save area.

QUITFL: flag that is normally set only while inside Quit Handler. QUITAD: address of most recent QUIT. QUITPC: instruction address at most recent QUIT. QUITST: program status at most recent QUIT. 5/78