## **BBN Communications**

# Pluribus Hardware Configuration Maintenance Manual

BBNCC Task Order #83-014

**Revision B**

Date: September, 1983

Submitted To:

Maryland Procurement Office FT. Meade, MD Contract No. MDA 904-83-C-0869

Prepared By:

BBN Communications Corporation 33 Moulton Street Cambridge, MA 02238 Pluribus Board Configuration Marial Version Number: B September 1983

1 6

419 1 2

The information in this document is subject to charge without notice and should not be construed as a commitment by BBN Communications Corporation. While we make every effort to ensure the accuracy and completeness of all our publications, BBBN Communications Corporation can assume no responsibility for the consequences to users of any errors that may remain.

Printed in the United States of America.

Text by Pete Marti (1983), drawing upon Pluribus Document 7: Maintenance; Report No. 3004 (1976).

Edited by Eugene Chang and Shirley Taggart (1993).

First printing May, 1983.

Second printing September, 1983

The following are trademarks of BBN Communications Corporation:

Pluribus

BBN Communications Corporation, 33 Moulton Street, Cambridge, Mass. 02238

,

.

.

ĸ

| Page                                        |

|---------------------------------------------|

| 1 Introduction                              |

| 1.1 Purpose 1                               |

| 1.2 Description                             |

| 2 CONTROL PANEL                             |

| 2.1 PBI-PCB                                 |

| 2.1.1 Purpose                               |

| 2.1.2 Description                           |

| 2.1.3 Switches                              |

| 2.1.4 Master Mode 9                         |

| 2.1.5 Slave Mode 13                         |

| 2.1.6 Line Frequency 15                     |

| 2.1.7 Optional Functions 15                 |

| 2.1.8 Configuration 17                      |

| 3 PROCESSORS 20                             |

| 3.1 Physical Description 20                 |

| 3.1.1 CPA 20                                |

| 3.1.2 CPC 20                                |

| 3.2 Specifications 21                       |

| 3.2.1 Power Requirements 21                 |

| 3.2.2 Performance                           |

| 3.3 Instruction Set And Format Summary      |

| 3.4 Processor States 23                     |

| 3.5 Quit Handling 25                        |

| 3.6 Functional Description                  |

| 3.6.1 Infibus Interface Section             |

| 3.6.2 Microcode Control Section             |

| 3.6.3 Master-Slave Modes 30                 |

| 3.6.4 Programming Considerations            |

| 3.6.5 Multiple Processors                   |

| 3.6.6 Configuration 38                      |

| 4 MEMORIES 41                               |

| 4.1 Functional Description 41               |

| 4.2 Multiple Memory Modules 42              |

| 4.3 Programming Considerations              |

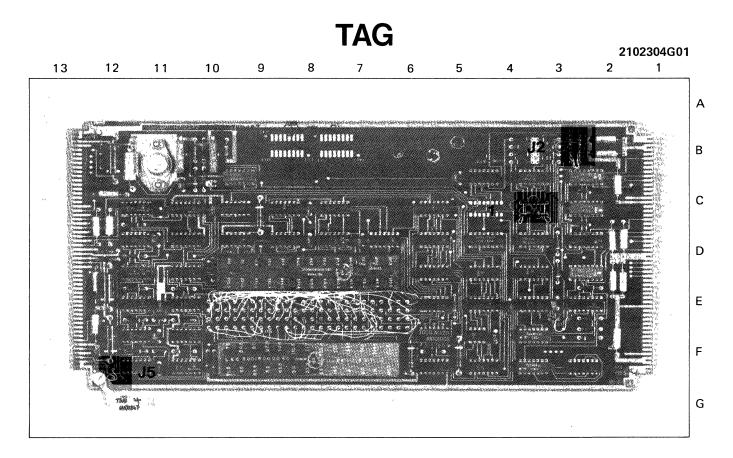

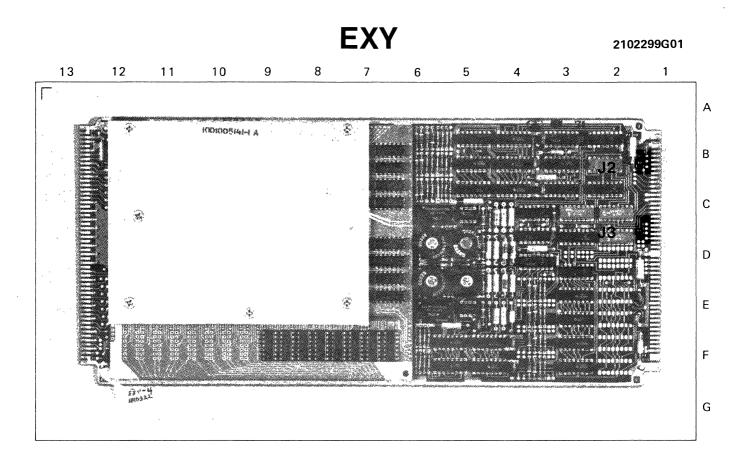

| 4.4 TAG, SID, EXY - Magnetic Core Memory 45 |

| 4.4.1 Purpose                               |

| 4.4.2 Description 45                        |

| 4.4.3 Power Requirements 46                 |

| 4.4.4 Performance Criteria 46               |

| 4.4.5 Configuration 46                      |

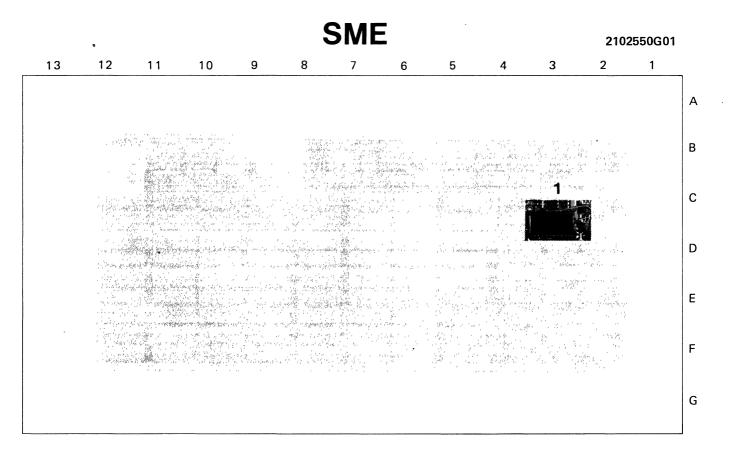

| 4.5 SME - Semiconductor Memory 52           |

| 4.5.1 Purpose                               |

| 4.5.2 Description                           |

| 4.5.3 Performance Criteria                  |

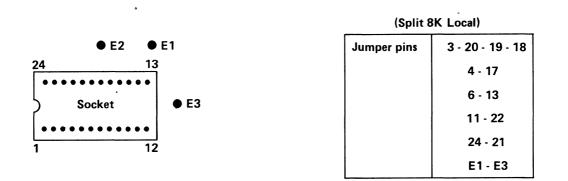

| 4.5.4 Configuration 52                      |

| 5 BUS COUPLERS                              |

| 5.1 A Typical Scenario 56                   |

| 5.2 BCP                                     |

| 5.3 Configuration                              |     |

|------------------------------------------------|-----|

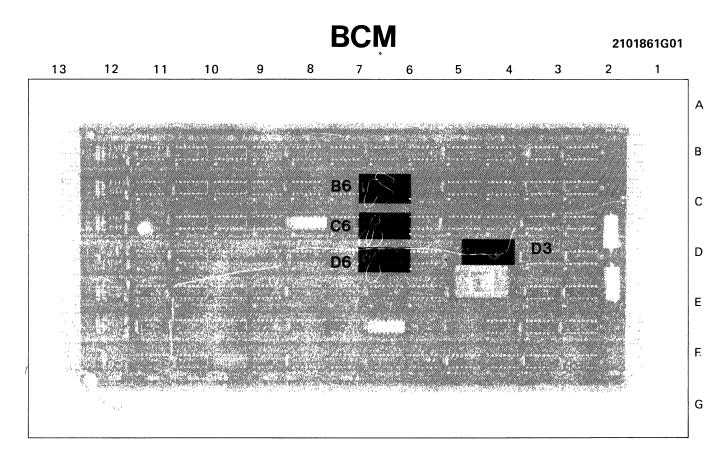

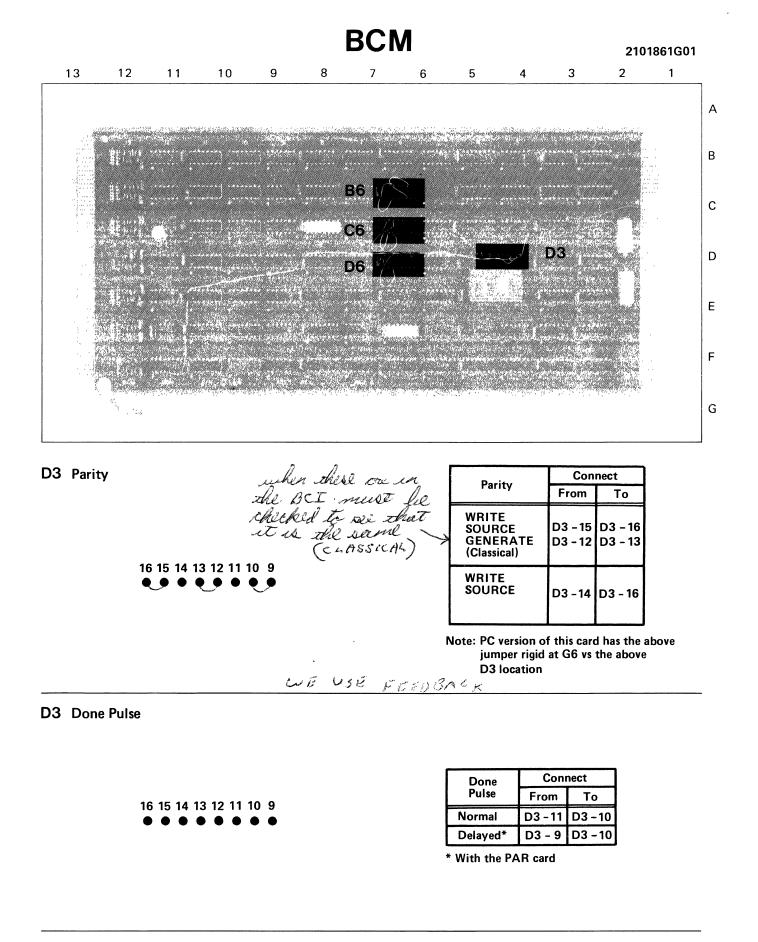

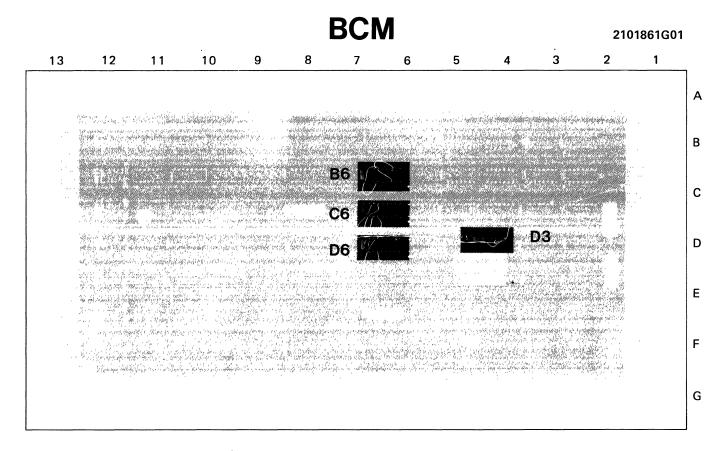

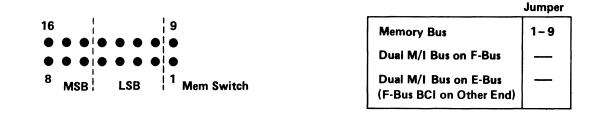

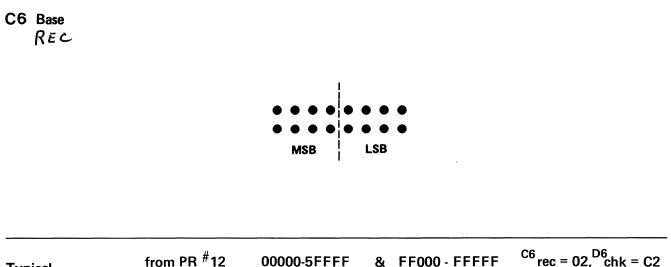

| 5.4 BCM                                        |     |

| 5.4.1 Switches                                 |     |

| 5.4.2 Control Register                         |     |

| 5.5' Backwards Bus Coupling (BBC)              | 65  |

| 5.6 Configuration                              |     |

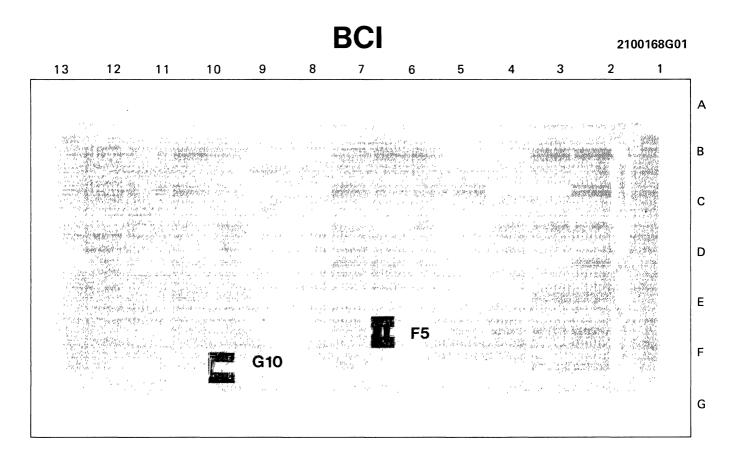

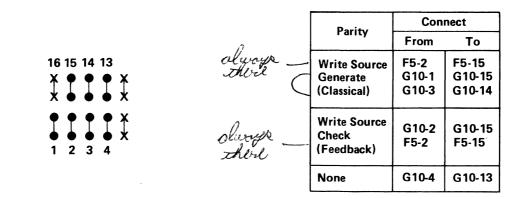

| 5.7 BCI                                        | 67  |

| 5.8 Configuration                              | 67  |

| 5.9 Power Sense                                | 68  |

| 5.10 Parity Generation/Checking                | 68  |

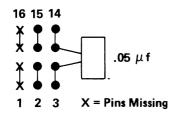

| 6 BCU - BUS CONTROL UNIT                       | 76  |

| 6.1 Purpose                                    | 76  |

| 6.2 <sup>1</sup> Configuration                 | 76  |

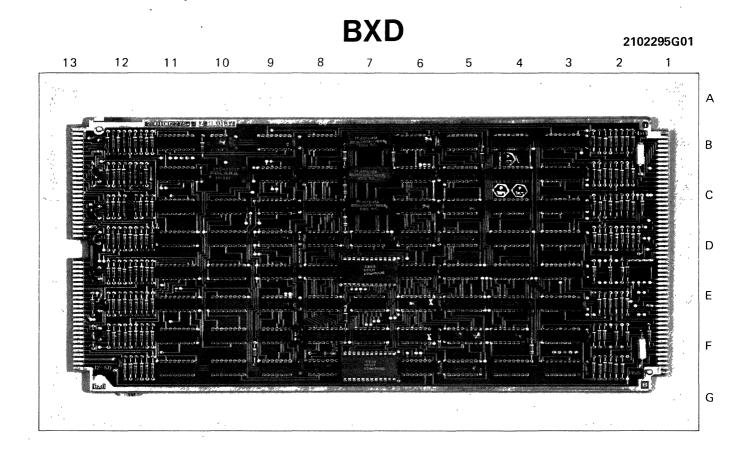

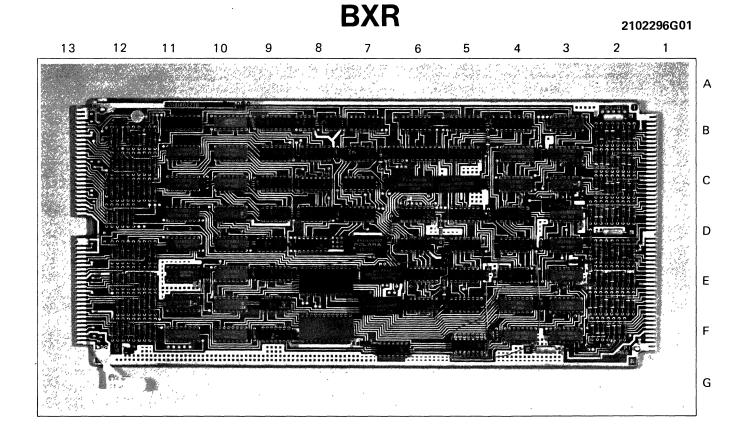

| 7 BXD/BXR                                      | 78  |

| 7.1 BUS EXTENDERS                              |     |

| 7.1.1 Purpose                                  | 78  |

|                                                | 78  |

|                                                | 79  |

|                                                | 80  |

|                                                | 80  |

|                                                | 83  |

|                                                | 83  |

|                                                | 83  |

|                                                | 83  |

|                                                | 85  |

| 8.1.4 External (Remote) Control                | 85  |

|                                                | 85  |

|                                                | 88  |

| 8.2.1 Purpose                                  | 88  |

| 8.2.2 Description                              | 88  |

| 8.2.3 Data Bus Drivers/Receivers & Multiplexer | 88  |

| 8.2.4 Input & Output Data Registers            | 89  |

| 8.2.5 Control Register                         | 89  |

| 8.2.6 Read/Write Control & Status              | 89  |

| 8.2. $\hat{T}^{\dagger}$ Configuration         | 91  |

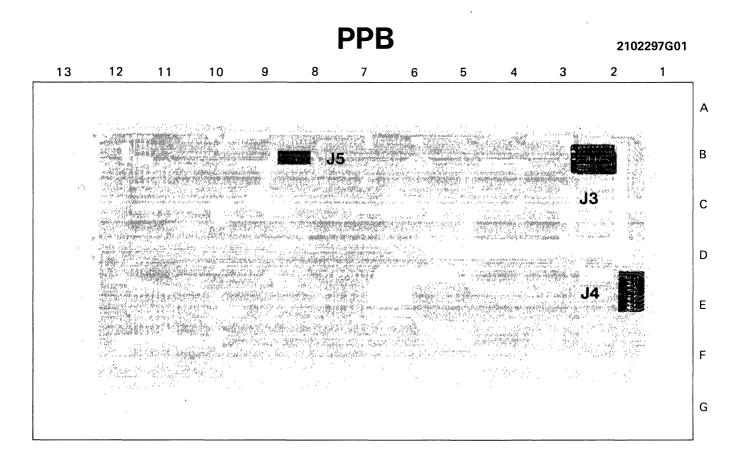

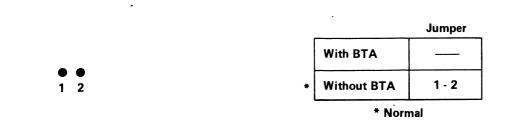

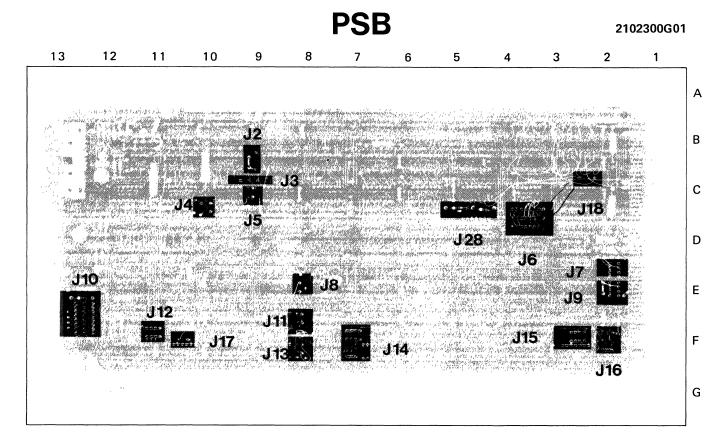

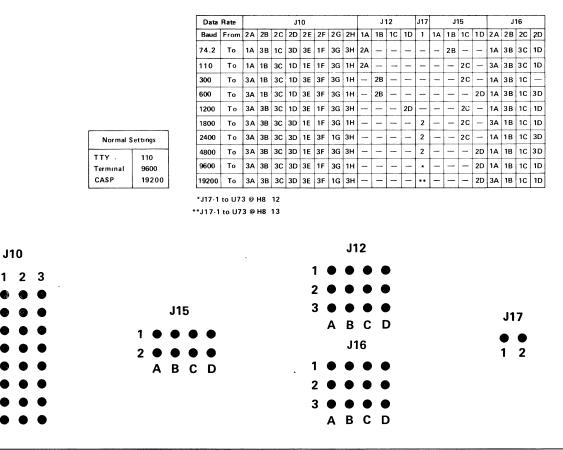

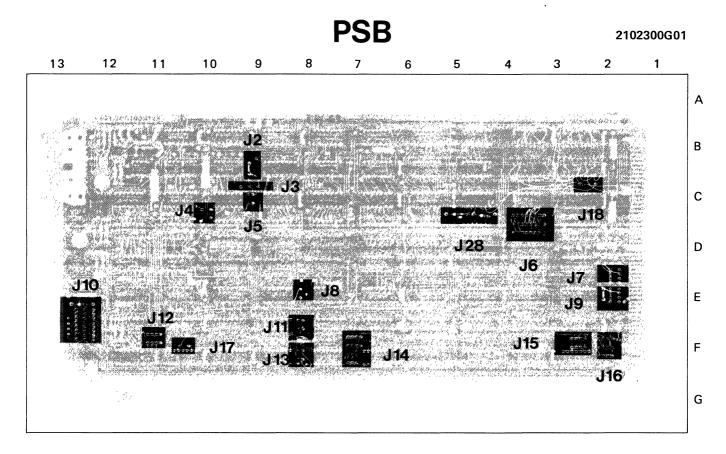

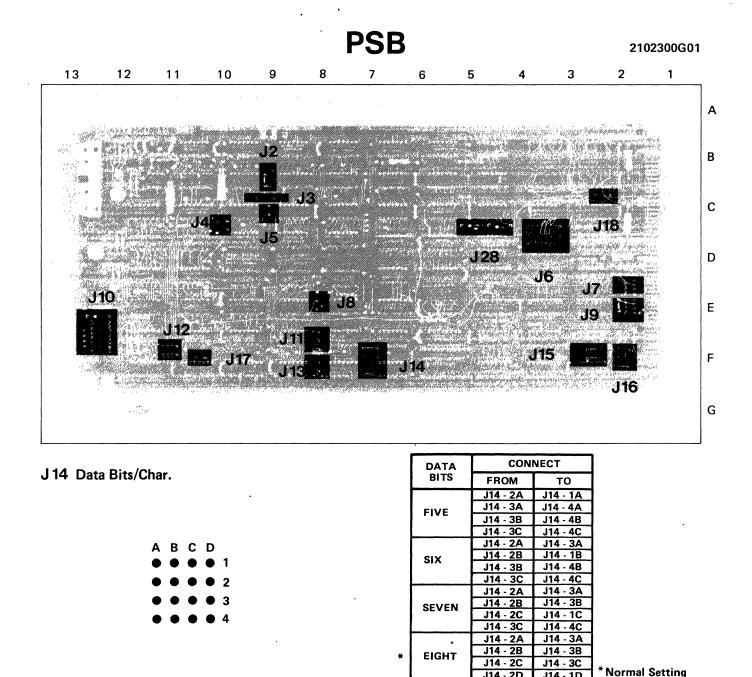

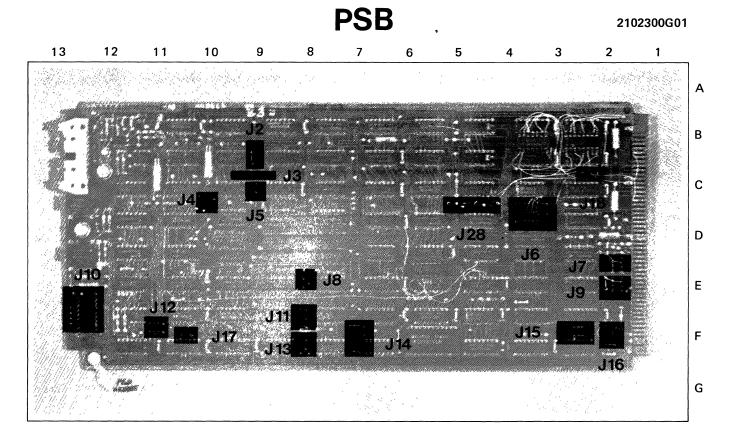

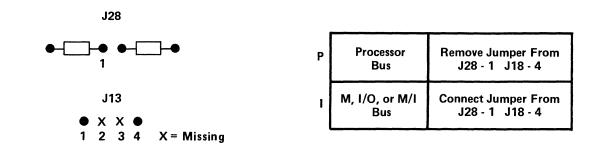

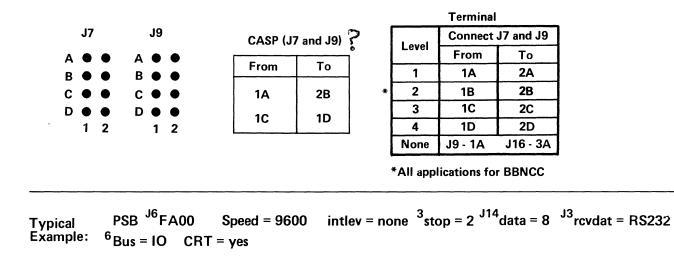

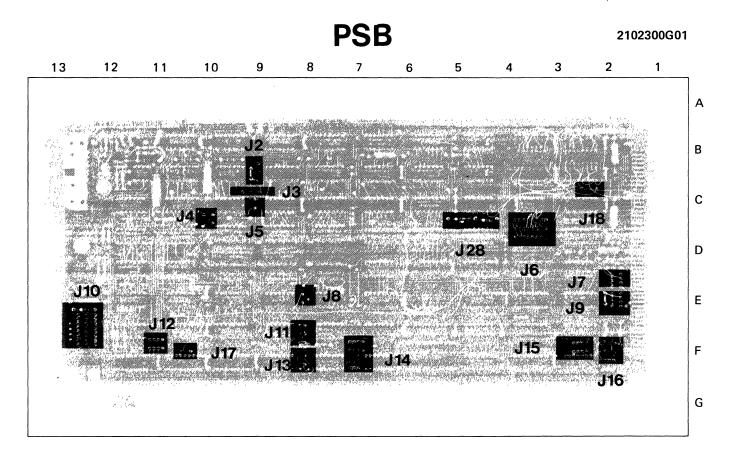

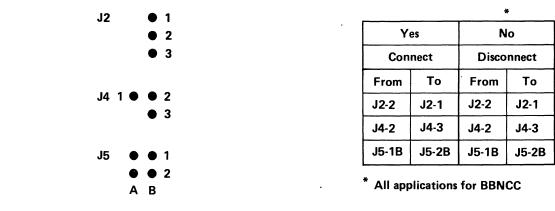

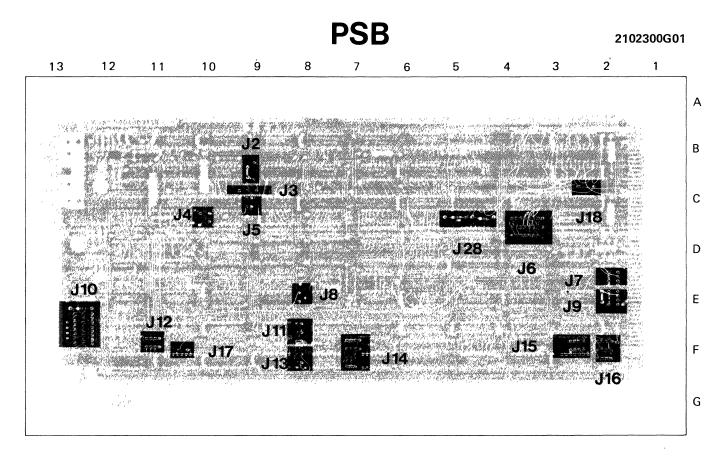

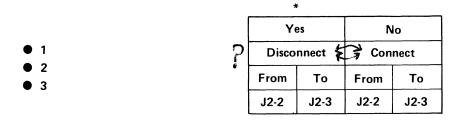

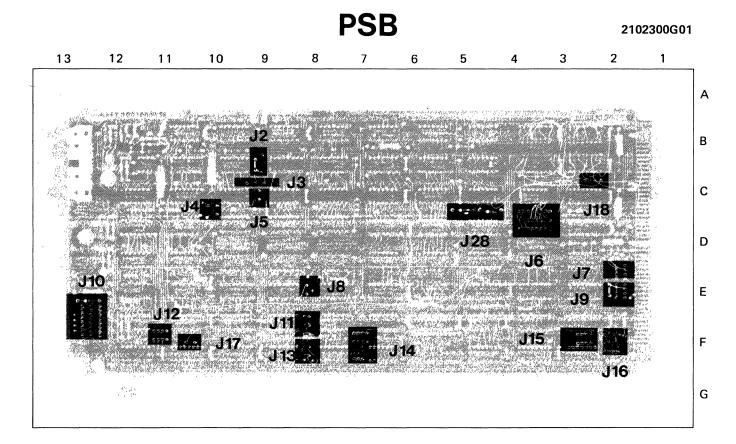

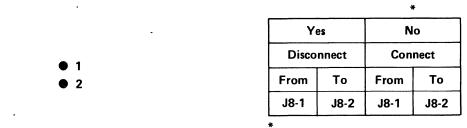

| 8.3 PSB - PERIPHERAL SERIAL BUFFER             | 94  |

| 8.3.1 Purpose                                  | 94  |

| 8.3.2 Description                              | 94  |

| 8.3.3 Cabling                                  | 94  |

| 8.3.4 Configuration                            | 95  |

|                                                | 104 |

|                                                | 104 |

|                                                | 104 |

|                                                | L04 |

|                                                | 105 |

|                                                | 107 |

|                                                | 108 |

| 8.4.7 Indicators 1                             | 108 |

.

`,

| 8.4.8 Reload Connector Pin Assignments 108       |

|--------------------------------------------------|

| 8.4.9 Modem Conector Pin Assignments 110         |

| 8.4.10 Configuration 110                         |

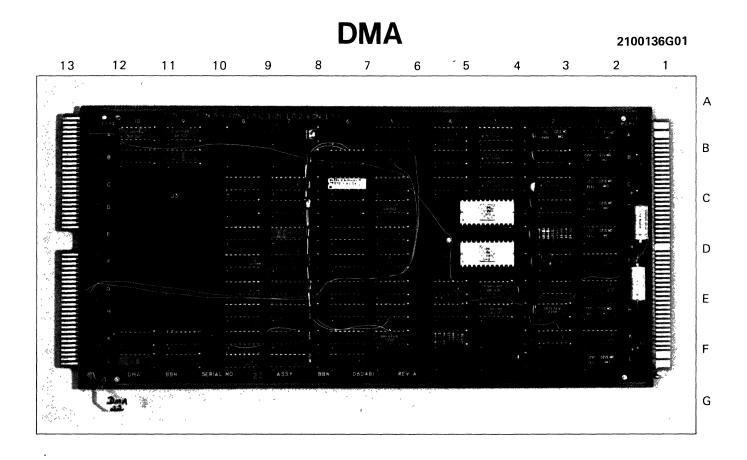

| 9 DMA - Direct Memory Access 112                 |

| 9.1 Purpose 112                                  |

| 9.2 Infibus Interface                            |

| 9.2.1 Address and Registers                      |

| 9.3 Device Interface                             |

| 9.4 Implementation                               |

| 9.5 Switches (on DI)                             |

| 9.6 Addresses                                    |

| 9.7 DMA Logic Description                        |

| 9.8 Configuration                                |

| 10 HOST PORTS                                    |

| 10.1 HLC - Local Host Interface                  |

| 10.1.1 Purpose                                   |

| 10.1.2 Host Connections                          |

| 10.1.3 DMA Connection                            |

|                                                  |

|                                                  |

|                                                  |

|                                                  |

|                                                  |

| 10.2.3 DMA Connection                            |

| 10.2.4 INFIBUS Configuration                     |

| 10.2.5 Configuration                             |

| 11 MODEM PORTS                                   |

| 11.1 MLR-MLX Low Speed Modem Interface           |

| 11.1.1 Line Protocol 141                         |

| 11.1.2 Programming                               |

| 11.1.3 Configuration                             |

| 11.2 MUR-MHX High Speed Modem Interface 145      |

| 11.2.1 Line Protocol                             |

| 11.2.2 Programming 147                           |

| 11.2.3 Configuration 149                         |

| 12 MISCELLANEOUS BOARDS 160                      |

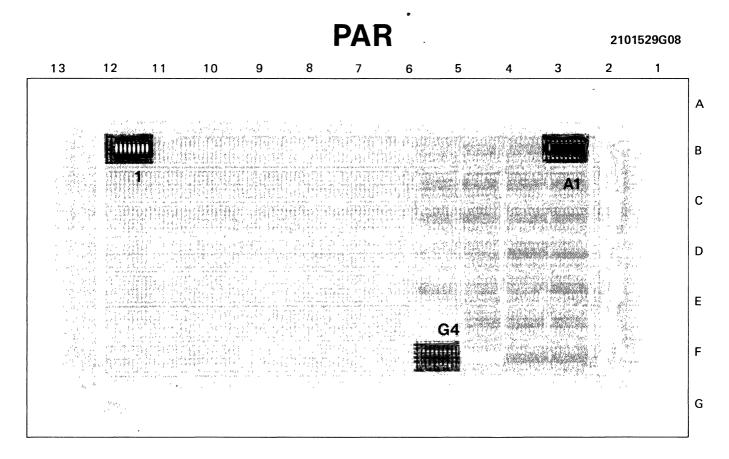

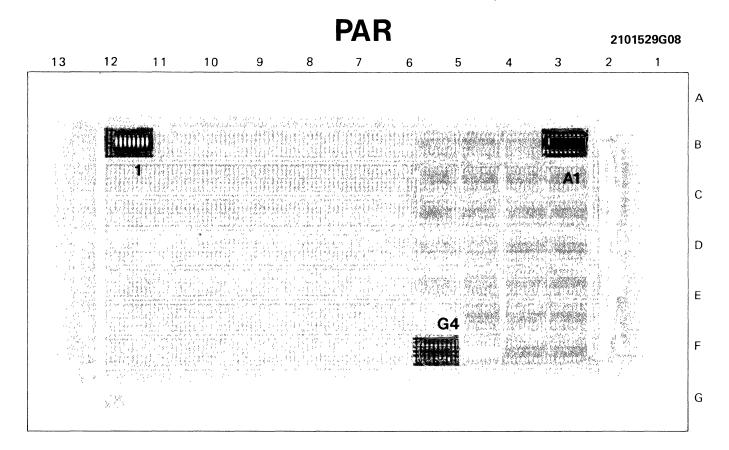

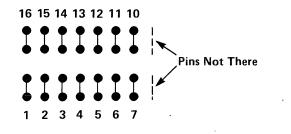

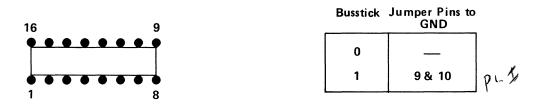

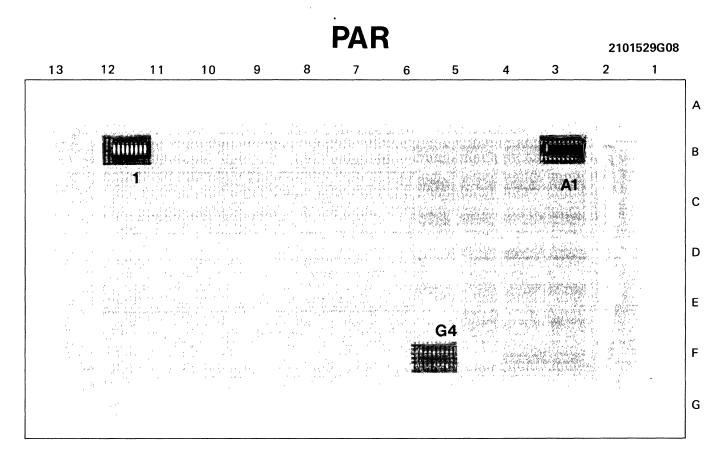

| 12.1 PAR - Parity Card                           |

| 12.1.1 Purpose                                   |

| 12.1.2 Write Source Gen. or Class. Parity 160 g  |

| 12.1.3 Write Source Check or Feedback Parity 161 |

| 12.1.4 Parity Algorithm 162                      |

| 12.1.5 Implementation                            |

| 12.1.6 Implications                              |

| 12.1.7 Configuration 163                         |

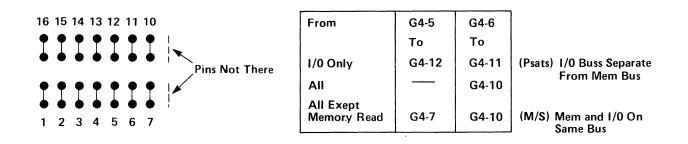

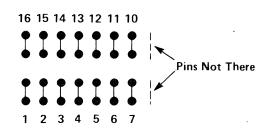

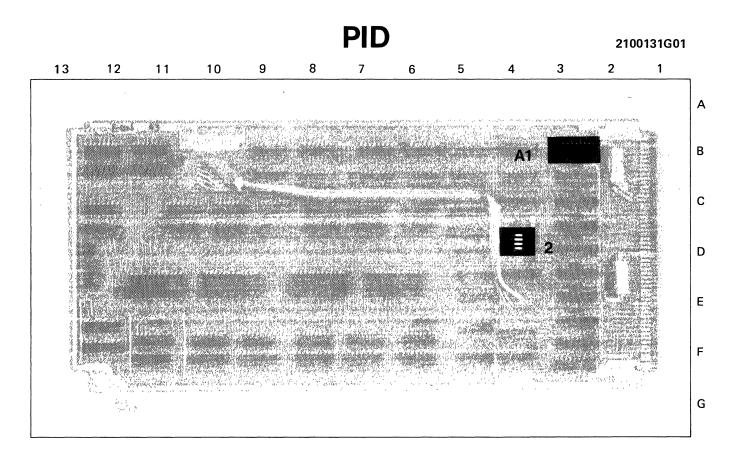

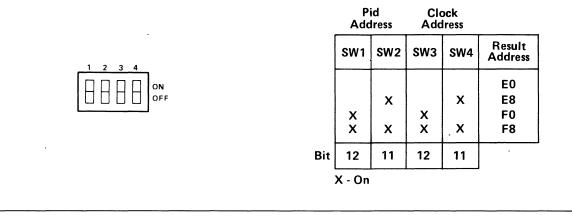

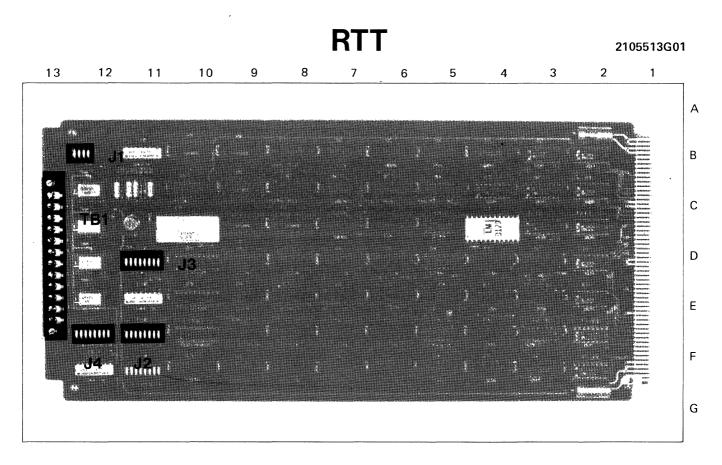

| 12.2 PID - Pseudo-Interrupt 167                  |

| 12.2.1 PURPOSE 167                               |

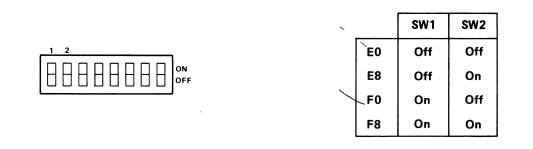

| 12.2.2 Addresses (XY=E0, E8, F0, F8) 167         |

| 12.2.3 Configuration                             |

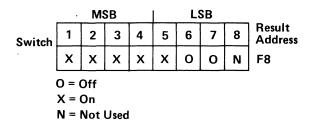

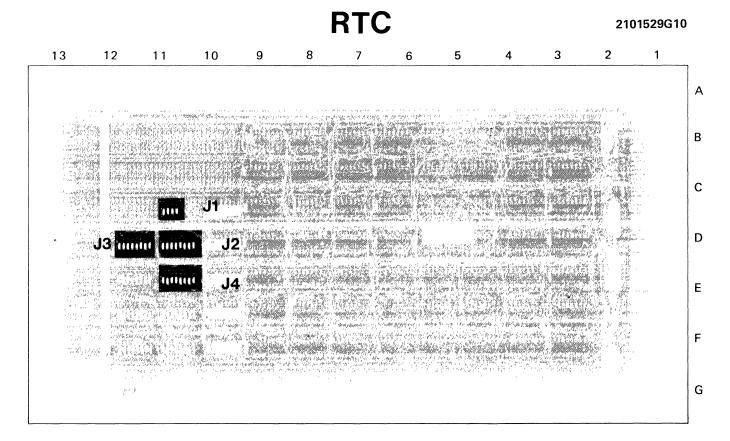

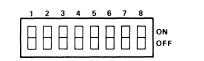

| 12.3 RTC                                         |

|                                                  |

|                                                  |

| 12.3.1 Purpose                            | 170 |

|-------------------------------------------|-----|

| 12.3.2 Addresses (XY=E0,E8,F0,F8)         |     |

| 12.3.3 Configuration                      | 171 |

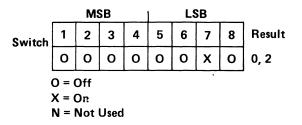

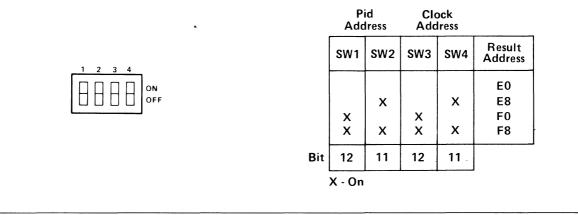

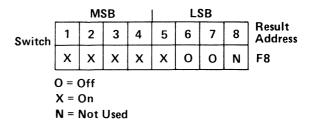

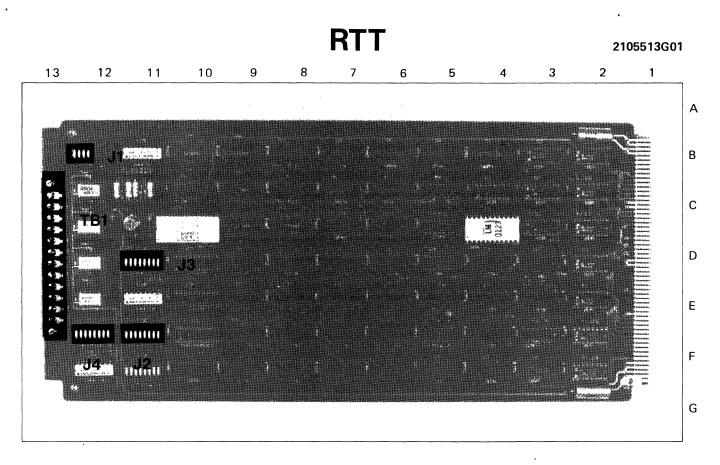

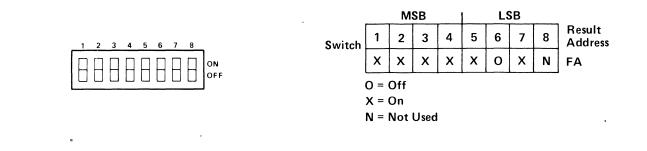

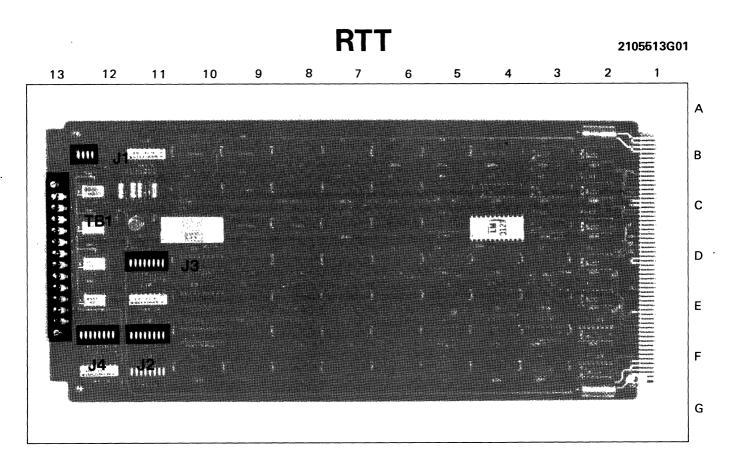

| 12.4 RTT                                  | 174 |

| 12.4.1 Purpose                            | 174 |

| 12.4.2 Description                        | 174 |

| 12.4.3 Addresses (XY=E0,E8,F0,F8)         | 174 |

| 12.4.4 Configuration                      | 175 |

|                                           | 179 |

| 13.1 Master Slave Modules                 | 180 |

| 13.2 Addressing                           | 181 |

| 13.3 Bus Access and Service               | 182 |

| 13.4 Selection and Service Control        | 182 |

|                                           | 183 |

|                                           | 185 |

| 13.4.3 Internal Interrupts                | 186 |

| 13.4.4 External Interrupts                | 186 |

| 13.4.5 Self Interrupts                    | 187 |

| 13.4.6 Line Interrupt Operation           | 187 |

|                                           | 189 |

| 13.5.1 Select Cycle Lines                 | 190 |

| 13.5.2 Service Cycle Timing               | 192 |

|                                           | 193 |

|                                           | 194 |

|                                           | 194 |

| 13.5.6 Block Transfer Adapter Lines (BTA) | 198 |

| 13.5.7 Memory Option Lines                | 199 |

| 13.6 Pin Assignments                      |     |

|                                           | 202 |

| 14.1 Address Structure                    | 202 |

| 14.2 Programming DMA I/O DEVICES          | 203 |

| 14.3 Non-DMA I/O DEVICES                  | 208 |

| 15 BPK - BATTERY PACK                     | 209 |

| 15.1 Purpose                              | 209 |

| 15.2 Description                          | 209 |

| 15.3 Indicator Lights                     | 209 |

| 15.4 Voltage Adjustments                  |     |

| 15.5 Preventive Maintenance               | 210 |

| 16 POWER SUPPLIES                         | 211 |

| 16.1 Purpose                              | 211 |

| 16.1.1 Power Failure (PWST-N)             | 211 |

| 16.1.2 Power Recovery                     | 211 |

| 16.1.3 Line Frequency Signal (LFRQ-N)A    | 212 |

| 16.1.4 Descriptions                       | 212 |

| 16.1.4.1 Specifications                   | 212 |

| 16.1.4.2 PS1                              | 212 |

| 16.1.4.3 PS2                              | 213 |

| 16.1.4.4 PS3                              | 213 |

| 17   | APPENDIX A - Master Pluribus Glossary | 215 |

|------|---------------------------------------|-----|

| 18   | APPENDIX B - Host Pinouts             | 260 |

| 19   | APPENDIX C - Looping Plugs            | 261 |

|      | 1822 Distant (750589G02)              |     |

| 19.2 | 1822 Local (750589G01)                | 261 |

•

.

· -

· • .

1 Introduction

1.1 Purpose

This manual describes Pluribus configuration aspects, and provides the necessary documentation to verify and/or to change Pluribus system configuration. In order to effectively utilize this manual, technicians require the System Release Notice (SRN) that is shipped with every BBN Computer Pluribus system.

In order to provide technicians with a useful and comprehensive document, the information in each chapter is divided into sections and subsections. Sections refer to board type, while subsections refer to a specific board. Sections on each board's "function in life" provide additional in-depth board information.

The following pertinent information appears at the end of each subsection:

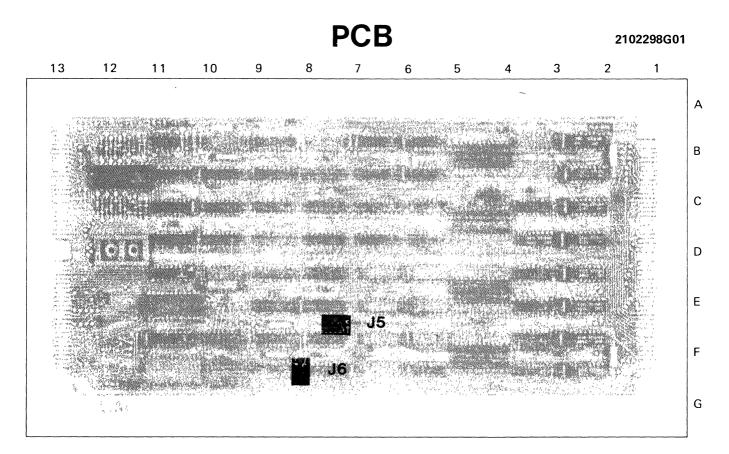

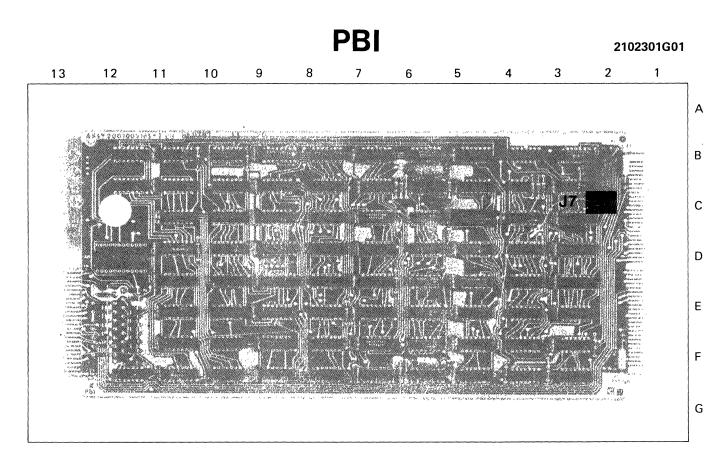

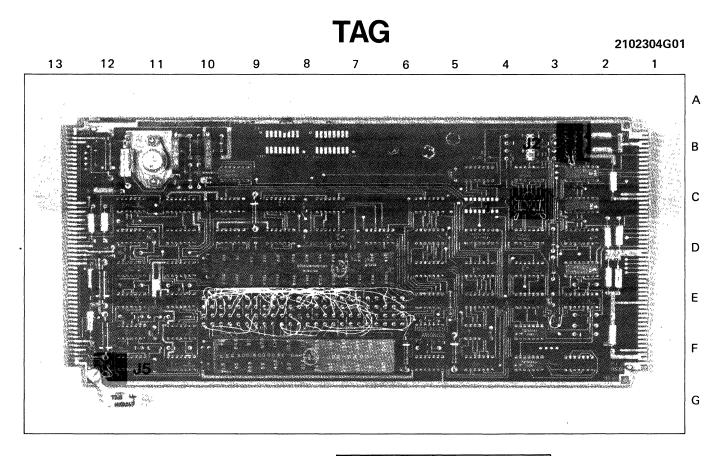

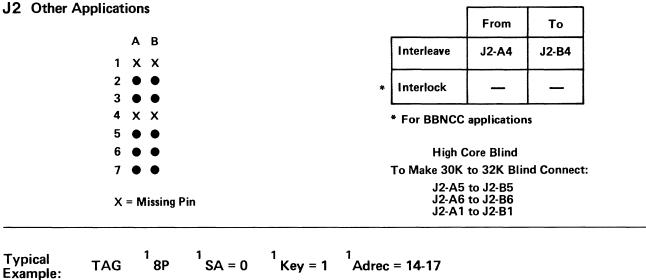

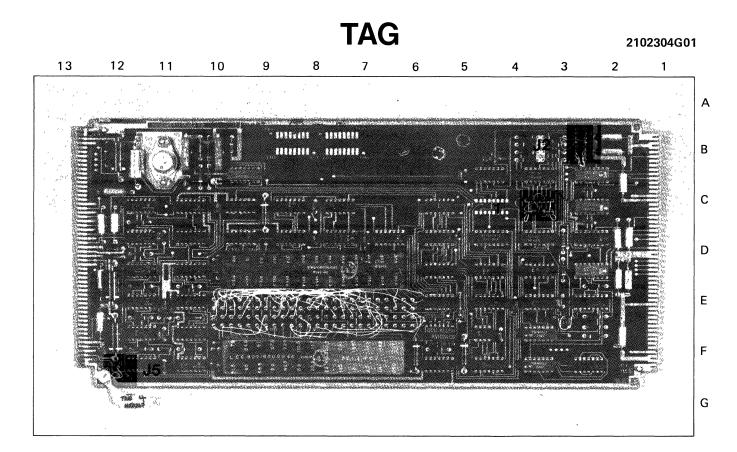

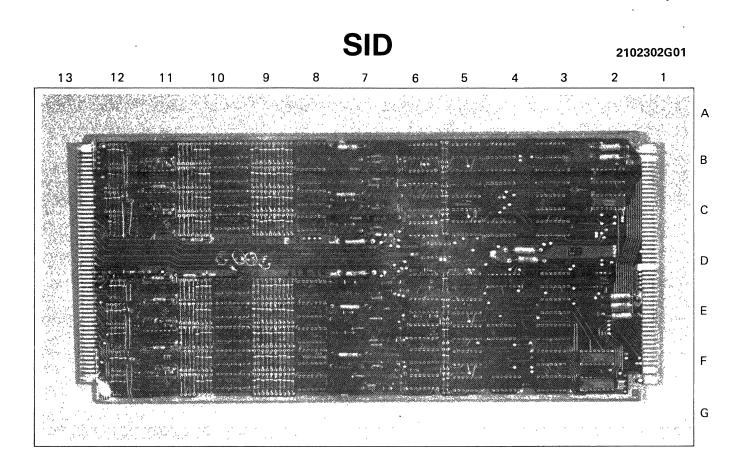

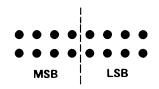

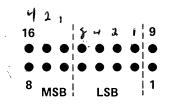

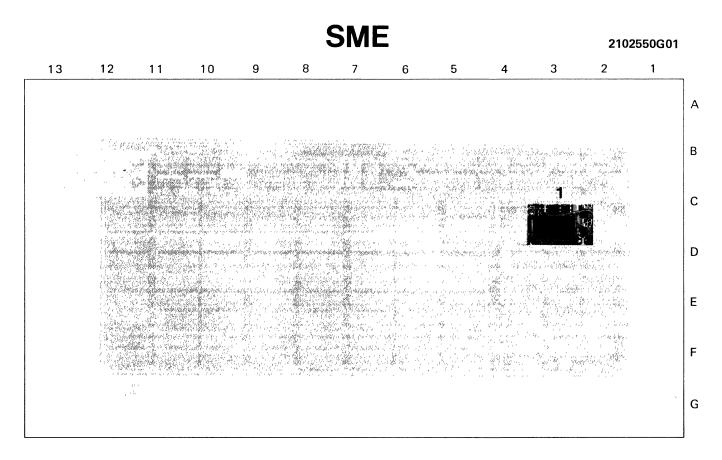

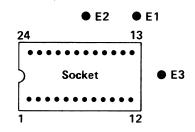

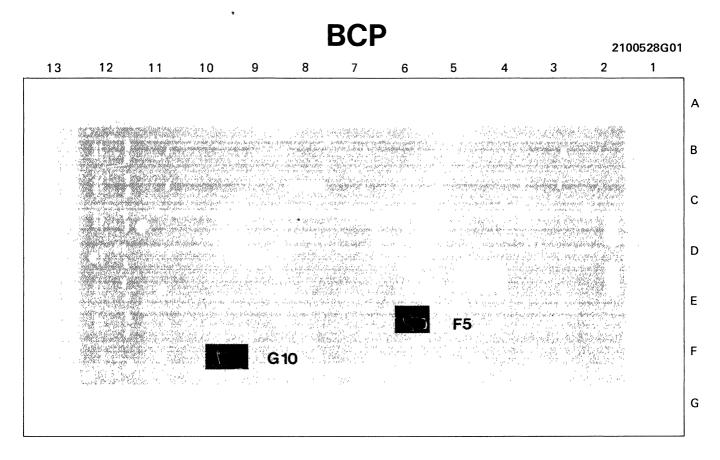

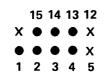

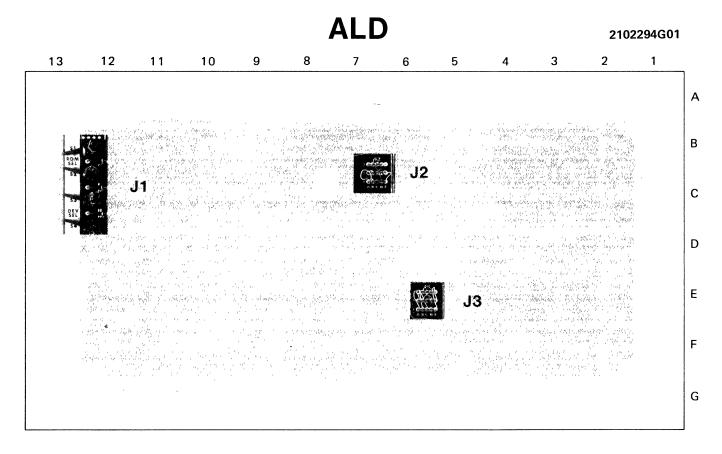

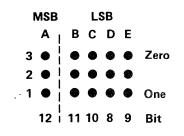

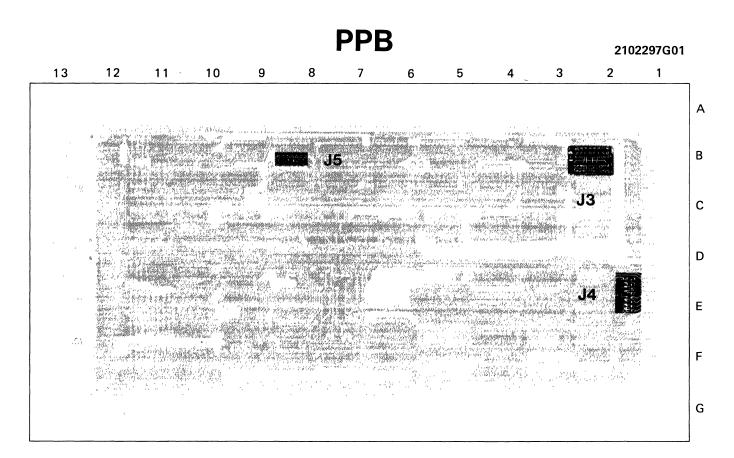

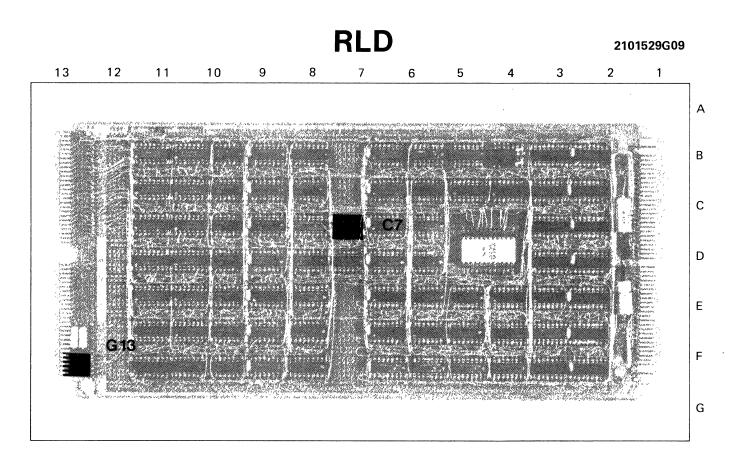

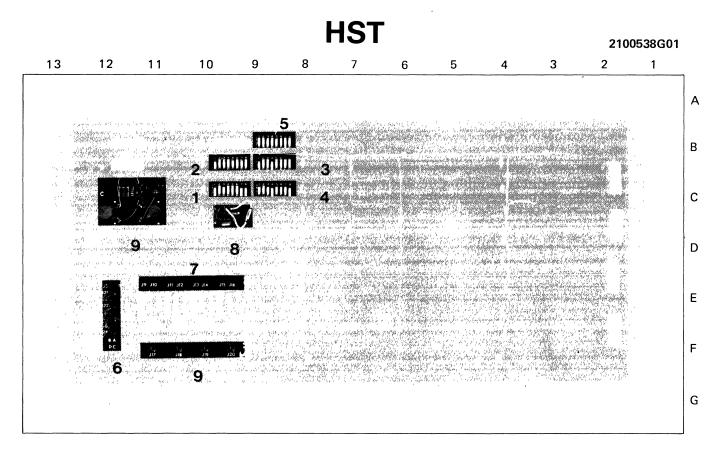

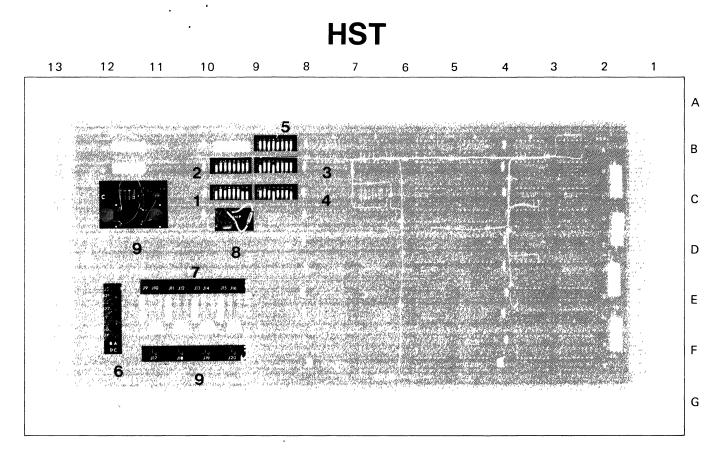

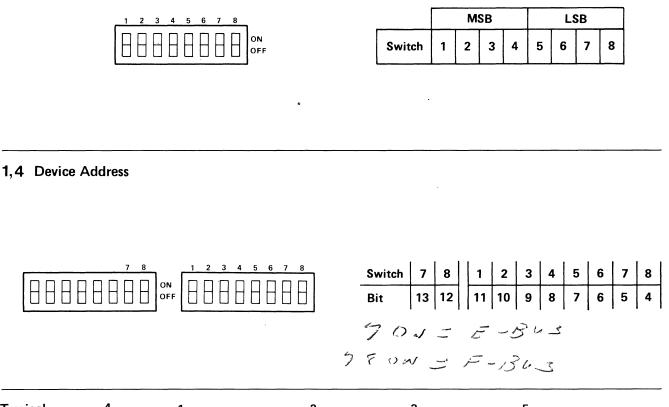

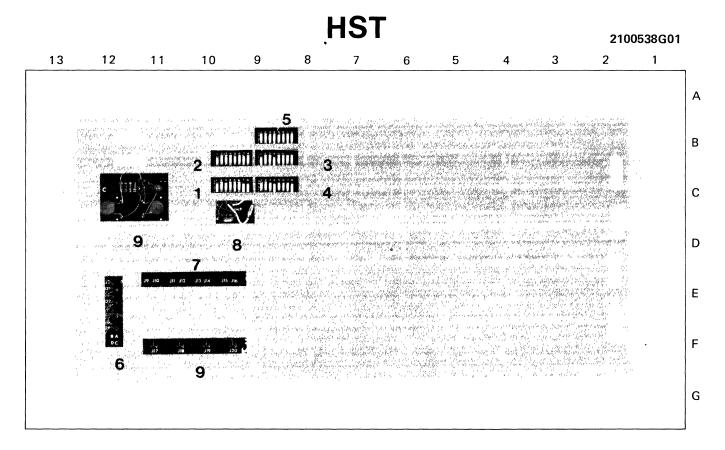

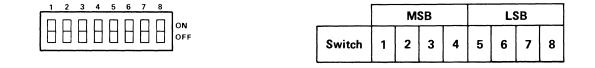

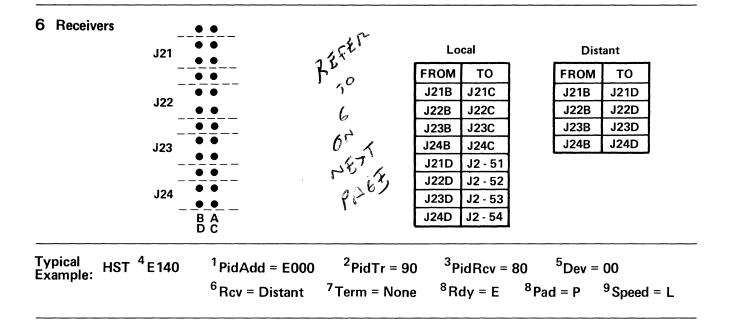

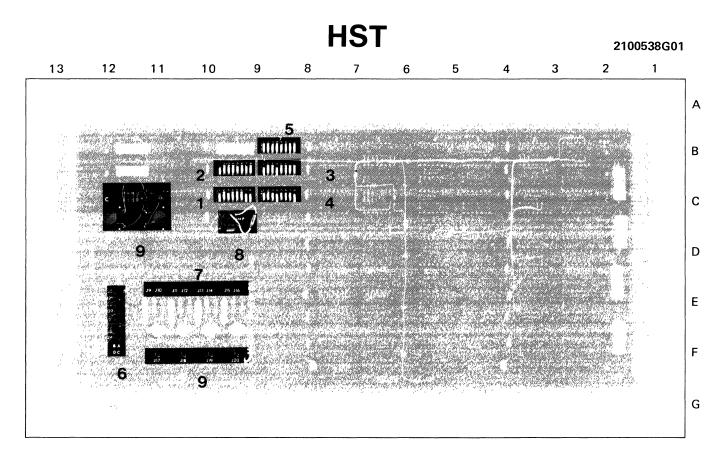

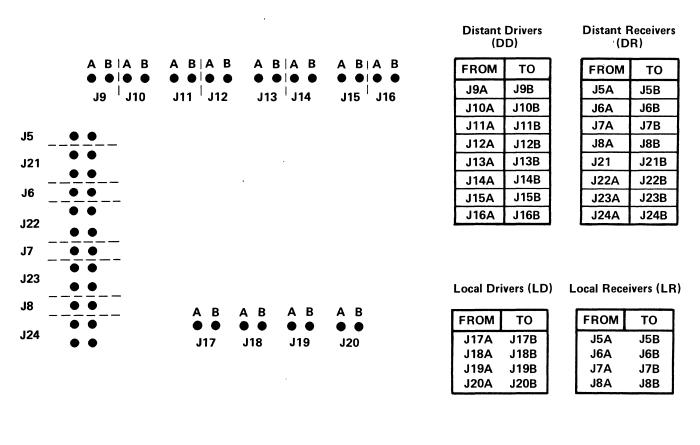

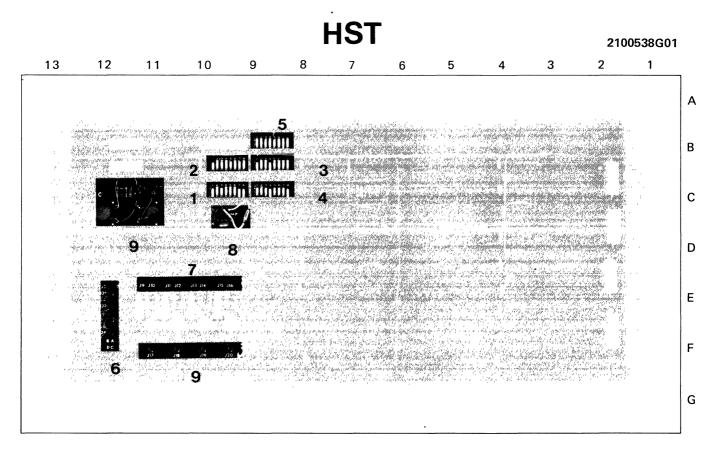

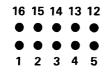

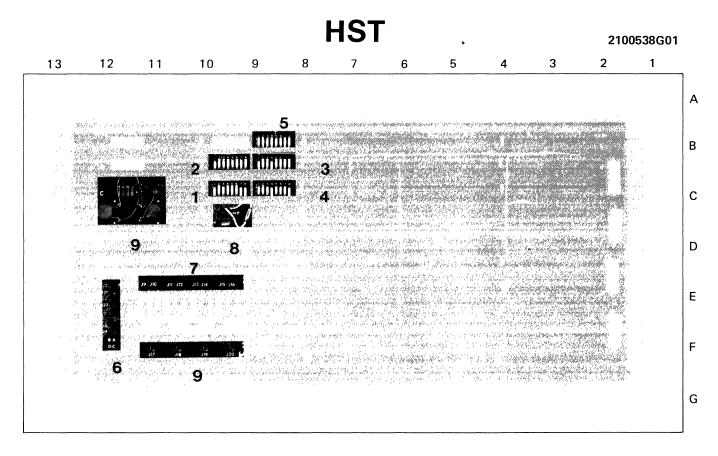

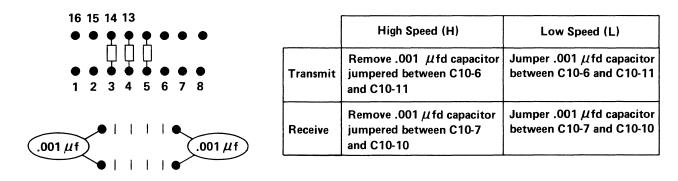

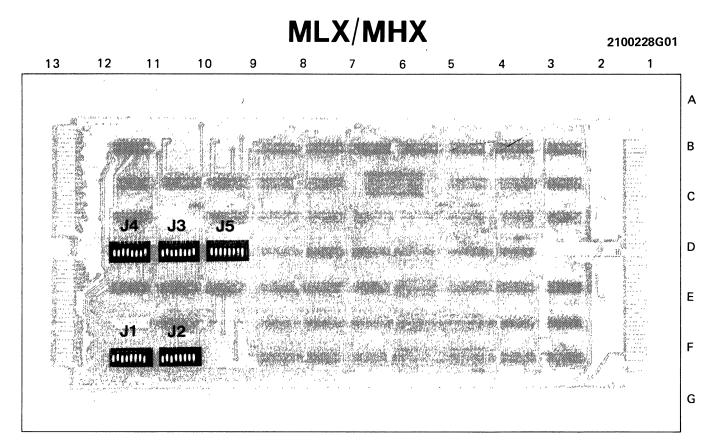

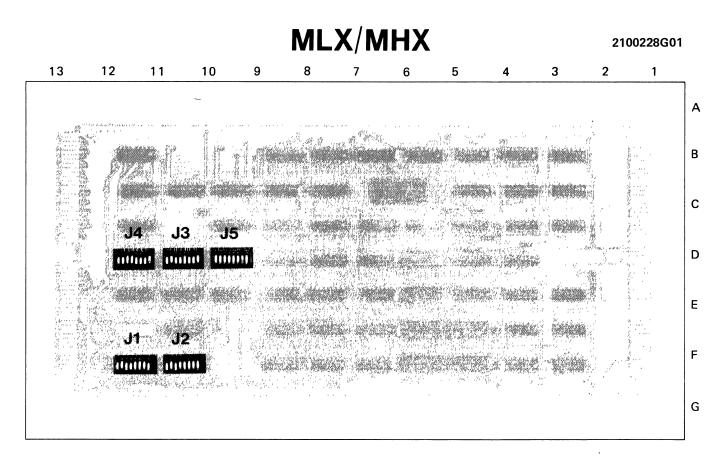

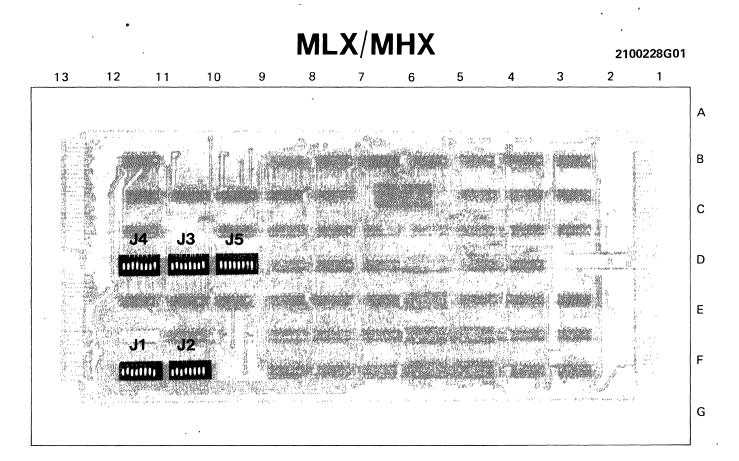

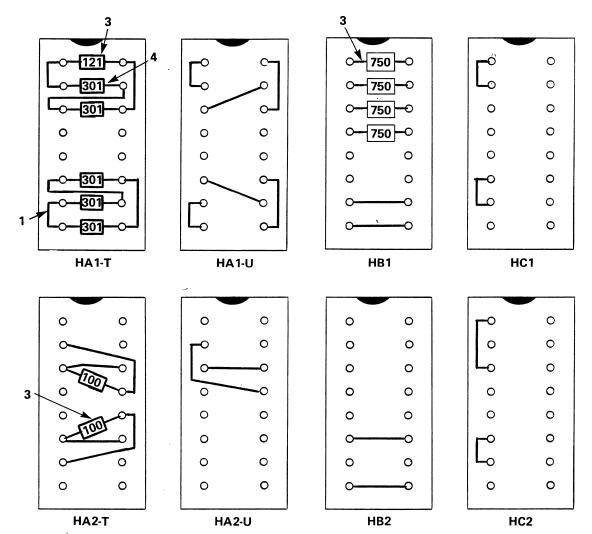

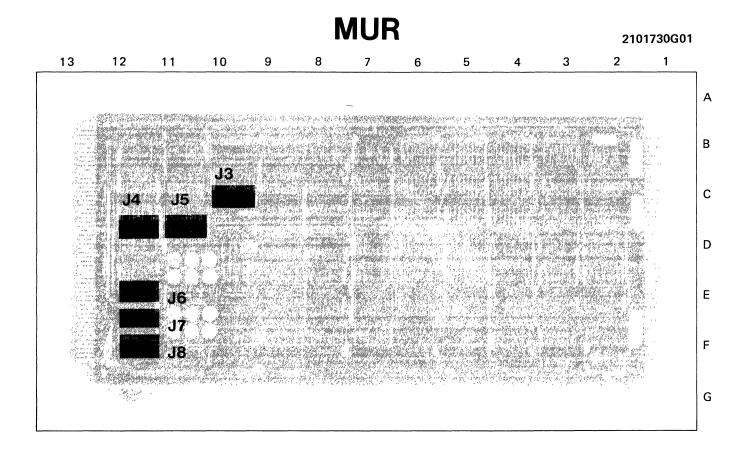

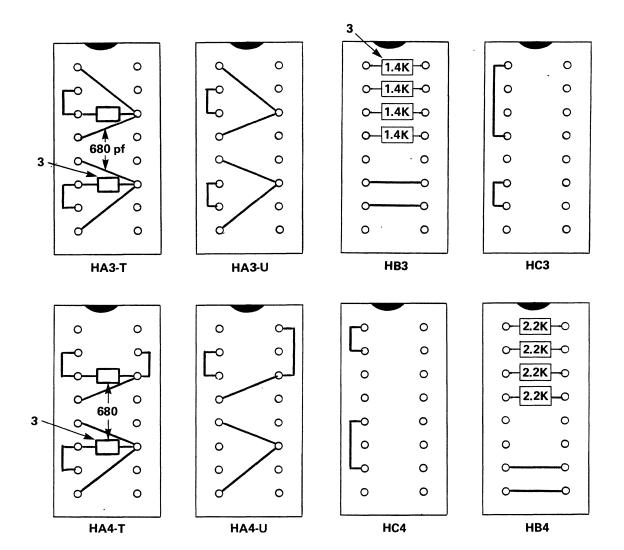

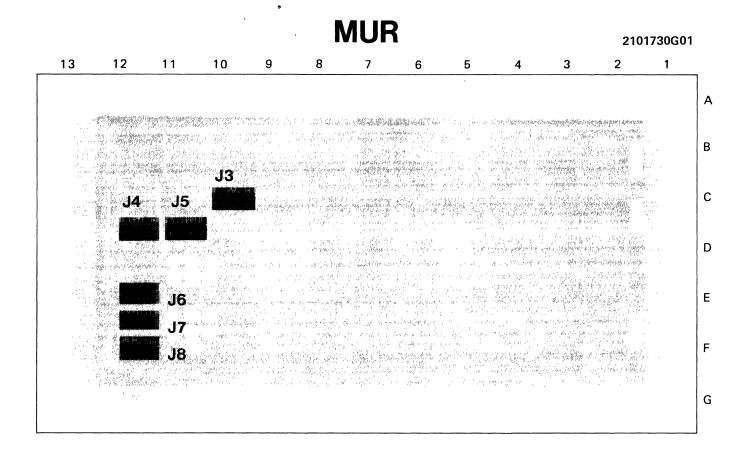

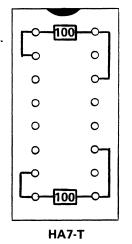

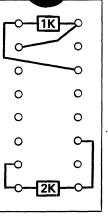

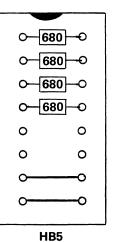

1. A. A pictorial of the board (half-intensity)

B. Relevant strappable fields (full-intensity).

C. A coordinate system indexing fields and boards.

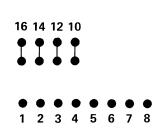

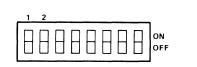

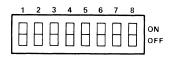

- 2. Exploded view of the strappable fields or representations of the switches.

- 3. Charts for strapping the field and the most probable switch setting.

- 4. A sample SRN for each board.

Introduction

The manual contains the following items to increase its effectiveness and systemize its contents:

- 1. A Table of Contents

- 2. Page and Section Numbers

- 3. Page and Section Labels

- 4. Pictorial, Field/Charts, and Typical Example are connected via superscripts.

- 5. Appendices at the end of the manual to give supportive information for configuring, maintaining, and repairing Pluribus systems.

#### 1.2 Description

The Pluribus has a modular design. Depending on system configuration, many boards have fields that require an initial adjustment. Since identical boards are strapped in different ways depending on their location, board information is particularly important.

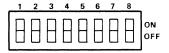

A technician straps a board by adding or deleting wires between wire-wrap pins or by changing the postions (ON/OFF) of the switches.

The SRN is a series of configuration patterns (layouts) used by manufacturing to build a system, and by Field Service to verify the present configuration. The SRN, reflecting the current machine configuration, is invaluable to the technicians that repair and maintain the systems. Without this information, a technician may incorrectly interpret the diagnostics and, as a result, troubleshoot the wrong portion of the machine. In addition, misconfiguration may cause other intermittent problems.

Since the SRN provides a detailed and comprehensive diagram of a product, and as such, is the product's most valuable companion, a technician must ensure that a particular SRN and machine match. An up-to-date and correct SRN is the technician's first step toward solving a Pluribus problem.

REV B

## 2 CONTROL PANEL

2.1 PBI-PCB

## PBI - 2102301G01 PCB - 2102298G01

## 2.1.1 Purpose

The control panel (or console) is an addressable system module that provides the operator with a method to interface with the Infibus, and therefore the system. As such, the control panel can communicate with any other addressable system or peripheral device.

From the control panel, an operator has input and output cabalities to the system, and can perform the following functions:

- A. Analyze system status (Control panel operating in slave mode)

- B. Communicate with the following system modules (Control panel operating in master mode):

- processors

memories

any I/O device

### 2.1.2 Description

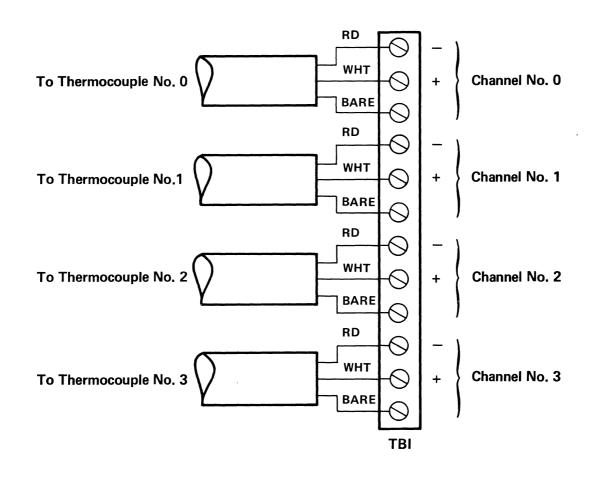

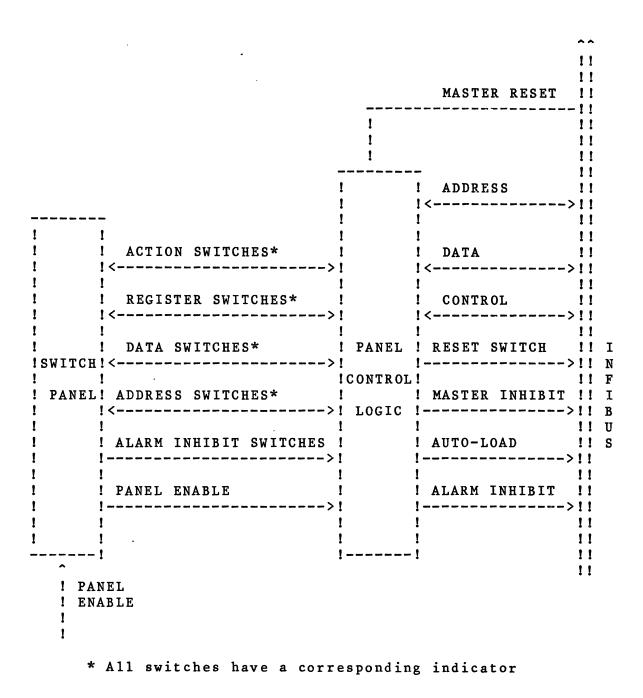

The control panel module consists of the switch panel, PCB card, PBI card, a small ribbon cable to interconnect the PCB and PBI cards, and 3 ribbon cables to connect the switch panel to the PCB and PBI cards.

The control panel uses +5 volts DC power. The control panel has 63 touch-response switches and indicators to regulate system interaction and visual display during program development and maintenance.

> NOTE The touch-response switches require

## Pluritus Board Configuration Manual

## a slight amount of pressure DO NOT overdo it.

The switch is located behind the markings and below the neon indicator associated with the switch.

## CAUTION

Only the operator's fingers should actuate the switches.

DO NOT use pencils, tools and other sharp objects.

NOTE

A touch-response function can be effected only when the panel is enabled.

## 2.1.3 Switches

#### RESET SWITCH

The switch marked RESET is located in the lower lett-hand corner of the switch panel. When touched, the RESET indicator lights, and the bus computer system is reset. During the reset the HALT indicator flashes once for about .1 second.

As a result of resetting the bus, the LOAD switch indicator, the IDLE indicator, and the REGISTER O indicator remain lit until a new command is given. (NOTE: These indicators remain lit even though the RESET switch is no longer being touched.)

#### AUTO-LOAD SWITCH

The auto-load switch, marked LOAD, is located to the right of RESET.

To enable the bootstrap loader press **RESET**. The LOAD indicator lights, indicating the bootstrap loader is enabled.

Whenever AC power is applied, the LOAD switch is automatically enabled and lit. The lit LOAD indicator is extinguished when the panel is disabled, but its indicator is lit again, as soon as the panel is enabled.

## INHIBIT SWITCH

The inhibit switch, marked INH, is the second switch from the right in the bottom row and, when activated, inhibits all system interrupts on priority levels 1 through 4. The INH switch is similar to a toggle switch. Therefore, if the first touch lights (turns on) the indicator, the second touch darkens (turns off) the indicator and vice versa. The INH indicator, when lit, indicates that all system interrupts are inhibited.

## **REGISTER SWITCH**

The top row contains sixteen switches and indicators marked 0 through 15. The word REGISTER. appears directly above the switches. The REGISTER switches select any one of sixteen possible system processor registers (Reter to table 1). The selected register can be accessed by pushing the READ or WRITE switch located in the top row.

The switch indicator most recently touched is lit, while the previously lit indicator is darkened. The number on the lighted switch indicator is the selected register number.

Following a system reset or after AC power is turned on, REGISTER 0 is always selected.

| 1 | Register | 1     | Register Address  | 1     | Register Name !           |

|---|----------|-------|-------------------|-------|---------------------------|

| 1 | Switch   | 1     | (Hex)             | 1     | · 1                       |

|   | 0        | <br>! | FFx0              | 1     | General Register 0 (PC) ! |

| t | 1        | 1     | FFx2              | 1     | General Register 1        |

| i | - 2      | 1     | <br>FFx4          | 1     | General Register 2 !      |

| 1 | 3        | 1     | FFx6              | 1     | General Register 3 !      |

| 1 | 4        | 1     | FFx8              |       | General Register 4 !      |

| 1 | 5        | 1     | FFxA              |       | General Register 5 !      |

| 1 | 6        | 1     | FFxC              | !     | General Register 6 !      |

| 1 | 7        | 1     | FFxE              | 1     | General Register 7 !      |

| 1 | 8        | 1     | FFyO              | 1     | Status Register !         |

| 1 | 9        | 1     | FFy2              | 1     | Instruction Register !    |

| 1 | 10       | 1     | FFy4              | 1     | Firmware A (address of !  |

| ! |          | 1     |                   | 1     | last instruction) !       |

| 1 | 11       | !     | FFy6              | 1     | Firmware B !              |

| 1 | 12       | 1     | FFy8              | 1     | Not used !                |

| 1 | 13       | 1     | FFyA              | 1     | Not used í                |

| 1 | 14       | 1     | FFyC              |       | Not used !                |

| 1 | 15       | 1     | FFyE              | 1     | Halt/Run Control !        |

|   | x = 0, 2 |       | . 6 for processor | - — · | 0, 1, 2, 3 respectively.  |

| 1 |          |       |                   |       | 0, 1, 2, 3 respectively.  |

|   |          |       |                   |       |                           |

Table 1. Register Addresses

Control Panel

7

REV B

#### ADDRESS SWITCHES

Sixteen ADDRESS bit switches marked 0 through 15 are located in the second row from the top, below the REGISTER switches. The word ADDRESS appears directly above the switches. The coded address switches select the address and when touched, the second row READ or WRITE switch acesses this address.

Lighted, the ADDRESS switch indicators represent binary ONES; extinguished, they represent binary ZEROS. Each switch has toggle-switch action. Therefore, if the first touch lights (turns on) the indicator, the second touch darkens (turns off) the indicator, and vice versa.

After touching **RESET** or after AC power is turned on, the address switch indicators are always cleared to hexadecimal 0000.

#### CLEAR (ADDRESS) SWITCH

The switch marked CLEAR. is located in the second row from the top on the right-hand side. When tocuhed it clears the ADDRESS switch indicators to hexadecimal 0000.

#### DATA SWITCHES

The third row from the top (below the ADDRESS switches) contains sixteen DATA bit switches marked 0 through 15. The word DATA appears directly above these switches.

The DATA switches code and generate the written data into the location selected by the ADDRESS or REGISTER switches.

The location can be in memory or a selected processor register. The DATA switches operate in the same manner as the ADDRESS switches. The DATA switch indicators also diplay the data read from any address or register location. CLEAR (DATA) SWITCH

The switch marked CLEAR is located in the third row from the top on the right-hand side. When touched, it clears the DATA switch indicators to hexadecimal 0000.

BUSY INDICATOR

The indicator marked BUSY is located directly above the RESET indicator.

The BUSY indicator lights for at least .l second whenever the Infibus is busy with at least one bus transfer.

IDLE INDICATOR

The indicator marked IDLE is located between the RUN and the HALT switches in the bottom row.

The IDLE indicator lights when the CPU or another system processor is waiting for an external interrupt.

## 2.1.4 Master Mode

The following touch-response switches and LED indicators either initiate or are related, by the control panel logic, to an actual Infibus access.

Such an Infibus access implies that the control panel is the master and the addressed module is the slave.

#### DONE INDICATOR

The DONE indicator is located on the right-hand side in the third row from the top. When lit, the DONE indicator acknowledges that a bus access (with the control panel as the master) has been successfully completed. The DONE indicator remains dark if the

action is aborted.

The DONE indicator functions only when coupled with the following switch actions:

- a. WRITE (to register)

b. READ (from register)

c. WRITE (at address)

d. READ (at address)

e. RUN

f. HALT

g. ADH

- h. STEP

The ATTN switch (which accesses the bus on external interrupt level 1 instead of on the direct data transfer level) does not use the DONE indicator.

WRITE (TO REGISTER)

The switch marked WRITE is located on the lefthand side of the top row.

The WRITE switch lights, and then writes the data displayed in the DATA indicators into the selected CPU or system processor register. If the DONE indicator is lit, access was successful.

READ (FROM REGISTER)

The switch, marked READ is located on the righthand side of the top row.

When touched, the READ switch lights. If the DONE indicator is also lit, the DATA indicators display the contents of the addressed processor register.

WRITE (AT ADDRESS)

The switch marked WRITE is located on the lefthand side of the second row of switches.

The WRITE (at address) switch operates in the same manner as the WRITE (to register) switch with one exception. Depressing the WRITE (at address) switch

writes the DATA indicators settings into the address displayed by the ADDRESS indicators.

READ (AT ADDRESS)

The switch marked READ is located on the righthand side of the second row of switches.

The READ (at address) switch operates in the same manner as the READ (from register) switch with one exception. Depressing the READ (at address) displays the DATA indicators at the address displayed by the ADDRESS indicators.

The first touch of the READ switch does not increment the ADDRESS indicators before accessing the address. However, each successive touch of the READ switch increments the ADDRESS indicators by 2 prior to access. Touching any switch except the REGISTER or DATA switches before touching the READ switch, prevents the ADDRESS indicators from being incremented prior to the access.

#### RUN

The switch marked RUN is located in the bottom row directly to the lett of the IDLE indicator.

If the DONE indicator is lit, touching the RUN switch forces the selected processor to resume executing instructions. The RUN switch indicator remains lit if at least one processor is executing instructions. If the IDLE indicator is lit, the processor unit is waiting for an external interrupt. After all processors have halted program execution, the HALT indicator turns on.

The RUN and HALT indicators may appear to be on simultaneously when the Run and Halt conditions are interlaced at a high repetition rate. If this occurs the HALT indicator may be less intense than the RUN indicator since the HALT has a minimum delay time of .1 second.

HALT

Control Panel

REV B

The switch marked HALT is located to the right of the IDLE indicator in the bottom switch row.

If the DONE indicator is lit, touching the HALT switch forces the selected processor to stop executing instructions. After all processors have halted program execution, the HALT indicator is lit.

ADDRESS HALT

The switch marked ADH (Address Halt) is located directly to the right of HALT in the bottom row.

When the address on the Infibus compares exactly to the ADDRESS switch indicators of the switch panel the HALT indicator is lit. The selected processor is halted as long as the DONE indicator remains lit. The ADH switch is ineffective during the time the panel control logic, functioning as the master, accesses the Infibus.

The ADH switch-indicator has toggle action.

#### STEP

The switch marked STEP is located to the right of the ADH in the bottom switch row.

Touching the STEP switch lights its indicator and causes the addressed processor unit to execute the next instruction. At the completion of this instruction the contents of the selected processor register (REGISTER 0-15) are displayed on the DATA indicators. The DONE indicator must remain lit following this action.

#### ATTENTION

Touching the ATTN switch causes the generation of an "attention" interrupt. The ATTN, switch differs from all other switches since it does not actuate its function until the touch is released. The ATTN indicator may appear to remain off if the processor immediately services the attention interrupt. However, if the processor was not interrupted upon release of the ATTN switch, then the ATTN switch inicator remains lit and the control panel is locked until the interrupt is serviced.

This condition occurs:

- a. if all processors are halted

- b. if the INH switch indicator was lit prior to releasing the ATTN switch

- c. if the CPU is operating with all interrupts inhibited

The ATTN switch can always be switched off by touching and releasing the switch a second time, thereby unlocking the control panel.

The control panel address (device number) is issued for the ATTN interrupt on priority level 1.

#### 2.1.5 Slave Mode

The control console ADDRESS and DATA switchindicators are used either for visual display or for manual input of information during processor execution.

There are two 16-bit registers in the panel control logic, one for address and the other for data, that can be addressed by processors and other master system modules. Each of these registers is associated with its respective set of switch-indicators on the panel. The registers are assigned special addresses that can be accessed in the same manner as a location in memory. To display data on either the ADDRESS or DATA indicators, the program must include a registerto-memory class of instruction when the display data is written into the addressed panel register.

To sample the ADDRESS or DATA switch settings, the program must include a memory-to-register class of instruction where the switch contents are read from the panel register.

REV B

A maximum of four separate control panels may be operated on the Infibus. However, most Pluribus systems have only a single panel, and this panel is always designated as control panel number 1. Table 2 lists the possible register addresses for four control panels in a system.

Since a conflict between an operator and the program may occur during a write function, the contents of the register should be read back to verify what was written. If the contents do not compare, another attempt should be made to write the proper data.

Table 2. Addressable Registers (Switch-Indicators)

| 1 | Panel No. | 1 | Panel Register | Name | 1 | Hex Address | ! |

|---|-----------|---|----------------|------|---|-------------|---|

| 1 | 1         | 1 | address        |      | ! | FF80        | ! |

| 1 | 1         | 1 | data           |      | 1 | FF82        | 1 |

| 1 | 2         | 1 | address        |      | 1 | FF84        | 1 |

| 1 | 2         | ! | data           |      | ! | FF86        | 1 |

| 1 | 3         | 1 | address        |      | 1 | FF88        | ! |

| 1 | 3         | 1 | data           |      | 1 | FF8A        | ! |

| 1 | 4         | ! | address        |      | 1 | FF8C        | ! |

| ! | 4         | ! | data           |      | 1 | FF8E        | ! |

## INTERRUPT INHIBIT

Figure 3 shows the location of three toggle switches on the back side of the switch panel assembly. These switches permit manually enabling or inhibiting the power fail interrupt, power recover/autoload and line frequency interrupts.

POWER FAIL The PWR FAIL switch (S72) (PFIN) is located as shown in figure 3. Placing the switch OFF inhibits the power fail interrupt (PWST).

In the ON position the power fail interrupt is issued when the BCU detects a power fail condition.

**POWER RECOVERY**

Control Panel

The PWR RCVRY switch (S71) (PRIN) has three positions, OFF, IN, and AL, to inhibit or to enable the power recovery (PWST) interrupt and power recovery via auto-load (PRAL) interrupts.

In OFF position neither interrupt is issued upon recovery.

In IN position the power recovery interrupt is enabled and the auto-load interrupt is inhibited.

In AL positon, the power recovery via auto-load interrupt is enabled and power recovery interrupt is inhibited.

The auto-load interrupt can only be issued if the system contains an auto-load module (ALD).

2.1.6 Line Frequency

The LINE FREQ switch (S70) (LFIN) inhibits or enables the line frequency interrupt (LFRQ) (JIFFY CLOCK). Turning the switch OFF inhibits the line frequency interrupts. In the ON position, the line frequency interrupt is enabled and a level 4 interrupt service request is issued once during each line frequency cycle.

2.1.7 Optional Functions

Several optional functions are available as jumpers or switches on the switch panel.

The On switch position has the same effect as connected jumper; the OFF position the same effect as a disconnected jumper. The switches or jumpers are described in table 3.

| Switch or<br>Jumper                                       | ! Jumper<br>! Position                        | Function                                                                                                                                                                                               |

|-----------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYTE (S66)                                                | ! ON<br>! .<br>! * OFF<br>!                   | Only bytes are read or<br>written. Full word can<br>be read or written.                                                                                                                                |

| INCREMENT<br>CONTINUOUS<br>READ OR WRITE<br>ADDRESS (S67) | ! ON<br>!<br>!<br>!<br>! * OFF<br>!<br>!<br>! | Address increments<br>continuously during read<br>mode if S68 (below) is<br>ON; during write mode if<br>S688 and S69 are ON.<br>Address increment<br>disabled during<br>continuous read/write<br>mode. |

| CONTINUOUS<br>READ/WRITE<br>(S68)                         | !<br>! ON<br>!<br>!<br>! * OFF<br>!<br>!      | Enable continuous<br>read/write mode.<br>Disable continuous<br>read/write mode.                                                                                                                        |

| WRITE<br>INCREMENT<br>(S69)                               | ! ON<br>! !<br>! !<br>! * OFF<br>!            | Allows address increment<br>during write.<br>Address does not<br>increment during write.                                                                                                               |

Table 3. Optional Switch/Jumper Functions.

.

The \* jumper positions are the standard settings

2.1.8 Configuration

The following pages explain the strapping necessary to properly configure the PBI and PCB for BBNCC applications.

.

,

REV B

## **3 PROCESSORS**

## 3.1 Physical Description

Each processor(CPU)module consists of two printed circuit cards, the CPA and the CPC. These cards are interconnected by their backedge connectors (those opposite the Infibus end). An ICM module connects the first CPU on a bus (or primary processor) to the BCU. The ICM module contains three connectors that interconnect the CPA, CPC\* and BCU.

In multiprocessor systems, the secondary (or buddy) processor CPA and CPC\* are interconnected by an IDM interconnect module containing two connectors. The CPU is always located in the first slot left of the BCU (viewing the chassis from the insertion end). The CPA is always left of the CPC\*. Secondary processors are always located in the slot to the left of the primary CPU. Secondary processors are always located in any slots to the left of the CPU.

Edge connectors on the primary circuit cards are keyed to prevent improper insertion on the Infibus. However, circuit cards are not keyed to prevent improper relative slot locations.

\* In older systems a CPB may be used instead of a CPC. Both cards are functionally equivalent.

3.1.1 CPA

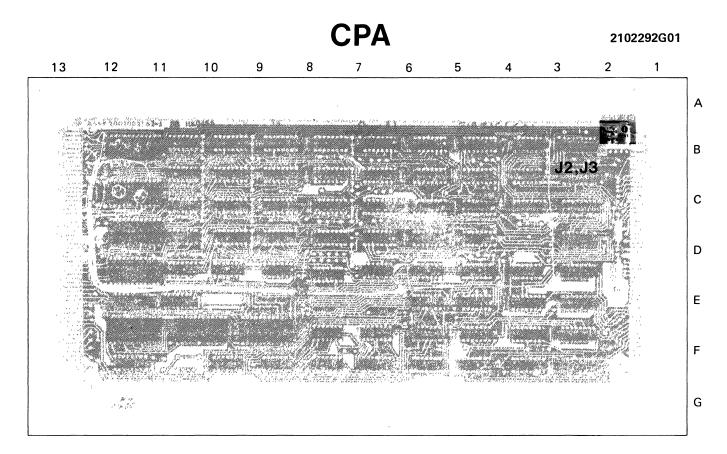

#### CPA - 2102292G01

The CPA contains the ALU, ALU multiplexor (MUX), register file and Infibus interface logic.

3.1.2 CPC

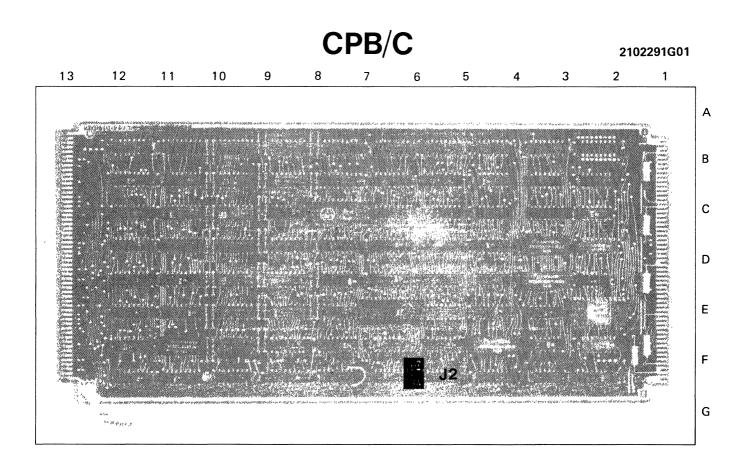

CPC -2102291G01

REV B Pluribus Board Configuration Manual The CPC contains the microcode control logic and ROM storage. 3.2 Specifications 3.2.1 Power Requirements +5V, +15V and -15VAll voltages are plus or minus 1% 3.2.2 Performance Instruction execution rate 250 instructions per second (average) Arithmetic function process time 165 nanoseconds 2 parallel 16-bit operands Logical function process time 145 nanoseconds 2 parallel 16-bit operands Addressable registers 12 Program Counter (RO) 16-bits 1 General registers (R1-R7)16-bits 7 Status register 16-bits 1 Instruction register 1 Firmware register A 16-bits 1 Firmware register B 16-bits 1 Halt/Run Control 1 Interface registers 4 16-bit Receiver register Transmitter register 16-bit Address register 16-bit Protect key 2-bit

| Internal control registers | 3                    |

|----------------------------|----------------------|

| E register                 | 16-bit               |

| S register                 | 12-bit               |

| M register                 | 36-bit               |

| Microcode memory           | 256-word, 36-bit ROM |

| Lookup table memory        | 256-word, 8-bit ROM  |

3.3 Instruction Set And Format Summary

The basic processor in the Pluribus system is a microprogrammed general purpose 16-bit minicomputer with 8 general registers (including a program counter) a status register, and a control register. These registers may be accessed externally by other devices. The multiprocessor architecture allows one processor to stop another, to examine and change its registers, and to restart the system.

Most of our Pluribus systems use a general purpose processor that executes a 65-mnemonic instruction set. This processor functions as a central processor unit (CPU) in a single processor system, or as either primary processor (CPU) or a secondary processor in a multiprocessor system. The Infibus can accomodate up to three secondary processors.

Every primary processor is connected with the BCU. This allows the processor to recieve system interrupts on priority levels 4 through 1, and to perform central processing functions. Secondary processors have no control over system interrupts.

There are 8 general instruction classes: MOVE, ADD, SUBTRACT, INCLUSIVE OR, EXCLUSIVE OR, AND, COMPARE, and TEST. Each of these instructions may use a variety of addressing modes including register-toregister, memory-to-register, register-to-memory, indexed, indirect, and auto-indexed. Rotate, shift, conditional branch, unconditional branch, and subroutine call instructions are also available.

The bits in the processor's status register test the branch conditions, and have tests for the following results: result = zero

result = negative

carry on last arthmetic instruction

register value odd

overflow

value greater-than on last comparison

value equal on last comparison

loop completion

The branch can occur on either value TRUE or FALSE. Instructions contain either one or two words. The processor's status register contains 3 programmable flags. The software manuipulates these flags.

The processor recognizes and generates 16-bit addresses. In addition, it contains a 2-bit KEY register which is settable by the SKEY instruction in the processor. The contents of this register are appended to the most significant end of the 16-bit address to generate an 18-bit address. Every memory access by a processor has these two bits appended. Certain of these 18-bit addresses are mapped into 20bit system addresses described later.

The processor operates on either 16-bit words or 8-bit bytes of data. Bit 0 is identified with the low order bit and bit 15 with the high order bit.

## 3.4 Processor States

The processors can be in one of three states: halted, running, or idle. Transitions between these states may be affected either by the processor itself or by external manipulation. The implications of each of these three states are as follows:

- Halt: No instructions executed, interrupts disabled, registers externally accessible.

- Run: Instructions executed, interrupts enabled, registers not externally accessible except control register.

- Idle: No instructions executed, interrupts enabled, registers not externally accessible except control register.

External references to registers which are not accessible will result in a QUIT, as described in Chapter 12. The IDLE state is entered from the running state by executing a WAIT instruction; the HALT state, by a HALT instruction. The RUN state is entered from the Idle state by the occurrence of an interrupt.

External manipulation of these states operates as follows:

The processor control register is the only register accessible while the processor is running. To halt a processor, a one is written to its control register.

The processor normally halts when the instruction it is currently executing is completed. However, if the control register is read between the time that a zero is written to the control register and the time that the processor completes its current instruction, the halt signal will be lost. To guarantee that a processor does in fact halt, an algorithm such as the one in the following example is used: To guarantee an algorithm such as the one in the following example is used:

L: Write 1 to the processor control register. Read some other processor register. If QUIT results go to L. At this point the processor is halted.

To start a processor, one must initialize all important registers to needed values and store the number two into the control register.

This is done as follows:

- 1. Assure that the processor is halted.

- 2. Initialize the program counter to the address of the program to be executed.

- 3. Load the general registers with any values to be passed to the program

- 4. Initialize the status register to specify the enabled interrupt levels, initial status flags, and programmable flags.

- 5. Set bit 11 (hexadecimal constant 0800) to activate the processor.

- 6. Write a 2 to the control register and to start the

processor.

The ability to single-step through an instruction sequence is one of the processor's advantageous features. The procedure for this function is identical to the procedure for starting a processor except that a 3 is written to the control register instead of a 2.

## 3.5 Quit Handling

Processors requesting access to memory locations on I/O registers do so by directly or indirectly placing the desired address on the appropriate bus along with the required operation (e.g., read, write) and any required data(for a write operation).

When the requested operation is complete, the processor receives a signal called DONE. If no device on the destination bus recognizes the relayed address, or if the device recognizing the address malfunctions, the DONE signal is not returned to the processor. Instead, after a fixed period of time, the BCU on the requesting processor bus will send a QUIT signal to the processor, causing a conventional interrupt. Requests by I/O devices for I/O busses yields an equivalent outcome.

To determine if known devices have disappeared or if new ones have appeared, a device discovery routine in the reliability software searches system address space, reads the device registers, and checks for resulting Quits. This mechanism requires an interrupt level routine which responds to Quits, and then passes the intormation back to the application program. A unique pattern surrounding the Quit instruction generates this routine.

For example, to check for a QUIT occurring when location ABC is referenced you may write the following: LDA A2, ABC NOP BR + 4 -----! L: QUIT BRANCH ADDRESS !

If no QUIT, program continues here. <----!

The QUIT interrupt service, upon receiving control, would check to see if the two instructions following the one which caused the QUIT were NOP and BR . +4. If so, the QUIT service simply stores the two bytes starting at location L (the address of the instruction causing the QUIT plus 8) in the program counter and dismisses the interrupt.

If the two instructions at L-4 and L-2 do not match the NOP BR . +4 pattern, the interrupt service routine handles the QUIT in the usual manner.

Of course, references to ABC which do not cause QUITS cause the execution to continue at L+2 as indicated. Under the control of a microprogram stored in a Read Only Memory (ROM) on the processor module, each processor executes its respective instructions.

## 3.6 Functional Description

The microprogram is stored in one 1024-bit ROM microcircuit components. Each component is arranged in 256, four-bit words. Therefore, the nine components store 256 thirty-six-bit control words that compose the microprogram.

After each 36-bit control word is read out of the ROM (and sometimes modified), the word is decoded into 13 fields to supply enabling and timing signals to functional elements throughout the processor.

Figure 1 shows the general data flow between processor function elements. The functional elements can be grouped into three sections: Infibus interface, arithmetic-register, and microcode control. The Infibus interface section logically interconnects the processor and the Infibus. The arithmetic register section performs arithmetic and logical functions under control of the microprogram. The microcode control section stores, reads out, assembles and decodes the microcode control words.

## 3.6.1 Infibus Interface Section

The Infibus interface section consists of drivers/receivers that interconnect the processor and Infibus. This section also contains address recognition and decoding logic, three 16-bit registers: address (A Reg), data receive (R Reg) and data transmit (T Reg), the run/halt control flip-flops and a protect-key register.

The A, R, and T registers are gated to the Arthimetic Logic Unit (ALU) through the ALU multiplexor (MUX) in the arthmetic-register section. The A register holds addresses placed on the Infibus when the processor is addressing a location in memory or a system register. The R register holds 16-bit data words received on the Infibus. The T register has left- and right-bit shift capability.

The halt/run flip-flop enable processor control functions, and the protect-key bits (address bits AB16 and AB17) enable Key 0 and Key 1 bits, respectively, on the Infibus.

## 3.6.2 Microcode Control Section

The processor microcode control section consists of three registers: E, S and M, the ROM control storage, a ROM data lookup table, and microcode selection logic.

#### E Register

The E register holds 16 bits of data used to modify the next microcode word.

Fields in this register correspond to the macroinstruction word format and specify the instruction code, addressing mode, general register (Rl through R7), index register and, occasionally, a literal operand. E register bits 3 through 0 also operate as a loop counter.

#### S Register

The S register is a 12-bit counter that sequences microsteps, addresses the ROM control storage, and is under control of the microcode word. The four most significant bits (bits 11 through 8) are always ZERO. Bits 7 through 0 are used to address the 256-word ROM.

#### M Register

The M register receives the 36-bit microcode word that specifies the action of the current microstep as well as controlling the next sequential microstep. M register outputs are decoded into enabling signals, and distributed with clock pulses throughout the processor as the processor control logic.

## ROM Control Storage

Microcode control words are stored in the ROM control storage - a 36-bit by 256-word read-only memory consisting of nine 256 by 4-bit LSI microcircuits. The 36-bit microcode word contains 13 fields that are decoded to select operands and specify control functions within the processor.

Test and conditional skip or conditional branch microfunctions are provided to allow coding that minimizes the number of microsteps required per function. Functions of the 13 fields are summarized here:

- a. S Field Specifies type of microcommand. The type may be a normal sequential step, special command, branch, memory synchronize, or conditional jump command.

- b. T and A Fields Select one of 16-logical functions if T=ZERO, or one of 16-arithemetic functions if T=ONE, to be performed by the ALU.

· .

- c. C Field Specifies option of adding or subtracting a Carry In to the ALU and also controls setting Carry and Overflow flip-flops.

- d. D Field Selects the option of skipping the next micro order either unconditionally or based on the ALU output being all ONEs or the jump condition being met.

- e. X Field Selects the X field of 12 registers in register file for an ALU input and/or an ALU destination.

- f. F Field Specifies the X field modification for the next micro-instruction.

- g. Y Field Selects R, A, or T register or literal fields L2 and L1 in the microcode (under control of the M field) for input to ALU.

- h. M Field Operates with other fields to provide different functions. When Y=3, it controls mapping of literals L2 and L1 fields to the ALU's Y input. When S=1 and L2=7, it specifies the type of shift to perform. When S=2, it is part of the branch address. When S=4 or 5, it specifies conditional jump codes. When S=6 or 7, it specifies a bit position in the T register to be tested.

- i. L2 Field When Y=3, it is part of the literal that is gated to the ALU Y input. When S=1, it is a special command. For S=2 through 7, L2 represents the most significant bits of the control storage branch or jump addresses. For Z=1 and L1=0,4,8 or 12; L2 represents the four most significant bits of the data lookup table address.

- j. Ll Field When Y=3, it is part of the literal that is gated to the ALU Y input. For S=2 through 7, it represents the 4 least significant bits of branch or jump addresses. When Z=1, the Ll field specifies bits to be used to generate a special literal source or which field of the E register is to be used as the least significant four bits of the lookup table address.

- k. Z Field This bit is used to enable special

Processors

interpretation of L2 and Ll fields to select a field from the E register or other sources for generation of special literals on the next micro instruction (by modifying the Ll and L2 or M fields).

1. W Field - Selects register file specified in X field and/or one of the A, T, or E registers or the loop counter to receive the ALU output. For W=5,6, or 7 both the register file and A, T, or E register are selected to receive ALU output, respectively. For W=0 or 4 the ALU1 signal is copied into the ONEs flip-flop. For W=3 the four least significant bits are copied into the loop counter.

#### ROM Data Lookup Table

The ROM data lookup table is an 8-bit, 256-word read-only-memory consisting of two 256 by 4-bit LSI microcircuits. The lookup table is enabled and addressed by the current microcontrol word in the M register and a 4-bit field from the E register.

When enabled, its output is ANDed with the literal fields of the next ROM control word. Other status conditions, when enabled by the current ROM control word, also may be ANDed into the literal fields of the next ROM control word.

The microcode selection logic forms the AND of the ROM control storage and the other enabled functions and places the control word into the M register. Through a look-ahead feature inherent in the processor, the next control word is read while the current word is executed.

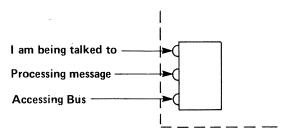

## 3.6.3 Master-Slave Modes

The processors operate in either a master or slave mode. A processor operates in the master mode when addressing a system module; and in the slave mode when addressed by a system module. The master mode is the most common mode of operation when the processor executes programmed instructions and self interrupts. If operating as a CPU, the processor allows the requesting device number to be received while in the slave mode, and thereby controls system interrupts on priority levels 4 through 1. Since the register file cannot be accessed by an external module (such as a control panel), the processor usually halts when addressed in the slave mode. However, the run/halt control register is accessible in either the halt or run modes and, as a result, a processor can be halted while running.

#### 3.6.4 Programming Considerations

Several programming considerations are discussed in the following paragraphs: register addressing, ACTIVE-IDLE states, HALT-RUN control, interrupt control and multiple processors.

### Register Addressing

Thirteen registers, addressable from the control panel, provide register display when the processor is in the HALT mode. Table 1 contains a list of the addressable registers and identifies their function in the processor.

#### Active-Idle State

Bit 11 of the status register specifies, under control of the firmware, the operation mode that the processor assumes after executing an instruction or servicing an interrupt request.

If bit 11 is a Zero, the processor assumes the IDLE state. If bit 11 is a One, the processor assumes the ACTIVE state.

The IDLE state is a simple loop operation with the Run flip-flop asserted. The processor interrogates the Halt flip-flop, and if the processor is a CPU, it looks for any enabled interrupt service requests.

In ACTIVE state, the RUN flip-flop is asserted and the processor executes the next instruction in a program sequence or services an enabled interrupt request.

|    | Register                                     |    | Register Address                                                               | <br>1 | Register Name !           |  |  |  |  |  |  |

|----|----------------------------------------------|----|--------------------------------------------------------------------------------|-------|---------------------------|--|--|--|--|--|--|

| !  | Switch                                       |    | (Hex)                                                                          | !     |                           |  |  |  |  |  |  |

| 1  | 2 186 646 668 689 689 649 640 640 640 640 64 |    | 17 MPF Tana ilan ilan paté dan dasi dati dati dati dati dati dan awa dasi dasi | !     |                           |  |  |  |  |  |  |

| 1  | 0                                            | 1  | FFx0                                                                           | !     | General Register 0 (PC) ! |  |  |  |  |  |  |

| 1  | 1                                            | 1  | FFx2                                                                           | !     | General Register 1 !      |  |  |  |  |  |  |

| 1  | 2                                            | 1  | FFx4                                                                           | !     | General Register 2 !      |  |  |  |  |  |  |

| 1  | 3                                            | 1  | FFx6                                                                           | !     | General Register 3 !      |  |  |  |  |  |  |

| 1  | 4                                            | 1  | FFx8                                                                           | !     | General Register 4 !      |  |  |  |  |  |  |

| !  | 5                                            | 1  | FFxA                                                                           | !     | General Register 5 !      |  |  |  |  |  |  |

| 1  | 6                                            | 1  | FFxC                                                                           | 1     | General Register 6 !      |  |  |  |  |  |  |

| 1  | 7                                            | 1  | FFxE                                                                           | !     | General Register 7 !      |  |  |  |  |  |  |

| 1  | 8                                            | 1  | FFyO                                                                           | !     | Status Register !         |  |  |  |  |  |  |

| 1  | 9                                            | 1  | FFy2                                                                           | 1     | Instruction Register !    |  |  |  |  |  |  |

| 1  | 10                                           | 1  | FFy4                                                                           | 1     | Firmware A )address of !  |  |  |  |  |  |  |

| 1  |                                              | 1  | -                                                                              | !     | last instruction) !       |  |  |  |  |  |  |

| 1  | 11                                           | 1  | FFy6                                                                           | !     | Firmware B !              |  |  |  |  |  |  |

| 1  | 12                                           | 1  | FFy8                                                                           | !     | Not implemented !         |  |  |  |  |  |  |

| 1  | 13                                           | 1  | FFyA                                                                           |       | Not implemented !         |  |  |  |  |  |  |

| 1  | 14                                           | 1  | FFyC                                                                           | !     | Not implemented !         |  |  |  |  |  |  |

| 1  | 15                                           | 1  | FFyE                                                                           | 1     | Halt/Run Control !        |  |  |  |  |  |  |

| 1  |                                              | 1  | -                                                                              | !     | 1                         |  |  |  |  |  |  |

|    | x = 0, 2,                                    | 4, | , 6 for processor                                                              | s     | 0, 1, 2, 3 respectively.  |  |  |  |  |  |  |

|    |                                              |    |                                                                                |       | 0, 1, 2, 3 respectively.  |  |  |  |  |  |  |

| Ha | Halt-Run Control                             |    |                                                                                |       |                           |  |  |  |  |  |  |

| Ta | b 1 | е | 1 | • | R | е | g | i | s | t | е | r | A | d | d | r | е | S | s | e | S |

|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|    |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

The control register consists of two flip-flops that control HALT and RUN modes of operation. The Halt flip-flop is asserted or negated any time it is addressed. The Run flip-flop is asserted any time the processor is taken out of the HALT mode.

The flip-flops are addressable from a control panel. The control register (Run/Halt flip-flops) read out is 0000 if the processor is running and FFFF if the processor is halted.

-

#### NOTE

Since the CPU is incapable of servicing interrupts in the HAL1 mode, the programmer should ensure that a secondary processor does not place the CPU in this mode.

The control register functions in four possible states. Table 2 identifies these states and the processor mode for the three meaningful states. Table 2 is a list of four possible states for the control register, identifying the processor mode for the three meaningful states. Bit Zero of the control register controls the Halt flip-flop and bit one, the Run flipflop.

The Halt flip-flop is interrogated at the end of each instruction execution and, if asserted, the processor is halted. If the Halt flip-flop is negated, the processor is in the RUN mode or is executing a WAIT instruction. If both Halt and Run flip-flops are asserted, the processor executes one instruction at a time. This single instruction execution can be initiated by pushing STEP on the control panel.

| !<br>!<br>! | 0      | -      | 0      | 1      | Not defined           | 1   |                                              | 1      |

|-------------|--------|--------|--------|--------|-----------------------|-----|----------------------------------------------|--------|

| 1           | -      | -      | U      | -      |                       |     |                                              |        |

|             | •      | •      | 1      | -      | HALT                  | -   | Cannot be serviced                           | !      |

| 1           | 1<br>1 | !<br>1 | 0<br>1 |        | RUN* or IDLE*<br>STEP |     | Allowed (if enabled)<br>Allowed (if enabled) | 1<br>1 |

| 1           |        | 1      | _      | 1      |                       | 1   |                                              | 1      |

| !           |        |        |        |        |                       |     | status register is a one                     | !      |

| !           | RU     | N      | (IDLH  | 3)<br> | if bit ll of a        | st: | atus register is a ZERO                      | !<br>  |

# Table 2. HALT-RUN Control Codes

Interrupt Control

The CPU accepts a system interrupt only if a bit in the status register corresponding to the interrupt priority level is enabled, and the control panel's master interrupt inhibit signal (INH) is absent from the Infibus.

Processors

Pluribus Board Configuration Manual

Bits 15 through 12, of the processor status register, control system interrupts 4 through 1, respectively. Zero enables and One disables the interrupt. When the CPU executes an interrupt, all system interrupt priority levels 4 through 1 are disabled.

The program is written to ensure that interrupts permitted during an interrupt subroutine are enabled by resetting corresponding status bits to Zero at execution time.

Executive memory is reserved for interrupt control. The programmer reserves addresses 0000 to 005F for system and self interrupt executive space, and provides the proper vector addresses for interrupt service routines.

Memory executive space and the memory addresses assigned to each interrupt level appear in Table 3.

Executive space for two self interrupts(level 5 and 6) are available for each processor, in additioin to the space for four system interrupts. (See below). Pluribus Board Configuration Manual

Table 3. System and Self Interrupt Executive Space

.

|   | _ |                   |     |               |   | -            |       |             |       |

|---|---|-------------------|-----|---------------|---|--------------|-------|-------------|-------|

|   | 1 | ADDRESS THAT      | 1   | STATUS        | l | ABORTED      | 1     | SERVICE     | 1     |

| 6 | 1 | CAUSED ABORT      |     |               | ļ | INSTRUCTION  | Ī     | ROUTINE     | i     |

|   | 1 |                   | 1   |               | 1 | ADDRESS      | 1     | VECTOR      | 1     |

|   | 1 | ADDR00 0028       | 1   | ADDROO 002A   | 1 | ADDR00 002C  | 1     | ADDROO 002E | 1     |

|   | 1 | ADDR01 0038       | 1   | ADDR01 003A   | 1 | ADDR01 003C  | 1     | ADDR01 003E | 1     |

|   | 1 | ADDR10 0048       | 1   | ADDR10 004A   | 1 | ADDR10 004C  | !     | ADDR10 004E | 1     |

|   | 1 | ADDR11 0058       | 1   | ADDR11 005A   | 1 | ADDR11 005C  | 1     | ADDR11 005E | 1     |

|   |   |                   |     |               |   |              |       |             |       |

|   | 1 | UNIMPLEMENTED     | !   | STATUS        | 1 | UNIMPLEMENTE | D 1   | SERVICE     | 1     |

| 5 | 1 | INSTRUCTION       | !   |               | 1 | INSTRUCTION  | !     | ROUTINE     | !     |

|   | 1 |                   | !   |               | 1 | ADDRESS      | 1     | VECTOR      | !     |

|   | 1 | ADDR00 0020       | !   | ADDR00 0022   | ! | ADDR00 0024  | 1     | ADDR00 0026 | !     |

|   | 1 | ADDR01 0030       | l   | ADDR01 0032   | 1 | ADDR01 0034  | !     | ADDR01 0036 | 1     |

|   | 1 | ADDR10 0040       | !   | ADDR10 0042   | 1 | ADDR10 0044  | 1     | ADDR10 0046 | 1     |

|   | 1 | ADDR11 0050       | !   | ADDR11 0052   | 1 | ADDR11 0054  | 1     | ADDR11 0056 | !     |

|   | - |                   | - • |               |   |              |       |             |       |

| , | 1 | MODULE            | 1   | STATUS        | 1 | PROGRAM      | 1     | SERVICE     | 1     |

| 4 | 1 | ADDRESS           | 1   |               |   | COUNTER      | 1     | ROUTINE     | 1     |

|   | 1 | 0010              | 1   | 0.01.4        | 1 | 0010         | 1     | VECTOR      | 1     |

|   | 1 | 0018              | !   | 001A          | 1 | 001C         | !<br> | 001E        | !<br> |

|   | 1 | MODULE            | 1   | STATUS        | 1 | PROGRAM      | 1     | SERVICE     | 1     |

| 3 | 1 | ADDRESS           | 1   |               | 1 | COUNTER      | 1     | ROUTINE     | 1     |

| - | 1 |                   | 1   |               | 1 | 1            | 1     | VECTOR      | 1     |

|   | 1 | 0010              | 1   | 0012          | 1 | 0014         | 1     | 0016        | 1     |

|   | - |                   |     |               |   |              |       |             |       |

|   | 1 | MODULE            | !   | STATUS        | 1 | PROGRAM      | 1     | SERVICE     | !     |

| 2 | 1 | ADDRESS           | !   |               | 1 | COUNTER      | 1     | ROUTINE     | !     |

|   | 1 |                   | !   |               | 1 | 1            | 1     | VECTOR      | 1     |

|   | 1 | 0008              | !   | A000          | 1 | 0000         | 1     | 000E        | !     |

|   | - | <br>Морит е       |     | C TT & TT T C |   |              |       |             |       |

| 1 | 1 | MODULE<br>ADDRESS | 1   | STATUS        |   | PROGRAM      | 1     | SERVICE     | 1     |

| T | 1 | ADDKE22           | 1   |               | 1 | COUNTER      | 1     | ROUTINE     | 1     |

|   | 1 | 0000              | 1   | 0002          | 1 | 0004         | 1     | VECTOR      | 1     |

|   | - |                   | •   | 0002          | • | 0004         | 1     | 0006        | 1     |

|   |   |                   |     |               |   |              |       |             | -     |

# Typical Interrupt Operation

When the CPU acknowledges an enabled interrupt request, the firmware accepts the module address and interrupt number, and stores the requesting module address, processor current status, and program counter contents (next instruction address) into system interrupt executive space.

Processors

REV B

The firmware then loads the service routine vector address into the program counter (RO), and vectors to the interrupt subroutine address with all interrupts disabled.

Once the interrupt subroutine has been serviced, and to return to a a program executed prior to the interrupt, activate a Return-From-Interrupt instruction (RETN). This instruction replaces the status register with the previous processor status and loads the program counter (RO) with the address of the interrupted program's next sequential instruction.

If the CPU acknowledges a second interrupt before RETN is executed, the CPU loads the new interrupt module address, status and program counter information in the executive space for the interrupt, and vectors to a new subroutine. Consequently, another interrupt should not be enabled on the same or previous level before either returning or saving the interrupt status in a return stock. Self Interrupts

-

Each processor controls two self interrupts: unimplemented instruction and address abort, levels 5 and 6, respectively.

Unimplemented instruction (level 5) signals the system, and may be used for trapping to arithmetic or logic subroutines that simulate the operation of the unimplemented instruction. Address abort or trap (level 6) avoids Infibus tie-up and notifies the system of an erroneous address or a unresponsive slave module.

Since any one of four possible processors in a multiple processor system can execute self interrupts, four different sets of memory address locations are reserved within the system interrupt executive space for self interrupts (Reter to figure 3).

#### 3.6.5 Multiple Processors

When a processing task is too large for the CPU, the work load is divided among additional processors. REV B

Secondary processors may be added to do different tasks, subtasks to those required by the CPU, or a parallel task (the same task with different input data). The second, third and fourth processors are designated as 01, 02, 03, respectively. The CPU, electrically connected to the BCU, is automatically designated as 00.

Regardless of the secondary processors' functions, the CPU schedules the work load, and passes data to memory or to the other processors if input is from an interrupt-driven device.

If the CPU does not schedule tasks, the processor communications routine must be designed with great care so that the processors do not lock up. The status register of each processor establishes a communication link between processors, and thereby determines task status and passes information.

Instructions from within the processor control the status register's three flag bits (F1, F2 and F3). These flag bits may also be used as a branch test, and may be interrogated by halting the processor and reading its status register.

When more complex information is passed between processors, a number of core memory locations are dedicated to each processor. These information blocks are then placed in these locations to await processor interrogation. Either incoming or outgoing information blocks may be used.

All processors have unlimited access to memory. As a result, partitioning memory and using multiple processors on an Infibus with common memory requires caution.

Software is designed to allow multiple processors to access the same programs, thus greatly reducing core memory requirements. 3.6.6 Configuration

.

The following pages explain the necessary strapping to properly configure the CPA and CPC boards.

.

#### 4 MEMORIES

#### 4.1 Functional Description

Memory modules only operate in the slave mode. The address and mode control signals sent by a master module initiates memory operations.

The memories perform one of three operations: read-restore, clear-write, or read-modify-write. The mode control signals from the master module initiating the operation specifies the particular operation. A full word consisting of 16 bits, or a byte consisting of either 8 bits or 9 bits, for each respective model, can be transferred during any of these operations.

During read byte operations, the memory module transmits the selected byte (left or right) in bit positions 7 through 0 on the Infibus data lines. The remaining bits are transmitted as zeros.

During write byte operations, data bits 7 through 0 are transferred into either the lett or right byte position of the addressed memory location, and the other byte position of the word remains unchanged. Read-Restore Operation

In the read-restore operation, a full memory cycle is initiated when the memory module recognizes the address of an accessed location. Data at the accessed location is read out destructively during the read portion of the cycle, and transferred to the data register. The data is written back into the same location during the restore portion of the cycle. Clear-Write Operation

In the clear-write operation, a full memory cycle is initiated. Data at the addressed location is read out destructively and discarded during the clear portion of the cycle. During the write portion of the cycle, the new data in the data register is transferred to the accessed location.

Read-Modify-Write Operation

In the read-modify-write operation, a split memory cycle occurs. The read portion of the cycle is the same as the first half of a read-restore operation. The word or byte from the accessed location is sent to the master module. The memory cycle is temporarily suspended to allow the master module sufficient time to modify the data.

When modified, the data is returned to memory. The master module initiates the write half of the cycle, and the modified word is restored to the accessed location. The cycle time depends on the time the master module requires to modify the word and to start the write portion of the cycle.

## 4.2 Multiple Memory Modules

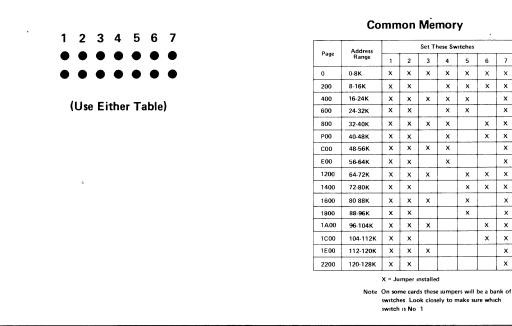

In systems containing two or more memory modules, memory addressing can be modified to enhance operation for specific applications. Jumpers and/or switch settings on each memory module determine module address and addressing mode: overlap, interleave, or interlock.

Overlap Mode

In the overlap mode, two memory modules are operated simultaneously within the same system, where the next cycle is started in the second memory module before the current cycle is completed in the first, or vice versa. Therefore, the time required on the Infibus for communication with the master module is minimized. This capability is inherent in computer systems that contain two or more memory modules.

Each memory module contains its own data and address registers so that each may operate asynchronously and independently of other system modules. The overlap mode can be used either by a single master module alternately reading data from, or writing data into, two memory modules; or by two or more master modules, where each operates with a separate memory module.

For example, a processor can be executing instructions from one memory module while an I/O controller with a block transfer adapter is transmitting data received from a peripheral device to a second memory module.

42

Interleave Mode

The interleave mode is an extension of th overlap mode. To enhance the overlap mode in configurations having one master module operating with two memory modules, the memory can be modified by jumper wires to operate in the interleave mode.

Interleaving is accomplished by interchanging address bit positions 1 and 13 for 4K memories, and 1 and 14 for 8K memories throughout the entire storage address decode logic. One memory module is made to contain even-numbered word addresses, the other bank odd-numbered word addresses. With this arrangement, a single proccessor receives or transmits alternately data addressed consecutively from, or to, the two memory modules.

Interlock Mode

The interlock mode inhibits the overlap mode. Threfore, a new memory cycle cannot begin in any memory module until the current cycle is completed.

To implement the interlock mode, the memory modules are provided with a special jumper to disable the inherent overlap mode. Modification to this mode is used to minimize power consumption when system performance can be reduced.

## 4.3 Programming Considerations

Memory operations can be initiated only when the applied module address code matches the assigned, hardwired memory address code. Thereafter, memory operatins are controlled by cycle-initiation, byte- or word-mode, and other control signals that are stored in the control storage register.

Memory Addressing

All memory locations in a Pluribus Computer System are assigned a 16-bit address. Coding of the address is shown in figure 1 and is described as follows:

1. Address bits 13, 14 and 15 specify the 4K module

Memories

address; bits 14 and 15 specify the 8K module address.

- 2. Address bits 1 through 12 for 4K modules and bits 1 through 13 for 8K modules, specify the storage location within the selected memory module.

- 3. Address bit 0 specifies which of the two bytes in the selected storage location is to be accessed during the byte mode operations: ZERO specifies left byte; ONE specifies right byte.

- 4. Address bits 16 and 17 specify the KEY bits, which correspond to Infibus signals KEYO-N and KEYI-N, respectively. If this option is enabled, the KEY bits can be used by the program as a code to enable and disable access to portions of memory.

# Memory Addressing 4K MEMORY

| !KEY!KEY! | ! Module  | !     | Word    | ! B | YTE! |

|-----------|-----------|-------|---------|-----|------|

| ! 1 ! 0 ! | ! Address | 1     | Address | 1   | 1    |

|           |           |       |         |     |      |

| 17 16     | 15 1      | 3 1 2 |         | 1   | 0    |

**8K MEMORY**

| !KEY!KE | Y ! | ! Module | 1     | Word    | ! B Y | TE! |

|---------|-----|----------|-------|---------|-------|-----|

| ! 1 ! 0 | !   | ! Addres | s !   | Address | !     | 1   |

|         |     |          |       |         |       |     |

| 17      | 16  | 15       | 14 13 |         | 1     | 0   |

#### System Addressing

One memory module in any Pluribus system must be addressed ZERO so that the auto-load, interrupt, power fail and restart functions are operative. All other memory modules are assigned addresses consecutively, ONE, TWO, THREE and so forth.