# Addendum to

## Domain Personal Workstations and Servers Hardware Architecture Handbook

Order No. 019411-A00

© Hewlett-Packard Co. 1991

UNIX is a registered trademark of UNIX System Laboratories Inc.

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett–Packard Company.

RESTRICTED RIGHTS LEGEND. Use, duplication, or disclosure by government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software Clause at DFARS 252.227.7013. Hewlett-Packard Co., 3000 Hanover St., Palo Alto, CA 94304

## Preface

This addendum contains corrections and additions to information in the Domain Personal Workstations and Servers Hardware Architecture Handbook (Order Number 007861-A01) manual.

Please use the information in this addendum in place of existing information in the Domain Personal Workstations and Servers Hardware Architecture Handbook manual as indicated.

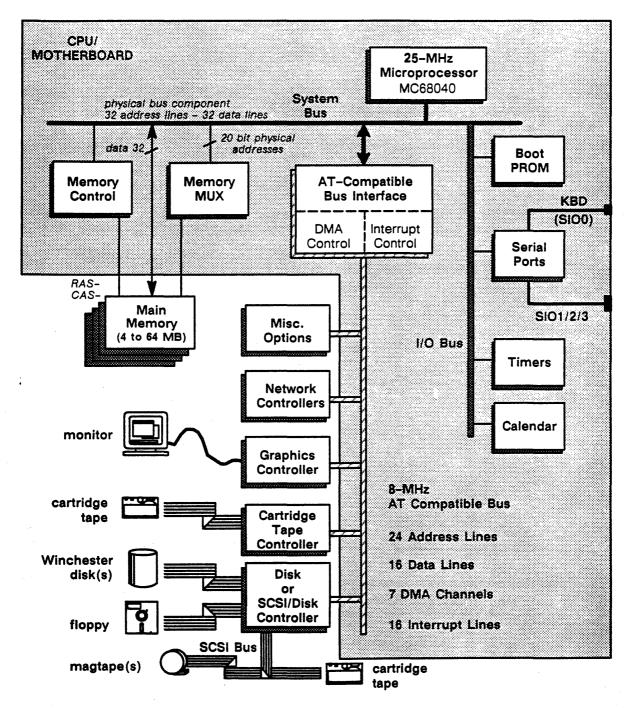

### Replace the figure on page 1–6 with the following figure.

Figure 1-5. DS5500 System

## Replace the Table on page 2–7 with the following table.

| Physical          |                                         | Physical                                                 |                                                                                     |  |  |

|-------------------|-----------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| Address           | Function                                | Address                                                  | Function                                                                            |  |  |

| 000000-<br>00FFFF | BOOT PROM                               | 080000-                                                  | AT BUS-COMPATIBLE<br>MEMORY SPACE<br>OR                                             |  |  |

| 010000-<br>0100FF | CPU STATUS REGISTER                     | 09FFFF                                                   | ÉTHERCONTROLLER-AT<br>MEMORY SPACE<br>(80000 - 84000; ALTERNATE =<br>81FFF - 85FFF) |  |  |

| 010100-<br>0101FF | CPU CONTROL REGISTER                    | 0A0000-<br>OBFFFF GRAPHICS MEMORY SPACE                  |                                                                                     |  |  |

| 010200-<br>0102FF | CACHE STATUS REGISTER                   |                                                          | ALTERNATE MONO GRAPHICS<br>MEMORY SPACE                                             |  |  |

| 010400-<br>0104FF | SIO CONTROLLER No. 1                    | 0C0000-<br>0DFFFF                                        | OR<br>SINGLE-BOARD RING<br>CONTROLLER MEMORY SPACE<br>(D0000 - DFFF)                |  |  |

| 010500-<br>0105FF | SIO CONTROLLER No. 2                    | 0E0000-                                                  | ALTERNATE COLOR GRAPHICS<br>MEMORY SPACE<br>OR ALTERNATE<br>SINCLE POARD RING       |  |  |

| 010800-<br>0108FF | INTERVAL TIMER                          | 0FFFFF                                                   | SINGLE-BOARD RING<br>CONTROLLER MEMORY SPACE<br>(E0000 - EFFFF)                     |  |  |

| 010900-<br>0109FF | CALENDAR                                | 100000-<br>FFFFFF                                        | AT COMPATIBLE BUS<br>MEMORY SPACE                                                   |  |  |

| 010C00-<br>010CFF | DMA CONTROLLER No. 1                    | FA0000-<br>FDFFFF                                        | MONO GRAPHICS<br>MEMORY SPACE                                                       |  |  |

| 010D00-<br>010DFF | DMA CONTROLLER No. 2                    | FE0000-<br>FFFFFF                                        | AT COMPATIBLE BUS<br>MEMORY SPACE                                                   |  |  |

| 011000-<br>0110FF | INTERRUPT CONTROLLER No. 1              | 1000000-<br>1FFFFFF                                      | MAIN MEMORY<br>(16 MB)                                                              |  |  |

| 011100-<br>0111FF | INTERRUPT CONTROLLER No. 2              | 2000000-<br>2FFFFFF                                      | MAIN MEMORY<br>(16 MB)                                                              |  |  |

| 011200-<br>0112FF | NETWORK ID PROM                         | 300000-<br>3FFFFFF                                       | MAIN MEMORY<br>(16MB)                                                               |  |  |

| 011300-<br>0113FF | LATCH-PAGE-ON-PARITY-<br>ERROR REGISTER | 4000000-<br>4FFFFFF                                      | MAIN MEMORY<br>(16MB)                                                               |  |  |

| 011400<br>0114FF  | MEMORY PRESENT REGISTER                 | 5000000-<br>6FFFFFF                                      | RESERVED                                                                            |  |  |

| 011600-<br>0116FF | MASTER REQUEST REGISTER                 | 700000-<br>700FFFF                                       | I/O PROTECTION MAP                                                                  |  |  |

| 016400-<br>0164FF | SELECTIVE CLEAR<br>LOCATIONS 1          | 7010000-<br>F7FFFFFF                                     | RESERVED                                                                            |  |  |

| 017000-<br>017FFF | ADDRESS TRANSLATION<br>MAP              | F8000000-<br>FDFFFFFF                                    | DESKTOP VISUALIZATION SPACE                                                         |  |  |

| 040000-<br>05FFFF | AT BUS-COMPATIBLE<br>I/O SPACE          | Physical A                                               |                                                                                     |  |  |

| 060000-<br>07FFFF | NOT USED                                | 00016400<br>00016404<br>00016406<br>00016408<br>0001640A | Clear Parity Error Flag<br>Clear Bus Error Status                                   |  |  |

Table 2-5. DS5500 256-MB Physical Address Space Allocation

### On pages 4–10 and 4–11, replace section 4.2.1.4 with the following information.

#### 4.2.1.4 DS3500, DS4000, DS4500, and DS5500 Address Translation Map

The Address Translation Map exists in the DS3500, DS4000, DS4500, and DS5500. The map has the following two functions:

- It allows the DS3500, DS4000, DS4500, or DS5500 to perform DMA to or from noncontiguous physical memory (while it appears that the DMA transfer is taking place from contiguous physical memory)

- It provides a 512-KB window through which external AT compatible bus masters can access CPU main memory.

The Address Translation Map holds one entry for every main memory page that is accessed via a DMA controller or other external AT compatible bus master. The operating system allocates an Address Translation Map entry (or multiple entries) each time DMA is required. The map provides the interface between the DMA controller 64-KB (for 8-bit transfers) or 128-KB (for 16-bit transfers) address spaces and the DS3500 or DS4000 physical address space (64 MB).

When an external bus master assumes control of the AT compatible bus, the physical address space between addresses 000000 and 07FFFF is used by the Address Translation Map to access the 64- to 128-KB bus master's address space.

During 8-bit DMA transfers in the DS3500, DS4000, DS4500, and DS5500, address bits <15:10> provide an index into the Address Translation Map; they select one of the 64 entries contained within it. The 16-bit Address Translation Map entry (a physical page number, bits <25:10>) is concatenated with the page offset (DMA address bits <9:0>), which yields a 26-bit physical address.

During 16-bit DMA transfers in the DS3500, DS4000, DS4500, and DS5500, address bits <16:10> provide an index into the Address Translation Map; they select one of the 128 entries contained within it. The 16-bit Address Translation Map entry (a physical page number, bits <25:10>) is concatenated with the page offset (DMA address bits <9:1>), which yields a 26-bit physical address.

For more information about DMA on the AT compatible bus, refer to Subsection 4.3.3.

### On page 4–19, add the following line to Table 4–6.

PC ON/OFF

Physical Cache (DS4500 Only)

# On page 4–24, Replace the information in section 4.2.1.14 with the following information.

#### 4.2.1.14 DS5500 Cache Status Register

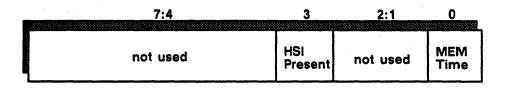

This 8-bit, read-only register exists in the DS5500. This register holds miscellaneous status information. Figure 4-9 and Figure 4-10 show the register.

#### HSI Present <3>

This bit is cleared (0) to indicate that a graphics device is in the HSI connector.

MEM Time <0> This bit indicates an access to non-existant memory.

Figure 4–9. DS5500 Cache Status Register

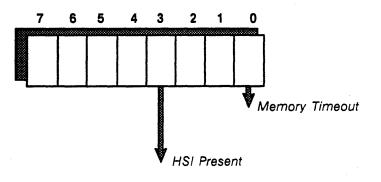

HSI Present <3> This bit is cleared (0) to indicate that a graphics device is in the HSI connector. MEM Time <0> This bit indicates an access to non-existant memory.

Figure 4-10. DS5500 Cache Status Register

# On page 4–26, after section 4.2.1.17, add the following section .

#### 4.2.1.18 DS5500 Memory Present Register

This 8-bit, read-only register exists in the DS5500. This register holds memory board existence information. The following figure shows the register.

|                | 7              | 6              | 5              | 4              | 3              | 2              | 1              | 0              |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| No.            |                |                |                |                |                |                |                |                |

| AND ADDRESS OF | MEM<br>Present |

**MEM Present <7-0>** These bits are cleared (0) when memory boards are present.

In this register, each consecutive pair of bits identifies the condition of a memory board slot. Bits 0 and 1 are slot 0, bits 2 and 3 are slot 1, bits 4 and 5 are slot 2, and bits 6 and 7 are slot 3.

The locations of memory board slots on the CPU Motherboard is as follows:

- Slot 0 is location P25 on the CPU Motherboard (Right-most slot)

- Slot 1 is location P24 on the CPU Motherboard

- Slot 2 is location P23 on the CPU Motherboard

- Slot 3 is location P22 on the CPU Motherboard (Left-most slot)

| Memory Bd.<br>Size (MB)                                                                                                                                                                                           |                                                                                                          | Memory Bd.<br>Size (MB)                              |                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Slot No.<br>0 1 2 3                                                                                                                                                                                               | Register value<br>(Hexadecimal)                                                                          | Slot No.<br>0 1 2 3                                  | Register value<br>(Hexadecimal)                                                                    |  |

| (No Board)<br>4<br>4 4<br>4 4 4 -<br>4 4 4 4<br>8<br>8 4 4 -<br>8 8 4 -<br>8 8 4 -<br>8 8 4 4<br>8 8 8 -<br>8 8 8 4<br>8 8 8 8<br>16<br>16 4 -<br>16 4 4 - | FF<br>FE<br>FA<br>EA<br>AA<br>FC<br>F8<br>E8<br>A8<br>F0<br>E0<br>A0<br>C0<br>80<br>00<br>FD<br>F9<br>E9 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | A9<br>F1<br>E1<br>A1<br>C1<br>81<br>01<br>F5<br>E5<br>A5<br>C5<br>85<br>05<br>D5<br>95<br>15<br>55 |  |

The following table shows the hexadecimal value of the Memory Present register for all possible memory configurations.

.