# Data Conversion PRODUCTS CATALOG

# Data Conversion PRODUCTS CATALOG

# TABLE OF CONTENTS

| 1. General Information<br>Introduction<br>Placing An Order<br>Data Sheets/Literature<br>Prices and Terms<br>Quotations<br>Returns and Warranty Service<br>Applications/Technical Assistance<br>Sales Offices                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2. Amplifiers<br>Selection Guide<br>Glossary<br>AH201-1 Single Channel Audio Distortion Suppressor<br>AH201-2 Dual Channel Audio Distortion Suppressor<br>MP221 Low Noise Chopper Stabilized Amplifier.<br>MP227A Precision Isolation Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-3<br>2-5<br>2-5<br>2-11                     |

| <ul> <li>Sample-and-Hold Amplifiers         <ul> <li>Selection GuideGlossary</li> <li>MP260 3 μs, 0.002% Linearity S/H (Optimized for Simultaneity)</li> <li>MP261 5 μs, 0.002% Linearity, Low Droop S/H</li> <li>MP270 1 μs, 0.005% Linearity S/H</li> <li>MP271 1 μs, 0.003% Linearity S/H</li> <li>MP272 350 ns, 0.01% Linearity S/H</li> <li>MP282A Dual Simultaneous S/H with 1-bit Gain Ranging</li> </ul> </li> </ul>                                                                                                                                                                                                                                             | 3-3<br>3-5<br>3-5<br>3-11<br>3-15<br>3-21     |

| 4. Analog-to-Digital Converters<br>Selection Guide<br>Glossary<br>MP2316 16-bit, Floating Input, Programmable Gain, Analog Processor<br>MP2321 3 1/2 Digit BCD Output Integrating A/D<br>MP2322 12-bit Binary Output Integrating A/D<br>MP2712D 12-bit, 5 $\mu$ s A/D<br>MP2713C 13-bit, 10 $\mu$ s A/D<br>MP2714C 14-bit, 10 $\mu$ s A/D<br>MP2734 14-bit, 6.8 $\mu$ s A/D<br>MP2735-1 Low Distortion, 15-bit Audio Digitizer (S/H and A/D)<br>MP2735-2 Low Distortion, 15-bit, 5 $\mu$ s A/D<br>MP8014 14-bit, 10 $\mu$ s Precision A/D<br>MP8015 15-bit, 15 $\mu$ s Precision A/D<br>MP8016 16-bit, 32 $\mu$ s Precision A/D<br>MP8037 17-bit, 250 Hz Integrating A/D |                                               |

| <ul> <li>5. Data Acquisition Subsystems         Selection GuideADAM-724 14-bit, 6.8 μs A/D with Integral S/H and Differential Amplifier         ADAM-812 Dual Simultaneous S/H and 12-bit 50 kHz A/DADAM-822 Dual Simultaneous S/H and 12-bit 26 kHz A/DADAM-824A Low Power, 14-bit, 50 kHz A/D with S/HADAM-825A Low Power, 15-bit, 50 kHz A/D with S/H     </li> </ul>                                                                                                                                                                                                                                                                                                 | 5-3<br>5-13<br>5-17<br>5-23                   |

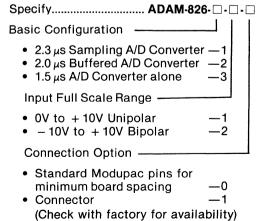

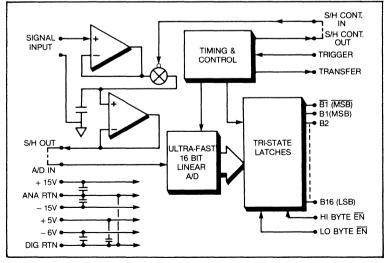

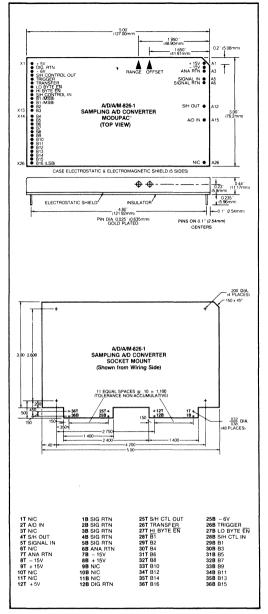

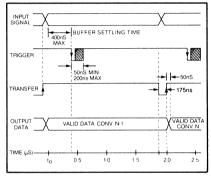

| ADAM-826 Family of 16-bit, Ultra Speed A/D Converters                                                      | 5-27 |                                 |

|------------------------------------------------------------------------------------------------------------|------|---------------------------------|

| ADAM-826-1 16-bit, 1.5 µs A/D with integral 800 ns S/H                                                     |      |                                 |

| ADAM-826-2 16-bit, 1.5 µs A/D with Integral 400 ns Buffer Amplifier                                        | 5-37 | -jē                             |

| ADAM-826-3 16-bit, 1.5 µs A/D (Unbuffered)                                                                 |      | ATA                             |

| ADAM-834A Low Power, Extended Temperature 14-bit A/D and S/H                                               |      | N. N.                           |

| ADAM-835A Low Power, Extended Temperature 15-bit A/D and S/H                                               |      | GENERAL<br>NFORMATION           |

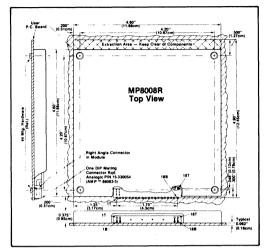

| MP8008R 8-bit, 300 kHz, Ultra-high Differential Linearity, Sampling A/D Conve                              |      | ≤                               |

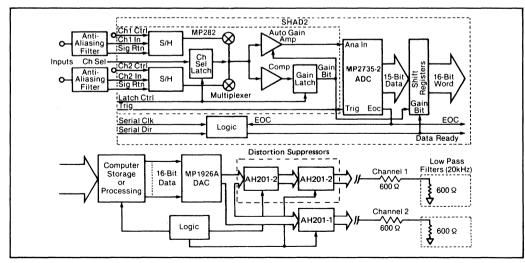

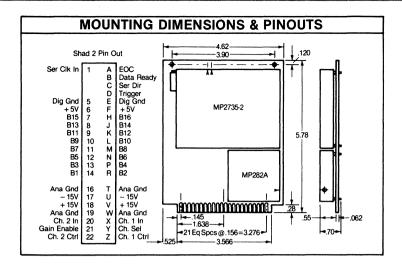

| SHAD2A Two-Channel, 16-bit Audio Digitizing Subsystem                                                      | 5-53 |                                 |

|                                                                                                            |      |                                 |

| 6. Digital-to-Analog Converters                                                                            |      |                                 |

| Selection Guide                                                                                            | 6-2  | 10                              |

| Glossary                                                                                                   | 6-3  | Ë                               |

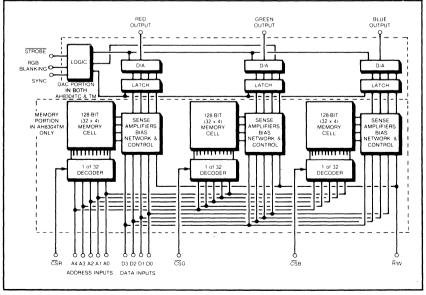

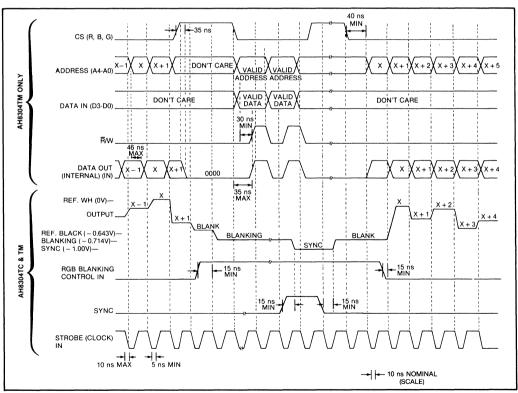

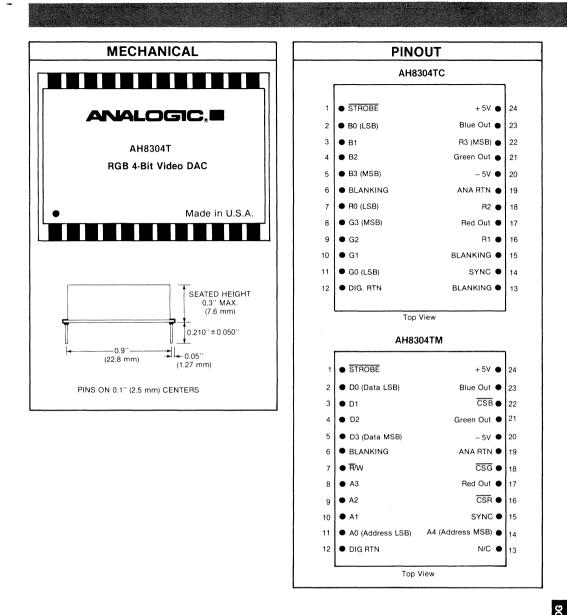

| AH8304TC Triple 4-bit 100 MHz TTL-compatible Video D/A                                                     | 6-7  | E                               |

| AH8304TM Triple 4-bit 20 MHz TTL-compatible Video D/A with                                                 |      | AMPLIFIERS                      |

| 32 word color LUT memory                                                                                   | 6-7  | AN                              |

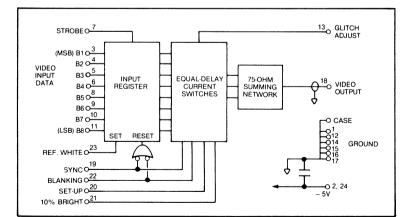

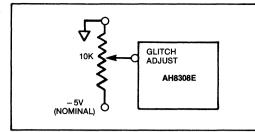

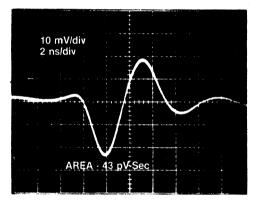

| AH8308E Single 8-bit, 150 MHz, ECL-compatible Video D/A                                                    | 6-13 |                                 |

| AH8308T Single 8-bit, 100 MHz, TTL-compatible Video D/A                                                    | 6-21 |                                 |

| AH8308TC Triple 8-bit, 100 MHz TTL-compatible Video D/A                                                    |      |                                 |

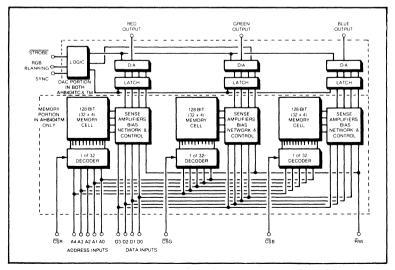

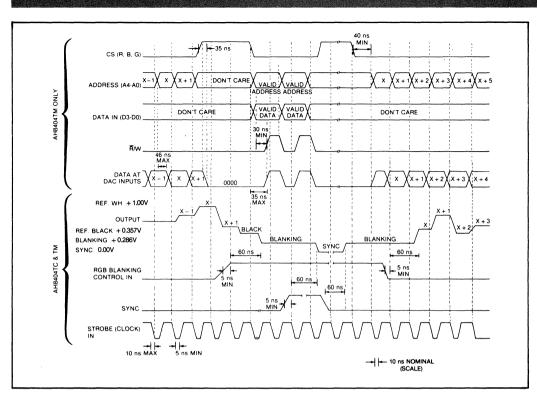

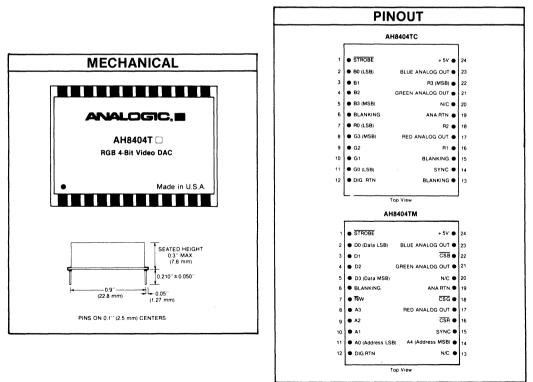

| AH8404TC Triple 4-bit, 25 MHz TTL-compatible Video D/A                                                     | 6-33 | Q                               |

| AH8404TM Triple 4-bit, 20 MHz TTL-compatible Video D/A with                                                |      | β                               |

| 32-word color LUT memory                                                                                   | 6-33 | φü                              |

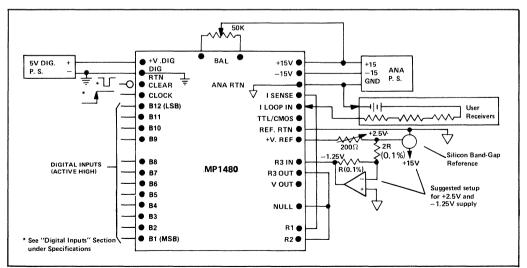

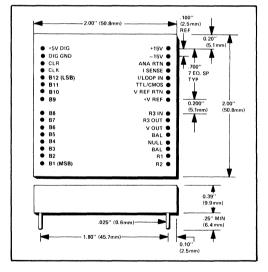

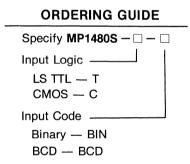

| MP1480S 12-bit D/A with 4-20 mA Current Loop or Voltage Output                                             | 6-37 | SAMPLE-AND-HOLD<br>AMPLIFIERS   |

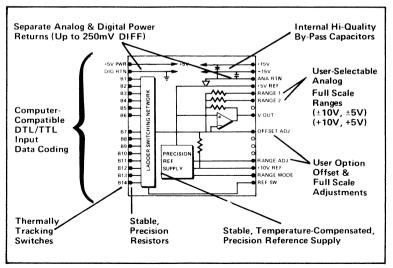

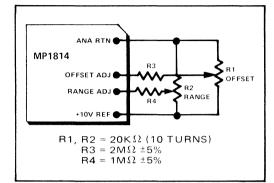

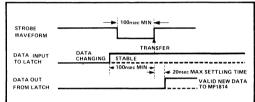

| MP1814 14-bit General Purpose D/A                                                                          | 6-43 | E E                             |

| MP1913A 13-bit Precision D/A                                                                               |      | × ₹                             |

| MP1914A 14-bit Precision D/A                                                                               | 6-47 | S                               |

| MP1915A 15-bit Precision D/A                                                                               | 6-47 |                                 |

| MP1916A 16-bit Precision D/A                                                                               |      | <u> </u>                        |

| MP1914TC 14-bit Temperature Stabilized Precision D/A                                                       | 6-51 | ANALOG-TO-DIGITAL<br>CONVERTERS |

| MP1915TC 15-bit Temperature Stabilized Precision D/A                                                       | 6-51 | SE                              |

| MP1916TC 16-bit Temperature Stabilized Precision D/A                                                       |      | <u>o k</u>                      |

| MP1926A 16-bit Sign/Magnitude, Professional Audio D/A                                                      | 6-55 | 5 N                             |

| MP1926S 16-bit Ultra-stable Sign/Magnitude D/A                                                             | 6-55 | 28                              |

| MP1936 16-bit Sign/Mag. Professional Audio D/A with                                                        |      | NA N                            |

| Integral Distortion Suppressor                                                                             | 6-63 |                                 |

| MP8116 16-bit Ultra-Stable, Ultra-Precision D/A                                                            |      |                                 |

| MP8308ECL 8-bit ECL-compatible Modular Composite Video D/A                                                 |      | N                               |

| MP8308TTL 8-bit TTL-compatible Modular Composite Video D/A                                                 |      | ULL SW                          |

| MP8318ECL 8-bit ECL-compatible non-composite Video D/A                                                     | 6-79 | SE                              |

| MP8318TTL 8-bit TTL-compatible non-composite Video D/A                                                     | 6-79 | S<br>S<br>S                     |

| 7 de/de Convertere                                                                                         |      | DATA ACQUISITION<br>SUBSYSTEMS  |

| 7. dc/dc Converters<br>Selection Guide                                                                     | 70   | SAT                             |

| Glossary                                                                                                   |      |                                 |

|                                                                                                            |      |                                 |

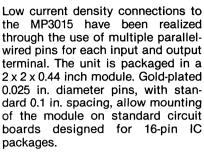

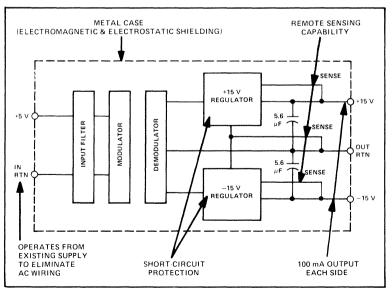

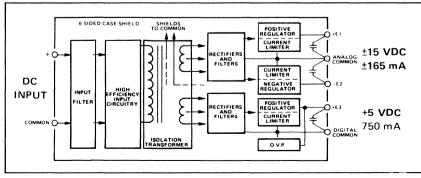

| MP3015 + 5V In, ± 15V @ 100 mA Out, dc/dc Converter<br>MP3020 + 5V In, ± 15V @ 150 mA Out, dc/dc Converter |      | G                               |

| MP3020 $\pm$ 5V in, $\pm$ 15V @ 75 mA Out, dc/dc Converter                                                 |      | S LO                            |

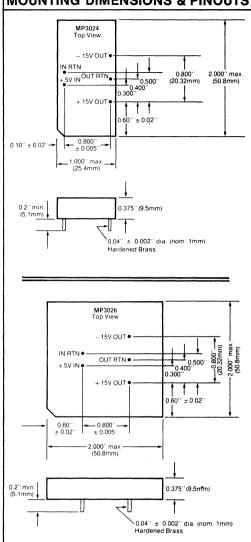

| MP3024 + 5V In, $\pm$ 15V @ 75 InA Out, dc/dc Converter                                                    | 7 12 | N H                             |

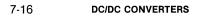

| MP3026 + 5V In, $\pm$ 15V @ 165 mA & + 5V @ 750 mA Out dc/dc Converter                                     | 7 17 | 0 H                             |

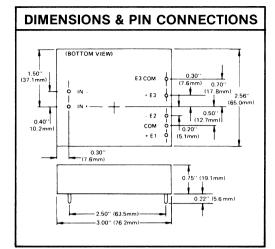

| $MF3033 + 5V$ in, $\pm 15V$ @ 105 inA a + 5V @ 150 inA Out doubt converter                                 |      | 52                              |

|                                                                                                            |      | DIGITAL-TO-ANALOG<br>CONVERTERS |

|                                                                                                            |      | ă                               |

|                                                                                                            |      |                                 |

|                                                                                                            |      |                                 |

DC/DC CONVERTERS

# ALPHANUMERIC PRODUCT INDEX

| Model                | Product                                                                      | Page |

|----------------------|------------------------------------------------------------------------------|------|

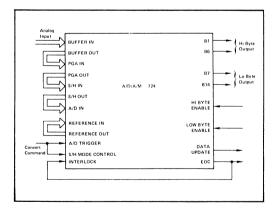

| ADAM-724             | 14-Bit, 6.8 $\mu$ s A/D with S/H and Diff. Amp                               | 5-3  |

| ADAM-812             | Dual Simultaneous S/H and 12-bit, 50 kHz A/D                                 | 5-13 |

| ADAM-822             | Dual Simultaneous S/H and 12-bit, 25 kHz A/D                                 | 5-17 |

| ADAM-824A            | Low Power, 14-bit, 50 kHz A/D with Integral S/H                              | 5-23 |

| ADAM-825A            | Low Power, 15-bit, 50 kHz A/D with Integral S/H                              | 5-23 |

| ADAM-826-1           | 16-bit, 1.5 $\mu$ s A/D with Integral 800 ns S/H                             | 5-33 |

| ADAM-826-2           | 16-bit, 1.5 µs A/D with Integral 400 ns Buffer Amplifier                     |      |

| ADAM-826-3           | 16-bit, 1.5 μs A/D (Unbuffered)                                              | 5-41 |

| ADAM-834A            | Low Power, Extended Temp. Range 14-bit A/D and S/H                           |      |

| ADAM-835A            | Low Power, Extended Temp. Range 15-bit A/D and S/H                           |      |

| AH201-1              | Single Channel Audio Distortion Suppressor                                   | 2-5  |

| AH201-2              | Dual Channel Audio Distortion Suppressor                                     | 2-5  |

| AH8304TC             | Triple 4-bit, 100 MHz, TTL Video D/A Converter                               | 6-7  |

| AH8304TM             | Triple 4-bit, 20 MHz TTL Video D/A with                                      |      |

| AU 00005             | 32-word color LUT Memory                                                     |      |

| AH8308E              | Single 8-bit, 150 MHz, ECL-compatible Video D/A                              |      |

| AH8308T              | Single 8-bit, 100 MHz, TTL-compatible Video D/A                              |      |

| AH8308TC             | Triple 8-bit, 100 MHz, TTL-compatible Video D/A                              |      |

| AH8404TC<br>AH8404TM | Triple 4-bit, 25 MHz, TTL-compatible Video D/A                               | 0-33 |

| A11040411W           | Triple 4-bit, 20 MHz, TTL-compatible Video D/A with 32-word color LUT memory | 6-33 |

| MP221                | Low Noise Chopper Amplifier                                                  |      |

| MP227A               | Precision Isolation Amplifier                                                | 2.17 |

| MP260                | 3 μs Sample-and-Hold (Optimized for Simultaneity)                            | 3-5  |

| MP261                | $5\mu s$ Sample-and-Hold.                                                    | 3-5  |

| MP270                | 1 μs, 0.005% Linearity Sample-and-Hold                                       | 3-11 |

| MP271                | 1 $\mu$ s, 0.003% Linearity Sample-and-Hold                                  |      |

| MP272                | 350 ns, 0.01% Linearity Sample-and-Hold                                      |      |

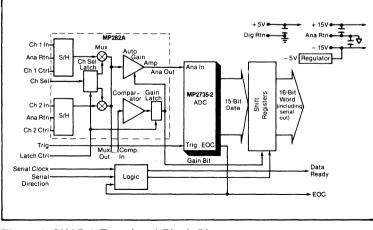

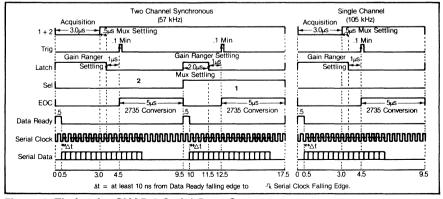

| MP282A               | Dual Channel Sample-and-Hold with 1-bit Gain Ranging                         |      |

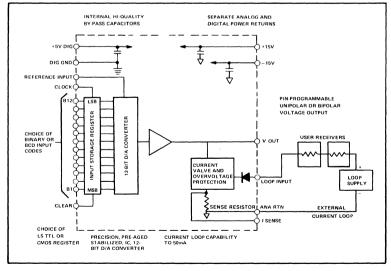

| MP1480S              | 12-bit D/A with 4-20 mA Current Loop or Voltage Output                       | 6-37 |

| MP1814               | 14-bit General Purpose D/A Converter                                         |      |

| MP1913A              | 13-bit Precision D/A Converter                                               |      |

| MP1914A              | 14-bit Precision D/A Converter                                               | 6-47 |

| MP1915A              | 15-bit Precision D/A Converter                                               | 6-47 |

| MP1916A              | 16-bit Precision D/A Converter                                               |      |

| MP1914TC             | 14-bit Temperature Stabilized Precision D/A Converter                        |      |

| MP1915TC             | 15-bit Temperature Stabilized Precision D/A Converter                        |      |

| MP1916TC             | 16-bit Temperature Stabilized Precision D/A Converter                        |      |

| MP1926A              | 16-bit Sign/Magnitude Professional Audio D/A Converter                       | 6-55 |

| MP1926S              | 16-bit Ultra-stable Sign/Magnitude D/A Converter                             | 6-55 |

| MP1936               | 16-bit Sign/Magnitude Professional Audio D/A with                            |      |

|                      | Audio Distortion Suppressor                                                  | 6-63 |

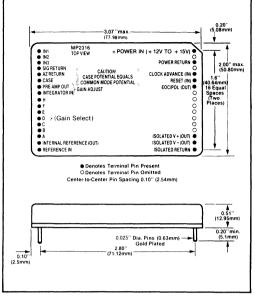

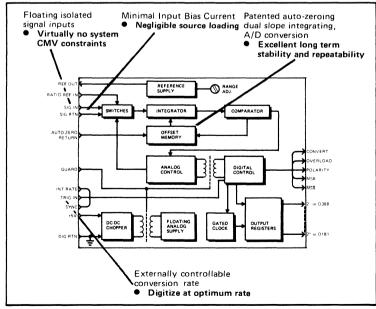

| MP2316    | 16-bit Floating Input, Programmable Gain, Analog Processor     | 4-11 |

|-----------|----------------------------------------------------------------|------|

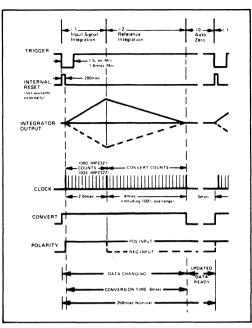

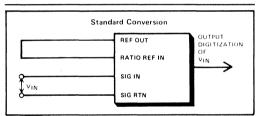

| MP2321    | 3 1/2 Digit BCD Output Integrating A/D Converter               | 4-21 |

| MP2322    | 12-bit Binary Output Integrating A/D Converter                 |      |

| MP2712D   | 12-bit, 5 μs A/D Converter                                     |      |

| MP2713C   | 13-bit, 10 μs A/D Converter                                    |      |

| MP2714C   | 14-bit, 10 μs A/D Converter                                    |      |

| MP2734    | 14-bit, 6.8 μs A/D Converter                                   |      |

| MP2735-1  | Low Distortion, 15-bit Audio Digitizer (A/D + S/H)             |      |

| MP2735-2  | Low Distortion, 15-bit, 5 µs A/D Converter                     |      |

| MP3015    | + 5V In, ± 15V @ 100 mA Out, 0.01% Regulation dc/dc Converter  |      |

| MP3020    | + 5V In, ± 15V @ 150 mA Out, 0.1% Regulation dc/dc Converter   |      |

| MP3024    | + 5V In, ± 15V @ 75 mA Out, 0.75% Regulation dc/dc Converter   |      |

| MP3026    | + 5V In, ± 15V @ 150 mA Out, 0.2% Regulation dc/dc Converter   |      |

| MP3035    | + 5V In, ± 15V @ 165 mA Out, 0.1% Regulation, + 5V @           |      |

|           | 750 mA Out 1% Regulation dc/dc Converter                       | 7-17 |

| MP8008R   | 8-bit, 300 kHz, Ultra-high Differential Linearity Sampling A/D |      |

| MP8014    | 14-bit, 10 μs A/D Converter                                    |      |

| MP8015    | 15-bit, 15 μs A/D Converter                                    |      |

| MP8016    | 16-bit, 32 μs A/D Converter                                    | 4-43 |

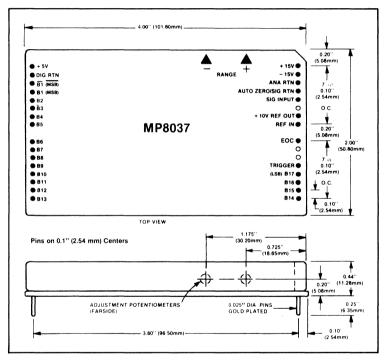

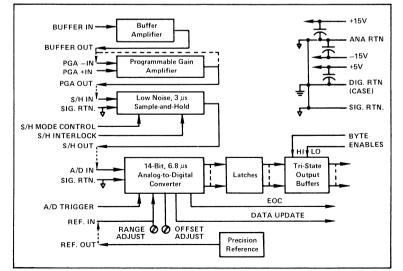

| MP8037    | 17-bit, 250 Hz Integrating A/D Converter                       |      |

| MP8116    | 16-bit, Ultra-Stable, Ultra-Precision D/A Converter            |      |

| MP8308ECL | 8-bit, ECL-compatible, modular composite video D/A Converter   |      |

| MP8308TTL | 8-bit, TTL-compatible, modular composite video D/A Converter   |      |

| MP8318ECL | 8-bit, ECL-compatible, modular non-composite video D/A         |      |

| MP8318TTL | 8-bit, TTL-compatible, modular non-composite video D/A         |      |

| SHAD2A    | Two-channel, 16-bit Audio Digitizing Subsystem                 |      |

| UT TO LA  |                                                                |      |

# PRICING AND TERMS

Pricing on Analogic data conversion products is available from any of our Sales Offices, Subsidiaries, International Distributors and Sales Representatives, or direct from the factory.

All prices are FOB Wakefield, Massachusetts, USA, in US dollars unless otherwise noted. Applicable federal, state, and local taxes are extra. Terms are net 30 days.

# QUOTATIONS

Price quotations made by Analogic or its authorized field sales representatives are valid for 30 days. Delivery quotations are subject to reconfirmation at the time the order is placed.

## RETURNS AND WARRANTY SERVICE

When returning products for any reason, it is necessary to contact Analogic, prior to shipping, for authorization and shipping instructions. In the U.S., contact our Customer Service Department at the factory in Wakefield, MA at (617) 246-0300 or 1-800-237-2200. In other countries, contact your nearest Analogic sales office or representative.

# APPLICATIONS ASSISTANCE

If you need technical assistance regarding any aspect of the standard Data Conversion Products offered in this catalog, or, if you require a modification to a standard product to meet your requirements, or, if you would like to discuss your application and the use of Analogic's extensive expertise in the signal conditioning and data conversion areas to design and manufacture a subsystem or component to meet your specific requirements, please call our Applications Engineering Group at (617) 246-0300 Ext. 2368 or 2168.

# INTRODUCTION

The purpose of this Catalog is to provide you, the system designer, with an easy to use reference on data conversion technology as well as a selection guide for Analogic's Data Conversion Products. Complete technical data is provided for all of our standard product line. Similar products are grouped according to function, i.e. all amplifiers are in one section, all sample-and-hold amplifiers are in another section. A/D converters in another, etc. Selection guides are provided to assist in the selection of the appropriate product with respect to the most critical parameters for a given application. If information on a specific product is required, an alphanumeric index of all products is also provided.

Special modifications to standard products are easily accomplished; please consult the factory for details.

# PLACING AN ORDER

Orders may be placed via mail, telephone, or Telex with any Regional Sales Office, sales representative, or our headquarters in Wakefield, Massachusetts. Our offices are listed on the inside back cover of the catalog. When placing your order, please provide complete information, including Analogic Model Number with all option designations, your Part Number (if required), product description or name, quantity required, and ship-to and bill-to addresses

# DATA SHEETS/LITERATURE

Product data sheets on new products not found in this Catalog, or containing more recent revisions, are available from your local sales representative or Analogic sales office.

# SECTION 1 General Information

####

Amplifiers

# **SELECTION GUIDE**

| MAJOR CHARACTERISTIC<br>OR APPLICATION REQ'MT |                               | SECONDARY<br>PARAMETER     | RECOMMENDED<br>MODEL NO. | DATA SHEET<br>ON PAGE |

|-----------------------------------------------|-------------------------------|----------------------------|--------------------------|-----------------------|

| Signal Conditioning                           | Differential<br>Input         | High Isolation<br>Voltage  | MP227A                   | 2-17                  |

|                                               | Single-Ended<br>Input         | Low Noise<br>Low Bandwidth | MP221                    | 2-11                  |

| DAC Deglitching<br>Professional Audio         | Low<br>Harmonic<br>Distortion | Single-<br>Channel         | AH201-1                  | 2-5                   |

|                                               |                               | Dual-Channel               | AH201-2                  | 2-5                   |

# **GLOSSARY OF TERMS**

# AMPLIFIERS

**FULL POWER BANDWIDTH** The highest frequency at which an amplifier, loaded to maximum rated output, will track a sinusoidal signal large enough to drive the output to its rated full-scale value at peak input. The nominal relationship between full power bandwidth and the slew rate is:

$f = Slew Rate / 2 \pi e_{fs}$

where: f = Full Power Bandwidth e

$e_{fs}$  = rated full scale output.

**GAIN ACCURACY** The maximum amount that the actual voltage gain deviates from the nominal value expressed as a percentage of that nominal value. This takes into account the effects of temperature variations, power supply variations, and drift with time, if significant.

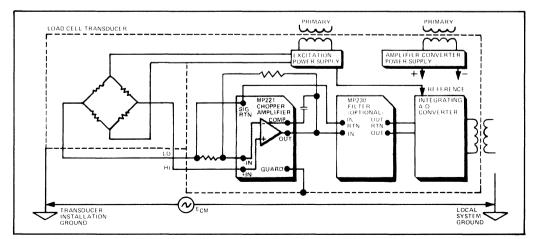

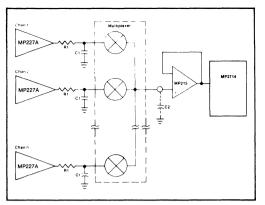

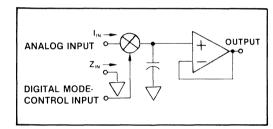

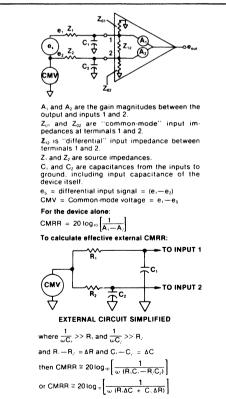

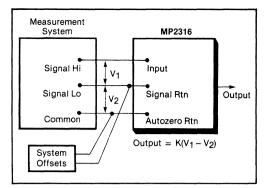

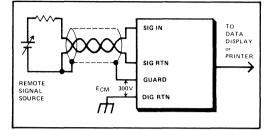

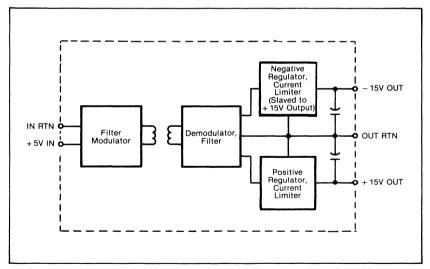

**ISOLATION AMPLIFIER** A circuit that typically accepts a low level signal, often in the presence of a high level common mode voltage, from a transducer, and amplifies it to produce a clean, accurate output signal. Figure 1 shows a simplified functional diagram.

**OVERLOAD RECOVERY TIME** The time required for the circuit to return to linear operation, within a stated tolerance, after removal of a sustained input that was large enough to drive the circuit into complete saturation (i.e., a condition in which further increase in the input did not significantly increase the output).

**SETTLING TIME** The maximum time required for the output to track the input to within the specified accuracy after a full range step change.

**SLEW RATE** The maximum slew rate is the fastest rate of change of the output of the amplifier. This is normally obtained by a step input signal that drives the output from end to end of its range.

**SMALL SIGNAL BANDWIDTH** The maximum small signal bandwidth is the highest frequency at which an amplifier will track, to within 3 db of the low frequency response, a sinusoidal signal having an amplitude below that for which the slew rate limitation is significant.

Figure 1. Simplified Functional Diagram.

2-4 AMPLIFIERS

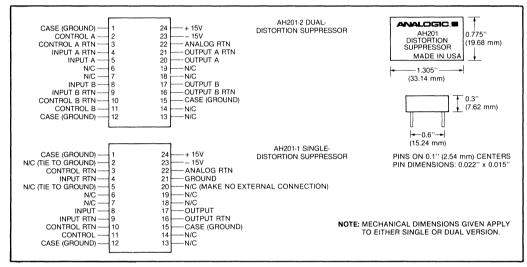

**AH201** Distortion Suppressor

# Description

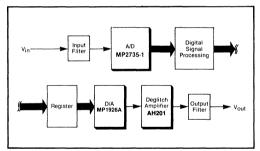

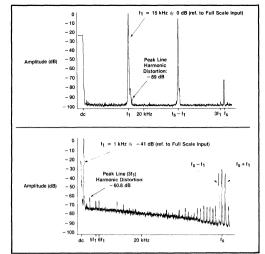

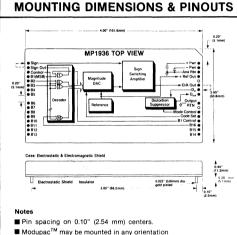

The AH201 is a low-cost distortion suppressor, used to reduce the total distortion generated by unmatched bit switching in the decoder digitalto-analog (D/A) converter section of a digital audio or communications system. The AH201 features exceptionally low noise (- 115 dB), and a time-constant limited response that eliminates slew-rate limiting problems, yet is short enough (3.4  $\mu$ s) to ensure no significant attenuation of signals up to 20 kHz. These features, combined with a typical feedthrough rejection of 100 dB, provide a significant improvement in the performance of any digital audio decoder. Optimum performance is obtained by using the AH201 in combination with a true 16-bit D/A converter such as the ANALOGIC MP1926A

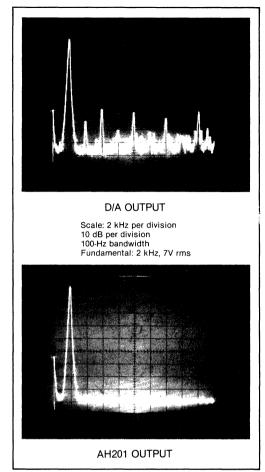

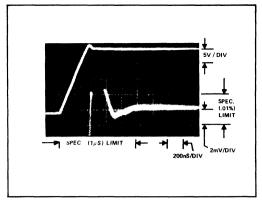

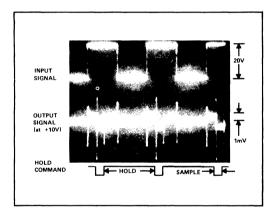

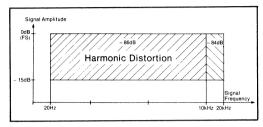

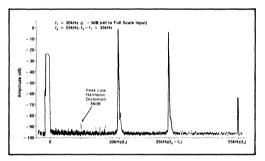

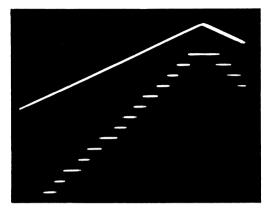

All D/A converters generate some dynamic distortion each time they perform a conversion. This distortion results from code-dependent switching glitches or from slew-rate limiting of the D/A's output amplifier. Conventional sample-and-hold (S/H) amplifiers used at the D/A output do not suppress this distortion adequately for high performance, professional audio applications due to slew-rate limiting when changing modes. The AH201, however, can reduce the distortion from these nonlinearities by up to 40 dB or more, depending upon the decoder with which it is used. (Refer to Figure 2 for example).

The AH201 is a direct result of ANALOGIC's considerable experience in digital audio including professional audio recording, studio links, and telecommunications, Designed for ease of interconnection and maximum flexibility, the distortion suppressor requires a single control line per channel to provide all necessary control. The AH201 accepts a ±10V input and can drive up to  $\pm 16$  mA into a 600-ohm load. The distortion suppressor is offered as a single or dual device, packaged in a 24-pin, double-width DIP, fully shielded metal can. Its small size, low noise. low cost and exceptional performance qualify the AH201 for use in any digital-audio system.

# Features

- Low Harmonic Distortion 0.003% (-90 dB), maximum

- Ultra-low Noise - 115 dB

- Single-Channel (AH201-1) or Dual-Channel (AH201-2) Versions

- Time-Constant Limited Response Eliminates distortion due to slew-rate limiting

- Small Size 24-pin DIP

- Single Control Line/Channel

- Optimized for D/A Deglitching

#### **Applications**

- Professional Digital Recording Systems

- Satellite Downlinks

- Video Disc Audio

- Signal-Processing Systems

- Compact-Disc Systems

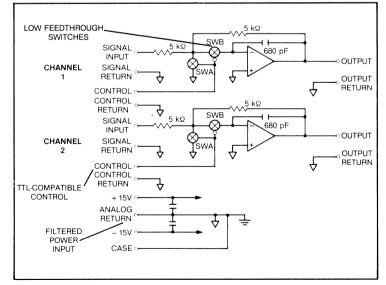

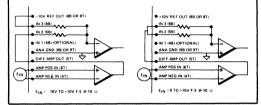

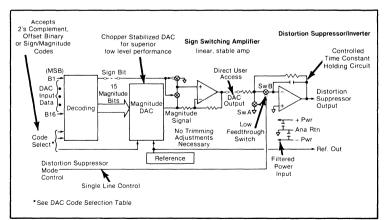

Figure 1. AH201 -2 Functional Block Diagram

#### SPECIFICATIONS

(All Specifications are guaranteed at 25 °C unless otherwise noted)

#### INPUT

Input Voltage Range: ± 10V Input Voltage Without Damage: ± 15V Input Impedance:

5 kohms, ±2%

## OUTPUT

Output Voltage: ± 10V Load: 600 ohms, minimum

Protection: Short circuit to ground

Output Impedance @ dc: 0.1 ohm, maximum

#### TRANSFER CHARACTERISTICS

Frequency Response dc to 20 kHz: 0 dB, ± 0.3 dB maximum

**Time Constant**<sup>1</sup>: 3.4 μs, nominal

Settling Time: Determined by time constant

Bandwidth (SAMPLE Mode): 46 kHz (Time-constant limited)

Gain<sup>2</sup>: -1,  $\pm 0.02$ , maximum

#### ACCURACY (AT 25°C)

Integral Nonlinearity: ± 0.002% FSR, maximum

Noise (20 kHz Bandwidth)<sup>3</sup>: 10 μV rms, maximum

Total Distortion: Down by at least 90 dB for frequencies up to 20 kHz (including harmonic distortion)

Peak Line Harmonic Distortion: Down by at least 96 dB for frequencies up to 20 kHz

Output Offset Voltage (SAMPLE Mode)<sup>2</sup>: ± 12 mV, maximum

Feedthrough (HOLD Mode)<sup>5</sup>: Down by 96 dB minimum, 100 dB typical for ± 10V sinewave up to 20 kHz

Power Supply Sensitivity Gain: 20 ppm FSR/V, maximum Offset:

20 µV/V, maximum

Channel-to-Channel Crosstalk<sup>4</sup>: Down by at least 100 dB

#### DIGITAL CONTROL INPUT

Logic Levels: TTL compatible

SAMPLE Mode (Output Connected to Input): Logic 0; 0V to 0.4V, maximum

HOLD Mode (Output Disconnected from Input): Logic 1; + 2.4V, minimum to + 5V

#### **POWER REQUIREMENTS (Exclusive of load)**

+ 15V,  $\pm$  3%: 10 mA, maximum (single channel, -1) 20 mA, maximum (dual channel, -2) - 15V,  $\pm$  3%: 10 mA, maximum (single channel, -1) 20 mA, maximum (dual channel, -2)

#### ENVIRONMENTAL AND MECHANICAL

**Operating Temperature Range:** 0°C to 70°C

Storage Temperature Range: -25 °C to +85 °C

Relative Humidity: 0 to 85%, noncondensing to 40°C

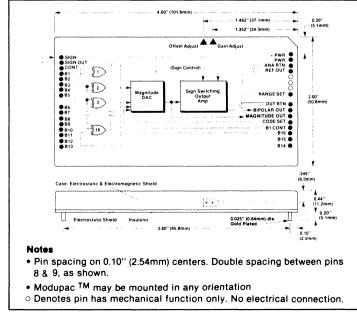

Dimensions (Single or Dual Channel) 1.305" x 0.775" x 0.3", maximum (20.07 x 33.14 x 7.62 mm) 24-pin double-width DIP

**Pin Spacing:** 0.6" x 0.1"

Packaging: Metal can

#### Shielding:

Electromagnetic—6 sides Electrostatic—6 sides

- Note 1: Other time constants also available. Consult factory.

- Note 2: From 0°C to +70°C.

- Note 3: Measured at 50% duty cycle. 10  $\mu$ V rms equals 115 dB referenced to rms full scale.

- Note 4: Measured on one channel with its input grounded, with a ± 10V sinewave of frequency up to 20 kHz applied to the input of the other channel; applies to dual-channel AH201-2 version only.

Note 5: Feedthrough specification given is for standard 3.4 μs time constant. Feedthrough performance will be different for time constants other than 3.4 μs. Please consult factory.

## **Theory of Operation**

The operation of a single-channel AH201-1 is described. Each channel of the AH202-2 operates in a similar manner.

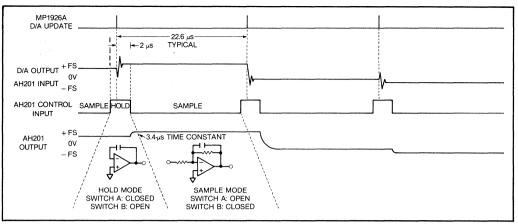

The AH201-1 consists of an inverting amplifier, a hold capacitor, and a pair of specially selected analog switches controlled by an external mode command. As shown in Figure 3, the mode is switched to minimize the effects of DAC nonlinearities on the output of the recovery system.

When the D/A output has settled to the value corresponding to the digital code at its input, the AH201 is commanded to the SAMPLE mode; shunt switch "A" opens and series switch "B" closes, connecting the settled D/A output to the output of the AH201. In this mode, the AH201's output response is exponential with the 3.4- $\mu$ s time constant.

The AH201 remains in the SAMPLE mode until just prior to the time when the D/A is updated to a new value, when it is commanded into the HOLD mode. The switch positions reverse, shunting the changing D/A output signal to ground. The previous output level, now stored on the capacitor, is maintained as the output of the AH201. The 96-dB, minimum, feedthrough rejection of the AH201 effectively isolates the output from the transients and other nonlinear settling characteristics of the D/A converter.

When the distortion suppressor is switched between its two modes, it passes signals up to 20 kHz without introducing significant distortion. For example, with the AH201 switching at 50 kHz, the peak line distortion for a full amplitude sinewave at 20 kHz is 96 dB down with respect to the full-scale level.

# **USING THE AH201**

#### Grounding

AMPLIFIERS

The power return, analog input and output returns, and control return are all tied together internally and to the case. For convenience in pc-board layout, return pins for each function are located adjacent to the corresponding signal pins. To avoid ground loops, no connection should be made to the case ground pins 1, 12, and 15.

When using the AH201-1 single-channel version, it is necessary to connect pins 2 to 3 and 5 to 4. In addition, no connection should be

Figure 2. System Improvement with AH201

made to pin 20. In both the single-channel AH201-1 and dual-channel AH201-2 versions, no connection should be made to pins 6, 7, 13, 14, 18, 19, or the case ground pins 1, 12, and 15.

## Control

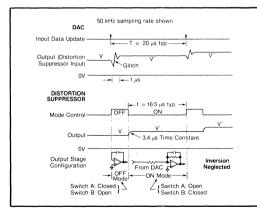

One control line is provided for each channel of the AH201. A logic 0 selects the SAMPLE mode, connecting the output to the input; a logic 1 selects the HOLD mode, isolates the output from the input. Please refer to Figure 3 for typical timing information. AMPLIFIERS

A time-constant limited response affects all input-voltage changes in the same proportion as long as the settling time allowed is constant. For this example, the on (SAMPLE) time of 17  $\mu$ s (5 time constants) results in a gain error of 0.1 dB. If required, this gain reduction can be corrected by the system gain adjustment.

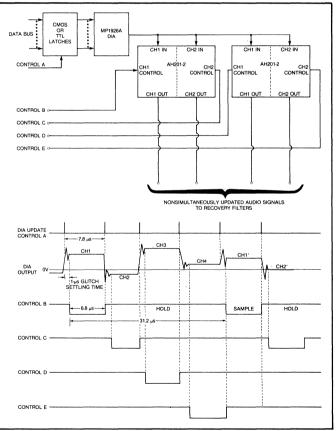

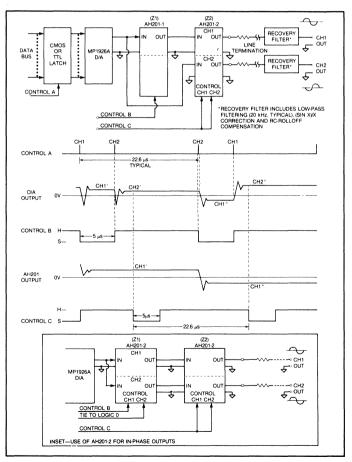

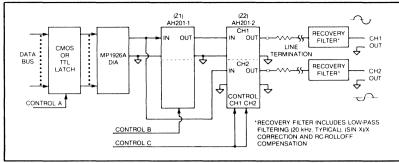

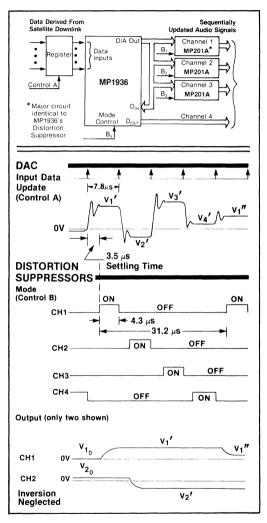

Figure 4. Non-Simultaneous Updating of Multiple Audio Channels (15 kHz bandwidth per channel, 16-bit resolution, 32 kHz sampling rate).

# TYPICAL APPLICATIONS Satellite Downlink Program Distribution

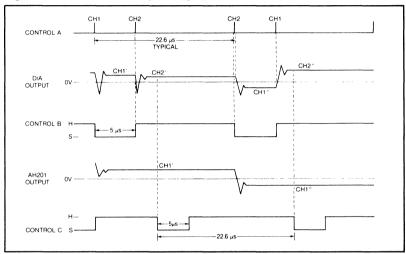

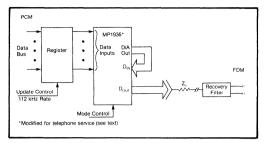

Multiple channels may be sequentially updated using one high-speed, high-accuracy D/A converter (such as the ANALOGIC MP1926A 16-bit Sign/Magnitude D/A) and multiple AH201s (-1 or -2). For example, a satellite ground station used in a programchannel distribution system would be required to update multiple audio outputs, but not necessarily simultaneously. Figure 4 illustrates one possible implementation using a single D/A converter to sequentially update four, 15-kHz bandwidth, audio channels. A nominal 32-kHz sample rate per channel is assumed. This means that the D/A converter must update four channels every 31.2  $\mu$ s or one channel every 7.8  $\mu$ s, which is well within the settling capability of the MP1926A. The AH201 circuit in each channel is simply turned on (SAMPLE mode) for the last 6.8  $\mu$ s of the corresponding MP1926A update period.

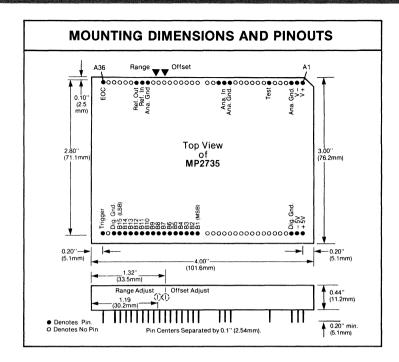

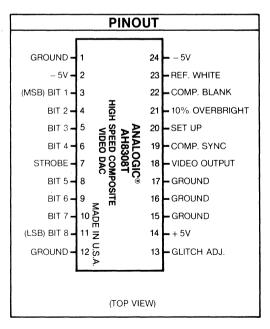

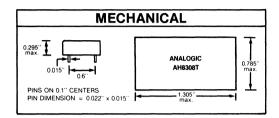

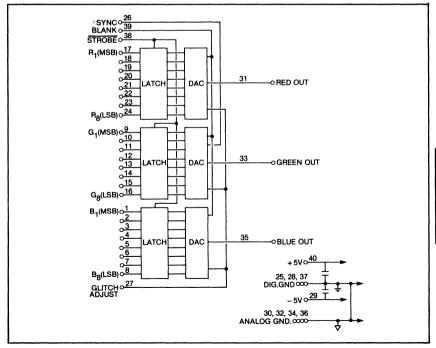

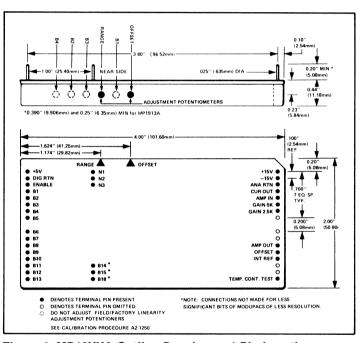

**Mechanical & Pinout**

# **ORDERING GUIDE**

Single-Channel Distortion Suppressor...Specify AH201-1 Dual-Channel Distortion Suppressor...Specify AH201-2

#### **Stereo Program Distribution**

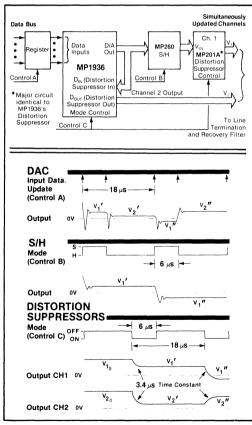

Figure 5 illustrates the highest performance yet lowest cost method available for simultaneously updating stereo analog outputs, at rates up to 55 kHz from 16-bit resolution data (98 dB dynamic range). Conventional implementation requires two D/A converters plus digital double buffering to achieve simultaneous updating. The ANALOGIC MP1926A, with a voltage settling time of only 5  $\mu$ s to 1 LSB for a 5V step, allows both channels to be updated from a single D/A converter within the 18  $\mu$ s available. The only buffering required for simultaneous updating can be provided by an additonal AH201-2 configured as shown in Figure 5.

The timing diagram shows that the AH201 (Z1 in the Figure) samples the D/A output during a time slot assigned to Channel 1. It then holds this new Channel 1 level while the D/A output

settles to a new Channel 2 value. As a result of the AH201's 96 dB feedthrough rejection in the HOLD mode, the Channel 2 information signal has a negligible effect on Channel 1. When the inputs to the AH201-2 (Z2 in the Figure) have settled to the new levels, both channels are switched into the SAMPLE mode simultaneously, causing both channel outputs to be updated. It should be noted that the two channels will be 180 degrees out of phase due to the double inversion in Channel 1. To bring both channels in-phase, an AH201-2 can be substituted for the AH201-1 (Z1), and the control for its second channel can be hardwired in the SAMPLE mode, as shown in the inset of Figure 4: alternatively. the sign of the data for one of the channels can be inverted prior to being presented to the DAC inputs.

Figure 5. Simultaneous Updating of Stereo Audio Channels.

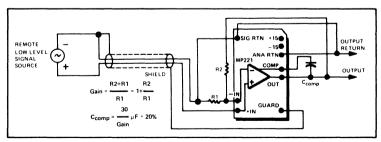

# MP221

Low Noise, Low Level Chopper Amplifier

# Description

The Analogic MP221 Chopper Amplifier provides unprecedented low level signal amplification for instrument and industrial applications in the microvolt-to-millivolt region. The MP221 design generates less than 0.1 µV p-p noise from dc to 1 Hz. less than  $0.3 \,\mu V$  p-p from dc to 10 Hz, less than  $1 \mu V p p$  from dc to 100 Hz, and less than 3 pA noise current from dc to 1 Hz. These superior specifications include flicker noise and Johnson noise components as well (See Figure 1). Moreover, the MP221 is virtually drift free with a maximum voltage drift of 0.05 µV/°C, a maximum current drift of 2 pA/°C, and a long term drift of 1  $\mu$ V/month or 2  $\mu$ V/year.

#### Implementation

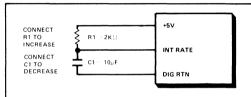

Optimized for non-inverting signal applications, the MP221 amplifier is normally soldered to a user's PC board. Gold-plated pins enhance solderability and conductivity. Amplifier gain is determined by selecting and connecting two resistors and a capacitor external to the MP221 as shown in Figure 1. Both resistors must possess an operational stability of 10 ppm/°C or better to maintain the performance capability inherent in the MP221 advanced design. Thermal effects at the amplifier input terminals can be minimized by using low thermal solder and utilizing the installation precautions customary for low level signal circuits.

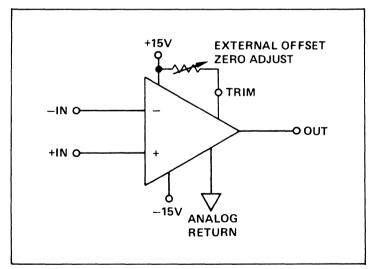

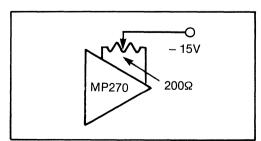

Current offset of the MP221 can be trimmed to zero by adjusting a built-in potentiometer. An external offset voltage adjustment may be incorprated as shown in Figure 4. When the MP221 is used in the noninverting mode, the offset voltage can be buffered from the input by using a voltage follower to avoid interaction with the gain components.

## Features

- Low Noise <0.1 μV p-p <3 pA p-p</p>

- Low Drift <0.03 µV/°C <2 pA/°C

- Gain Linearity within ± 0.002%

- High Input Impedance 10<sup>9</sup>Ω

- Short-Circuit Protected

#### **Applications**

- Instrumentation, Load Cells, Thermocouples, Strain Gauges

- Measurement Preamplifiers

- Low Level Buffers

Figure 1. MP221 Non-Inverting Pin Connections and Gain Resistor/Capacitor Calculations.

#### **SPECIFICATIONS**

(All specifications guaranteed at 25 °C unless otherwise noted) (Note: All performance at dc power of ±15V, gain = 100,  $R_1 = 100\Omega$ ,  $R_2 = 10 k\Omega$ , and  $C_{COMP} = 0.27 \mu$ F.)

#### ANALOG INPUT

Noise Current (0 to 1 Hz) 3 pA p-p **Offset Voltage**  $\pm 2 \mu V$  typ.,  $\pm 5 \mu V$  max. (ext. trim, Figure 4) **Bias Current (Non-Inverting)** ± 20 pA max. (trimmable to zero, Figure 3) **Bias Current (Inverting Mode)**  $\pm 2$  nA max. Input Impedance 10<sup>9</sup>Ω **Common Mode Voltage** ± 0.5V **Commom Mode Rejection Ratio** 140 dB Maximum Input Without Damage ± 20V

#### ANALOG OUTPUT

Voltage Range  $\pm 10V$ Current  $\pm 3 \text{ mA}$ Impedance at dc  $\pm 0.01\Omega$ Load  $3 \text{ k}\Omega$  in parallel with 0.1  $\mu$ F max. Short-Circuit Protection Output short-circuit protected ground

#### GAIN CHARACTERISTICS

Linearity  $\pm 0.002\%$ Gain Range 10 to 10,000\* Open Loop Gain 160 dB

#### NOISE BANDWIDTH

$\begin{array}{l} \mbox{dc to 1Hz} \\ < 0.1 \ \mu V \ p\mbox{-}p \\ \mbox{dc to 10Hz} \\ < 0.3 \ \mu V \ p\mbox{-}p \\ \mbox{dc to 100 Hz} \\ < 1 \ \mu V \ p\mbox{-}p \end{array}$

#### STABILITY

Tempco of Offset Voltage 0.03  $\mu$ V/°C typ., 0.05  $\mu$ V/°C max.

**Tempco of Bias Current** 2 pA/°C max.

Power Supply Sensitivity 0.01  $\mu$ V/1% power supply change

Warmup Drift To within 2  $\mu$ V of final value in 2 minutes Long Term Drift

1 μV/month, 2 μV/year

Thermal Step Offset Recovery 5 minutes for 25 °C step Offset Resulting from ac Input 1  $\mu$ V for 4 mV p-p 60 Hz Overlaod Recovery Time

200 ms to within 2  $\mu$ V for 10 x FSR input

### FREQUENCY RESPONSE

Bandwidth - 3 dB at 100 Hz Settling Time to 0.002% FS (50 + 8Vsw)ms; Vsw = Output voltage swing Slew Rate 130 V/s

#### POWER REQUIREMENTS

±15V 2.5 mA plus load current

#### ENVIRONMENTAL & MECHANICAL OPERATING TEMPERATURE

0°C to +70°C

Non-Operating Temperature - 25°C to + 85°C

Relative Humidity 0 to 95%, non-condensing

Shielding Protection RFI 6 sides; EMI 5 sides

Dimensions

2 x 1 x 0.39" Modupac<sup>TM</sup> (50.8 x 25.4 x 9.91 mm)

\*Note: At Gain <20, inputs must be  $< \pm 0.5$ V.

# **Application Information**

The Analogic MP221 Low Level Chopper Amplifier is designed to perform in the microvolt-to-millivolt signal range for instrument and industrial applications. This amplifier has been optimized for operation in the non-inverting mode so that gains from 10 to 10,000 can be achieved with minimum loading of the signal source. Because of its unique features, which include low noise, low thermal offset drift, and low bias current, the MP221 is ideally suited for use as a preamplifier with load cells, thermocouples, and other low level transducers. However, to obtain a level of performance consistent with the superior specifications of the MP221, some usage quidelines must be exercised. This application note provides several recommended techniques for operating the MP221 with low level input signals.

#### **Amplifier Operation**

The MP221 amplifier has a chopper input that effectively samples the voltage difference between its plus (+) and minus (-)inputs. A circuit employing this amplifier should be considered a "sampled data" system, and proper attention must be paid to the generated errors. The most important error is unwanted signals or noise appearing at the amplifier output, which can be attributed to aliasing or intermodulation distortion. These effects can be reduced by filtering the amplifier input and by choosing an optimum chopper frequency. Since most systems are subject to noise pickup at the line frequency and its harmonics, the MP221 has been set to sample at 925 Hz, which is 25 Hz removed from the nearest 60 Hz or 50 Hz harmonic. These harmonic components at the amplifier input are translated to 25 Hz at the output. Because most A/D converters can respond at this speed, post filtering is often necessary.

## Low Noise Techniques

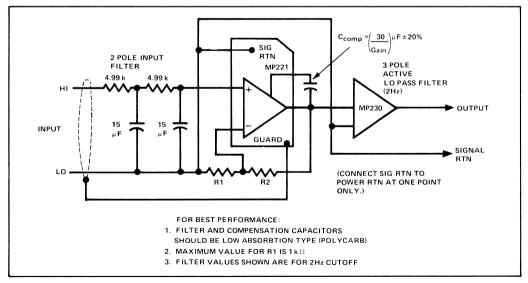

For low noise operation, it is recommended that low-pass filtering be used before and after the amplifier. (See Figure 2). Because most active-type filters generate noise within the amplifier bandwidth, the pre-filter should be composed of passive components. Noise injected after the amplifier is less critical, and for that reason, a threepole active-type low pass filter can be used as a post-filter. The component values shown in Figure 2 are effective for 2 Hz filtering.

Another consideration is to limit the bandwidth of the MP221 to that required in the system. Because the output noise generated by the amplifier varies as the square root of the bandwidth, there is 10 times more noise at a 100 Hz bandwidth than at 1.0 Hz bandwidth. The output capacitor ( $C_{comp}$ ) shown in Figure 2 sets the bandwidth for a given gain. The  $C_{comp}$

Figure 2. Recommended Filtering of MP221.

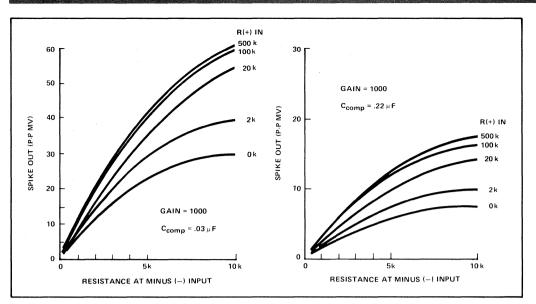

Figure 3. Switching Spikes vs. Input Source Impedance.

recommended value of (30/Gain) µF is for a 100 Hz bandwidth and bandwidth decreases proportionally as C<sub>comp</sub> is increased. For example, at a gain of 100, a 3  $\mu$ F C<sub>comp</sub> sets a bandwidth of 10 Hz. The parameters of the pre- and post-filters should also be set to obtain only the needed bandwidth. An additional source of noise appearing at the amplifier output is due to internal chopper switching transients. The magnitude of this noise depends upon the input resistances, primarily that between the minus (-) terminal and common. Figure 3 illustrates this dependence and also shows the reduction of this noise as  $C_{comp}$ is increased. Reduction of this noise is another reason why a post-filter is recommended.

For the stated reasons and because of the unavoidable Johnson noise effects, the resistors associated with the MP221 amplifier should be as low in magnitude as practical (a limitation being the current available to generate the output voltage levels). A maximum of 1 k $\Omega$  from the minus (-) input to ground is recommended. Because carbon composition and some film resistors generate noise in excess of Johnson noise, only stable wirewound resistors or known low noise film resistors should be used.

The signal input wiring should be shielded to reduce pickup; a shielded-twisted pair is recommended. The amplifier power supply inputs are decoupled internally, so that in most applications, external capacitors are not required.

## **Thermal Offset Techniques**

If noise could be reduced to that of the source (theoretical minimum), thermal offset voltages would still appear when amplifying microvolt input signals. These thermal offsets are caused by joining dissimilar metals and by existing temperature gradients across the input circuit. For example, a thermocouple of copper and lead/tin solder can generate an offset voltage of 0.3  $\mu V$  for 0.1 °C temperature difference between the metals. Since this temperature gradient varies with time, the thermal offset appears similar to low frequency noise or "wandering". The techniques used to minimize these thermal offsets are: (1) keep signal high and low input connections physically close to reduce temperature differences, (2) shield connections from all convection air currents (breezes), (3) heat sink the input connections tightly, and (4) only join similar metals (copper) using low thermal solder (cadmium/tin). When operating at the microvolt (or below) level. all four techniques may be required. If all copper connections are made at the MP221 input terminals using low thermal solder and the amplifier is wrapped in polyurethane foam, then the total thermal offset wandering should be less than  $0.1 \,\mu V$ .

#### **Bias Current Adjustment**

Another low level error is caused by bias current flowing through the external source resistance, thereby generating offset voltages. These voltages can be balanced externally but they are temperature dependent. An adjustment is provided on the MP221 so that the bias current at either input can be set to zero. However, since the currents at the inputs are not equal, only one input can be compensated, leaving a residual bias current at the other input.

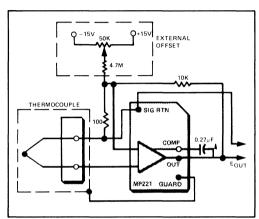

Figure 4. MP221 Amplification of the Thermocouple Low Level Output and Illustrating External Offset.

When an MP221 is used in the recommended positive gain configuration, the positive input bias current can be adjusted to zero with the negative input bias current remaining less than  $\pm 2$  nA. If the resistor connected to the negative input is less than 1 k $\Omega$  (R1, Figure 2), the offset voltage due to the  $\pm 2$  nA should be only  $\pm 2 \mu V$  (referred to the input). This value is much less than the offset voltage specification of the amplifier ( $\pm 5 \mu V$  maximum).

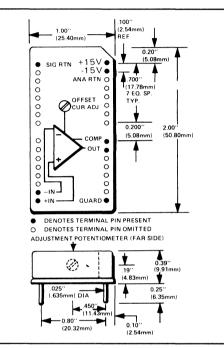

Figure 6. Mechanical & Pinout.

Figure 5. MP221 Low Level Amplification with Guarded System in Presence of High Common Mode Voltage.

# ORDERING GUIDE

Low Noise, Low Level Chopper Amplifier

Specify MP221.

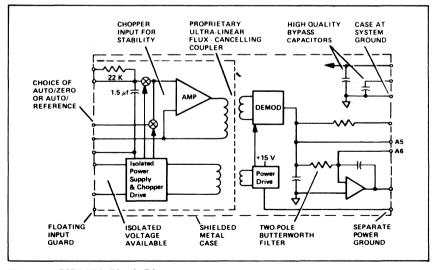

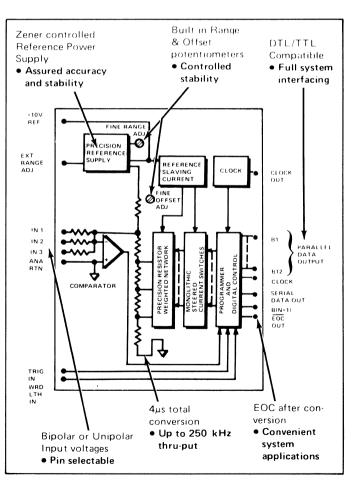

MP227A Isolation Amplifier

## Description

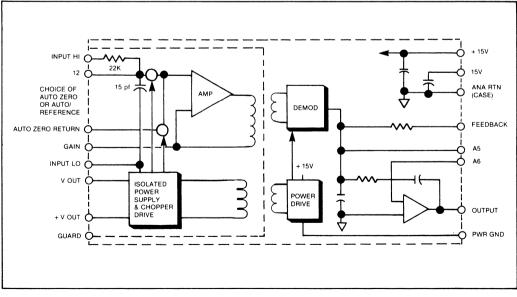

The Analogic **MP227A** is a precision isolation amplifier that provides an unparalleled combination of linearity, stability, isolation, and very low cost. It is designed primarily to replace relays and filter elements in multichannel data acquisition systems. However, its unique features make it attractive wherever low-level, low frequency signals must be amplified in the presence of severe common mode interference.

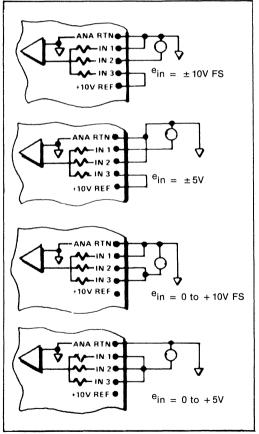

The **MP227A** offers user-selectable gains from 10 to 1000, input full-scale voltage ranges from  $\pm$  10 mV to  $\pm$  1V, 3-pole (60 dB/decade) filtering from 5 Hz, extremely good linearity, superb common-mode rejection, and very low drift. All parameters are commensurate with A/D conversion at levels up to 13 bits.

The **MP227A** includes an internal power oscillator and isolated supply so that no external drivers are needed. The isolated power  $(\pm 4V$ nominal) can be used for open thermocouple indication or offsetting strain gauge inputs.

#### Features

- High Common Mode Rejection 170 dB

- Excellent Linearity 0.0075%

- Selectable Input Range ± 10 mV FS to ± 1V FS

- Low Noise <0.5 μV rms</p>

- Low Drift 3.0 μV RTI per month

- Built-in 3-pole Filtering

- Built-in Oscillator/Driver

#### Applications

- Thermocouple Temperature Measurement

- Weighing Systems

- Strain Gauge Measurements

- Remote Data Acquisition and Precision Telemetry Systems

- Microvolt and Millivolt Level Measurements

- Replacement for Classical Instrumentation Amplifier

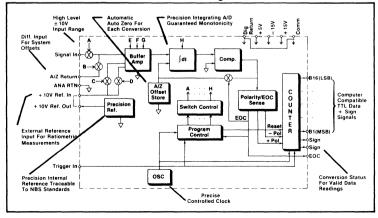

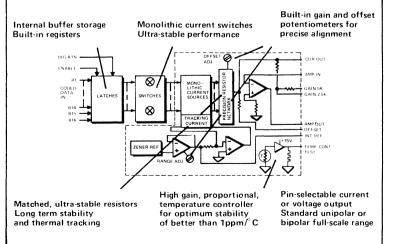

Figure 1. MP227A Block Diagram.

AMPLIFIERS

## SPECIFICATIONS

(All specifications guaranteed at 25°C unless otherwise noted)

#### ANALOG INPUT

#### **Gain Range**

10 to 1000, non-inverting, resistor programmable; optimized for gains of 50 to 500

#### Non-linearity

$\pm 0.0075\%$  FSR maximum at G = 50 to 500;  $\pm 0.01\%$  FSR maximum at G = 1000;  $\pm 0.05\%$  FSR maximum at G = 10

#### Input Amplifier Type Isolated Chopper

Linear Differential Input Voltage Range

$\pm$  10 mV to  $\pm$  1V full scale

Maximum Safe Differential Input Voltage 16V rms continuous, without damage

Common Mode Isolation Voltage 1000 Vdc, 750V rms, maximum

#### **Common Mode Rejection Ratio**

At dc, with G = 100 and 1000, 166 dB minimum; 1 k $\Omega$  source unbalance

At 60 Hz, with G = 100 and 1000, 176 dB typical, 160 dB minimum; 1 k $\Omega$  source unbalance

#### Common Mode Impedance 10,000 MΩ / / 80 pF

**Differential Input Impedance** At dc, 12 M $\Omega$ ; at ac, low-pass filter of 22 k $\Omega$  and 1.5  $\mu$ F

Overload input Impedance 22 k $\Omega$ , at 50/60 Hz

Input Bias Current 0.5 nA typical, 3.0 nA maximum; bias current increases if open input indicator circuit is used

#### **Offset Voltage**

At G = 10,  $\pm$  1 mV typical,  $\pm$  5 mV maximum; at G = 1000,  $\pm$  150  $\mu$ V maximum; all referred to input (RTI); offset voltage may be determined by interpolation for other gain values

Voltage Noise (0.01 to 5 Hz) At G = 10, 1.5  $\mu$ V rms maximum; at G = 100 and 1000, 0.5  $\mu$ V rms maximum; RTI

Bandwidth (See Note 1) dc to 5 Hz nominal; 6 dB down at 5 Hz

Overall Filtering (See Note 2) 3-pole, 60 dB/decade roll-off (- 60 dB at 50 Hz) Input Filter

1-pole RC, 3 dB cut-off at 5 Hz

Output Filter 2-pole Butterworth, 3 dB cut-off at 5 Hz

#### ANALOG OUTPUT

Voltage Range ± 10V full scale Output Impedance at dc 0.1Ω

Maximum Load ± 5 mA and 500 pF

#### **Output Protection**

Continuous short circuit to ground Output Chopper Noise (1 MHz BW)

$\pm$  1 mV p-p spike at approximately 10 kHz (See Note 3)

#### STABILITY

#### Gain Tempco

At G = 10 and 100,  $\pm$  25 ppm FSR/°C maximum; at G = 1000,  $\pm$  35 ppm FSR/°C maximum; exclusive of external gain setting resistor

#### Offset Voltage Tempco

At G = 10,  $\pm 5.0 \ \mu$ V/°C maximum; At G = 100,  $\pm 1.7 \ \mu$ V/°C maximum; At G = 1000,  $\pm 0.5 \ \mu$ V/°C maximum; all RTI

Bias Current Tempco 100 pA/°C maximum, at 25°C; doubles every 10°C (maximum)

Power Supply Sensitivity

At G = 1000,  $\pm 2.0 \ \mu$ V/%; at G = 10,  $\pm 10 \ \mu$ V/% maximum; RTI

Warm up Drift (5 Minutes) Within 2  $\mu$ V RTI typical at G = 1000

**Long Term Drift** 3.0 µV RTI/month typical

#### **ISOLATED POWER SUPPLY OUTPUT**

Voltage ±4 Vdc nominal, with respect to INPUT LO

Current

±3 mA full load

Regulation 12%, no load to full load

**Ripple** 60 mV p-p at 10 kHz

#### INPUT POWER SUPPLY REQUIREMENTS

+ 15V, ± 3% 3 mA, no load - 15V, ± 3% 5 mA, no load

#### ENVIRONMENTAL AND MECHANICAL

**Operating Temperature Range**  $0^{\circ}C$  to  $+70^{\circ}C$

Storage Temperature Range  $-55^{\circ}$ C to  $+85^{\circ}$ C

Relative Humidity 0 to 85%, non-condensing up to 40°C

Dimensions

1.2" x 2.8" x 0.5" (30 x 70 x 12 mm)

Shielding RFI: 6 sides; EMI: 5 sides

#### NOTES:

- 1. Modifications for bandwidths from dc to 100 Hz, or optimized for specific settling times are available on special order. Please contact factory.

- 2. Filter nodes are externally accessible to allow modification of characteristics.

- 3. Output Chopper noise can be reduced to negligible level by suggested output multiplexer circuit.

## **OPERATION DATA**

#### Application

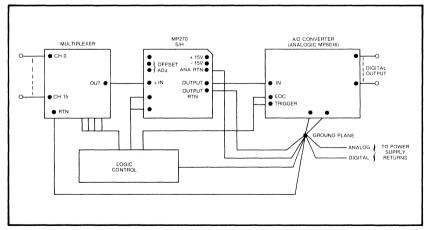

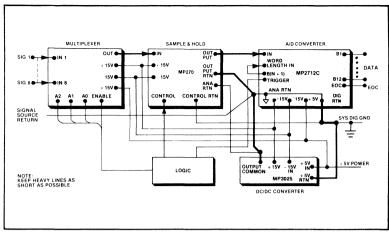

The **MP227A** was designed as an economically competitive and functionally superior alternative to the relay multiplexing circuits traditionally used in multichannel data acquisition systems. In a typical thermocouple system, the **MP227A** replaces two functional blocks for each channel — the input filter and a dual relay, as well as the common channel high gain amplifier — and permits high-level, solid-state multiplexing to be used for low cost and high reliability.

The **MP227A** provides significantly better isolation and common-mode rejection than low-level relays and it puts the gain at a point in the system where the bandwidth is lowest (prior to multiplexing), thereby reducing total system noise. Even where multiplexing is not used, the unusual combination of performance and price makes the **MP227A** attractive for a wide variety of industrial applications.

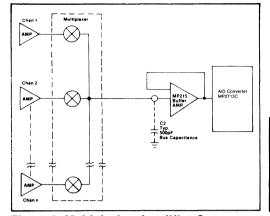

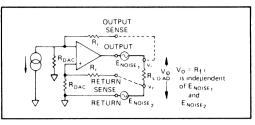

When many **MP227A's** are used in a system, a high speed, high level analog multiplexer switches the **MP227A** outputs to a common analog output bus for subsequent A/D conversion. Any high precision isolation amplifier/filter used in such a configuration has an inherent error source of sizable magnitude that is often overlooked, ignored or simply unknown, that is, dumped charge effects. This Application Note discusses the problem, the solution, and the fringe benefits.

#### **Dumped Charge**

Figure 2 shows the apparently straightforward connection of multiple amplifiers/filters and multiplexer to a common A/D converter.

Figure 2. Multiplexing Amplifier Outputs.

Each time the multiplexer in Figure 2 switches channels, for instance, from Channel 1 to Channel 2, the Channel 1 output appears across C2, the capacitance of the output bus. The output stage of Channel 2 must absorb that dumped charge before it can reach a true final value dependent only on its input. The exact magnitude of the dumped charge is not important: what is significant is that the Channel 2 amplifier may be forced to deliver a peak instantaneous current beyond its design specifications.

The dumped charge (Q) is defined as, Q = idt,

where i = C dv/dt

In a typical example, the outputs of the two channels could be at the extreme ends of the range.

Channel 1 output = +10V.

Channel 2 output = -10V.

This makes the voltage difference (dv).

dv = 20 volts.

Assume that the capacitance of the output bus C2 is about 500 pF, and a reasonable turn-on time for an analog switch is 100 ns, or.

$$C = 500 (10^{12})$$

$dt = 100 (10^9)$

Solving first for the current and then the dumped charge, gives:

$$i = C (dv/dt) = \frac{500 (10^{12})}{100 (10^{9})} 20 = 100 \text{ mA}$$

$Q = idt = (100)(10^3)(100)(10^9) = 10,000$ pico Coulomb Under these conditions, IC op amps, such as the popular 741, have been found to have full-scale current excursion lasting as long as a microsecond.

If the design factors allow a conventional IC output stage to drive the multiplexer instead of a high precision amplifier with an output/filter stage, no real harm is done by the dumped charge. The amplifier eventually recovers and C2 charges to the new value. The recovery time constant is the ON resistance of the multiplexer switch and C2

for R on =  $300\Omega$

$C2 = 500 \, pF$

$T = (300)(500) \ 10^{12} = 0.15 \ \mu s$

In high resolution systems, 10 time constants should be allowed to reach a voltage within 0.005% of final value. Therefore, the actual time should be  $1.5 \,\mu$ s.

The 1.5  $\mu$ s settling time required in this example is usually less than the settling time of the conventional buffer amplifier at the multiplexer output and the dumped charge effect can be safely ignored. The dumped charge cannot be ignored, however, when high precision amplifiers employing output filters are required.

## The Problem

Many isolation and/or instrumentation

amplifiers do not include an output filter. On the other hand, the **MP227A** has an integral two-pole Butterworth filter in the output stage. The feedback element of the **MP227A** is a capacitor and a sudden voltage step at the amplifier output, such as the dumped charge, presents a problem.

The dumped charge demands excessive current in too short a time and causes the amplifier to momentarily open-loop. The summing node changes to a large voltage, inducing current flow in the input resistor and causing an extraneous charge on the feedback capacitor.

This error source has produced observed errors as large as 0.05% in typical applications.

#### **The Solution**

Figure 4 shows the addition of a single-pole filter (R1, C1) at the output of each **MP227A** and ahead of the multiplexer. C1 of the succeeding channel, now absorbs the charge accumulated on C2 from the preceding channel. The **MP227A** no longer sees a step but a well controlled exponential change, well within its capabilities. Hence, the output stage in the **MP227A** does not openloop, and no spurious charge is placed on the feedback capacitor.

Figure 3. MP227A Isolation Amplifier Functional Block Diagram.

Figure 4. MP227A with Output Filters Added.

The best results are obtained with a time constant between 0.25 and  $0.5 \,\mu$ s. This must be short for two reasons: 1) a settling time of up to 10RC does not significantly add to multiplexer settling time and 2) the recovery time is sufficiently short for final values that are independent of the duty cycle involved in reading a channel.

R1 should be between 50 and  $270\Omega$ : this value is kept intentionally low to reduce voltage divider error (R1 + R<sub>on</sub> relative to R<sub>in</sub> of the follower at the multiplexer output) to an insignificant level. These values of R1 yield values for C1 between 10,000 pF and 1,000 pF which is an acceptable range for C1. In the capacitive voltage divider, formed by C1 and the bus capacitance C2, as C1 decreases in size relative to C2, the initial voltage transferred to C1 by a succeeding channel approaches its final value and leaves a smaller exponential rise portion.

R1, C1 MUST BE INCLUDED FOR ALL HIGH RESOLUTION (>12 BITS) APPLICATIONS OF THE MP227A.

# **Fringe Benefits**

Noise spikes inherent in the design of high performance isolation amplifiers are attenuated by 10 dB or more by the R1 C1 output filter.

The superior isolation of the **MP227A** is provided by transformer coupling. A modulator/demodulator is used in the analog signal path and is driven by an integral chopper/power driver. It is impossible to avoid some stray capacitance between the driver circuitry and the output. Careful design and layout of the **MP227A** has reduced the resulting output noise spikes caused by stray capacitance to 1 mVp-p, which is 0.01% relative to 10V F.S., when measured over a bandwidth of 1 MHz. The noise spikes repeat at 20 kHz, or twice the nominal 10 kHz frequency of the **MP227A** chopper driver.

If the output filter time constant (R1 C1) is equal to 0.5  $\mu$ s, then

- $fc = \frac{1}{2}\pi RC$

- = 333 kHz

This low cut-off frequency ensures that the output spikes, over an effective bandwidth in excess of 1 MHz, are attenuated 10 dB or more, which is enough to reduce this error source from .01% to a negligible level.

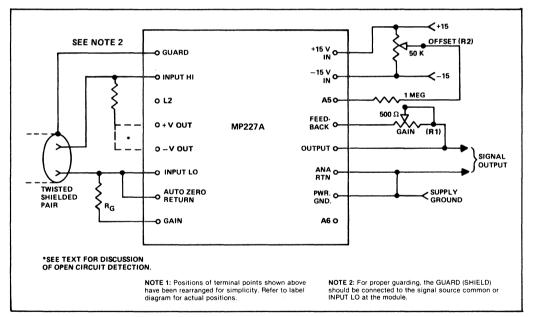

# USING THE MP277A Offset Adjustment

Provision is made for external offset adjustment on the **MP227A** Precision Isolation Amplifier by connecting a 25k or 50 k $\Omega$ (100 ppm/°C or better) multi-turn potentiometer (R2) with a 1 M $\Omega$  resistor as shown in Figure 2. To adjust, momentarily short INPUT HI, INPUT LO, and AZ RTN to the output ANA RTN and set the offset potentiometer for zero output at the OUTPUT terminal.

# Setting the MP227A Gain

The gain of the **MP227A** may be set to any value from 10 to 1000 by connecting an external resistor ( $R_G$ ) between the GAIN and INPUT LO terminals as shown in Figure 2. Gain is equal to:

$$Gain = \frac{10.27 \times 10^3}{R_G \Omega}$$

An RN55E or better resistor is recommended for temperature stability. Untrimmed, the absolute gain will be within +2% and -3% of the calculated value.

# **Gain Trimming**

The gain may be deliberately fine-trimmed, if desired, by connecting a  $500\Omega$  (100 ppm/°C or better) potentiometer (R1) between the FEED-BACK and OUTPUT terminals as shown in Figure 2. R1 compensates for the tolerance of R<sub>G</sub> plus the unit-to-unit gain variability (3%) between multiple **MP227As.** This also allows standardization of the outputs of multiple **MP227As** to a common full-scale range. For volume production where cost is a factor, the trimpot may be replaced with a fixed resistor selected during final testing.

#### Auto-Zero Return

The signal that is amplified by the **MP227A** is actually the difference between the INPUT LO and the Auto-Zero (AZ) voltages. For normal operation, tie the AZ terminal directly to the INPUT LO terminal. In some applications, it may be convenient to offset the input deliberately by an amount that exceeds the range of the OFFSET trimpot (for example, to obtain expanded scale operation or to cancel out the initial or "tare" output of a load cell). To do this, connect the AZ terminal to a source of voltage equal to the desired offset, with noise performance and stability at least as good as the signal source.

Observe that both the INPUT HI signal and the AZ signal (if any) are measured with respect to the INPUT LO terminal. For best linearity, each signal must be within  $\pm 1V$  of INPUT LO.

#### **Open Input Indication**

The user-accessible isolated power supply voltages make it possible to use a simple open input indication network. Connect a resistor on the order of 180 M $\Omega$  to the INPUT HI and either the +4V or -4V isolated power output terminal. This network produces a bleeder current of approximately 20 nA through the input source circuitry. If the source should open, this bleeder current will drive the **MP227A** output into a saturated state. The speed of this response is a function of the **MP227A** gain setting and input time constant.

#### Multiplexing MP227As

The outputs of multiple **MP227As** may be multiplexed to a common analog line as indicated in Figure 4. A single RC filter ahead of each MUX input is suggested.

Figure 5. Typical External Connections—MP227A.

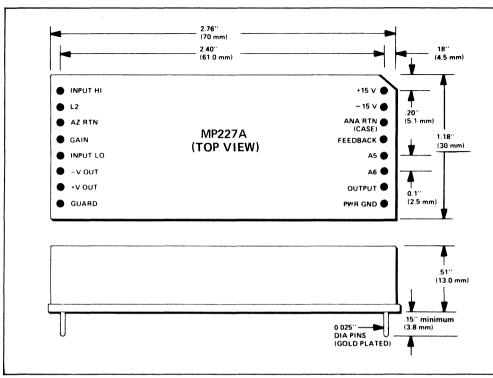

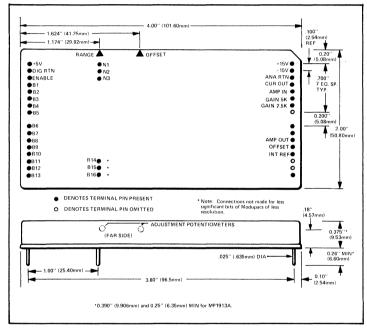

Figure 6. MP227A Mechanical & Pinout.

# **ORDERING GUIDE**

Specify MP227A

----

#### - -

# TABLE OF CONTENTS

# PAGE

| Selection Guide                                               | 3-2  |

|---------------------------------------------------------------|------|

| Glossary                                                      | 3-3  |

| MP260 3 µs, 0.002% Linearity S/H (Optimized for Simultaneity) |      |

| MP261 5 µs, 0.002% Linearity, Low Droop S/H                   | 3-5  |

| MP270 1 µs, 0.005% Linearity S/H                              | 3-11 |

| MP271 1 µs, 0.003% Linearity S/H                              |      |

| MP272 350 ns, 0.01% Linearity S/H                             |      |

| MP282A Dual Simultaneous S/H with 1-bit Gain Ranging          |      |

|                                                               |      |

Sample-and-Hold Amplifiers

# **SELECTION GUIDE**

| MAJOR CHARACTERISTIC<br>OR APPLICATION REQ'MT |                     | SECONDARY<br>PARAMETER | RECOMMENDED<br>MODEL NO. | DATA SHEET<br>ON PAGE |

|-----------------------------------------------|---------------------|------------------------|--------------------------|-----------------------|

| Simultaneous<br>Multi-Channel<br>Sampling     | Droop Rate          | Acquisition<br>Time    | MP260                    | 3-5                   |

|                                               |                     |                        | MP261                    | 3-5                   |

| Multiple, Multiplexed<br>Inputs/Single<br>S/H | Acquisition<br>Time | High Linearity         | MP270                    | 3-11                  |

|                                               |                     | Linearity              | MP271                    | 3-15                  |

|                                               | Acquisition<br>Time | Medium<br>Linearity    | MP272                    | 3-27                  |

#### **GLOSSARY OF TERMS**

### SAMPLE AND HOLD AMPLIFIERS

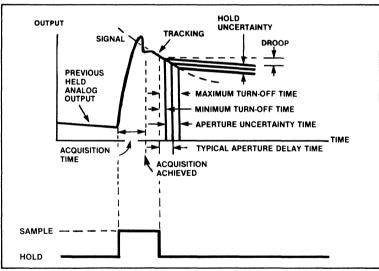

ACQUISITION TIME The time it takes the S/H amplifier to start tracking the input signal. It is measured as the maximum elapse time between application of the sample command and the point at which the output starts to track the input within a specified accuracy regardless of the previous state of the output or the magnitude or polarity of the input. See Figure 1.

**APERTURE DELAY TIME** The time delay between the HOLD command and the actual start of the HOLD mode. In reference to the SAMPLE mode this is called the turn-off time. See Figure 1.

**APERTURE UNCERTAINTY** A specification indicating how much the aperture delay time varies. It is measured as the difference between the maximum turn-off time and the minimum turn-off time. See Figure 1.

$$\triangle \mathsf{E} = \mathsf{E}_{\mathsf{s}} \mathsf{K} \log_{10} \left( \frac{\mathsf{t}_{\mathsf{s}} + \mathsf{t}_{\mathsf{h}}}{\mathsf{t}_{\mathsf{s}}} \right)$$

where:

- $\triangle E = Output voltage error$

- $E_s = Capacitor voltage change$

- $\ddot{K}$  = Empirical constant for Hold capacitor dielectric (K = 1.5 x 10<sup>4</sup> for polystyrene capacitor in MP270)

- $t_s =$  Sample time;  $t_h =$  Hold time

- Example: For a 20V step, a Sample time of 2  $\mu$ s, and a Hold time of 5  $\mu$ s,  $\triangle$ E = 1.5 mV.

#### DIGITAL CONTROL SPECIFICATIONS

These are specifications for interfacing the digital control signals to the S/H and include: the logic type, e.g., TTL; the sense of the logic, e.g., 1 = SAMPLE, 0 = HOLD; and the required speed of the rise or fall time between SAMPLE and HOLD modes.

**DISTORTION** Unwanted output signals generated as a result of non-linearities in the sample and hold.

Figure 1. S/H Amplifier Terminology.

**DIELECTRIC ABSORPTION ERROR** Dielectric absorption error is the decaying of the HOLD voltage on the HOLD capacitor due to the charge redistribution within the capacitor dielectric. This error occurs as a result of rapidly charging the HOLD capacitor and then disconnecting the charging source. The output voltage will decay according to the following relationship: **DROOP RATE** The maximum rate of change of the output voltage in the HOLD mode.

**FEEDTHROUGH REJECTION** The ratio, in db, of a specified input signal to the resultant output signal, during HOLD, over a stated frequency range.

FULL POWER BANDWIDTH The highest frequency at which an analog circuit will track a sinusoidal signal large enough to drive the output to its rated full-scale value at its maximum rated power. The equation is as follows:

$f = Slew Rate / 2 \pi e_{fs}$

where  $f = Full Power Bandwidth and e_{fs} = rated full scale output.$

**GAIN ACCURACY** The maximum amount that the actual voltage gain deviates from the nominal value expressed as a percentage of that nominal value. This takes into account the effects of temperature variations, power supply variations, and drift with time, if significant.

**INPUT IMPEDANCE** Specified as a nominal resistance in parallel with a capacitance value, given for the SAMPLE mode. If the HOLD mode impedance is significantly different it will also be given. Input impedance is given at maximum rated input voltage.

**INPUT SIGNAL RANGE** The acceptable input signal levels, over the full power bandwidth, for which the S/H will maintain rated linearity.

**LINEARITY** In the sample mode, linearity is a measure of how accurately the output tracks the analog input signal. In the hold mode, it refers to the pedestal offset which varies over the input signal range.

**OFFSET DRIFT** The worst case variation in output offset voltage due to changes in ambient temperature, power supply voltage, and drift with time.

**OUTPUT OFFSET VOLTAGE** The maximum value of output voltage observed when sampling zero input at a stated temperature and power supply voltage.

**OUTPUT VOLTAGE SWING** The rated nominal output voltage range into a specified minimum load impedance.

**OVERLOAD RECOVERY TIME** The time required for the circuit to return to linear operation, within a stated tolerance, after removal of a sustained input that was large enough to drive the circuit into complete saturation (i.e., a condition in which further increase in the input did not significantly increase the output).

**PEDESTAL OFFSET ERROR** An offset error caused by switching to the HOLD mode. It is affected by a number of parameters including the capacitance of the mode con-

trol switch, the HOLD mode command signal level, the analog input signal level and the sample rate. The pedestal offset error may be nonlinear.

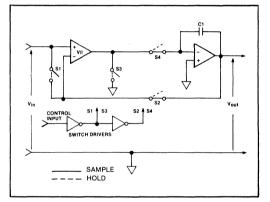

SAMPLE AND HOLD AMPLIFIER Sometimes called a track and hold amplifier, this is a circuit used to monitor a rapidly changing analog signal and, upon command, hold that signal level for processing by another circuit, typically an ADC. The S/H operates in two sequential modes. SAMPLE and HOLD, as determined by the state of a switch at the input to the amplifier which is controlled by an external digital control signal. In the SAMPLE mode the switch is closed, the input signal is connected to the amplifier and the output tracks it very closely. In the HOLD mode the switch is open, the input is disconnected from the amplifier and its level at the time of disconnect is maintained by a capacitor across the input. See Figure 2.

Figure 2. S/H Amplifier Block Diagram.

**SETTLING TIME** The maximum time required for the output to track the input to within the specified accuracy after a full range step change while in the SAMPLE mode.

**SLEW RATE** The maximum slew rate is the fastest rate of change of the output of the amplifier in the SAMPLE mode. The output changes most rapidly when a step change is applied at the input sufficient to drive the output from one end of its range to the other.

**SMALL SIGNAL BANDWIDTH** The maximum small signal bandwidth is the highest frequency at which an amplifier will track, to within 3 db of the low frequency response, a sinusoidal signal of less than the slew rate limited amplitude.

TURN OFF TIME See aperture delay time.

**VOLTAGE GAIN** The nominal ratio of output to input.

## MP260/MP261

Low Cost High Speed High Accuracy Sample & Hold Amplifiers

#### Description

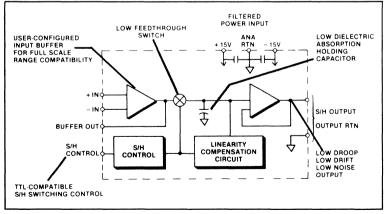

The Analogic MP260 and MP261 are low cost, highly accurate Sampleand-Hold (S/H) Amplifiers that sustain precise over-all system performance in applications requiring resolutions of up to 16-bits. The MP260 design is optimized for a time-shared S/H function at the input of a high speed (50 µs or faster conversion time) analog-to-digital converter. Its fast acquisition time of 5 µs and excellent linearity of 0.002% are representative of its superior performance. The MP261, with its extremely low droop rate of only 20µV/ms, is ideal for simultaneous sample-and-hold applications. For example, as many as 500 channels may be held and sequentially sampled (at 16-bit resolution, 30  $\mu$ s/sample, ± 10V full scale) before the last channel has drooped by only one significant bit  $(300 \mu V)!$ The rated performance of these units is maintained in the presence of harsh electromagnetic and electrostatic interference by shielding all components, including the low dielectric absorption hold capacitor, within a 1" x 2" Modupac<sup>TM</sup> metal case.

#### Features

#### MP260/MP261

- Excellent Linearity ± 0.002% FSR maximum

- Negligible Feedthrough 100 dB Rejection (0.001%)

- Low Aperture Uncertainty 1 nanosecond

- Complete Small Size Module 1" x 2" Modupac<sup>TM</sup> Case

- User-Selectable Input Configurations Buffer or Inverter

- Very Low Cost

#### MP260

#### Optimized for Time-Shared S/H Applications

- Fast Acquisition time 5 µs to ±0.003% Full Scale Step

- Low Pedestal Non-Linearity ± 0.003% max.

#### MP261

## Optimized for Simultaneous S/H Applications

- Very Low Droop rate 20 μV/rms max.

- Very Low Pedestal Non-Linearity

± 0.002% max.

#### Applications

- Low-Cost Simultaneous Sample & Hold Systems

- Automatic Test Equipment Systems

- Multi-Channel, Multi-Input-Level, 12- to 16-bit Data Acquisition Systems

- High Resolution, High Speed Data Acquisition Systems

- Audio Digitizing Systems.

Figure 1. MP260/MP261 Block Diagram.

#### **SPECIFICATIONS**

(All specifications guaranteed at 25°C unless otherwise noted)

#### SAMPLE MODE

(Input configured for Unity Gain Buffer) Full Scale Linear Input Voltage Range (FSR) ± 10V Without Damage  $\pm 15V$ Input Impedance 10°Ω || 10 pF Full Power Bandwidth 80 kHz, (MP261 - 20 kHz) Small Signal Bandwidth 1 MHz, (MP261 - 150 kHz) Slew Rate 10 V/µs, (MP261 — 2 V/µs) Non-Linearity ± 0.002% (max.) Noise (300 kHz bandwidth) 40 µV rms Gain  $1 \pm 0.02\%$ Total Harmonic Distortion (20-20 kHz sinusoid (tugni

0.002% max.

#### SAMPLE-TO-HOLD TRANSITION

Aperture Delay Time 50 ns Aperture Uncertainty 1 ns Switching Transient Decay Time to 0.003% 0.5 μs typ., 1 μs max.

#### HOLD MODE

Voltage Swing into 2K  $\Omega \parallel$  500 pF load)  $\pm$  10V min.

Impedance <1Ω @ dc

Hold Offset Pedestal 10 mV max; Proportional to input, (MP261 — 5 mV max; Constant for all input signals

Offset Pedestal Non-Linearity ( $\pm$  5V FSR)  $\pm$  0.001% max.

Offset Pedestal Non-Linearity ( $\pm$  10V FSR)  $\pm$  0.003% max., (MP261 —  $\pm$  0.002% max.) Offset @ 25°C (Externally Adjustable to Zero) 10 mV max., (MP261 — 5 mV max.)

**Offset Tempco** (20 typ., 0.2 max. μV/μs, (MP261 — (5 typ., 15 max.) μV/<sup>o</sup>C

Voltage Feedthrough Attenuation (20V p-p 100 kHz input) 100 dB typ., 96 dB min.

Droop Rate @ 25°C (typically doubles every 14°C)

0.02 typ., 0.2 max. μV/μs, (MP261 — 1 typ., 20 max. μV/ms) Noise (300 kHz bandwidth) 50  $\mu$ V rms Dielectric Absorption Error<sup>1</sup> ± 0.003% of input voltage change typ.

#### HOLD-TO-SAMPLE TRANSITION

Acquisition Time (Measured with 5K  $\Omega \parallel$  500 pF load) To within ±0.01% of 10V Step 3.5  $\mu$ s max. To within 0.003% of 10V Step 4.0  $\mu$ s max., (MP261 — 10  $\mu$ s max.) To within 0.01% of 20V Step 4.5  $\mu$ s max. To within 0.003% of 20V Step 5.0  $\mu$ s max., (MP261 — 15  $\mu$ s max.)

#### DIGITAL CONTROL INPUT

Logic Type TTL Compatible Sample Logic "1" (+ 3V min.) Hold Logic "0" (0.4V max.) Required Fall Time 10 ns max.

#### POWER, MECHANICAL, ENVIRONMENTAL

Power Supply  $\pm 15V \pm 3\%$  @ 12 mA nom. (Plus load current), (MP261 —  $\pm 15 \pm 3\%$  @ 6 mA nom. (Plus load current)

#### Operating Temperature

0°C to 70°C

**Relative Humidity (Up to 40°C) non-condensing** 0 to 95%

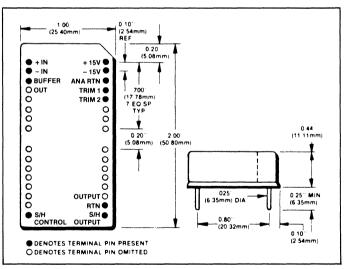

#### Modupac<sup>TM</sup> Dimensions

1" x 2" x 0.44" (25.4 x 50.8 x 11.2 mm)

Shielding RFI 6 sides; EMI 5 sides

<sup>1</sup>At Hold Time = Twice Sample Time \*\*Unless otherwise stated, percentage values apply to FSR of 20V.

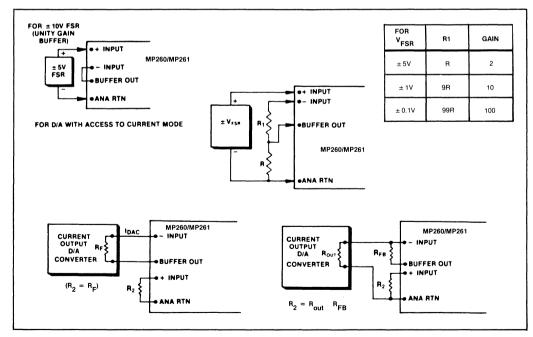

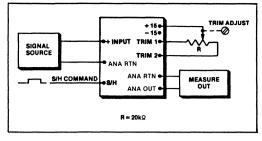

The high speed Input Buffer Amplifier feedback path is completed at the S/H pin terminals. This provides user capability for gain programming (Figure 1), or for replacing the amplifier stage in typical D/A converters. Performance specifications of the uncommited amplifier are furnished below.

Input Offset Voltage <6.0 mV, (MP261 — <2.0 mV)

Input Offset Current

<5 nA, (MP261 — <1 nA)</td>

Input Bias Current

<10 nA, (MP261 — < 2 nA)</td>

Input Impedance

10°Ω || 10 pF

Gain Bandwidth Product

3 MHz

Output Voltage Swing

± 10.5V min. ( $R_L ≥ 5 kΩ$ ) Common Mode Rejection Ration (CMRR) 85 dB min.

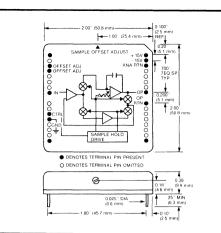

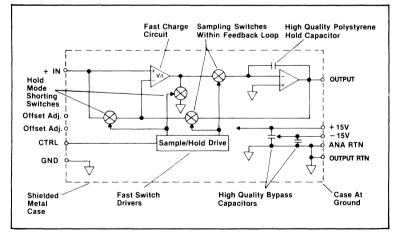

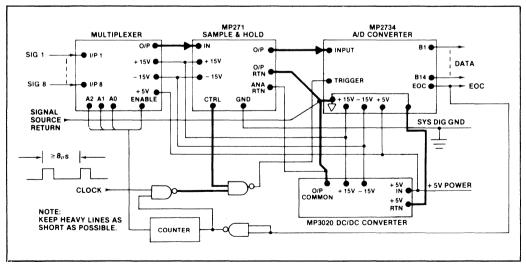

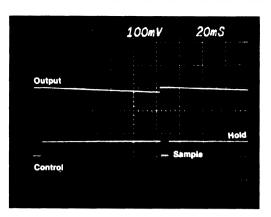

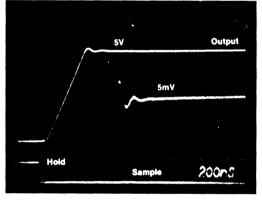

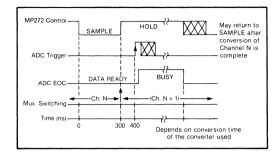

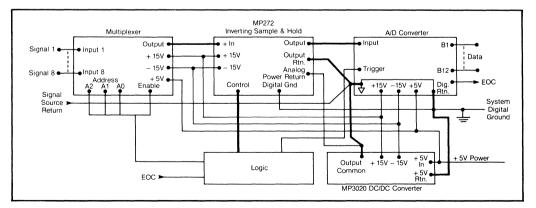

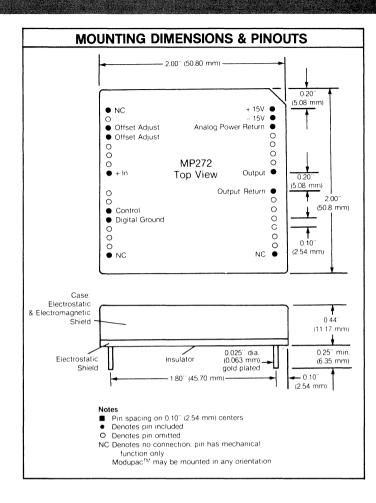

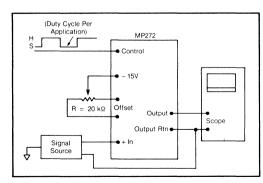

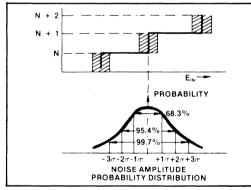

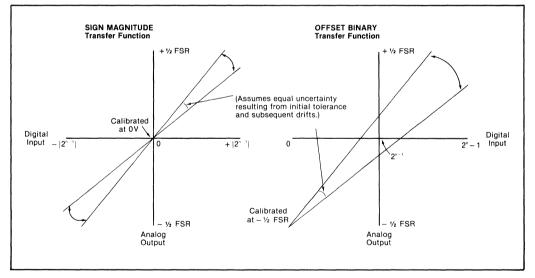

#### **Design Features**