ANALOG DEVICES

Architecture

# ADSP-2100 \_\_\_\_ User's \_\_\_ Manual \_\_\_

You may contact the Digital Signal Processing Division in the following ways.

- By contacting your local Analog Devices Sales Representative

- For Marketing information, call (617) 461-3881 in Norwood, Massachusetts, USA

- For Applications Engineering information, call (617) 461-3672 in Norwood, Massachusetts, USA

- The Norwood office Fax number is (617) 461-3010

- The Norwood office may also be reached by Telex: 924491

- TWX: 710/394-6577 Cables: ANALOG NORWOODMASS

- The DSP Division runs a Bulletin Board Service that can be reached at 300, 1200 or 2400 baud, no parity, 8 bits data, 1 stop bit by dialing: (617) 461-4258

- By writing to:

Analog Devices DSP Division One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 USA

### ADSP-2100 User's Manual

© 1989 Analog Devices, Inc. ALL RIGHTS RESERVED

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

PRINTED IN U.S.A.

FOURTH EDITION

## Literature

### **ADSP-2100 FAMILY MANUALS**

#### ADSP-2100 User's Manual/Architecture

Complete description of architecture and system interface.

#### ADSP-2100 Cross-Software Manual

Complete programmer's reference including optional C compiler.

#### **ADSP-2100 Emulator Manual** User's manual for the in-circuit Emulator.

**ADSP-2100 Evaluation Board Manual** A guide to the Evaluation Board including schematics for prototyping.

### ADSP-2101 User's Manual/Architecture (preliminary)

Complete description of architecture and system interface.

### **APPLICATIONS INFORMATION**

**ADSP-2100 Applications Handbook, Volume 1** Topics include arithmetic, filters, FFTs, LPC, modem algorithms.

**ADSP-2100 Family Applications Handbook, Volume 2** Topics include graphics, pulse-code modulation, multirate filters, DTMF.

#### **ADSP-2100 Family Applications Handbook, Volume 3** Topics include optimized and 2D FFTs, memory interface, multiprocessing, host interface, sonar beamforming.

### SPECIFICATIONS INFORMATION

ADSP-2100A/ADSP-2100 Data Sheet

ADSP-2101 Data Sheet (preliminary)

. .

## Contents 🗖

#### **CHAPTER 1 INTRODUCTION**

| 1.1 | GENERAL DESCRIPTION               | 1 – 1 |

|-----|-----------------------------------|-------|

| 1.2 | SUMMARY OF ADSP-2100 KEY FEATURES | 1 – 2 |

| 1.3 | INTERNAL ARCHITECTURE             | 1 – 5 |

| 1.4 | ADSP-2100 DEVELOPMENT SYSTEM      | 1 – 8 |

| 1.5 | MANUAL ORGANIZATION               | 1 – 9 |

#### **CHAPTER 2 COMPUTATIONAL UNITS**

| 2.1     | ARITHMETIC ON THE ADSP-2100     |        |

|---------|---------------------------------|--------|

| 2.1.1   | Binary String                   |        |

| 2.1.2   | Unsigned-Magnitude              |        |

| 2.1.3   | Signed Numbers: Twos-Complement |        |

| 2.1.4   | Fractional Representation: 1.15 |        |

| 2.1.5   | ALU Arithmetic                  |        |

| 2.1.6   | MAC Arithmetic                  |        |

| 2.1.7   | Shifter Arithmetic              |        |

| 2.1.8   | Summary                         |        |

| 2.2     | ARITHMETIC/LOGIC UNIT (ALU)     |        |

| 2.2.1   | ALU Block Diagram Discussion    |        |

| 2.2.2   | Standard Functions              |        |

| 2.2.3   | ALU Input/Output Registers      |        |

| 2.2.4   | Multiprecision Capability       |        |

| 2.2.5   | ALU Saturation Mode             |        |

| 2.2.6   | ALU Overflow Latch Mode         |        |

| 2.2.7   | Division                        |        |

| 2.2.8   | ALU Status                      |        |

| 2.3     | MULTIPLIER/ACCUMULATOR (MAC)    |        |

| 2.3.1   | MAC Block Diagram Discussion    |        |

| 2.3.2   | MAC Operations                  |        |

| 2.3.2.1 | Standard Functions              |        |

| 2.3.2.2 | Input Formats                   | 2 – 17 |

| 2.3.2.3 | MAC Input/Output Registers      |        |

| 2.3.2.4 | MR Register Operation           |        |

| 2.3.2.5 | MAC Overflow and Saturation      |        |

|---------|----------------------------------|--------|

| 2.3.2.6 | Rounding Mode                    |        |

| 2.4     | BARREL SHIFTER                   |        |

| 2.4.1   | Shifter Block Diagram Discussion | 2 – 21 |

| 2.4.2   | Shifter Operations               |        |

| 2.4.2.1 | Shifter Input/Output Registers   |        |

| 2.4.2.2 | Derive Block Exponent            |        |

| 2.4.2.3 | Immediate Shifts                 |        |

| 2.4.2.4 | Denormalize                      |        |

| 2.4.2.5 | Normalize                        | 2 – 32 |

### CHAPTER 3 DATA MOVES

| 3.1      | INTRODUCTION                           | 3 – 1 |

|----------|----------------------------------------|-------|

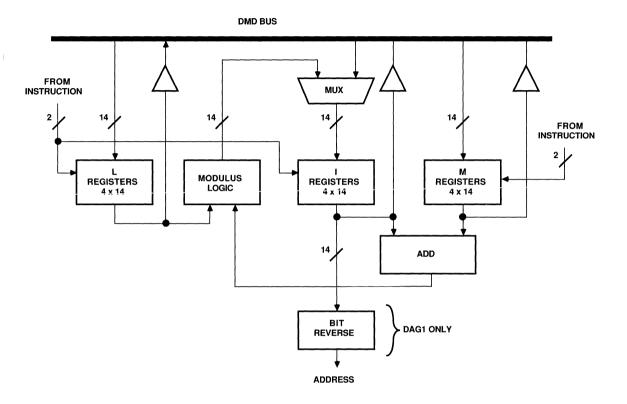

| 3.2      | DATA ADDRESS GENERATORS (DAGs)         | 3 – 1 |

| 3.2.1    | DAG Block Diagram Discussion           | 3 – 1 |

| 3.2.2    | Modulo Addressing                      | 3 – 3 |

| 3.2.2.1. | Circular Buffer Base Address Example 1 | 3–4   |

| 3.2.2.2. | Circular Buffer Base Address Example 2 | 3–4   |

| 3.2.2.3. | Circular Buffer Operation Example 1    | 3 – 4 |

| 3.2.2.4. | Circular Buffer Operation Example 2    | 3 – 5 |

| 3.2.3    | Bit-Reverse Addressing                 | 3 – 5 |

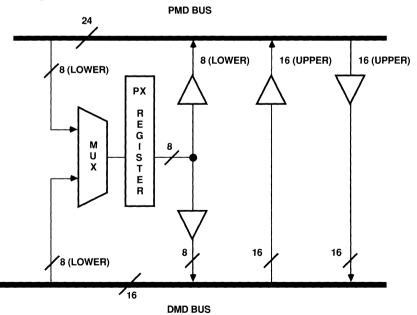

| 3.3      | PMD-DMD BUS EXCHANGE                   | 3 – 6 |

| 3.3.1    | PMD-DMD Block Diagram Discussion       | 3 – 6 |

#### CHAPTER 4 PROGRAM CONTROL

| 4.1     | INTRODUCTION                     | 4 – 1 |

|---------|----------------------------------|-------|

| 4.2     | PROGRAM SEQUENCER & STATUS       |       |

| 4.2.1   | Next Address Select Logic        | 4 – 1 |

| 4.2.2   | Program Counter and Stack        |       |

| 4.2.3   | Down Counter and Stack           |       |

| 4.2.4   | Loop Comparator and Stack        |       |

| 4.2.5   | Interrupt Controller             |       |

| 4.2.5.1 | Configuring Interrupts           |       |

| 4.2.5.2 | Interrupt Handling               |       |

| 4.2.6   | Sequencer Operations Illustrated |       |

| 4.2.6.1 | Linear Flow                      |       |

| 4.2.6.2 | JUMP Sequence                    |       |

| 4.2.6.3 | CALL Sequence                    |       |

| 4.2.6.4 | Interrupt Sequence               |       |

| 4.2.6.5 | DO UNTIL Loop                                    |  |

|---------|--------------------------------------------------|--|

| 4.2.6.6 | Register Indirect                                |  |

| 4.3     | STATUS REGISTERS AND STACK                       |  |

| 4.3.1   | Arithmetic Status Register (ASTAT)               |  |

| 4.3.2   | Stack Status Register (SSTAT)                    |  |

| 4.3.3   | Mode Status Register (MSTAT)                     |  |

| 4.3.4   | Interrupt Control Register (ICNTL)               |  |

| 4.3.5   | Interrupt Mask Register (IMASK)                  |  |

| 4.3.6   | Condition Logic                                  |  |

| 4.4     | INSTRUCTION CACHE                                |  |

| 4.4.1   | Cache Memory Operation                           |  |

| 4.4.2   | Cache Memory Monitor                             |  |

| 4.4.3   | Programmers' Guidelines For Cache Memory Usage . |  |

| 4.4.4   | Cache Memory Example                             |  |

### CHAPTER 5 SYSTEMINTERFACE

| 5.1   | OVERVIEW                         | 5 – 1 |

|-------|----------------------------------|-------|

| 5.1.1 | Note On Timing Diagrams          |       |

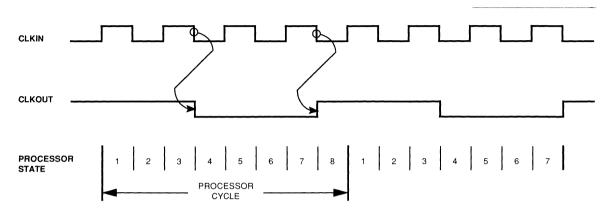

| 5.1.2 | Clock Signals & Processor States |       |

| 5.1.3 | Synchronization Delay            | 5-3   |

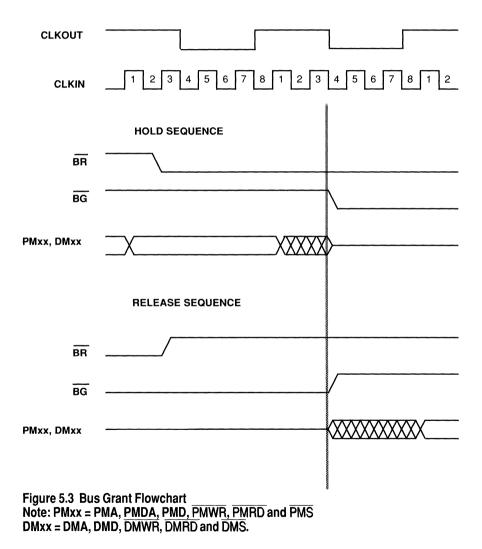

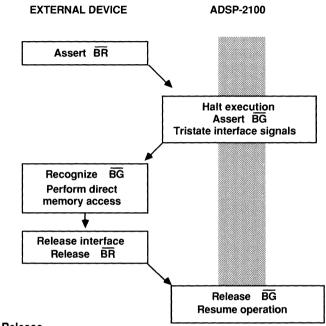

| 5.2   | BUS RÉQUEST / GRANT              | 5 – 3 |

| 5.2.1 | Bus Request at RESET             | 5 – 6 |

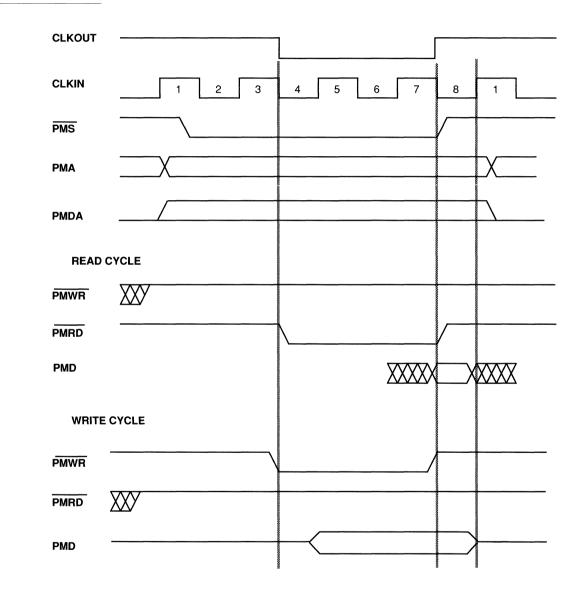

| 5.3   | PROGRAM MEMORY INTERFACE         | 5-6   |

| 5.3.1 | Program Memory Read Cycle        |       |

| 5.3.2 | Program Memory Write Cycle       | 5 – 7 |

| 5.4   | DATA MEMORY INTERFACE            | 5 – 9 |

| 5.4.1 | Data Memory Read Cycle5          | - 11  |

| 5.4.2 | Data Memory Write Cycle5         |       |

| 5.5   | CONTROLINTERFACE                 | - 12  |

| 5.5.1 | <u>RESE</u> T5                   | - 13  |

| 5.5.2 | HALT5                            | - 13  |

| 5.5.3 | TRAP5                            | - 14  |

| 5.6   | INTERRUPT OPERATION              | – 15  |

| 5.7   | PIN DESCRIPTION                  | – 17  |

#### **CHAPTER 6 INSTRUCTION SET OVERVIEW**

| 6.1     | INTRODUCTION                                  | 6 – 1  |

|---------|-----------------------------------------------|--------|

| 6.2     | INSTRUCTION TYPES                             | 6 – 2  |

| 6.2.1   | Multifunction Instructions                    |        |

| 6.2.1.1 | ALU/MAC with Data & Program Memory Read       |        |

| 6.2.1.2 | Data & Program Memory Read                    | 6 – 5  |

| 6.2.1.3 | Computation With Memory Read                  |        |

| 6.2.1.4 | Computation With Memory Write                 | 6-5    |

| 6.2.1.5 | Computation With Data Register Move           |        |

| 6.2.2   | ALU, MAC and Shifter Instructions             | 6 – 8  |

| 6.2.2.1 | ALU Group                                     |        |

| 6.2.2.2 | MAC Group                                     |        |

| 6.2.2.2 | Shifter Group                                 |        |

| 6.2.3   | MOVE: Read & Write                            | 6 – 12 |

| 6.2.4   | Program Flow Control                          |        |

| 6.2.5   | Miscellaneous Instructions                    | 6 – 14 |

| 6.3     | DATA STRUCTURES                               |        |

| 6.3.1   | Arrays                                        |        |

| 6.3.2   | Circular Arrays/Buffers                       | 6 – 16 |

| 6.3.3   | Ports & Memory-Mapping                        | 6 – 17 |

| 6.4     | PROGRAM EXAMPLE                               | 6 – 18 |

| 6.4.1   | Example Program: Setup Routine Discussion     |        |

| 6.4.2   | Example Program: Interrupt Routine Discussion | 6 – 20 |

|         |                                               |        |

#### APPENDIX A INSTRUCTION FORMATS

| A.1 | OPCODESA-1          |

|-----|---------------------|

| A.2 | ABBREVIATION CODING |

### APPENDIX B DIVISION EXCEPTIONS

| B.1   | DIVISION FUNDAMENTALS   | B – 1 |

|-------|-------------------------|-------|

| B.1.1 | Signed Division         | B-1   |

| B.1.2 | Unsigned Division       |       |

| B.1.3 | Output Formats          |       |

| B.1.4 |                         | B-3   |

| B.2   | ERROR ŠITUATIONS        |       |

| B.2.1 | Negative Divisor Error  | B-3   |

| B.2.2 | Unsigned Division Error |       |

| B.3   | SOFTWARESOLUTION        |       |

|       |                         |       |

INDEX

### FIGURES

| 1.1<br>1.2                                                                                  | ADSP-2100 System                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                                               | ALU Block Diagram2 - 5DIVS Block Diagram2 - 10DIVQ Block Diagram2 - 11Quotient Format2 - 12Multiplier/Accumulator Block Diagram2 - 14Multiplier Result Format2 - 17Shifter Block Diagram2 - 22                                                                                                                                                                                                                                  |

| 3.1<br>3.2                                                                                  | Data Address Generator Block Diagram                                                                                                                                                                                                                                                                                                                                                                                            |

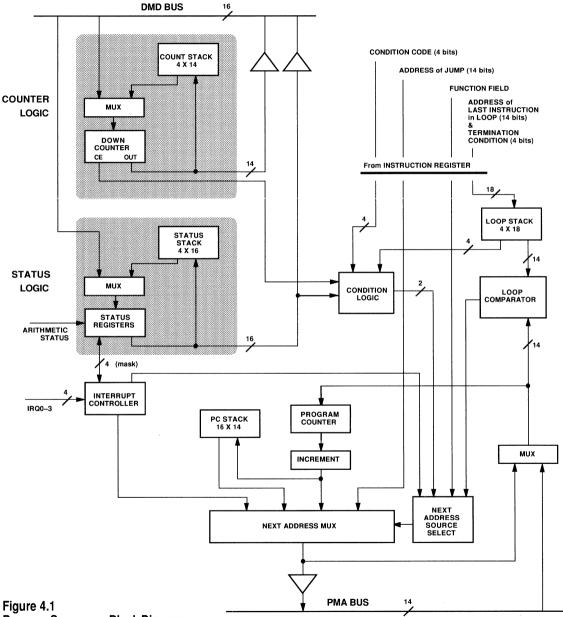

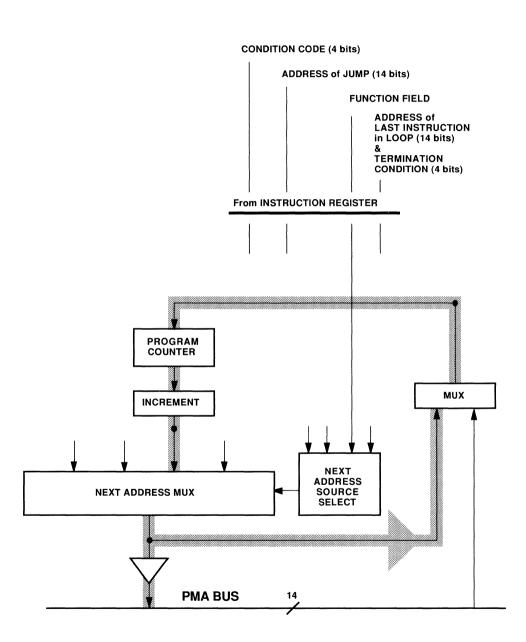

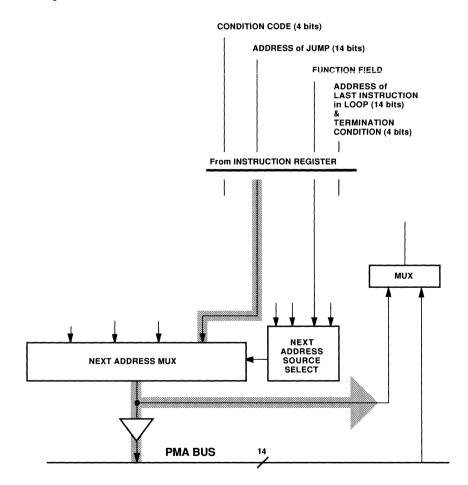

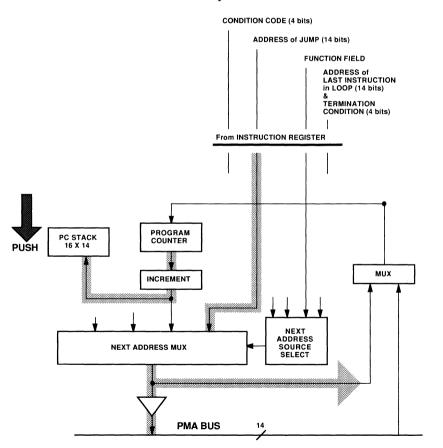

| 4.1<br>4.2<br>4.3<br>4.4                                                                    | Program Sequencer Block Diagram       4 - 2         Linear Flow       4 - 11         JUMP Sequence       4 - 12         CALL Sequence4 - 13       4 - 13                                                                                                                                                                                                                                                                        |

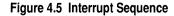

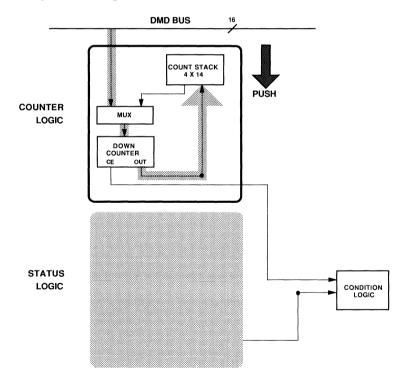

| 4.5<br>4.6A<br>4.6B                                                                         | Interrupt Sequence                                                                                                                                                                                                                                                                                                                                                                                                              |

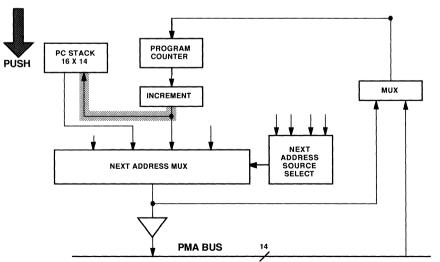

| 4.6C<br>4.6D                                                                                | DO UNTIL: Flow Inside Loop                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.6E<br>4.7<br>4.8                                                                          | DO UNTIL: Final Iteration                                                                                                                                                                                                                                                                                                                                                                                                       |

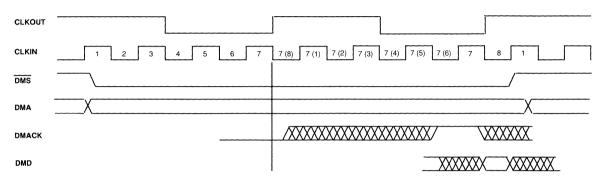

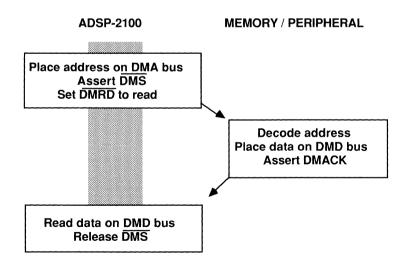

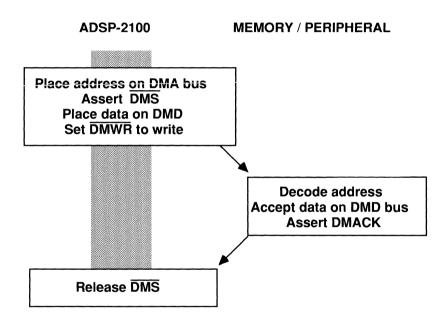

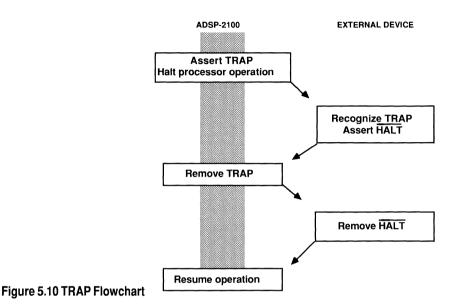

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13 | Basic System Configuration5 - 2Clock Signals & Processor States5 - 3Bus Grant Flowchart5 - 4Bus Hold / Release5 - 5Program Memory Read / Write5 - 8Data Memory Read / Write5 - 10Data Memory Read Extended by DMACK5 - 11Data Memory Read Flowchart5 - 11Data Memory Write Flowchart5 - 12TRAP Flowchart5 - 15Interrupt Service Timing5 - 16ADSP-2100 Pins, Top View, Pins Down5 - 21ADSP-2100 Pins, Bottom View, Pins Up5 - 22 |

| B.1                                                                                         | Listing B–1: Division Error RoutineB–6-8                                                                                                                                                                                                                                                                                                                                                                                        |

ix

#### TABLES

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Arithmetic Formats Used by the ADSP-2100<br>ALU Saturation Mode<br>MAC Saturation Instruction Effect<br>Shifter Array Characteristic<br>Shifter Exponent Detector Characteristic | 2 – 8<br>2 – 19<br>2 – 25 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 4.1                             | DO UNTIL Condition Logic                                                                                                                                                         | 4 – 6                     |

| 4.2                             | IMASK Entering Interrupt Service Routines                                                                                                                                        | 4 – 24                    |

| 4.3                             | IF Condition Logic                                                                                                                                                               | 4 – 25                    |

| 6.1                             | Summary of Valid Combinations For Multifunction Instructions                                                                                                                     |                           |

| 6.2                             | Multifunction Instructions                                                                                                                                                       |                           |

| 6.3                             | ALU Instructions                                                                                                                                                                 | 6 – 8                     |

| 6.4                             | MAC Instructions                                                                                                                                                                 |                           |

| 6.5                             | Shifter Instructions                                                                                                                                                             |                           |

| 6.6                             | ADSP-2100 Register Set: reg & dreg                                                                                                                                               |                           |

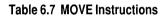

| 6.7                             | MOVE Instructions                                                                                                                                                                |                           |

| 6.8                             | Program Flow Control Instructions                                                                                                                                                | 6 – 14                    |

| 6.9                             | Miscellaneous Instructions                                                                                                                                                       |                           |

| 6.10                            | Program Example Listing 1, Main Routine & Constants File                                                                                                                         |                           |

| 6.11                            | Program Example Listing 2, Interrupt Routine                                                                                                                                     | 6 – 20                    |

#### 1.1 GENERAL DESCRIPTION

The ADSP-2100 is a programmable single-chip microprocessor optimized for digital signal processing (DSP) and other high-speed numeric processing applications. The ADSP-2100 incorporates computational units, data address generators and a program sequencer in one device, utilizing external data and program memories.

The ADSP-2100 contains three full-function and independent computational units: an arithmetic/logic unit, a multiplier/accumulator and a barrel shifter. The computational units process 16-bit data directly and provide for multiprecision computation.

Two dedicated data address generators and a powerful program sequencer supply addresses. The sequencer supports single-cycle conditional branching and executes program loops with zero overhead. Dual address generators allow the processor to output simultaneous addresses for dual operand fetches. Together the sequencer and data address generators allow computational operations to execute with maximum efficiency. With the ability to store data in both program and data memory, the ADSP-2100 is capable of fetching two operands on the same instruction cycle.

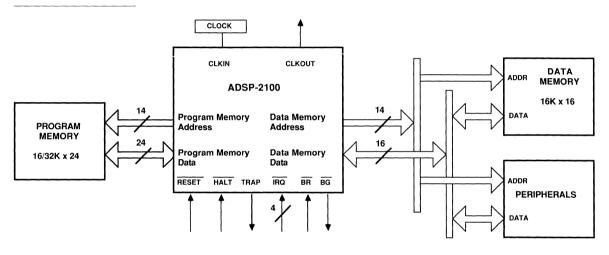

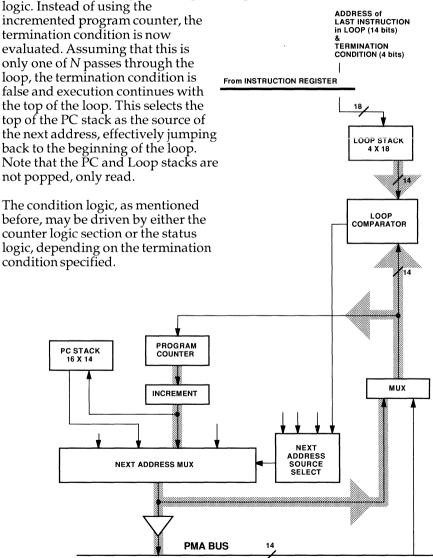

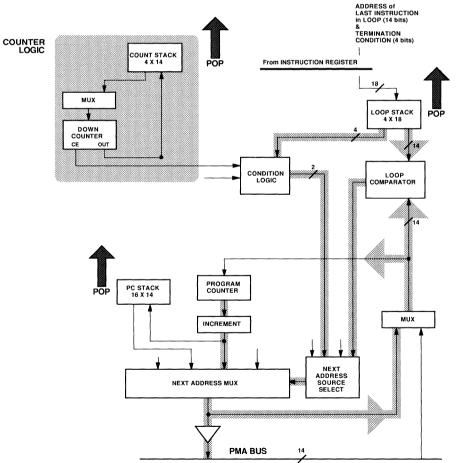

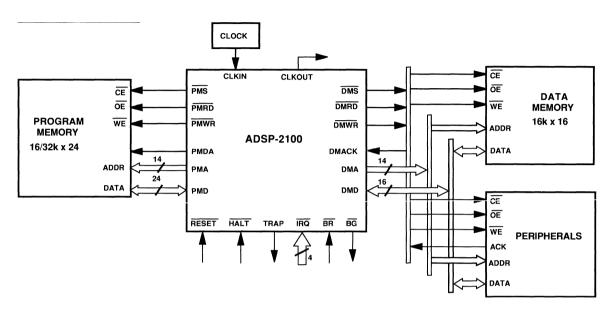

Figure 1.1 is a simplified representation of the ADSP-2100 in a system context. The figure shows the two external memories used by the processor. Program memory stores instructions and is also used to store data. Data memory stores only data. The data memory address space may be shared with memory-mapped peripherals, if desired. Both memories may be accessed by external devices, such as a system host, if desired. Figure 1.1 also shows the processor control interface signals, (RESET, HALT and TRAP) the four interrupt request lines, the bus request and bus grant lines (BR and BG) and the clock input (CLKIN) and output (CLKOUT). Complete interfacing information is presented in the chapter "System Interface."

The ADSP-2100 assembly language uses an algebraic syntax for ease of coding and readability. The sources and destinations of computations

and data movements are written explicitly in each assembly statement, eliminating cryptic assembler mnemonics. Each assembly statement, however, corresponds to a single 24-bit instruction, executable in one cycle.

The ADSP-2100 architecture rivals the performance of a board level solution implemented with bit-slice building blocks, without the difficulty of microcode programming.

Figure 1.1 ADSP-2100 System

### 1.2 SUMMARY OF ADSP-2100 KEY FEATURES

- Separate Program and Data Buses, Extended Off-Chip

- Single-Cycle Direct Access to 16K x 16 of Data Memory

- Dual Purpose Program Memory for Both Instruction and Data Storage

- Single-Cycle Direct Access to 16K x 24 (Expandable to 32K) of Program Memory

• Three Independent Computational Units:

Arithmetic/Logic Unit (ALU) Multiplier/Accumulator (MAC) Barrel Shifter

- Two Independent Data Address Generators

- Powerful Program Sequencer

- Internal Instruction Cache

- Provisions for Multiprecision Computation and Saturation Logic

- Single-Cycle Instruction Execution

- Multifunction Instructions

- Four External Interrupts

- 50 MHz Clock Speed

- 80 ns Cycle Time

- Low Power Standby Mode

- 100-Pin Grid Array Package

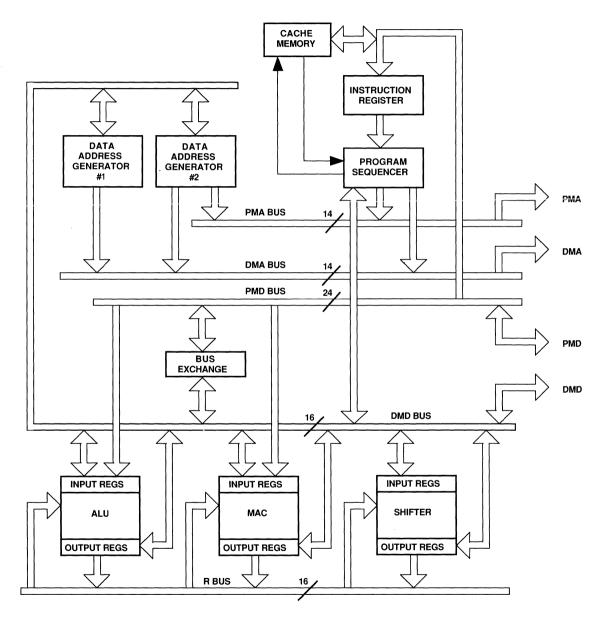

Figure 1.2 ADSP-2100 Internal Architecture

1 – 4

### 1.3 INTERNAL ARCHITECTURE

This section gives a broad overview of the ADSP-2100 internal architecture. The overview is based on Figure 1.2, on the facing page, which shows the architecture of the ADSP-2100. Each component is described in detail in the following chapters.

Component

Chapter / Section

| • | Arithmetic/logic unit       | 2.2 |

|---|-----------------------------|-----|

| • | Multiplier/accumulator      | 2.3 |

|   | Barrel shifter              | 2.4 |

| ٠ | Two data address generators | 3.2 |

| • | PMD-DMD bus exchange        | 3.3 |

| ٠ | Program sequencer           | 4.2 |

| ٠ | Status registers and stack  | 4.3 |

| • | Cachememory                 | 4.4 |

These components are supported by five internal buses.

- Program Memory Address (PMA) bus

- Program Memory Data (PMD) bus

- Data Memory Address (DMA) bus

- Data Memory Data (DMD) bus

- Result (R) bus (which interconnects the computational units)

The first four of these buses are extended off-chip for direct connection to external memories.

The program memory data (PMD) bus serves primarily to transfer instructions from off-chip memory to the internal instruction register. Instructions are fetched and loaded into the instruction register during one processor cycle and execute during the following cycle while the next instruction is being fetched. The instruction register introduces a single level of pipelining in the program flow. Instructions loaded into the instruction register are also written into the cache memory, described below.

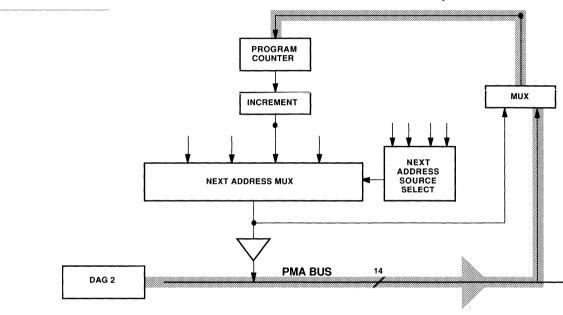

The next instruction address is generated by the program sequencer depending on the current instruction and internal processor status. This address is output onto the program memory address (PMA) bus. The program sequencer minimizes program flow overhead with features such as conditional branching, loop counters and zero-overhead looping.

1 – 5

The program memory address (PMA) bus is 14 bits wide allowing direct access of up to 16K words of instruction code and 16K words of data. The PMDA pin distinguishes between code and data access of program memory. The program memory data (PMD) bus is 24 bits wide to accommodate the 24-bit instruction width.

The data memory address (DMA) bus is 14 bits wide allowing direct access of up to 16K words of data. The data memory data (DMD) bus is 16 bits wide. The data memory data (DMD) bus provides a path for the contents of any register in the processor to be transferred to any other register or to any external data memory location in a single cycle. The data memory address comes from two sources: an absolute value specified in the instruction code (direct addressing) or the output of a data address generator (indirect addressing). Only indirect addressing is supported for data fetches via the program memory bus.

The program memory data (PMD) bus can also be used to transfer data to and from the computational units through direct paths or via the PMD-DMD bus exchange unit. The PMD-DMD bus exchange unit permits data to be passed from one bus to the other. It contains hardware to overcome the 8-bit width discrepancy between the two buses, if necessary.

The ADSP-2100 contains three computational blocks: an arithmetic/logic unit (ALU), a multiplier/accumulator (MAC) and a barrel shifter. Each unit functions independently of the others. All operate directly on 16-bit input data with provision for multiprecision operations. See the section "ADSP-2100 Arithmetic" in the next chapter.

All computational units contain a set of dedicated input and output registers. Computational operations generally take their operands from input registers and load the result into an output register. The registers act as a stopover point for data between the external memory and the computational circuitry, effectively introducing one pipeline level on input and one level on output. The computational units are arranged side by side instead of in a cascade fashion. To avoid excessive pipeline delays when a series of different operations are performed, the internal result (R) bus allows any of the output registers to be used directly as the input to another computation.

For a wide variety of calculations, it is desirable to fetch two operands at the same time; one from data memory and one from program memory. Fetching data from program memory, however, makes it impossible to fetch the next instruction on the same cycle. An additional cycle would be required to fetch the next instruction. To avoid this overhead, the ADSP-2100 incorporates an instruction cache which holds sixteen words. The benefit of the cache architecture is most apparent when executing a program loop totally contained in the cache memory. In this situation, the ADSP-2100 functions like a three bus system with an instruction fetch and two operand fetches taking place at the same time. Many algorithms can be coded in loops of sixteen instructions or less because of the efficiency and high-level syntax of the ADSP-2100 Assembly language. See the chapter "Instruction Set Overview."

Briefly, the cache functions in the following way. Every instruction loaded into the instruction register is also written into cache memory. As additional instructions are fetched, they overwrite the current contents of cache in a circular fashion. When the current instruction does a program memory data access, the cache automatically sources the instruction register if its contents are valid. Operation of the cache is completely transparent to user.

There are two independent data address generators (DAGs). Having two DAGs allows the simultaneous fetch of data stored in program and in data memory for executing dual-operand instructions in a single cycle. Data address generator one (DAG1) can supply addresses to the data memory only, but data address generator two (DAG2) can supply addresses to either the data memory or the program memory. Each DAG can handle linear addressing as well as modulo addressing for circular buffers.

With its multiple bus structure, the ADSP-2100 supports a high degree of operational parallelism. In a single cycle, the ADSP-2100 can fetch an instruction, compute the next instruction address, perform one or two data transfers, update one or two data address pointers and perform a computation. All instructions execute in a single cycle.

### 1.4 ADSP-2100 DEVELOPMENT SYSTEM

The ADSP-2100 is supported with a complete set of software and hardware development tools. The ADSP-2100 Development System consists of the Cross-Software Development System to aid the software design and the real-time Emulator to facilitate the debug cycle. An Evaluation Board is available for evaluating the ADSP-2100. It is also suitable for limited prototyping of hardware interfacing.

The Cross-Software Development System includes:

• System Builder

This module allows the designer to specify the amount of RAM and ROM available, the allocation of program and data memory and any memorymapped I/O ports for the target hardware environment. It uses high-level constructs to simplify this task. This specification is used by the other modules in the Cross-Software Development System.

• Assembler

This module assembles your source code and data modules. It supports the high-level syntax of the instruction set. To support modular code development, the Assembler provides flexible macro processing and include files. It provides a full range of diagnostics.

• Linker

The Linker links separately assembled modules. It maps the linked code and data output to the target system hardware, as specified by the System Builder output.

Simulator

This module performs an instruction-level simulation. The user interface is both interactive and symbolic. It supports a full symbolic assembly and disassembly. The simulator fully simulates the hardware configuration described by the System Builder module. It flags illegal operations and provides several displays of the internal operations of the ADSP-2100.

• PROM Splitter

This module reads the Linker output and generates PROM burner compatible files.

• C Compiler

The C Compiler reads ANSI (Draft Standard) C source and outputs ADSP-2100 source code ready to be assembled. It also supports inline assembler code.

• In-Circuit Emulator

The Emulator provides stand-alone real-time in-circuit emulation, using the ADSP-2100 in a self-emulation mode. The Emulator design provides execution with little or no degradation in processor performance. In addition, there are interfaces to external instrumentation. The Emulator virtually duplicates the Simulator's interactive and symbolic user interface.

For complete information on the Development System, consult the *ADSP-2100 Cross-Software Manual* and the *ADSP-2100 Emulator Manual*.

### 1.5 MANUAL ORGANIZATION

The *ADSP-2100 User's Manual* provides the information necessary for an engineer to understand and evaluate the operation of the ADSP-2100. Together with the *ADSP-2100 Data Sheet*, this manual provides all the information required to design a hardware system with the ADSP-2100. You must consult the *ADSP-2100 Cross-Software Manual* for complete information on programming the chip. Additional applications information may be found in the *ADSP-2100 Applications Handbook*, *Volume 1* and *Volume 2*.

Chapter 2, "Computational Units," describes the internal architecture and function of the ADSP-2100 computational units.

Chapter 3, "Data Moves," describes the data address generators and the PMD-DMD bus exchange units.

Chapter 4, "Program Control," describes the program sequencer, instruction cache and status words.

Chapter 5, "System Interface," describes the chip externally. It discusses all major interfaces to the ADSP-2100: the program memory (PM) interface, the data memory (DM) interface, the control interface and the interrupt lines. This chapter gives a functional description of the interfaces and their sequence of operations. For actual timing parameters, refer to the *ADSP-2100 Data Sheet*. A summary of the pin descriptions is given in this chapter.

Chapter 6, "Instruction Set Overview," is an overview of the ADSP-2100 instruction set. All instructions are grouped by major type. Detailed programmer's reference material is in the *ADSP-2100 Cross-Software Manual*; this chapter gives enough information for you to understand the capabilities and flexibility of the instruction set.

Appendix A, "Instruction Coding," shows the complete set of opcodes and gives the bit patterns for the choices for each field within the instruction word.

Appendix B, "Division Exceptions," discusses the details of signed and unsigned division.

This edition also includes an Index at the end of the book.

### 2.1 ARITHMETIC ON THE ADSP-2100

This chapter describes the architecture and function of the three computational units of the ADSP-2100: the arithmetic/logic unit, the multiplier/accumulator and the barrel shifter.

To better understand the detailed discussion of these units you should first understand how the ADSP-2100 handles binary arithmetic. The ADSP-2100 is a 16-bit, fixed-point machine. Special features support multiword arithmetic and block floating point. Most operations assume a twos-complement number while others assume an unsigned-magnitude number or a simple binary string. This section discusses the arithmetic used by each computational unit or operation.

#### 2.1.1 Binary String

This is the simplest form of binary notation. Sixteen bits are treated as a bit pattern. The best examples of computation using this format are the logical operations: NOT, AND, XOR. These ALU operations treat their operands as binary strings with no provision for sign bit or binary point placement.

#### 2.1.2 Unsigned-Magnitude

Unsigned magnitude binary numbers have no sign bit. They are frequently thought of as positive, having nearly twice the magnitude of a signed number of the same bit length. The lower words of multiword numbers are treated as unsigned-magnitude numbers.

#### 2.1.3 Signed Numbers: Twos-Complement

Twos-complement is one of the most common ways to represent signed binary numbers. It uses the MSB of a binary number as a sign bit. Twoscomplement provides a unique representation for zero, where some other formats have both a positive and negative zero. In twos-complement the largest negative magnitude is one LSB greater than the largest positive magnitude.

In discussions of ADSP-2100 arithmetic "signed" refers to twoscomplement. Most ADSP-2100 operations presume or support twoscomplement arithmetic. The ADSP-2100 does not use signed-magnitude formats.

#### 2.1.4 Fractional Representation: 1.15

A large number of DSP algorithms use sinusoidal and cosinusoidal values and coefficients. The ADSP-2100 is optimized for arithmetic values in a fractional binary format denoted by 1.15 ("one dot fifteen"). (Referred to in some contexts as 16.15.) This is a fixed-point format. Used with the MSB as a sign bit, the 1.15 means one sign bit and fifteen fractional bits representing values from –1 up to one LSB less than +1. In the ADSP-2100 the fractional notation and twos-complement always occur together.

#### 2.1.5 ALU Arithmetic

All operations on the ALU treat operands and results as simple 16-bit binary strings, except the signed division primitive (DIVS). Various status bits treat the results as signed: the overflow (AV) condition code, and the zero (AZ) and negative (AN) flags.

The logic of the overflow bit (AV) is based on twos-complement. It is set if the MSB changes in a manner not predicted by the signs of the operands and the nature of the operation. For example, adding two positive numbers must generate a positive result; a change in the sign bit signifies an overflow and sets AV. Adding a negative and a positive may result in either a negative or positive result, but cannot overflow.

The logic of the carry bit (AC) is based on unsigned-magnitude. It is set if a carry is generated from bit 16 (the MSB). The (AC) bit is most useful for the lower word portions of a multiword operation.

#### 2.1.6 MAC Arithmetic

The multiplier array itself produces results that are simple binary strings, but the inputs are "interpreted" according to the information given in the multiplication instruction itself (signed by signed, unsigned by unsigned, a mixture or round).

The number loaded into MR from the multiplier is assumed to be signed in that it is always sign-extended across the full 40 bit width of the MR register set.

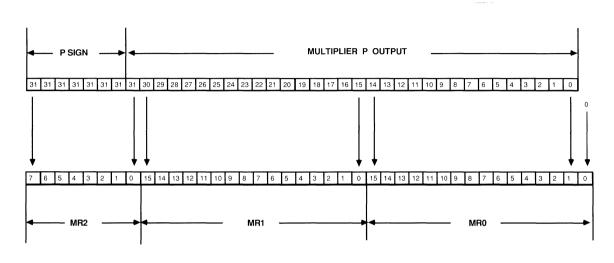

There is a built-in shift left that occurs between the multiplier product (P) and the multiplier result register (MR). Figure 2.6, in the MAC section of this chapter, shows this graphically. This shift occurs because the ADSP-2100 assumes that the operands are in 1.15 format. Without the shift the 32-bit result would be in 2.30 format. If a 2.30 value is rounded to 16-bits, the result would be 2.14, which is incompatible with 1.15. For this reason, the multiplier result is always shifted one bit to the left, producing a 1.31 result, which can be rounded to 1.15.

Therefore, to multiply twos-complement integers (16.0 not 1.15 format), you must compensate for the shift that occurs. Typically, this would mean shifting the result down (or right) one bit to get the correct 32-bit, twos-complement value. Since the MAC output register set stores 40 bits, this result is not lost and can be retrieved with the Shifter.

#### 2.1.7 Shifter Arithmetic

Many operations in the Shifter are explicitly geared to signed (twoscomplement) or unsigned values: Logical Shifts assume unsignedmagnitude or binary string values and Arithmetic Shifts assume twoscomplement.

The exponent logic assumes twos-complement numbers. The exponent logic supports block floating point, which is also based on twos-complement numbers.

#### 2.1.8 Summary

In addition to the numeric types described in this section, the ADSP-2100 C Compiler supports a form of 32-bit floating-point in which one 16-bit word is the exponent and the other 16-bit word is the mantissa. See the discussion in the C Compiler chapter of the *ADSP-2100 Cross-Software Manual*.

The table below summarizes some of the arithmetic characteristics of the ADSP-2100 computational units and operations.

| <b>O</b> <i>PERATION</i>                                                                                           | Arithmetic Formats                                                                                                                                           | Result                                                                                          |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| ALU                                                                                                                | Operands                                                                                                                                                     | кезин                                                                                           |

| Addition<br>Subtraction<br>Logical Operations<br>Division<br>ALU Overflow<br>ALU Carry Bit<br>ALU Saturation       | Signed or unsigned<br>Signed or unsigned<br>Binary string<br>Explicitly signed / unsigned<br>Signed<br>16-bit unsigned<br>Signed                             | Interpret flags<br>Interpret flags<br>same<br>same<br>same<br>same<br>same<br>same              |

| MAC                                                                                                                |                                                                                                                                                              |                                                                                                 |

| Multiplication (P)<br>Multiplication (MR)<br>Mult+Cum. Add<br>Mult+Cum. Subtract<br>MAC Overflow<br>MAC Saturation | 1.15 Explicitly signed/unsigned<br>1.15 Explicitly signed/unsigned<br>1.15 Explicitly signed/unsigned<br>1.15 Explicitly signed/unsigned<br>Signed<br>Signed | 32-bits<br>2.30 shifted to 1.31<br>2.30 shifted to 1.31<br>2.30 shifted to 1.31<br>same<br>same |

| Shifter                                                                                                            |                                                                                                                                                              |                                                                                                 |

| Logical Shift<br>Arithmetic Shift<br>Exponent Detection                                                            | Unsigned / binary string<br>Signed<br>Signed                                                                                                                 | same<br>same<br>same                                                                            |

#### Table 2.1 Arithmetic Formats Used by the ADSP-2100

#### 2.2 ARITHMETIC/LOGIC UNIT (ALU)

The Arithmetic/Logic Unit (ALU) provides a standard set of arithmetic and logical functions. The arithmetic functions are add, subtract, negate, increment, decrement and absolute value. These are supplemented by two division primitives with which multiple cycle division can be constructed. The logic functions are AND, OR, XOR (exclusive OR) and NOT.

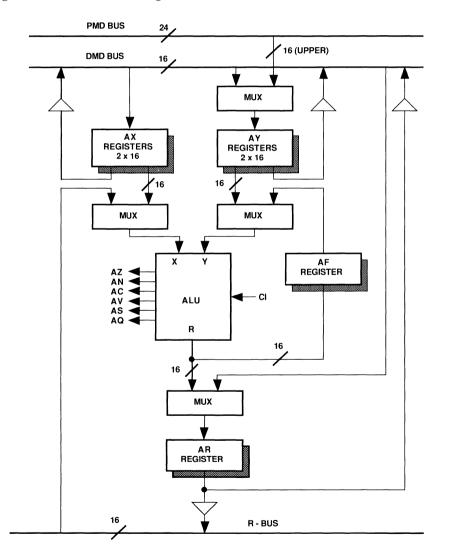

### 2.2.1 ALU Block Diagram Discussion

Figure 2.1 shows a block diagram of the ALU.

Figure 2.1 ALU Block Diagram

The ALU is 16 bits wide with two 16-bit input ports, X and Y, and one output port, R. The ALU accepts a carry-in signal (CI) which is the carry bit from the processor arithmetic status register (ASTAT). The ALU generates six status signals: the zero (AZ) status, the negative (AN) status, the carry (AC) status, the overflow (AV) status, the X-input sign (AS) status, and the quotient (AQ) status. All arithmetic status signals are latched into the arithmetic status register (ASTAT) at the end of the cycle.

The X input port of the ALU can accept data from two sources: the AX register file or the result (R) bus. The R bus connects the output registers of all the computational units, permitting them to be used as input operands directly. The AX register file is dedicated to the X input port and consists of two registers, AX0 and AX1. These AX registers are readable and writable from the DMD bus. The AX register file outputs are dual-ported so that one register can provide input to the ALU while either one simultaneously drives the DMD bus.

The Y input port of the ALU can also accept data from two sources: the AY register file and the ALU feedback (AF) register. The AY register file is dedicated to the Y input port and consists of two registers, AY0 and AY1. These registers are readable and writable from the DMD bus and writable from the PMD bus. The ADSP-2100 instruction set also provides for reading these registers over the PMD bus, but there is no direct connection; this operation uses the DMD-PMD bus exchange unit. The AY register file outputs are also dual-ported: one AY register can provide input to the ALU while either one simultaneously drives the DMD bus.

The output of the ALU is loaded into either the ALU feedback (AF) register or the ALU result (AR) register. The AF register is an ALU internal register which allows the ALU result to be used directly as the ALU Y input. The AR register can drive both the DMD bus and the R bus. It is also loadable directly from the DMD bus.

All the registers surrounding the ALU can be both read and written in the same cycle. Registers are read at the beginning of the cycle and written at the end of the cycle. All register reads, therefore, read values loaded at the end of a previous cycle. A new value written to a register cannot be read out until a subsequent cycle. This allows an input register to provide an operand to the ALU at the beginning of the cycle and be updated with the next operand from memory at the end of the same cycle. It also allows a

result register to be stored in memory and updated with a new result in the same cycle. See the discussion of "Multifunction Instructions" in the chapter "Instruction Set Overview" for an illustration of this same-cycle read and write.

The ALU section contains a duplicate bank of registers, shown in Figure 2.1 as a "shadow" behind the primary registers. There are actually two sets of AR, AF, AX, and AY register files. Only one bank is accessible at a time. The additional bank of registers can be activated during an interrupt service routine for extremely fast context switching. A new task, such as an interrupt service routine, can be executed without transferring current states to storage.

The selection of the primary or alternate bank of registers is controlled by a bit in the processor mode status register (MSTAT). Toggling this bit switches back and forth between the two register banks.

### 2.2.2 Standard Functions

The standard functions performed by the ALU are listed below with a brief comment.

| $\mathbf{R} = \mathbf{X} + \mathbf{Y}$                   | Add X and Y operands                        |

|----------------------------------------------------------|---------------------------------------------|

| $\mathbf{R} = \mathbf{X} + \mathbf{Y} + \mathbf{CI}$     | Add X and Y operands and carry-in bit       |

| R = X - Y                                                | Subtract Y from X operand                   |

| $\mathbf{R} = \mathbf{X} - \mathbf{Y} + \mathbf{CI} - 1$ | Subtract Y from X operand with "borrow"     |

| R = Y - X                                                | Subtract X from Y operand                   |

| R = Y - X + CI - 1                                       | Subtract X from Y operand with "borrow"     |

| R = -X                                                   | Negate X operand ( <i>twos-complement</i> ) |

| $\mathbf{R} = -\mathbf{Y}$                               | Negate Y operand (twos-complement)          |

| $\mathbf{R} = \mathbf{Y} + 1$                            | Increment Y operand                         |

| $\mathbf{R} = \mathbf{Y} - 1$                            | Decrement Y operand                         |

| R = PASS X                                               | Pass X operand to result unchanged          |

| R = PASS Y                                               | Pass Y operand to result unchanged          |

| $\mathbf{R} = 0 \ (PASS \ 0)$                            | Clear result to zero                        |

| R = ABS X                                                | Absolute value of X operand                 |

| R = X AND Y                                              | Logical AND of X and Y operands             |

| R = X OR Y                                               | Logical OR of X and Y operands              |

| R = X XOR Y                                              | Logical Exclusive OR of X and Y operands    |

| R = NOT X                                                | Logical NOT of X operand (ones-complement)  |

| R = NOT Y                                                | Logical NOT of Y operand (ones-complement)  |

|                                                          |                                             |

### 2.2.3 ALU Input/Output Registers

The sources of ALU input and output registers are shown below.

| Source for X input port | Source for Y input port | Destination for R |

|-------------------------|-------------------------|-------------------|

|                         |                         | output port       |

| AX0, AX1                | AY0, AY1                | AR                |

| AR                      | AF                      | AF                |

| MR0, MR1, MR2           |                         |                   |

| SR0, SR1                |                         |                   |

MR0, MR1 and MR2 are Multiplier/Accumulator result registers; SR0 and SR1 are Shifter result registers.

#### 2.2.4 Multiprecision Capability

Multiprecision operations are supported in the ALU with the carry-in (CI) signal and ALU carry (AC) status bit. The carry-in signal is the AC status bit that was generated by a previous ALU operation. The "add with carry" (+CI) operation is intended for adding the upper portions of multiprecision numbers. The "subtract with borrow" (CI - 1 is effectively a "borrow") operation is intended for subtracting the upper portions of multiprecision numbers.

#### 2.2.5 ALU Saturation Mode

The AR register has an optional saturation mode of operation which automatically sets it to plus or minus the maximum value if an ALU result overflows or underflows. This feature is a "mode" and is enabled by setting a bit in the processor mode status register (MSTAT). When enabled, the value loaded into AR during an ALU operation depends on the state of the overflow and carry status generated by the ALU on that cycle. The following table summarizes the loading of the AR when the saturation mode is enabled.

| Overflow (AV) | Carry (AC) | AR Contents        |                     |

|---------------|------------|--------------------|---------------------|

| 0             | 0          | ALUOutput          |                     |

| 0             | 1          | ALUOutput          |                     |

| 1             | 0          | 011111111111111111 | full-scale positive |

| 1             | 1          | 10000000000000000  | full-scale negative |

Table 2.2 Saturation Mode

The operation of the ALU saturation mode is in contrast to the Multiplier/ Accumulator saturation ability, which is enabled only on an instruction by instruction basis. For the ALU, enabling saturation means that all subsequent operations are processed this way.

### 2.2.6 ALU Overflow Latch Mode

The ALU overflow latch mode, enabled by a bit in the processor mode status register (MSTAT), causes the AV bit to "stick" once it is set. In this mode, when an ALU overflow occurs, AV will be set and remain set, even if subsequent ALU operations do not generate overflows. In this mode, AV can only be cleared by writing a zero to it directly from the DMD bus.

### 2.2.7 Division

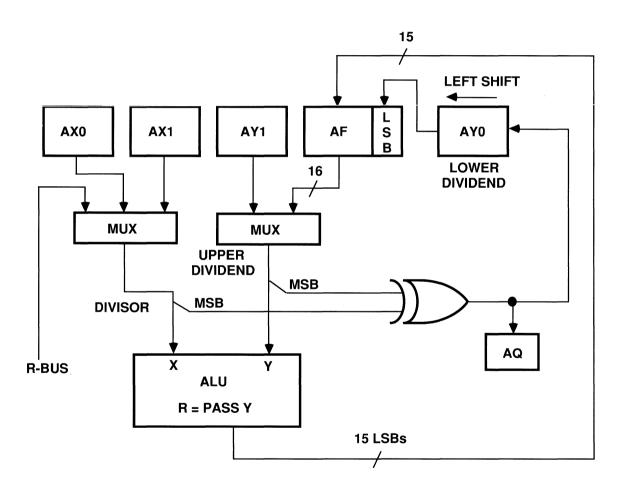

The ALU section supports division. The divide function is achieved with additional shift circuitry not shown in Figure 2.1, the block diagram. Division is accomplished with two special divide primitives. These are used to implement a non-restoring conditional add-subtract division algorithm. The division can be either signed or unsigned, however, the dividend and divisor must both be of the same type. Appendix B details various exceptions to the normal division operation as described in this section.

A single precision divide, with a 32-bit dividend (numerator) and a 16-bit divisor (denominator), yielding 16-bit quotient, executes in 16 cycles. Higher precision dividends can also be calculated. The divisor can be stored in AX0, AX1 or any of the R registers. The upper half of a signed dividend can be in either AY1 or AF. The upper half of an unsigned dividend must be in AF. The lower half of any dividend must be in AY0. At the end of the divide operation, the quotient will be in AY0.

The first of the two primitive instructions "divide-sign (DIVS)" is executed at the beginning of the division when dividing signed numbers. This operation computes the sign bit of the quotient by performing an exclusive-OR of the sign bits of the divisor and the dividend. The AY0 register is shifted one place so that the computed sign bit is moved into the LSB position. The computed sign bit is also loaded into the AQ bit of the arithmetic status register. The MSB of AY0 shifts into the LSB position of AF, and the upper 15 bits of AF are loaded with the lower 15 R bits from the ALU, which simply passes the Y input value straight through to the R output. The net effect is to left shift the AF-AY0 register pair and move the quotient sign bit into the LSB position. The operation of DIVS is illustrated in Figure 2.2 (on the following page).

2-9

When dividing unsigned numbers, the DIVS operation is not used. Instead, the AQ bit in the arithmetic status register (ASTAT) should be initialized to zero by manually clearing it. The AQ bit indicates to the following operations that the quotient should be assumed positive.

#### Figure 2.2 DIVS Operation

2 – 10

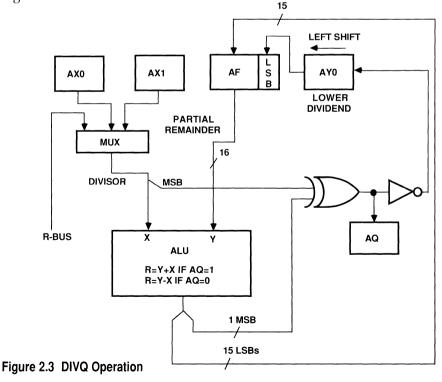

The second primitive instruction is the "divide-quotient (DIVQ)" operation which generates one bit of quotient at a time and is executed repeatedly to compute the remaining quotient bits. For unsigned single precision divides, the DIVQ instruction is executed 16 times to produce 16 quotient bits. For signed single precision divides, the DIVQ instruction is executed 15 times after the sign bit is computed by the DIVS operation. DIVQ instruction shifts the AY0 register left by one bit so that the new quotient bit can be moved into the LSB position. The status of the AQ bit generated from the previous operation determines the ALU operation to calculate the partial remainder. If AQ = 1, the ALU adds the divisor to the partial remainder in AF. If AQ = 0, the ALU subtracts the divisor from the partial remainder in AF. The ALU output R is offset loaded into AF just as with the DIVS operation. The AQ bit is computed as the exclusive-OR of the divisor MSB and the ALU output MSB, and the quotient bit is this value inverted. The quotient bit is loaded into the LSB of the AY0 register which is also shifted left by one bit. The DIVQ operation is illustrated in Figure 2.3.

2 – 11

The format of the quotient for any numeric representation can be determined by the format of the dividend and divisor. Let NL represent the number of bits to the left of the binary point, and NR represent the number of bits to the right of the binary point of the dividend; DL represent the number of bits to the left of the binary point, and DR represent the number of bits to the right of the binary point, and DR represent the number of bits to the right of the binary point of the divisor; then the quotient has NL–DL+1 bits to the left of the binary point and NR–DR–1 bits to the right of the binary point.

Some format manipulation may be necessary to guarantee the validity of the quotient. For example, if both operands are signed and fully fractional (dividend in 1.31 format and divisor in 1.15 format) the result is fully fractional (in 1.15 format) and therefore the dividend must be smaller than the divisor for a valid result. To divide two integers (dividend in 32.0 format and divisor in 16.0 format) and produce an integer quotient (in 16.0 format), you must shift the dividend one bit to the left (into 31.1 format) before dividing. Additional discussion and code examples can be found in the *ADSP-2100 Applications Handbook, Volume* 1.

| Dividend | BBBBB.BBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBB                |                |

|----------|-------------------------------------------------------|----------------|

|          | NL bits                                               | NR bits        |

| Divisor  | BB.BBBBBB                                             | BBBBBBBB       |

|          | DL bits                                               | DR bits        |

| Quotient | uotient <u>BBBB.BBBBBBBBBBBBB</u> BBBBBBBBBBBBBBBBBBB |                |

|          | (NL-DL+1) bits                                        | (NR-DR-1) bits |

#### Figure 2.4 Quotient Format

The algorithm overflows if the result cannot be represented in the format of the quotient as calculated above or when the divisor is zero or less than the dividend.

### 2.2.8 ALU Status

The ALU status bits in the ASTAT register are defined below. Complete information about the ASTAT register and specific bit mnemonics and positions is provided in Chapter 4, "Program Control."

| Flag | Name     | Definition                                                                                             |

|------|----------|--------------------------------------------------------------------------------------------------------|

| AZ   | Zero     | Logical NOR of all the bits in the ALU result register.<br>True if ALU output equals zero.             |

| AN   | Negative | Sign bit of the ALU result. True if the ALU output is negative.                                        |

| AV   | Overflow | Exclusive-OR of the carry outputs of the two most significant adder stages. True if the ALU overflows. |

| AC   | Carry    | Carry output from the most significant adder stage.                                                    |

| AS   | Sign     | Sign bit of the ALU X input port. Affected only by the ABS instruction.                                |

| AQ   | Quotient | Quotient bit generated only by the DIVS and DIVQ instructions.                                         |

### 2.3 MULTIPLIER/ACCUMULATOR (MAC)

The Multiplier/Accumulator (MAC) provides high-speed multiplication, multiplication with cumulative addition, multiplication with cumulative subtraction and clear-to-zero functions. A feedback function allows part of the accumulator output to be directly used as one of the multiplicands on the next cycle.

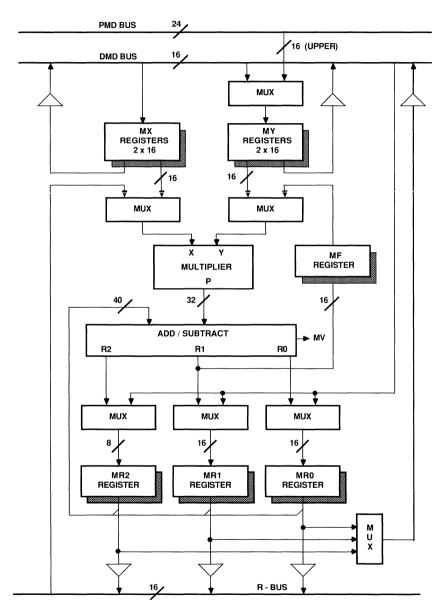

#### 2.3.1 MAC Block Diagram Discussion

Figure 2.5, on the following page, shows a block diagram of the multiplier/accumulator section.

The multiplier has two 16-bit input ports X and Y, and a 32-bit product output port P. The 32-bit product is passed to a 40-bit adder/subtractor which adds or subtracts the new product from the content of the multiplier result (MR) register. The MR register is 40-bits wide. In this manual, we refer to the entire register as MR. The register actually consists of three smaller registers: MR0 and MR1 which are 16 bits wide and MR2 which is 8 bits wide. The adder/subtractor is greater than 32 bits to allow for intermediate overflow in a series of multiply/accumulate operations. The multiply overflow (MV) status bit is set when the accumulator has overflowed beyond the 32-bit boundary, that is, when there are significant (non-sign) bits in the top nine bits of the MR register (based on twos-complement arithmetic).

Figure 2.5 Multiplier/Accumulator Block Diagram

2 – 14

The input/output registers of the MAC section are similar to the ALU.

The X input port can accept data from either the MX register file or from any register on the result (R) bus. The R bus connects the output registers of all the computational units, permitting them to be used as input operands directly. There are two registers in the MX register file, MX0 and MX1. These registers can be read and written from the DMD bus. The MX register file outputs are dual-ported so that a single register can drive the DMD bus at the same time it supplies operands to the multiplier.

The Y input port can accept data from either the MY register file or the MF register. The MY register file has two registers, MY0 and MY1; these registers can be read and written from the DMD bus and written from the PMD bus. The ADSP-2100 instruction set also provides for reading these registers over the PMD bus, but there is no direct connection; this operation uses the DMD-PMD bus exchange unit. The MY register file outputs are also dual-ported so that a single register can drive the DMD bus at the same time it supplies operands to the multiplier.

The output of the adder/subtractor goes to either the MF register or the MR register. The MF register is a feedback register which allows bits 16–31 of the result to be used directly as the multiplier Y input on a subsequent cycle. The 40-bit adder/subtractor register (MR) is divided into three sections: MR2, MR1, and MR0. Each of these registers can be preloaded directly from the DMD bus and output to either the DMD bus or the R bus.

All the registers surrounding the MAC can be both read and written in the same cycle. Registers are read at the beginning of the cycle and written at the end of the cycle. All register reads, therefore, read values loaded at the end of a previous cycle. A new value written to a register cannot be read out until a subsequent cycle. This allows an input register to provide an operand to the MAC at the beginning of the cycle and be updated with the next operand from memory at the end of the same cycle. It also allows a result register to be stored in memory and updated with a new result in the same cycle. See the discussion of "Multifunction Instructions" in the chapter "Instruction Set Overview" for an illustration of this same-cycle read and write.

The MAC section contains a duplicate bank of registers, shown in Figure 2.5 as a "shadow" behind the primary registers. There are actually two sets of MR, MF, MX, and MY register files. Only one bank is accessible at a

time. The additional bank of registers can be activated during an interrupt service routine for extremely fast context switching. A new task, such as an interrupt service routine, can be executed without transferring current states to storage.

The selection of the primary or alternate bank of registers is controlled by a bit in the processor mode status register (MSTAT). Toggling this bit switches back and forth between the two register banks.

#### 2.3.2 MAC Operations

This section explains the functions of the MAC, its input formats and its handling of overflow and saturation.

#### 2.3.2.1 Standard Functions

The functions performed by the MAC are:

| X*Y    | Multiply X and Y operands                               |

|--------|---------------------------------------------------------|

| MR+X*Y | Multiply X and Y operands and add result to MR register |

| MR-X*Y | Multiply X and Y operands and subtract result from MR   |

|        | register                                                |

| 0      | Clear result (MR) to zero                               |

In performing a multiply/accumulate, the multiplier output P is fed into a 40-bit adder/subtractor which adds or subtracts the new product with the current contents of the MR register to form the final 40-bit result R. The 32-bit P output is format adjusted, that is, sign-extended and shifted one bit to the left before being added to MR. Bit 31 of P lines up with bit 32 of MR (which is bit 0 of MR2) and bit 0 of P lines up with bit 1 of MR (which is bit 1 of MR0). The LSB is zero-filled. The multiplier result format is shown in Figure 2.6.

This is usually a more convenient format because it eliminates the redundant sign bit from the lower 32 bits of the result when multiplying signed numbers. This justification is maintained even if one or both of the inputs are in unsigned format.

Figure 2.6 Multiplier Result Format

### 2.3.2.2 Input Formats

To facilitate multiprecision multiplications, the multiplier accepts X and Y inputs represented in any combination of signed twos-complement format and unsigned format.

| X input  |   | Y input  |

|----------|---|----------|

| signed   | х | signed   |

| unsigned | Х | signed   |

| signed   | Х | unsigned |

| unsigned | х | unsigned |

The input formats are specified as part of the instruction. These are dynamically selectable each time the multiplier is used.

The (signed x signed) mode is used when multiplying two signed single precision numbers or the two upper portions of two signed multiprecision numbers.

2 – 17

The (unsigned x signed) and (signed x unsigned) modes are used when multiplying the upper portion of a signed multiprecision number with the lower portion of another or when multiplying a signed single precision number by an unsigned single precision number.

The (unsigned x unsigned) mode is used when multiplying unsigned single precision numbers or the non-upper portions of two signed multiprecision numbers.

### 2.3.2.3 MAC Input/Output Registers

The sources of MAC input and output are:

| Source for X input port | Source for Y input port | Destination for R output |

|-------------------------|-------------------------|--------------------------|

|                         |                         | port                     |

| MX0, MX1                | MY0, MY1                | MR (MR2, MR1, MR0)       |

| AR                      | MF                      | MF                       |

| MR0, MR1, MR2           |                         |                          |

| SR0, SR1                |                         |                          |

### 2.3.2.4 MR Register Operation

As described, and shown on the block diagram, the MR register is divided into three sections: MR0 (bits 0-15), MR1 (bits 16-31), and MR2 (bits 32-39). Each of these registers can be preloaded from the DMD bus and output to the R bus or the DMD bus.

The 8-bit MR2 register is tied to the lower 8 bits of these buses. When MR2 is output onto the DMD bus or the R bus, it is sign extended to form a 16-bit value. MR2 also has an automatic sign extend capability. When MR1 is preloaded from the DMD bus, every bit in MR2 will be set equal to the sign bit (MSB) of MR1, so that MR2 appears as an extension of MR1. To preload the MR2 register with a value other than MR1's sign extension, you must load MR2 after MR1 has been loaded.

### 2.3.2.5 MAC Overflow and Saturation

The adder/subtractor generates an overflow status signal (MV) which is loaded into the processor arithmetic status (ASTAT) every time a MAC operation is executed. The MV bit is set when the accumulator result, interpreted as a twos-complement number, crosses the 32-bit boundary. That is, MV is set if the accumulator result crosses the MR1/MR2 boundary. Another way of stating this is that the MV bit is set if the upper nine bits of the result register MR are not all ones or all zeros.

The MR register has a saturation capability which sets MR to plus or minus the maximum value if an overflow or underflow has occurred. The saturation operation depends on the overflow status bit (MV) in the processor arithmetic status (ASTAT) and the MSB of the MR2 register. The following table summarizes the MR saturation operation.

|  | MV bit | MSB of MR2 | MR content after saturation |

|--|--------|------------|-----------------------------|

|--|--------|------------|-----------------------------|

| 0 | 0 | no change                              |

|---|---|----------------------------------------|

| 0 | 1 | no change                              |

| 1 | 0 | 00000000 01111111111111 11111111111111 |

| 1 | 1 | 11111111 10000000000000 00000000000000 |

#### Table 2.3 MAC Saturation Content

Saturation in the MAC is an instruction rather than a mode as in the ALU. The saturation instruction is intended to be used at the completion of a string of multiply/accumulates so that intermediate overflows do not cause the accumulator to saturate.

Overflowing beyond the MSB of MR2 should never be allowed. The true sign bit of the result is then irretrievably lost and saturation may not produce a correct value. It takes more than 255 overflows (MV type) to reach this state, however.

#### 2.3.2.6 Rounding Mode

The accumulator has the capability for rounding the 40-bit result R at the boundary between bit 15 and bit 16. Rounding can be specified as part of the instruction code. The rounded output is directed to either MR or MF. When rounding is invoked with MF as the output register, register contents in MF represent the rounded 16-bit result. Similarly, when MR is selected as the output, MR1 contains the rounded 16-bit result; the rounding effect in MR1 affects MR2 as well and MR2 and MR1 represent the rounded 24-bit result.

The accumulator uses an unbiased rounding scheme. The conventional method of biased rounding is to add a 1 into bit position 15 of the adder chain. This method causes a slight positive net bias since the midway value is always rounded upward. This problem is eliminated by detecting this midway point and rounding half of the midway values upward and

half of them downward, yielding a zero net bias over a large number of values. When the midway point is detected, bit 16 in the result output is forced to zero. This is also known as round to even.

For example, using x to represent any bit pattern (not all zeros), here are two examples of how this rounding scheme operates.

| Example 1                           | MR2      | MR1             | MR0               |

|-------------------------------------|----------|-----------------|-------------------|

| Unrounded value:                    | XXXXXXXX | xxxxxxx00100101 | 1xxxxxxxxxxxxxxx  |

| Bit 15 = 1<br>Add 1 to bit 15 and 0 | carry    |                 | 1                 |

| Rounded value:                      | XXXXXXXX | xxxxxxx00100110 | 0xxxxxxxxxxxxxxxx |

The first example illustrates the typical rounding operation. The compensation to avoid net bias becomes visible when the lower 15 bits are all zero and bit 15 is one, i.e. the midpoint value. This is shown below.

| Example 2                                                   | MR2      | MR1             | MR0                                     |  |

|-------------------------------------------------------------|----------|-----------------|-----------------------------------------|--|

| Unrounded value:                                            | XXXXXXXX | xxxxxxx01100110 | 100000000000000000000000000000000000000 |  |

| Bit 15 = 1 and bits 0-14 = 0<br>Add 1 to bit 15 and carry 1 |          |                 |                                         |  |

| Rounded value:                                              | XXXXXXXX | xxxxxxx01100111 | 000000000000000000000000000000000000000 |  |

| Since bit 16 = 1, force it to 0                             |          |                 |                                         |  |

In this last case, bit 16 is forced to zero. This algorithm is employed on every rounding operation, but is only evident when the bit patterns shown in the last example are present.

#### 2.4 BARREL SHIFTER

The shifter unit provides a complete set of shifting functions for 16-bit inputs, yielding a 16-bit or 32-bit output. These include arithmetic shift, logical shift, normalization, derivation of exponent and derivation of

common exponent for an entire block of numbers. These basic functions can be combined to efficiently implement any degree of numerical format control, including full floating point representation.

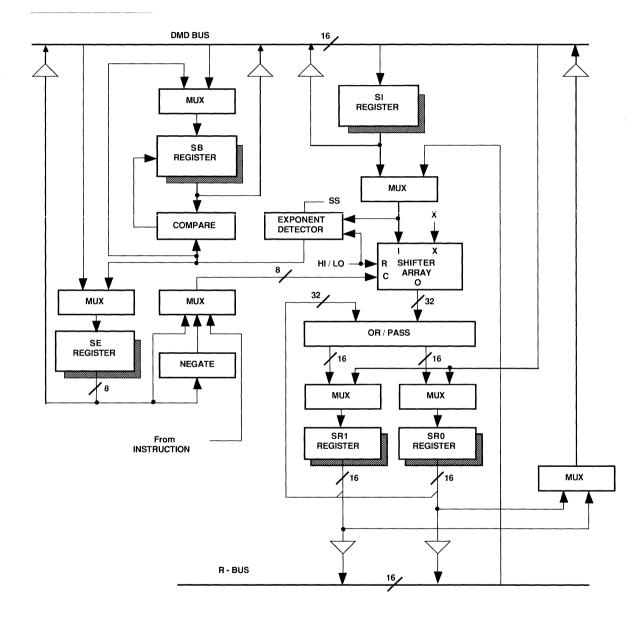

### 2.4.1 Shifter Block Diagram Discussion

Figure 2.7 (on the following page) shows a block diagram of the shifter section. The shifter section can be divided into the following components: the shifter array, the OR/PASS logic, the exponent detector, and the exponent compare logic.

The shifter array is a 16x32 barrel shifter. It accepts a 16-bit input and can place it anywhere in the 32-bit output field, from off-scale right to off-scale left, in a single cycle. This gives 49 possible placements within the 32-bit field. The placement of the 16 input bits is determined by a control code (C) and a HI/LO reference signal.

The shifter array and its associated logic are surrounded by a set of registers. The shifter input (SI) register provides input to the shifter array and the exponent detector. The SI register is 16 bits wide and is readable and writable from the DMD bus. The shifter array and the exponent detector can also take any result registers from the R bus as inputs. The shifter result (SR) register is 32 bits wide and is divided into two 16-bit sections, SR0 and SR1. The SR0 and SR1 registers can be preloaded from the DMD bus and output to either the DMD bus or the R bus. The SR register is also fed back to the OR/PASS logic to allow double-precision shift operations.

The SE register ("shifter exponent") drives the shifting operation itself. SE is 8 bits wide and holds the exponent during the normalize and denormalize operations. The SE register is loadable and readable from the lower 8 bits of the DMD bus. It is a twos-complement, 8.0 value.

The SB register ("shifter block") is important in block floating-point operations where it holds the block exponent shift value, that is, the value by which the block values must be shifted to conform to the actual exponent. SB is 5 bits wide and holds the most recent block exponent value. The SB register is loadable and readable from the lower 5 bits of the DMD bus. It is a twos-complement, 5.0 value.

Whenever the SE or SB registers are output onto the DMD bus, they are sign-extended to form a 16-bit value.

Figure 2.7 Shifter Block Diagram

2 – 22

The SI, SE and SR registers can be read and written in the same cycle. Registers are read at the beginning of the cycle and written at the end of the cycle. All register reads, therefore, read values loaded at the end of a previous cycle. A new value written to a register cannot be read out until a subsequent cycle. This allows an input register to provide an operand to the Shifter at the beginning of the cycle and be updated with the next operand from memory at the end of the same cycle. It also allows a result register to be stored in memory and updated with a new result in the same cycle. See the discussion of "Multifunction Instructions" in the chapter "Instruction Set Overview" for an illustration of this same-cycle read and write.

The shifter section contains a duplicate bank of registers, shown in Figure 2.7 as a "shadow" behind the primary registers. There are actually two sets of SE, SB, SI, SR1, and SR0 registers. Only one bank is accessible at a time. The additional bank of registers can be activated during an interrupt service routine for extremely fast context switching. A new task, such as an interrupt service routine, can be executed without transferring current states to storage.

The selection of the primary or alternate bank of registers is controlled by a bit in the processor mode status register (MSTAT). Toggling this bit switches back and forth between the two register banks.

The shifting of the input is determined by a control code (C) and a HI/LO reference signal. The control code is an 8-bit signed value which indicates the direction and number of places the input is to be shifted. Positive codes indicate a left shift (upshift) and negative codes indicate a right shift (downshift). The control code can come from three sources: the content of the shifter exponent (SE) register, the negated content of the SE register or an immediate value from the instruction.

The HI/LO signal determines the reference point for the shifting. In the HI state, all shifts are referenced to SR1 (the upper half of the output field), and in the LO state, all shifts are referenced to SR0 (the lower half of the output field). The HI/LO reference feature is useful when shifting 32-bit values since it allows both halves of the number to be shifted with the same control code. HI/LO reference signal is dynamically selectable each time the shifter is used.

The shifter fills any bits to the right of the input value in the output field with zeros, and bits to the left are filled with the extension bit (X). The extension bit can be fed by three possible sources depending on the instruction being performed. The three sources are the MSB of the input, the AC bit from the arithmetic status register (ASTAT) or a zero. The AC bit is used when constructing 32-bit results from successive multiword operations in the ALU.

Table 2.4 gives a listing of shifter array output as a function of the control code and HI/LO signal.