AMPEX

REV 2 V0034

# "HANDBOOK OF SOLID-STATE LOGIC"

By Members of the Training Department

AMPEX CORPORATION

TRAINING USE ONLY V0007 REV 2

#### SECTION I: NUMBERING SYSTEMS

- Any discussion of so-called "digital", "binary", "logic", or "computer" techniques usually starts off with a discussion of numbering systems.

- 1.1 Electronic devices, particularly relays and solid-state (transistor) devices can be very efficiently and accurately operated ON or OFF. It is usually called switching mode of operation.

- 1.2 A system was developed during the 19th century, called Boolean Algebra, after its inventor, an Englishman named George Boole. It defined rules for a system containing only two conditions - George did it or George did not do it. Statements were either TRUE or FALSE. It was an attempt to logically attack non-mathematical problems with the preciseness of classical algebra.

- 1.3 What was a rather obscure theory gathering dust in a small volume on library shelves became a factor in modern electronics when telephone companies expanding their dial switching systems, needed something to rapidly evaluate the action of many two condition devices relays.

- 1.4 They discovered that the rules of Boolean Algebra could be used to simplify complex relay paths and minimize redundancy.

- 2. Our daily life is tied to a system based on ten discrete levels frequently attributed to the fact that we have ten fingers.

- 2.1 Since, at the time that man began to require numbers to express quantities, feet were bare, a system based on 20 seems more logical - and at least one historical civilization used such a system.

- 2.2 Even using only ten fingers, eleven events can be expressed, if the absence of any events (zero) is considered a valid happening.

- 2.2-1 The ROMAN numbering system I, II, III, etc. had no discrete symbol for zero events. The idea of zero came into "Western" (European) civilization from Asia through the Islamic civilization. At least one American Indian civilization understood the concept.

I - 1

AMPEX DEPARTMENT

3.

5

7

0

1

One man can then express, using his fingers, an amount of oranges, apples, or events.

|            |   |   |   |   |   |   | *0* | * • * | * 9* |

|------------|---|---|---|---|---|---|-----|-------|------|

| COUNT O 1  | 2 | 3 | 4 | 5 | 6 | 7 | 8   | 9     |      |

| EVENTS 1 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9   | 10    | 11   |

- 3.1 If it is necessary to count more than the number of events, a second man will be required who uses a finger to indicate that the first man has gone back to the the closed fist - the fact that he had used all his fingers (digits) was remembered, or CARRIED to the second man.

- 3.1-1 Some primitive tribes have considered anything over ten events as "many".

- 3.2 Two men can express 20 events, and three men 30 events, in our system. Each additional man becomes more significant as he represents a greater number of hands, hence the least and most significant character, or bit.

| <u>\</u> <u></u> * |                                    |                                                                                     |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------|

|                    | Least Significant –<br>(LS)        | counted sevenths since the last<br>time fists closed.                               |

| Ť.                 | 2nd Least Significant-<br>(2 L S ) | LS has reached maximum finger<br>count seven times                                  |

|                    | 3rd Least Significant-<br>(3 L S ) | 2LS has not reached maximum<br>finger count, or has reached<br>it one time or more. |

|                    | Most Significant -<br>( M S )      | 3LS has been through maximum count ten times and LS 1000 times.                     |

3.3 The BASE or RADIX of our numbering system is TEN (10). The more significant position a digit occupies the larger the power of ten it represents. The number 1075 can be expressed as:

> 5 x 10<sup>0</sup> = 5 x 1 = 57 x 10<sup>1</sup> = 7 x 10 = 700 x 10<sup>2</sup> = 0 x 100 = 0001 x 10<sup>3</sup> = 1 x1000 = <u>1000</u>1075

AMPEX PERMIT

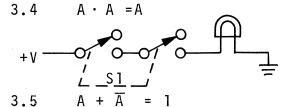

3.4 Note that the base ten system has ten digits, or discrete bits, 0-9, none of which represent 10.

3.4-1 Any system will utilize base ten digits to a value of RADIX less one.

With only eight fingers we could have developed a system based on a RADIX of 8 (octal). With 12 fingers -

| RADIX 10 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 0 | 1 | 2 | 3                |  |

|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|------------------|--|

| RADIX 8  | Û | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Û | 1 | 2 | 3 | 4 | 3<br>5<br>1<br>1 |  |

| RADIX 12 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | 0 | 1                |  |

| RADIX 2  | 0 |   | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | Ó | 1 | 0 | 1,,,             |  |

4.1 Only the least significant digits are shown in the table above. Note that a system based on eight used the digits 0 through 7; the system based on two used zero and one; whereas for a system based on twelve it was necessary to provide two additional symbols.

4.2 Numbers in the base 10 system can be rapidly converted to numbers expressed to another RADIX.

a. Base 10 to base 10.

4.

| 10 | 107 | 5  | Rema | ainder |       |      |

|----|-----|----|------|--------|-------|------|

| 10 | 10  | )7 | 5    | LSD    |       |      |

| 10 | 1   | 0  | 7    |        | -1075 | (10) |

| 1( | ן נ | 1  | 0    |        |       |      |

|    |     | 0  | 1    | MSD    |       |      |

b. Base 10 to base 12.

| 12 1 | 075 |   |     |          |

|------|-----|---|-----|----------|

| 12   | 89  | 7 | LSD | 757 (12) |

| 12   | 7   | 5 |     |          |

|      | 0   | 7 | MSD | •        |

I - 3

AMPEX TRAINING

c. Base 10 to base 8.

d. Base 10 to base 2.

1

| 2 1 | 075 | -  | a   |     |        |      |     |

|-----|-----|----|-----|-----|--------|------|-----|

| 2   | 537 | 1  | LSD |     |        |      |     |

| 2   | 268 | 1. |     |     |        |      |     |

| 2   | 134 | 0  |     | 100 | 00 110 | 0011 | (2) |

| 2   | 67  | 0  |     |     |        |      |     |

| 2   | 33  | 1  |     |     | •      |      |     |

| 2   | 16  | 1  |     |     |        |      |     |

|     | 2 8 | 0  |     |     |        |      |     |

|     | 2 4 | 0  |     |     |        |      |     |

|     | 2 2 | 0  |     |     |        |      |     |

|     | 2 1 | 0  |     |     |        |      |     |

|     | 0   | 1  | MSD |     |        |      |     |

4.3 To convert back to RADIX 10 a base 10 to base 10  $(1075_{10})$ .

$5 \times 10^{0} = 5 \times 1 = 5$ 7 \times 10^{1} = 7 \times 10 = 70 0 \times 10^{2} = 0 \times 100 = 000 1 \times 10^{3} = 1 \times 1000 =  $\frac{1000}{1075}$

Base 12 to base 10  $(757_{12})$ . b. 107510 Base 8 to base 10  $(2063_{g})$ . с.  $3 \times 8^{0} = 3 \times$ 1 = 3 107510 d. Base 2 to base 10  $(10000110011_2)$ . 1 x 20 1 x 21 = ] x 1 ] = = 1 x 2 = 2 0 x 22 0 x 23 0 x 23 = 0 xΞ 4 0 X X = 0 x 8 = 0 24 1 = 1 x 16 16 =2<sup>5</sup> 1 х = 1 x 32 = 32 26 27 х 1 = 0 x64 = 0 х 128 = 0 = 0 x 0 x 28 0 = 0 x 256 =0 29 210 x x = 0 x 512 = 0 0  $= 1 \times 1024 = 1024$ 107510 RADIX 8 and RADIX 2 enjoy a peculiar relationship because 8 is the cube of 2. a. Divide the binary version of 1075 into groups of 3, starting from LSD, and convert each of these groups into an equivalent base 10 digit. 010 b. 000 110 0112 107510 . = 2 38 0 6 107510 = This ease of conversion is sometimes utilized in с. economically priced computers to convert the machine binary computations to a numbering system requiring less discrete digits, making it easier to

4.4

I – 5

interface with the human machine.

AMPEX DEPARTMENT

5. Can 1075 = 5701? It can if the least significant digit is clearly defined.

- 5.1 In binary counters, the schematic is usually drawn in such a way that the least significant digit is on the left.

- 6. Operations in Numbering Systems

- 6.1 Table 6.1 gives the values from one to 40, of digits to bases 10, 12, 8, 4, 3, and 2.

- a. Look for the patterns

- b. Try addition:

| <sup>12</sup> 10 +  | 1210            | = | <sup>24</sup> 10 |      |   |    |       |    |

|---------------------|-----------------|---|------------------|------|---|----|-------|----|

| <sup>10</sup> 12 +  | 1012            | = |                  |      |   |    |       |    |

| 148 +               | 148             | = |                  | (4+4 | = | 0, | carry | 1) |

| 304 +               | <sup>30</sup> 4 | = |                  | (3+1 | = | 0, | carry | 1) |

| 1100 <sub>2</sub> + | 1100<br>2       | = |                  | (1+1 | = | 0, | carry | 1) |

#### 7. SUMMARY

- 7.1 Counting need not be confined to the current system based on ten. Almost any base can be utilized, although more or less characters may be required. The system can be manipulated and valid conclusions reached.

- a. Our system of telling time is one using only part of base ten digits. The maximum number is 60-it runs from 00 hours, 00 minutes, 00 seconds, 00 frame to a maximum count of 23 hours, 59 minutes, 59 seconds, 29 frames. - One more frame generates a carry which puts the numbering system back to zero.

- b. The carry in the hours column could be used to advance a "day" counter to 1.

- 7.2 The section on gating logic discusses the two fingered world of electronic OFF/ON circuits. The rules for manipulating in such a system are covered in detail.

- 7.3 Additional information on methods of electronic counting binary counters and decoders are covered in section or binary counters and shift registers.

TRAINING DEPARTMENT AMPEX

|                    | TABLE              | 6.1 NUMB          | ERING SYS          | TEMS                |                       |

|--------------------|--------------------|-------------------|--------------------|---------------------|-----------------------|

| BASE 10            | BASE 12            | BASE 8            | BASE 4             | BASE 3              | BASE 2                |

| 00 10 <sup>0</sup> | 00 12 <sup>0</sup> | 00 8 <sup>0</sup> | 000 4 <sup>0</sup> | 0000 3 <sup>0</sup> | 000000 2 <sup>0</sup> |

| 01                 | 01                 | 01                | 01                 | 01                  | 000001                |

| 02                 | 02                 | 02                | 02                 | 02                  | 000010 2 <sup>1</sup> |

| 03                 | 03                 | 03                | 03                 | 10 3 <sup>1</sup>   | 000011                |

| 04                 | 04                 | 0 4               | 10 4 <sup>1</sup>  | 11                  | 000100 2 <sup>2</sup> |

| 05                 | 05                 | 05                | 11                 | 12                  | 000101                |

| 06                 | 06                 | 06                | 12                 | 20                  | 000110                |

| 07                 | 07                 | 07                | 13                 | 21                  | 000111                |

| 08                 | 08                 | 10 8 <sup>1</sup> | 20                 | 22                  | 001000 2 <sup>3</sup> |

| 09                 | 09                 | 11                | 21                 | 100 3 <sup>2</sup>  | 001001                |

| 10 10 <sup>1</sup> | 0 A                | 12                | 22                 | 101                 | 001010                |

| 11                 | 0 B                | 13                | 23                 | 102                 | 001011                |

| 12                 | 10 12 <sup>1</sup> | 14                | 30                 | 110                 | 001100                |

| 13                 | 11                 | 15                | 31                 | 111                 | 001101                |

| 14                 | 12                 | 16                | 32                 | 112                 | 001110                |

| 1                  | 13                 | 17                | 33                 | 120                 | 001111                |

| 16                 | 14                 | 20                | 100 4 <sup>2</sup> | 121                 | 010000 2 <sup>4</sup> |

| 17                 | 15                 | 21                | 101                | 122                 | 010001                |

| 18                 | 16                 | 22                | 102                | 200                 | 010010                |

| 19                 | 17                 | 23                | 103                | 201                 | 010011                |

| 20                 | 18                 | 24                | 110                | 202                 | 010100                |

| 21                 | 19                 | 25                | 111                | 210                 | 010101                |

| 22                 | 1 A                | 26                | 112                | 211                 | 010110                |

| 23                 | <b>1</b> B         | 27                | 113                | 212                 | 010111                |

| 24                 | 20                 | 30                | 120                | 220                 | 011000                |

| 25                 | 21                 | 31                | 121                | 221                 | 011001                |

| 26                 | 22                 | 32                | 122                | 222                 | 011010                |

| 27                 | 23                 | 33                | 123                | 1000 3 <sup>3</sup> | 011011                |

| 28                 | 24                 | 34                | 130                | 1001                | 011100                |

| 29                 | 25                 | 35                | 131                | 1002                | 011101                |

| 30                 | 26                 | 36                | 132                | 1010                | 011110                |

## TABLE 6.1 NUMBERING SYSTEMS

. . . .

1

I – 7

|       | TRAINING   |

|-------|------------|

| AMPEX | DEPARTMENT |

ī

| BASE 10 | BASE 12 | BASE 8 | BASE 4 | BASE 3 | BASE 2                |  |

|---------|---------|--------|--------|--------|-----------------------|--|

|         |         |        |        |        |                       |  |

| 31      | 27      | 37     | 133    | 1011   | 011111                |  |

| 32      | 28      | 40     | 200    | 1012   | 100000 2 <sup>5</sup> |  |

| 33      | 29      | 41     | 201    | 1020   | 100001                |  |

| 34      | 2 A     | 42     | 202    | 1021   | 100010                |  |

| 35      | 2 B     | 43     | 203    | 1022   | 100011                |  |

| 36      | 30      | 44     | 210    | 1100   | 100100                |  |

| 37      | 31      | 45     | 211    | 1101   | 100101                |  |

| 38      | 32      | 46     | 212    | 1102   | 100110                |  |

| 39      | 33      | 47     | 213    | 1110   | 100111                |  |

| 40      | 34      | 50     | 220    | 1111   | 101000                |  |

|         |         |        |        |        |                       |  |

V-0008 TRAINING USE ONLY REV 2

#### SECTION II: GATING LOGIC

1. <u>Boolean Algebra</u> is a method of expressing statements in the form of equations which can be manipulated. Often circuits can be simplified by cancelling out redundant terms. The results are expressed in terms easily simulated by electronic circuits:

|                                    | TRUE     | OR | FALSE    |

|------------------------------------|----------|----|----------|

|                                    | ONE (1)  |    | ZERO (O) |

| COMMON<br>ELECTRONIC<br>CONDITIONS | CLOSED   |    | OPEN     |

|                                    | / HIGH   |    | LOW      |

|                                    | ) ON     |    | OFF      |

|                                    | POSITIVE |    | NEGATIVE |

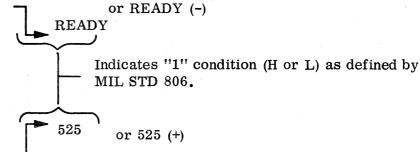

#### 2. TERMS AND SYMBOLS

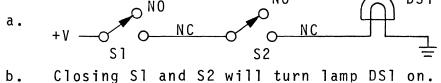

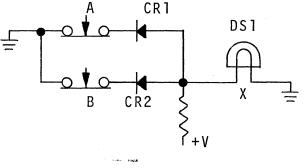

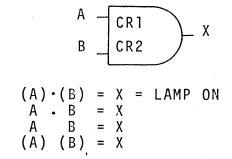

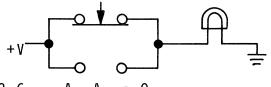

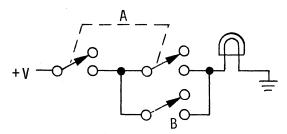

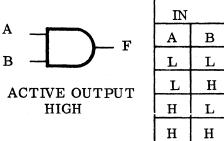

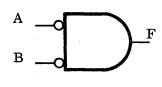

2.1 AND: all switches must be closed before an event can occur.

- D. Closing S1 and S2 will turn lamp DS1 on. S1 and S2 = DS1 (S1) (S2) = DS1 = S1·S2

- c. The algebraic symbol for multiplication is used. It is also referred to, in some texts, as juxtaposition, or conjunction.

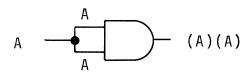

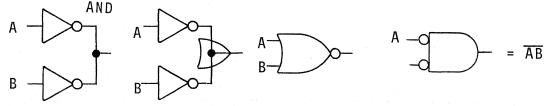

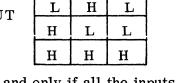

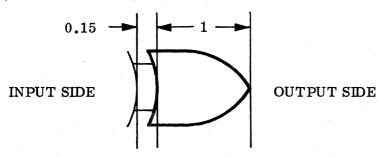

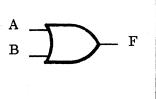

- d. When electronic components are used LOGIC symbols are employed to represent the AND function.

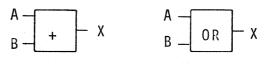

e. Other symbols: A - - X = A - AND - XB - - X = B - AND - X

II-1

AMPEX

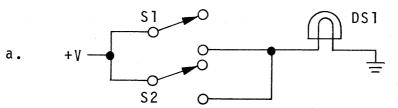

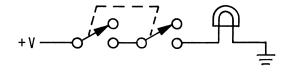

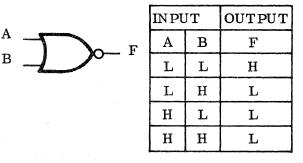

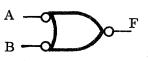

2.2 OR: An output occurs when either of two switches, or both of them, are closed.

- c. The algebraic symbol for addition is used to indicate the OR function.

- d. It is also called DISJUNCTION.

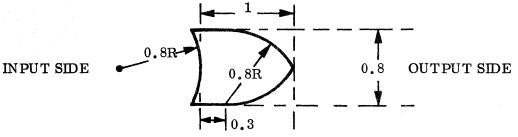

- e. The standard symbol for "OR".

f. Symbols also used:

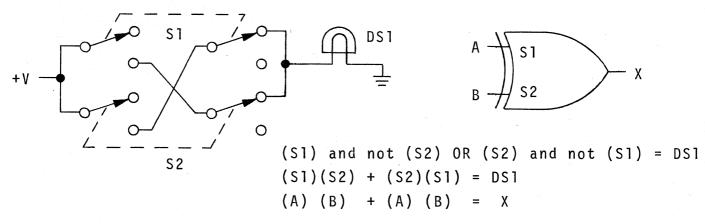

g. If the circuit is such that if one OR the other is closed, but not both for a result, it is called an EXCLUSIVE OR

h. A later paragraph discusses this circuit in more detail

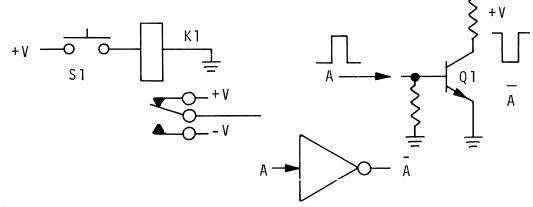

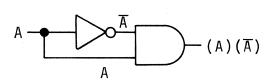

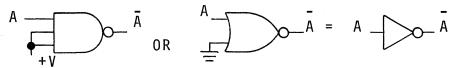

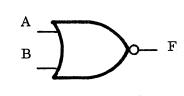

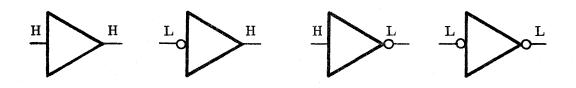

2.3 <u>NOT</u>: inversion, complement, phase reversal are common electronic equivalents.

- a. Operating the relay Kl inverts the positive voltage from Sl to a negative voltage.

- b. Across Q1, base to collector, the signal is inverted.

- c. In the equation, the inverted output is indicated by the bar over the "A".

- d. The small circle on the output of the amplifier symbol indicated that if the input is positive, the output will be negative.

- e. Older symbols:

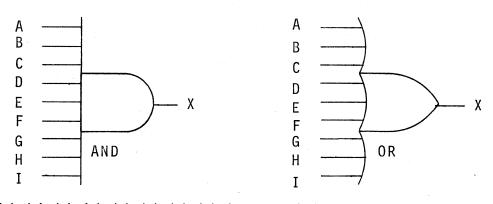

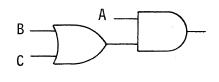

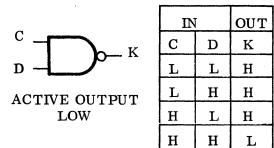

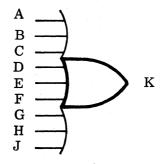

2.4 When the gates discussed in paragraphs 2.1 and 2.2, have multiple inputs, the symbols are:

(A)(B)(C)(D)(E)(F)(G)(H)(I)=X

(A)+B+C+D+E+F+G+H+I=X

a. The convenience of equations becomes apparent when dealing with multiple input gates.

#### 3. LOGIC EQUATIONS

TRAINING

MPEX

- 3.1 Useful in simplifying circuit requirements, Boolean Algebra has a set of axioms, similar to those in conventional algebra. Some are obvious.

- a. A + B = B + Ab.  $A \cdot B = B \cdot A$ c. (A+B) + C = A + (B+C) = A + B + Cd.  $(AB) \cdot (C) = (A) \cdot (BC) = A \cdot B \cdot C = ABC$

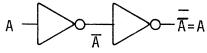

3.2 Double inversion equals no inversion or  $\overline{A} = A$

of course in practical electronic circuits, load requirements may make the double inversion necessary.

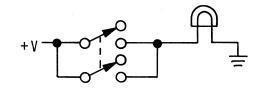

3.3 A + A = A

.

Δ

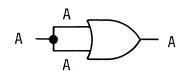

$3.6 \quad A \cdot A = 0$

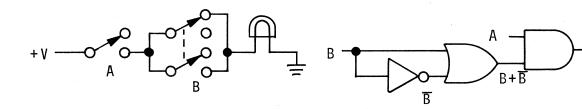

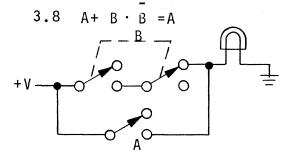

3.7

A  $(B+\overline{B}) = AB + A\overline{B} = A$

A+Ā

A

II - 4

AMPEX

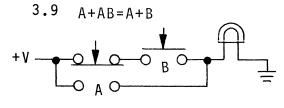

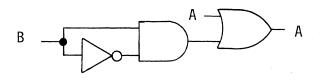

3.10 A (A+B) = AA + AB = A + AB = A

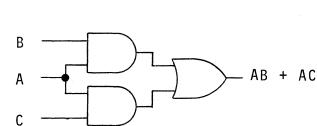

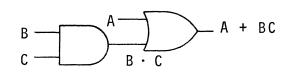

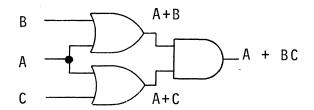

3.11  $A \cdot (B+C) = AB+AC$

3.12  $A+BC = (A+B) \cdot (A+C)$

3.13 Performing the same action on both sides of an equation does not affect the equality.

####

4.

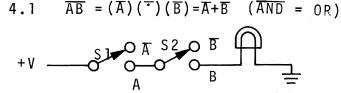

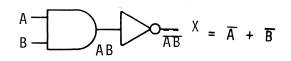

DEMORGAN'S THEOREM is useful in understanding logic circuits because of the inversion which occurs when using transistor gates.

If S1 or S2 is not closed, the lamp will not light; or X is low if A or B is low.

If S1 and S2 are not operated, the lamp will not light.

- 4.3 Up to this point the actual levels involved have been ignored. In practical circuits the value of "1" and "0" will be defined a specific voltage levels.

- a. Positive Logic: The TRUE or one (1) condition is positive (HIGH) with respect to the FALSE, or ZERO (LOW) condition.

| ייןיי  | "0"    |

|--------|--------|

| +4.5   | GROUND |

| GROUND | -5.2V  |

| +12    | -12    |

In a typical equation  $A \cdot B = X$ , X will be high if A and B are high.

b. Negative logic assumes that the TRUE, or ONE (1) condition is negative with respect to the ZERO (0) condition.

| 1      | 0      |

|--------|--------|

| GROUND | +4.5V  |

| -5.2   | GROUND |

| -12    | +12    |

In the equation  $A \cdot B = X$  when (A) and (B) are negative, (X) will be negative.

4.4 AMPEX training material will use positive logic, and equations will be written to indicate where the highs are occurring, unless otherwise indicated.

AMPEX

V0010 TRAINING USE ONLY

5. The examples of paragraphs 3 and 4 can be summarized by the following equations: 5.1 For  $(\cdot)$  read AND; (+) read OR. 5.2 **Basic Axioms**  $0 \cdot 0 = 0$ a. 1.1=1 b .  $0 \cdot 1 = 1 \cdot 0 = 0$ с. 0 + 0 = 0d. 1 + 0 = 0 + 1 = 1е. |+| = |f. Theorems (proven from the basic axioms) 5.3  $0 \cdot x = 0$ 1. a.  $1 \cdot x = x = x \cdot x$ b. 1 + x = 1с. 0+x = x = x+xd. 0 = 1 2. a. T = 0b. с.  $x \cdot x = 0$ d. x + x = 13. x+y = y+x Commutative Rule (Ref 3.1.a, 3.1.b) a.  $\mathbf{x} \cdot \mathbf{y} = \mathbf{y} \cdot \mathbf{x}$ b. xyz = (xy)z = x(yz) Associative Rule (REF 3.1.c, 3.1.d) 4. a. x+y+z = (x+y)+z = x+(y+z)b. 5. xy+xz = x(y+z) Distributive Rule (Ref 3.11) a.  $(x+y) \cdot (x+z) = x+yz$  Absorptive Rule (Ref 3.12) b. 6. x + xy = xa. Proof:  $x(x+y) = x(1+y) = x \cdot 1 = x$  (Ref 3.10) b. x(x+y) = xProof: x(x+y) = x + x + y = x + x = xa.  $x + \overline{xy} = x + y$  (Ref 3.8) 7.  $(x+\overline{y})y = xy$ b. De Morgan's Theorem (Ref 4.0) 8.  $\overline{x \cdot y \cdot z} = \overline{x} + \overline{y} + \overline{z}$ a.  $\overline{X+Y+Z} = \overline{X} \cdot \overline{Y} \cdot \overline{Z}$ b. (x+y)  $(\overline{x}+z) = xz + \overline{x}y$ Expansion Theorem 9. a.  $(xy)+(\overline{x}z) = (x+z)(\overline{x}+y)$ b.

AMPEX

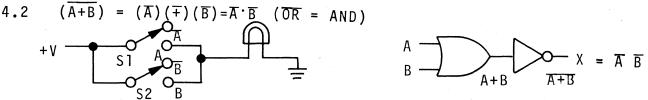

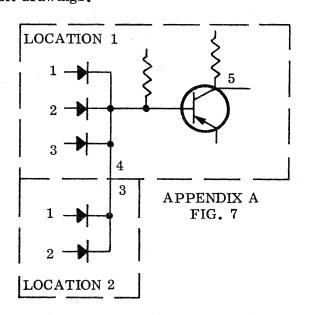

#### 6. <u>TYPICAL GATING CIRCUITS</u>

7.

If any input goes to ground (high), the output will be high (A+B+C) = X. If all inputs are negative, the output will be negative. If all inputs are positive, the output is positive  $A \cdot B \cdot C = X$ If any input goes to ground (low) the output will be low.

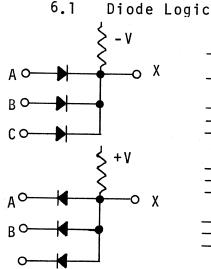

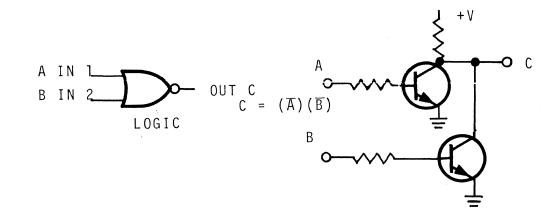

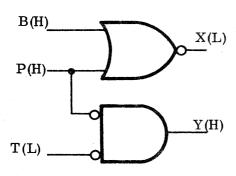

6.2 Transistor logic, or diode transistor logic is more common. This frequently involves inversion.

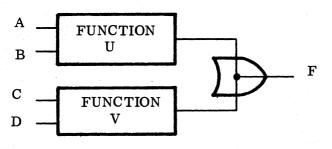

Most manufacturers use the symbol that indicates the function the integrated logic circuit is performing when the input is positive.

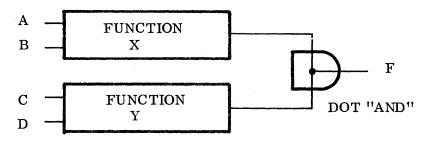

AMPEX drawings are currently using a system of FUNCTIONAL LOGIC drawings. This system utilizes the symbol which describes the particular function being performed by a group of gates.

II-8

AMPEX Sustained

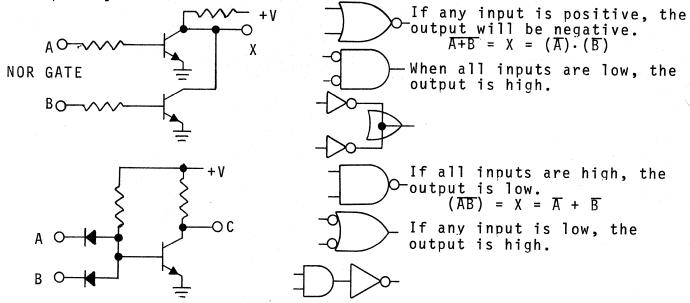

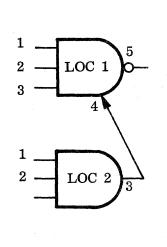

| AND            | OR          | A B                      | X                | HIGHS                             | LOWS                                   |

|----------------|-------------|--------------------------|------------------|-----------------------------------|----------------------------------------|

| A<br>B<br>AND  |             | H H<br>H L<br>L H<br>L L | H<br>L<br>L<br>L | (A)(B) = X                        | $A+B = X_L$                            |

|                |             | H H<br>H L<br>L H<br>L L | L<br>L<br>H<br>L | (A)(B) = X                        | $A+B = X_L$                            |

| A $B$ $X$      |             | H H<br>H L<br>L H<br>L L | L<br>H<br>L<br>L | (A)(B) = X                        | $-A+B = X_L$                           |

|                |             | H H<br>H L<br>L H<br>L L | L<br>L<br>H      | (Ā)(Ē) = X                        | $A+B = X_{L}$                          |

|                | A<br>B<br>X | H H<br>H L<br>L H<br>L L | H<br>H<br>H<br>L | A+B = X                           | $(\overline{A})(\overline{B}) = X_{L}$ |

|                | A<br>B<br>X | H H<br>H L<br>L H<br>L L | H<br>L<br>H<br>H | -<br>A+B = X                      | $(A)(\overline{B}) = X_{L}$            |

|                |             | H H<br>H L<br>L H<br>L L | H<br>H<br>L<br>H | A + B = X                         | (Ā)(B) = X <sub>L</sub>                |

| A<br>B<br>NAND |             | H H<br>H L<br>L H<br>L L | L<br>H<br>H<br>H | $\overline{A} + \overline{B} = X$ | (A)(B) = X <sub>L</sub>                |

11-9

λ.

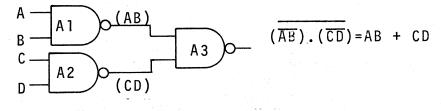

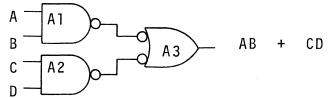

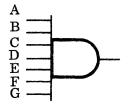

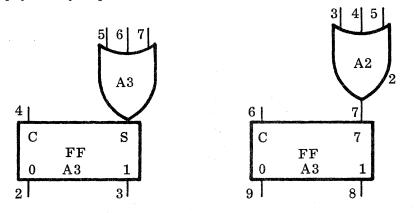

7.1 b. If the circuit driven by gate A3 requires a positive level to cause an event (relay closure, reversal of a flip-flop) the circuit, using functional logic, would be drawn:

7.2

The conditions - location of "ONE'S" - required to produce a negative output from A3 may be obtained by complementing the equation AB+CD

$\overline{AB+CD} = (\overline{AB}) (\overline{CD}) = (\overline{A}+\overline{B}) \cdot (\overline{C}+\overline{D})_{1}$

If the circuit driven by A3 requires a negative level, then the logic could be functionally indicated:

The equation is still AB+CD although the functional logic drawing indicates that the complemented equation drives the following circuit.

- 7.4 Note that the small circles indicate the relative polarity between input and output to perform the logic function.

- 7.5 See chart on page 10.

- 7.6

a. NAND and NCR gates are frequently seen on logic schematics with only one signal input. Other inputs may be tied to a voltage, ground, or left unconnected. These units are being used as inverters.

b. A diode used for isolation may also be drawn as an OR GATE

7.7 a. Two inverters may have their outputs tied together to form what is sometimes called a WIRED OR or WIRED

AMPEX PARTMENT

- b. In some cases it may be necessary to refer to the manufacturer's literature when using this configuration.

- c. In general, an input level which drives one of the outputs to ground controls the logic. The other output cannot rise or fall from ground.

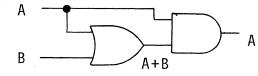

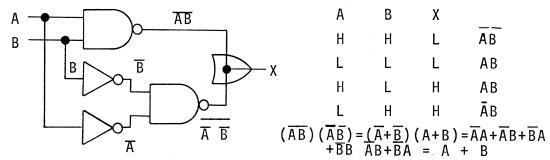

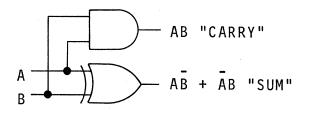

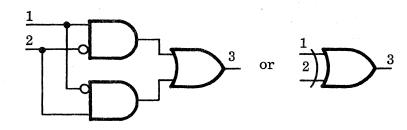

#### 7.8 EXCLUSIVE OR

a. The Boolean logic OR is now defined as A or B or both. It is inclusive. Frequently required is the function A or B, but not both, designated the EXCLUSIVE OR

b. If all the circuitry is mounted on a single chip, or if a logic schematic has been simplified, it may be shown as an EXLCUSIVE OR.

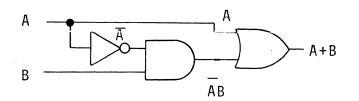

$$A \longrightarrow A\overline{B} + \overline{A}B = A + B$$

- c. It is also referred to as a half adder because of binary addition relationships:

- 0+0=01+0=10+1=1

d.

- l+l= 0, carry l to next most significant digit.

- It is called a 1/4 ADDER because it is ambiguous for the sum of both 0+0 and 1+1; the output, in the example given, is low in both cases.

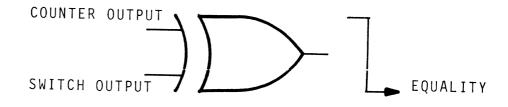

e. In the case where the comparison of two conditions only is important, the half adder is sufficient. In the electronic tape timer, a low output can be used to indicate that switch settings agree with the outputs of the tape counters. The only concern is that conditions are the same, whether they be "ONES" or "ZEROES".

AMPEX

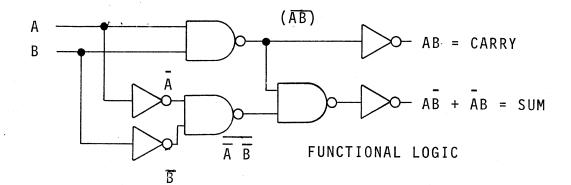

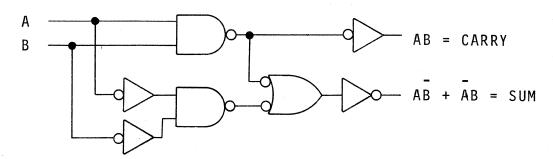

7.9 A " 1/2 adder" must sense the difference between O+O (AB) and 1+1 A B and generate a carry to the next stage when the A B condition exists.

SIMPLIFIED

7.10 The "full adder" is two half adders-it includes provisions for a "CARRY" input.

AMPEX BEAT

Revision No. 2

Training Use Only V-0001

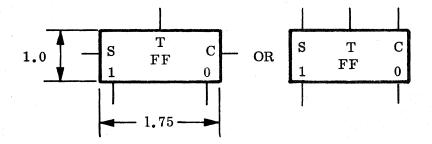

#### SECTION III BISTABLE MULTIVIBRATOR, OR FLIP FLOP

- 1. The bistable multivibrator, or flip-flop is one of the most useful circuits in logic design

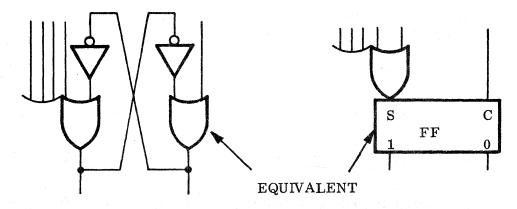

- 1.1 The unit may come as an integrated circuit, or consist of NOR and NAND gates.

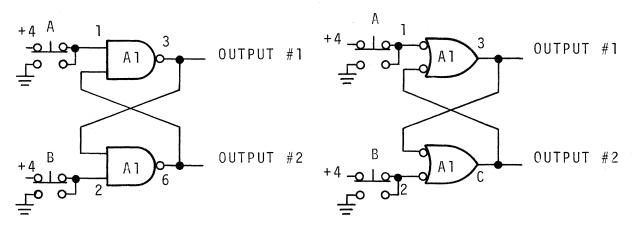

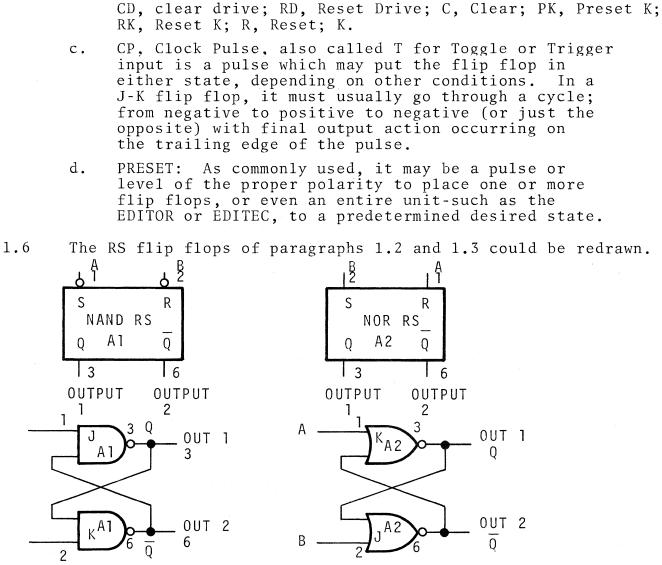

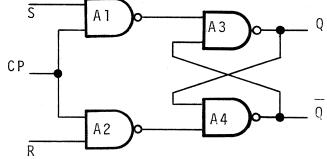

- 1.2 NAND R-S (RESET/SET) flip-flop.

- a. Pressing Switch A puts a low level into Al-3, and its output goes high (NAND GATE, any low in, output goes high).

- b. The output of A1-6, with two highs in, goes low.

- c. This is fed back to Al-3 to maintain its output high.

- d. Further pressing of switch A will have no effect.

- e. Pressing Switch B will reverse the flip flop.

- f. Pressing both switches will cause both outputs to go high, and is generally considered an ambiguous, or not allowed condition, although this mode of operation is occassionally used.

- g. The final state will depend on which side is released first.

| А    | В    | OUTPUT 1  | OUTPUT 2  |

|------|------|-----------|-----------|

| HIGH | HIGH | NO CHANGE | IN OUTPUT |

| LOW  | HIGH | HIGH      | LOW       |

| HIGH | LOW  | LOW       | HIGH      |

| LOW  | LOW  | HIGH      | HIGH      |

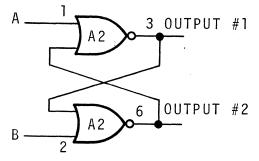

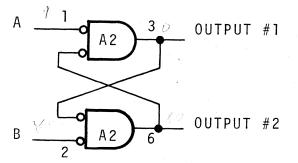

### 1.3 NOR R/S FLIP FLOP

| А    | В    | OUTPUT 1  | OUTPUT 2        |

|------|------|-----------|-----------------|

| LOW  | LOW  | MAINTAINS | PREVIOUS STATE  |

| HIGH | LOW  | LOW       | HIGH            |

| LOW  | HIGH | HIGH      | LOW             |

| HIGH | HIGH | LOW       | LOW (AMBIGUOUS) |

1.4 The designators for the inputs depend on output levels. Unless in the ambiguous, or undefined condition, the outputs are always 180° out of phase.

| OUTPUT 1 | OUTPUT 2                |

|----------|-------------------------|

| 1        | 0                       |

| 1        | Ī                       |

| SET      | RESET                   |

| S        | R                       |

|          | CLEAR                   |

|          | С                       |

| TRUE     | FALSE                   |

| HIGH     | LOW                     |

| FUNCTION | FUNCTION                |

| Q        | $\overline{\mathbf{Q}}$ |

|          |                         |

- 1.5 The can now be defined in terms of an output high level

- a. SET: a level of either negative or positive polarity that places the Q output to a binary 1 state; in positive logic a high level called: SD, Set Drive; PJ, Preset J; S, Set; SJ, Set J; J.

AMPEX

RESET: a level of either polarity which puts the

Q output in a binary zero condition called:

b.

These circuits are sometimes referred to as "latches".

TRATEG AMPEX

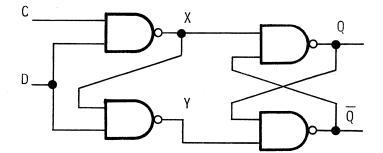

2.0 The buffered store RS flip flop (delay flip flop)

NO CHANGE NO CHANGE

- a. "C" information is stored only when "D" is high.

- b. Information stored as long as "D" remains low.

- c. Q follows "C" when D is high.

- d. State of "C" stored when commanded by D.

- e. Sometimes called a delay flip flop since the transfer of "C" to Q depends on "D".

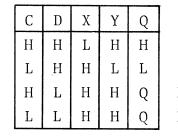

CP is a trigger which goes positive some time after S and R inputs have changed state:

| S | R | Q | Q after CP |

|---|---|---|------------|

| Н | L | Н | H          |

| Η | L | L | Н          |

| L | Η | L | L          |

| L | Н | Н | L          |

Q follows S on application of clock pulse.

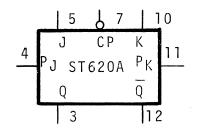

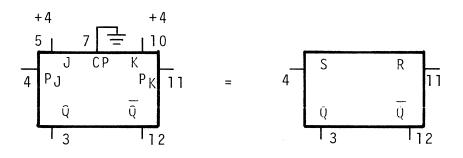

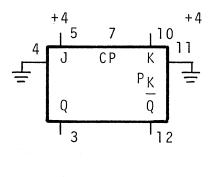

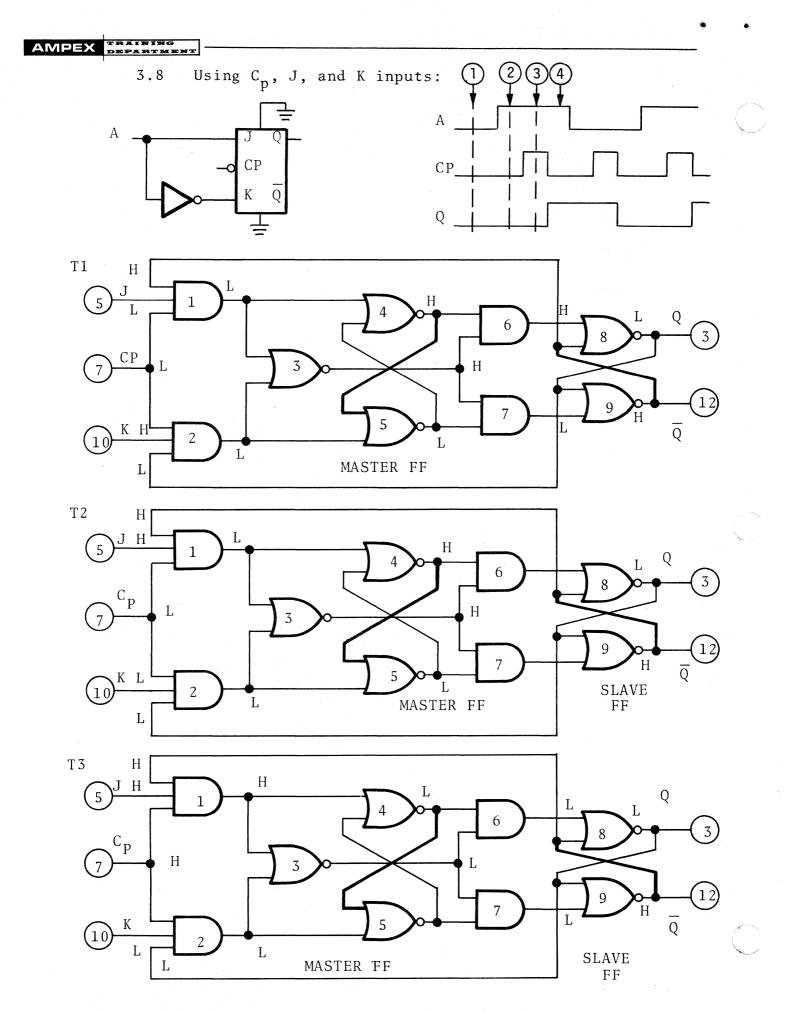

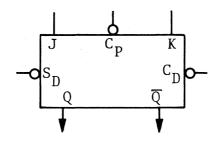

- 3. The J-K flip flop, Signetics 620A.

- 3.1 The J-K flip flop is widely available and used in integrated circuit applications frequently. It can be used in any of the configurations discussed so far, and has other applications as well.

- 3.2 The discussion applies directly to the Signetics ST 620A used in the AMPEX HS-100B. Other J-K type flip flops will operate in a similar manner, but will follow specific level rules which may differ. While the particular J-K requires positive levels on the J and/or K inputs other types call for negative levels. The clock pulse is one that first goes positive then negative. In other units, just the opposite may be true. Refer to the manufacturers spec sheet for a particular type.

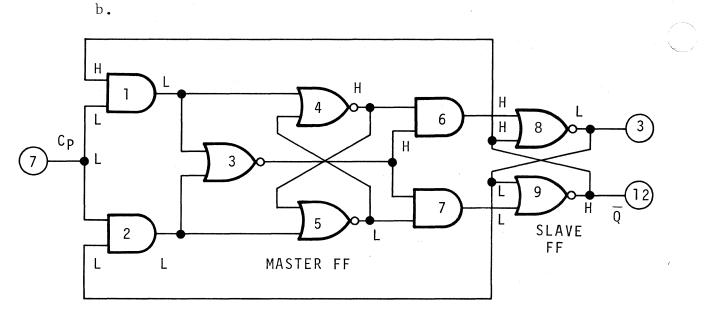

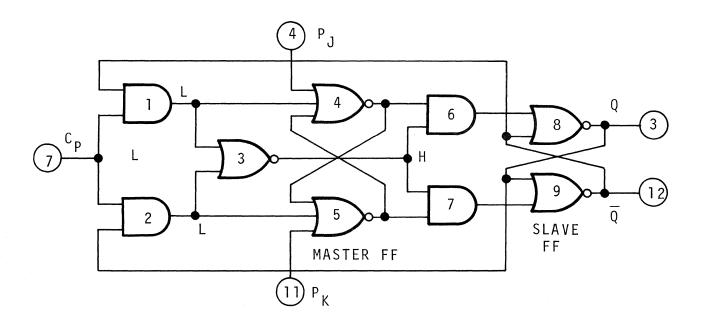

- 3.3 General Logic Diagram

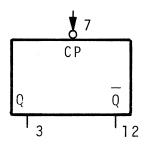

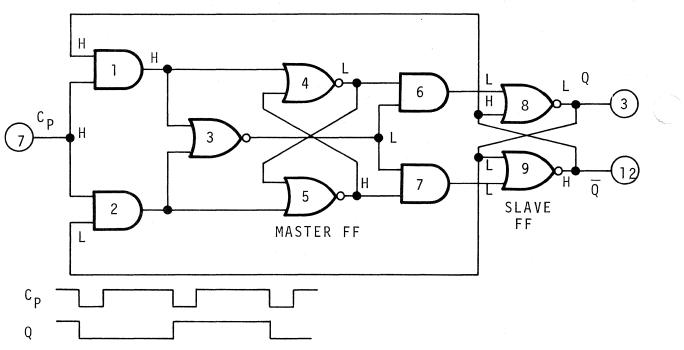

- a. The circle on the CP input indicates that a positive going pulse must be applied, with the output changing state when the pulse shifts from positive to negative. If a square wave was applied, the output would change state only on the negative transition of the signal, dependent, of course, on the conditions set up for other inputs.

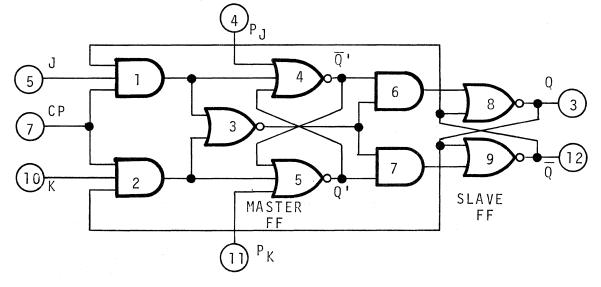

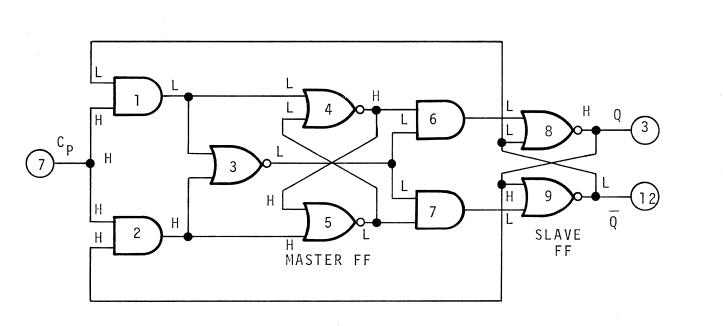

- b. Detailed logic, typical JK (ST 620A)

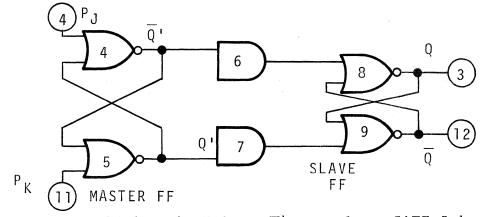

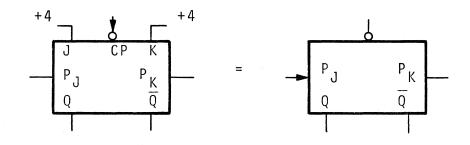

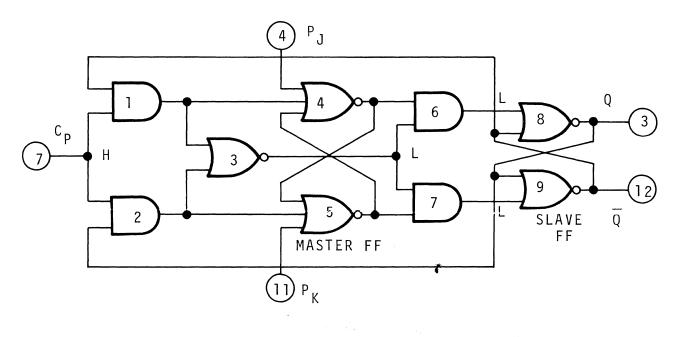

3.4 If pin 7 is tied to ground (a low), then the output of gates 1 and 2 are low and have no effect on the MASTER FF. With two lows as inputs, gate 3 has a high output, and has no effect on Gate 6 and 7, which merely pass the output of the MASTER flip flop to the SLAVE F/F. The logic diagram can be simplified and a truth table developed for PJ and PK.

|     | РJ | РK | Q'    | Q |           |

|-----|----|----|-------|---|-----------|

| (1) | Н  | L  | Н     | Н |           |

| (2) | L  | L  | $Q^1$ | Q | NO CHANGE |

| (3) | L  | Н  | L .   | L |           |

| (4) | Н  | Н  | L*    | Q | NO CHANGE |

\*condition 4 is ambiguous for the master FF, but not for the Slave FF and the output.

(1) With PJ high and PK low,  $\overline{Q}$  goes low; GATE 5 has

two inputs low, so that  $Q^1$  goes high. GATE 9 goes low. The two negative inputs to GATE 8 put its output high.

- (2) If both inputs PJ and PK go low there will be no change in state.

In truth tables it is customary to enter "Q" when the inputs listed cause no change of state.

- (3) Taking PK High and PJ low reverses the flip-flop

- (4) If both PJ and PK are high Q and  $\overline{Q}$  go low, but there is no change in the output. The final state of Q will depend on which level goes positive first.

- The PJ and/or PK inputs are frequently used to put the JK flip flop into a known PRESET condition. 3.5

- This mode of operation makes an RS type flip flop а. out of the JK.

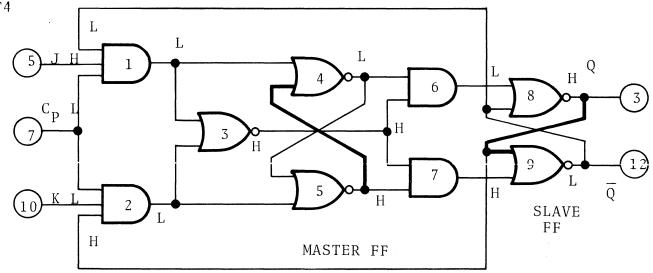

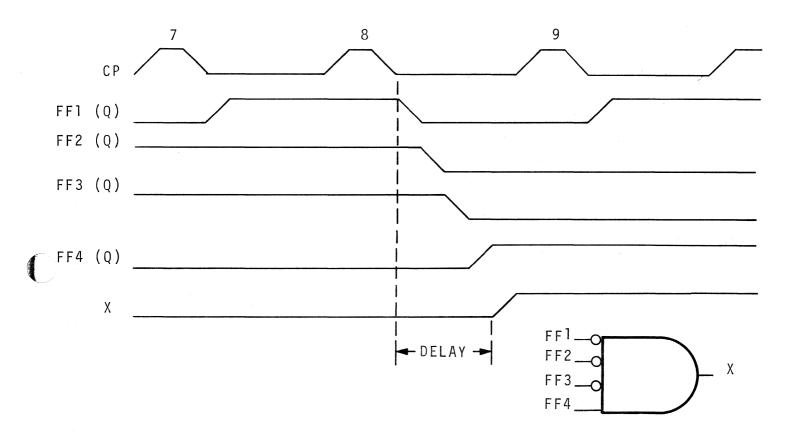

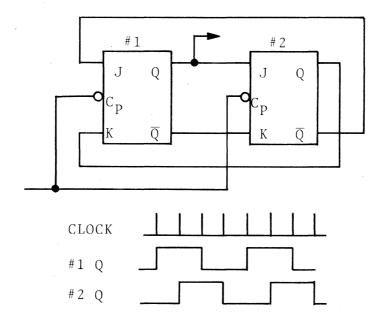

If only the CP input is used, a simple "divide-by-two" 3.6 results.

а.

III-7

,

С.

3.7 Using PJ, PK and the CP inputs, the circuit can act as an RST (Para 2.1) or CP can be used as an inhibit to prevent, during some duration of time, the PJ and PK inputs from affecting the output.

I I I - 8

a. The high condition of CP will cause a high out of Gate 1 or 2 (depending on Q and  $\overline{Q}$ ) inhibiting Gates 1 and 2.

b. When CP goes low Q and Q will follow PJ and PK when they are 180° out of phase, and remain in their previous condition when ever PJ=PK.

AMPEX

- As long as the Cp input is low, any changes in J and 3.9 а. K are not felt in the flip flop.

- When the clock pulse goes high, then the Master FF reacts to changes in J and K, but there is no effect on the slave FF or the output b.

- At the time that the clock pulse goes from a high с. to a low, Q follows J.

| J | K | Qt | Qt+1 |

|---|---|----|------|

| Н | Н | L  | Н    |

| Н | Н | Н  | L    |

| Н | L | Н  | Н    |

| Н | L | L  | Н    |

| L | Н | Н  | L    |

| L | Н | L  | L    |

| L | L | L  | L    |

| L | L | Н  | Н    |

"TOGGLE" OR : 2

Qt clock pulse goes high

Qt+1 clock pulse goes from high to low

4. This section has covered the bi-stable multivibrator or flip-flop in a general way. Sections covering counters and shift registers will cover common applications.

AMPEX

DEPARTMENT

- 4.1 The ST620A J-K flip-flop used as an example is typical but other versions may follow slightly different rules.

- 4.2 The following rules apply generally to the JK flip-flop.

- a. The J and K inputs must not change during the time that a clock pulse goes through a complete cycle.

- b. The state of the master flip-flop is established by the leading edge of the clock pulse transition.

- c. The trailing edge of the clock pulse transfers the Master flip-flop condition to the Slave flip-flop.

- d. In the ease of the ST620A the Pj and Pk inputs affect the output only when the clock pulse input is negative.

- (1) In other types, the equivalent inputs may over-ride all other circuit inputs.

AMPEX H

#### Revision No.2

Training Use Only V-0002

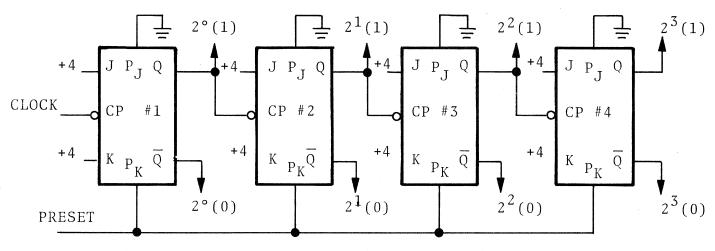

#### SECTION IV BINARY COUNTERS

- 1. In the Television system, it is frequently necessary to count specific events, number of frames, number of lines, etc.. The flip-flop can be configured as a counter to perform this function. It is also acting as a frequency divider.

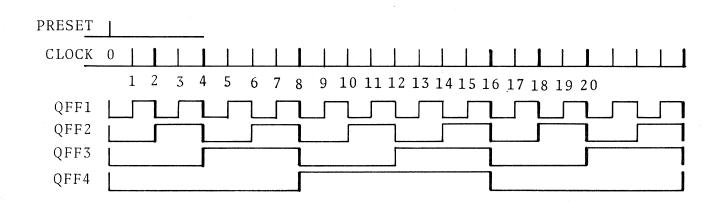

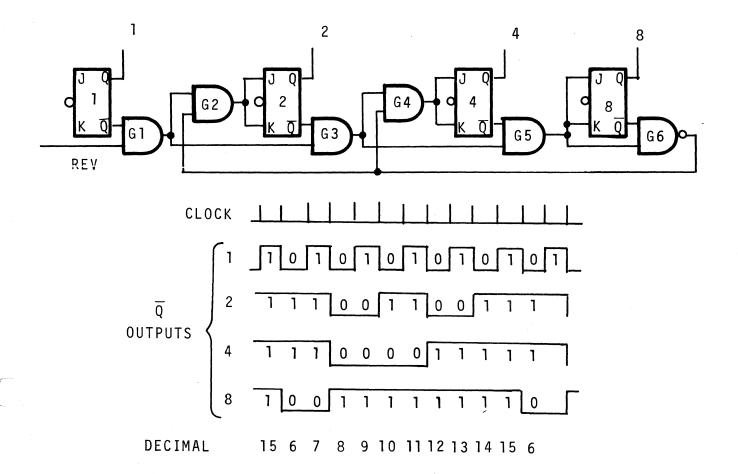

- 2. The "ripple" binary counter. The ST620A discussed under JK FF, is used. Output changes state when CP moves Hi to Lo.

|      |     | Q<br>FF1 | Q<br>FF2 | Q<br>FF3 | Q<br>FF4 | 1<br>2° | 2<br>2 <sup>1</sup> | 4<br>$2^2$ | 8<br>2 <sup>3</sup> | 16<br>2 <sup>4</sup> |

|------|-----|----------|----------|----------|----------|---------|---------------------|------------|---------------------|----------------------|

| PRES | SET | L        | L        | L        | L        | 0       | 0                   | 0          | 0                   | 0                    |

| CI   | P 1 | Н        | L        | L        | L        | 1       | 0                   | 0          | 0                   | 0                    |

|      | 2   | ·L       | Н        | L        | L        | 0       | 1                   | 0          | 0                   | 0                    |

|      | 3   | Н        | Н        | L        | L        | 1       | 1                   | 0          | 0                   | 0                    |

|      | 4   | L        | L        | H        | L        | <br>0   | 0                   | 1          | 0                   | 0                    |

|      | 5   | Н        | L        | Н        | L        | 1       | 0                   | 1          | 0                   | 0                    |

|      | 6   | L        | Н        | H        | L        | 0       | 1                   | 1          | 0                   | 0                    |

|      | 7   | Н        | Н        | Н        | L        | 1       | 1                   | 1          | 0                   | 0                    |

|      | 8   | L        | L        | L        | Н        | 0       | 0                   | 0          | 1                   | 0                    |

|      | 9   | Н        | L        | L        | Н        | 1       | 0                   | 0          | 1                   | 0                    |

|      | 10  | L        | H        | L        | Н        | 0       | 1                   | 0          | 1                   | 0                    |

|      | 11  | Н        | Н        | L        | Н        | 1       | 1                   | 0          | 1                   | 0                    |

|      | 12  | L        | L        | Н        | Н        | 0       | 0                   | 1          | 1                   | 0                    |

|      | 13  | Н        | L        | Н        | Н        | 1       | 0                   | 1          | 1                   | 0                    |

|      | 14  | L        | Н        | Н        | Н        | <br>0   | 1                   | 1          | 1                   | 0                    |

|      | 15  | Н        | Н        | Н        | Н        | 1       | 1                   | 1          | 1                   | 0                    |

|      | 16  | L        | L        | L        | L        | 0       | 0                   | 0          | 0                   | 1                    |

|      | 17  | Н        | L        | L        | L        | 1       | 0                   | 0          | 0                   | 1                    |

|      | 18  | L        | Н        | L        | L        | 0       | 1                   | 0          | 0                   | 1                    |

|      | 19  | Н        | Н        | L        | L        | 1       | 1                   | 0          | 0                   | 1                    |

|      | 20  | L        | L        | Н        | L        | 0       | 0                   | 1          | 0                   | 1                    |

2.1 By tabling the conditions of the flip-flops, the similarity to the binary numbering system is apparent.

,

AMPEX H

# 2.2 If FF1 is defined as $2^{\circ}$ , FF2 as $2^{1}$ , FF3 as $2^{2}$ , and FF3 as $2^{3}$ .

- a. Looking at the outputs of the four stages after

a certain number of clock pulses have occurred

can be converted (High = 1, Low = 0) to an equivalent

binary number defining the number of clock pulses.

- b. Using four stages any one of fifteen clock pulses can be uniquely defined. But at the sixteenth pulse, all flip-flops return to their "PRESET" state. All Q outputs are low.

- a binary counter can uniquely define a binary number equal to  $2^n$ -1, where N equals the total number of flip-flops.

- in the case above, 2<sup>4</sup>-1 or 16-1=15 pulses are uniquely defined by the four stage counter.

- c. Each stage is dividing by two. Assuming a Clock Pulse rate of 15kHz, then:

| FF1 | out     | = | 7.5kHz   |

|-----|---------|---|----------|

| FF2 |         | = | 3.75kHz  |

| FF3 | · · · · | = | 1.875kHz |

| FF4 |         | = | 9375kHz  |

- d. A flip-flop changes state only when the "Q" side of all previous stages move from a high to a low

- to determine the state of the flip-flops after the eighth pulse in, look at the binary equivalent of decimal 8-1000 (MSB on the left) and convert the zero's and ones to lows and highs.

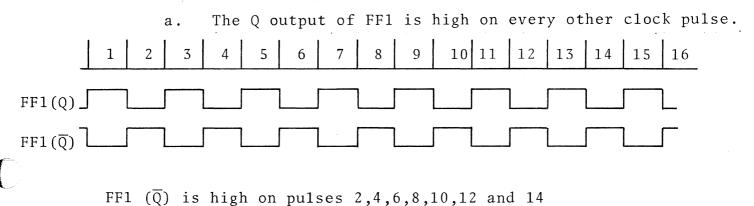

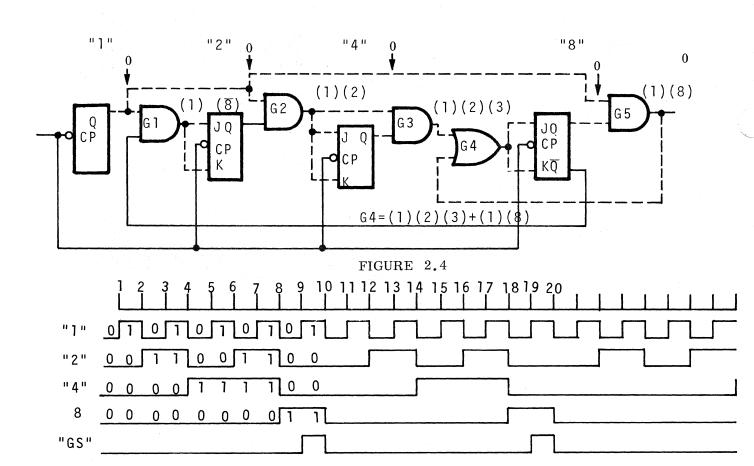

- 3.0 Decoding the counter condition.

- 3.1 To determine the time at which the twelfth clock pulse is received, Binary 1100.

d. ANDing  $FF1(\overline{Q})$ ,  $FF2(\overline{Q})$ , FF3(Q) and FF4(Q) will uniquely define clock pulse 12

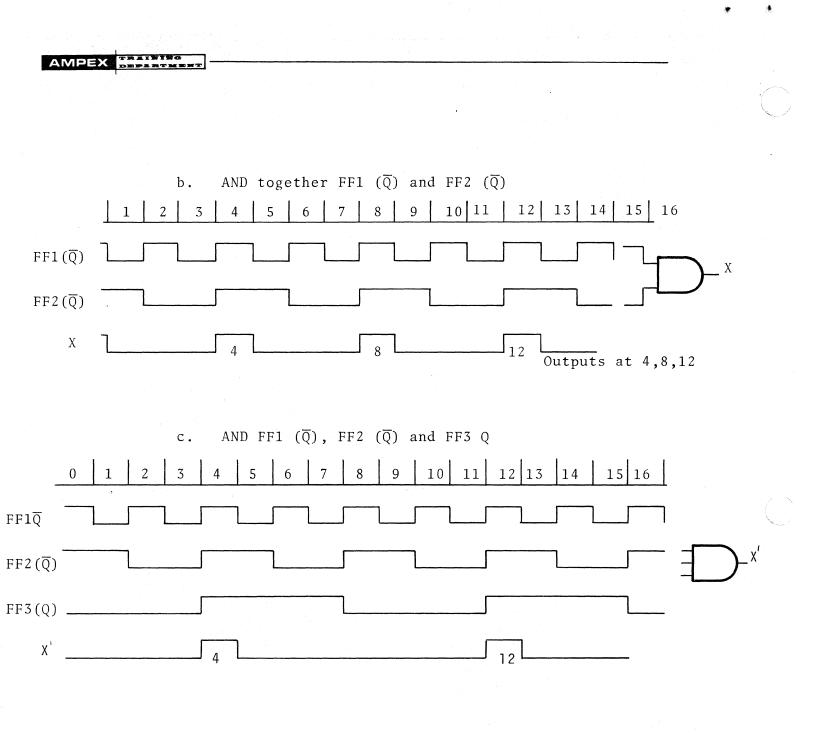

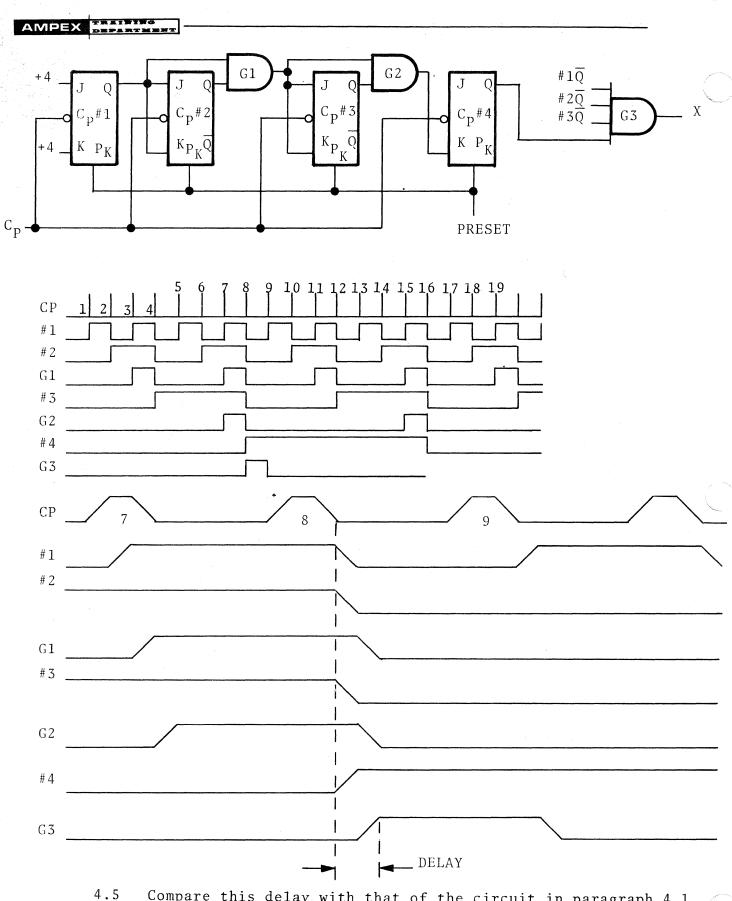

4.1 The "ripple" binary counter is relatively slow. Succeeding stages are changed when the previous stage Q output moves negative. But a definite time is required to affect the following stage. Worst case in this four stage counter would be the 8th pulse, where all four stages change state.

- 4.2 In the rather exaggerated case above an output pulse from the decode gate is delayed almost a full cycle with respect to the input pulse.

- 4.3 In some cases the delay, with respect to the frequency of the input pulses, is unimportant, but should be taken into account when examining timing relationships. In other cases special counter circuits have been devised to minimize the ripple delay.

- 4.4 When the amount of delay cannot be tolerated, the other circuits are necessary.

Compare this delay with that of the circuit in paragraph 4.1

IV-6

| AMPEX   | TRAINING<br>DEPARTMENT |

|---------|------------------------|

| TRAININ | G USE ONLY             |

| V00     | 19                     |

| · RFV   | #2                     |

SECTION 5: BINARY CODED COUNTERS

- 1.0. The counters discussed in the previous section were limited in that they could only divide by 2 so that outputs would always be directly related to a power of 2.

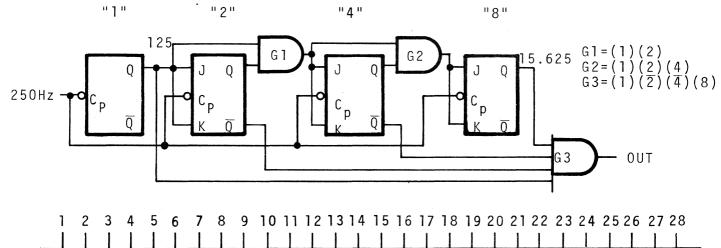

- 2.0. There is then no provision for divide by 3,5, or 10, among others. A requirement in the AVR-1 is to count 250HZ down to 25HZ - divide by 10.

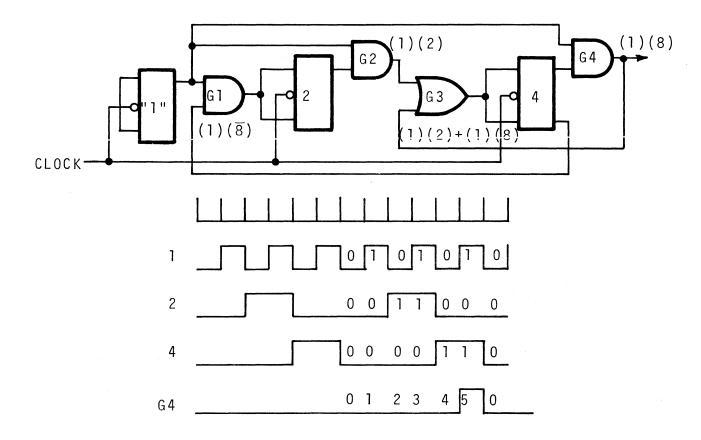

- 2.2. To count to ten a four stage counter must be used, and a decode gate can be used to identify the tenth pulse received.

2.3.

This decodes a binary ten, but the counter does not return to zero until the sixteenth pulse, so that the next output occurs 15 pulses later.

| 10. <u>-</u> |      | T        | RAI | MIMO  |          |

|--------------|------|----------|-----|-------|----------|

|              | IPE> | <b>3</b> |     | RTMMM | <u> </u> |

2.4.

To make it divide by ten, the output pulse must return the counter to the state it was in before the first pulse was received.

One method would be to take the Gate 3 output Α. back to clear inputs and zero the counter.

- However, the tenth clock pulse will return stage "1'" to that state ( $\overline{Q}$  high); the "4" stage is al-Β. ready in that state.

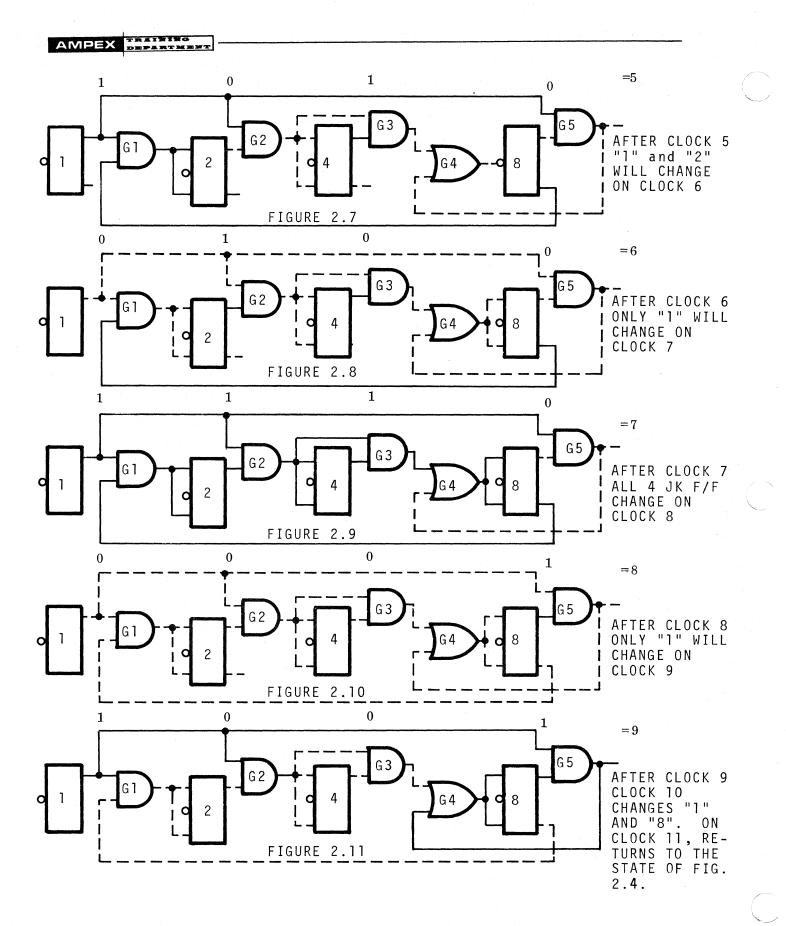

- All that is necessary is to prevent the "2" stage from clocking, and to reset the "8" stage. Logic С. equations for controlling all the flip-flops can be written, and then the required gates put in.

- Stage 1 Allowed to clock as a straight 1. divide by 2.

- Stage 2 Not allowed to clock if "8" is high 2.

- Stage 3 Clock whenever "1" and "2" are high. Stage 4 Clock when "1", "2", and "4" are high or when "1" and "8" are high. 3. 4.

ģ.

D. Remember that the JK flip-flop acts as a divide by two only if the J and K inputs are high prior to the clock pulse.

AMPEX

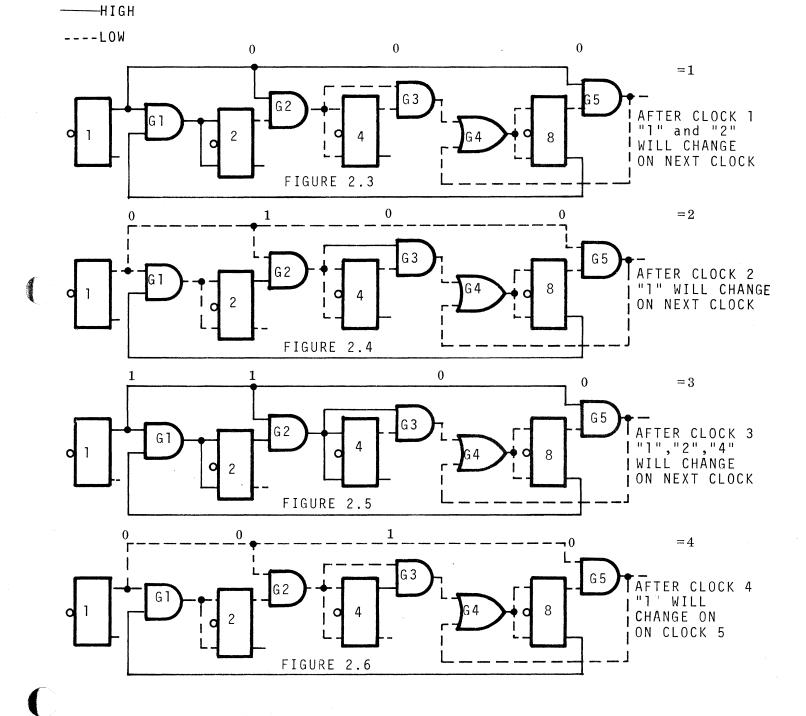

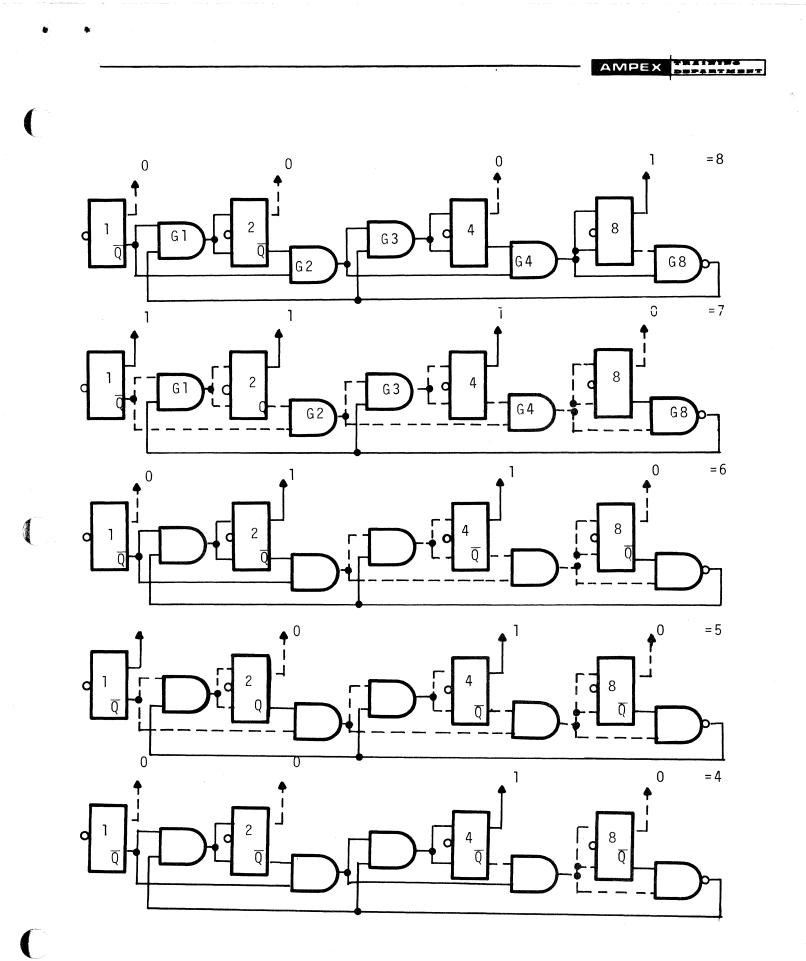

E. Figures 2.3 through 2.11 describe the state of the counter after each clock pulse.

2.5.

This is sometimes called a "permuted" counter

V-3

V - 4

AMPEX

2.6. The technique used here to develop a divide by ten can also be used to design a counter to divide by any factor. Α. Briefly, feedback is applied to certain stages of a divide by 2 counter to return it to the initial reset state as soon as the desired count is reached in this example, ten. 3.0. Binary Coded Counters. 3.1. Another disadvantage of the binary counter is that it has a two finger mentality. A display of 111000010000 (LSD on right), representing 3600 seconds - one hour, can be used internally for computation, but would be impractical as a readout for those of us more familar with our numbering system of ten discrete digits. 3.2. While elaborate decoding networks could be devised, a more frequently used system uses a binary code to describe decimal numbers. Each decimal number is separately coded. "49" in straight binary is 11001 (LSD on right) Α. or  $(2^{\circ})(\overline{2}^{1})(\overline{2}^{2})(\overline{2}^{3})(2^{4})(2^{5})$  from a 6 stage binary counter. Β. To display this in decimal an AND GATE could drive the "4" nixie in one column and the "9" nixie in the next. С. To discretely display 00 through 49 - 50 decode gates would be required, each with 5 inputs.While logic analysis could propably reduce the number of gates, it is a complex system.

3.3.

A binary coded decimal simplifies the problem. While several codes are possible, only the 8-4-2-1 will be discussed.

|     |   |  | TR     | AI. | <b>N X X</b> | A G |   |

|-----|---|--|--------|-----|--------------|-----|---|

| JI) | 4 |  | <br>DR | -   | R T          | -   | T |

3.4.

Using a four stage counter with proper feedback to make it into a divide by ten, each of the ten digits of the decimal system can be defined.

Α.

| BINARY        | COUNTER STAGES                                                             |         |

|---------------|----------------------------------------------------------------------------|---------|

| 8 - 4 - 2 - 1 | $1 - \frac{2}{3} - \frac{4}{5} - \frac{8}{5}$                              | DECIMAL |

| 0 0 0 0       | $(\overline{2}^{0})(2^{\overline{1}})(2^{\overline{2}})(\overline{2}^{3})$ | 0       |

| 0001          | $(2^{0})(\overline{2}^{1})(\overline{2}^{2})(\overline{2}^{3})$            | 1       |

| 0 0 1 0       | $(\overline{2}^{0})(2^{1})(\overline{2}^{2})(\overline{2}^{3})$            | 2       |

| 0011          | $(2^{0})(2^{1})(\overline{2}^{2})(\overline{2}^{3})$                       | 3       |

| 0 1 0 0       | $(\overline{2}^{0})(\overline{2}^{1})(2^{2})(\overline{2}^{3})$            | 4       |

| 0 1 0 1       | $(2^{0})(\overline{2}^{1})(2^{2})(\overline{2}^{3})$                       | 5       |

| 0 1 1 0       | $(\overline{2}^{0})(2^{1})(2^{2})(\overline{2}^{3})$                       | 6       |

| 0 1 1 1       | $(2^{0})(2^{1})(2^{2})(\overline{2}^{3})$                                  | 7       |

| 1000          | $(\overline{2}^{0})(\overline{2}^{1})(\overline{2}^{2})(2^{3})$            | 8       |

| 1001          | $(2^{0})(\overline{2}^{1})(\overline{2}^{2})(2^{3})$                       | 9       |

|               |                                                                            |         |

B. The number 49 would then be two coded groups 0100 - 1001.

C. If the most significant digit, 4 in this case,

is not going to exceed 5, then only 3 stage counter is needed in that position. It must return to zero when 5 is reached - a case is the tape timer, where 59 seconds is displayed in the largest number.

D. A six-stage binary counter will define the

- numbers  $2^6 1 = 64 1 = 63$ .

- E. The binary coded counter requires seven flipflops, but the decoding process is simpler. A T,I SN7441, to be described later, will convert a 4 wire binary coded decimal to a ten wire decimal output.

- 3.5. The electronic tape timer schematically looks extremely complex; actually it is basically the same circuit repeated for frames, seconds, minutes and hours, where each requires two binary coded counters to describe the decimal numbers.

- 3.6. The counter described in section 2.6-C is used for the least significant digit, since it can be anything from "0" to "9".

1.7.53.44.6 AMPEX

3.6.

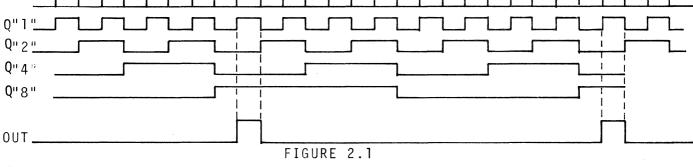

A. Tens of seconds and tens of minutes use only the digits "O" through 5, so a three stage counter will suffice.

B. If this were the tens of seconds counter, then the pulse out of G4 would enable the Units of Minutes Counter J and K inputs to advance on the next clock pulse.

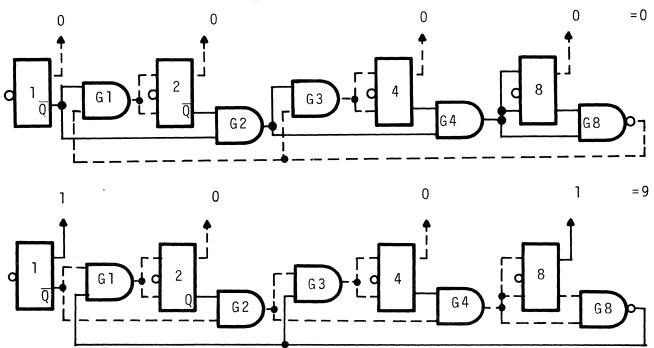

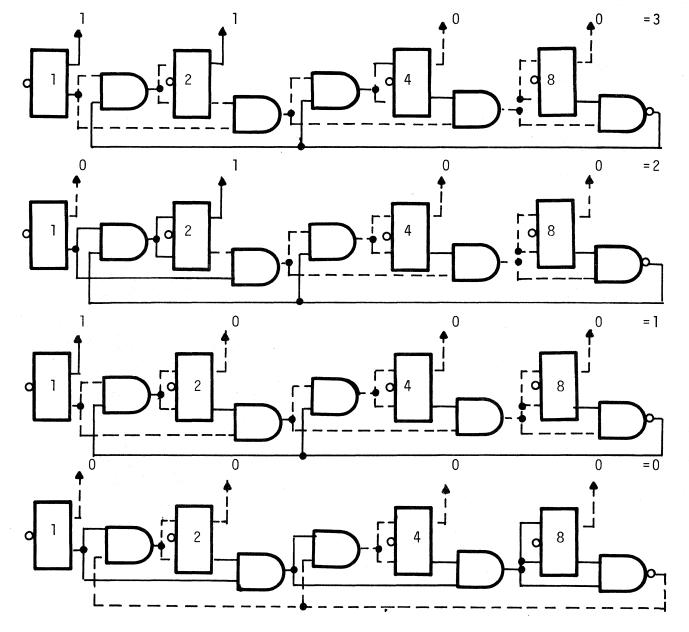

4.0. Counting backwards.

4.1. The tape timer must be able to count in reverse the decimal digits decreasing. The outputs to drive the display are always taken from the same side - the Q output.

| AAAA |   | DRIGIART   |  |

|------|---|------------|--|

| ANDE | 1 | DEPERTMENT |  |

4.2.

| Compare | the Q and | <u></u> οι | tputs  | of  | the | binary | coded |  |

|---------|-----------|------------|--------|-----|-----|--------|-------|--|

| counter | when coun | ting       | forwar | ٠d. |     |        |       |  |

|   |   |   | Junioer | when ocurreng |   |   |   |   |         |  |

|---|---|---|---------|---------------|---|---|---|---|---------|--|

|   | Q |   |         | DECIMAL       |   | Ī | Ī |   | DECIMAL |  |

| 8 | 4 | 2 | 1       |               | 8 | 4 | 2 | T |         |  |

| 0 | 0 | 0 | 0       | 0             | ٦ | 1 | 1 | 1 | 15      |  |

| 0 | 0 | 0 | 1       | 1             | 1 | ٦ | 1 | 0 | 14      |  |

| 0 | 0 | 1 | 0       | 2             | 1 | 1 | 0 | 1 | 13      |  |

| 0 | 0 | 1 | 1       | 3             | ٦ | 1 | 0 | 0 | 12      |  |

| 0 | 1 | 0 | 0       | 4             | 1 | 0 | 1 | 1 | 11      |  |

| 0 | 1 | 0 | 1       | 5             | 1 | 0 | 1 | 0 | 10      |  |

| 0 | 1 | 1 | 0       | 6             | 1 | 0 | 0 | 1 | 9       |  |

| 0 | 1 | 1 | 1       | 7             | ٦ | 0 | 0 | 0 | 8       |  |

| 1 | 0 | 0 | 0       | 8             | 0 | 1 | ٦ | 1 | 7       |  |

| 1 | 0 | 0 | 1       | 9             | 0 | 1 | 1 | 0 | 6       |  |

| 0 | 0 | 0 | 0       | 0             | 1 | 1 | 1 | 1 | 15      |  |

|   |   |   |         |               |   |   |   |   |         |  |

4.3.

When counting in reverse, a feedback network utilizing the Q outputs is used which, with succeeding clock pulses progresses 1111, 0110, 0111, (15,6,7) etc. The outputs of the Q side to drive the decoder will progress 0000, 1001, 1000 (0,9,8) etc.

A. The  $\overline{\mathbb{Q}}$  side is used because the Q sides are used when counting forward. If the counter always counted backwards, then suitable feedback could be arranged for that side.

V-8

۷-9

.

.

FIGURE 4.1 ÷10 COUNTER, IN REVERSE MODE

AMPEX HIM

4.4.

4.5.

The full counter, capable of counting in either direction on command would contain these gates and the feedback for a forward count.

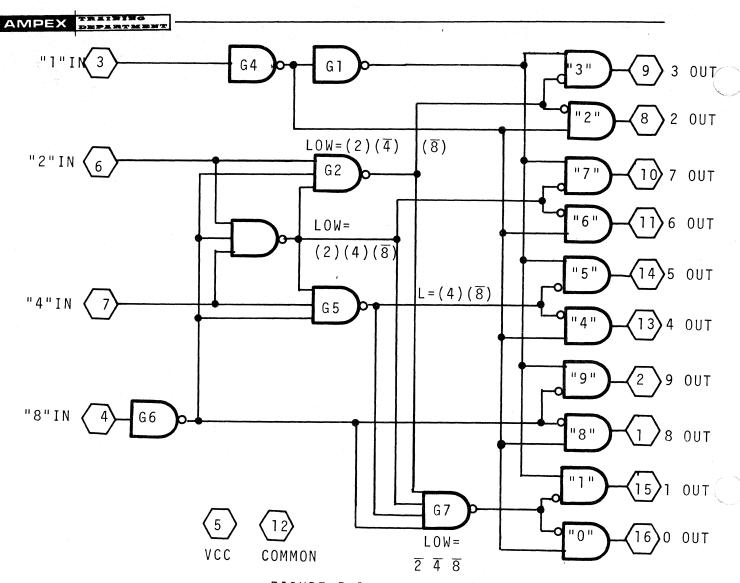

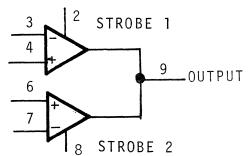

5.0. BCD to decimal decoder.

5.1. The Texas Instruments SN7441AN, is a BCD to decimal decoder in single package capable of directly driving gas filled cold-cathode indicator tubes.

V11

FIGURE 5.1 BCD TO DECIMAL DECODER

6.0.

Comparison Decoding

6.1.

Another form of decoding involves comparing the output of two devices and producing an output. A. The tape timer external event capability, where switch outputs are compared with the contents of

- the tape timer or decoded tape address.

- B. The RA4000 which compares a requested location with tape addresses code.

- C. The frame counter on the HS100.

AMPEX

6.2.

While again schematically it looks quite complicated, it is a simple circuit. The AVR-1 event comparator has some 81 gates, plus inverts and control logic. But the heart of it is an exclusive OR. Twenty-six separate bits in the binary coded "time word" must each be compared with a similar number of outputs from the switches.

Α. The output of an exclusive OR is High only when the inputs are different. If both the inputs are the same, the output is low. So whether searching for a "zero" or "one" in the comparison makes no difference - the output goes low when the input is identical.

7.0. CLEARING or Presetting the Counter.

- Under certain conditions, such as turn on, it may be desireable to Reset the counter to zero, or even hold it at zero for some time.

- The clear (C<sub>D</sub>) input is used. This input over-Α. rides the J K and Clock ( $C_{p}$ ) inputs.

- If it is held negative, then all  $\overline{Q}$  outputs will be high, and Q outputs low or the display will Β. read zero.

7.2.

7.1.

- To PRESET the counter to a previously determined count - either from a random selector such as thumbwheels, or from a fixed predetermined logic, the counter is first cleared using the CD inputs. Then lows are applied to the set (SD) inputs of

- Α. those stages it is desired to put in a "1" state.

AMPEX DEPARTMENT

TRAINING USE ONLY V0023

REV 2

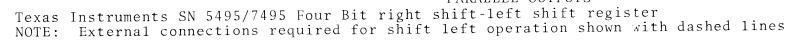

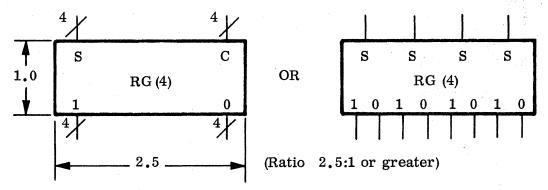

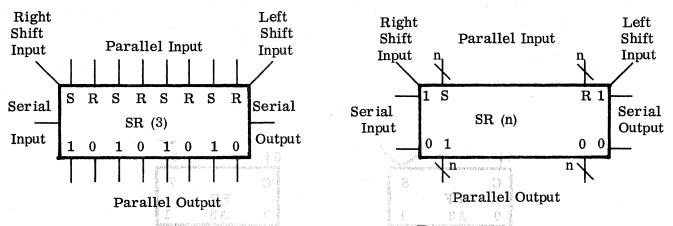

SECTION 6: THE SHIFT REGISTER

- 1. In general, the state of a binary counter stage after a clock pulse depends on the condition of all previous stages prior to the clock pulse.

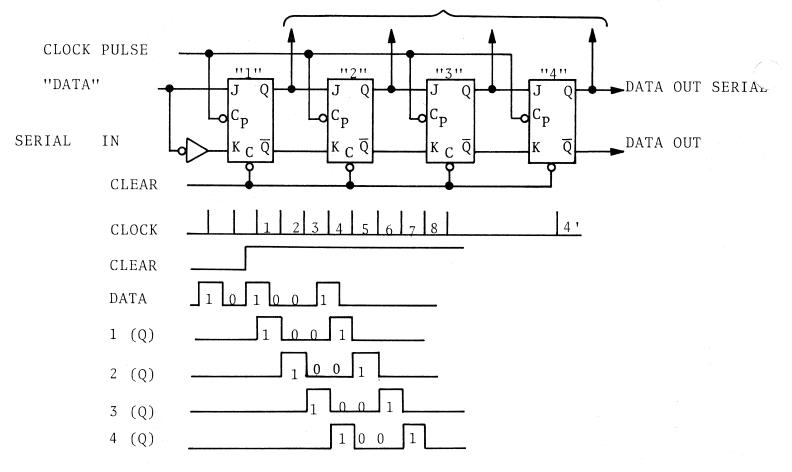

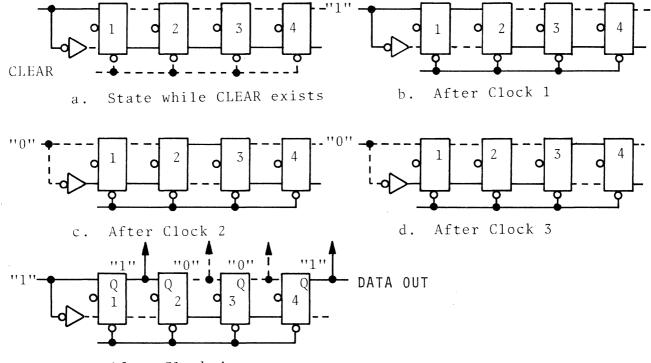

- 2. In a shift register, in general, the condition of a particular stage after the clock pulse depends only on the conditions existing at the output of the previous stage prior to the application of the clock pulse.

- 2.1 The term "shift register" is frequently shortened to "register"

a. The clock pulses are usually called "shift pulses".

- 2.2 The term "ring counter" usually describes a special application of the shift register.

- 2.3 It can be used as a short term memory or storage device. Information can be retrieved without destruction.

- 2.4 The register can convert "serial" information into "parallel" data.

- a. The television tube could be considered a serial to parallel converter. The television signal is transmitted serially - any instant of time contains one bit of information; or a horizontal sync pulse is followed by 1/525th of the total information required to display a complete television frame or picture.

- b. Because of phosphor persistance, the information presented serially over a period of 33 milliseconds seems to appear instantaneously. Continuous updating with new information produces the illusion of motion.

- c. The waveform monitor, particularly when operated at a field rate, displays the same information in its serial format.

- 2.5 The register can also convert parallel information into a serial format.

- a. The television camera converts the scene in front of the lens into the serial television signal required for transmission.

2.6 As a memory device, the shift register may accept information in parallel form, hold (delay) it, and then transmit it in serial form or parallel. It can also accept serial information and store it, then read it out in either serial or parallel form.

- 2.7 The RA-4000 TIME CODE GENERATOR puts the information from a clock counter into a register in parallel form, then reads it out on to tape in serial form.

- a. The RA-4000 TIME CODE READER takes the serial information coming off of tape, puts it into a register; then the parallel outputs of the register drive a binary to decimal decoder and displays the output on a nixie readout.

- 3. Review of the J-K Flip-Flop

TRAINING

MPEX

- 3.1 If both J and K are HIGH, the F/F acts as a divide by two whenever both J and K are high and the Clock Pulse shifts positive to negative.

- a. In the counter application J and K were tied together.

- b. If J and K are separately controlled, the Q follows J on the clock pulse transition.

- c.  $S_{D}$  and  $C_{D}$  override any other inputs.

## 3.2 TRUTH TABLE, typical J-K Flip-Flop

$(Q_n+1 \text{ is time after clock pulse has made plus-minus change})$

| PRESET,                | J<br>ANY | K<br>STATE | S <sub>D</sub><br>LOW | C <sub>D</sub><br>LOW | Q<br>HIGH | Q <sub>n+1</sub><br>HIGH | ₹<br>NIGH | Q <sub>n+1</sub><br>HIGH (N.D.) |

|------------------------|----------|------------|-----------------------|-----------------------|-----------|--------------------------|-----------|---------------------------------|

| RESET,                 | ANY      | STATE      | HIGH                  | LOW                   | LOW       | HIGH                     | HIGH      | HIGH                            |

| PARALLEL DATA<br>INPUT | ANY      | STATE      | LOW                   | HIGH                  | HIGH      | HIGH                     | LOW       | LOW                             |

| BINARY OR BCD          | HIGH     | HIGH       | HIGH                  | HIGH                  | HIGH      | LOW                      | LOW       | HIGH                            |

| COUNTER DIVIDE<br>BY 2 | HIGH     | HIGH       | HIGH                  | HIGH                  | LOW       | HIGH                     | HIGH      | LOW                             |

|                        | LOW      | LOW        | HIGH                  | HIGH                  | LOW       | LOW                      | HIGH      | HIGH                            |

| INHIBIT (STORE)        | LOW      | LOW        | HIGH                  | HIGH                  | HIGH      | HIGH                     | LOW       | LOW                             |

| SHIFT                  | HIGH     | LOW        | HIGH                  | HIGH                  | LOW       | HIGH                     | HIGH      | LOW                             |

| REGISTER               | HIGH     | LOW        | HIGH                  | HIGH                  | HIGH      | HIGH                     | LOW       | LOW                             |

| ⊃PERATION              | LOW      | HIGH       | HIGH                  | HIGH                  | HIGH      | LOW                      | LOW       | HIGH                            |

| SERIAL                 | LOW      | HIGH       | HIGH                  | HIGH                  | LOW       | LOW                      | HIGH      | HIGH                            |

- 3.3 The state of J and K must be established prior to the clock pulse transition from positive to negative.

- 4. The J-K as a memory or delay device.

- 4.1 In the AVR-1 Control System, a flip/flop is set by hitting the PLAY button momentarily. The flip/flop remains set until STOP or SHUTTLE is commanded, remembering that the machine is to be in PLAY.

- 4.2 Another application, which is in a sense a one stage shift register is the retiming application. It is frequently necessary to retime a random event to a precise oscillator, or to external information.

- a. In the HS-100, the slow motion rate is determined by a free running oscillator operating at approximately the desired frame rate. The oscillator is retimed using vertical sync.

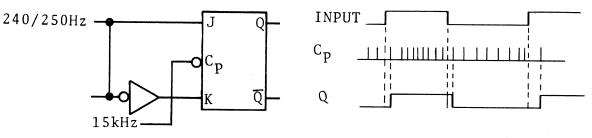

In the AVR-1 Blanking Switcher, the Headwheel tachometer signal is retimed so that each of its transitions occur during horizontal blanking - or each edge of the 240/250 Hz signal is delayed up to 64 microseconds.

- c. The above techniques are also referred to as "Time Quantizing".

- 5. The basic shift register.

DATA OUT PARALLEL

5.1 Step by Step Operation

,

e. After Clock 4

6. To produce a two phase output with  $90^{\circ}$  between phases:

#### AMPEX DEPARTMENT

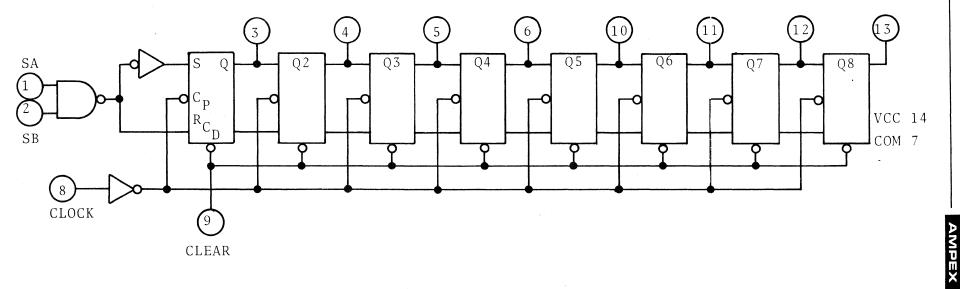

The Shift Register is available as an integrated circuit

Fairchild FC9328 Dual 8 Bit Shift Register, AMPEX P/N 586-303.

a. Used in MK IV EDITOR (AVR-1)

- b. Includes two eight stage shift registers

- c. Serial in, serial out capability only

- d. The register shifts on the positive transition of the clock.

- e. A negative on the CLEAR holds all stages reset, and Q7 (the eighth stage) is low

7.2 The National Semiconductor DM8870, AMPEX P/N 586-450 serial in/parallel out register contain a single 8 bit register.

training Department

V I - 7

# AMPEX DEPARTMENT

- a. Clocks on positive transition.

- b. Negative on CLEAR holds through Q8 low.

- c. Q8 output is equivalent to Q7 output on the Fairchild 9328.

- d. Used in MK IV EDITOR (AVR-1)

PARALLEL OUTPUTS

TRAINING AMPEX

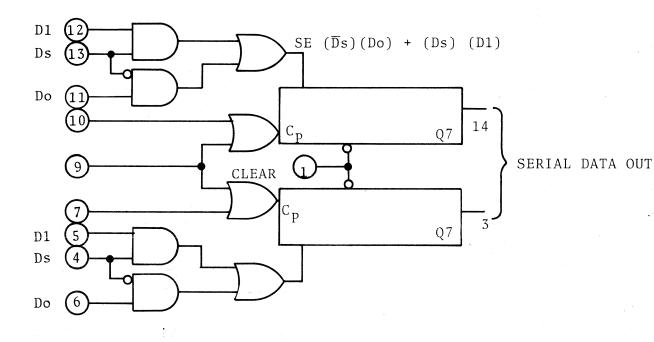

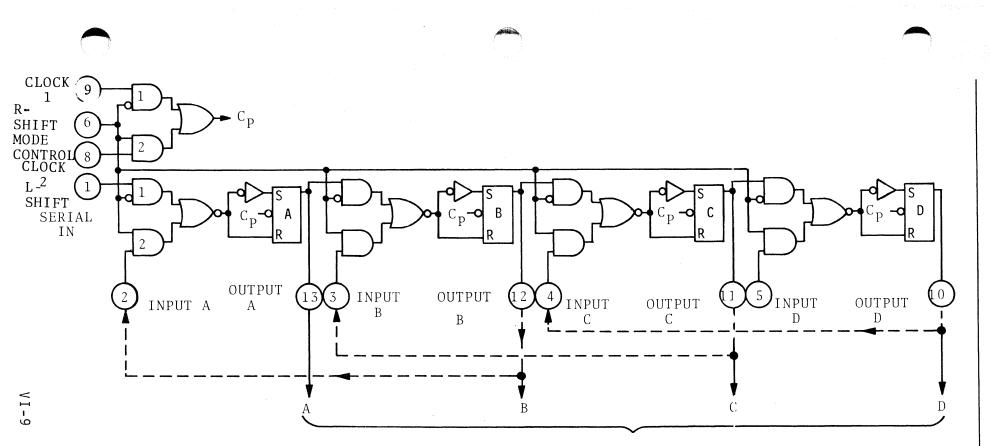

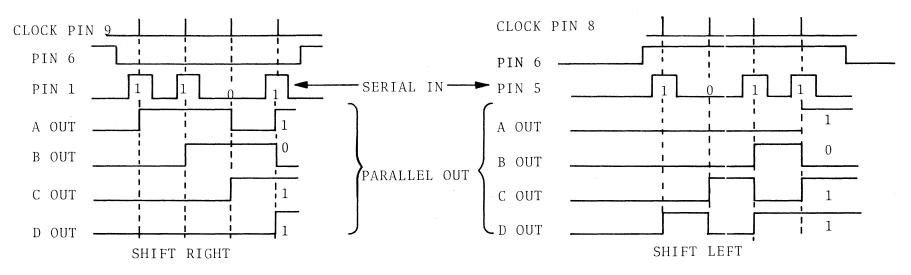

- 8. The Texas Instruments SN 5495/7495 Four Bit Right Shift -Left Shift Register is a very flexible unit.

- a. Serial in, serial or parallel out

- b. Date may be shifted in from two directions

- c. Clocked parallel input

- d. Data transfer occurs when the clock pulse shifts from a high to a low.

- 8.1 In RA-4000 operation the format of serial time code information recovered from magnetic tape depends on the direction of tape travel - the most significant bits may be deserialize and standardize the format.

- 8.2 The SN7495 may be operated in a shift right-shift left mode to accomplish this.

- a. If a low is applied to pin 6 "MODE CONTROL", the number 1 gate are enabled. Clock pulses at pin 9 "CLOCK 1 RIGHT SHIFT" will move data appearing at pin 1 "SERIAL IN" to be shifted to the right, A-B-C-D.

- 8.3 If it is connected as shown, with the output of each stage connected to the input of the previous stage, data can be entered serially in the opposite direction.

- a. With a high on pin 6 "MODE CONTROL" the Number 2 gates are enabled.

- b. Clock pulses are applied to pin 8 "CLOCK 2 LEFT SHIFT" and serial data to pin 5 "INPUT D". The data is shifted on successive clock pulses from "D" to "C" to "B" to "A".

- c. Outputs "A", "B", "C", and "D" provide parallel information

- 8.4 The register may also be connected for parallel input operation. Pins 2,3,4, and 5 are parallel inputs where the information will be entered when pin 6 "MODE CONTROL" is high, and a clock pulse occurs at pin 8 "CLOCK 2" input.

- a. The data could then be shifted out serially by causing "MODE CONTROL" input to go low, and applying clock pulses to pin 9. Serial data would appear at pin 10, "OUTPUT D".

- b. If the serial data out at Pin 10 (OUTPUT "D") were to be fed back to serial data input pin 1 (SERIAL IN) the register would be in ring type configuration such that the same data could be continuously shifted and read out in parallel and/or serial format.

- c. In actual operation all of these modes and their distinct operations could be controlled by proper "time share" gating.

AMPEX

TRAINING USE ONLY VOO17

NOTE:

Some of us tend to forget the basic electronic circuits we learned. This series by the AMPEX Training Department is intended primarily as a rapid review and summary. For this section, we suggest you review the section on Resistance/ Capacitance time constant concept in your favorite basic text.

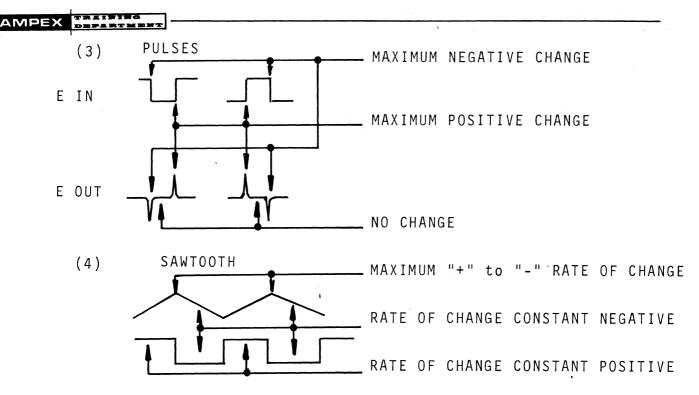

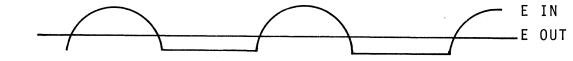

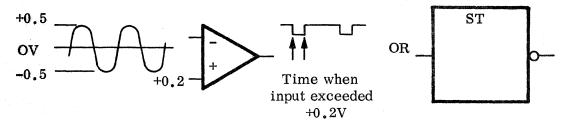

- 1.0. A common requirement in pulse circuits of the narrowing of a wide pulse, or defining the leading and trailing edge of a pulse. Frequently, a large amount of pulse delay is required, without the use of LC type delay lines.

- The most frequently seen circuit is some variation of the RC (Resistance/Capacitance) network. A. Some common names for such circuits are "delay"; "boxcar"; "pulse former"; "differentiator".

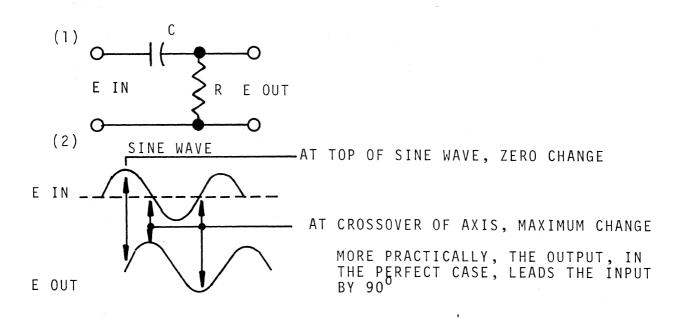

- The term "differentiator" is derived from the calculus

- A. It defines the process of measuring the rate of change of a waveform.

- B. By the proper choice of resistance and capacitance, the mathematical process can be electrically simulated.

1.2.

1.1.

1.2.

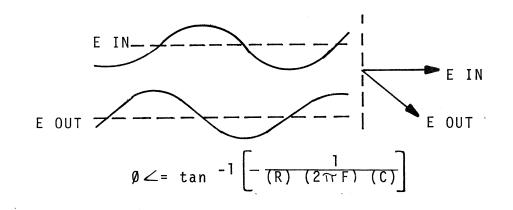

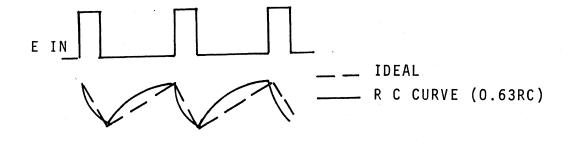

- C. Theoretically differentiation is mathematically perfect if the time constant, equal to R x C, is infinitesimal. Of course under these conditions the output voltage is also infinitesimal. The real value of a practical RC network will determine the amount of phase shift of a sine wave, or the width of the output pulse when a square wave is applied.

- D. It may be more familiar as the grid or base coupling circuit of a resistance coupled amplifier, but with the resistance and capacitance selected so as not to pass low frequencies. It is a high pass filter. "R" and "C" are selected on the basis of the lowest frequency that must be passed.

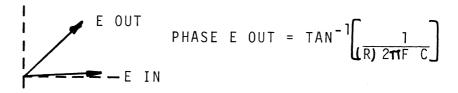

1.3

The circuit is sometimes used to deliberately introduce a specific amount of phase shift.

1.4

It is more frequently encountered in circuits requiring sharply defined pulses.

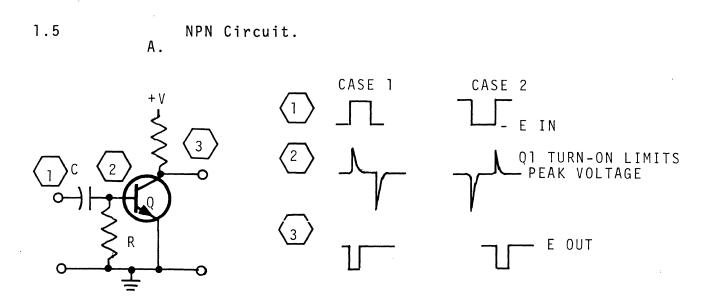

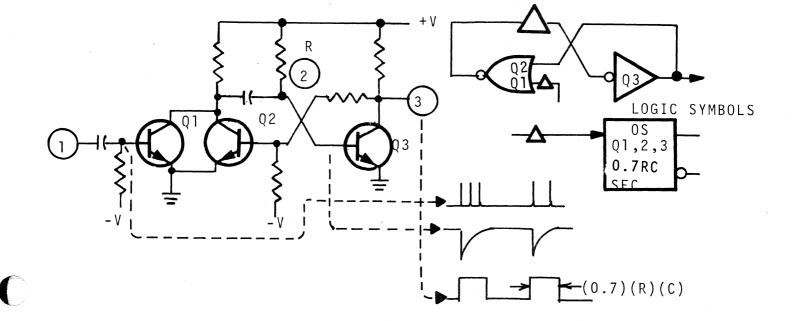

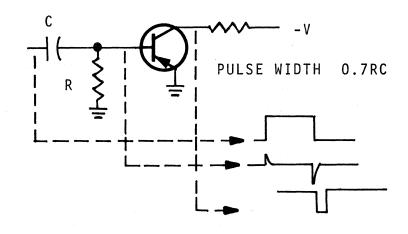

B. The output pulse width equals approximately 0.7 RC

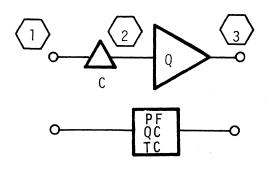

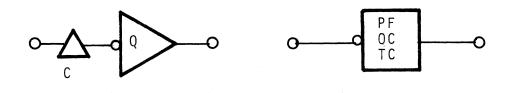

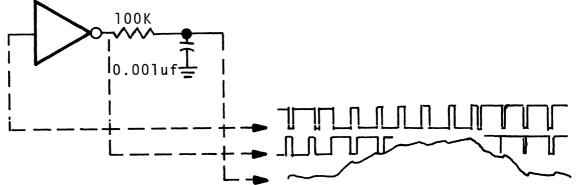

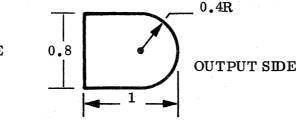

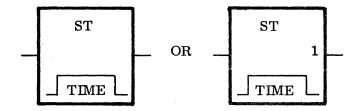

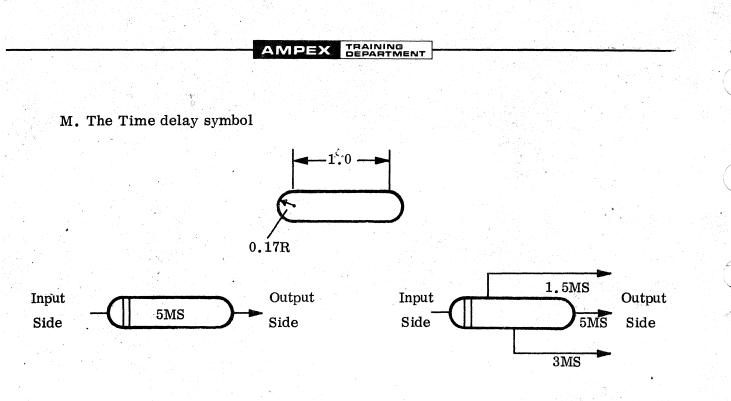

C. AMPEX Training Department block diagrams have used the following symbol:

AMPEX

PART

D. Case 2 represents delay.

DEPARTM AMPEX

1.6.

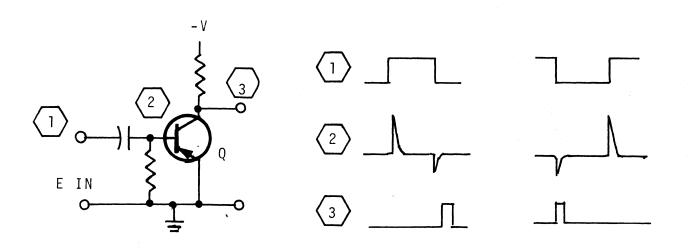

PNP Circuit A.

,

B. Symbols used.

C. On block diagrams, the period of the final pulse is included only when it is important in understanding the circuit.

1.7.

When the network is used with integrated circuits ("chips") all or part of the "R" in the RC equation may be internal to the chip, and must be taken into account, when computing the time constant to determine the pulse width. The multiplying factor may be included on the manufacturer's spec sheet.

AMPEX

2.0 2.1.

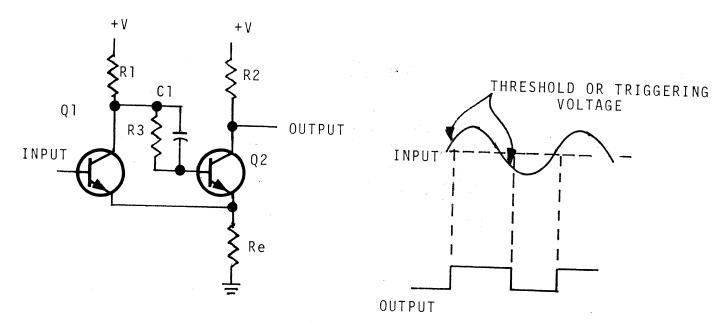

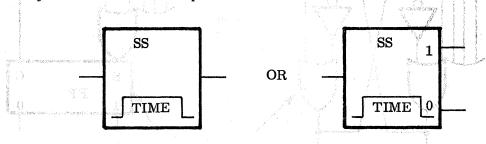

#### THE MONO STABLE MULTIVIBRATOR

The flip-flop, or bi-stable multivibrator is basically two saturation type amplifiers with 100% feedback. It normally assumes one of two states indefinitely until triggered into a reverse condition. It is duscussed in Section III.

2.2.

If one of the feedback paths is changed to an RC differentiator network, the result is: a circuit designated:

- ONE ŠHOT (O.S.) Single Shot (SS) Α.

- Β.

- С. Delay multivibrator, or delay multi

- D. Monostable multivibrator, or simply "mono"

2.4.

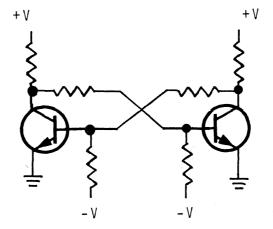

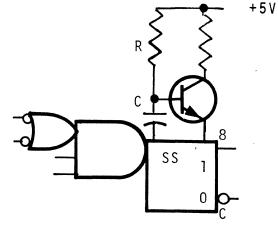

Collector Driven One Shot

# AMPEX

- A. In the stable state Q3 is conducting, and the output 3 is close to ground.

- B. Q1/Q2 are off, and their collectors are positiveC. A positive trigger on the base of Q1 send its

- collector to ward ground

- D. The negative shift is differentiated by RC, and the pulse turns off Q3.

- E. The feedback from the collector of Q3 to the base of Q2 keeps it conducting for 0.7 RC.

- F. Any input pulses during the active time of the one shot are ignored-the one shot in this case is nonretriggerable.

- G. Output may be taken from either side

- 2.5.

- If R is made variable, then the period of the oneshot can be adjusted.

- A. The "R" may include a transistor as the charging source, with some type of error signal controlling the current and therefore the period of the one shot

The trigger may be brought in on the base of Q2.

2.6.

2.7.

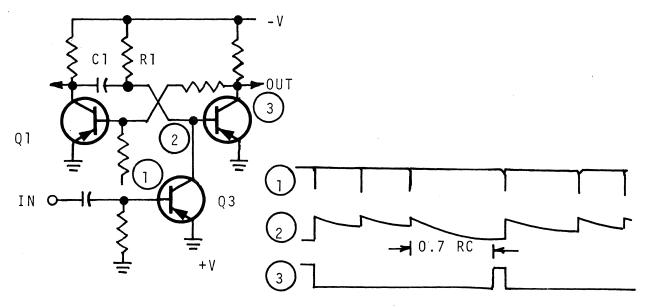

Retriggerable One-Shot

- A. Input pulse turns on Q3 and charges C, positive, and turning off Q2.

- B. Cl starts charging through Rl until sufficiently negative to turn on Q2.

- C. If the period (0.7RC) is longer than the period between input pulses, the one shot does not revert to its stable state.

- D. A missing pulse will allow it to revert to a stable state.

- E. It is sometimes called a pulse to dc converter.

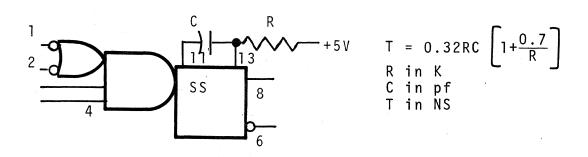

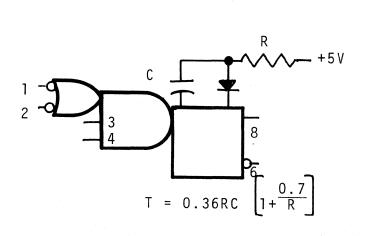

- Nand/Nor Integrated Circuit One Shots

3.1.

3.0.

The FC 914 NOR Gate may be used as a one-shot

A. If either input goes high, the output will swing low. If both inputs are low (near ground) the output will be high (near supply voltage)

3.2.

One-Shot

- AMPEX DEPARTMENT

- A. The period of the One-Shot, using the FC914 is 0.33RC.

- B. This will vary depending on the integrated circuit used, and its internal resistance.

- C. In general, it may be used in the same way as a one-shot using discrete components.

- D. Diode-Transistor logic circuits may also be used in a similar way.

- 3.3.

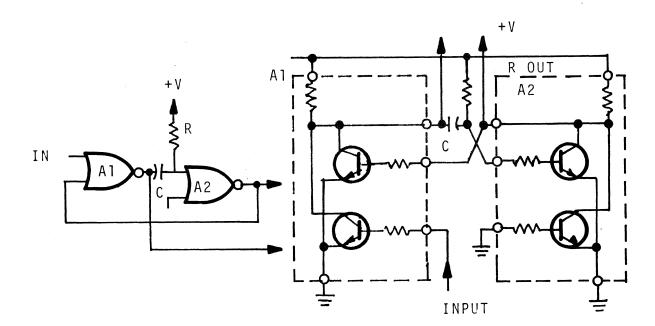

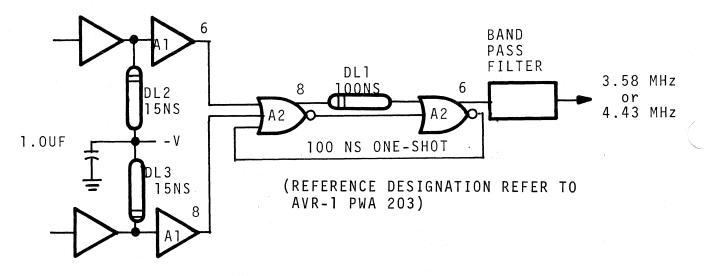

- The system subcarrier phase shifter in the Universal Colortec (Model 1012) and the Reference Subcarrier Processor #1, Module 203 in the AVR-1 employ a different version of the differentiator. Delay lines are used instead of resistance and capacitance.

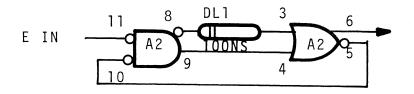

- A. The logic units are Motorola MECL 1204L, where a high is between ground and -0.7 volts, and a low is on the order of minus 2 volts.

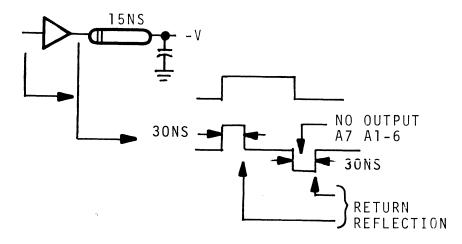

- B. Input pulses are at 1/2 television signal color subcarrier rate. The preceeding circuit discussed later varies the timing of the positive transitions of the input pulse.

- C. DL2 and DL3 appear as shorted delay lines due to the 1.0ufd capacitor and the input frequency of 1.79 or 2.2 MHZ.

Because of the bias at the end of the delay line Al-6 and Al-8 see only the positive going С. reflections.

D. Initial (Stable) State

- Ein low

- A2 pin 10 also low Pin A2-9 high, keeping A2-8 low, and maintaining the stable state.

Ε. Unstable (triggered state)

- MPEX

- Pin 11 goes high for 30 nano seconds

Pin 8 goes high, but it is 100 nanoseconds later before A2-3 goes high

- The low out of A2-9 keeps Å2-5 high, keeping A2-9 low.

- 100 nano seconds later A2-3 goes high, A2-5 goes low, and the one shot reverts to its stable state.

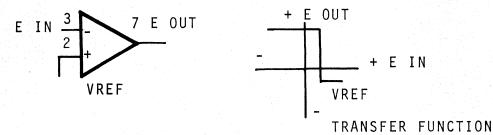

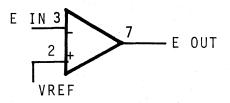

- 4.0. Integrated Circuit One-Shot

- 4.1.

- The Fairchild 9601 Retriggerable Monostable Multivibrator is a single "chip" that performs the oneshot function.

- A. An external resistor and capacitor determine the period.

- B. Inputs are d.c. coupled so that triggering is independent of input transition time.

- C. For trouble shooting purposes, T=0.32RC is adequate.

- 4.2.

When electrolytic capacitors are used, Fairchild recommends a diode or transistor across the capacitor to prevent reverse voltage across it.

VII-10

4.3.

General considerations for the FC9601

- A. If 3 and 4 are not used they are tied to +5V B. If NOR inputs 1 and 2 are not used they are

- tied to ground.

- C. If the period is longer than the input trigger period, the one-shot will continuously retrigger and the output will be a dc level. NOTE: Retriggering will not occur if the retrigger pulse comes within 0.32 CX RX (.7RC) after the initial trigger.

AMPEX

DEPARTME

4.4.

Non-retriggerable connections.

- A. This circuit is used in the Video Tape Recorder to identify the horizontal component of composite sync. It eliminates the half line information during the 7½ (625) or 9 line (525) vertical interval.

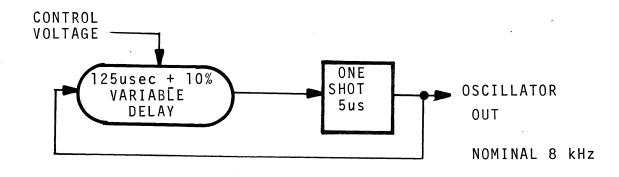

- Voltage Controlled Oscillator

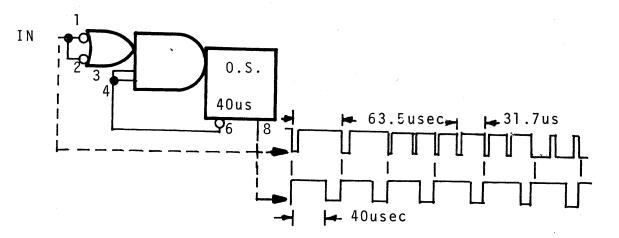

- A. Basic circuit-the output of the one-shot is delayed by a period equal to the nominal period of the desired frequency, then retriggers the one-shot.

# 4.5.

AMPEX DEPARTMENT

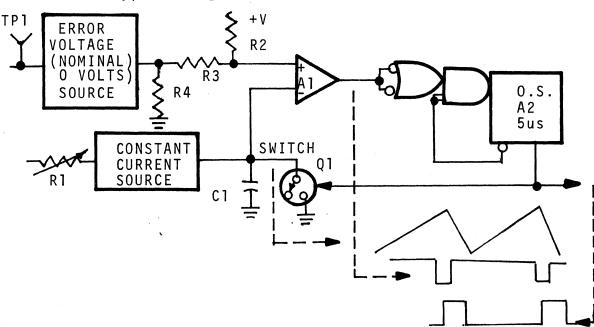

B. Typical Logic Circuit.

4 6.

Circuit operation of voltage controlled oscillator. A. A 5 usec pulse from the one shot turns on transistor. switch Ql, discharging Cl to ground.

- B. At the end of the pulse, the capacitor starts charging at a linear rate, the ramp rate determined by the constant current source.

- -the constant current source may be adjustable (R1)

-it would probably be adjusted so that the error voltage (TP1) equalled zero volts under some special control condition.

- C. The positive going ramp (in the AVR-1 it is usually +5V) is the minus input to voltage comparator Al.

- D. The positive input to the comparator is determined by voltage divider R2, R3, and R4.

- -when the error voltage is zero, then the divider is R2, and R3.

- -this determines the nominal operating frequency

- E. When the ramp voltage exceeds the reference voltage, the output of Al swings negative, triggering one-shot A2.

- F. The action repeats.

AMPEX

5.0.

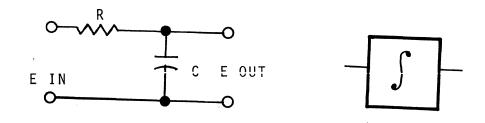

A less frequently encountered circuit is the "Integrator"-essentially the complement of the differentiator. Again the term is derived from the claculus.

5.1.

The process is simulated electrically by a resistance capacitance network.

A. Again, the integration approaches mathematical perfection if R and C are infinite in value. Of course E out becomes infinitesimal.

It can also be considered a low pass filter-and the circuit is probably most familar as an RC Power Supply Filter.

5.3.

5.2.

In the case of sine wave, a phase shift results.

5.4.

The ramp generator is another example

5.5. The AVR-1 uses a variation of the integrator . circuit to perform the differentiator pulse former function. Review of differentiator pulse former

Α.

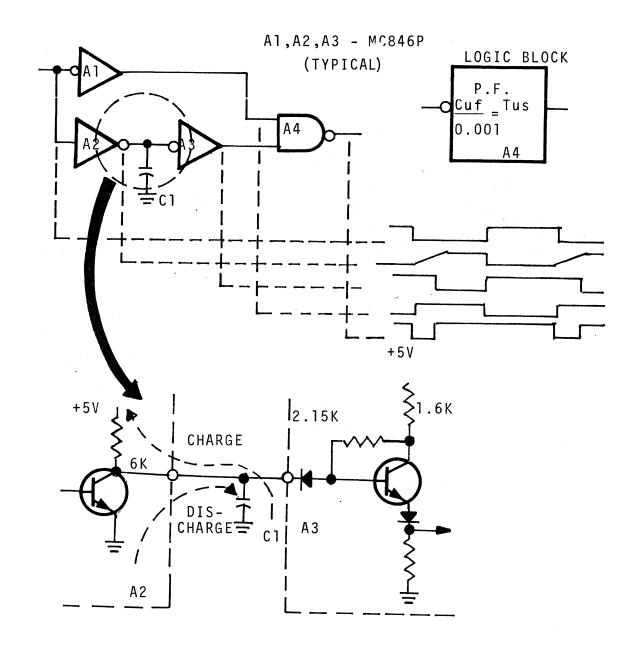

B. AVR-1 Pulse Former

O

ſ

VII-15

- C. Circuit Operation

- -Every negative transition of the input signal produces a pulse at the output.

- Pulse width approximately 1 micro second for every 1040pf of C1 in most applications

- -As long as input to A2 is positive, its output

- transistor is conducting, keeping Cl at ground -When the input to A2 swings negative, the output transistor turns off, and Cl starts charging towards +5V through 6000ohms, until positive enough to turn on the input transistor of A3, causing A3 output to go low, to ground.

5.6.

A variation of this circuit uses the "WIRED AND" gate

- A. The output of "WIRED AND" gate low when either Al or A2 output low (ground)

- B. The circuit produces a positive pulse out for every negative transition of the input signal.

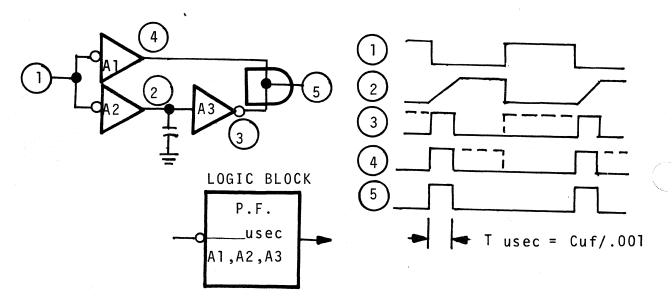

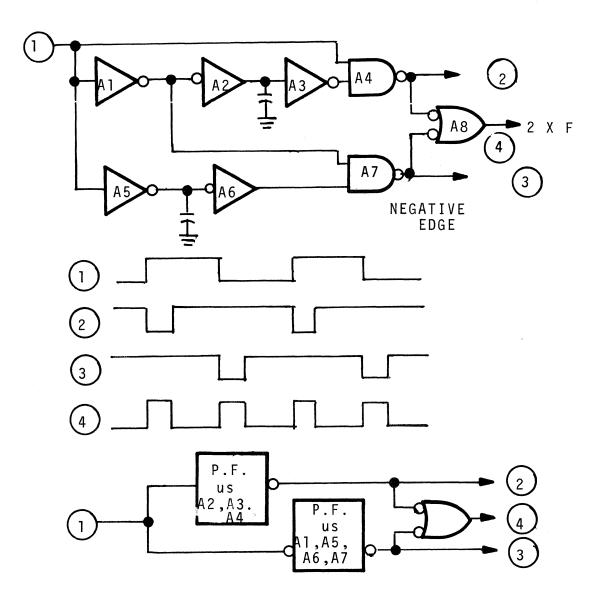

5.7. The pulse former ciruit may be utilized as a frequency doubler.

$\bigcirc$

## VII-17

5.8.

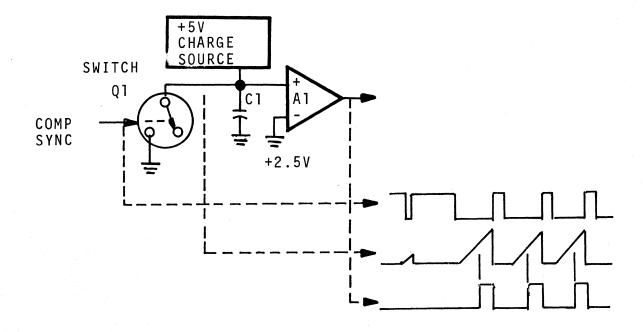

One method of pulse width discrimination uses the ramp generator.

- A. During the time that the compostie sync signal is positive, switch Q1 operates and keeps C1 at ground.

- B. When a sync pulse swings negative, Ql turns off and allows Cl to charge positive.

- C. During H sync time, it is allowed to charge for about 4.5 usec; during the 5 or 6 equalizing pulses, about 2.5 usec.

- D. During the servated vertical pulse, Cl has about 27 usec to charge towards +5Volts.

- -Only during the vertical interval can Cl charge positive enough to exceed the +2.5V bias on the minus input to voltage comparator Al, and allow its output to swing positive.

AMPEX DEPARTM

The integrator is in another way to recognize the vertical sync interval.

- The RC time constant is 100 usec. Α.

- During horizontal sync pulses (about 4.6 usec) Β. and equalizing pulses (about 2.5 usec) the capacitor gets very little charge and during the following line or half line is completely charged

- С. During the serrated vertical sync pulse it has has about 27 usec to charge positive, but only 5 micro seconds to discharge, so that it produces a pulse representing the vertical pulse.

- D. Or, the circuit has acted as a low pass filter, leaving only the fifty or sixty cycle component of the synchronizing signal.

- 5.10. In one case in the AVR-1 this circuit is used as a frequency discriminator, producing a D.C. voltage out which is proportional to the period of the input constant width pulses.

- 6.0. Phase shifter

- 6.1. The editor tach phase shifter or PWA 141 of the AVR-1 operates at 240/250HZ

5.9.

VII-19

####

- 6.1.

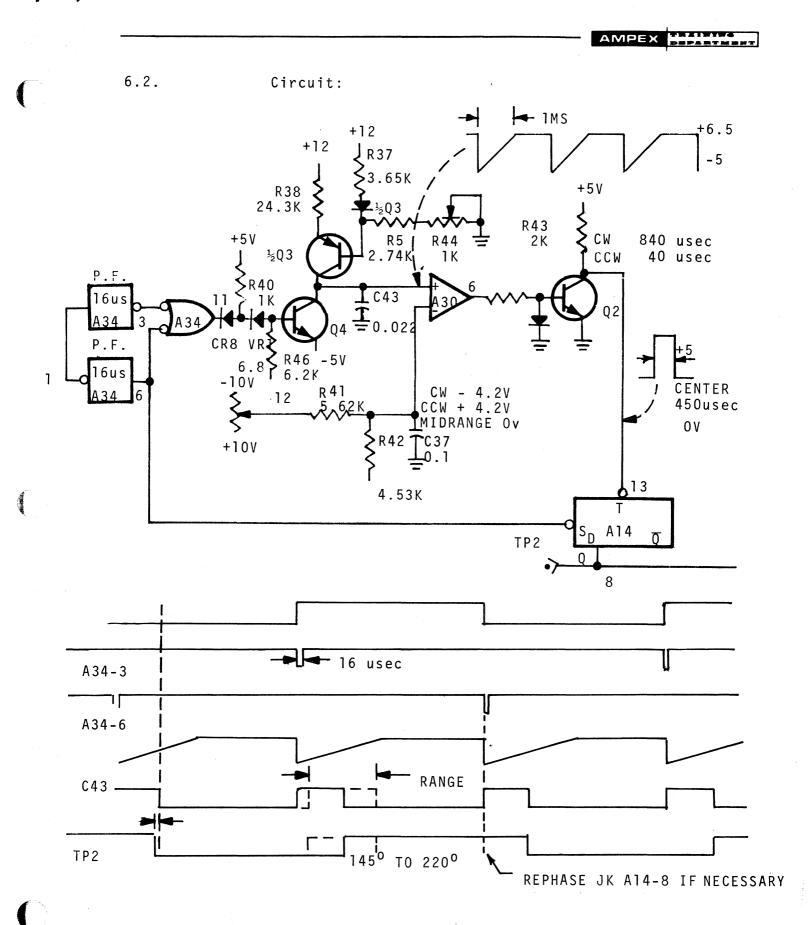

- A. Two pulse formers and NOR GATE A34-11 produce a series of narrow pulses at twice tach frequency (480/500Hz) which, through, Q4 discharge C43 to -5 volts.

- B. At the end of the pulse C43 starts charging through Q3 towards +6 volts.

- Requires about 1 millisecond, or 90<sup>0</sup> of tach. and is the "+" input to A30-6.

- C. The negative input to A30-6 is a voltage from the EDIT TACH PHASE potentiometer on the EDITOR Control Panel. At the input to A-30, it varies continuously from +4.2V to -4.2Vdc.

- D. At the center of the range it is zero volts.

- E. As long as the "+" input to A30-6 is more negative than the "-" input, the output is negative.

- The output of A30 swings positive when the "+" input (ramp) voltage is more positive than the "-" input (variable dc voltage).

- E. Q2 inverts the signal and the variable (now negative going because of the inversion) transition clocks J-K Flip-Flop Al4-8, connected as a divide-by-two

- G. A pulse from A34-6 to the "SD" input of A14-8 assures that output phase is correct.

- 1. A negative level on the "SD" input overrides and other inputs and puts A14-8 (Q output) High.

VII-21

TRAINING DEPARTMENT AMPEX

6.3.

A somewhat different version is used in the ref-erence subcarrier phase shifter in the Universal Colortec and the AVR-1 Module 203.

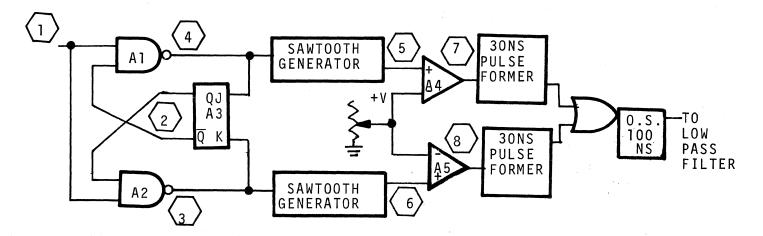

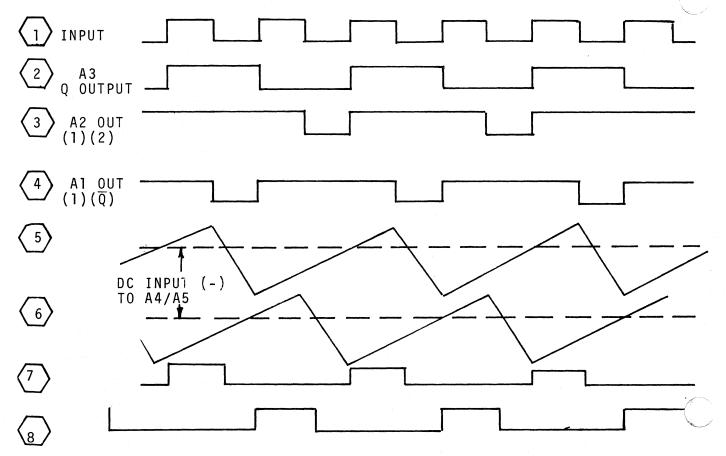

### SIMPLIFIED CIRCUIT

- The input signal is subcarrier (3.58/4.43MHZ) which has been squared up in a limiter. A3 is an AC coupled JK Flip-Flop. A positive Α.

- Β. transition on J causes Q to go high.

AMPEX

TRAINING USE ONLY V0018

SECTION: 8

1.

### DIFFERENTIAL & OPERATIONAL AMPLIFIERS

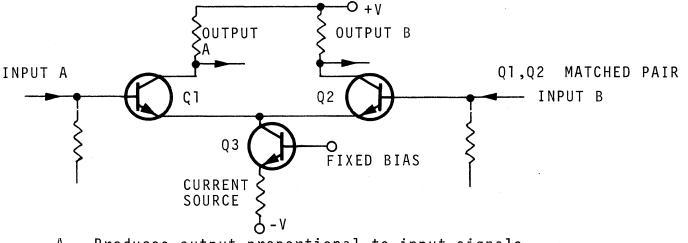

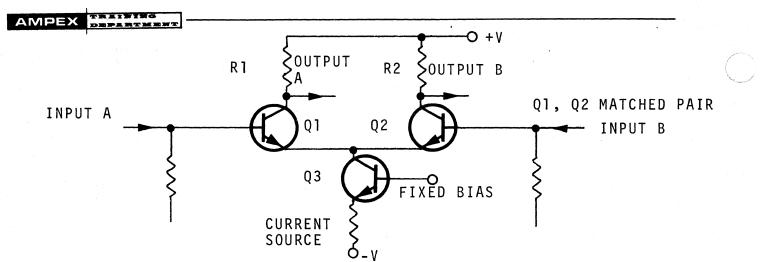

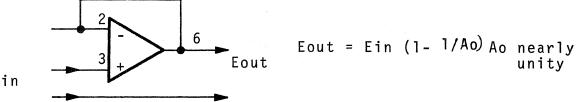

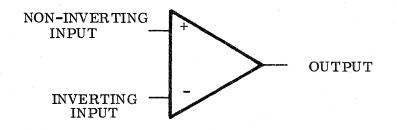

I. Differential Amplifier - Basic Circuit

A. Produces output proportional to input signals

Signals of equal amplitudes and same polarities applied to input would cancel at outputs.

- a. Example Output taken at Output A with equal inputs at Input A & B

- b. Input A is inverted to A at Q1 collector

- c. Input B sees Q2 as emitter follower with no inversion and Q1 as common base amplifier with no inversion

- d. Signal at Ql collector equals A + B, signal at Q2 collector equals A - B

- Differential Amplifier used as phase splitter driven single ended produces outputs of opposite polarity and amplified

- a. Example: Signal at Input A is amplified and inverted by Q1 to produce - A, Q2 base tied to fixed bias.

- b. Signal also sees Ql as Emitter follower and is coupled to Q2 emitter where it is amplified by Q2 operating in common base configuration to produce amplified A at A2 collector.

- Differential Amplifier used in input circuits to reduce hum caused by different ground potentials between two chassis. (Common Mode Rejection)

- a. Input A driven single ended from center conductor of unbalanced line. Output taken from Q2 collector. Input B connected to shield of unbalanced line.

- b. Common Mode Signal (hum) would cancel at Q2 collector. (A - B)

- c. Main line signal at Input A would be amplified and appear at Q2 collector free from hum.

- 4. Differential amplifier used as reference amplifier. (Power Supplies)

- a. Q2 base tied to stable voltage source (Zener Diode)