# 0.6 Micron CMOS Standard Cell Data Book

Copyright © 1996 American Microsystems, Inc. (AMI). All rights reserved. Trademarks registered.®

Information furnished by AMI in this publication is believed to be accurate. Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMI makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI makes no warranty of merchantability or fitness for any purposes. AMI reserves the right to discontinue production and change specifications and prices at any time and without notice.

AMI's products are intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements or high reliability applications such as military, medical life-support or life-sustaining equipment, are specifically **not** recommended without additional processing by AMI for such application.

Printed in U.S.A.

| ix  |

|-----|

| 1-1 |

| 2-1 |

| 3-1 |

| 4-1 |

| 5-1 |

| 6-1 |

| 7-1 |

|     |

.....

# **Selection Guide**

**Section 1**

# **Library Characteristics**

Section 2

**Core Logic Section 3**

**Pad Logic Section 4**

Megacells

Megacells **Section 5**

Memories

# **Memories Section 6**

# **Sales Information** ormation **Section 7**

۷

vi

viii

۰i

# General Introduction

## AMI6S 0.6 micron CMOS Standard Cells

#### American Microsystems, Inc. - Making ASICs Easier for More Than a Quarter Century

merican Microsystems, Inc. (AMI) pioneered the levelopment of the world's first custom MOS ICs in 1966. Vith more experience than any other ASIC vendor, you an be assured that when you bring your ASIC levelopment project to AMI, you are working with a lependable team that has the depth of experience to rovide you with an optimum solution, on time and on udget.

he vision shared by all employees at AMI is expressed in –ur mission statement:

Ve will satisfy your customers by producing products that neet or surpass their quality, reliability, cost and delivery eeds.

MI is a corporation whose headquarters and ASIC esign and manufacturing operations are located in a 92,000 square foot facility in Pocatello, Idaho; the tandard Products division is also headquartered in ocatello. AMI has a software R&D facility in Twain Harte, alifornia, and owns a subsidiary, AMI (Phillippines), Inc., cated in a 64,000 square foot facility in Manila, hilippines, for electrical testing of AMI's products.

## Markets

- Communications

- EDP

- Consumer

- Military

- Industrial

- Automotive

- Medical

## **Sales and Distribution**

- Eight full-service sales and technical support offices located in key markets throughout North America.

- Eight additional satellite offices in secondary markets.

- Six technical service centers located in San Jose, Los Angeles, Boston, Portland, Dresden, and Tokyo, which offer customers a full range of digital ASIC design resources and services.

- 44 sales representative offices throughout North America, with more than 110 outside salespeople.

- AMI's standard product offerings are available through 74 distributor's offices in the United States and Canada.

- In Europe, AMI is represented by distributors or sales representatives in the United Kingdom, Germany, France, Italy, Spain, Netherlands, Belgium, Israel, Sweden, and Denmark. AMI maintains a technical service center in Dresden, Germany.

- In addition to a sales office in Tokyo, Japan, AMI is represented by distributor/sales representatives in that country and in Singapore, Taiwan, Australia, Hong Kong, and India.

# General Introduction

## AMI6S 0.6 micron CMOS Standard Cells

## **Products**

#### ASICs

Mixed-signal, standard cell, and gate array ASICs. AMI's ASIC products are supported with a library of more than 500 digital cells and megacells, designed in the company's 0.6 and 0.8 micron CMOS process technologies and compatible with all popular industry-standard CAE environments.

# Mask Programmable ROMs (read-only memories)

AMI's ROMs offer capabilities from 16 megabits to 16 kilobits, response times as fast as 90 nanoseconds, and require only a 3 to 5 volt power supply. Design flexibility is afforded by multiple user-definable control pins and a variety of packaging options.

#### **ASIC Design Software**

ACCESS Design Tools<sup>™</sup> software-for optimizing ASIC design at customer sites. AMI's ACCESS product line includes Design Analyzer<sup>™</sup> and Pattern Analyzer<sup>™</sup> softare, as well as the company's NETRANS<sup>™</sup> FPGA-to-ASIC conversion software for use at customer sites, and NETRANSplus<sup>™</sup> for fast system prototyping with FPGAs.

#### **Multichip Solutions**

Manufacturing and testing multichip solutions with one or more IC's, combined with other electrical components, in various combinations of substrates, interconnects, and package form factors.

## Services

#### **PLD/ASIC Conversions**

- NETRANS/PALTRANS<sup>TM</sup>—the first fully automated PLD to-ASIC conversion service offered by an ASIC vendor.

- NETRANSplus<sup>™</sup>—the first fully automated ASIC-to FPGA conversion service offered by an ASIC vendor to provide quick-turn prototyping.

#### ASIC Test

- NETSCAN™—AMI's automated ASIC test-patteri generator software for increasing fault coverage.

- NETTAG™—AMI's automated JTAG insertion tool fo boundary scan testing.

#### **ASIC Design**

• Design Analyzer, Gate Gobbler™, Five-Corner Logi Simulator™, and Accolade™ cell-compiler software—fc optimizing customers' ASIC design and swiftly tailoring logic functions to customers' specific requirements.

#### Foundry/Marketing

- Advanced CMOs technology- brings low powe consumption, high noise immunity, and high circu densities to digital and analog/digital ASICs

- Feature sizes as small as 0.6 micron (drawn), and a large as 5 micron (drawn).

- Process modularity -enables automated fabricatio steps to be variously combined in ways tailored to mee the specific manufacturing requirements of analoc digitial, and mixed-signal devices.

- "Flexible factory" -provides a diversity of fabricatio processes and schedule options to meet custome requirements.

- · Long term support of mature processor.

#### **Corporate Headquarters**

American Microsystems, Inc. 2300 Buckskin Road Pocatello, Idaho 83201 Phone: (208) 233-4690 Fax: (208) 234-6796

ACCESS Design Tools, Accolade, ASIS, Design Analyzer, Pattern Analyzer, Five-Corner Logic Simulator, Gate Gobbler, Mixed-Signal Design Solutic (MSDS), NETRANS, NETRANSplus, NETSCAN, NETTAG, and PALTRANS are trademarks of American Microsystems, Inc. PEEL is a trademark of International CMOS Technology, Inc. and/or its successors or assigns.

ij

Selection Guide

| Simple Gates |                            |           |

|--------------|----------------------------|-----------|

| Name         | Description                | Page      |

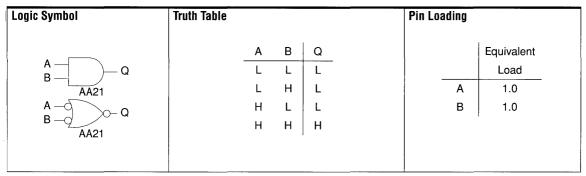

| AA21         | 2-input AND gate           | . 3-Right |

| AA22         | 2-input AND gate           | 3-2       |

| AA31         | 3-input AND gate           | 3-3       |

| AA32         | 3-input AND gate           | 3-4       |

| AA41         | 4-input AND gate           | 3-5       |

| AA42         | 4-input AND gate           | 3-6       |

| EN21         | 2-input exclusive NOR gate | 3-96      |

| EO21         | 2-input exclusive OR gate  | 3-98      |

| EO31         | 3-input exclusive OR gate  | 3-100     |

| NA21         | 2-input NAND gate          | 3-142     |

| NA22         | 2-input NAND gate          | 3-143     |

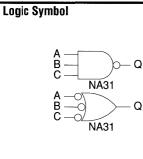

| NA31         | 3-input NAND gate          | 3-144     |

| NA32         | 3-input NAND gate          | 3-145     |

| NA41         | 4-input NAND gate          | 3-146     |

| NA42         | 4-input NAND gate          | 3-147     |

| NA51         | 5-input NAND gate          | 3-148     |

| NA52         | 5-input NAND gate          | 3-149     |

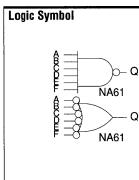

| NA61         | 6-input NAND gate          | 3-150     |

| NA81         | 8-input NAND gate          | 3-151     |

| NO21         | 2-input NOR gate           | 3-152     |

| NO22         | 2-input NOR gate           | 3-153     |

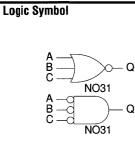

| NO31         | 3-input NOR gate           | 3-154     |

| NO32         | 3-input NOR gate           | 3-155     |

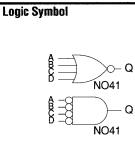

| NO41         | 4-input NOR gate           | 3-156     |

| NO42         | 4-input NOR gate           | 3-157     |

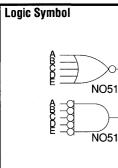

| NO51         | 5-input NOR gate           | 3-158     |

| NO52         | 5-input NOR gate           | 3-159     |

| OR21         | 2-input OR gate            | 3-174     |

| OR22         | 2-input OR gate            | 3-175     |

| OR31         | 3-input OR gate            | 3-176     |

| OR32         | 3-input OR gate            |           |

| OR41         | 4-input OR gate            | 3-178     |

| OR42         | 4-input OR gate            | 3-179     |

| Complex | Gates |

|---------|-------|

|---------|-------|

| Name | Description                                       | Page  |

|------|---------------------------------------------------|-------|

| AN11 | Two 2-input ANDs into 2-input NOR                 | 3-7   |

| AN21 | 2-input AND into 2-input NOR                      | 3-8   |

| AN31 | 2-input AND into 3-input NOR                      | 3-9   |

| AN41 | 3-input AND into 2-input NOR                      | 3-10  |

| AN51 | 2-input AND and 3-input AND into 2-input NOR      | 3-11  |

| AN61 | Two 3-input ANDs into 2-input NOR                 | 3-12  |

| AN71 | 3-input AND into 3-input NOR                      | 3-13  |

| AN81 | Two 2-input ANDs into 3-input NOR                 | 3-14  |

| AN91 | 2-input AND and 3-input AND into 3-input NOR      | 3-15  |

| ANA1 | Two 3-input ANDs into 3-input NOR                 | 3-16  |

| ANB1 | Three 2-input ANDs into 3-input NOR               | 3-17  |

| ANC1 | Two 2-input ANDs and 3-input AND into 3-input NOR | 3-18  |

| AND1 | 2-input AND and two 3-input ANDs into 3-input NOR | 3-19  |

| ANE1 | Three 3-input ANDs into 3-input NOR               | 3-20  |

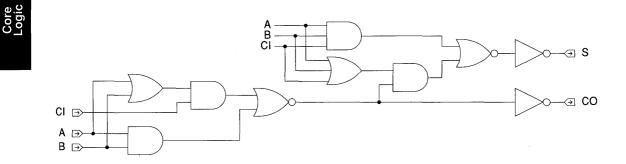

| AU11 | One-Bit full adder                                | 3-21  |

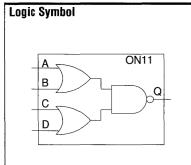

| ON11 | Two 2-input ORs into 2-input NAND                 | 3-160 |

| ON21 | 2-input OR into 2-input NAND                      | 3-161 |

| ON31 | 2-input OR into 3-input NAND                      | 3-162 |

| ON41 | 3-input OR into 2-input NAND                      | 3-163 |

| ON51 | 2-input OR and 3-input OR into 2-input NAND       | 3-164 |

| ON61 | Two 3-input ORs into 2-input NAND                 | 3-165 |

| ON71 | 3-input OR into 3-input NAND                      | 3-166 |

| ON81 | Two 2-input ORs into 3-input NAND                 | 3-167 |

| ON91 | 2-input OR and 3-input OR into 3-input NAND       | 3-168 |

| ONA1 | Two 3-input ORs into 3-input NAND                 | 3-169 |

| ONB1 | Three 2-input ORs into 3-input NAND               | 3-170 |

| ONC1 | Two 2-input ORs and 3-input OR into 3-input NAND  | 3-171 |

| OND1 | 2-input OR and two 3-input ORs into 3-input NAND  | 3-172 |

| ONE1 | Three 3-input ORs into 3-input NAND               | 3-173 |

# AMI6S 0.6 micron CMOS Standard Cells

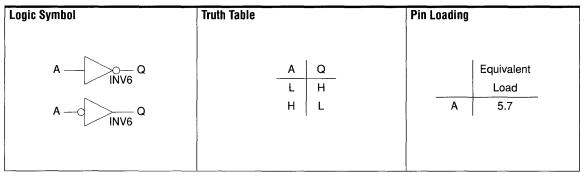

## **Inverting Drivers**

| Name | Description | Page  |

|------|-------------|-------|

| INV1 | Inverter    | 3-106 |

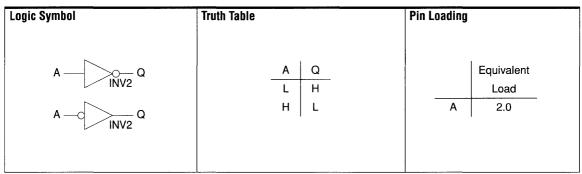

| INV2 | Inverter    | 3-107 |

| INV3 | Inverter    | 3-108 |

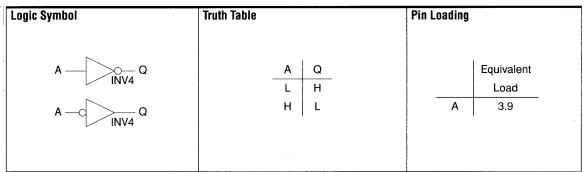

| INV4 | Inverter    | 3-109 |

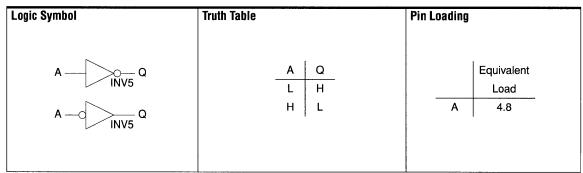

| INV5 | Inverter    | 3-110 |

| INV6 | Inverter    | 3-111 |

## **Internal 3-State Drivers**

| ITA1 | Internal non-inverting tri-state bu | Iffer3-112 |

|------|-------------------------------------|------------|

| ITA2 | Internal non-inverting tri-state bu | Iffer3-113 |

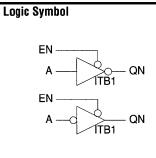

| ITB1 | Internal inverting tri-state buffer | 3-114      |

| ITB2 | Internal inverting tri-state buffer | 3-115      |

| ITD1 | Internal inverting tri-state buffer |            |

| ITD2 | Internal inverting tri-state buffer | 3-117      |

| ITE1 | Internal inverting tri-state buffer | 3-118      |

| ITE2 | Internal inverting tri-state buffer | 3-119      |

# **Clock Drivers**

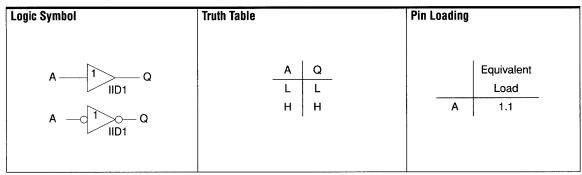

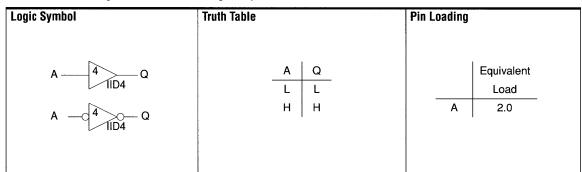

| IID1   | Non-inverting clock driver                    | 3-102 |

|--------|-----------------------------------------------|-------|

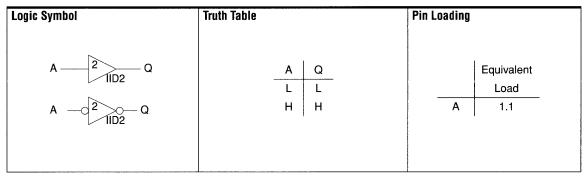

| IID2   | Non-inverting clock driver                    | 3-103 |

| IID4   | Non-inverting clock driver                    | 3-104 |

| IID6   | Non-inverting clock driver                    | 3-105 |

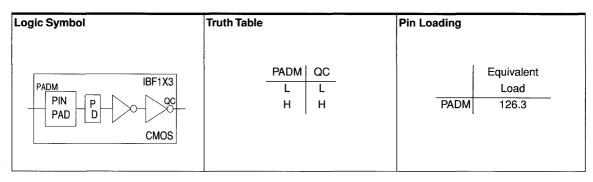

| IBF1X3 | Non-inverting, CMOS input clock-driver pad    | 4-82  |

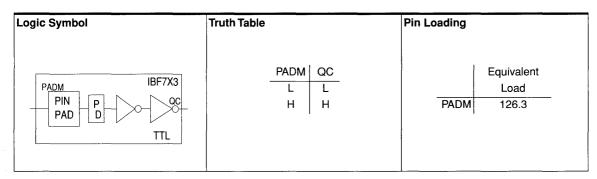

| IBF7X3 | Non-inverting, TTL input clock -driver pad    | 4-83  |

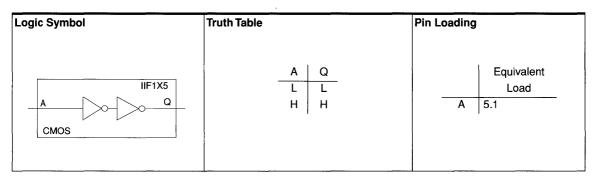

| IIF1X5 | Non-inverting, CMOS clock-driver, second ring | 4-84  |

#### **Muxes and Decoders**

| DC24   | 2:4 Line decoder                  | 3-29  |

|--------|-----------------------------------|-------|

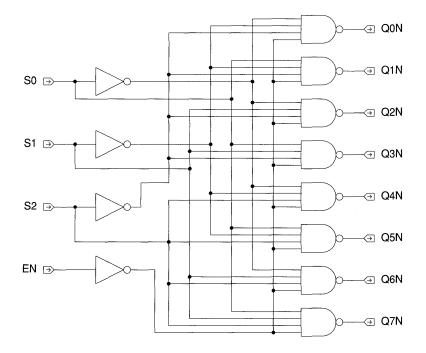

| DC38   | 3:8 Line decoder                  | 3-30  |

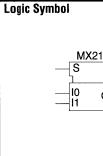

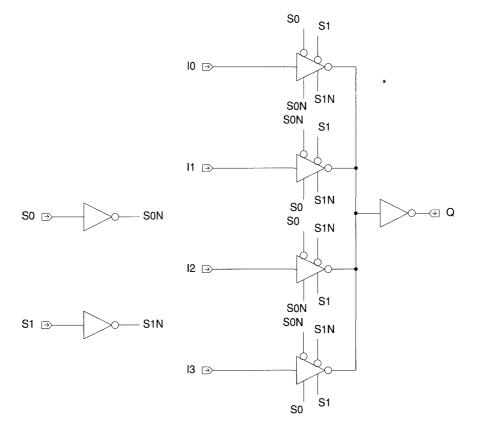

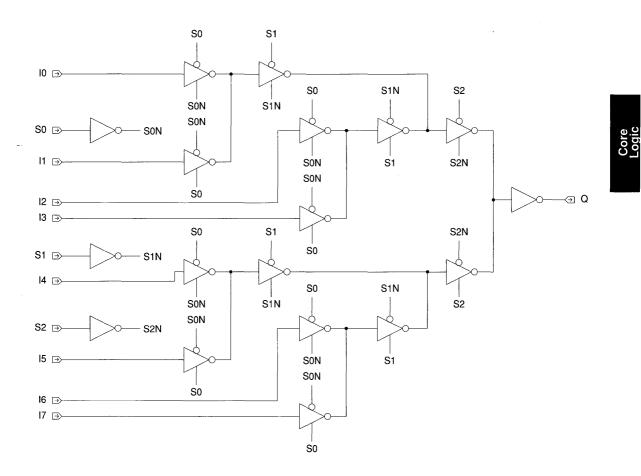

| MX21   | 2:1 Digital multiplexer           | 3-134 |

| MX212  | 2:1 Digital multiplexer           | 3-135 |

| MX41   | 4:1 Digital multiplexer           | 3-136 |

| MX81   | 8:1 Digital multiplexer           | 3-138 |

| MXI21  | Inverting 2:1 Digital multiplexer | 3-140 |

| MXI212 | Inverting 2:1 Digital multiplexer | 3-141 |

# AMI6S 0.6 micron CMOS Standard Cells

## **Sequential Logic**

| Name  | Description                                                                       | Page |

|-------|-----------------------------------------------------------------------------------|------|

| DF001 | D-type F/F without set and reset. Output is Q                                     | 3-32 |

| DF011 | D-type F/F with active low reset. Output is Q                                     | 3-34 |

| DF021 | D-type F/F with active low set. Output is Q                                       | 3-36 |

| DF031 | D-type F/F with active low set and reset. Output is Q                             | 3-38 |

| DF041 | D-type F/F without set and reset. Output is QN                                    | 3-40 |

| DF051 | D-type F/F with active low reset. Output is QN                                    | 3-42 |

| DF061 | D-type F/F with active low set. Output is QN                                      | 3-44 |

| DF071 | D-type F/F with active low set and reset. Output is QN                            | 3-46 |

| DF101 | D-type buffered F/F with active low set.<br>Output is Q and QN                    | 3-48 |

| DF111 | D-type buffered F/F with active low reset.<br>Output is Q and QN                  | 3-50 |

| DF121 | D-type buffered F/F with active low set and reset.<br>Output is Q and QN          | 3-52 |

| DF1F1 | D-type buffered F/F without set and reset.<br>Output is Q and QN                  | 3-54 |

| DF201 | D-type mux scan F/F without set and reset<br>Output is Q                          | 3-56 |

| DF211 | D-type mux scan F/F with active low reset<br>Output is Q                          | 3-58 |

| DF221 | D-type mux scan F/F with active low set. Output is Q                              | 3-60 |

| DF231 | D-type mux scan F/F with active low set and reset<br>Output is Q                  | 3-62 |

| DF401 | D-type buffered mux scan F/F with active low set<br>Output is Q and QN            | 3-64 |

| DF411 | D-type buffered mux scan F/F with active low reset<br>Output is Q and QN          | 3-66 |

| DF421 | D-type buffered mux scan F/F with active low set<br>and reset. Output is Q and QN | 3-68 |

| DF4F1 | D-type buffered mux scan F/F. Output is Q and QN                                  | 3-70 |

| DL001 | D-type latch without set and reset. Output is Q                                   | 3-72 |

| DL011 | D-type latch with active low reset. Output is Q                                   | 3-74 |

| DL021 | D-type latch with active low set. Output is Q                                     | 3-76 |

| DL031 | D-type latch with active low set and reset.<br>Output is Q                        | 3-78 |

| DL041 | D-type latch without set or reset. Output is QN                                   | 3-80 |

| DL051 | D-type latch with active low reset. Output is QN                                  | 3-82 |

| Name  | Description Page                                                             |

|-------|------------------------------------------------------------------------------|

| DL061 | D-type latch with active low set. Output is QN3-84                           |

| DL071 | D-type latch with active low set and reset<br>Output is QN                   |

| DL631 | D-type buffered latch without set and reset<br>Output is Q and QN            |

| DL641 | D-type buffered latch with active low reset<br>Output is Q and QN3-90        |

| DL651 | D-type buffered latch with active low set<br>Output is Q and QN3-92          |

| DL661 | D-type buffered latch with active low set and reset<br>Output is Q and QN    |

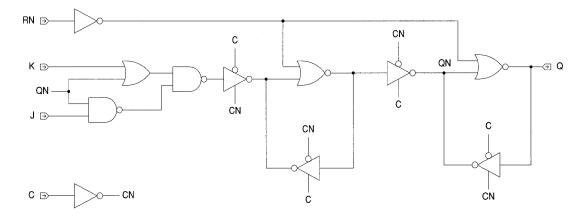

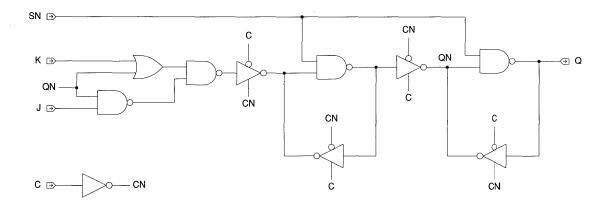

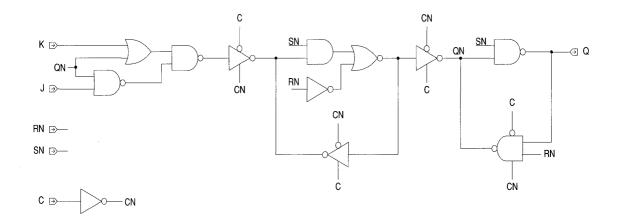

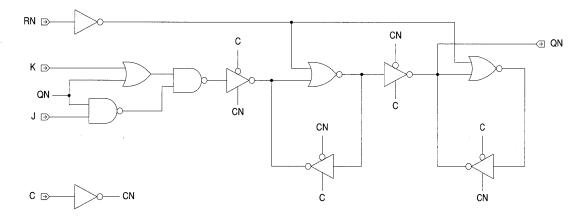

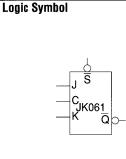

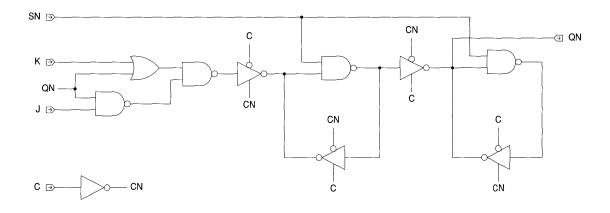

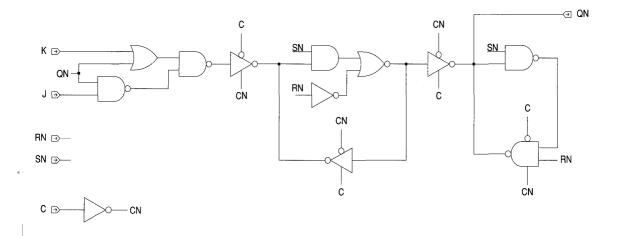

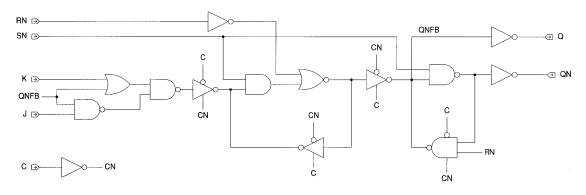

| JK011 | JK-type F/F with active low reset. Output is Q3-120                          |

| JK021 | JK-type F/F with active low set. Output is Q3-122                            |

| JK031 | JK-type F/F with active low set and reset<br>Output is Q3-124                |

| JK051 | JK-type F/F with active low reset. Output is QN3-126                         |

| JK061 | JK-type F/F with active low set. Output is QN3-128                           |

| JK071 | JK-type F/F with active low set and reset.<br>Output is QN3-130              |

| JKBB1 | JK-type F/F with active low set and reset.<br>Output is Q and QN             |

| SLFA1 | Multiplexed scan latch D-type F/F with active low reset.<br>Output is Q3-180 |

| <b>Power Cel</b> | ls                                                                     |       |

|------------------|------------------------------------------------------------------------|-------|

| Name             | Description                                                            | Page  |

| CVDD             | Core cell resistive tie-up to core V <sub>DD</sub> bus                 | 3-27  |

| CVSS             | Core cell resistive tie-down to core $V_{SS}$ bus $\ldots\ldots\ldots$ | 3-28  |

| Special Co       | pre Cells                                                              |       |

| BL02             | Tri-state bus latch                                                    | 3-23  |

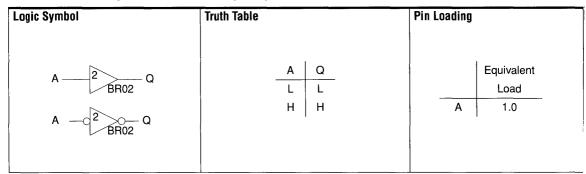

| BR02             | Tri-state bus receiver                                                 | 3-24  |

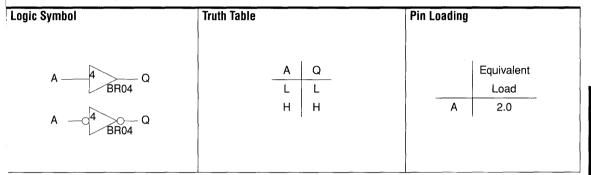

| BR04             | Tri-state bus receiver                                                 | 3-25  |

| BR06             | Tri-state bus receiver                                                 | 3-26  |

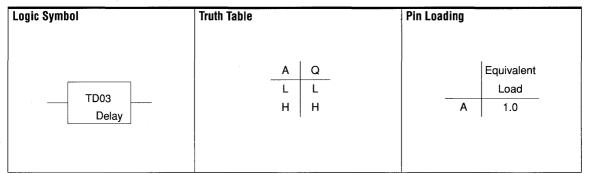

| TD02             | Time delay cell, non-inverting                                         | 3-182 |

| TD03             | Time delay cell, non-inverting                                         | 3-183 |

| TD08             | Time delay cell, non-inverting                                         | 3-184 |

| <b>Input Drive Pi</b> | eces                                                                                             |

|-----------------------|--------------------------------------------------------------------------------------------------|

| Name                  | Description Page                                                                                 |

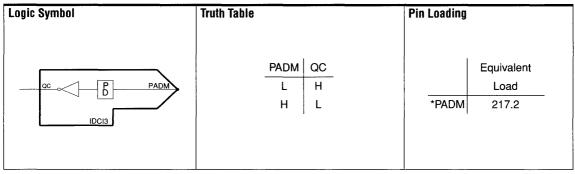

| IDCI3                 | Inverting CMOS inpuut buffer piece4-1                                                            |

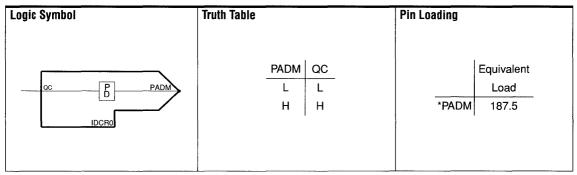

| IDCR0                 | non-buffered, resistive analog interface input piece                                             |

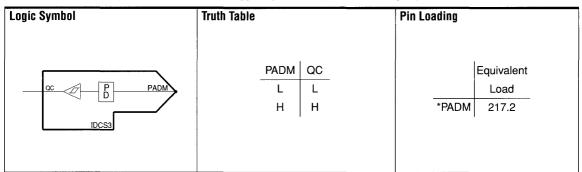

| IDCS3                 | non-inverting, CMOS Schmitt trigger input buffer piece4-3                                        |

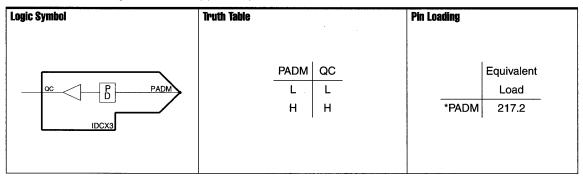

| IDCX3                 | non-inverting, CMOS-level input buffer piece4-4                                                  |

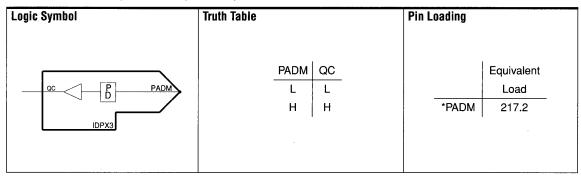

| IDPX3                 | non-inverting, PCI-level input buffer piece4-5                                                   |

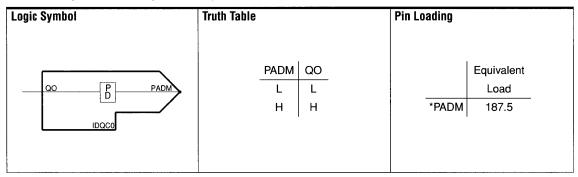

| IDQC0                 | crystal oscillator input receiver piece4-6                                                       |

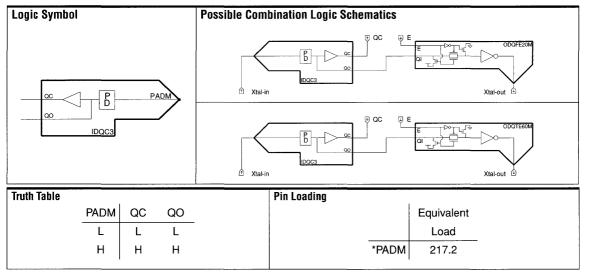

| IDQC3                 | crystal oscillator input receiver piece<br>w/ non-inverting, CMOS clock input4-7                 |

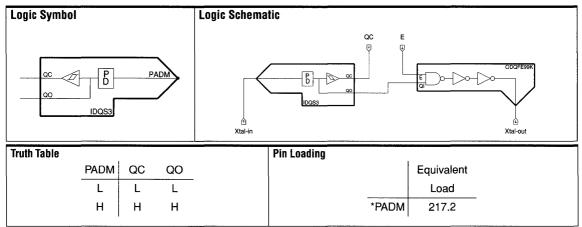

| IDQS3                 | crystal oscillator input receiver piece<br>w/ non-inverting, CMOS Schmitt trigger clock input4-8 |

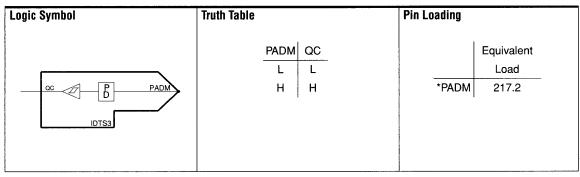

| IDTS3                 | non-inverting, CMOS Schmitt trigger input buffer piece                                           |

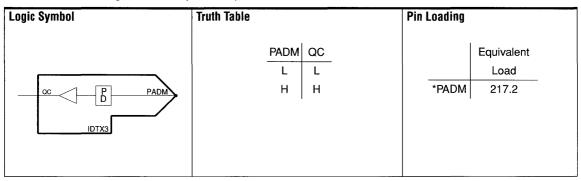

| IDTX3                 | non-inverting, TTL input buffer piece4-10                                                        |

| Pull Pieces           |                                                                                                  |

| PLD3                  | active pull-down buffer piece4-11                                                                |

| PLP3                  | programmable pull-up/pull-down buffer piece                                                      |

| PLU3                  | active pull-up buffer piece4-13                                                                  |

| Output Drive I        | Pieces                                                                                           |

| ODCSIP04              | CMOS inverting P-channel open drain buffer piece<br>w/ slew rate control output, 1 mA4-14        |

| ODCSIP08              | CMOS inverting P-channel open drain buffer piece<br>w/ slew rate control output, 8 mA4-15        |

| ODCSIP12              | CMOS inverting P-channel open drain buffer piece<br>w/ slew rate control output, 12 mA4-16       |

| ODCSXE04              | CMOS tri-statable non-inverting buffer piece<br>w/ slew rate control output, 4 mA4-17            |

| ODCSXE08              | CMOS tri-statable non-inverting buffer piece<br>w/ slew rate control output, 8 mA4-18            |

| ODCSXE12              | CMOS tri-statable non-inverting buffer piece<br>w/ slew rate control output, 12 mA4-19           |

| ODCSXE16              | CMOS tri-statable non-inverting buffer piece<br>w/ slew rate control output, 16 mA4-20           |

| ODCSXE24              | CMOS tri-statable non-inverting buffer piece<br>w/ slew rate control output, 24 mA4-21           |

| ODCSXX04              | CMOS non-inverting buffer piece<br>w/ slew rate control output, 4 mA4-22                         |

| Name     | Description                                                                               | Page |

|----------|-------------------------------------------------------------------------------------------|------|

| ODCSXX08 | CMOS non-inverting buffer piece<br>w/ slew rate control output, 8 mA                      | 4-23 |

| ODCSXX12 | CMOS non-inverting buffer piece                                                           |      |

|          | w/ slew rate control output, 12 mA                                                        | 4-24 |

| ODCSXX16 | CMOS non-inverting buffer piece<br>w/ slew rate control output, 16 mA                     | 4-25 |

| ODCSXX24 | CMOS non-inverting buffer piece<br>w/ slew rate control output, 24 mA                     | 4-26 |

| ODCXIP01 | CMOS inverting P-channel open drain buffer piece,<br>1 mA                                 | 4-27 |

| ODCXIP02 | CMOS inverting P-channel open drain buffer piece, 2 mA                                    | 4-28 |

| ODCXIP04 | CMOS inverting P-channel open drain buffer piece,<br>4 mA                                 | 4-29 |

| ODCXIP08 | CMOS inverting P-channel open drain buffer piece,<br>8 mA                                 | 4-30 |

| ODCXXE01 | CMOS tri-statable non-inverting buffer piece, 1 mA                                        | 4-31 |

| ODCXXE02 | CMOS tri-statable non-inverting buffer piece, 2 mA                                        | 4-32 |

| ODCXXE04 | CMOS tri-statable non-inverting buffer piece, 4 mA                                        | 4-33 |

| ODCXXE08 | CMOS tri-statable non-inverting buffer piece, 8 mA                                        | 4-34 |

| ODCXXE12 | CMOS tri-statable non-inverting buffer piece, 12 mA                                       | 4-35 |

| ODCXXE16 | CMOS tri-statable non-inverting buffer piece, 16 mA                                       | 4-36 |

| ODCXXE24 | CMOS tri-statable non-inverting buffer piece, 24 mA                                       | 4-37 |

| ODCXXX01 | CMOS non-inverting buffer piece, 1 mA                                                     | 4-38 |

| ODCXXX02 | CMOS non-inverting buffer piece, 2 mA                                                     | 4-39 |

| ODCXXX04 | CMOS non-inverting buffer piece, 4 mA                                                     | 4-40 |

| ODCXXX08 | CMOS non-inverting buffer piece, 8 mA                                                     | 4-41 |

| ODCXXX12 | CMOS non-inverting buffer piece, 12 mA                                                    | 4-42 |

| ODCXXX16 | CMOS non-inverting buffer piece, 16 mA                                                    | 4-43 |

| ODCXXX24 | CMOS non-inverting buffer piece, 24 mA                                                    | 4-44 |

| ODPSXE24 | PCI non-inverting tri-state buffer piece<br>w/ slew rate control output                   | 4-45 |

| ODTSXN04 | TTL non-inverting N-channel open drain buffer piece<br>w/ slew rate control output, 4 mA  | 4-46 |

| ODTSXN08 | TTL non-inverting N-channel open drain buffer piece<br>w/ slew rate control output, 8 mA  | 4-47 |

| ODTSXN12 | TTL non-inverting N-channel open drain buffer piece<br>w/ slew rate control output, 12 mA | 4-48 |

Selection Guide

| Name     | Description Page                                                                              |

|----------|-----------------------------------------------------------------------------------------------|

| ODTSXN16 | TTL non-inverting N-channel open drain buffer piece                                           |

|          | w/ slew rate control output, 16 mA4-49                                                        |

| ODTSXN24 | TTL non-inverting N-channel open drain buffer piece<br>w/ slew rate control output, 24 mA4-50 |

| ODTSXE04 | CMOS tri-state output buffer piece<br>w/ slew rate control output, 4 mA4-51                   |

| ODTSXE08 | CMOS tri-state output buffer piece<br>w/ slew rate control output, 8 mA4-52                   |

| ODTSXE12 | CMOS tri-state output buffer piece<br>w/ slew rate control output, 12 mA4-53                  |

| ODTSXE16 | CMOS tri-state output buffer piece<br>w/ slew rate control output, 16 mA4-54                  |

| ODTSXE24 | CMOS tri-state output buffer piece<br>w/ slew rate control output, 24 mA4-55                  |

| ODTSXX04 | TTL non-inverting buffer piece                                                                |

|          | w/ slew rate control output, 4 mA                                                             |

| ODTSXX08 | TTL non-inverting buffer piece                                                                |

|          | w/ slew rate control output, 8 mA                                                             |

| ODTSXX12 | TTL non-inverting buffer piece                                                                |

|          | w/ slew rate control output, 12 mA4-58                                                        |

| ODTSXX16 | TTL non-inverting buffer piece<br>w/ slew rate control output, 16 mA4-59                      |

| ODTSXX24 | TTL non-inverting buffer piece                                                                |

|          | w/ slew rate control output, 24 mA4-60                                                        |

| ODTXXN01 | TTL non-inverting N-channel open drain buffer piece, 1 mA4-61                                 |

| ODTXXN02 | TTL non-inverting N-channel open drain buffer piece,<br>1 mA4-62                              |

| ODTXXN04 | TTL non-inverting N-channel open drain buffer piece,<br>4 mA4-63                              |

| ODTXXN08 | TTL non-inverting N-channel open drain buffer piece,<br>8 mA4-64                              |

| ODTXXN12 | TTL non-inverting N-channel open drain buffer piece,<br>12 mA4-65                             |

| ODTXXN16 | TTL non-inverting N-channel open drain buffer piece,<br>16 mA4-66                             |

| ODTXXN24 | TTL non-inverting N-channel open drain buffer piece,<br>24 mA4-67                             |

| ODTXXE01 | TTL tri-statable non-inverting buffer piece, 1 mA4-68                                         |

# AMI6S 0.6 micron CMOS Standard Cells

| Name     | Description Page                                       |

|----------|--------------------------------------------------------|

| ODTXXE02 | TTL tri-statable non-inverting buffer piece, 2 mA4-69  |

| ODTXXE04 | TTL tri-statable non-inverting buffer piece, 4 mA4-70  |

| ODTXXE08 | TTL tri-statable non-inverting buffer piece, 8 mA4-71  |

| ODTXXE12 | TTL tri-statable non-inverting buffer piece, 12 mA4-72 |

| ODTXXE16 | TTL tri-statable non-inverting buffer piece, 16 mA4-73 |

| ODTXXE24 | TTL tri-statable non-inverting buffer piece, 24 mA4-74 |

| ODTXXX01 | TTL non-inverting output buffer piece, 1 mA4-75        |

| ODTXXX02 | TTL non-inverting output buffer piece, 2 mA4-76        |

| ODTXXX04 | TTL non-inverting output buffer piece, 4 mA4-77        |

| ODTXXX08 | TTL non-inverting output buffer piece, 8 mA4-78        |

| ODTXXX12 | TTL non-inverting output buffer piece, 12 mA4-79       |

| ODTXXX16 | TTL non-inverting output buffer piece, 16 mA4-80       |

| ODTXXX24 | TTL non-inverting output buffer piece, 24 mA4-81       |

## **Power Pad Cells**

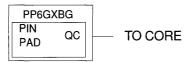

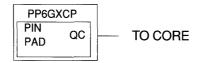

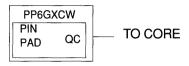

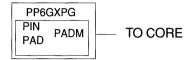

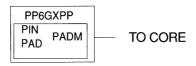

| PP6GXBG | V <sub>SS</sub> power pad for core and pad cells                 | 4-85 |

|---------|------------------------------------------------------------------|------|

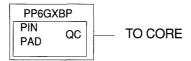

| PP6GXBP | V <sub>DD</sub> power pad for core and pad cells                 | 4-86 |

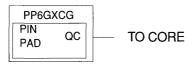

| PP6GXCG | V <sub>SS</sub> power pad for input buffers and core cells only  | 4-87 |

| PP6GXCP | V <sub>DD</sub> power pad for input buffers and core cells only  | 4-88 |

| PP6GXCW | Power pad pin for additional bus                                 | 4-89 |

| PP6GXPG | V <sub>SS</sub> power pad for output buffers only                | 4-90 |

| PP6GXPP | V <sub>DD</sub> power pad for output buffers and core cells only | 4-91 |

## **Special Pad Cells**

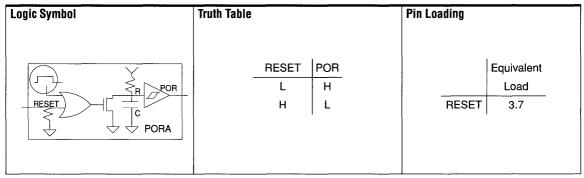

| PORA     | Power-on-reset     | 4-92 |

|----------|--------------------|------|

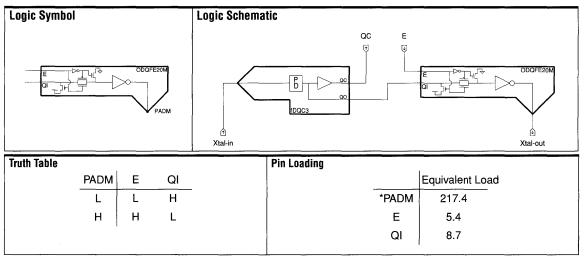

| ODQFE20M | Crystal oscillator | 4-93 |

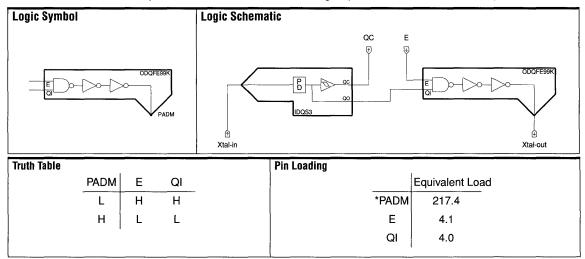

| ODQFE99K | Crystal oscillator | 4-94 |

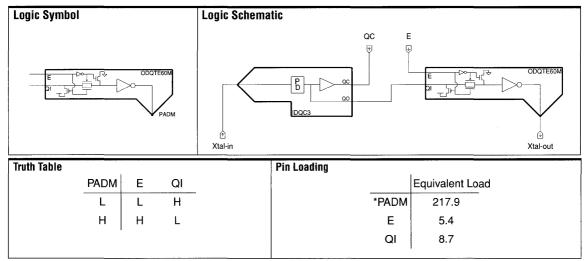

| ODQTE60M | Crystal oscillator | 4-95 |

# SECTION 2 INTRODUCTION TO CORE & PAD LOGIC WITH LIBRARY CHARACTERISTICS

## Description

The "AMI6S" standard cell family continues the AMI eadership tradition of combining true compact building lock standard cells and megacells with high speed nemory and datapath functions. Using a 0.6µm high berformance CMOS process, the AMI6S product can iffer a lower cost alternative to gate array for high volume ipplications.

#### <sup>:</sup>eatures

#### Excellent performance:

- 480 MHz maximum toggle rate on clocked flip-flops (T\_J = 135°C).

- 210 ps delay (FO=2; L=2mm) for a 2-input NAND gate.

- 130 ps delay (FO=2; L=0mm) for a 2-input NAND gate.

#### Operating temperatures range from -55 to 125°C:

Few competing products allow this range.

#### \_ Clock Tree Synthesis:

AMI supports Clock Tree Synthesis for the default clocking methodology. In this methodology, clock drivers are placed by the Place and Route tool to minimize clock skew and latency effects on circuit performance. Parameterized clock buffers called CLKBUF and CLKBUFN are provided to model the clock trees before layout. AMI is able to match the simulation parameters of the CLKBUF prelayout models with a physical clock tree during layout.

#### User-designed pad cells:

AMI allows the user to design pad cells by piecing together predefined components.

## AMI6S 0.6 micron CMOS Standard Cells

#### Cost driven architecture:

Offers both 2 and 3 level metal interconnect to provide the lowest user cost for the number of gates and pads required.

Compiled memory blocks on standard cells are compacted precisely to parameters. No leaf cell overhead.

#### Extensive library for quick design:

- Complete primary cell and I/O library.

Asynchronous and synchronous, single and dual-port RAM compilers with over 2000 compiled RAM sizes from 32x1 to 2Kx32 bits.

- Synchronous ROM compiler from 64x1 to 16Kx32 bits.

- Megacells include processors, peripherals, and datapath synthesizers.

- 100% compatible with AMI's proven ASIC Standard Library.

#### • 1 to 24 mA drive per single I/O cell:

Slew rate limiting available for 4, 8, 12, 16, and 24 mA drive. Custom configurations for I/O drive up to 96 mA can be supported.

- Wide range of packaging: Full QFP and PLCC line, BGAs and PGAs, individual die. Burn-in capability as required.

- Automatic Test Program Generation: Includes scan macros (NETSCAN™) for high fault coverage.

- · JTAG Boundary Scan macro support

- Full operating voltage range from 2.7V to 5.5V

- ESD protection > 2kV; latchup > 100 mA

- · Power dissipation:

2.5µW/MHz/gate

| Feature    |               | Description                                             | Comment                                                                              |

|------------|---------------|---------------------------------------------------------|--------------------------------------------------------------------------------------|

| Complexity |               | Up to 900,000 gates <sup>1</sup><br>Up to 500,000 gates | 50% memory, 50% megacell and user defined logic 100% user defined logic              |

| I/O Count  |               | Up to 512 pins<br>Up to 836 pins                        | Test equipment limit; signal pins only<br>Die size limit; includes power supply pins |

| Delay      | Internal Gate | 102 ps (Fanout=1, L=0mm)<br>215 ps (Fanout=2, L=2mm)    | 2 input NAND gate, T=25°C, V <sub>DD</sub> =5V                                       |

| Time       | Input Buffer  | 675 ps (Fanout=2, L=2mm)                                | CMOS Input buffer, T=25°C, V <sub>DD</sub> =5V                                       |

|            | Output Buffer | 860 ps (C <sub>L</sub> =15pf)                           | CMOS Output buffer,T=25°C, V <sub>DD</sub> =5V                                       |

#### MI6S Standard Cell Family Overview

## AMI6S 0.6 micron CMOS Standard Cells

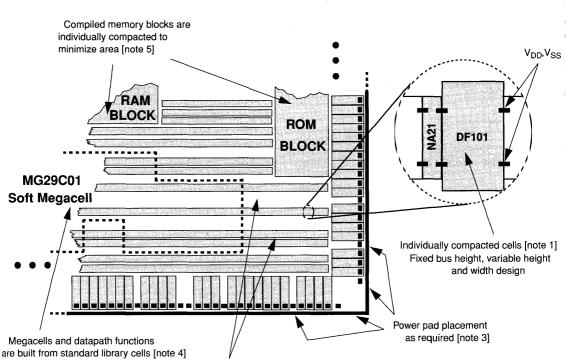

## FIGURE 2: STANDARD CELL ARCHITECTURE

Routing channel width varies with local cell routing requirements [note 2]

## **Architectural Overview**

Some important elements of the AMI6S standard cell family are:

- 2 or 3 level metal interconnect selectable.

- [Note 1] Each cell function is tightly compacted to a fixed bus height. Cells are then placed in rows allowing  $V_{DD}$  and  $V_{SS}$  supplies to feed through the cells. Since some functions require more gates than others, their widths and heights may increase to allow for the added gates. Transistor sizes and routing are optimized for their function, giving a much tighter cell design than with gate arrays or fixed pad ring embedded array products.

- [Note 2] Rows of cells can be placed adjacently if little routing is required between them, or largely separated to allow a large data bus to route through. Tracks of

unused channels are not lost as in gate array c embedded array products. For 3 level metal, thi feature can combine with routing over cells to give very area efficient design.

- [Note 3] Power pads are placed as required among I/( cells and can be placed in corners. Core power can b either 3V or 5V. Each individual I/O can be powered t 3V or 5V. Operating voltage range is 2.7V to 5.5V.

- [Note 4] AMI's megacells and compiled datapat functions are soft cells. They are placed as if part of th customer defined logic. Full netlists are provide allowing modification by the customer for his design.

- [Note 5] Memory blocks are tightly compacted t customer defined width and depth. See table on page for available memory compilers.

## AMI6S 0.6 micron CMOS Standard Cells

# **Product Applications**

The AMI6S standard cells are targeted at higher volume digital ASIC products. The lower cost also fits designs requiring significant on-board memory, datapath logic, or megacells.

FPGA OR PAL CONVERSION: Using NETRANS<sup>™</sup> AMI can convert netlists from most gate array, FPGA, and PAL devices to a more cost and performance effective AMI6X design for volume production.

**2ND SOURCE EXISTING PRODUCTS:** Netlist conversion capabilities from AMI allow a competitive alternate supply with AMI6X components for current high volume designs.

NEW DESIGN CAPTURE: AMI6X design is supported by nany popular 3rd party software platforms, as well as \MI's Enhanced Design Utilities<sup>™</sup> (EDU) environment.

PROCESS UPGRADE: Designs done in AMI's 1.25µm, 1.0µm, and 0.8µm ASIC products can easily be upgraded o the AMI6X family. The AMI ASIC Standard Library →rovides a common netlist design base.

**ADDING CUSTOM BLOCKS:** AMI specializes in adding sustom logic to ASIC designs. Simple analog functions are also possible.

## ASIC Design Tools and Methodology

MI6X and other AMI ASIC families are supported on nany front-end design environments:

Cadence<sup>™</sup> Mentor Graphics® Synopsys® Viewlogic® Intergraph® Compass® Verilog® simulation IKOS® simulation accelerator (AMI's sign-off simulator)

MI has maintained critical proprietary software tools to insure a tight, well coupled design to our silicon process. This methodology includes our expert-system design inalysis tools, AMI's Enhanced Design Utilities (EDU), a oftware support methodology that covers the complete et of wafer processing possibilities, and a dedicated, experienced engineering staff that can assist at any level of the design process.

#### AMI Design Flow

AMI will supply an AMI6X design kit which includes a cell library containing symbols, simulation models and software for design verification, timing calculations, and netlist generation. For pre-layout timing simulations, capacitance and resistance values derived from statistical

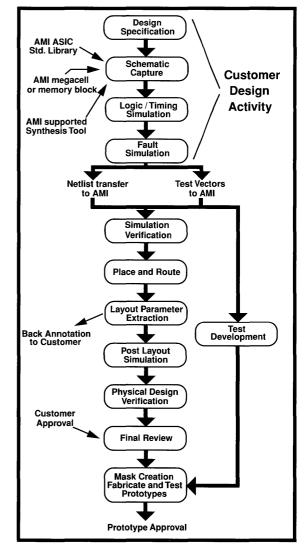

#### FIGURE 3: ASIC DESIGN FLOW

## AMI6S 0.6 micron CMOS Standard Cells

#### AMI Design Flow (cont.)

averages of known layouts are used. Once actual layout is completed by AMI, a post-layout interconnect capacitance and resistance table will be supplied for final validation of device timing.

Figure 3 shows a typical design flow for a new design.

Working with an AMI design center, the customer is responsible for capturing and verifying the design using the AMI ASIC Standard Library. He is also responsible for creating the test vectors that will eventually serve as the logical part of the manufacturing test. Software aids such as logic synthesis, megacells, automatic test program generation, netlist rule checkers, etc. can greatly speed up this process. (A fault coverage check of the test vector set is optional and can be done as an additional service.)

When the design is received by the factory, the "Design Start Package" is reviewed by AMI engineers. This start package, which is completed by the customer, contains the device specification, netlist, pinlist file, critical timing paths, and test vectors. The design is pre-screened on the Enhanced Design Utilities (EDU) and then resimulated on IKOS, AMI's sign-off simulator. The results are compared to the customer's simulation from the third-party CAE tool.

Once the design has passed the initial screening it is then ready for placement and routing. The layout proceeds by first placing memory and megacells, assigning priority to critical paths, and designing the distribution and buffering of clocks. Next, the layout is completed with automatic place-and-route on the balance of the circuit.

After layout has been completed the interconnect data is extracted from the physical layout to be fed back to the sign-off simulator for final circuit verification. This poslayout interconnect data can be sent to the customer foi final validation on his simulator. When the post-layour simulation has been completed and approved by the customer the design is then released for mask and wafe fabrication.

The test program is developed in parallel using interna automatic test program generation software. Prototypes can then be tested before they are shipped.

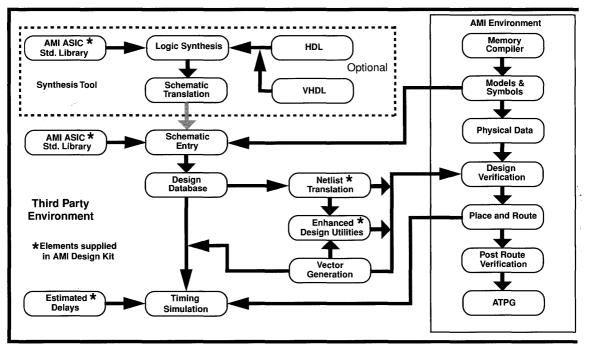

#### FIGURE 4: DESIGN ENVIRONMENT WITH THIRD PARTY SOFTWARE

# AMI6S 0.6 micron CMOS Standard Cells

#### Memory Compiler Library

| Memory Compiler                             | S      | lize     | Increment       | Comments                      |  |

|---------------------------------------------|--------|----------|-----------------|-------------------------------|--|

|                                             | min.   | max.     | nicrement       |                               |  |

| SRAM (single-port, synchronous, self-timed) | 32 x 1 | 2K x 32  | 16 words, 1 bit | preliminary version available |  |

| SRAM (dual-port, synchronous)               | 32 x 1 | 1K x 32  | 16 words, 1 bit | preliminary version available |  |

| ROM (single-port, synchronous)              | 64 x 1 | 16K x 32 | 64 words, 1 bit | preliminary version available |  |

| SRAM (single-port, asynchronous)            | 32 x 1 | 2K x 32  | 16 words, 1 bit | preliminary version available |  |

Figure 4 outlines a typical software environment when using third party tools. AMI uses EDIF to speed ports -between various software products.

AMI's Enhanced Design Utilities Tools are intended to be used interactively at each stage of the design. EDU software is a set of design analysis tools that check both the design and test vectors for correctness and compatibility with in-house ASIC testers, and analyze the design for inefficiencies and possible flaws that could -cause problems in manufacturing the device.

#### **The Design Library**

AMI provides a robust collection of building blocks for the AMI6X family. A broad range of primary cells is "complemented with memory cell compilers and useful megafunctions. With such broad, US-based design alent, AMI can quickly design specific cells that customers need to add an edge in customization.

#### The AMI ASIC Standard Library

The AMI ASIC Standard Library contains a rich set of core and configurable pad cells which allow great lexibility in building competitive devices for customer applications. The library is portable across all AMI's gate array and standard cell families.

#### **Memory Compilers**

The AMI6X family includes the line of memory compilers shown above. Each of the thousands of possible memory plocks is optimized precisely to the customers' parameters rather than built from a presized leaf cell that povers a range of sizes. This yields a better size and performance match for each application.

Jpon supplying the cell specification to AMI, the sustomer can receive an accurate simulation timing specification overnight by facsimile and a full simulation nodel for any AMI supported software environment within ive working days.

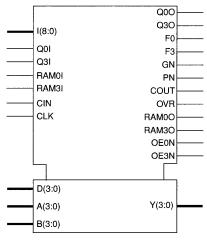

#### **Digital Soft Megacells**

The AMI6X gate array and standard cell families support soft megacells that are compatible with many popular functions. These megacells are functionally and logically compatible with the stand-alone products.

A soft megacell is defined only at the functional schematic level. Each instance of the megacell will have exactly the same functional definition; however, the physical mask layout will be different depending on other functions being used, the place-and-route tools, and process technology. The megacell becomes part of the design netlist, requiring back annotation of interconnect capacitance after placeand-route for final verification.

Because AMI's soft megacells are defined at the gate level, simulation models are more accurate than that of behavioral models. Since our soft megacells use AMI's ASIC Standard Library they have the advantages of design flexibility, portability, and a path for future cost reduction by process migration.

AMI's selection of soft megacells include Core Processors and Peripherals which duplicate the function of industry standard parts. In addition AMI offers FIFOs and Datapath megacells which are developed using synthesizers. These products are listed in the following tables.

#### **Core Processors and Peripherals**

The Core Processor and Peripheral megacells are designed to duplicate the function of industry standard, stand-alone parts. Detailed functional information can be found in any standard device datasheet.

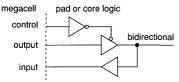

#### AMI's Innovative Pad Piece Methodology

The AMI6X standard libraries provide an innovative new approach to IO pad cell design. By choosing from a vast array of input, output, and pullup/pulldown pad piece cells, the ASIC designer can literally create thousands of different IO cell configurations simply by making the appropriate schematic or HDL connections. In addition,

## AMI6S 0.6 micron CMOS Standard Cells

AMI conversion libraries can easily migrate netlist designs from previous technologies that use ASIC STD pad cells. AMI's Enhanced Design Utilities Tools flatten pad cells to their functional (fundamental) pad-piece blocks. Custom configurations are arrived at simply by "swapping out" the pieces. Pad-piece design benefits AMI customers by drastically reducing the need to request and wait for workstation simulation models of IO pad cells that would not yet exist. For detailed information of pad piece usage see AMI applications note *Pad Pieces* (4401035).

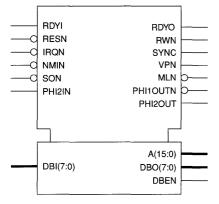

#### **Core Processors**

| Name     | Function                          |

|----------|-----------------------------------|

| MG29C01  | 4-bit microprocessor slice        |

| MG29C10  | Microprogram controller/sequencer |

| MG65C02  | 8-bit microprocessor              |

| M8042    | 8-bit slave microcontroller       |

| M8048    | 8-bit microcontroller             |

| MG80C85  | 8-bit microprocessor              |

| MGMC51   | Core processor, 8051 compatible   |

| MGMC51I  | MGMC51 with ICE port              |

| MGMC51FB | Core processor, 8051FB compatible |

| MGMC51SD | Reduced function MGMC51           |

#### Peripherals

| Name      | Function                         |

|-----------|----------------------------------|

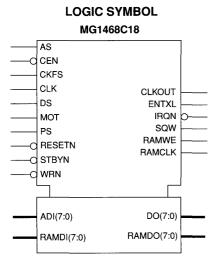

| MG1468C18 | Real-time clock                  |

| M16C450   | UART                             |

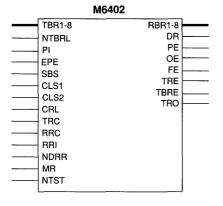

| M6402     | UART                             |

| M6845     | CRT controller                   |

| M765A     | Floppy disk controller           |

| M8251A    | Communication interface USART    |

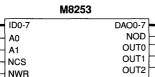

| M8253     | Programmable interval timer      |

| M82530    | Serial communications controller |

| MG82C37A  | Programmable DMA controller      |

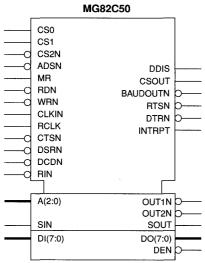

| MG82C50A  | Asynchronous comm. element       |

| Name     | Function                                      |

|----------|-----------------------------------------------|

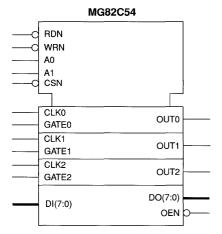

| MG82C54  | Programmable interval timer                   |

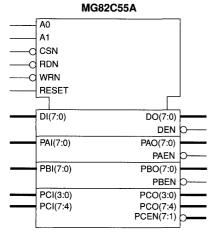

| MG82C55A | Programmable peripheral interface             |

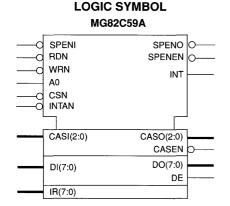

| MG82C59A | Programmable interrupt controller             |

| M8490    | SCSI controller                               |

| M85C30   | Serial communications controller              |

| M8868A   | UART                                          |

| M91C36   | Digital data separator                        |

| M91C360  | Digital data separator                        |

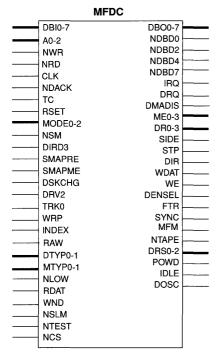

| MFDC     | Floppy disk controller                        |

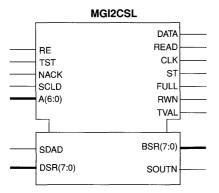

| MGI2CSL  | I <sup>2</sup> C Serial bus slave transceiver |

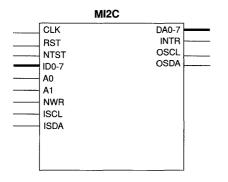

| MI2C     | I <sup>2</sup> C Bus Interface                |

#### **FIFOs**

The AMI6X library supports both latched-based and dualport ram based FIFOs. The latch-based FIFO has a fallthrough architecture and is applicable when the FIFO size is limited. For large sizes the RAM based FIFO is appropriate.

#### **FIFOs**

| Name       | Function          |  |

|------------|-------------------|--|

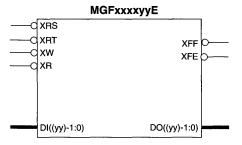

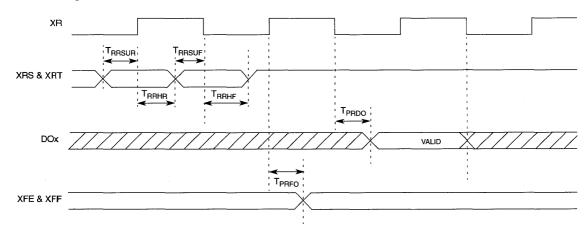

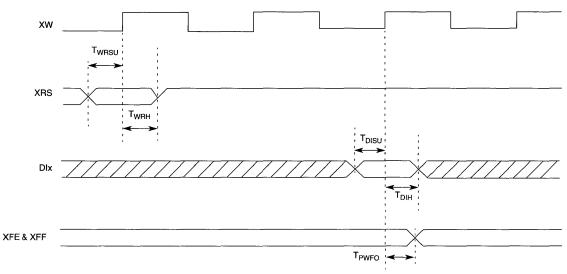

| MGFxxyyC1  | Fall-through FIFO |  |

| MGFxxxxyyD | Synchronous FIFO  |  |

| MGFxxxxyyE | Asynchronous FIFO |  |

## AMI6S 0.6 micron CMOS Standard Cells

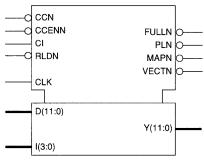

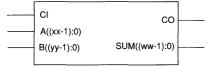

#### Datapath

AMI also supports the complex datapath logic functions listed here. These functions are synthesized from an input set of design parameters. They can be optimized for either minimum delay, minimum gate count or can be designed to meet a specified delay. Contact AMI for the size range and parameter set for any desired functions.

These logic synthesizers produce soft megacell schematics in the ASIC Standard Library, and a schematic symbol for incorporation and simulation with the design netlist.

#### Datapath

| Name      | Function                     |

|-----------|------------------------------|

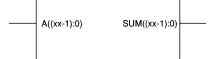

| MGAxxyyDv | Adder                        |

| MGAxxyyEv | Adder-subtractor             |

| MGBxxyyAv | Barrel/arithmetic shifter    |

| MGBxxBv   | Barrel shifter               |

| MGBxxyyCv | Arithmetic shifter           |

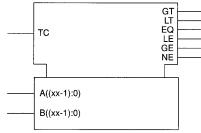

| MGCxxAv   | 2-function binary comparator |

| MGCxxBv   | 6-function binary comparator |

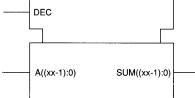

| MGDxxAv   | Decrementer                  |

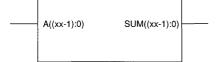

| MGIxxAv   | Incrementer                  |

| MGIxxBv   | Incrementer/decrementer      |

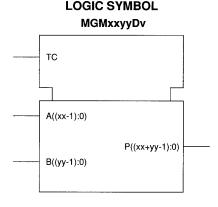

| MGMxxyyDv | Signed/unsigned multiplier   |

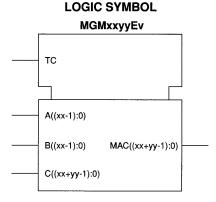

| MGMxxyyEv | Multiplier-accumulator       |

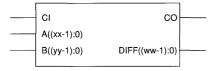

| MGSxxyyAv | Signed/unsigned subtractor   |

#### Ordering information

With each megacell, AMI supplies schematics and test vectors on the requested EDA tool. To order a megacell, use the *Digital Soft Megacell order form*. Contact the factory for information on the delivery of soft megacells on various EDA tools or for information on specific speeds and sizes of particular Datapath megacells.

# AMI6S 0.6 micron CMOS Standard Cells

## **DC Specifications**

#### **Operating Specifications**

|                                | Parameter                                                                                 | Minimum             | Maximum             | Units |

|--------------------------------|-------------------------------------------------------------------------------------------|---------------------|---------------------|-------|

| V <sub>DD</sub> Supply Voltage |                                                                                           | 2.7                 | 5.5                 | Volts |

| Ambient Temperature            | - Military                                                                                | -55                 | 125                 | °C    |

|                                | - Commercial                                                                              | 0                   | 70                  | °C    |

| <b>CMOS Input Specifica</b>    | tions (4.5V <vdd<5.5v;0°c<t< td=""><td>&lt;70°C)</td><td></td><td></td></vdd<5.5v;0°c<t<> | <70°C)              |                     |       |

| Vil                            | Low Level Input Voltage                                                                   |                     | 0.3*V <sub>DD</sub> | Volts |

| Vih                            | High Level Input Voltage                                                                  | 0.7*V <sub>DD</sub> |                     | Volts |

| lil                            | Low Level Input Current                                                                   |                     | -1.0                | μΑ    |

| lih                            | High Level Input Current                                                                  |                     | 1.0                 | μΑ    |

| lil                            | Input Pull-Up Current                                                                     | -39                 | -100                | μΑ    |

| lih                            | Input Pull-Down Current                                                                   | 41                  | 125                 | μΑ    |

| Vt-                            | Schmitt Negative Threshold                                                                | 0.2*V <sub>DD</sub> |                     | Volts |

| Vt+                            | Schmitt Positive Threshold                                                                |                     | 0.8*V <sub>DD</sub> | Volts |

| Vh                             | Schmitt Hysteresis                                                                        | 1.0                 |                     | Volts |

| TTL Input Specificatio         | ons (4.5V <vdd<5.5v; 0°c<t<70<="" td=""><td>°C)</td><td></td><td></td></vdd<5.5v;>        | °C)                 |                     |       |

| Vil                            | Low Level Input Voltage                                                                   |                     | 0.8                 | Volts |

| Vih                            | High Level Input Voltage                                                                  | 2.0                 |                     | Volts |

| 81                             | Low Level Input Current                                                                   |                     | -1.0                | μA    |

| lih                            | High Level Input Current                                                                  |                     | 1.0                 | μA    |

| lit                            | Input Pull-Up Current                                                                     | -39                 | -100                | μΑ    |

| lih                            | Input Pull-Down Current                                                                   | 41                  | 125                 | μA    |

| Vt-                            | Schmitt Negative Threshold                                                                | 0.7                 |                     | Volts |

| Vt+                            | Schmitt Positive Threshold                                                                |                     | 2.1                 | Volts |

| Vh                             | Schmitt Hysteresis                                                                        | 0.4                 |                     | Volts |

#### Output Operating Specifications (4.5V<V<sub>DD</sub><5.5V;0°C<T<70°C)

| Driver       | Vol<br>Maximum | Voh<br>Minimum | lol<br>Maximum | loh<br>Maximum |

|--------------|----------------|----------------|----------------|----------------|

| 1 mA Driver  | 0.4            | 2.4            | 1.0            | -1.0           |

| 2 mA Driver  | 0.4            | 2.4            | 2.0            | -2.0           |

| 4 mA Driver  | 0.4            | 2.4            | 4.0            | -4.0           |

| 8 mA Driver  | 0.4            | 2.4            | 8.0            | -8.0           |

| 16 mA Driver | 0.4            | 2.4            | 16.0           | -16.0          |

| 24 mA Driver | 0.4            | 2.4            | 24.0           | -24.0          |

\_/ol = Low Level Output Voltage given in Volts

/oh = High Level Output Voltage given in Volts

Iol = Low Level Output Current given in mA

Ioh = High Level Output Current given in mA

#### **Absolute Maximum Ratings**

IERICAN MICROSYSTEMS, INC

| Parameter                              | Minimum | Maximum              | Units          |

|----------------------------------------|---------|----------------------|----------------|

| V <sub>DD</sub> , Supply voltage       | -0.3    | 6.0                  | Volts          |

| Input pin voltage                      | -0.3    | V <sub>DD</sub> +0.3 | Volts          |

| Input pin current                      | -10.0   | 10.0                 | mA             |

| Storage temperature - Plastic packages | -55     | 125                  | ℃              |

| - Ceramic packages                     | -65     | 150                  | °C             |

| Lead temperature                       |         | 300                  | °C for 10 sec. |

ote that these specifications are to indicate levels where permanent damage to the device may occur. Functional operation is not guaranteed under these conditions. In ther, operation at absolute maximum conditions for extended periods may adversely affect the long term reliability of the device.

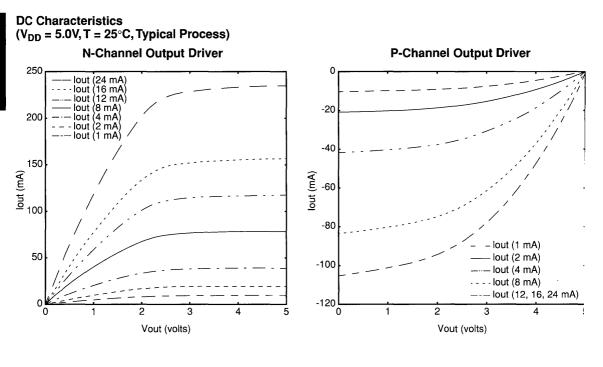

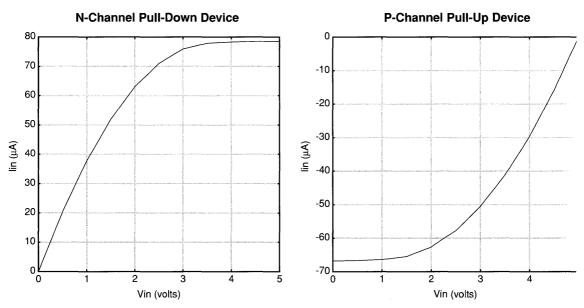

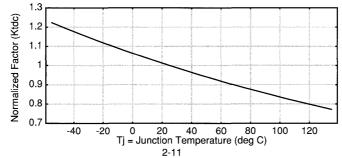

### **DC Derating Information**

The DC Characteristics on page 2-11 can be derated to obtain values at other operating conditions using the formula:

#### IDC\*KPDC\*KVDC\*KTDC

where  $I_{DC}$  is a value from the current curves on page 11.  $K_{PDC}$ , the DC process derating coefficient;  $K_{VDC}$ , the DC voltage derating coefficient; and  $K_{TDC}$ , the DC temperature derating coefficient, are described below. Due to the ESD protection structures, the N-channel driver has a different set of coefficients for  $K_{PDC}$  and  $K_{TDC}$ .

#### DC Variations with process (K<sub>PDC</sub>)

DC variations with process are given as fixed constants determined at the limits of acceptable manufacturing of the process. These are described below where WCS is the "Worst Case Speed" fabrication, TYP is the "Target" fabrication, and WCP is the "Worst Case Power" fabrication.

|                  | N-Cha | nnel Output<br>(Vol = 0.4V) |      | N-Chan | nel Pull-Dowi<br>(Vol = 0.4V) | n Device | -    | All P-Channe<br>(Voh = 2.4V) | -    |

|------------------|-------|-----------------------------|------|--------|-------------------------------|----------|------|------------------------------|------|

| Process          | WCS   | TYP                         | WCP  | WCS    | TYP                           | WCP      | WCS  | TYP                          | WCP  |

| K <sub>PDC</sub> | 0.61  | 1.00                        | 1.47 | 0.71   | 1.00                          | 1.27     | 0.68 | 1.00                         | 1.45 |

#### DC Variations with Voltage (K<sub>VDC</sub>)

|                  |      | All N-Channel<br>(Voi = 0.4V) |      |      | All P-Channel<br>(Voh = 2.4V) |      |

|------------------|------|-------------------------------|------|------|-------------------------------|------|

| V <sub>DD</sub>  | 4.5  | 5.0                           | 5.5  | 4.5  | 5.0                           | 5.5  |

| K <sub>VDC</sub> | 0.97 | 1.00                          | 1.03 | 0.79 | 1.00                          | 1.21 |

#### DC variations with temperature for the N-Channel output driver (K<sub>TDC</sub>)

#### DC variations with temperature for all other N-Channel and P-Channel devices

### **Delay Derating Information**

The propagation delays listed in the data sheets are for typical temperature, 25°C; typical supply voltage, 5.0V; and typical processing conditions. To calculate the delay at other conditions (including V<sub>DD</sub> equals 3.0V) the following equation can be used:

#### $T_{pdx} = T_{pdx}(typ) * K_P * K_V * K_T$

where  $T_{pdx}$ (typ) is given in the data sheets.  $K_P$  the process derating coefficient;  $K_T$ , the temperature derating coefficient and  $K_V$  the supply voltage derating coefficient, are described below.

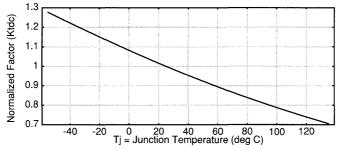

#### Delay Variations with Temperature (K<sub>T</sub>)

Delay varies linearly with temperature. The following formulas and common operating points can be used.

| Temp  | K <sub>T</sub> |

|-------|----------------|

| -55°C | 0.84           |

| -25°C | 0.90           |

| O°C   | 0.94           |

| 25°C  | 1.00           |

| 70°C  | 1.09           |

| 100°C | 1.16           |

| 125°C | 1.22           |

| Temp. Range   | K <sub>T</sub> Formula                                                 |

|---------------|------------------------------------------------------------------------|

| -55°C to 25°C | $K_{\rm T} = 1.0 - (25 - T_{\rm J}^{\circ} C)^{*} 2.12 \times 10^{-3}$ |

| 25°C to 140°C | $K_{T} = 1.0 + (T_{J}^{\circ}C-25)^{*}2.12 \times 10^{-3}$             |

| 25 C to 140 C |                                                                        |

Where T<sub>J</sub>°C is the temperature at the silicon junction.

#### Delay Variations with Process (K<sub>P</sub>)

Delay variations with process are given as fixed constants determined at the limits of acceptable manufacturing of the process. These are described below.

| Derating Coefficient (K <sub>P</sub> ) | Process Variation Point                                     |

|----------------------------------------|-------------------------------------------------------------|

| 1.36                                   | Delay increase due to "Worst Case Speed" (WCS) fabrication  |

| 1.00                                   | Typical delay; Fabrication target                           |

| 0.71                                   | Delay reduction due to "Worst Case Power" (WCP) fabrication |

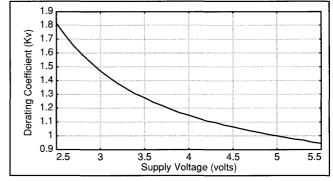

#### Delay Variations with Voltage (K<sub>V</sub>)

Delay varies nonlinearly with voltage. Some common operating points and a characteristic curve are shown.

| V <sub>DD</sub> | Kv   |

|-----------------|------|

| 2.7V            | 1.65 |

| 3.0V            | 1.47 |

| 3.3V            | 1.34 |

| 4.5V            | 1.07 |

| 4.75V           | 1.03 |

| 5.0V            | 1.00 |

| 5.25V           | 0.97 |

| 5.5V            | 0.95 |

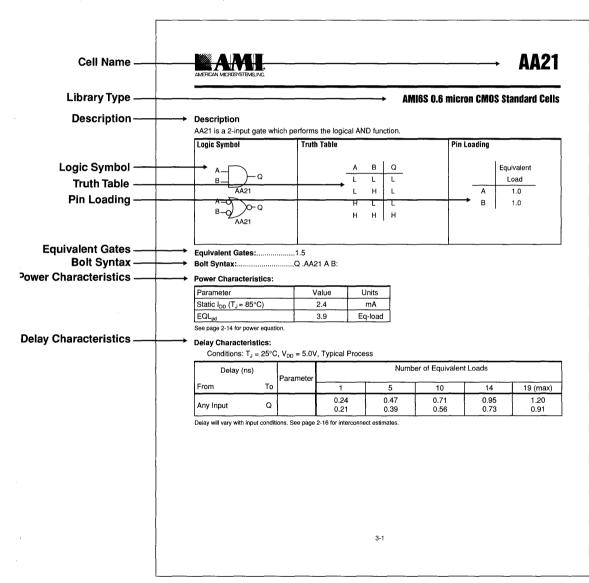

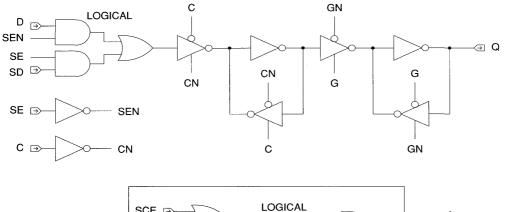

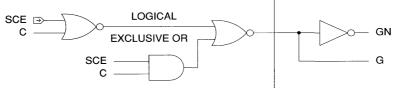

### **Interpreting the Data Sheet**

The figure below shows a typical data sheet and points out the main features of the data sheet. Not shown is a schematic which accompanies some of the more complex cells.

# Library Characteristics

### AMI6S 0.6 micron CMOS Standard Cells

A description of data sheet features are as follows.

**LIBRARY TYPE:** Designates the feature size and library type such as standard cell or gate array.

CELL NAME: AMI's cell name.

DESCRIPTION: A brief sentence about the function of the cell.

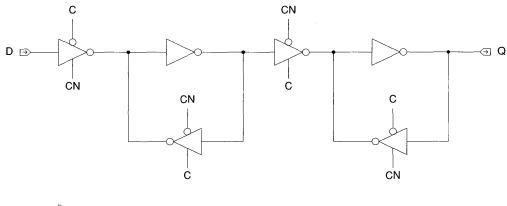

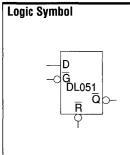

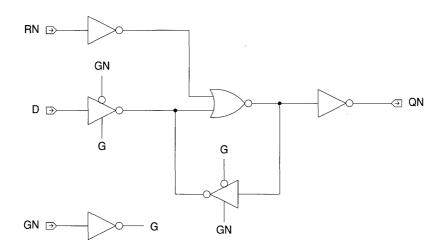

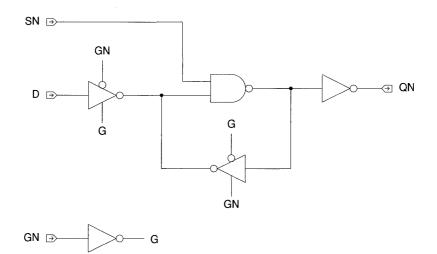

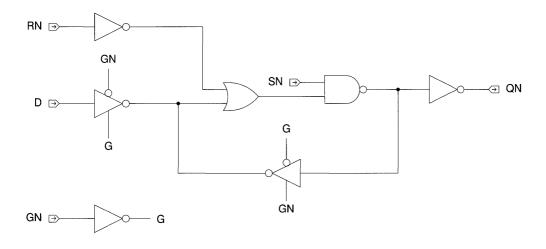

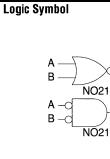

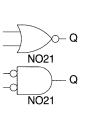

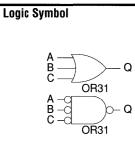

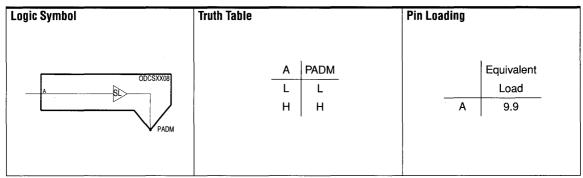

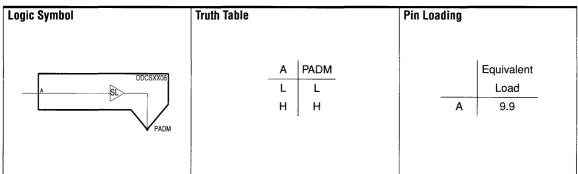

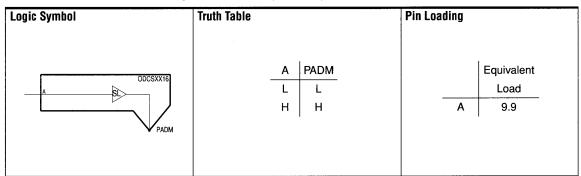

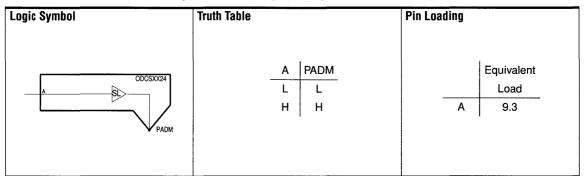

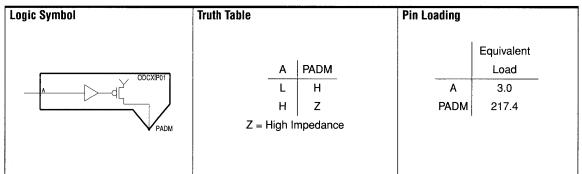

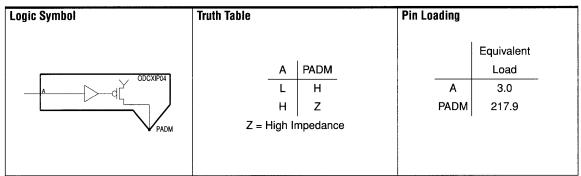

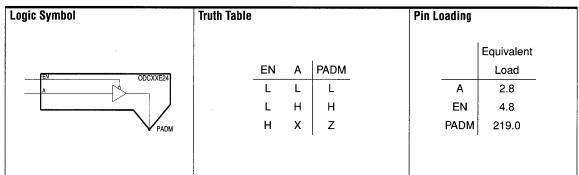

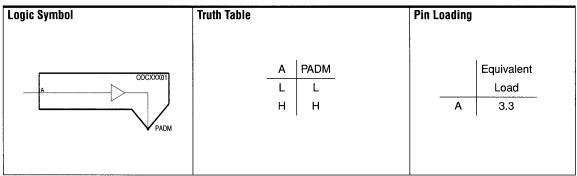

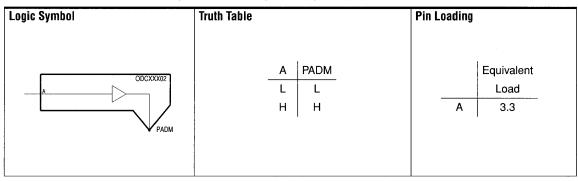

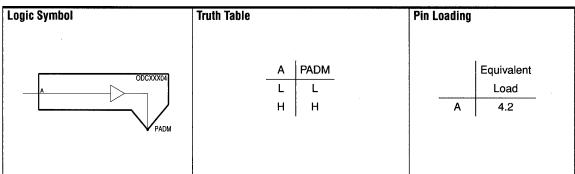

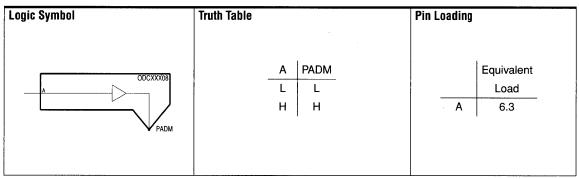

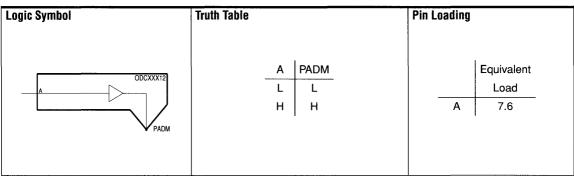

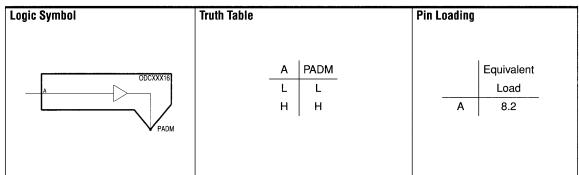

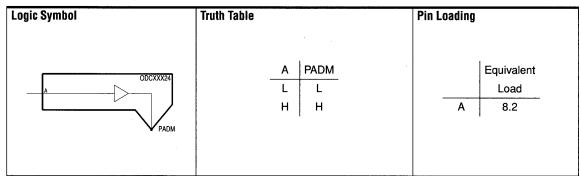

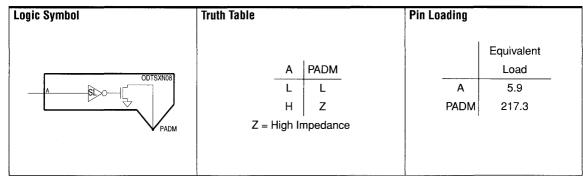

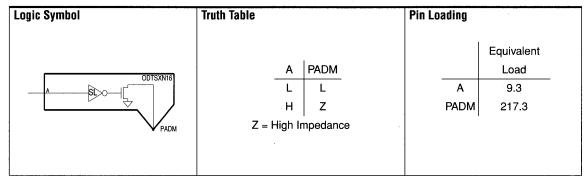

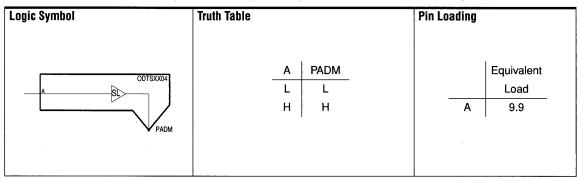

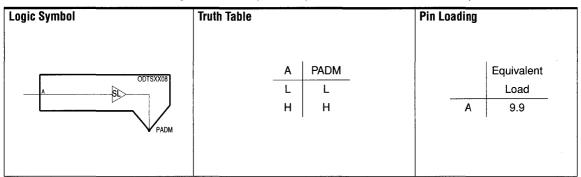

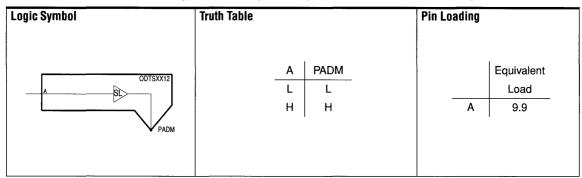

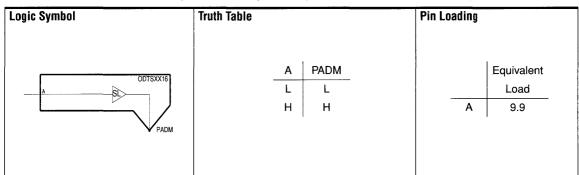

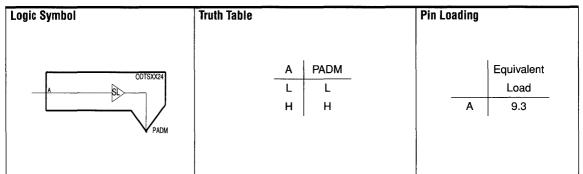

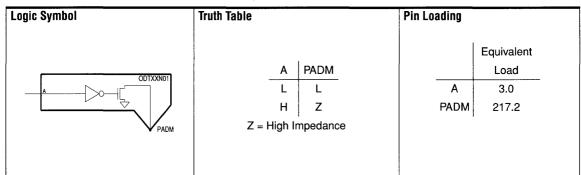

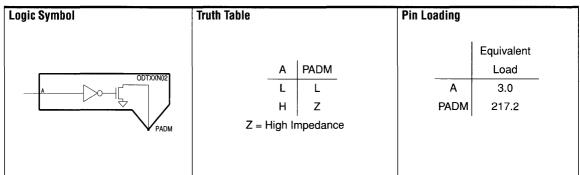

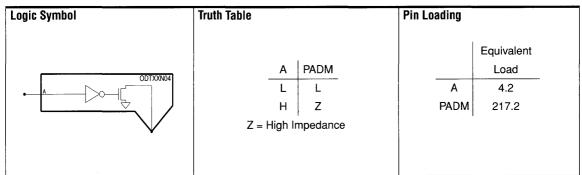

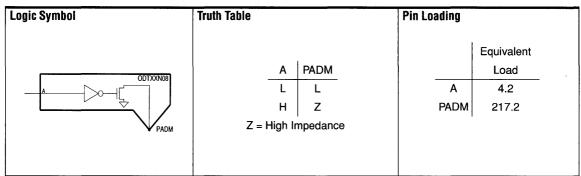

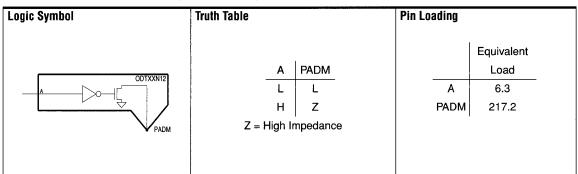

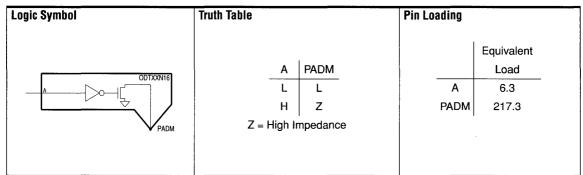

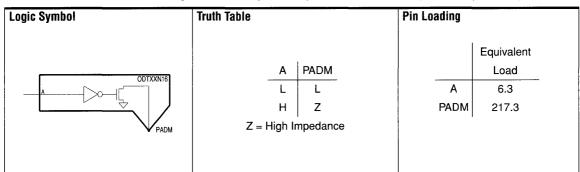

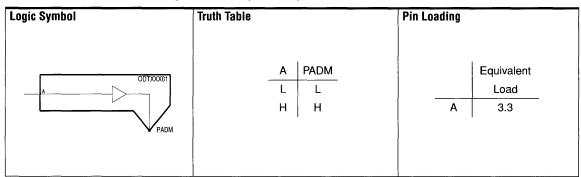

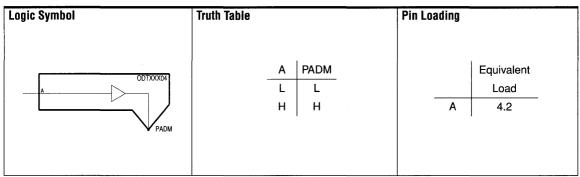

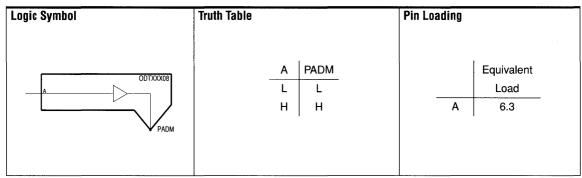

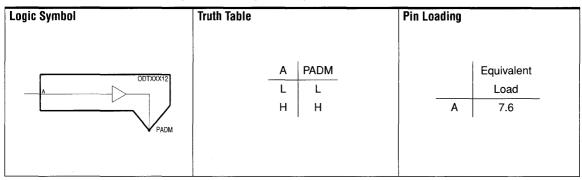

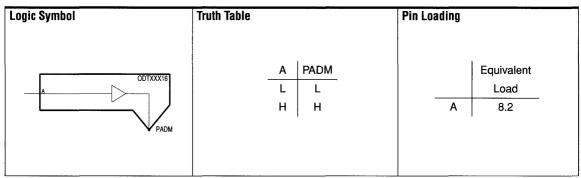

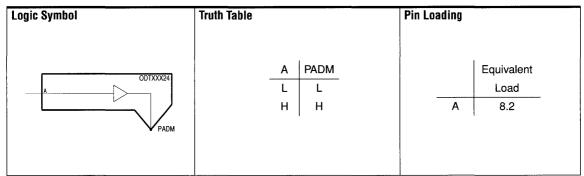

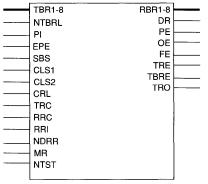

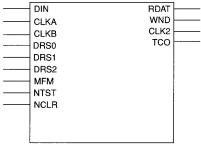

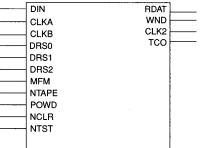

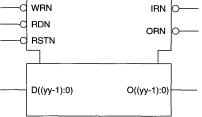

LOGIC SYMBOL: Shows a picture of the symbol as it may appear in the workstation design kits.

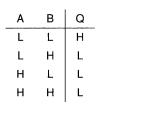

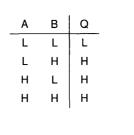

TRUTH TABLE: A boolean table showing the output logic levels as a function of the input logic levels.

Types of logic levels found in the logic tables are as follows:

- H = High level steady state,

- = Low level steady state,

- = Transition from low level to high level,

- $\downarrow$  = Transition from high level to low level,

- X = Any level including transitions,

- NC = No change in output level for a given set of input levels,

- IL = The output level is unknown for this set of illegal input levels,

- Z = High impedance level,

- UN = Undriven node or input,

- Q(n) = The level of Q before an active transition on the affecting node, and

- QN(n) = The level of QN before an active transition on the affecting node.

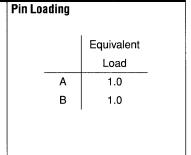

**PIN LOADING:** A table of cell input loads in units of equivalent loads (the input load normalized to the input load of ar NA21, 2-input NAND gate).

EQUIVALENT GATES: Equivalent gates for the cell is defined as the cell area normalized to the area of the NA21.

**BOLT SYNTAX:** BOLT (Block Oriented Logic Translator) is an AMI proprietary netlist format. This line shows the BOLT syntax for the cell. One example of the use of BOLT is as a design interface from the workstation design kits to AMI.

**POWER CHARACTERISTICS:** Power for the cell can be described in three parts. The first part is the power dissipated due to the leakage current across the channels and through the formed diodes. The second part is due to the switching voltage across loads on the internal nodes of the cell. Finally, the third part is due to the switching voltage across a load that a cell is driving.

The power characteristics table provides the static leakage current for a junction temperature of 85°C, and the dissipative load for all the switching nodes in the cell in terms of equivalent loads. The load that a cell drives can be calculated by adding up input loads and adding to it the estimated load from the Load Estimation table on page 2-15. Below are equations for calculating the power dissipation.

Core Cells and Input Buffers

POWER = (Static I<sub>DD</sub>)  $V_{DD}$  + (0.035E-12)EQL<sub>pd</sub> $V_{DD}^{2}$ f + (0.035E-12)EQL<sub>I</sub> $V_{DD}^{2}$ f

Output Buffers

$POWER = (Static I_{DD}) V_{DD} + (0.035E-12)EQL_{pd}V_{DD}^{2}f + C_{ol}V_{DD}^{2}f$

where:

Static I<sub>DD</sub> = static leakage current of the cell

- V<sub>DD</sub> = operating voltage

- $EQL_{pd} = load of the switching nodes in the cell$

- $\tilde{f}$  = frequency of operation

- Col = load in farads on the output buffer

- EQLI = load of the driven interconnect and driven input pins

The frequency term of the power equation dominates, making the static current term insignificant. However, the term cal be used to find the standby current.

L

↑

## Library Characteristics

### AMI6S 0.6 micron CMOS Standard Cells

Generally, three types of buffers (input, output, and bidirectional) may be assembled using pad piece cells. Calculating power characteristics for pad pieces is dependent on the desired buffer type. The power dissipated by a buffer is the cumulative power dissipated by its component pad pieces.

- · ID pieces use the input buffer equation. (The input and output buffer equations are described on the previous page.)

- Output pieces use the output buffer equation. Note that C<sub>OL</sub> does not include any PADM pin loading of ID or PL pad piece cells that may be connected to the OD piece.

- PL pieces use the output buffer equation. C<sub>OL</sub> does not include any PADM pin loading of ID or OD pad piece cells that may be connected to the PL piece.

**DELAY CHARACTERISTICS:** This table contains delay data for the various input to output paths in the cells. The table below explains each column in the delay characteristics. AMI models the effects of input slew as well as output resistive -and capacitive loading for a particular cell's path delay. The delay on the data sheets represents a typical load on the nputs of the cell. More accurate timing can be obtained using one of AMI's workstation kits. Contact your sales representative or the factory for details.

| Column Name                      | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delay (ns)<br>From To            | Names the two pins that identify the path for the delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Parameter                        | Mnemonic for the propagation delay or timing parameter whose value can be obtained from the values listed under the number of equivalent loads column.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                  | t <sub>PLH</sub> Input to output propagation delay for a rising edge on the output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                  | t <sub>PHL</sub> Input to output propagation delay for a falling edge on the output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

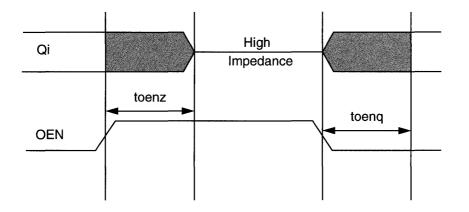

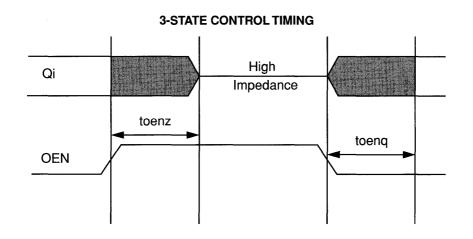

|                                  | t <sub>ZH</sub> High impedance to high level delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                  | t <sub>ZL</sub> High impedance to low level delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                  | t <sub>HZ</sub> High level to high impedance delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                  | t <sub>LZ</sub> Low level to high impedance delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

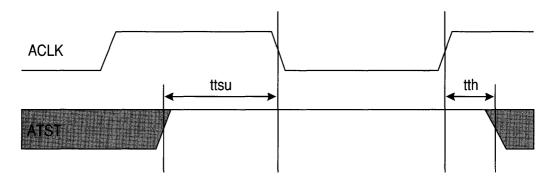

|                                  | t <sub>su</sub> Input setup time with respect to clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                  | t <sub>h</sub> Input hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

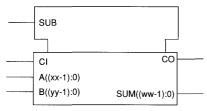

|                                  | tw Input pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |