# 1990 Products Catalog

Gould AMI

.

. .

·---/

¥

ж. - , , \* У. , , ф

١

## 1990 Products Catalog

Gould AMI 2300 Buckskin Road Pocatello, ID 83201 Telephone: (208) 233-4690

## Introduction

Gould AMI, a division of Gould, Inc., is headquartered in Pocatello, Idaho and is the semiconductor industry leader in the design and manufacture of application specific integrated circuits. It manufactures special circuits for leading computer manufacturers, telecommunications companies, automobile manufacturers, consumer and military product companies worldwide.

Gould AMI has always focused on customer needs. As the original architect of Application Specific Integrated Circuit (ASIC) technology, Gould has a rock solid foundation and knows that great service, short development spans, good first silicon, competitive production prices, and the highest quality product are what it takes to keep our customers competitive. From the early days of handdrawn custom through the CAE/CAD boom, to today's silicon compilers, Gould has been providing custom, semicustom and standard product solutions for over 20 years, longer than any other ASIC vendor.

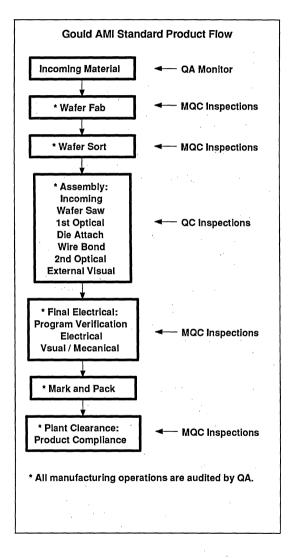

While extensive quality assurance programs are utilized, the Gould belief is that quality must be "built-in" to a product, not "inspected-in." This is a critical element in the philosophy of Gould AMI. Statistical Process Control (SPC) is the tool which has been implemented throughout the company to assure that quality products are produced and the improvement process is on-going. The company leads all other U.S. semiconductor manufacturers in the implementation of SPC.

Gould brings to its customers what is known as the ASIC continuum. This is a complete range of ASIC design styles which will allow each of its customers to have the optimum solution suited to his unique application. The ASIC continuum includes: programmable logic in the form of Electrically Erasable Programmable Logic devices (EEPLDs), gate arrays, standard cells and cell-based custom designs supported by industry-leading cell compilers, and silicon foundry services. Gould engineers and marketers work with each customer to select the type of ASIC that best meets the requirements of his system.

Our E<sup>2</sup>PLDs are desirable for lower volume production or low gate-density requirements. Gould's HCMOS gate arrays provide solutions for a variety of high-performance applications with gate-counts up to 40K. For higher production volume requirements or mega cell implementation, Gould's standard cell and cell-based circuits are especially cost effective.

Along with being the leading designer of custom VLSI, Gould is a leading innovator in combining digital and analog circuitry on a single silicon chip, and is a recognized leader of standard products based on switched capacitor filter technology.

Gould provides components for station equipment, PABX and Central Office Switching systems, data communications, and advanced digital signal processing (DSP) applications.

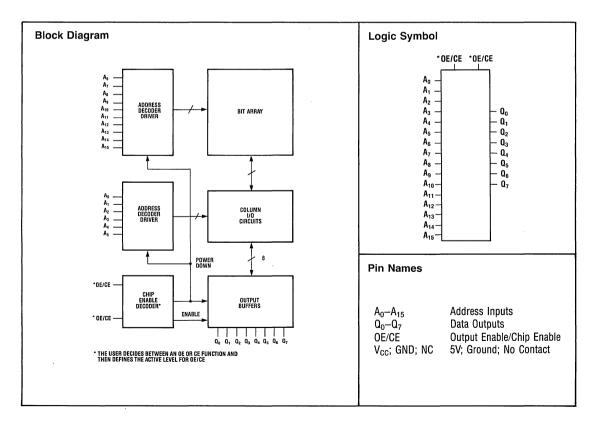

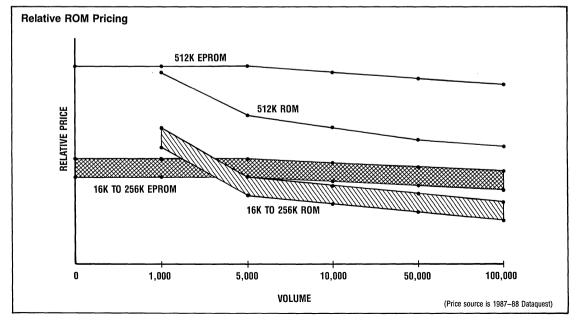

The company also provides ROMs, ranging from 16K to 1 Meg.

Gould offers silicon foundry services including water fabrication, assembly and final test. Originally founded as an MOS company, Gould currently offers process flexibility with more than 30 high-speed, low-power CMOS processes which span 1.25-micron to the mature 5-micron processes.

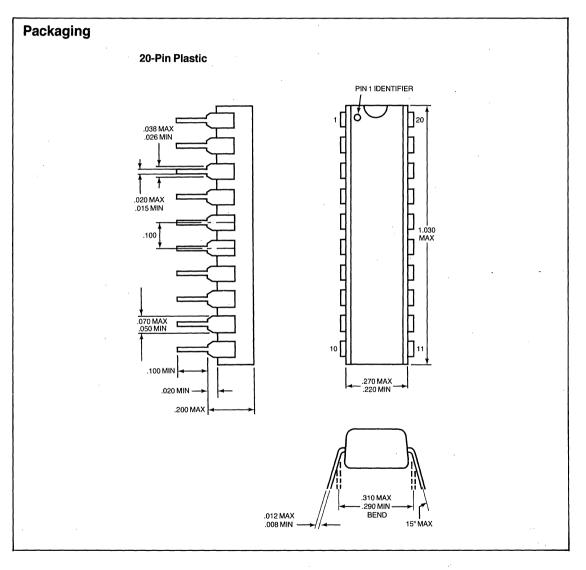

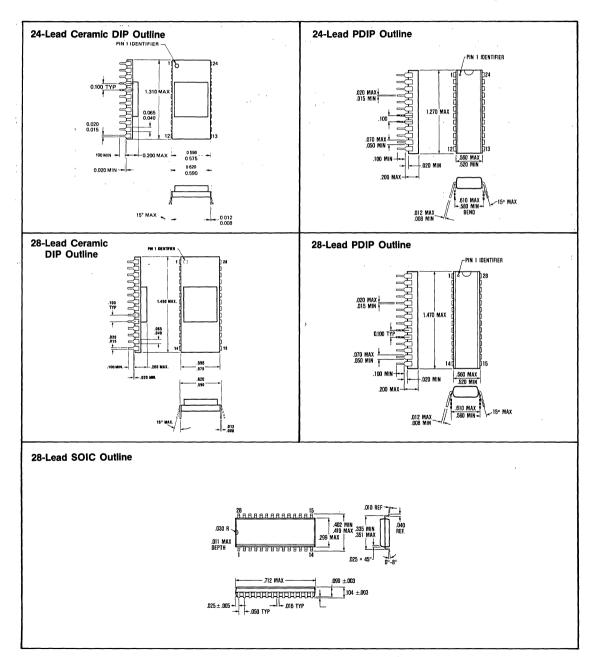

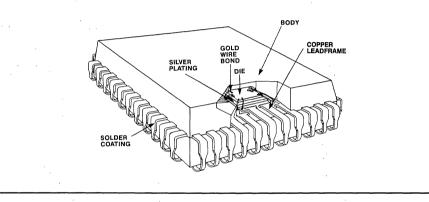

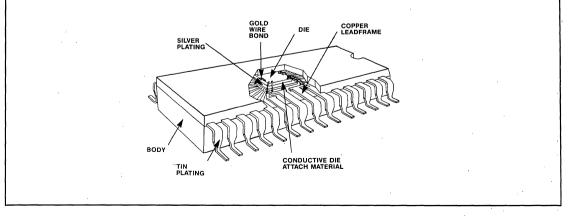

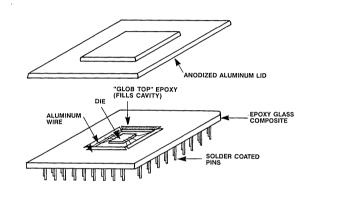

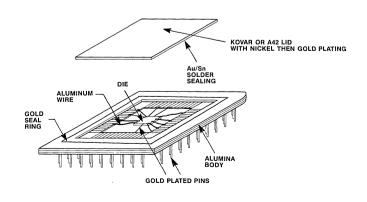

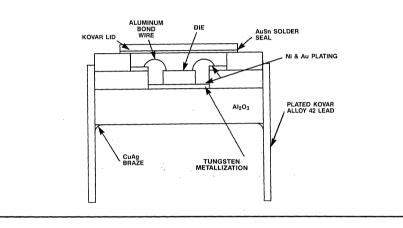

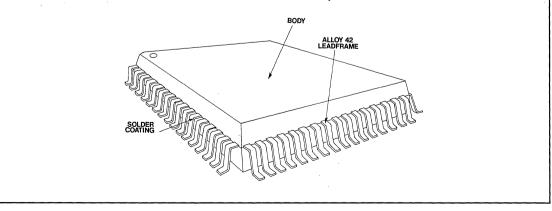

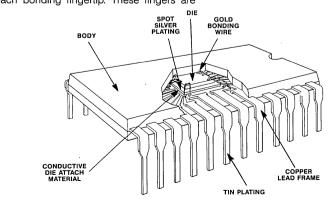

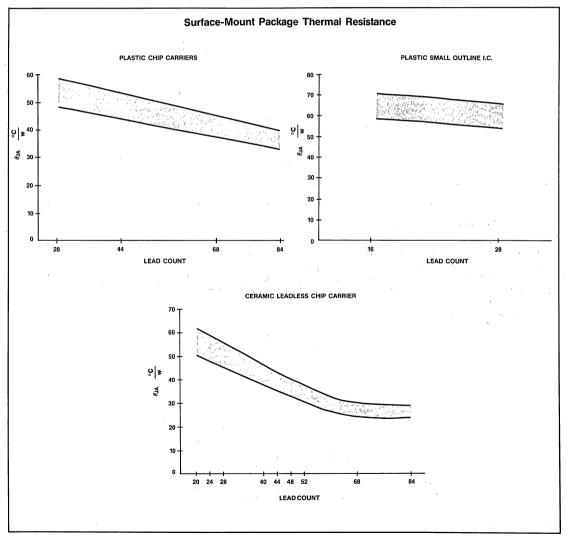

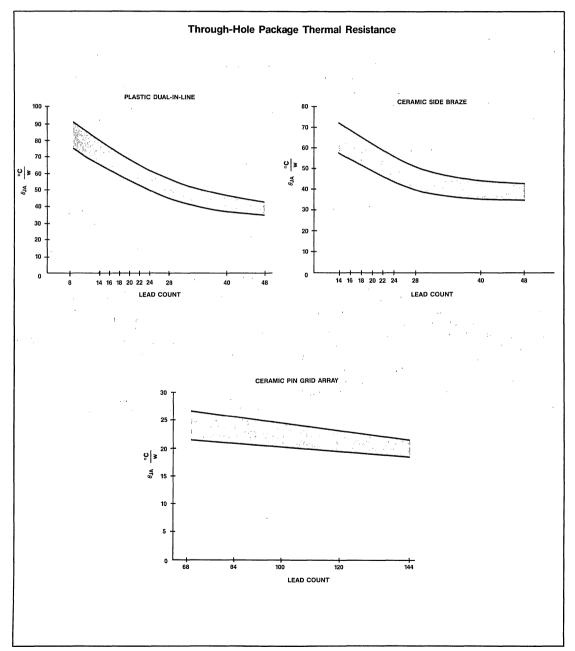

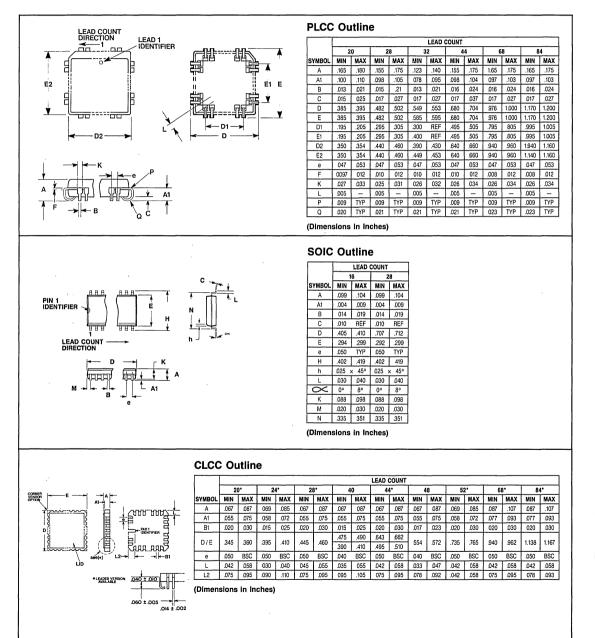

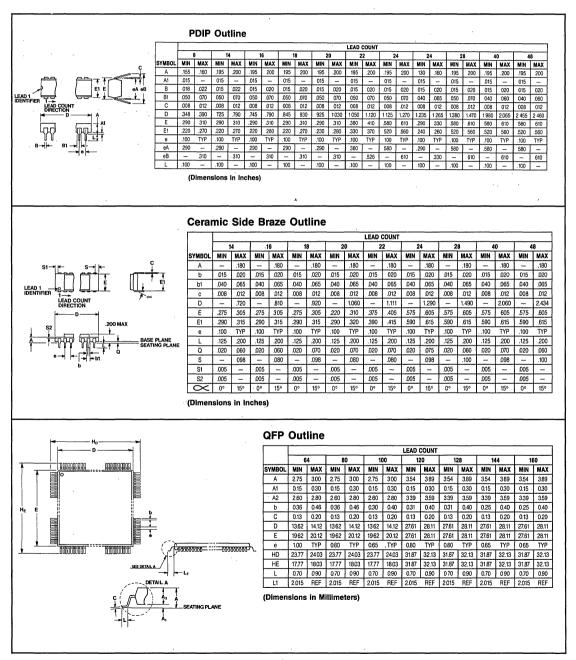

Gould offers one of the broadest package selections available in the industry. Over 250 standard packaging alternatives, all meeting JEDEC standards, are available to meet your individual circuit requirements.

Gould operates an assembly and test operation in Manila, Philippines. Regional sales offices and representatives are extensive; please see listing in the last section.

**Table of Contents**

## 1. Indices

- □ Numerical

- □ Functional

## 2. ASIC Products

- $\Box E^2 PLDs$

- □ Gate Arrays

- □ Standard Cells

- □ Cell-Based Custom

- □ Foundry

- □ ASIC Services

## 3. Communication Products

- □ Station Products

- □ Modems, Filters and PCM Products

- Digital Signal Processors and High Performance Digital Circuits

## 4. Microprocessor Support Circuits

## 5. Display Driver Circuits

6. PLDs

## 7. CMOS & NMOS ROMs

## 8. General Information

- □ Quality Program

- □ Packaging

- □ Ordering Information

- □ Terms of Sale

- World Wide Sales Offices

- Domestic Representatives

- □ Domestic Distributors

- □ International Representatives and Distributors

Copyright © 1989 Gould AMI (All rights reserved) Trade Marks Registered ®

Information furnished by Gould AMI in this publication is believed to be accurate. Devices sold by Gould are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Gould makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Gould makes no warranty of merchantability or fitness for any purposes. Gould reserves the right to discontinue production and change specifications and prices at any time and without notice.

Advanced Product Description means that this product has not been produced in volume, the specifications are preliminary and subject to change, and device programming or designing this product into a system, it is necessary to check with Gould for current information.

characterization has not been done. Therefore, prior to

**Preliminary** means that this product is in limited production, the specifications are preliminary and subject to change. Therefore, prior to programming or designing this product into a system, it is necessary to check with Gould for current information.

These products are intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability application, such as military, medical life-support or life-sustaining equipment are specifically **not** recommended without additional processing by Gould for such application.

Trademarks:

SCEPTRE III is a trademark of Gould Inc., Semiconductor Division PEEL is a trademark of International CMOS Technology, Inc.

Printed in U.S.A.

SCORE is a trademark of Gould Inc., Semiconductor Division Sentry ® is a registered trademark of Fairchild Camera and Instrument Corporation

SCHOLAR is a trademark of Gould Inc., Semiconductor Division NETRANS is a trademark of Gould Inc., Semiconductor Division GATE GOBBLER is a trademark of Gould Inc., Semiconductor Division EXPERT ASIC is a trademark of Gould Inc., Semiconductor Division

INDICES

· · · ·

## Indices

## Alpha/Numerical Index

| Device Page               |

|---------------------------|

| GB Family Gate Arrays 2.5 |

| GC Family Gate Arrays2.4  |

| 18CV86.3                  |

| 18CV8-156.13              |

| 20CG106.16                |

| 20CV106.24                |

| 22CV10Z6.29               |

| PEEL1536.34               |

| PEEL1736.39               |

| PEEL2536.44               |

| PEEL2736.49               |

| PDS6.54                   |

| S23128                    |

| S23256                    |

| S23256                    |

| S25089 3.34               |

| S2559E3.3                 |

| S2559F                    |

| S2560A3.12                |

| S2560G3.19                |

| S2560G13.19               |

| S2561 3.21                |

| Device  | Page  |

|---------|-------|

| S2561A  | 3.21  |

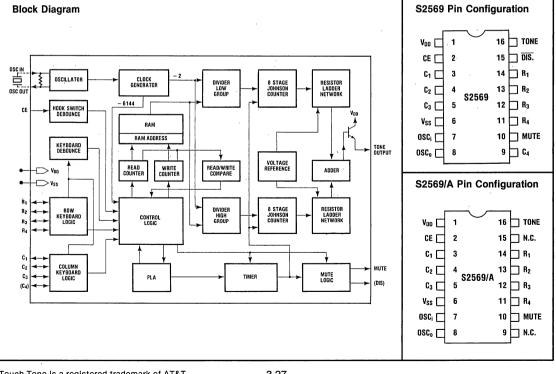

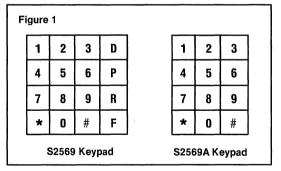

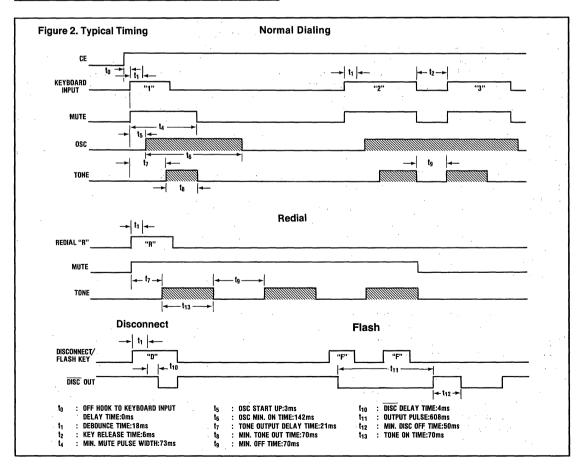

| S2569   | 3.27  |

| S2569A  | 3.27  |

| S2579   | 3.40  |

| S3506I  | 3.154 |

| S3507I  | 3.154 |

| S3507AI | 3.154 |

| S3524A  | 3.118 |

| S3525A  | 3.121 |

| \$3526B | 3.128 |

| S3528B  | 3.135 |

| S3529B  | 3.145 |

| S3531   | 3.103 |

| S3541   | 3.170 |

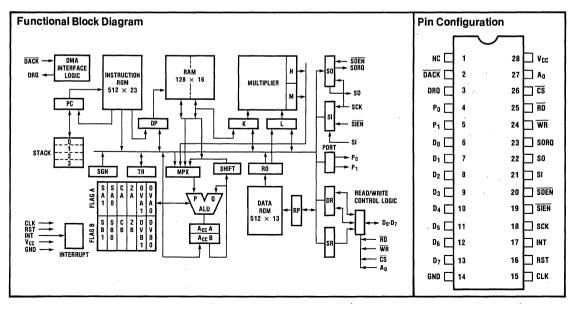

| S3547   | 3.171 |

| S35212A | 3.78  |

| S35212B | 3.84  |

| S35213  | 3.91  |

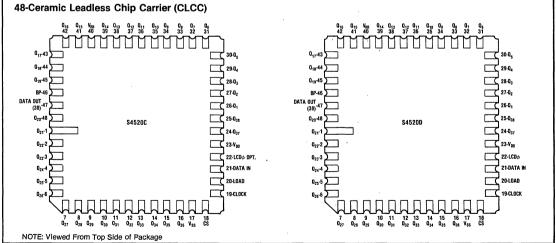

| S4520   | 5.3   |

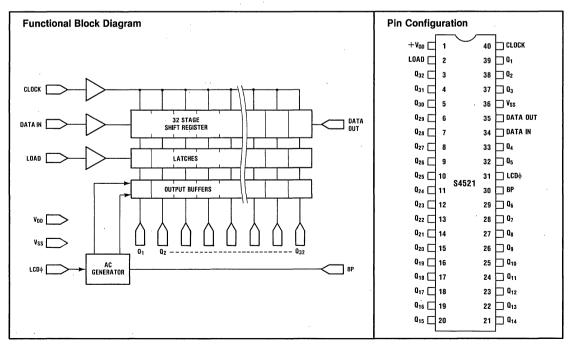

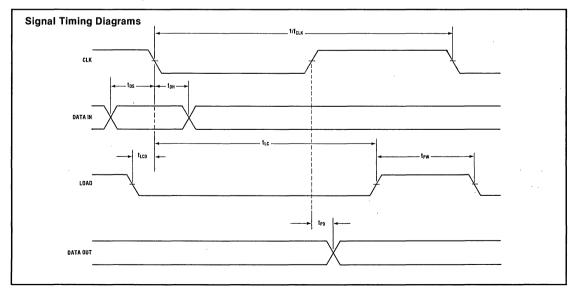

| S4521   | 5.11  |

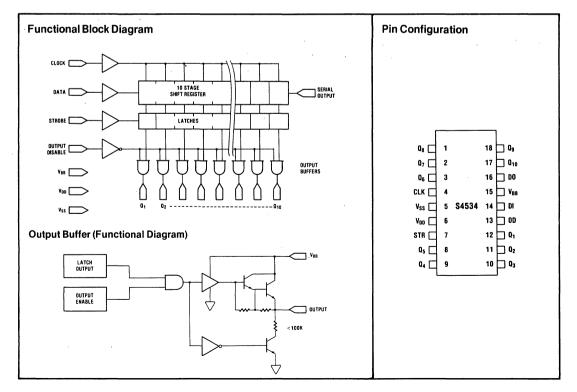

| S4534   | 5.14  |

| S4535   | 5.17  |

| Device  | Page    |

|---------|---------|

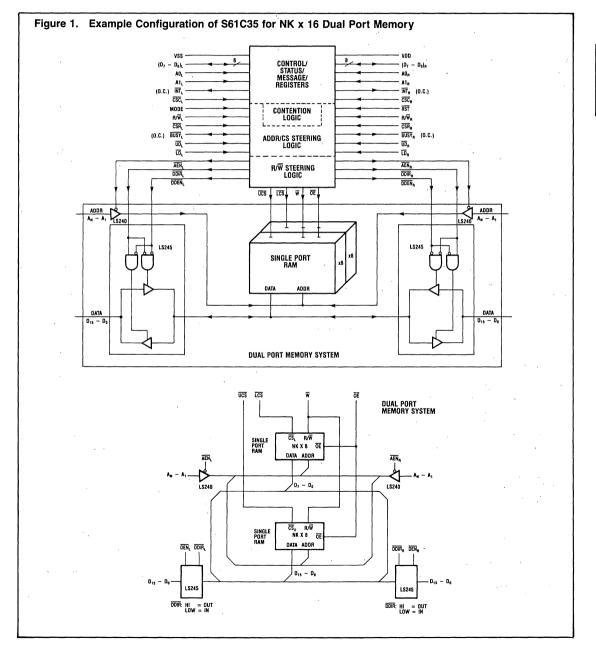

| S61C35  | . 3.202 |

| S61C337 | . 3.221 |

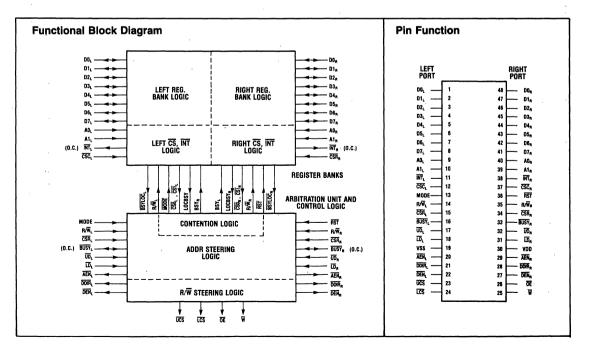

| S614381 | . 3.197 |

| S618839 | . 3.227 |

| S618840 | . 3.241 |

| S6316   | . 7.3   |

| S6333   | . 7.3   |

| S63256  | . 7.3   |

| S63332  | . 7.3   |

| S6364   | . 7.3   |

| S63364  | . 7.3   |

| S63512  | . 7.3   |

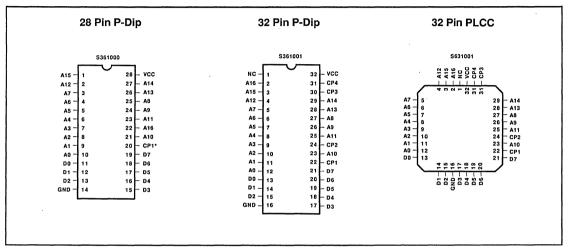

| S631000 | . 7.17  |

| S631001 | . 7.17  |

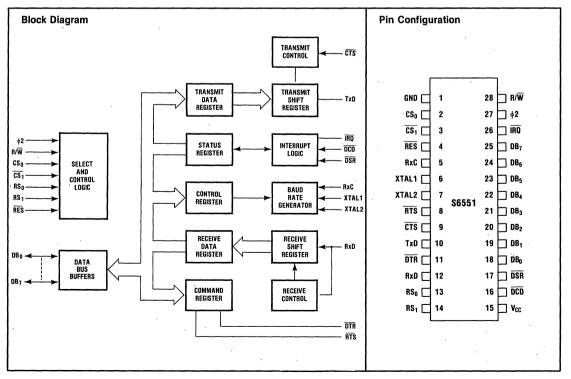

| S6551   | . 4.3   |

| S6551A  | . 4.3   |

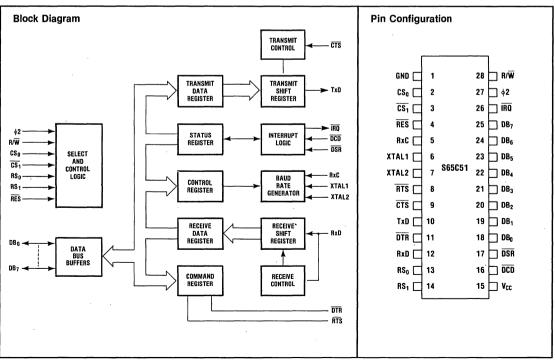

| S65C51  | . 4.11  |

| S6845E  | . 4.26  |

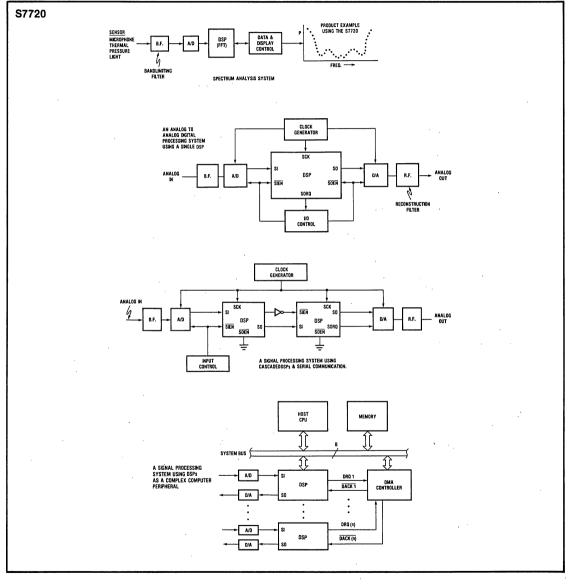

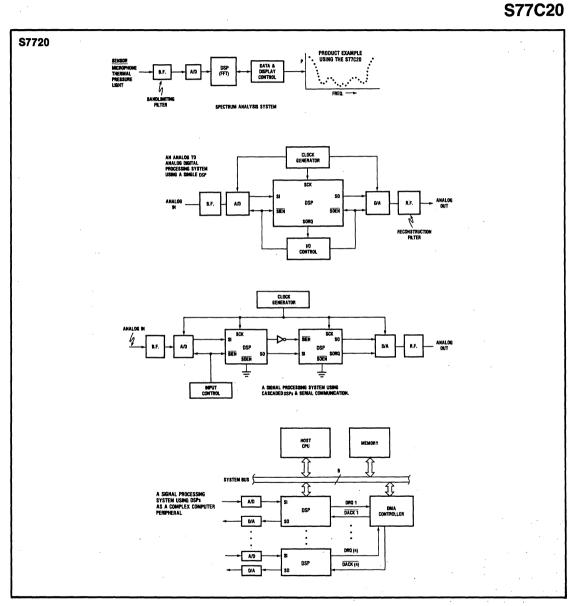

| S7720   | . 3.181 |

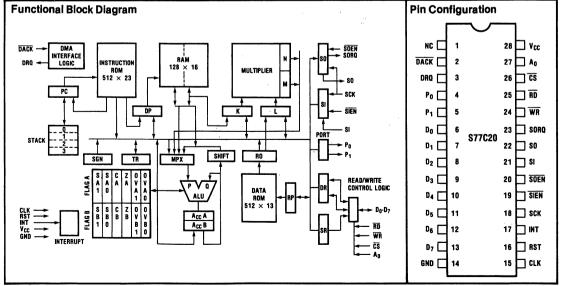

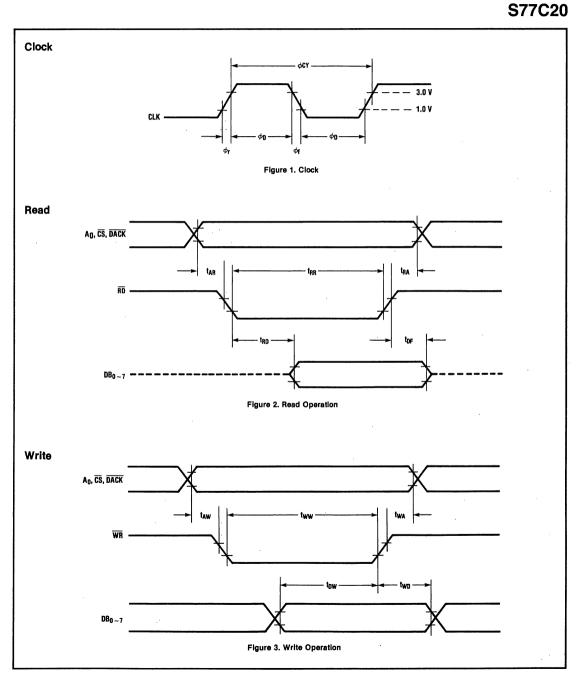

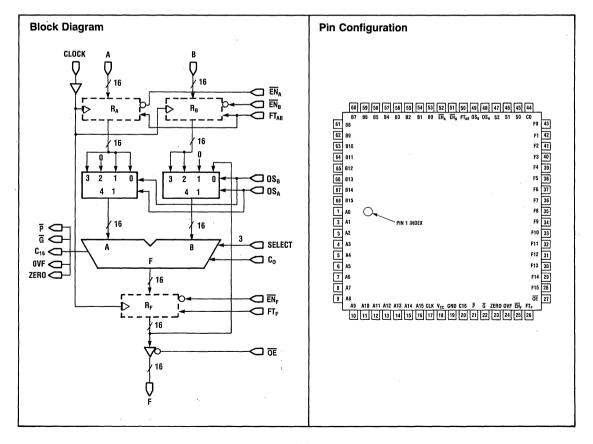

| S77C20  | . 3.186 |

| S8980   | . 3.48  |

| S8981   | . 3.62  |

## Indices

Page

## **Functional Index**

| Device            | Page |

|-------------------|------|

| ASIC Products     | 2.3  |

| EPLDs             | 2.3  |

| Gate Arrays       | 2.4  |

| Standard Cells    | 2.5  |

| Cell-based Custom | 2.6  |

| Foundry           | 2.7  |

| ASIC Services     | 2.8  |

### **Communication Products**

### Station Products

| S2559E  |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3.3 | 3  |

|---------|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|----|

| S2559F  |   |  |   |   |   |   |   |   |   |   |   |   |   |   | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3.3 | 3  |

| S2560A  |   |  |   |   | • |   | • |   |   |   |   |   |   |   | • | • | • |   |   |   |   |   | • |   | • |   | • |   |   |   | 3.  | 12 |

| S2560G/ | 1 |  |   |   | • |   |   | • |   |   |   | • |   |   | • | • | • |   |   | • | • | • | • |   | • |   | • |   |   | • | 3.1 | 19 |

| S2561 . |   |  |   |   |   | • |   |   | • |   |   |   | • |   | • | • |   |   |   |   |   |   | • |   | • |   |   |   |   |   | 3.2 | 21 |

| S2561A  |   |  | • | • | • |   |   | • |   |   |   | • | • |   | • | • |   |   | • |   | • | • | • | • | • |   | • |   | • |   | 3.2 | 21 |

| S2569 . |   |  |   | • | • |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   | ć | • |   |   |   |   | • |   |   |   | 3.2 | 27 |

| S2569A  |   |  |   |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • |   | • |   |   |   |   |   | 3.2 | 27 |

| S25089  |   |  |   |   | • | • | • | • |   |   | • | • |   |   | • | • | • | • | • |   | • | • | • | • | • |   | • | • |   | • | 3.3 | 34 |

| S2579 . |   |  | • | • | • |   | • | • |   | • | • | • |   | • | • | • | • |   |   |   | • | • | • | • | • |   | • | • |   | • | 3.4 | 40 |

| S8980 . |   |  | • | • | • | • | • | • | • |   | • | • |   | • |   | • | • |   |   | • | • | • | • | • | • | • | • |   |   |   | 3.4 | 48 |

| S8981 . |   |  | • | • | • |   | • |   |   |   |   | • |   |   |   | • |   |   |   |   |   | • | • |   | • |   | • |   |   |   | 3.6 | 62 |

### Modems, Filters and PCM Products

| S3521 | 12A      |  |  | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | З | .7  | 8  |   |

|-------|----------|--|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|---|-----|----|---|

| S3521 | 12B      |  |  | • |   |   |   |   |   |   |   |   |   | • |   |   | • |   |   |   |   |   |   |   |   |   |  |   | З | 8.8 | 4  |   |

| S3521 | 13.      |  |  | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | З | .9  | 1  |   |

| S3531 | Ι        |  |  | • |   |   |   |   |   |   |   |   | • |   |   |   | • |   |   | • | • |   |   |   |   |   |  |   | Ś | 1.1 | 0  | 3 |

| S3524 | 1A       |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | З | .1  | 18 | 3 |

| S3525 | 5A       |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | 3 | 1.1 | 2  | 1 |

| S3526 | βB       |  |  |   |   |   |   | • |   |   |   |   | • |   | • | • |   |   | • | • | • |   |   | • |   |   |  |   | 3 | 1.1 | 28 | 8 |

| S3528 | ЗB       |  |  | • |   |   |   |   |   |   | • |   |   |   |   |   |   |   | • |   | • |   |   |   |   |   |  |   | 3 | .1  | 3  | 5 |

| S3529 | θB       |  |  | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | 3 | .1  | 4  | 5 |

| S3506 | SI.      |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   |   |   |  |   | 3 | .1  | 54 | 4 |

| S3507 | η.       |  |  | • |   |   | • |   | • |   |   |   | • | • |   |   |   |   | • |   |   | • | • |   |   |   |  | • | 3 | .1  | 54 | 4 |

| S3507 | 7AI      |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | 3 | .1  | 5, | 4 |

| S3541 | ۱        |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | 3 | .1  | 7( | 0 |

| S3547 | <b>7</b> |  |  | , |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | 3 | .1  | 7  | 1 |

| S7720 | )        |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   | 3 | .1  | 8. | 1 |

| S77C2 | 20       |  |  |   |   | • |   |   |   | • |   |   |   |   | • |   |   |   | • |   |   |   | • |   | • | • |  |   | 3 | .1  | 8( | ô |

| S6143 | 881      |  |  |   |   |   |   |   |   |   | • | • | • |   |   |   |   | • | • | • |   |   |   |   |   |   |  | • | 3 | .1  | 97 | 7 |

|       |          |  |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   |   |     |    |   |

### Device

# S61C35 3.202 S61C337 3.221 S618839 3.227 S618840 3.241

### **Microprocessor Support Circuits**

| S6551 . | <br> |  | <br>  |      |  |  |  |  |   |   |  |   |  |   |   |   |   |   |  | 4.3  |

|---------|------|--|-------|------|--|--|--|--|---|---|--|---|--|---|---|---|---|---|--|------|

| S6551A  | <br> |  | <br>• | <br> |  |  |  |  |   |   |  |   |  |   | • | • |   | • |  | 4.3  |

| S65C51  | <br> |  | <br>• | <br> |  |  |  |  | • | • |  | • |  | • | • | • | • | • |  | 4.11 |

| S6845E  | <br> |  | <br>  | <br> |  |  |  |  |   |   |  |   |  |   |   |   |   |   |  | 4.26 |

### **Display Driver Circuits**

| S4520 |   |  |  |  |  |  |  |  |  |   |  |  |  |  |   |  |  | 5.3  |

|-------|---|--|--|--|--|--|--|--|--|---|--|--|--|--|---|--|--|------|

| S4521 |   |  |  |  |  |  |  |  |  |   |  |  |  |  |   |  |  | 5.11 |

| S4534 | • |  |  |  |  |  |  |  |  | • |  |  |  |  | • |  |  | 5.14 |

| S4535 |   |  |  |  |  |  |  |  |  |   |  |  |  |  |   |  |  | 5.17 |

### PLDs (PEELs)

| 18CV8           |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   | 6.3  |

|-----------------|----|---|---|---|---|----|----|---|---|----|----|---|---|---|----|---|---|---|----|---|---|---|---|---|---|---|---|---|---|------|

| 18CV8-15        |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   |      |

| 20CG10 .        |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   | 6.16 |

| 22CV10          |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   | 6.24 |

| 22CV10Z         |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   | • |   |   |   |   |   |   |   | 6.29 |

| <b>PEEL 153</b> |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   | 6.34 |

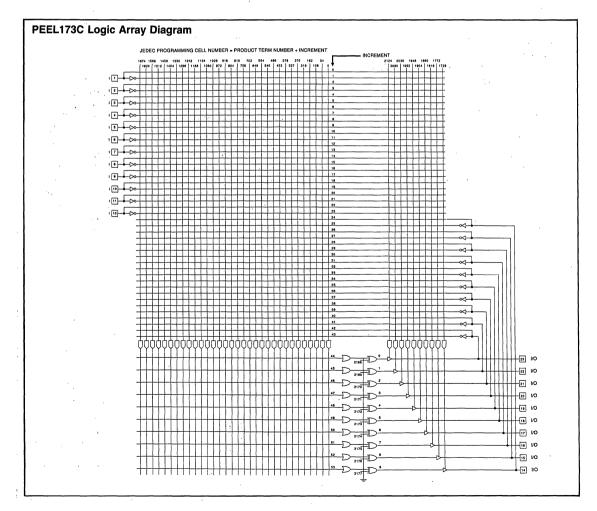

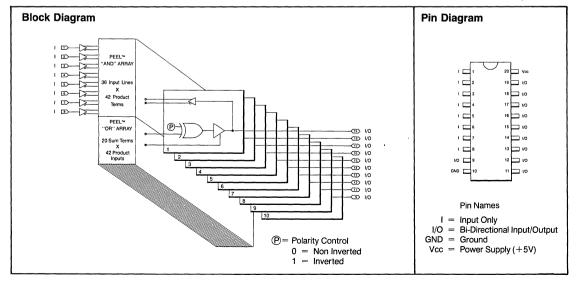

| PEEL 173        |    |   |   |   |   |    |    |   |   |    |    | • |   | • |    |   |   | • |    | • |   | • |   | • |   |   |   |   |   | 6.39 |

| PEEL 253        |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   | 6.44 |

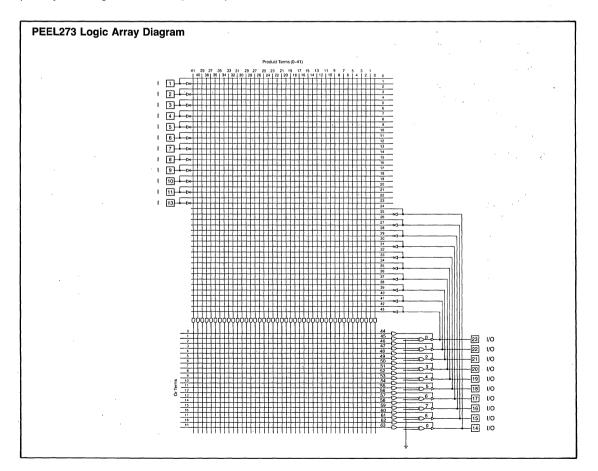

| PEEL 273        |    |   |   |   |   |    |    |   |   |    |    |   |   |   |    |   |   |   |    |   |   | - |   |   |   |   |   |   |   |      |

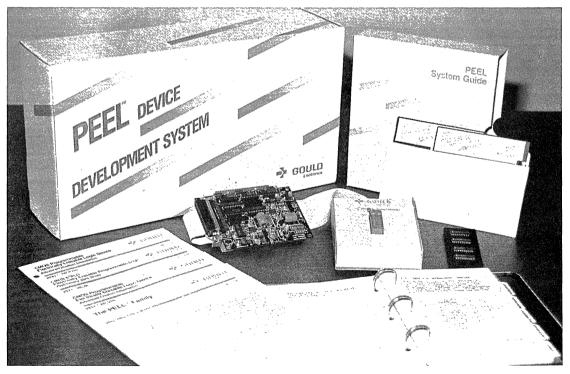

| PEEL Dev        | el | C | p | r | n | eı | nt | ŝ | 3 | ys | st | e | m | ۱ | (ł | כ | D | S | ;) |   | • | • | • | • | • | • | • | • | • | 6.54 |

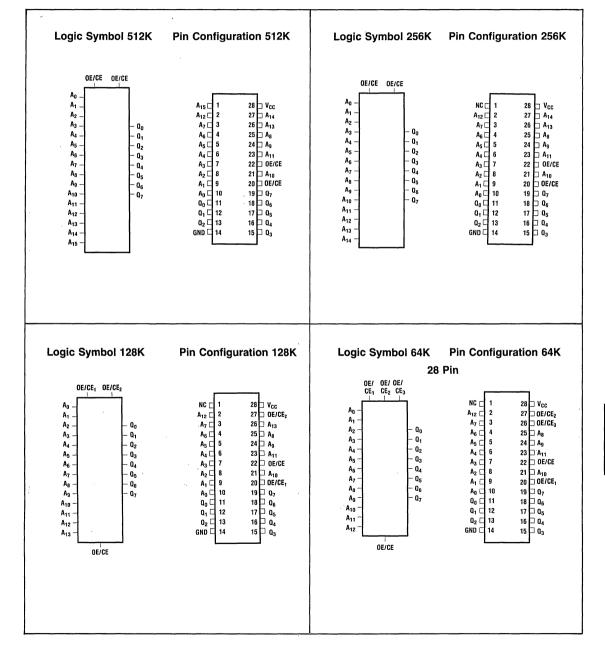

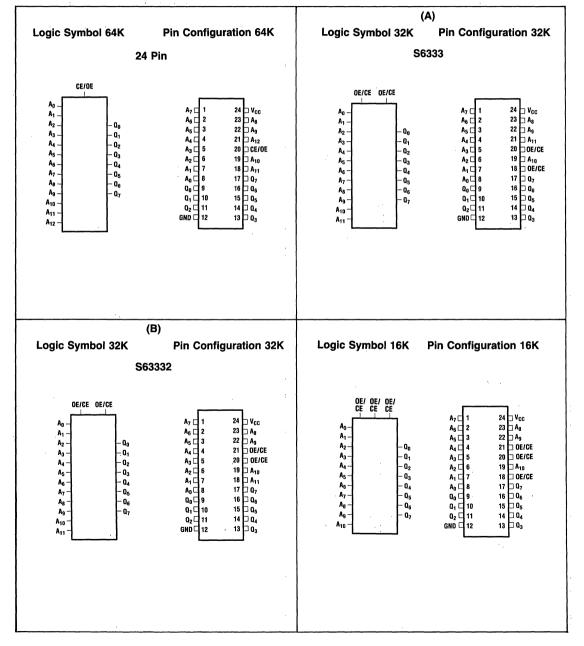

### Static CMOS & NMOS ROMs

| Static CMOS & NMOS ROMs Family of ROMs | 7.3  |

|----------------------------------------|------|

| S631000/1                              | 7.17 |

| Mask ROMs App Note                     | 7.24 |

### **General Information**

| Quality Program                | 8.3  |

|--------------------------------|------|

| Packaging                      |      |

| Ordering Information           |      |

| Sales Offices, Representatives |      |

| and Distributors               | 8.23 |

·

ASIC Roducts

Gould AMI was the first company to recognize the need for custom integrated circuits in the mid-1960's, and to pioneer the development of application-specific integrated circuits (ASICs). With more than twenty years' dedication to providing ASIC system solutions, Gould AMI has more experience than any other vendor of ASICs.

🗭 GOULD

AM Semiconductors

The company now offers a continuum of ASIC products, ranging from CMOS programmable logic devices to complex cell-based custom ICs. This spectrum of offerings provides customers with a full range of ASIC choices, so that the optimum solution for an application can be selected.

Gould AMI's ASIC technology allows system designers to tailor their systems and reduce the number of parts in their products by combining multiple memory and processing functions on a single device, instead of mixing and matching several standard parts. The result: smaller board sizes, lower final product cost and higher reliability. ASIC users also benefit by greater product differentiation due to custom tailoring and higher security ensured by an ASIC's resistance to duplication.

### CMOS EEPLDs

User-programmable digital devices ideal for small and medium-scale integration

Electrically erasable programmable logic devices are ideal for small and medium-scale integration system design in low-volume production. Our lowest development cost ASICs, these devices deliver plenty of performance and offer a surprising measure of versatility and customer-control.

Built using our unique PEL<sup>™</sup> (Programmable Electrically Erasable Logic) technology, these PLDs are userprogrammable, so there's no pre-production customer design and development risk. You may use PC-based or industry-standard PLD programmers to configure the macrocells and, if necessary, to repeatedly erase and reconfigure them.

The table below can help you select the right PLD for you. See the PLD section later in this catalog for detailed data sheets.

| Part No. | Architecture | Complexity                                                      | Speed    | Replaces                        |

|----------|--------------|-----------------------------------------------------------------|----------|---------------------------------|

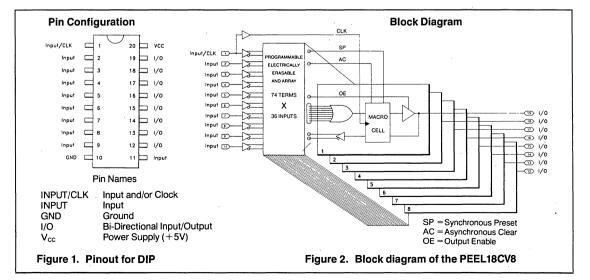

| 18CV8    | 20 pin E2PLD | 74 product terms x 36 input array                               | 25ns Tpd | Bipolar PLDs                    |

| 18CV8-15 | 20 pin E2PLD | 74 product terms x 36 input array                               | 15ns Tpd | Bipolar PLDs                    |

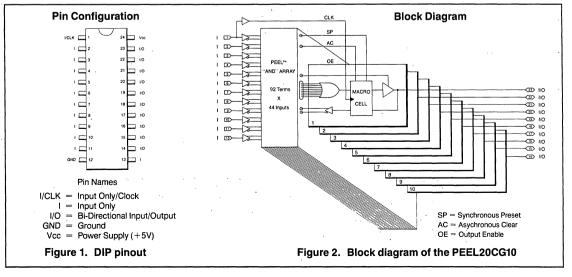

| 20CG10   | 24 pin E2PLD | 92 product terms x 44 input arrays                              | 25ns Tpd | 20V8, 20G10                     |

| 22CV10Z  | 24 pin E2PLD | 132 product terms x 44 inputs                                   | 25ns Tpd | Bipolar PLDs<br>Zero power mode |

| 22CV10   | 24 pin E2PLD | 132 product terms x 44 inputs                                   | 25ns Tpd | Bipolar PLDs                    |

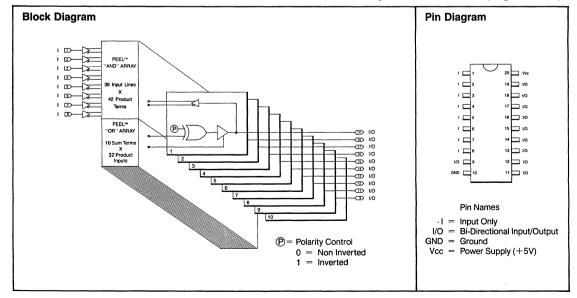

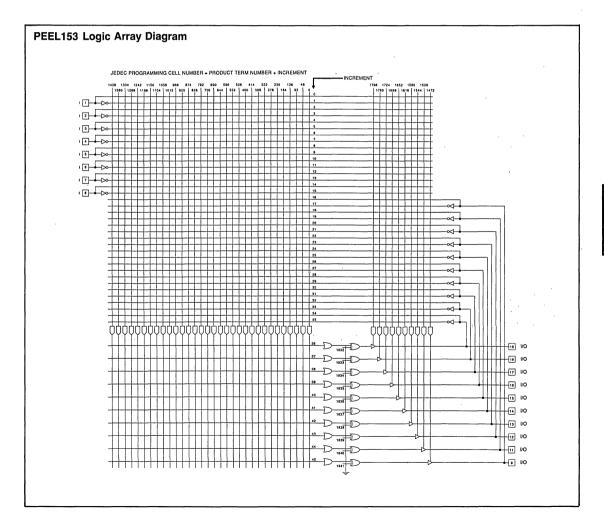

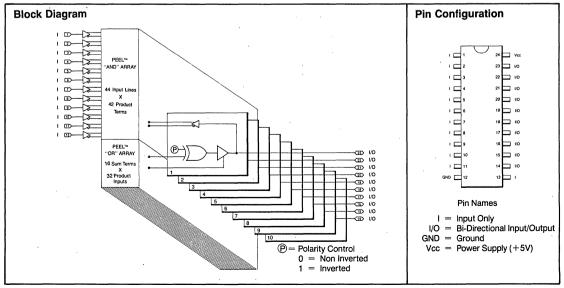

| PEEL 153 | 20 pin E2PLD | 42 product terms x 36 inputs<br>10 sum terms x 32 product terms | 30ns Tpd | Bipolar PLS153                  |

| PEEL 173 | 24 pin E2PLD | 42 product terms x 44 inputs<br>10 sum terms x 32 product terms | 30ns Tpd | Bipolar PLS173                  |

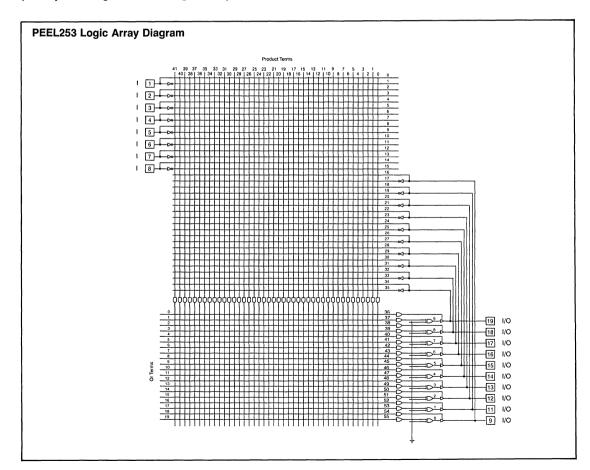

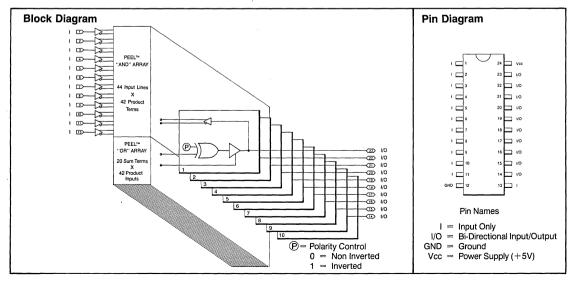

| PEEL 253 | 20 pin E2PLD | 42 product terms x 36 inputs<br>20 sum terms x 42 product terms | 30ns Tpd | Bipolar PLS 153<br>PEEL 153     |

| PEEL 273 | 24 pin E2PLD | 42 product terms x 44 inputs<br>20 sum terms x 42 product terms | 30ns Tpd | Bipolar PLS 173<br>PEEL 173     |

### Gould AMI's CMOS PLD Family

### **Gate Arrays**

Semi-finished digital chips provide high performance for medium volume production with quick development

- 1.25-micron and 2.0-micron Double Metal CMOS

Processes

- Basic Logic, Interface, MSI and 7400 Functions

- Custom RAMs and ROMs available in 1.25-micron gate arrays

- Artificial Intelligence Software Services Available for Netlist Translation and Gate Reduction

Gate arrays provide solutions for a variety of high performance digital applications--at a low development cost and quick design time. If you need fast turn production runs, gate arrays may be the right ASIC for you.

Gate arrays are semi-finished digital circuits that contain patterns of uncommitted transistors pre-fabricated on silicon base wafers. Using any major CAE workstation at your own facility, you can use Gould AMI libraries to customize your design as a network of logic functions. With only the metal layers to fabricate, gate array development time is fast--typically four weeks.

Gould AMI's gate arrays are fabricated in a double metal, single poly, twin tub CMOS process. They offer the CMOS advantages of low power dissipation, broad power supply voltage range (2.5 to 5.5 Volts), and high noise immunity.

Over 600 macros in the process families include:

| Basic functions:                      | Simple gates, clock drivers,<br>flip/flops, latches                  |

|---------------------------------------|----------------------------------------------------------------------|

| Interface functions:                  | TTL, CMOS Schmitt trigger, slew<br>rate buffers, TTL with hysteresis |

| MSI functions:                        | Counters, multiplexers, decoders, adders                             |

| 7400 functions:<br>Digital megacells: | Over 160 TTL compatible functions RAMs                               |

|         |                    |              | Programmable |            |                |            |

|---------|--------------------|--------------|--------------|------------|----------------|------------|

| Array   | <b>Total Gates</b> | Usable Gates | TAB          | Fine Pitch | Standard Pitch | Power Pins |

| GC 100K | 100000             | 54000        | 438          | 324        | 250            | 12         |

| GC 50K  | 51456              | 28300        | 312          | 236        | 184            | 12         |

| GC 40K  | 35640              | 19602        | 260          | 194        | 154            | 12         |

| GC 30K  | 31920              | 17556        | 246          | 184        | 142            | 12         |

| GC 25K  | 25728              | 14150        | 220          | 166        | 132            | 12         |

| GC 20K  | 19840              | 10912        | 196          | 146        | 116            | 12         |

| GC 15K  | 15000              | 8250         | 168          | 128        | 100            | 12         |

| GC 10K  | 10320              | 5676         | 136          | 100        | 84             | 12         |

| GC 7K   | 6912               | 3801         | 116          | 84         | 68             | 12         |

| GC 5K   | 5280               | 2904         | 98           | 72         | 56             | 12         |

| GC 3K   | 2520               | 1386         | 72           | 52         | 40             | 12         |

### 1.25-micron Gate Arrays

### 2.0-micron Gate Arrays

| Array Name | Equivalent Gates | Max. Usable Gates | Prog. Pins | Total Pins |

|------------|------------------|-------------------|------------|------------|

| GB1000D    | 1120             | 1008              | 60         | 68         |

| GB2000D    | 2128             | 1978              | . 76       | 84         |

| GB3000D    | 3264             | 3099              | 100        | 108        |

| GB4000D    | 4256             | 4086              | 112        | 120        |

| GB6000D    | 5880             | 5680              | 132        | 144        |

| GB8000D    | 7872             | 7637              | 168        | 184        |

| GB10000D   | 9776             | 9483              | 192        | 208        |

### Standard Cell Circuits

Analog and digital building blocks offer higher density and smaller size for medium to high volume needs

- 1.25 and 2-micron Double Metal CMOS Families

- 3-micron and 2-micron Double Poly, Double Metal CMOS Families

- · Cells Created by Expert-based Cell Generator

- Basic Logic, Interface, MSI, 7400 and Megacell Functions

- 2-micron Process includes Analog Functions

- Tailor-made RAMs, ROMs and PLAs Available

- Artificial Intelligence Software Services Available for Digital Netlist Translation and Gate Reduction

Chips designed with these cells, offered in analog and digital formats, surpass gate array density and approach that of cell-based custom designs at half the development cost and development time. They're cost effective for medium to high-volume production.

Standard cells are pre-designed circuit building blocks whose functional, timing and performance parameters exist in Gould AMI's libraries. As with a gate array, you design a standard cell circuit by choosing logic functions from a library installed on a CAE workstation. But while a gate array design specifies only the final metal layers of a pre-fabricated silicon base, all of a standard cell's base and metal layers are custom fabricated from precharacterized cells. This feature gives standard cells greater design flexibility, but requires an eight week development time.

A standard cell circuit also uses only the number of cells required for a design, whereas gate arrays seldom utilize all of the available cells. This means a smaller die size and lower cost to you for a given circuit function.

Gould AMI offers over 850 cells in its four standard cell families:

- 1.25-micron digital CMOS (CAB family)

- 2-micron digital CMOS (CBB family)

- 3-micron analog and digital CMOS (CCI family)

- 2-micron analog and digital CMOS (ABX family)

### **Digital Standard Cells**

Both the CAB and CBB families use a double metal, single poly, twin tub CMOS process. They are intended primarily for 5 Volt operation but will operate down to 2.5 Volts.

9 9

## **ASIC Products**

Cells in these libraries include:

| Basic functions:     | simple gates, clock drivers,<br>flip/flops. latches                |

|----------------------|--------------------------------------------------------------------|

| Interface functions: | TTL, CMOS, Schmitt trigger, slew rate buffers, TTL with hysteresis |

| MSI functions:       | counters, multiplexers, decoders, adders                           |

| 7400 functions:      | over 160 TTL compatible functions                                  |

| Digital megacells:   | barrel shifter, funnel shifter, RAM,<br>ROM and PLA                |

### Analog/Digital Standard Cells

The CCI family uses a 3-micron double metal, double poly, p-well CMOS process. It is intended primarily for analog and/or digital applications running at 10 Volts analog with 5 Volts digital operation.

Gould AMI's new ABX process is a 2-micron double poly, double metal process. This is Gould AMI's most flexible process, built on N or P-type starting material, with a range of 13 to 17 process layers. Ideal for mixed signal analog and digital applications, it can operate from 5 to 12 volts. Functions include electrically erasable ROMs, implant programmable ROMs and NPN and PNP bipolar transistors on board.

Cells in the CCI and ABX libraries include:

| Basic functions:                                                                                                 | simple gates, clock drivers,<br>flip/flops, latches                                                |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Interface functions:                                                                                             | TTL, CMOS, Schmitt trigger                                                                         |

| MSI functions:                                                                                                   | counters, multiplexers, decoders, adders                                                           |

| 7400 functions:                                                                                                  | over 160 TTL compatible functions                                                                  |

| Analog functions:                                                                                                | Op amps, A/D, D/A, comparators,<br>switches, voltage references,<br>input buffer and output buffer |

| and the second | 1                                                                                                  |

### **Cell-based Custom**

Most tailored ASIC solution--best for high performance, mixed signal or high volume needs

Cell-based custom chips use a combination of Gould's megacells, custom cells and standard cells to provide you with the ultimate in design tailoring and performance. This approach is ideal when you have a requirement for high speed, special interfaces, mixed analog/digital, or very high volume production runs.

Though their development costs and time are longer than with standard cells, cell-based custom circuits pack the most functions into the smallest area. Fewer custom chips need be used in a given design, thus saving board space. Custom devices also provide greater security because they are nearly impossible to copy.

Over twenty years' experience in custom design have given Gould AMI's design team the kind of engineering expertise that complex solutions demand. Particular areas of expertise are analog, mixed signal, high voltage and E2 applications. The following illustrate some examples of Gould AMI's answers to our customers' technical challenges.

### Case History #1

A consumer products manufacturer is developing an instrumentation device that measures pressure, room dimensions and weight. The technical challenge? To reduce the number of discrete logic parts and consolidate into one device, which requires analog and digital functions on a single ASIC.

Gould AMI's Solution: A cell-based custom chip which incorporates LCD drivers, a comparator, a/d converters, gain stages and voltage references on a single chip, thus making the measuring device perform more reliably and reducing the number of components required. This saves the customer money in component costs, as well as assembly and inventory costs.

and the second second

##

## **ASIC Products**

### Case History #2

Problem: An automotive company needs a drop-in replacement for a device that nearest fuel, oil and temperature and displays the results on a car dashboard. The technical challenge? This smart device needs to be fast and super-accurate, with numerous features on a single densely packed chip. The customer also requires fault coverage to be 99%.

Gould AMI's solution: To integrate analog and digital blocks on a single custom chip. The analog portion of the circuit allows sampling of a greater number of bits, thus resulting in a faster, more accurate display. The integrated solution enables Gould AMI to meet the size, power, speed and accuracy requirements so that the device will drop right in to the customer's board.

### Silicon Foundry Capabilities

Flexible and experienced foundry services for existing customer designs

Gould AMI 's foundry service is the solution for customers who have circuits ready for fabrication and need a primary or secondary manufacturing source. Fifteen years' experience in providing foundry services means well-documented process specifications and a flexible factory, with the ability to accomodate process variations for an existing customer design.

### Foundry Steps

Gould AMI performs a thorough engineering review of your database tape to assure accurate input. After receiving your Calma II database tape, we generate both single level plots and a final layout tape and submit them for your approval. This verifies the design data transfer to the tooling tape--before you commit the design to silicon. You'll then receive either untested protoypes or mapped wafers that met our visual and parametric process specifications. You'll inspect the sample to verify circuit functionality and performance. With your approval, we produce and assemble additional units that are tested rigorously with your test program (or one we generate from your specs). Gould AMI uses a variety of industrystandard and specialty testers, including Sentry, Gen-Rad, Teradyne, and LTX.

### Gould AMI Process Technology Comparison

| Process<br>Family | Geometry | Maximum<br>Voltage | Characteristics |

|-------------------|----------|--------------------|-----------------|

| CMOS              | 1.25 μ   | 5.5 Volts          | Digital         |

| CMOS              | 2.0 μ    | 5.0 to 12.0 Volts  | Mixed Signal    |

| CMOS              | 2.0 μ    | 5.5 Volts          | Digital         |

| смоѕ              | 3.0 μ    | 5.0 to 10.0 Volts  | Analog          |

| CMOS              | 3.0 μ    | 5.5 Volts          | Digital         |

| CMOS              | 2.0 μ    | 5.5 Volts          | EE Digital      |

| CMOS              | 5.0 μ    | 5.5 Volts          | Digital         |

| CMOS              | 5.0 μ    | 5.5 Volts          | Analog          |

| CMOS              | 7.0 μ    | 5.5 Volts          | Digital         |

| CMOS              | 7.0 μ    | 5.5 Volts          | Analog          |

| NMOS              | 3.0 μ    | 5.5 Volts          | Digital         |

| NMOS              | 4.0 μ    | 5.5 Volts          | Digital         |

| NMOS              | 5.0 μ    | 5.5 Volts          | Digital         |

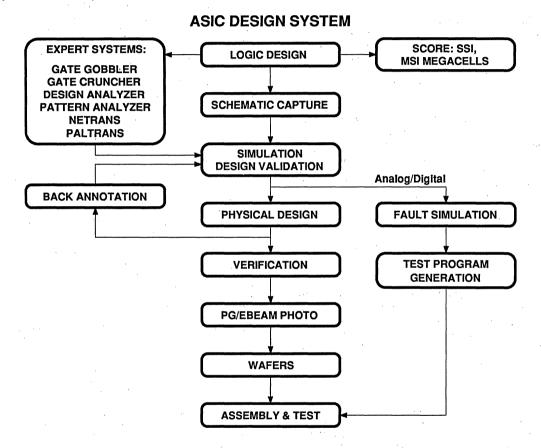

### **Typical ASIC Development Flow**

### **ASIC Software Services**

Optional design services give you the power of choice and ease your designs

Unlike many ASIC vendors that accept only completed designs or finished netlists, Gould AMI is able to pick up an ASIC design at any stage, whether customers submit a partially finished design, a foundry-ready database tape, or a simple set of specifications. In order to ease

logic design for its customers, Gould AMI has installed its analog and digital cell libraries on popular engineering workstations including Mentor Graphics, Daisy Systems, Intergraph, VALID Logic Systems, FutureNet and Viewlogic.

Gould AMI uses several advanced expert systems inhouse, each of which taps the combined experience of Gould AMI's engineers to accelerate device layout and design optimization.

### ASIC Netlist Translation Services:

If a client has already designed a digital chip using another vendor's or their own proprietary tools. Gould AMI's NETRANS<sup>™</sup> expert system will "translate" the netlist into Gould AMI-compatible form in just a few hours. This automated design transfer works independently of workstation libraries or processes, and can save customers thousands of dollars and weeks of precious time. For turning programmable logic device into gate arrays or standard cells. PALTRANS<sup>™</sup> is the answer. PALTRANS converts standard programmable array logic (PAL), programmable electrically erasable logic (PEEL) and field programmable gate arrays (FPGAs) into netlists used to design gate array or standard cell ASICs. You can use an off-the-shelf PLD as a prototype for programming, debugging, and beta-testing logic designs, instead of first requiring the production of an ASIC. Engineers then use PALTRANS to convert the data into a netlist. In about eight hours, mask production can begin and an ASIC design is produced in two to three weeks.

### **Tools Speed Layout and Optimization**

The SCORE<sup>™</sup> cell compiler generates and tailors cells to a client's specific requirements in one-tenth the time required for hand-built cells.

Gate Gobbler, Gate Cruncher, Design Analyzer and Pattern Analyzer are artificial intelligence (AI) tools that assist with the conversion of conventional standard devices to CMOS ASICs.

By the end of 1989, Gould AMI will offer an Automatic Test Generation tool that will generate test vectors in a matter of hours, relieving designers of the task and saving at least six weeks for manual test generation This tool will automatically partition a circuit into a set of combinatorial functions and insert a scan path. Each function, seen as a distinct circuit, can be quickly and easily tested with an automatic test program generator employing the D-Algorithm.

Transitioning from standard TTL parts to ASICs can be fraught with difficulty, and when ASIC prototypes don't work, design re-work through traditional analysis and optimization techniques can take weeks or months. Gould AMI's AI tools minimize the delays caused by having to re-work a design through traditional analysis and optimization techniques. The tools incorporate a continually expanding knowledge base, applying Gould AMI's hundreds of engineering man-years to every job.

## **Communication Products**

.

.

.

.

## **DTMF Tone Generator**

## S2559E/F

### Features

- □ Wide Operating Supply Voltage Range: 2.5 to 10 Volts

- Low Power CMOS Circuitry Allows Device Power to be Derived Directly from the Telephone Lines or from Small Batteries, e.g., 9V

- Uses TV Crystal Standard (3.58MHz) to Derive all Frequencies thus Providing Very High Accuracy and Stability

- □ Mute Drivers On-Chip

- □ Interfaces Directly to a Standard Telephone Push-Button or Calculator Type X-Y Keyboard

- □ The Total Harmonic Distortion is Below Industry Specification

- Oscillator Resistor On Chip

- On-Chip Generation of a Reference Voltage to Assure Amplitude Stability of the Dual Tones Over the Operating Voltage and Temperature Range

- □ Single Tone as Well as Dual Tone Capability

- Two Options Available: E: Mode Select F: Chip Disable

### **General Description**

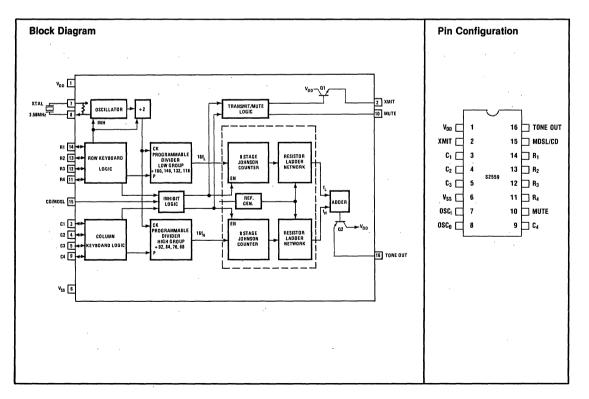

The S2559 DTMF Generator is specifically designed to implement a dual tone telephone dialing system. The device can interface directly to a standard pushbutton

COMMUNI CATION PRODUCT

### **General Description (Continued)**

telephone keyboard or calculator type X-Y keyboard and operates directly from the telephone lines. All necessary dual-tone frequencies are derived from the widely used TV crystal standard providing very high accuracy and stability. The required sinudsoidal waveform for the individual tones is digitally synthesized on the chip. The waveform so generated has very low total harmonic distortion. A voltage reference is generated on the chip which is stable over the operating voltage and temperature range and regulates the signal levels of the dual tones to meet the recommended telephone industry specifications. These features permit the S2559 to be incorporated with a slight modification of the standard 500 type telephone basic circuitry to form a pushbutton dual-tone telephone. Other applications of the device include radio and mobile telephones, remote control, Point-of-Sale, and Credit Card Verification Terminals and process control.

### Absolute Maximum Ratings

| DC Supply Voltage (V <sub>DD</sub> – V <sub>SS</sub> ) |                                                              |

|--------------------------------------------------------|--------------------------------------------------------------|

| Operating Temperature                                  |                                                              |

|                                                        |                                                              |

| Storage Temperature<br>Power Dissipation at 25°C       |                                                              |

| Input                                                  | V <sub>SS</sub> – 0.3≤V <sub>IN</sub> ≤V <sub>DD</sub> + 0.3 |

|                                                        |                                                              |

### S2559E/F Electrical Characteristics:

(Specifications apply over the operating temperature range of  $0^{\circ}$ C to  $+70^{\circ}$ C unless otherwise noted. Absolute values of measured parameters are specified.)

| Symbol           | Parameter/Condition                                                   | S                  |                   | (V <sub>DD</sub> -V <sub>SS</sub> )<br>Voits | Min. | Тур.  | Max.     | Units |

|------------------|-----------------------------------------------------------------------|--------------------|-------------------|----------------------------------------------|------|-------|----------|-------|

|                  | Supply Voltage                                                        |                    |                   | ······································       |      |       | · · · ·  | 1     |

|                  | Tone Out Mode (Va                                                     | lid Key Depressed) |                   | ·                                            | 2.5  | · · · | 10.0     | v     |

| V <sub>DD</sub>  | Non Tone Out Mode (No Key Depressed)                                  |                    | )                 | · · ·                                        | 1.6  |       | 10.0     | V     |

|                  | Supply Current                                                        |                    |                   |                                              |      |       |          |       |

|                  | Standby (No Key Selected, Tone, XMIT                                  |                    |                   | 3.0                                          | 1.1  | 0.3   | 30       | μA    |

|                  | and MUTE Outputs Unloaded)                                            |                    |                   | 10.0                                         |      | 1.0   | 100      | μA    |

| IDD              | Operating (One Key Selected, Tone, XMIT<br>and MUTE Outputs Unloaded) |                    | 3.0<br>10.0       |                                              | 1.0  | 2.0   | mA<br>mA |       |

|                  | Tone Output                                                           |                    |                   | ,                                            | · ·  |       | ;        | · ·   |

|                  | Single Tone                                                           | Row Tone,          | $R_L = 390\Omega$ | 3.5                                          | 335  | 465   | 565      | mVrms |

| S2559E/F         | Mode Output                                                           |                    |                   | 5.0                                          | 380  | 540   | 710      | mVrms |

| V <sub>OR</sub>  | Voltage                                                               | Row Tone,          | $R_L = 240\Omega$ | 10.0                                         | 380  | 550   | 735      | mVrms |

| dB <sub>CR</sub> | Ratio of Column to Row Tone (Dual Tone Mode)2559E/F                   |                    | e Mode)2559E/F    | 3.5-10.0                                     | 1.0  | 2.0   | 3.0      | dB    |

| %DIS             | Distortion*                                                           | 2559E/F            | :                 | 3.5 - 10.0                                   |      |       | 7        | %     |

### S2559E/F Electrical Characteristics: (continued)

| Symbol          | Parameter/Conditions                                     |                          | (V <sub>DD</sub> -V <sub>SS</sub> )<br>Volts | Min. | Тур. | Max. | Units |

|-----------------|----------------------------------------------------------|--------------------------|----------------------------------------------|------|------|------|-------|

|                 | XMIT, MUTE Outputs                                       |                          |                                              |      |      |      |       |

|                 | XMIT, Output Voltage, High                               | (I <sub>OH</sub> = 15mA) | 3.0                                          | 1.5  | 1.8  |      | V     |

| ∙он             | (No Key Depressed)(Pin 2)                                |                          | 10.0                                         | 8.5  | 8.8  |      | v     |

| lof             | XMIT, Output Source Leakage Current, V <sub>OF</sub> =0V |                          | 10.0                                         |      |      | 100  | μA    |

| N               | MUTE (Pin 10) Output Voltage, Low,                       |                          | 2.75                                         |      | 0    | 0.5  | V     |

| V <sub>OL</sub> | (No Key Depressed), No Load                              |                          | 10.0                                         |      | 0    | 0.5  | V     |

| M               | MUTE, Output Voltage, High,                              |                          | 2.75                                         | 2.5  | 2.75 |      | V     |

| V <sub>OH</sub> | (One Key Depressed) No Load                              |                          | 10.0                                         | 9.5  | 10.0 |      | V     |

| loL             | MUTE, Output Sink                                        | V <sub>01</sub> = 0.5V   | 3.0                                          | 0.53 | 1.3  |      | mA    |

| 'UL             | Current                                                  | ·0L 0.0V                 | 10.0                                         | 2.0  | 5.3  |      | mA    |

| ЮН              | MUTE, Output Source                                      | V <sub>OH</sub> = 2.5V   | 3.0                                          | 0.17 | 0.41 |      | mA    |

| UH              | Current V <sub>OH</sub> = 9.5V                           |                          | 10.0                                         | 0.57 | 1.5  |      | mA    |

\*Distortion is defined as "the ratio of the total power of all extraneous frequencies, in the VOICE band above 500Hz, to the total power of the DTMF frequency pair".

### Table 1. Comparisons of Specified vs Actual Tone Frequencies Generated by S2559

|                 | OUTPUT FRE |         |                     |

|-----------------|------------|---------|---------------------|

| ACTIVE<br>INPUT | SPECIFIED  | ACTUAL  | % ERROR<br>See Note |

| • R1            | 697        | 699.1   | + 0.30              |

| R2              | ·* 770     | 766.2   | - 0.49              |

| R3              | - 852      | 847.4   | - 0.54              |

| · R4 · · · ·    | 941        | 948.0   | + 0.74              |

| C1              | 1,209      | 1,215.9 | + 0.57              |

| C2              | 1,336      | 1,331.7 | -0.32               |

| · C3            | 1,477      | 1,417.9 | - 0.35              |

| C4              | 1,633      | 1,645.0 | +0.73               |

Table 2. XMIT and MUTE Output Functional Relationship

| OUTPUT<br>Released | 'Digit' key<br>Depressed | 'Digit' key       | COMMENT                                                   |

|--------------------|--------------------------|-------------------|-----------------------------------------------------------|

| XMIT               | V <sub>DD</sub>          | High<br>Impedance | Can source at least<br>50mA at 10V with<br>1.5V max. drop |

| MUTE               | V <sub>SS</sub>          | V <sub>DD</sub>   | Can source or sink current                                |

NOTE: % Error does not include oscillator drift.

3.5

### **Circuit Description**

The S2559 is designed so that it can be interfaced easily to the dual tone signaling telephone system and that it will more than adequately meet the recommended telephone industry specifications regarding the dual tone signaling scheme.

### **Design Objectives**

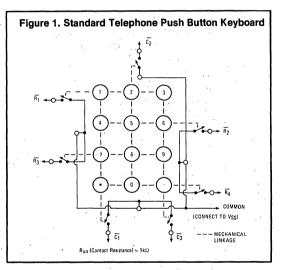

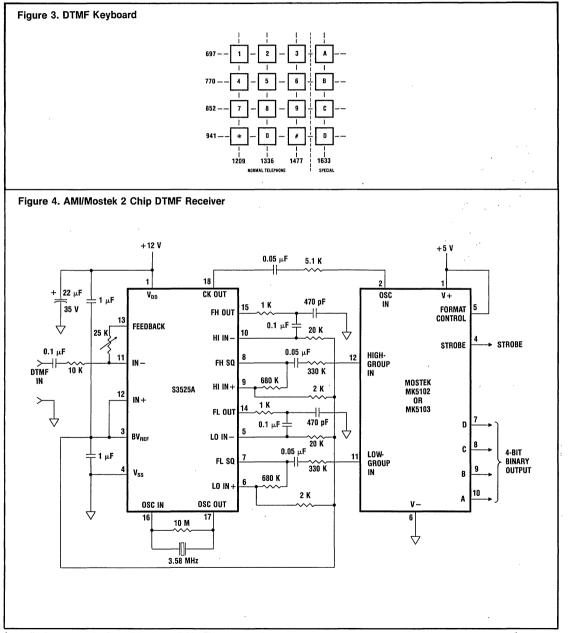

The specifications that are important to the design of the DTMF Generator are summarized below: the dual tone signal consists of linear addition of two voice frequency signals. One of the two signals is selected from a group of frequencies called the "Low Group" and the other is selected from a group of frequencies called the "High Group". The low group consists of four frequencies 697, 770, 852 and 941 Hz. The high group consists of four frequencies 1209, 1336, 1477 and 1633 Hz, A keyboard arranged in a row, column format (4 rows x 3 or 4 columns) is used for number entry. When a push button corresponding to a digit (0 thru 9) is pushed, one appropriate row (R1 thru R4) and one appropriate column (C1 thru C4) is selected. The active row input selects one of the low group frequencies and the active column input selects one of the high group frequencies. In standard dual tone telephone systems, the highest high group frequency of 1633Hz (Col. 4) is not used. The frequency tolerance must be  $\pm 1.0\%$ . However, the S2559 provides a better than .75% accuracy. The total harmonic and intermodulation distortion of the dual tone must be less than 10% as seen at the telephone terminals. (Ref. 1.) The high group to low group signal amplitude ratio should be 2.0  $\pm$  2dB and the absolute amplitude of the low group and high group tones must be within the allowed range. (Ref. 1.) These requirements apply when the telephone is used over a short loop or long loop and over the operating temperature range. The design of the S2559 takes into account these considerations.

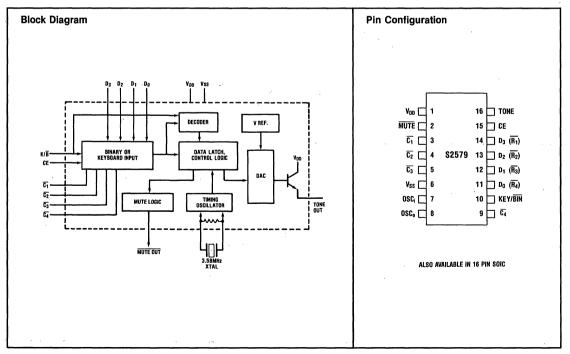

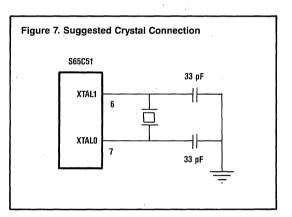

### Oscillator

The device contains an oscillator circuit with the necessary parasitic capacitances and feedback resistor on chip so that it is only necessary to connect a standard 3.58MHz TV crystal across the  $OSC_1$  and  $OSC_0$  terminals to implement the oscillator function. The oscillator functions whenever a row input is activated. The reference frequency is divided by 2 and then drives two sets of programmable dividers, the high group and the low group.

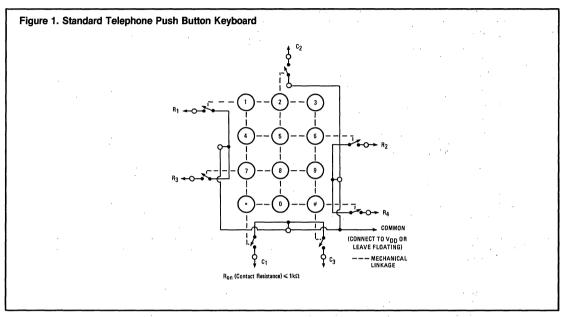

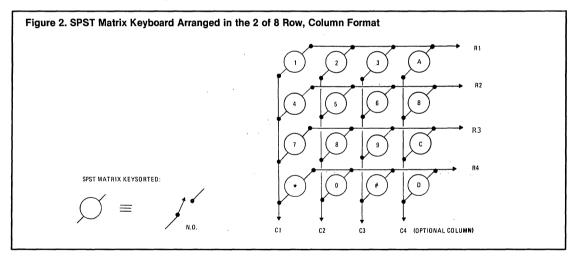

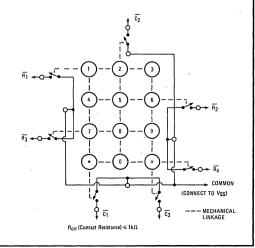

### **Keyboard Interface**

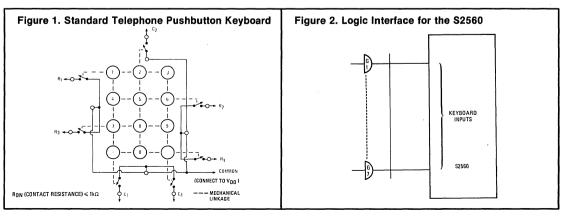

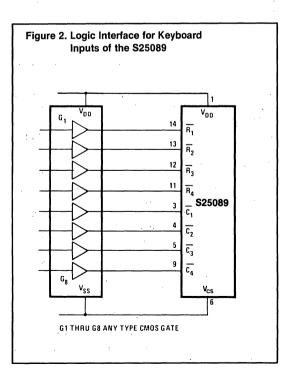

The S2559 employs a calculator type scanning circuitry to determine key closures. When no key is depressed, active pull-down resistors are "on" on the row inputs and active pull-up resistors are "on" on the column inputs. When a key is pushed a high level is seen on one of the row inputs, the oscillator starts and the keyboard scan logic turns on. The active pull-up or pull-down resistors are selectively switched on and off as the keyboard scan logic determines the row and the column inputs that are selected. The advantage of the scanning technique is that a keyboard arrangement of SPST switches are shown in Figure 2 without the need for a common line, can be used. Conventional telephone push button keyboards as shown in Figure 1 or X-Y keyboards with common can also be used. The common line of these keyboards can be left unconnected or wired "high".

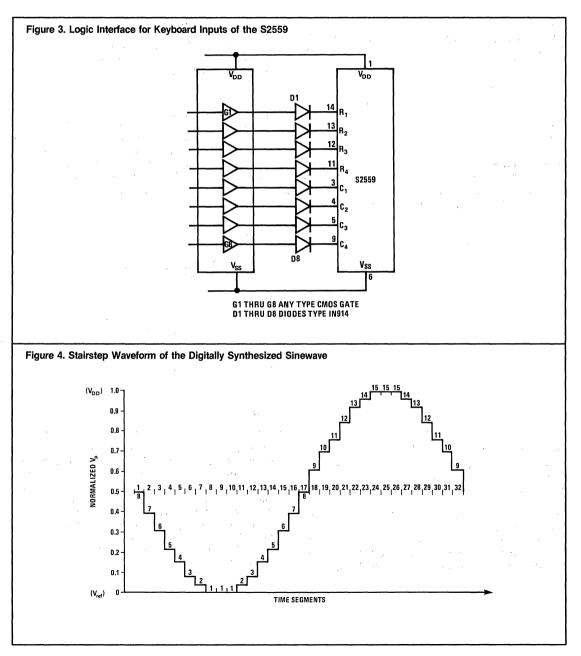

### Logic Interface

The S2559 can also interface with CMOS logic outputs directly. The S2559 requires active "High" logic levels. Since the active pull-up resistors present in the S2559 are fairly low value ( $500\Omega$  typ), diodes can be used as shown in Figure 3 to eliminate excessive sink current flowing into the logic outputs in their "Low" state.

### **Tone Generation**

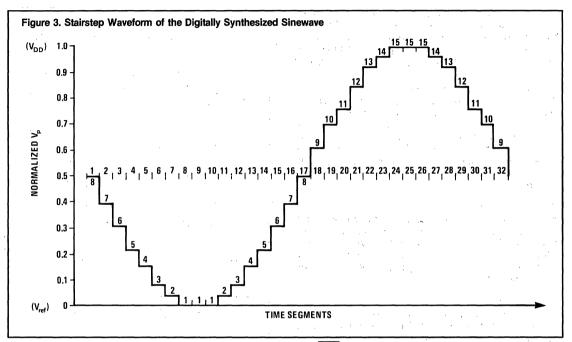

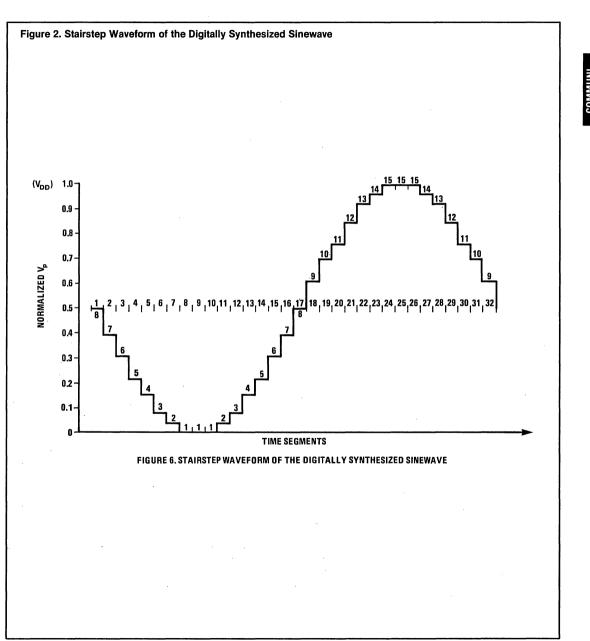

When a valid key closure is detected, the keyboard logic programs the high and low group dividers with appropriate divider ratios so that the output of these dividers cycle at 16 times the desired high group and low group frequencies. The outputs of the programmable dividers drive two 8-stage Johnson counters. The symmetry of the clock input to the two divide by 16 Johnson counters allows 32 equal time segments to be generated within each output cycle. The 32 segments

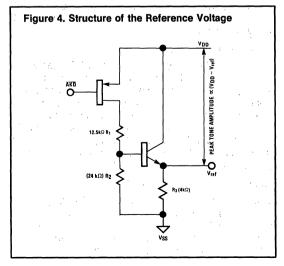

are used to digitally synthesize a stair-step waveform to approximate the sinewave function (see Figure 3). This is done by connecting a weighted resistor ladder network between the outputs of the Johnson counter,  $V_{DD}$  and  $V_{REF}$ .  $V_{REF}$  closely tracks  $V_{DD}$  over the operating voltage and temperature range and therefore the peak-to-peak amplitude  $V_{P}$  ( $V_{DD}-V_{REF}$ ) of the stairstep function is fairly constant.  $V_{REF}$  is so chosen that  $V_{P}$  falls within the allowed range of the high group and low group tones.

The individual tones generated by the sinewave synthesizer are then linearly added and drive a bipolar NPN transistor connected as emitter follower to allow proper impedance transformation, at the same time preserving signal level.

### **Dual Tone Mode**

When one row and one column is selected dual tone output consisting of an appropriate low group and high group tone is generated. If two digit keys, that are not either in the same row or in the same column, are depressed, the dual tone mode is disabled and no output is provided.

### Single Tone Mode

Single tones either in the low group or the high group can be generated as follows. A low group tone can be generated by activating the appropriate row input or by depressing two digit keys in the appropriate row. A high group tone can be generated by depressing two digit keys in the appropriate column, i.e., selecting the appropriate column input and two row inputs in that column.

### **Mode Select**

The S2559E has a Mode Select (MDSL) input (Pin 15). When MDSL is left floating (unconnected) or connected to  $V_{DD}$ , both the dual tone and single tone modes are available. If MDSL is connected to  $V_{SS}$ , the single tone mode is disabled and no output tone is produced if an attempt for single tone is made. The S2559F does not have the Mode Select option.

### **Chip Disable**

The S2559F has a Chip Disable input at Pin 15 instead of the Mode Select input. The chip disable for the S2559F is active "high." When the chip disable is active, the tone output goes to  $V_{SS}$ , the row, column inputs go into a high impedance state, the oscillator is inhibited and the MUTE and XMIT outputs go into active

| Quartz Crystal Specification (25° C ± 2°C) |

|--------------------------------------------|

| Operating Temperature Range: 0°C to +70°C  |

| Frequency                                  |

| Frequency Calibration Tolerance            |

| Load Capacitance                           |

| Effective Series Resistance                |

| Drive Level-Correlation/Operating 2mW      |

| Shunt Capacitance                          |

| Oscillation Mode Fundamental               |

states. The effect is the device essentially disconnects from the keyboard. This allows one keyboard to be shared among several devices. The CD pin has an internal pull-down.

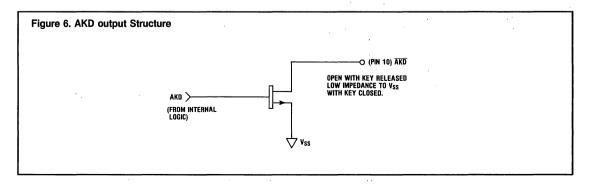

### MUTE, XMIT Outputs

The S2559E, F have a CMOS buffer for the MUTE output and a bipolar NPN transistor for the XMIT output. With no keys depressed, the MUTE output is "low" and the XMIT output is in the active state so that substantial current can be sourced to a load. When a key is depressed, the MUTE output goes high, while the XMIT output goes into a high impedance state. When Chip Disable is "high" the MUTE output is forced "low" and the XMIT output is in active state regardless of the state of the keyboard inputs.

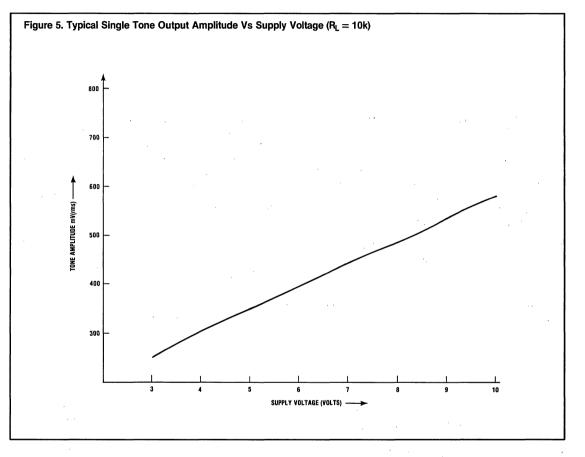

### **Amplitude/Distortion Measurements**

Amplitude and distortion are two important parameters in all applications of the Digital Tone Generator. Amplitude depends upon the operating supply voltage as well as the load resistance connected on the Tone Output pin. The on-chip reference circuit is fully operational when the supply voltage equals or exceeds 5 volts and as a consequence the tone amplitude is regulated in the supply voltage range above 5 volts. The load resistor value also controls the amplitude. If RL is low the reflected impedance into the base of the output transistor is low and the tone output amplitude is lower. For R<sub>I</sub> greater than 5kΩ the reflected impedance is sufficiently large and highest amplitude is produced. Individual tone amplitudes can be measured by applying the dual tone signal to a wave analyzer (H-P type 3581A) and amplitudes at the selected frequencies can be noted. This measurement also permits verification of the preemphasis between the individual frequency tones.

Distortion is defined as "the ratio of the total power of all extraneous frequencies in the voiceband above 500Hz accompanying the signal to the power of the frequency pair." This ratio must be less than 10% or when expressed in dB must be lower than -20dB.

(Ref. 1.) Voiceband is conventionally the frequency band of 300Hz to 3400Hz. Mathematically distortion can be expressed as:

Dist. =

$$\frac{\sqrt{(V_1)^2 + (V_2)^2 + ... + (V_N)^2}}{\sqrt{(V_L)^2 + (V_H)^2}}$$

where  $\left(V_{1}\right)$  . .  $\left(V_{N}\right)$  are extraneous frequency (i.e., intermodulation and harmonic) components in the 500Hz to

3400Hz band and  $V_L$  and  $V_H$  are the individual frequency components of the DTMF signal. The expression can be expressed in dB as:

DIST<sub>dB</sub> = 20 log

$$\sqrt{\frac{(V_1)^2 + (V_2)^2 + ... (V_N)^2}{\sqrt{(V_1)^2 + (V_H)^2}}}$$

$$= 10 \{ \log[(V_1)^2 + ... (V_N)^2] - \log[(V_L)^2 + (V_L)^2 + (V_H)^2] \} ... (1)$$

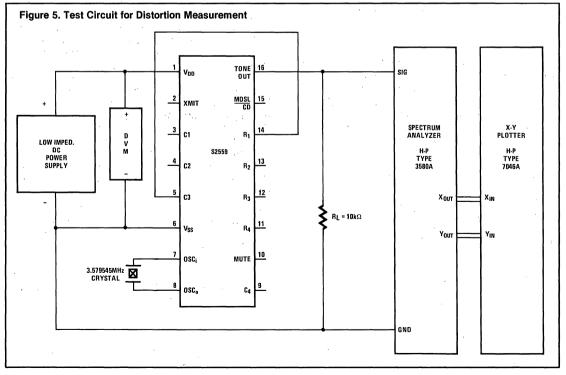

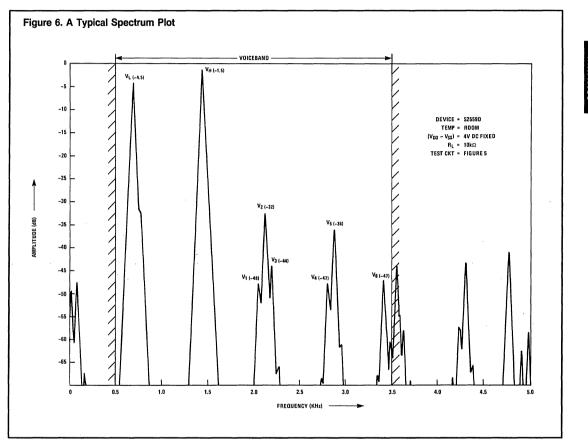

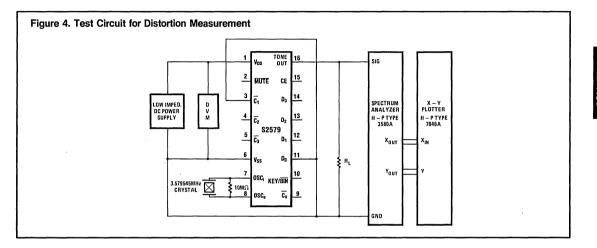

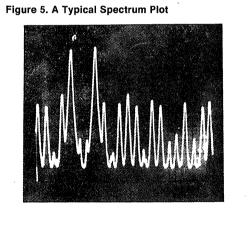

An accurate way of measuring distortion is to plot a spectrum of the signal by using a spectrum analyzer (H-P type 3580A) and an X-Y plotter (H-P type 7046A). Individual extraneous and signal frequency components are then noted and distortion is calculated by using the expression (1) above. Figure 6 shows a spectrum plot of a typical signal obtained from a S2559 device operating from a fixed supply of 4Vdc and  $R_L = 10k\Omega$  in the test circuit of Figure 5. Mathematical analysis of the spectrum shows distortion to be - 30dB (3.2%). For quick estimate of distortion, a rule of thumb as outlined below can be used. "As a first approximation distortion in dB equals the difference between the amplitude (dB) of the extraneous component that has the highest amplitude and the amplitude (dB) of the low frequency signal." This rule of thumb would give an estimate of -28dB as distortion for the spectrum plot of Figure 6 which is close to the computed result of -30dB.

In a telephone application amplitude and distortion are affected by several factors that are interdependent. For detailed discussion of the telephone application and other applications of the 2559 Tone Generator, refer to the applications note "Applications of Digital Tone Generator."

**Ref. 1: Bell System Communications Technical Reference, PUB 47001,** "Electrical Characteristics of Bell System Network Facilities at the Interface with Voiceband Ancillary and Data Equipment," August 1976.

An application note is also available describing the design considerations, test methods, and results obtained using the S2559 Tone Generator family in DTMF pushbutton telephones. Interface with type 500 and 2500 networks are discussed. Use in ancillary equipment is also covered. Please contact factory.

3.11

ommunication roducts

## **Pulse Dialer**

e de la companya de la compa

## S2560A

#### Features

- □ Low Voltage CMOS Process for Direct Operation from Telephone Lines

- □ Inexpensive R-C Oscillator Design Provides Better than ± 5% Accuracy Over Temperature and Unit to Unit Variations

- □ Dialing Rate Can be Varied by Changing the Dial Rate Oscillator Frequency

- Dial Rate Select Input Allows Changing of the Dialing Rate by a 2:1 Factor Without Changing Oscillator Components

- □ Two Selections of Mark/Space Ratios (331/3/662/3 or 40/60)

- □ Twenty Digit Memory for Input Buffering and for Redial with Access Pause Capability

- □ Mute and Dial Pulse Drivers on Chip

Accepts DPCT Keypad with Common Arranged in a 2 of 7 Format; Also Capable of Interface to SPST Switch Matrix

#### **General Description**

The S2560A Pulse Dialer is a CMOS integrated circuit that converts pushbutton inputs to a series of pulses suitable for telephone dialing. It is intended as a replacement for the mechanical telephone dial and can operate directly from the telephone lines with minimum interface. Storage is provided for 20 digits, therefore, the last dialed number is available for redial until a new number is entered. IDP is scaled to the dialing rate such as to produce smaller IDP at higher dialing rates. Additionally, the IDP can be changed by a 2:1 factor at a given dialing rate by means of the IDP select input.

## S2560A

### **Absolute Maximum Ratings:**

| Supply Voltage                      |  |

|-------------------------------------|--|

| Operating Temperature Range         |  |

| Storage Temperature Range           |  |

| Voltage at any Pin                  |  |

| Lead Temperature (Soldering, 10sec) |  |

### **Electrical Characteristics:**

Specifications apply over the operating temperature and 1.5V <V\_DD - V<sub>SS</sub> <3.5V unless otherwise specified.

| Symbol           | Parameter                            | V <sub>DD</sub> -V <sub>SS</sub><br>(Volts) | Min.                                          | Max.                                          | Units    | Conditions                                                                                                                                                                                        |

|------------------|--------------------------------------|---------------------------------------------|-----------------------------------------------|-----------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Output Current Levels                |                                             |                                               |                                               |          |                                                                                                                                                                                                   |

| IOLDP            | DP Output Low<br>Current (Sink)      | 3.5                                         | 125                                           |                                               | μΑ       | $V_{OUT} = 0.4V$                                                                                                                                                                                  |

| IOHDP            | DP Output High<br>Current (Source)   | 1.5<br>3.5                                  | 20<br>125                                     |                                               | μΑ<br>μΑ | $V_{OUT} = 1V$<br>$V_{OUT} = 2.5V$                                                                                                                                                                |

| IOLM             | MUTE Output Low<br>Current (Sink)    | 3.5                                         | 125                                           |                                               | μΑ       | $V_{OUT} = 0.4V$                                                                                                                                                                                  |

| I <sub>ОНМ</sub> | MUTE Output High<br>Current (Source) | 1.5<br>3.5                                  | 20<br>125                                     |                                               | μΑ<br>μΑ | $V_{OUT} = 1V$<br>$V_{OUT} = 2.5V$                                                                                                                                                                |

| IOLT             | Tone Output Low<br>Current (Sink)    | 1.5                                         | 20                                            |                                               | μΑ       | $V_{OUT} = 0.4V$                                                                                                                                                                                  |

| Iонт             | Tone Output High<br>Current (Source) | 1.5                                         | 20                                            |                                               | μΑ       | V <sub>OUT</sub> = 1V                                                                                                                                                                             |

| V <sub>DR</sub>  | Data Retention Voltage               |                                             | 1.0                                           |                                               | V        | "On Hook" $\overline{\text{HS}} = V_{\text{DD}}$ . Keyboard open, all                                                                                                                             |

| IDD              | Quiescent Current                    | 1.0                                         |                                               | 750                                           | nA       | other input pins to $V_{DD}$ or $V_{SS}$                                                                                                                                                          |

| I <sub>DD</sub>  | Operating Current                    | 1.5<br>3.5                                  |                                               | 100<br>500                                    | μΑ<br>μΑ | $\overline{\text{DP}}$ , $\overline{\text{MUTE}}$ open, $\overline{\text{HS}}$ = V <sub>SS</sub> (''Off Hook'')<br>Keyboard processing and dial pulsing at 10<br>pps at conditions as above       |

| fo               | Oscillator Frequency                 | 1.5                                         |                                               | 10                                            | kHz      |                                                                                                                                                                                                   |

| ∆fo/fo           | Frequency Deviation                  | 1.5 to 2.5<br>2.5 to 3.5                    | -3<br>-3                                      | +3<br>+3                                      | %        | Fixed R-C oscillator components<br>$50K\Omega \leq R_D \leq 750K\Omega$ ; $100pF \leq C_D^* \leq 1000pF$<br>$750k\Omega \leq R_E \leq 5M\Omega$<br>*300pF most desirable value for C <sub>D</sub> |

|                  | Input Voltage Levels                 | ·····                                       |                                               |                                               |          |                                                                                                                                                                                                   |

| V <sub>IH</sub>  | Logical "1"                          |                                             | 80% of<br>(V <sub>DD</sub> -V <sub>SS</sub> ) | V <sub>DD</sub><br>+ 0.3                      | v        |                                                                                                                                                                                                   |

| V <sub>IL</sub>  | Logical ''O''                        |                                             | V <sub>SS</sub><br>-0.3                       | 20% of<br>(V <sub>DD</sub> -V <sub>SS</sub> ) | v        |                                                                                                                                                                                                   |

| CIN              | Input Capacitance Any Pin            |                                             |                                               | 7.5                                           | pF       |                                                                                                                                                                                                   |

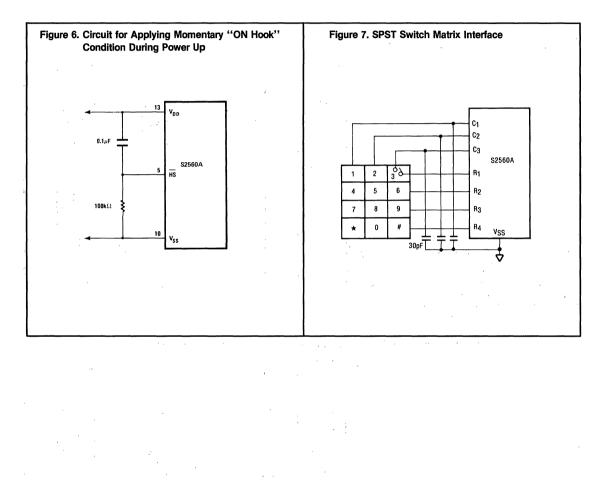

The device power supply should always be turned on before the input signal sources, and the input signals should be turned off before the power supply is turned off ( $V_{SS} \le V_{I} \le V_{DD}$  as a maximum limit). This rule will prevent over-dissipation and possible damage of the input-protection diode when the device power supply is grounded. When power is first applied to the device, the device should be in ''On Hook'' condition ( $\overline{HS} = 1$ ). This is necessary because there is no internal power or reset on chip and for proper operation all internal latches must come up in a known state. In applications where the device is hard wired in ''Off Hook'' ( $\overline{HS} = 0$ ) condition, a momentary ''On Hook'' condition can be presented to the device during power up by use of a capacitor resistor network as shown in Figure 6.

## S2560A

### **Functional Description**

The pin function designations are outlined in Table 1.

### Oscillator

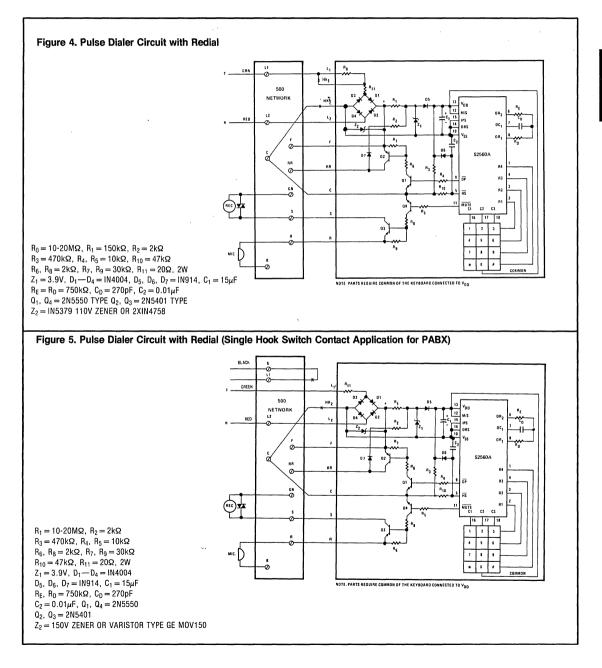

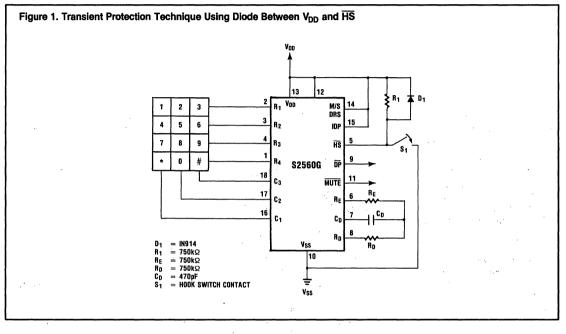

The device contains an oscillator circuit that requires three external components: two resistors (R<sub>D</sub> and R<sub>E</sub>) and one capacitor (C<sub>D</sub>). All internal timing is derived from this master time base. To eliminate clock interference in the talk state, the oscillator is only enabled during key closures and during the dialing state. It is disabled at all other times including the "on hook" condition. For a dialing rate of 10pps the oscillator should be adjusted to 2400Hz. Typical values of external components for this are R<sub>D</sub> and R<sub>E</sub> = 750k $\Omega$  and C<sub>D</sub> = 270pF. It is recommended that the tolerance of resistors to be 5% and capacitor to be 1% to insure a 10% tolerance of the dialing rate in the system.

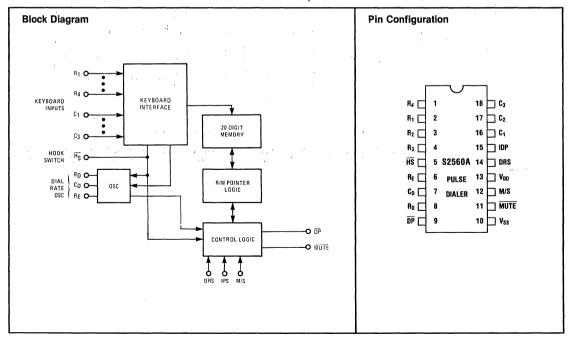

### Keyboard Interface (S2560A)

The S2560A employs a scanning technique to determine a key closure. This permits interface to a DPCT keyboard with common connected to  $V_{DD}$  (Figure 1), logic interface (Figure 2) and interface to a SPST switch matrix (Figure 7). A high level on the appropriate row and column inputs constitutes a key closure for logic interface. When using a SPST switch matrix, it is necessary to add small capacitors (30pF) from the column inputs to V<sub>SS</sub> to insure that the oscillator is shut off after a key is released or after the dialing is complete.

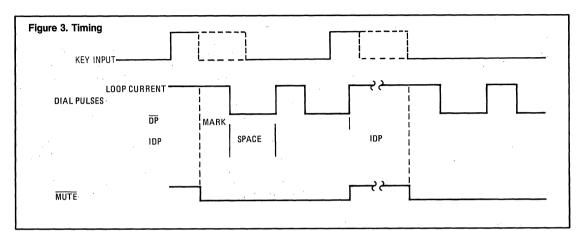

**OFF Hook Operation:** The device is continuously powered through a 150k $\Omega$  resistor during Off hook operation. The DP output is normally high and sources base drive to transistor Q<sub>1</sub> to turn ON transistor Q<sub>2</sub>. Transistor Q<sub>2</sub> replaces the mechanical dial contact used in the rotary dial phones. Dial pulsing begins when the user enters a number through the keyboard. The DP output goes low shutting the base drive to Q<sub>1</sub> OFF causing Q<sub>2</sub> to open during the pulse break. The MUTE output also goes low during dial pulsing allowing muting of the receiver through transistor Q<sub>3</sub> and Q<sub>4</sub>. The relationship of dial pulse and mute outputs are shown in Figure 3.

**ON Hook Operation:** The device is continuously powered through a  $10-20M\Omega$  resistor during the ON hook operation. This resistor allows enough current from the tip and ring lines to the device to allow the internal memory to hold and thereby providing storage of the last number dialed.

The dialing rate is derived by dividing down the dial rate oscillator frequency. Table 2 shows the relationship of the dialing rate with the oscillator frequency and the dial rate select input. Different dialing rates can be derived by simply changing the external resistor value. The dial rate select input allows changing of the dialing rate by a factor of 2 without the necessity of changing the external component values. Thus, with the oscillator adjusted to 2400Hz, dialing rates of 10 or 20pps can be achieved. Dialing rates of 7 and 14pps similarly can be achieved by changing the oscillator frequency to 1680Hz.

The Inter-Digit Pause (IDP) time is also derived from the oscillator frequency and can be changed by a factor of 2 by the IDP select input. With IDP select pin wired to  $V_{SS}$ , an IDP of 800ms is obtained for dial rates of 10 and 20pps. IDP can be reduced to 400ms by wiring the IDP select pin to  $V_{DD}$ . At dialing rates of 7 and 14pps, IDP's of 1143ms and 572ms can be similarly obtained. If the IDP select is connected to the dial rate select pin, the IDP is scaled to the dial rate such that at 10pps an IDP of 800ms is obtained.

The user can enter a number up to 20 digits long from a standard 3x4 double contact keypad with common (Figure 1). It is also possible to use a logic interface as shown in Figure 2 for number entry. Antibounce protection circuitry is provided on chip (min. 20ms) to prevent false entry.

Any key depressions during the on-hook condition are ignored and the oscillator is inhibited. This insures that the current drain in the on-hook condition is very low and used to retain the memory.

### **Normal Dialing**

The user enters the desired numbers through the keyboard after going off hook. Dial pulsing starts as soon as the first digit is entered. The entered digits are stored sequentially in the internal memory. Since the device is designed in a FIFO arrangement, digits can be entered at a rate considerably faster than the output rate. Digits can be entered approximately once every 50ms while the dialing rate may vary from 7 to 20pps. The number entered is retained in the memory for future redial. Pauses may be entered when required in the dial sequence by pressing the "#" key, which provides access pauses for future redial. Any number of access pauses may be entered as long as the total entries do not exceed twenty.

#### **Auto Dialing**

The last number dialed is retained in the memory and therefore can be redialed out by going off hook and pressing the "#" key. Dial pulsing will start when the key is depressed and finish after the entire number is dialed out unless an access pause is detected. In such a case, the dial pulsing will stop and will resume again only after the user pushes the "#" key.

## S2560A

### Table 1. S2560A/S2560B Pin/Function Descriptions

| Pin                                                                                                                                        | Number                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Keyboard</b><br>(R <sub>1</sub> , R <sub>2</sub> , R <sub>3</sub> , R <sub>4</sub> , C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub> ) | 2, 3, 4,<br>1, 16,<br>17, 18 | These are 4 row and 3 column inputs from the keyboard contacts. These inputs are open when the keyboard is inactive. When a key is pushed, an appropriate row and column input must go to $V_{DD}$ or connect with each other. A logic interface is also possible as shown in Figure 2. Active pull up and pull down networks are present on these inputs when the device begins keyboard scan. The keyboard scan begins when a key is pressed and starts the oscillator. Debouncing is provided to avoid false entry (typ. 20ms). |