# 1985 MOS Products Catalog

Schweber Electronics Corporation 90 East Tasman Drive San Jose. California 95134 408-946-7171

Copyright

1985

Gould AMI

(All rights reserved) Trade Marks Registered<sup>®</sup>

Information furnished by Gould AMI in this publication is believed to be accurate. Devices sold by Gould AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Gould AMI makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Gould AMI makes no warranty of merchantability or fitness for any purposes. Gould AMI reserves the right to discontinue production and change specifications and prices at any time and without notice.

Advanced Product Description means that this product has not been produced in volume, the specifications are preliminary and subject to change, and device characterization has not been done. Therefore, prior to programming or designing this product into a system, it is necessary to check with Gould AMI for current information.

**Preliminary** means that this product is in limited production, the specifications are preliminary and subject to change. Therefore, prior to programming or designing this product into a system, it is necessary to check with Gould AMI for current information.

These products are intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically **not** recommended without additional processing by Gould AMI for such application.

**GOULD AMI** Semiconductors

MOS Products Guide 1985 Edition

### Introduction

Gould AMI, headquartered in Santa Clara, California, is the semiconductor industry leader in the design and manufacture of custom MOS/VLSI (metal-oxide-silicon very-large-scale-integrated) circuits. It manufactures special circuits for leading computer manufacturers, telecommunications companies, automobile manufacturers and consumer product companies worldwide.

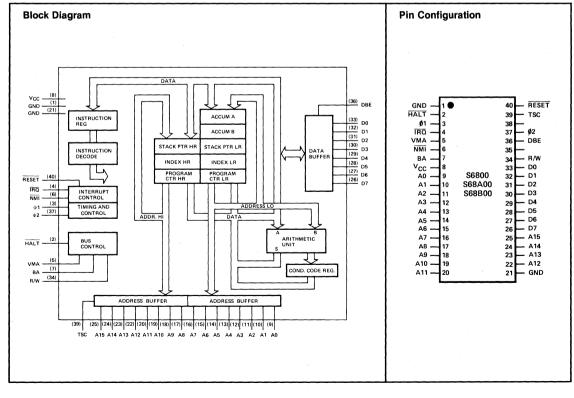

Along with being the leading designer of custom VLSI, Gould AMI is a major alternate source for the S6800 8-bit microprocessor family and the S80 family of microprocessors, which are integrated systems in silicon based on the popular Z80<sup>®</sup> microprocessor. This microprocessor family combines advanced microprocessor, memory, and custom VLSI technologies on a single chip.

The company provides the market with selected low power CMOS Static RAMs, and 16K, 32K, 64K, 128K and 256K ROMs for all JEDEC pinouts or as EPROM replacements.

The most experienced designer of systems-oriented MOS/VLSI communication circuits, Gould AMI provides components for station equipment, PABX and Central Office Switching systems, data communications and advanced signal processing applications.

Gould AMI is a leading innovator in combining digital and analog circuitry on a single silicon chip, and is a recognized leader in switched capacitor filter technology.

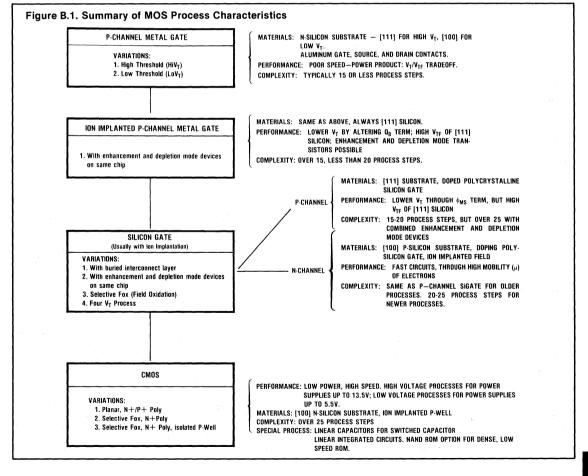

Processing technologies range from the advanced, small geometry, high performance silicon gate CMOS to mature silicon gate N-Channel. Over 27 variations are available.

Gould AMI has design centers in Santa Clara; Pocatello, Idaho; and Swindon, England. Wafer fabrication plants are in Santa Clara and Pocatello, and assembly facilities are in Seoul, Korea and the Phillipines. A joint venture company in Graz, Austria, Austria Microsystems Int'I. GmbH, includes complete design and manufacturing facilities, as will the facility in Tokyo, Japan, Asahi Microsystems, Inc.

Z80 is a registered trademark of Zilog, Inc.

### **Table of Contents**

### A. Indices

- Numerical

- Functional

- Cross-Reference

- 1. Gate Arrays

- 2. Standard Cells

- 3. Custom Continuum

- 4. Communication Products

- 5. Consumer Products

- 6. Memories

### **Microprocessors/Microcomputers**

- 7. S6800 Family

- 8. S80 Family

- 9. S9900 Family

- **10. Future Products**

### **11. Application Note Summary**

### **B.** General Information

- □ MOS Handling

- □ MOS Processes

- □ Product Assurance

- Packaging

- □ Ordering Information

- Terms of Sale

- □ Gould AMI Sales Offices

- Domestic Representatives

- Domestic Distributors

- □ International Representatives and Distributors

# Indices

# Indices

### Numerical Index

| Device  | Page  |

|---------|-------|

| S1602   | 7.103 |

| S23128A | 6.39  |

| S23128B | 6.39  |

| S2333   | 6.26  |

| S2350   | 7.111 |

| S2364A  | 6.32  |

| S2364B  | 6.32  |

| S23256B | 6.43  |

| S23256C | 6.43  |

| S25089  | 4.41  |

| S2550A  |       |

| S2559E  | 4.16  |

| S2559F  | 4.10  |

| S2560A  | 4.19  |

| S2560G  | 4.26  |

| S2560I  | 4.26  |

| S2561C  | 4.28  |

| S25610  | 4.47  |

| S2569   | 4.34  |

| S2569A  | 4.34  |

| S2579   | 4.55  |

| S25910  | 4.63  |

| S25912  | 4.63  |

| S3506   | 4.70  |

| S3507   | 4.70  |

| S3507A  | 4.70  |

| S3524   | 4.201 |

| S3525A  | 4.204 |

| S3526B  | 4.211 |

| S3528   | 4.218 |

| S3529   | 4.228 |

| S3530   | 4.237 |

| S35212  | 4.185 |

| S35212A | 4.185 |

| S35213  | 4.189 |

| S44230  | 4.86  |

| S44231  | 4.86  |

| Device    | Page  |

|-----------|-------|

| S44232    | 4.86  |

| S44233    | 4.86  |

| S44234    | 4.86  |

| S44235    | 4.98  |

| S44236    |       |

| S44237    |       |

| S44238    |       |

| S4520     |       |

| S4521     |       |

| S4534     |       |

| S4535     |       |

| S6800     |       |

|           | 7.3   |

|           | 7.3   |

| S6801     |       |

| S6802     |       |

| S68A02    |       |

| S68B02    |       |

| S68045    |       |

| S68A045   |       |

| S68B045   | 7.132 |

| S6805     |       |

| S6808     |       |

| S68A08    |       |

| S68B08    | 7.44  |

| S6809     | 7.70  |

| S68A09    | 7.70  |

| S68B09    |       |

| S6809(E)  | 7.99  |

| S68A09(E) |       |

|           | 7.99  |

| S6364     |       |

| S6514     | ••••• |

| S6516     | ••••• |

| S6551     |       |

| S6551A    | 7.114 |

| Device           | Page  |

|------------------|-------|

| S6810            |       |

| S68A10           |       |

| S68B10           |       |

| S6821            | 7.122 |

| S68A21           | 7.122 |

| S68B21           | 7.122 |

| S68A316          | 6.20  |

| S68A332          | 6.23  |

| S68A364          | 6.29  |

| S68B364          | 6.29  |

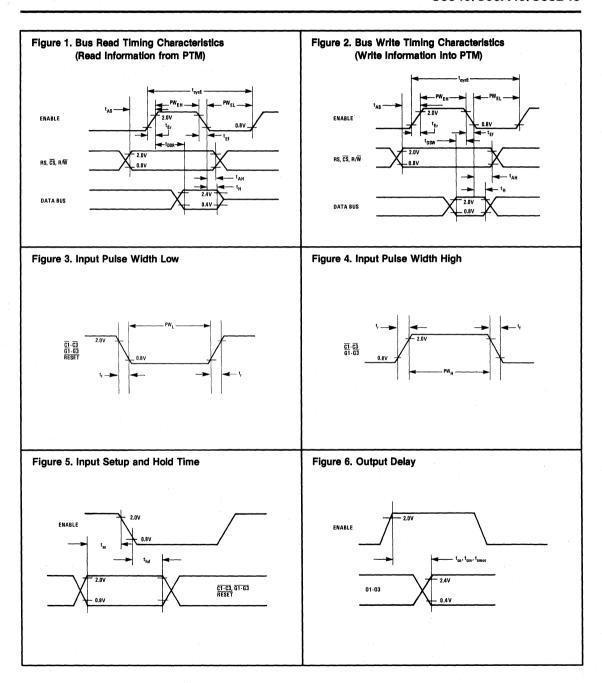

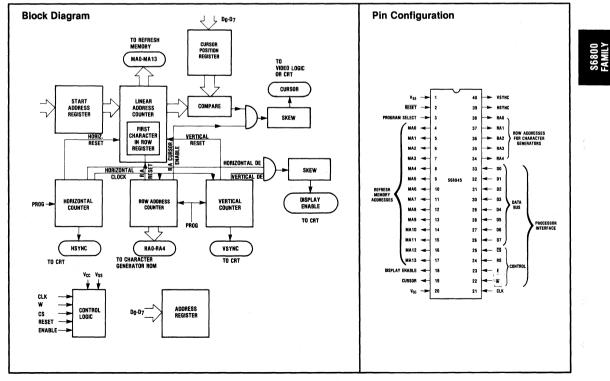

| S6840            | 7.128 |

| S68A40           | 7.128 |

| S68B40           | 7.128 |

| S6846            | 7.146 |

| S6850            | 7.150 |

| S68A50           | 7.150 |

| S68B50           | 7.150 |

| S6852            | 7.158 |

| S68A52<br>S68B52 | 7.158 |

|                  | 7.158 |

|                  | 7.161 |

| S68A54<br>S68B54 | 7.161 |

| S7720            | 4.106 |

| S83              | 4.100 |

| S8970            | 4.111 |

| S8975            | 4.122 |

| S8978            | 4.137 |

| S8980            | 4.156 |

| S8981            | 4.169 |

| \$9900           |       |

| S9901            | 9.15  |

| S9901-4          | 9.15  |

| S9902            | 9.26  |

| S9902-4          | 9.26  |

| S9980            | 9.10  |

|                  |       |

# Indices

### Functional Index

| Device               | Page    |

|----------------------|---------|

| Communications Produ | icts    |

| Station Products     |         |

| S2550A               | 4.3     |

| S2559E               | 4.10    |

| S2559F               | 4.10    |

| S2560A               | 4.19    |

| S2560G               | 4.26    |

| S2560G/I             | 4.26    |

| S2561                | 4.28    |

| S2561C               | 4.28    |

| S2569                | 4.34    |

| S2569A               | 4.34    |

|                      | 4.41    |

|                      | 4.47    |

| S25610<br>S2579      | 4.47    |

| 005040               | 4.55    |

|                      |         |

| S25912               | 4.63    |

| PCM Products         |         |

| S3506                | 4.70    |

| S3507                | 4.70    |

| S3507A               | 4.70    |

| S44230               | 4.86    |

| S44231               | 4.86    |

| S44232               | 4.86    |

| S44233               | 4.86    |

| S44234               | 4.86    |

| S44235               | 4.98    |

| S44236               | 4.98    |

| S44237               | 4.98    |

| S44238               | 4.98    |

| S7720                | 4.106   |

| S8970                | 4.111   |

| S8975                | 4.122   |

| S8978                | 4.137   |

| S8980                | 4.156   |

| S8981                | 4.169   |

|                      | 4.105   |

| Modems and Filters   | 4 4 0 5 |

| S35212               | 4.185   |

| S35212A              | 4.185   |

| S35213               | 4.189   |

| S3524                | 4.201   |

| S3525                | 4.204   |

| S3525A               | 4.204   |

| S3526B               | 4.211   |

| S3528                | 4.218   |

| S3529                | 4.228   |

| S3530                | 4.237   |

|                      |         |

| Device                         | Page         |

|--------------------------------|--------------|

| Consumer Products              |              |

| <b>Display Driver Circuits</b> |              |

| S4520                          | 5.3          |

| S4521                          | 5.11         |

| S4534                          | 5.14<br>5.17 |

| S4535                          |              |

| Gate Arrays                    | 1.2          |

| Memory Products                |              |

| RAMs                           |              |

| S6810                          | 6.3          |

| S68A10                         | 6.3          |

| S68B10                         | 6.3          |

| S6514                          | 6.7          |

| S6516                          | 6.11         |

| ROMs                           |              |

| S68A316                        | 6.20         |

| S68A332                        | 6.23         |

| S2333                          | 6.26         |

| S68A364                        | 6.29         |

| S68B364                        | 6.29         |

| S2364A                         | 6.32         |

| S2364B                         | 6.32         |

| S6364                          | 6.36         |

| S23128A                        | 6.39         |

| S23128B                        | 6.39         |

| S23256B<br>S23256C             | 6.43<br>6.43 |

|                                | 0.43         |

| Microprocessors/               |              |

| Microcomputers<br>S6800 Family |              |

| •                              | 70           |

| S6800<br>S68A00                | 7.3<br>7.3   |

|                                | 7.3<br>7.3   |

| S68B00<br>S6801                | 7.9          |

| S6803                          | 7.9          |

| S6803NR                        | 7.9          |

| S6802                          | 7.44         |

| S68A02                         | 7.44         |

| S68B02                         | 7.44         |

| S6808                          | 7.44         |

| S68A08                         | 7.44         |

| S68B08                         | 7.44         |

| S6805                          | 7.52         |

| S6809                          | 7.70         |

| S68A09                         | 7.70<br>7.70 |

| S68B09                         | 7.70         |

| S6809(E)                       | 7.99         |

| S68A09(E)                      | 7.99         |

| S68B09(E)                      | 7.99         |

| Device                                | Page  |

|---------------------------------------|-------|

| S1602                                 | 7.103 |

| S2350                                 | 7.111 |

|                                       |       |

| S6551                                 | 7.114 |

| S6551A                                | 7.114 |

| S6821                                 | 7.122 |

| S68A21                                | 7.122 |

| S68B21                                | 7.122 |

| S6840                                 | 7.128 |

|                                       |       |

| S68A40                                | 7.128 |

| S68B40                                | 7.128 |

| S68045                                | 7.132 |

| S68A45                                | 7.132 |

| S68B45                                | 7.132 |

| S6846                                 | 7.146 |

|                                       | 7.140 |

|                                       | 7.150 |

| S68A50                                | 7.150 |

| S68B50                                | 7.150 |

| S6852                                 | 7.158 |

| S68A52                                | 7.158 |

| S68B52                                | 7.158 |

|                                       | 7.161 |

|                                       |       |

| S68A54                                | 7.161 |

| S68B54                                | 7.161 |

| S6810                                 | 6.3   |

| S68A10                                | 6.3   |

| S68B10                                | 6.3   |

|                                       | 0.0   |

| S80 Family                            |       |

| S83                                   | 8.2   |

| S8970                                 | 4.111 |

| S8975                                 | 4.122 |

| S8978                                 | 4.137 |

|                                       |       |

| S8980                                 | 4.156 |

| S8981                                 | 4.169 |

| 9900 Family                           |       |

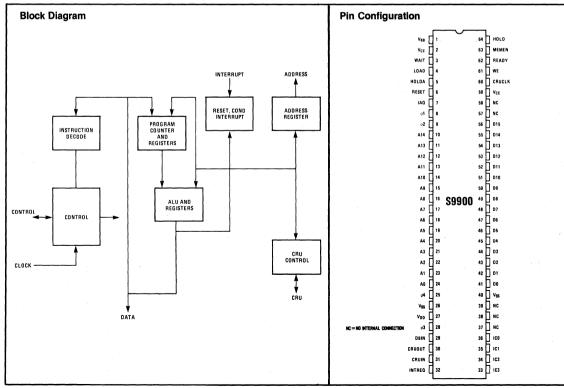

| S9900                                 | 9.3   |

|                                       | 9.10  |

|                                       |       |

| S9980A                                | 9.10  |

| S9901                                 | 9.15  |

| S9901-4                               | 9.15  |

| S9902                                 | 9.26  |

| S9902-4                               | 9.26  |

|                                       | 0.20  |

| Gate Array Circuits                   |       |

| Gate Array                            | 1.2   |

| · · · · · · · · · · · · · · · · · · · |       |

| Standard Cell Circuits                |       |

| Standard Cells                        | 2.2   |

| Custom Continuum                      | 3.2   |

| Custom Continuum                      | J.2   |

|                                       |       |

# **Cross Reference Guide**

### **Communication Products**

### Cross Reference by Manufacturer

| Manufacturer | Part Number      | AMI Functional<br>Equivalent Part | Manufacturer | Part Number | AMI Functiona<br>Equivalent Par |

|--------------|------------------|-----------------------------------|--------------|-------------|---------------------------------|

| AMD          | 7910             | S3530                             | Mostek       | MK 5089     | 25089                           |

| Cherry       | 820X             | S2561                             | Mostek       | MK 50981    | 2560A                           |

| ERSO         | CIC 9187         | 2559                              | Mostek       | MK 50982    | 2560A                           |

| ERSO         | CIC 9110E        | S25610                            | Mostek       | MK 50991    | 2560A                           |

| EXAR         | XR2120           | S35212                            | Mostek       | MK 50992    | 2560A                           |

| G.I.         | ACF 7310,12,7410 | 3526B                             | Mostek       | MK 5116     | 3507                            |

| G.I.         | ACF 7323C        | 3525A                             | Mostek       | MK 5151     | 3507                            |

| G.I.         | ACF 7363C        | 3525A                             | Mostek       | MK 5170     | 2562/2563                       |

| G.I.         | ACF 7383C        | 3525A                             | Mostek       | MK 5175     | 25610                           |

| G.I.         | AY5-9100         | 2560A                             | Mostek       | MK 5387     | 2559                            |

| G.I.         | AY5-9151         | 2560A                             | Mostek       | MK 5389     | 25089                           |

| G.I.         | AY5-9152         | 2560A                             | Mostek       | 5091        | 2559                            |

| G.I.         | AY5-9153         | 2560A                             | Mostek       | 5092        | 2559                            |

| G.I.         | AY5-9154         | 2560A                             | Mostek       | 5094        | 2559                            |

| G.I.         | AY5-9158         | 2560A                             | Mostek       | 5382        | 2569                            |

| G.I.         | AY5-9200         | 2563A                             | Mostek       | 5170        | 2563A                           |

| G.I.         | AY3-9400         | 2559                              | Mostek       | 5175        | S25610                          |

| G.I.         | AY3-9401         | 2559                              | Mostek       | 5380        | 2559                            |

| G.I.         | AY3-9410         | 2559                              | Motorola     | MC 14400    | 3507                            |

| G.I.         | AY5-9800         | 3525A                             | Motorola     | MC 14401    | 3507                            |

| Hitachi      | HD 44211         | 3507                              | Motorola     | MC 14402    | 3507                            |

| Hitachi      | HD 44231         | 3506                              | Motorola     | MC 14408    | 2560A                           |

| Intel        | 2913             | 3507                              | Motorola     | MC 14409    | 2560A                           |

| Intel        | 2914             | 3507                              | Motorola     | MC14412     | S3530                           |

| Intersil     | ICM 7206         | 2559                              | Motorola     | MC6170      | S35212                          |

| Mitel        | MT 4320          | 3525A                             | Motorola     | MC145433    | S3526                           |

| Mitel        | ML 8204          | 2561A                             | Motorola     | MC14413     | S3526                           |

| Mitel        | ML 8205          | 2561A                             | National     | TP53130     | S2579                           |

| Mitel        | MT 8865          | 3525A                             | National     | TP5088      | S2579                           |

| Mitel        | 8204             | S2561                             | National     | MF10        | S3528/S352                      |

| Mostek       | MK 5087          | 2559E                             |              |             |                                 |

## **Cross Reference Guide**

### **Communication Products**

### **Cross Reference by Manufacturer**

| Manufacturer Part Number |           | AMI Functional<br>Equivalent Part |

|--------------------------|-----------|-----------------------------------|

| National                 | MF6       | S3528/S3529                       |

| National                 | MM74HC942 | S3530                             |

| National                 | MM74HC943 | S3530                             |

| National                 | MM 5393   | 2560A                             |

| National                 | MM 5395   | 2559                              |

| National                 | TP5700    | S2550                             |

| NEC                      | μPD 7720  | 2811                              |

| Nitron                   | NC 320    | 2560A                             |

| Phillips                 | TDA 1077  | 2559                              |

| RCA                      | CD 22859  | 2559                              |

| Reticon                  | R5632     | S35212*                           |

| Reticon                  | R5612     | S3526/S3526M                      |

| Reticon                  | R5604     | S3528/S3529                       |

| Reticon                  | R5605     | S3528/S3529                       |

| Reticon                  | R5606     | S3528/S3529                       |

| Reticon                  | R5609     | S3528/S3529                       |

| Reticon                  | R5611     | S3529                             |

| Reticon                  | R5612     | S3528/S3529                       |

| Reticon                  | R5614     | S3528/S3529                       |

| Reticon                  | R5615     | S3528/S3529                       |

| Reticon                  | R5616     | S3528/S3529                       |

| Reticon                  | R5620     | S3528/S3529                       |

| Reticon                  | R5621     | S3528/S3529                       |

| Reticon                  | R5622     | S3528/S3529                       |

| Sanyo                    | 7350      | S2560A                            |

| Sanyo                    | 7351      | S2560A                            |

| Seiko                    | S7220A    | S2560A                            |

| Seiko                    | STC2560   | S2560A                            |

| Seiko                    | S7210A    | S25610                            |

| Sharp                    | 408X      | 2559                              |

| Siliconix                | DF 320    | 2560A                             |

| Siliconix                | DF 321    | 2560A                             |

| For Direct Beplacement   |           | Note: X Denotes any nu            |

|              | AMI Functional |                 |

|--------------|----------------|-----------------|

| Manufacturer | Part Number    | Equivalent Part |

| Siliconix    | DF 322         | 2560A           |

| T.I.         | TCM 170X       | S2550           |

| T.I.         | TCM 5089       | S25089*         |

| T.1.         | TCM 509X       | 2559            |

| T.I.         | TCM 508X       | 2559            |

| T.I.         | TCM 150X       | S2561           |

| T.I.         | TMS 99532      | S3530           |

| SSI          | 201            | S3525A          |

| SSI          | 202            | S3525A          |

| SSI          | 203            | S3525A          |

| Teltone      | M-980          | S3524           |

| Teltone      | M-900          | S3525A          |

| Teltone      | M-907          | S3525A          |

| Teltone      | M-917          | S3525A          |

| Teltone      | M-927          | S3525A          |

| Teltone      | M-947          | S3525B*         |

| Teltone      | M-948          | S3525A          |

| Teltone      | M-056          | S3525A          |

| Teltone      | M-957          | \$3525A         |

| Teltone      | M-967          | S3525A          |

|              |                |                 |

\* For Direct Replacement

Note: X Denotes any number

### **Cross Reference Guide**

### Memory Products

|          |         | CMOS RAI | Ms                                                  |           | 14. |        |

|----------|---------|----------|-----------------------------------------------------|-----------|-----|--------|

| Vendor   | 256 × 4 | 1K × 1   | ana sa ta ta sa | 1K×4      | 1.1 | 4K×1   |

| AMI      | S5101   |          |                                                     | S6514     |     |        |

| FUJITSU  | _       |          |                                                     | 6514/8414 |     | 8404   |

| HARRIS   | 6561    | 6508     |                                                     | 6514      |     | 6504   |

| HITACHI  | 435101  |          |                                                     | 4334      |     | 4315   |

| INTERSIL | 6551    | 6508     |                                                     | 6514      |     | 6504   |

| MOTOROLA | 145101  | 146508   |                                                     |           |     | 146504 |

| NATIONAL | 74C920  | 74C929   |                                                     | 6514      |     | 6504   |

| NEC      | 5101    | 6508     |                                                     | 444/6514  |     |        |

| OKI      | 573     | 574      |                                                     | 5115      |     |        |

| RCA      | 5101    | 1821     |                                                     | 1825      |     | 5104   |

| SSS      | 5101    | 5102     |                                                     | _         |     |        |

| TOSHIBA  | 5101    | 5508     |                                                     | 5514      |     | 5504   |

|           |           |                                        | BYTE WI  | DE NMOS ROMs         |             |          |          |

|-----------|-----------|----------------------------------------|----------|----------------------|-------------|----------|----------|

| Vendor    | 2K × 8    | 4K × 8                                 | 4K×8*    | $8K \times 8-24$ Pin | 8K×8-28 Pin | 16K × 8  | 32K × 8  |

| AMI       | S68A316   | S68A332                                | S2333    | S68A364              | S2364A      | S23128A  | S23256B  |

| AMD       | AM9218    | 9232                                   | 9233     | AM9264               | AM9265      | AM92128  |          |

| NEC/EA    | µPD2316   | µPD2332A                               | µPD2332B | µPD8364              | µPD2364     | µPD23128 | µPD23256 |

| FAIRCHILD | F68316    | F3532                                  | F3533    | F3564                |             |          |          |

| FUJITSU   |           | ······································ |          |                      |             | -        |          |

| GI        | R03-9316  |                                        | R03-9333 | R03-9364             | R03-9365    | SPR-128  |          |

| GTE       | 2316      | 2332                                   |          | 2364                 |             |          |          |

| MOS       |           | · · · · · · · · · · · · · · · · · · ·  |          | MPS2364              |             | -        |          |

| MOSTEK    | MK34000   |                                        |          | MK36000              | MK37000     |          | MK38000  |

| MOTOROLA  | MCM68A316 | MCM68A332                              |          | MCM68365             |             |          | MCM65256 |

| SIGNETICS | 2616      | 2632                                   |          | 2664A                | 2664AM      | 23128    | 23256    |

| SYNERTEK  | SY2316    | SY2332                                 | SY2333   | SY2364               | SY2365      | SY23128  | SY23256  |

| ОКІ       | MSM2916   | · · · · · · · · · · · · · · · · · · ·  |          |                      |             |          |          |

| ROCKWELL  | R2316     | R2332                                  |          | R2364A               | R2364B      | ·····    |          |

| SGS       | M2316     |                                        |          |                      |             |          |          |

| TOSHIBA   | TSU2316   |                                        | TSU333-2 |                      |             |          |          |

| NATIONAL  |           | MM52132                                |          | MM52164              |             |          |          |

| VTI       |           | VT2332                                 | VT2333   |                      | VT2365A     | VT23129  | VT23256  |

\*Pin compatible with 2732 EPROM

# Microprocessor Family

|            |                                                                                                              | /.                      | New Street | Print       | 30/0        | 2.50 - 1 - 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 | REPLACES                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------|-------------------------|------------|-------------|-------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| EVICE      | DESCRIPTION                                                                                                  | <u> </u>                |            | <u> </u>    | 1           | $\bigwedge$                                  |                                                                                                                                                 |

| 1602       | UART (UNIVERSAL ASYNCHRONOUS<br>Receiver/transmitter)                                                        |                         |            | P<br>C<br>D | P<br>C<br>D |                                              | S1883, MB8868A, AY-5-1013, AY-3-1015, TR1863, □□<br>TR1602, TMS6011, NATIONAL 5303, SMC2502                                                     |

| 2350       | USRT (UNIVERSAL SYNCHRONOUS<br>Receiver/transmitter)                                                         |                         |            | P<br>C<br>D | P<br>C<br>D |                                              |                                                                                                                                                 |

| 6800       | MPU (MICROPROCESSOR)                                                                                         | x                       | X          | PCD         | P<br>C<br>D |                                              | MC6800, HD46800D, F6800                                                                                                                         |

| 6801       | 8-BIT MICROCOMPUTER 2K ROM,<br>128 Bytes Ram, Uart, Timer, Vo                                                |                         |            | P<br>C<br>D | ç           | x                                            | MC6801, HD6801X                                                                                                                                 |

| 6802       | 8-BIT MICROPROCESSOR WITH CLOCK<br>AND 128 BYTES RAM                                                         | x                       | x          | P<br>C      | P<br>C      |                                              | MC6802, HD46802, F6802                                                                                                                          |

| 6803       | S6801 WITHOUT ROM                                                                                            |                         |            | P<br>C<br>D | C           |                                              | MC6803                                                                                                                                          |

| 6803NR     | S6803 WITHOUT RAM                                                                                            |                         |            | P<br>C<br>D | C           |                                              | MC6803NR                                                                                                                                        |

| 6805       | 8-BIT MICROCOMPUTER WITH 1.1K BYTES<br>Rom, 64 Bytes RAM, Timer, 1/0                                         |                         |            | PCD         | P<br>C<br>D | x                                            | MC6805P2, HD6805S                                                                                                                               |

| 6808       | MICROPROCESSOR AND CLOCK                                                                                     | x                       | x          | PC          | PC          |                                              | MC6808, HD46808, F6808                                                                                                                          |

| 6809       | ENHANCED 8-BIT MPU                                                                                           | x                       | x          | P<br>C<br>D | P<br>C<br>D |                                              | MC6809, HD6809, F6809E                                                                                                                          |

| 6809E      | ENHANCED 8-BIT MPU EXTERNAL<br>Clock input                                                                   |                         |            | P<br>C<br>D | PCD         |                                              | MC6809E, HD6809E, F6809E                                                                                                                        |

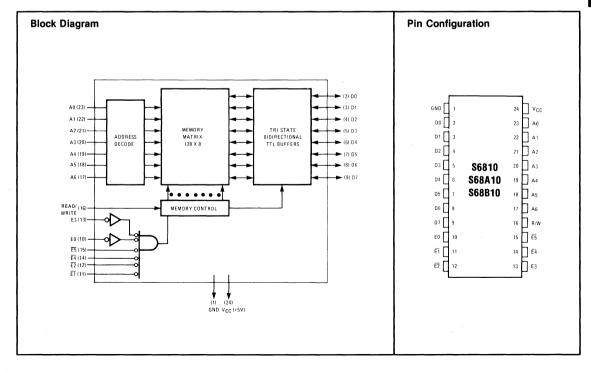

| 6810       | RAM (128x8)                                                                                                  | x                       | x          | PCD         | PCD         |                                              | MC6810, HD46810, F6810                                                                                                                          |

| 6810-1     | RAM LOW COST (575ns)                                                                                         |                         |            | PC          | PCD         |                                              |                                                                                                                                                 |

| 6821       | PIA                                                                                                          | x                       | x          | PCD         | PCD         |                                              | MC6821, HD46821, F6821, SY6520 🗆 🗆                                                                                                              |

| 6840       | TIMER                                                                                                        | x                       | x          | PC          | P<br>C<br>D |                                              | MC6840, HD46840, F6840                                                                                                                          |

| 6846       | ROM, VO, TIMER                                                                                               | x                       | x          | PC          | PCD         | x                                            | MC6846, HD46846, F6846                                                                                                                          |

| 6850       | ACIA                                                                                                         | x                       | x          | PCD         | PCD         |                                              | MC6850, HD46850, F6850                                                                                                                          |

| 6852       | SSDA                                                                                                         | x                       | x          | PC          | PC          |                                              | MC6852, HD46852, F6852                                                                                                                          |

| 6854       | ADLC                                                                                                         | x                       | x          | PC          | PCD         |                                              | MC6854, HD46854, F6854                                                                                                                          |

| 68045      | CRT CONTROLLER                                                                                               | x                       | x          | PCD         | PCD         | x                                            | MC6845, HD46505, SY6545 🗆 🗆                                                                                                                     |

| 6551/6551A | ACIA/BAUD RATE GENERATOR                                                                                     |                         | x          | PC          | PC          |                                              | SY6551, ROCKWELL 6551                                                                                                                           |

| 9900       | 16-BIT MICROPROCESSOR                                                                                        |                         |            | PC          |             |                                              | TM\$9900                                                                                                                                        |

| 9980A      | 16-BIT µPROCESSOR—8-BIT DATA BUS                                                                             |                         |            | P<br>C<br>D |             |                                              | TMS9980A                                                                                                                                        |

| 9901       | PCI                                                                                                          |                         |            | PCD         |             |                                              | TMS9901                                                                                                                                         |

| 9902       | ACC                                                                                                          |                         |            | PC          |             |                                              | TM\$9902                                                                                                                                        |

|            | R CONVENTIONS S = AMI PRODUCT<br>68 = FAMILY DESIG<br>L REPLACEMENT A = BUS SPEED (<br>NONE - 11)<br>A = 1.5 | GNATIO<br>OPTION<br>WHz | DN         | 0           | =           | = QUAI<br>None<br>I                          | DESIGNATIONPPACKAGE TYPEIFIER (OPTIONAL)PP LASTIC $0 - 70^{\circ}$ CCC ERAMIC $-40/+85^{\circ}$ CD= CERDIPLABLE=NOT AVAILABLE OR NOT APPLICABLE |

INDICES

### I. Introduction

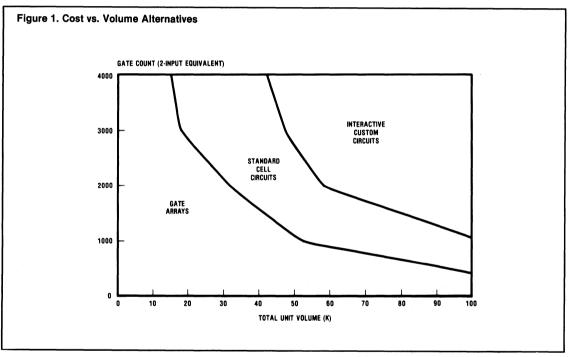

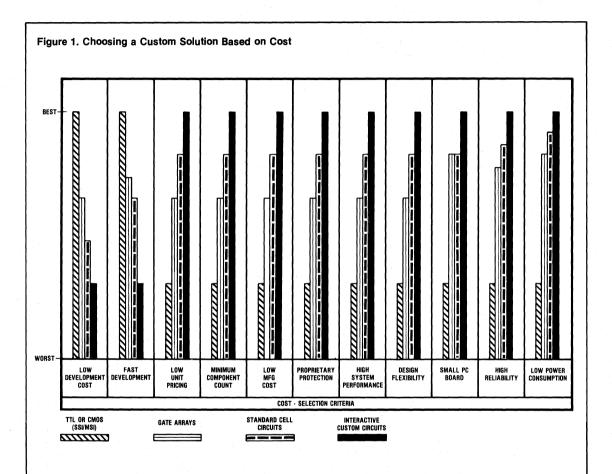

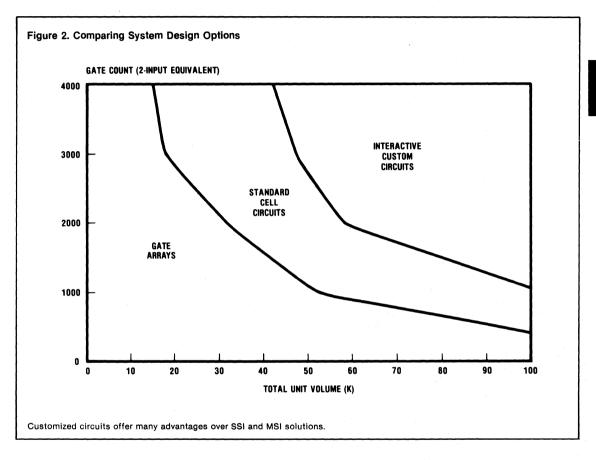

As the semiconductor industry has marched into the new era of VLSI, a new market has appeared - fast turn custom or, as it is now called, semicustom. Gould AMI, a leader in custom MOS since 1966, is also a leader in this new semicustom market. Gould AMI has introduced CAD software and hardware tools to allow customers to design, simulate, and layout circuits using Gould AMI gate array families. Figure 1 shows the economic tradeoffs between gate array, standard cell, and full custom, all of which are offered by Gould AMI. The best solution for your needs will depend upon your volume requirements and circuitry complexity.

The simplest semicustom ICs are gate arrays. A gate array consists of uncommitted component matrices of transistors (usually P- and N-type for CMOS) that allow userdefined interconnections through a single or double layer of metal. Since arrays employ fixed component locations and geometries, Gould AMI can process the wafers up to the metallization stage and inventory the wafers for future customization. Thus gate arrays look like late mask programmable ROMs and benefit from this large-volume production because they appear to be a standard product. Gould AMI can offer them at an economical price and with fast prototyping and production turn on spans.

The key to success in this new market is flexibility. Flexibility to the user entails: low risk circuit implementation, short development span, lower development cost, lower piece part cost (over discrete implementations), easy to change or modify, enhanced product features, etc. For the manufacturer, flexibility means: ease of manufacture, economies of scale, and easy interface with customers. One last point:

Gould AMI offers the user the opportunity to migrate at a low cost, from a gate array to a standard cell (or possibly full custom) to further enhance his/her product. By using analog cells, significant advances in chip function integration are at the user's disposal.

In addition, Gould AMI offers a wide selection of packages to meet specific user needs. Gould AMI offers the CAD tools needed to work in the new market. Gould AMI also offers the training required to move customers quickly and easily into this new technology. See the "Custom Solutions" section in this catalog for more details.

### **2 Micron Products**

Gould AMI is developing 2 micron CMOS technology to support the next generation of gate arrays and standard cells. These products will offer size and performance improvements of up to 50% from their 3 micron counterparts.

Introduction of the first 2 micron gate array family is planned for early 1985 and is expected to offer capabilities of up to 10,000 gates.

1.2

#### **Three-Micron Gate Array Family**

As part of Gould AMI's long range semicustom strategy in MOS/VLSI, Gould AMI will continue to introduce new gate array products. These new products will offer performance and cost advantages not currently realizable. In conjunction with these new array products, Gould AMI has introduced computer-aided design tools to automate the entire gate array design process.

### Table 1. Gould AMI Gate Array Configurations $3\mu$ Double Metal Family

| Part No. | Eg. 2-<br>Input Gates | Total Pads | General<br>VO | Power<br>Only |

|----------|-----------------------|------------|---------------|---------------|

| GA-1000D | 1152                  | 68         | 64            | 4             |

| GA-2000D | 2070                  | 88         | 84            | 4             |

| GA-3000D | 3080                  | 106        | 102           | 4             |

| GA-4000D | 4012                  | 124        | 120           | 4             |

#### 3µSingle Metal Family

| Eg. 2-<br>Input Gates | Total Pads                                                             | General<br>VO                                                                                                                         |

|-----------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 540                   | 40                                                                     | 40                                                                                                                                    |

| 1040                  | 54                                                                     | 52                                                                                                                                    |

| 1500                  | 64                                                                     | 64                                                                                                                                    |

| 2025                  | 74                                                                     | 74                                                                                                                                    |

| 2500                  | 84                                                                     | 84                                                                                                                                    |

|                       | Input Gates           540           1040           1500           2025 | Input Gates         Total Pads           540         40           1040         54           1500         64           2025         74 |

#### 5µ Single Metal Family

| Part No. | Eg. 2-<br>Input Gates | Total Pads | Low<br>Power<br>VO | High<br>Power<br>I/O | input<br>Only |

|----------|-----------------------|------------|--------------------|----------------------|---------------|

| UA-1     | 300                   | 40         | 17                 | 20                   | 3             |

| UA-2     | 400                   | 46         | 23                 | 20                   | 3             |

| UA-3     | 540                   | 52         | 25                 | 24                   | 3             |

| UA-4     | 770                   | 62         | 31                 | 28                   | 3             |

| UA-5     | 1000                  | 70         | 35                 | 32                   | 3             |

| UA-6     | 1260                  | 78         | 39                 | 36                   | 3             |

The newest gate array family is the high-performance GA and GA-D series which is based on Gould AMI's 3-micron CMOS silicon gate process technology.

The Gould AMI GA and GA-D series are designed for 5V operation over military temperature range (-55 to  $125^{\circ}$ C). Besides high speed (2 to 3ns typical delay) and high density (up to 4K gates), it features total I/O flexibility.

### Total Flexibility of I/O Options

Peripheral cell design offers total flexibility in determining pin-out configurations and maximizes the number of options associated with each pad. Each pin in the 3-micron gate array can serve any of the following functions:

- TTL Output Driver

- LSTTL Output Driver

- CMOS Output Driver

- Open Drain Output

- Tristate Output

- Analog Switch

- CMOS Input

- V<sub>DD</sub> Supply

- V<sub>SS</sub> Supply

Furthermore, the peripheral cell also contains high impedance transistors that can be used as pull-ups or pulldowns if required.

The single metal version provides up to 2500 gates and the double metal GA-D version 4000 gates. See Table 3 for configurations.

In conjunction with these new array products, Gould AMI offers a complete powerful set of design automation software to allow users complete design flexibility. Using a terminal tied to a central Gould AMI owned or customer owned minicomputer or mainframe, the user has access to a complete set of design automation tools including:

- Schematic capture

- Logic simulation

- · Circuit simulation

- · Interactive or autoplace and route

- · Automated placement and routing

#### Five-Micron Gate Array Family

The family of 5-micron CMOS products is offered in six configurations with circuit complexities equivalent to 300, 400, 540, 770, 1000, and 1260 two-input gates, respectively. All pads can be individually configured as inputs, outputs, or I/O's. Input switching characteristics can be programmed for either CMOS or TTL compatibility. LS buffer output drivers will support CMOS levels of two low power schottky TTL loads. TTL buffer outputs will also provide CMOS levels and are capable of driving up to six LS TTL loads. All output drivers can be programmed for tri-state or open drain (open collector) operation as required.

#### **General Description**

Gould AMI's gate array products consist of arrays of CMOS devices whose interconnections are initially unspecified. By "programming" interconnect at the metal layer mask level, virtually arbitrary configurations of digital logic can be realized in an LSI implementation.

Gould AMI gate array designs are based on topological cells—i.e., groups of uncommitted silicon-gate N-Channel and P-Channel transistors—that are placed at regular intervals along the X and Y axes of the chip with intervening polysilicon underpasses. Pads, input protection circuitry, and uncommitted output drivers are placed around the periphery.

Compared to SSI/MSI logic implementations, Gould AMI's gate array approach offers lower system cost and, in addition, all the benefits of CMOS LSI. The lower system cost is due to significant reductions in component count, board area and power consumption. Product reliability, a strong

### **II. Gate Array Families**

- Arrays of Uncommitted CMOS Transistors Programmed by Metal Layer Interconnect to Implement Arbitrary Digital Logic Functions

- Multiple Developmental Interfaces: Gould AMI or Customer Designed

- Three Array Families—5-Micron Single Metal CMOS, 3-Micron Single Metal CMOS, and 3-Micron Double Metal Versions

- Multiple Array Configurations From 300 to 1260 Gates for 5-Micron Devices, and 500 to 4000 Gates for 3-Micron Devices

- Quick Turn Prototypes and Short Production Turn-On Time

function of component count, is thereby greatly enhanced. And compared to fully custom LSI circuits, the gate array offers several advantages: low development cost; shorter development time; shorter production turn-on time; and low unit costs for small to moderate production volumes.

Gould AMI's CMOS gate arrays are offered in three families: the 5-micron UA series, the 3-micron single metal GA series, and the 3-micron double metal GA-D series. The 5-micron UA series has been in production since 1980 and well over one hundred circuits have been produced in that technology. The 3-micron GA and GA-D series are the high-speed high-density devices fabricated in Gould AMI's state-of-the-art 3-micron CMOS processes.

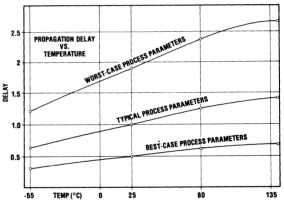

The CMOS technology used for these products is Gould AMI's 5-micron, oxide-isolated, silicon gate CMOS process. This process offers all the conventional advantages of CMOS-i.e., very low power consumption, broad power supply voltage range (3V to  $12V \pm 10\%$ ), and high noise immunity-as well as dense circuits with high performance. Gate propagation delays are in the five to ten ns range for 5 volt operation at room temperature. Gould AMI gate array products can be supplied in versions intended for operation over the standard commercial temperature range (0°C to  $+70^{\circ}$ C), the industrial range ( $-40^{\circ}$ C to  $+85^{\circ}$ C), or the full military range (- 55°C to + 125°C). MIL-STD-883 Class B screening, including internal visual inspection and high temperature burn-in, is offered. Similarly, customerspecified high reliability screening is available for commercial and industrial applications.

- Economical Semicustom Approach for Low-to-Medium Production Volume Requirements

- Advanced Oxide-Isolated Silicon Gate CMOS Technology

- High Performance—2 to 3ns Typical Gate Delay for 3-Micron Devices

- · Broad Power Supply Range

- TTL or CMOS Compatible I/O

- Up to 124 I/O Connections

- Numerous Package Options

- Full Military Temperature Range (- 55°C to 125°C) and MIL-STD-883 Class B Screening Available

#### **Table 2. Gate Array SSI Functional Macros**

|                                           | TTL FUNCTIONAL         | GATE  |

|-------------------------------------------|------------------------|-------|

| DESCRIPTION                               | EQUIVALENCE            | COUNT |

| INVERTER                                  | 1/6 LS04               | · 1   |

| DUAL-INVERTER DRIVER                      | 1/6 LS04               | 1     |

| TRIPLE-INVERTER DRIVER                    | 1/6 LS04               | 2     |

| QUADRUPLE-INVERTER DRIVER                 | 1/6 LS04               | 2     |

| QUINTUPLE-INVERTER DRIVER                 | 1/6 LS04               | 3     |

| 2-INPUT NAND                              | 1/4 LS00               | . 1   |

| 3-INPUT NAND                              | 1/3 LS10               | 1.5   |

| 4-INPUT NAND                              | 1/2 LS20               | 2     |

| 5-INPUT NAND                              |                        | 2.5   |

| 2-INPUT AND                               | 1/4 LS08               | 1.5   |

| 3-INPUT AND                               | 1/3 LS11               | 2     |

| 4-INPUT AND                               | 1/2 LS21               | 2.5   |

| 2-INPUT NOR                               | 1/4 LS02               | 1     |

| 3-INPUT NOR                               | 1/3 LS27               | 1.5   |

| 4-INPUT NOR                               | ·                      | 2     |

| 5-INPUT NOR                               | 1/2 S260               | 2.5   |

| 2-INPUT OR                                | 1/4 LS32               | 1.5   |

| 3-INPUT OR                                |                        | 2     |

| 4-INPUT OR                                | —                      | 2.5   |

| EXCLUSIVE OR                              | 1/4 LS86               | 2.5   |

| EXCLUSIVE NOR                             |                        | 2.5   |

| 2-IN AND/2-IN NOR                         | -                      | 1.5   |

| 2-WIDE AND-OR-INVERT                      | 1/2 S51                | 2     |

| 2-IN OR/2-IN NAND<br>2-WIDE OR-AND-INVERT |                        | 1.5   |

| INTERNAL TRI-STATE DRIVER                 |                        | 2     |

| 2 TO 1 MULTIPLEXER                        |                        | 1     |

| SET-RESET LATCH                           | 1/4 LS279              | 2     |

| CLOCKED LATCH                             | 1/4 LS2/9<br>1/4 LS75* | 2.5   |

| CLOCKED LATCH WITH SET                    | 1/4 10/5               | 2.5   |

| D FLIP-FLOP WITH RESET                    | 1/4 LS175**            | 5     |

| D FLIP-FLOP WITH SET                      | 1/4 L31/3              | 5     |

| D FLIP-FLOP SET AND RESET                 |                        | 6     |

| TTL LEVEL TRANSLATOR                      |                        | 2     |

| THE EFFE TRANSLATOR                       |                        | ٤     |

\* Both polarities of the enable signal are required for CMOS CLK

\*\* CLK and CLK are required for CMOS. The 74LS175 is reset on a positive going transition of the control signal whereas the CMOS implementation resets on a negative going transition of the same signal.

In conjunction with these arrays, Gould AMI has developed a set of "functional overlays." These are basic logic element building blocks—e.g. two input and larger gates of various types, flip-flops, and so forth—from which complete logic designs can be developed. Ease functional overlay corresponds to a metal interconnect pattern that is superimposed on a set of uncommitted transistors (and polysilicon underpasses) in the array to implement the logic element. Typical functional overlay logic elements and the number of equivalent two-input gates are shown in Table 3.

Currently over 100 functional cells exist for this family. D.C. characteristics for the 3 micron gate array family are summarized in Table 4.

#### Table 3. Gate Array MSI/LSI Functional Macros

| Table 3. Gate Array WSI/LSI Fund         | ctional macros                |               |

|------------------------------------------|-------------------------------|---------------|

| DESCRIPTION                              | TTL FUNCTIONAL<br>EQUIVALENCE | GATE<br>COUNT |

| 3 TO 8 DECODER                           | LS138                         | 23            |

| 4 TO 16 DECODER                          | LS154                         | 56            |

| 8 TO 1 MULTIPLEXER                       | LS151                         | 28            |

| 4-BIT FULL ADDER                         | LS283                         | 60            |

| 8-BIT FULL ADDER                         |                               | 120           |

| 12-BIT FULL ADDER                        |                               | 180           |

| 16-BIT FULL ADDER                        |                               | 240           |

| LOOK-AHEAD CARRY GENERATOR               | LS182                         | 34            |

| 4-BIT PRESETTABLE AND EXPANDABLE         | LOTOL                         | 04            |

| BINARY COUNTER                           | LS163                         | 52            |

| 4-BIT EXPANDABLE BINARY COUNTER          | LS163*                        | 39            |

| 4-BIT PRESETTABLE BINARY COUNTER         | LS163*                        | 47            |

| 4-BIT BINARY COUNTER                     | LS163*                        | 34            |

| 8-BIT PRESETTABLE BINARY COUNTER         | LOTUO                         | 104           |

| 12-BIT PRESETTABLE BINARY COUNTER        |                               | 156           |

| 16-BIT PRESETTABLE BINARY COUNTER        |                               |               |

| 4-BIT EXPANDABLE & PRESETTABLE           |                               | 208           |

|                                          | 1.04.00                       |               |

| BINARY UP/DOWN COUNTER                   | LS169                         | 62            |

| 4-BIT EXPANDABLE BINARY                  |                               |               |

| UP/DOWN COUNTER                          | LS169*                        | 49            |

| 4-BIT PRESETTABLE BINARY                 |                               |               |

| UP/DOWN COUNTER                          | LS169*                        | 58            |

| 4-BIT BINARY UP/DOWN COUNTER             | LS169*                        | 44            |

| 4-BIT EXPANDABLE & PRESETTABLE           |                               |               |

| DECADE COUNTER                           | LS162                         | 56            |

| 4-BIT EXPANDABLE DECADE COUNTER          | LS162*                        | 43            |

| 4-BIT PRESETTABLE DECADE COUNTER         | LS162*                        | 51            |

| 4-BIT DECADE COUNTER                     | LS162*                        | 38            |

| 4-BIT EXPANDABLE & PRESETTABLE           |                               |               |

| DECADE UP/DOWN COUNTER                   | LS168                         | 66            |

| 4-BIT EXPANDABLE DECADE UP/DOWN          |                               |               |

| COUNTER                                  | LS168*                        | 53            |

| 4-BIT PRESETTABLE DECADE UP/DOWN         |                               |               |

| COUNTER                                  | LS168*                        | 62            |

| 4-BIT DECADE UP/DOWN COUNTER             | LS168*                        | 48            |

| 4-BIT BIDIRECTIONAL SHIFT REGISTER       | LS194                         | 62            |

| 4-BIT PARALLEL-ACCESS SHIFT              |                               |               |

| REGISTER                                 | LS195                         | 42            |

| 8-BIT PARALLEL LOAD SHIFT REGISTER       | LS165                         | 88            |

| 8-BIT SHIFT/STORAGE SHIFT REGISTER       | LS299                         | 137           |

| 8-BIT SERIAL-IN/PARALLEL-OUT SHIFT       |                               |               |

| REGISTER                                 | LS164                         | 49            |

| 8-BIT PARALLEL IN/SERIAL-OUT SHIFT       |                               |               |

| REGISTER                                 | LS166                         | 78            |

| 8-BIT SYNCHRONOUS-LOAD SHIFT             |                               |               |

| REGISTER                                 | LS166                         | 78            |

| 8-BIT SERIAL-IN/SERIAL-OUT SHIFT         | 20,00                         |               |

| REGISTER                                 | LS 91                         | 48            |

|                                          |                               |               |

| * Simplified version of the TTL function |                               |               |

#### Gould AMI Service Makes It Simple

Gould AMI is committed to providing service which makes getting your gate arrays nearly as simple as buying off-theshelf, standard circuits. From your logic description, net list, database tape, or whatever format in which **you** choose to supply us the design information, Gould AMI has proven procedures designed to assure that you'll get circuits on time and that they work the first time.

- You supply **logic** and **specifications** and we'll complete the VLSI implementation for you.

- You supply logic using Gould AMI macros and we'll complete schematic capture, logic simulation, placement and routing, and the fabrication process.

- You do your own schematic capture on any of several Gould AMI approved workstations and give us a net list and we'll complete the process.

- You supply the database tape and we'll fabricate, package and test your gate array circuits.

Regardless of how or at what stage you supply your design data, you can be confident that your completed ICs are only a short time away. Why? Because Gould AMI's entire manufacturing cycle, including planning and tracking procedures, has been developed during 18 years of experience in delivering customized solutions for our customers. Producing small volumes of a large number of different designs is our standard way of doing business.

Our commitment to you won't get lost in the shuffle as is often the case with large producers of commodity circuits. Best yet, you get **service** and Gould AMI's **total MOS/VLSI capability**.

#### You Get State-of-the-Art CMOS Technology

The advanced CMOS process technology used for Gould AMI gate array products offers all of the conventional advantages of CMOS—very low power consumption, broad power supply voltage range, high noise immunity—as well as dense circuits with high performance. Arrays are currently available in 3-micron single and double metal, and in 1985, 2-micron double metal processes.

#### You Get Leading Edge Design Support

Gould AMI's CAD Technology is the most advanced integrated software system for MOS/VLSI circuit design available in the industry. It uses a common database for logic simulation, mask layout and test program generation. The common database approach eliminates errors due to data file transcription steps and allows a gate array design to be converted into a standard cell or a full custom circuit without entering the same logic description again.

The heart of the system is **BOLT**<sup>TM</sup> (Block Oriented Logic Translator) which is a hardware description language and a compiler for the language. It allows the system designer to describe the logic network in a hierarchical fashion due to an unlimited macro nesting capability.

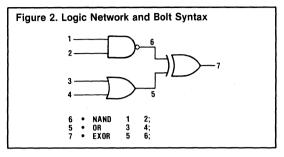

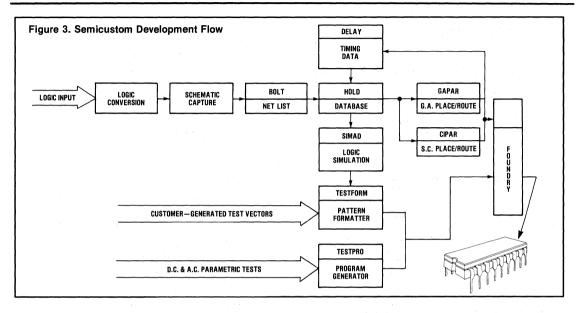

The logic description database is created by compiling a BOLT description of the logic network into the HOLD<sup>TM</sup> (see below) database format. Figure 2 shows a simple logic network and the corresponding BOLT syntax.

HOLD<sup>™</sup> (Hierarchically Organized Logic Database) is created by the BOLT compiler using the Gould AMI macro library and the BOLT description of the circuit. HOLD contains the description of the circuit for Gould AMI CAD programs and is updated after mask layout to include key performance information, e.g. net capacitance after routing.

SIMAD<sup>TM</sup> is an event and table driven, MOS logic simulator that creates a logic model of the circuit to be validated from the HOLD database. Nodes may assume any one of six logic states 0, 1, X, L, H, and Z, thus allowing accurate simulation of transmission gates.

Since each logic device in the model can be assigned propagation delays, SIMAD also allows timing verification, including race detection.

GAPAR<sup>™</sup> is the software package that does automatic placement and routing of arrays. GAPAR will complete at least 98% of the wiring connections on a 100% utilized array. The GAPAR system's correct-by-construction interactive editor can be used to manually connect any unrouted connections or to manually route critical delay paths.

${\rm DELAY^{\rm TM}}$  updates the HOLD database after routing with propagation delay parameters based on actual capacitance data.

TESTFORM<sup>™</sup> generates compressed functional test patterns from the SIMAD logic simulation results.

TESTPRO<sup>™</sup> allows off-line generation of D.C. parametric tests in the Factor<sup>™</sup> test language used in Fairchild test systems. Its output is merged with the compressed functional patterns from TESTFORM, and the result is a test program that can be tailored for use in any Sentry<sup>™</sup> tester.

Gould AMI's software makes it reasonably simple to convert a gate array to a standard cell or full custom circuit, resulting in lower circuit costs when your volume warrants it. Plus you get even more.

- We offer design training classes with full-time instructors.

- Gould AMI has design centers to allow you to do your design with our engineers available to assist you.

- Gould AMI's software is available on a variety of computer systems and workstations.

- Through volume purchase agreements we can help you get discounts on the hardware/software configuration that best fits your needs.

**Gate Arrays**

#### Packages

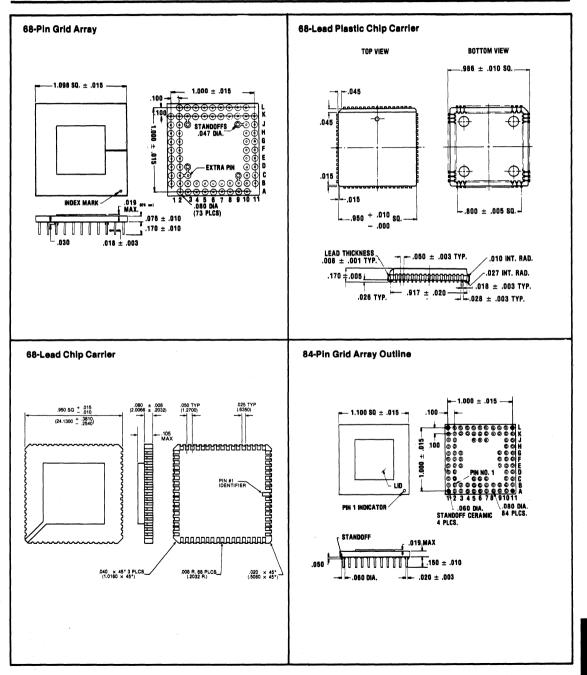

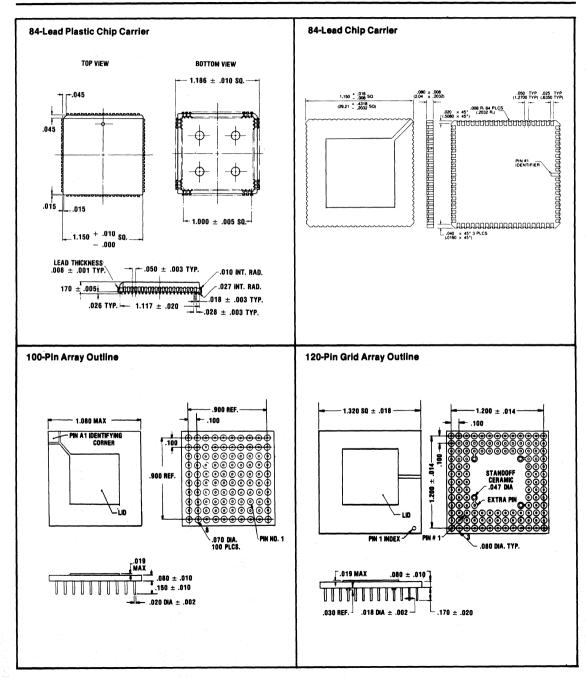

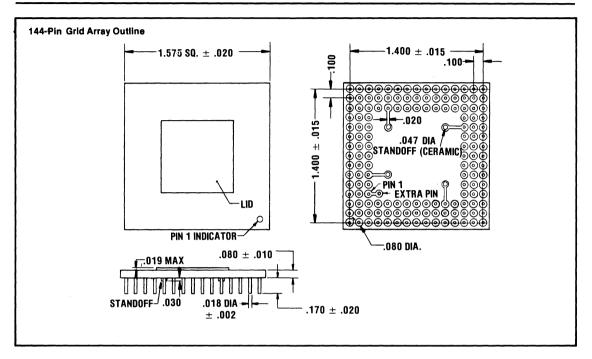

Pinout or lead count varies with die size and array complexity. The arrays are offered in standard plastic and ceramic dual-in-line packages with pin counts ranging from 8 to 64, JEDEC-Standard leadless and leaded chip carriers, miniflat packs to 84 pins, and pin grid arrays to 144 pins. Gould AMI gate array products are also available in wafer or unpackaged die form.

### Table 4. D.C. Electrical Characteristics, 3-Micron Gate Arrays Specified @ $V_{DD} = 5V \pm 10\%$ or $10V \pm 10\%$ , $V_{SS} = 0V$ , $T_A = -55^{\circ}$ to $+125^{\circ}C$

| Symbol          | Parameter                                | V <sub>DD</sub> M | in. Typ.       | Max.            | Units | Conditions                           |

|-----------------|------------------------------------------|-------------------|----------------|-----------------|-------|--------------------------------------|

| V <sub>OL</sub> | Low Level Output Voltage                 |                   |                | 0.05            | V     | $I_{0L} = 1.0 \mu A$                 |

|                 | High Power Output                        | 5                 |                | 0.4             | V     | $I_{01} = 2.4 \text{mA}$             |

|                 | High Power Output                        | 10                |                | 0.5             | . V . | $I_{01} = 4.8 \text{mA}$             |

|                 | Low Power Output                         | 5                 |                | 0.4             | V     | $I_{01} = 0.8 \text{mA}$             |

|                 | Low Power Output                         | 10                | 2              | 0.5             | V     | $I_{OL} = 1.6 \text{mA}$             |

| VOH             | High Level Output Voltage                | V <sub>DD</sub>   | 05             |                 | V     | $I_{OH} = -1.0 \mu A$                |

|                 | High Power Output                        | 5 2               | .4             |                 | V     | $I_{OH} = -1.6 mA$                   |

|                 | High Power Output                        | 10 9              | .5             |                 | V V   | $I_{0H} = -1.0 mA$                   |

|                 | Low Power Output                         | 5 2               | .4             |                 | V     | $I_{OH} = -0.8 mA$                   |

|                 | Low Power Output                         | 10 9              | .5             |                 | V     | $I_{OH} = -0.4 \text{mA}$            |

| VIL             | Input Low Voltage                        | 5 0               | .0             | 0.8             | V     | TTL Input                            |

|                 |                                          | 5 0               | .0             | 1.5             | V     | CMOS Input                           |

|                 |                                          | 10 0              | .0             | 3.0             | V     | CMOS Input                           |

| VIH             | Input High Voltage                       | 5 2               | .0             | V <sub>DD</sub> | V     | TTL Input                            |

|                 |                                          | 5 3               | .5             | V <sub>DD</sub> | V     | CMOS Input                           |

|                 |                                          | 10 7              | .0             | V <sub>DD</sub> | V     | CMOS Input                           |

| IN              | Input Leakage Current                    | 5 -               | -1 orașe de la | 1               | μA    | $V_{IN} = V_{DD} \text{ or } V_{SS}$ |

| I <sub>OZ</sub> | High Impedance Output<br>Leakage Current | 5 –               | 10 0.001       | 10              | μA    | $V_{OH} = V_{DD} \text{ or } V_{SS}$ |

| CIN             | Input Capacitance                        |                   | 5              |                 | pF    | Any Input                            |

#### Table 5. 3-Micron Gate Arrays Typical Performance Data

$V_{DD} = 5.0 \text{ VOLTS}, T_A = 25^{\circ}\text{C}$

|                  | FANOUT |      |       |     |        |       |

|------------------|--------|------|-------|-----|--------|-------|

| INTERNAL LOGIC   | .25pF* | .5pF | .75pF | 1pF | 1.25pF | UNITS |

| INVERTER         | 1.1    | 1.6  | 2.1   | 2.7 | 3.2    | NS    |

| 2-INPUT NAND     | 1.5    | 2.1  | 2.6   | 3.2 | 3.8    | NS    |

| 4-INPUT NAND     | 2.5    | 3.5  | 4.4   | 5.1 | 5.9    | NS    |

| 2-INPUT NOR      | 1.9    | 2.6  | 3.4   | 4.1 | 4.9    | NS    |

| 4 INPUT NOR      | 4.8    | 6.2  | 7.5   | 8.9 | 10.3   | NS    |

| D-TYPE FLIP-FLOP |        | 1    |       |     |        |       |

| CLUCK TO Q       | 3.7    | 4.2  | 4.7   | 5.1 | 5.6    | NS    |

| SET UP TIME      | 2.6    | 2.6  | 2.6   | 2.6 | 2.6    | NS    |

\*Equivalent to one gate-pair load plus 500µm of metal interconnect

| Vnn = | = 5.0 | VOLTS, | T۸ | = | 25°C |

|-------|-------|--------|----|---|------|

|-------|-------|--------|----|---|------|

|                                                                     | C/     | UNITS |          |          |

|---------------------------------------------------------------------|--------|-------|----------|----------|

| INTERFACE LOGIC                                                     | 15pF   | 30pF  | 50pF     | UNITS    |

| CMOS DRIVER                                                         | 4      | 6     | 9        | NS       |

| TTL DRIVER<br>with 2 TTL Loads                                      | 5      | 7     | 10       | NS       |

| TRI-STATE DRIVER<br>with 2 TTL Loads<br>ACCESS TIME<br>DISABLE TIME | 6<br>5 | 8     | 11<br>10 | NS<br>NS |

NOTE: - All propagation delays are the average of high-to-low and low-to-high transitions.

# **Standard Cells Summary**

|   | Introduction                                                        |

|---|---------------------------------------------------------------------|

|   | Benefits                                                            |

|   | Standard Cells at Gould AMI                                         |

|   | Analog Design                                                       |

|   | Macro Cells                                                         |

|   | Standard Cell Design                                                |

|   | Development Flexibility                                             |

|   | Development Cost                                                    |

| 1 | Development Schedule                                                |

|   | $3\mu$ Single-Metal (CCB) HCMOS Standard Cells                      |

|   | 3 $\mu$ Single-Metal, Double-Poly (CCF) HCMOS Analog Standard Cells |

|   | 3µ Double-Metal (CCD) HCMOS Standard Cells                          |

|   | 2μ Double-Metal (CBD) HCMOS Standard Cells                          |

### Introduction

**AMI** Semiconductors

For more than 19 years, Gould AMI Semiconductors has been a leader in the design and manufacture of custom MOS (metal-oxide-silicon) integrated circuits. Today, Gould AMI supports the entire spectrum of custom solutions — gate arrays, standard cell circuits, interactive full custom circuits and circuits fabricated from customer-owned tooling — with a goal of continually reducing the risk, development span and cost of application-specific circuits. In many cases, standard cell circuits represent the optimum solution for a particular application.

#### What are Standard Cells?

Standard cells are circuit "building blocks" which have been previously designed, characterized and stored in a computer data base. These building block cells can range from simple digital circuit elements such as logic gates (AND, NAND, NOR, OR) to more complex digital subsystems such as ALU, UART, CPU, PLA and RAM and ROM memory cells. The cells can also include basic analog circuit elements (operational amplifiers, comparators, etc.), as well as complicated analog subsystems (analog-to-digital converters, switched-capacitor filters, etc.). Both the digital and analog cells are available in a standard cell library to be integrated into various application-specific circuits.

#### How are Standard Cells Used?

Two basic types of circuits can be constructed from a standard cell library. The first type, **automatic standard cell circuits**, utilizes only those cells which exist in the standard cell library. The designer selects the necessary cells from the library and the circuit design is completed by automatically "placing" the cells and "routing" the interconnections between cells.

The second type of standard cell circuit, interactive custom standard cell circuits, is distinguished by either or both of two characteristics: 1) interactive placement and routing, and/or 2) integration of custom circuitry. Interactive layout is used to minimize the die size and/or to optimize overall circuit performance. With this technique, an experienced circuit designer uses an interactive computer-aided design (CAD) system to place the cells and manually route the necessary inter-connections. If specialized functions cannot be efficiently implemented with the available cells or if rigorous performance criteria must be met, custom circuits and content of the second circuit performance circuit and the custom circuit performance circuit performance circuits and the custom circuits of the second circuit performance circuits of the custom circuits of the second circuits of the custom circuits of the custo

cuitry can be used in conjunction with the standard cells to meet the requirements of a given circuit. This integration of custom circuitry with standard cells can be placed and routed interactively or automatically.

### **Benefits**

#### The Custom Advantage