# WINDCREST<sup>®</sup>/McGRAW-HILL

# Programmer's Guide to the AMIBIOS

Includes Descriptions of PCI, APM, and Socket Services BIOS Functions.

American Megatrends, Inc.

Windcrest<sup>®</sup>/McGraw-Hill

New York San Francisco Washington, D.C. Auckland Bogotá Caracas Lisbon London Madrid Mexico City Milan Montreal New Delhi San Juan Singapore Sydney Tokyo Toronto Library of Congress Cataloging-in-Publication Data

ISBN 0-07-001562-7 (p) ISBN 0-07-001561-9 (h)

© Copyright 1993 by American Megatrends, Inc. All rights reserved. Printed in the United States of America. American Megatrends, Inc. 6145F Northbelt Parkway Norcross, GA 30071

This publication contains proprietary information that is protected by copyright. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced, transcribed, stored in a retrieval system, translated to any language or computer language, or transmitted in any form whatsoever without the prior written consent of the publisher.

1234567890 FGR/FGR 99876543

ISBN 0-07-001562-7 (p) ISBN 0-07-001561-9 (h)

#### **Limitations of Liability**

While every precaution has been taken in the preparation of this book, the author and the publisher assume no responsibility for errors or omissions, or for the use made of the material contained herein or any decision based on such use. No warranties are made, express or implied, with regard to the contents of this work, its merchantability, or fitness for a particular purpose. In no event shall the publisher or American Megatrends, Inc. be held liable for any loss, expenses, or damages of any kind whatsoever, whether direct, special, indirect, incidental, or consequential, arising from the use or inability to use the contents of this book.

Printed and bound by Fairfield Graphics.

Information contained in this work has been obtained by McGraw-Hill, Inc., from sources believed to be reliable. However, neither McGraw-Hill nor its authors guarantees the accuracy or completeness of any information published herein and neither McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

## **Table of Contents**

| Preface                                     | . <b>x</b> |

|---------------------------------------------|------------|

| Chapter 1 Introduction                      | . 1        |

| Introducing the BIOS                        |            |

| Parts of the AMIBIOS                        |            |

| Types of BIOS                               |            |

|                                             | • •        |

| Chapter 2 AMIBIOS Features                  | . 9        |

| Standard BIOS Features                      |            |

| AMIBIOS Setup Features                      |            |

|                                             |            |

| Chapter 3 AMI BIOS Setup (Before 2/91)      | . 19       |

| CMOS Setup                                  | . 20       |

| CMOS Setup Options                          | . 21       |

| Advanced ROM Diagnostics                    | . 23       |

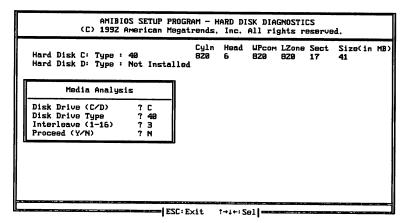

| Hard Disk Diagnostics                       |            |

| Floppy Disk Diagnostics                     |            |

| Keyboard Diagnostics                        |            |

| Video Diagnostics                           |            |

| Miscellaneous Diagnostics                   |            |

|                                             |            |

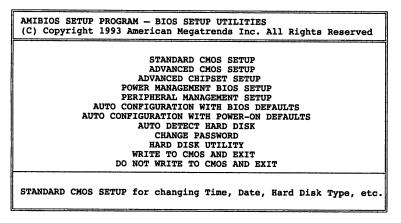

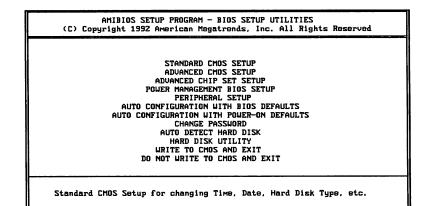

| Chapter 4 Hi-Flex AMIBIOS                   | . 35       |

| Hi-Flex AMIBIOS Setup Options               |            |

| Standard CMOS Setup                         |            |

| Advanced CMOS Setup                         |            |

| Advanced Chipset Setup                      |            |

| Power Management BIOS Setup                 |            |

| Peripheral Management Setup                 |            |

| Auto Configuration with BIOS Setup Defaults |            |

| Auto Configuration with Power-On Defaults   |            |

| Auto Detect Hard Disk                       |            |

| Change Password                             |            |

| Hard Disk Utility                           |            |

| Write to CMOS and Exit                      |            |

| Do Not Write to CMOS and Exit               |            |

| Section 1 Running AMIBIOS Setup             |            |

| Section 2 Standard CMOS Setup               |            |

| Section 3 Advanced CMOS Setup               |            |

| Section 4 Advanced Chipset Setup            | . 55       |

| Section 5 Power Management Setup            |            |

| Section 6 Peripheral Management Setup       |            |

| Section 7 AMIBIOS Password Support          |            |

| Section 8 Hard Disk Utility                 |            |

|                                             |            |

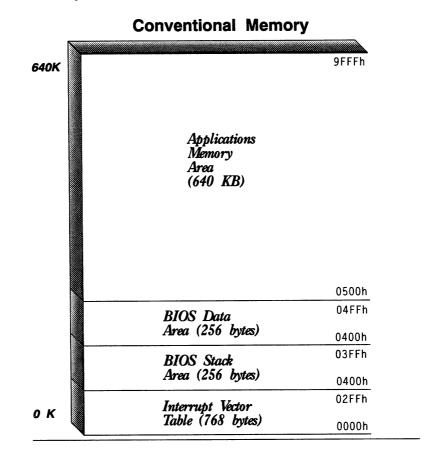

| Chapter 5 System Memory                     | . 99       |

| · · · · · · · · · · · · · · · · · · ·       |            |

| Chapter 6 BIOS Data Area                    | . 101      |

# Table of Contents, Continued

| ROM Compatibility Table       110         Floppy Drive Parameters       111         Hard Disk Parameter Table       115         Hard Disk Drive Types       116         System Configuration Data       119         Chapter 8 CMOS RAM Map       121         Chapter 9 J/O Port Addresses       133         ISA and EISA I/O Port Assignments       135         Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         Adding an Interrupt Routine       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Timer Interrupt (IRQ1)       187         INT 06h Invaid Op Code       185         INT 06h Service       190 <th>Chapter 7 ROM BIOS Data</th> <th></th>                           | Chapter 7 ROM BIOS Data                       |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|

| Hard Disk Parameter Table       115         Hard Disk Drive Types       116         System Configuration Data       119         Chapter 8 CMOS RAM Map       121         Chapter 9 I/O Port Addresses       133         ISA and EISA I/O Port Assignments       135         Video I/O Ports       155         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nomaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 07h Coprocessor Not Available       185         INT 06h Invalid Op Code       185         INT 06h Invalid Op Code                                                                          | ROM Compatibility Table                       |     |

| Hard Disk Drive Types       116         System Configuration Data       119         Chapter 8 CMOS RAM Map       121         Chapter 9 I/O Port Addresses       133         ISA and EISA I/O Port Assignments       135         Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 07h Coprocessor Not Available       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INT 08h Timer Interrupt (IRQ1)       187         INT 08h Timer I                                                          | Floppy Drive Parameters                       |     |

| System Configuration Data       119         Chapter 8 CMOS RAM Map       121         Chapter 9 I/O Port Addresses       133         ISA and EISA I/O Port Assignments       135         Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       185         INT 06h Invalid Op Code       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INT 09h Keyboard Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INT 09h Keybo                                                          | Hard Disk Parameter Table                     |     |

| Chapter 8 CMOS RAM Map       121         Chapter 9 I/O Port Addresses       133         ISA and EISA I/O Port Assignments       135         Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       183         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Pint Screen       185         INT 05h Nonmaskable Interrupt (IRQ0)       186         INT 05h Interrupt (IRQ0)       186         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 07h Coprocessor Not Available       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interr                                                          | Hard Disk Drive Types                         |     |

| Chapter 9 I/O Port Addresses       133         ISA and EISA I/O Port Assignments       135         Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Normaskable Interrupt (NMI)       183         INT 04h Overflow Error       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 09h Keyboard Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INT 00h Divide Service       199         INT 10h Video Service       190         INT 10h Video Service       190         INT 00h Set Video Mode       191         Function 02h Set Cursor Type       192         Function 02h Set Cursor T                                                          | System Configuration Data                     |     |

| ISA and EISA I/O Port Assignments       135         Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 08h Timer Interrupt (IRQ0)       186         INT 08h Timer Interrupt (IRQ1)       187         INT 10h Functions       190         INT 10h Functions       190         INT 10h Functions       190         Function 00h Set Video Mode       191         Function 02h Set Cursor Type       192         Function 02h Set Cursor Type       192 </th <th>Chapter 8 CMOS RAM Map</th> <th> 121</th>                  | Chapter 8 CMOS RAM Map                        | 121 |

| Video I/O Ports       153         Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       185         INT 08h Timer Interrupt (IRQ0)       186         INT 08h Timer Interrupt (IRQ1)       187         INT 09h Keyboard Interrupt (IRQ1)       187         INT 10h Functions       190         INT 10h Functions       190         Function 00h Set Video Mode       191         Function 02h Set Cursor Position       192         Function 02h Set Cursor Position       192         Function 03h Return Cursor Position       193                                                                                     | Chapter 9 I/O Port Addresses                  |     |

| Chapter 10 Power On Self Test       155         AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       185         INT 06h Invalid Op Code       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INT 00h Video Service       190         INT 10h Functions       190         Function 00h Set Video Mode       191         Function 01h Set Cursor Position       192         Function 03h Return Cursor Position       192         Function 03h Return Cursor Position       193                                                                                                                       | ISA and EISA I/O Port Assignments             |     |

| AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 07h Coprocessor Not Available       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INTs 0Ah Through 0Fh Miscellaneous Interrupts       189         INT 10h Video Service       190         INT 10h Functions       190         Function 00h Set Video Mode       191         Function 01h Set Cursor Type       192         Function 01h Set Cursor Position       192 <td< td=""><th>Video I/O Ports</th><td></td></td<>               | Video I/O Ports                               |     |

| AMIBIOS POST Checkpoint Codes       159         Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 07h Coprocessor Not Available       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INTs 0Ah Through 0Fh Miscellaneous Interrupts       189         INT 10h Video Service       190         INT 10h Functions       190         Function 00h Set Video Mode       191         Function 01h Set Cursor Type       192         Function 01h Set Cursor Position       192 <td< td=""><th>Chapter 10 Power On Self Test</th><td></td></td<> | Chapter 10 Power On Self Test                 |     |

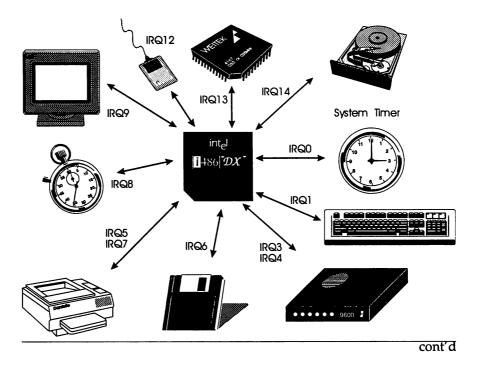

| Chapter 11 Using Interrupts       171         Replacing an Interrupt Routine       177         Adding an Interrupt Routine       177         BIOS Register Conventions       178         Chapter 12 BIOS Software Interrupts       179         BIOS Interrupt Summary       180         BIOS Stack Area       181         INT 00h Divide by Zero       182         INT 01h Single Stepping       182         INT 02h Nonmaskable Interrupt (NMI)       183         INT 03h Breakpoint       184         INT 04h Overflow Error       184         INT 05h Print Screen       184         INT 06h Invalid Op Code       185         INT 08h Timer Interrupt (IRQ0)       186         INT 09h Keyboard Interrupt (IRQ1)       187         INTs 0Ah Through 0Fh Miscellaneous Interrupts       189         INT 10h Video Service       190         INT 10h Functions       190         Function 01h Set Cursor Type       192         Function 02h Set Cursor Position       192         Function 03h Return Cursor Position       193                                                                                                                                                                                                            |                                               |     |

| Replacing an Interrupt Routine177Adding an Interrupt Routine177BIOS Register Conventions178Chapter 12 BIOS Software Interrupts179BIOS Interrupt Summary180BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen185INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                             |     |

| Adding an Interrupt Routine177BIOS Register Conventions178Chapter 12 BIOS Software Interrupts179BIOS Interrupt Summary180BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen185INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |     |

| BIOS Register Conventions178Chapter 12 BIOS Software Interrupts179BIOS Interrupt Summary180BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 01h Set Cursor Type192Function 02h Set Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |     |

| Chapter 12 BIOS Software Interrupts179BIOS Interrupt Summary180BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |     |

| BIOS Interrupt Summary180BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BIOS Register Conventions                     |     |

| BIOS Interrupt Summary180BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chapter 12 BIOS Software Interrupts           |     |

| BIOS Stack Area181INT 00h Divide by Zero182INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |     |

| INT 01h Single Stepping182INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |     |

| INT 02h Nonmaskable Interrupt (NMI)183INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INT 00h Divide by Zero                        |     |

| INT 03h Breakpoint184INT 04h Overflow Error184INT 05h Print Screen184INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INT 01h Single Stepping                       |     |

| INT 04h Overflow Error184INT 05h Print Screen184INT 05h Print Screen185INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INT 02h Nonmaskable Interrupt (NMI)           |     |

| INT 05h Print Screen184INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                             |     |

| INT 06h Invalid Op Code185INT 07h Coprocessor Not Available185INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position193Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |     |

| INT 07h Coprocessor Not Available185INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |     |

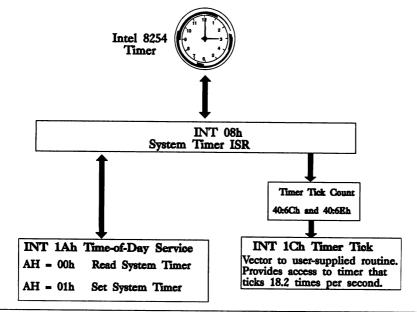

| INT 08h Timer Interrupt (IRQ0)186INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position193Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |     |

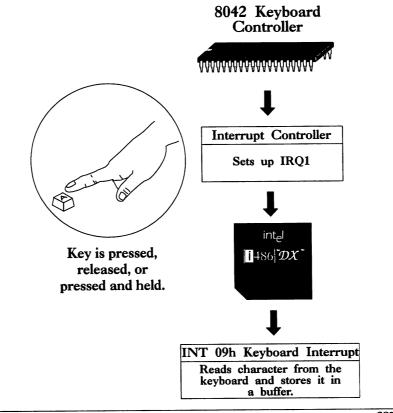

| INT 09h Keyboard Interrupt (IRQ1)187INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                             |     |

| INTs 0Ah Through 0Fh Miscellaneous Interrupts189INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |     |

| INT 10h Video Service190INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |     |

| INT 10h Functions190Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INTS OAN Through OFN Miscellaneous Interrupts |     |

| Function 00h Set Video Mode191Function 01h Set Cursor Type192Function 02h Set Cursor Position192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |     |

| Function 01h Set Cursor Type192Function 02h Set Cursor Position192Function 03h Return Cursor Position193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |     |

| Function 02h Set Cursor Position       192         Function 03h Return Cursor Position       193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |     |

| Function 03h Return Cursor Position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <i>21</i>                                     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |     |

| Function 05h Set Current Video Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |     |

| Function 06h Scroll Text Upward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |     |

| Function 07h Scroll Text Downward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |     |

| Function 08h Return Character or Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |     |

| Function 09h Write Character or Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |     |

#### Chapter 12 BIOS Software Interrupts, cont'd

| INT 10h Video Service, cont'd                                  |       |

|----------------------------------------------------------------|-------|

| Function 0Ah Write Character                                   | 196   |

| Function 0Bh Subfunction 00h Set Palette                       | 197   |

| Function 0Bh Subfunction 01h Set Color Palette                 | 197   |

| Function 0Ch Write Graphic Pixel                               |       |

| Function 0Dh Read Graphic Pixel                                | 198   |

| Function 0Eh Write Character                                   |       |

| Function 0Fh Return Video Display Mode                         |       |

| Function 13h Write Character String                            | 200   |

| INT 11h Equipment List Service                                 | 201   |

| INT 12h Return Memory Size Service                             |       |

| INT 13h Hard Disk Service                                      | 202   |

| Function 00h Reset Disk Drive                                  |       |

| Function 01h Return Hard Drive Status                          |       |

| Function 02h Read Disk Sectors                                 |       |

| Function 03h Write Disk Sectors                                |       |

| Function 04h Verify Disk Sectors                               |       |

| Function 05h Format Disk Cylinder                              |       |

| Function 06h Format Track and Mark Lead Sectors                |       |

| Function 07h Format Entire Disk Starting at Specified Cylinder |       |

| Function 08h Return Disk Parameters                            |       |

| Function 09h Initialize Hard Disk Controller                   | 209   |

| Function 0Ah Read Hard Disk Sectors and Error Correction       |       |

| Codes                                                          | 210   |

| Function 0Bh Write Hard Disk Sectors and Error Correction      |       |

| Codes                                                          |       |

| Function 0Ch Seek Hard Disk Cylinder                           |       |

| Function 0Dh Reset Hard Disk Controller                        |       |

| Function 10h Test Unit Ready                                   | 213   |

| Function 11h Recalibrate Hard Disk                             |       |

| Function 14h Perform Internal Controller Diagnostic            | 214   |

| Function 15h Return Drive Type                                 |       |

| INT 13h Floppy Disk Service                                    | 215   |

| Function 00h Reset Floppy Disk Drive                           |       |

| Function 01h Return Drive Status                               |       |

| Function 02h Read Disk Sectors                                 |       |

| Function 03h Write Disk Sectors                                |       |

| Function 04h Verify Disk Sectors                               | 219   |

| Function 05h Format Disk Track                                 |       |

| Function 08h Return Disk Parameters                            |       |

| Function 15h Return Drive Type                                 | 222   |

| Function 16h Disk Media Change Status                          | . 222 |

| Function 17h Set Floppy Disk Type                              | . 223 |

| Function 18h Set Floppy Disk Type before Format                | . 223 |

|                                                                |       |

| Chapter 12 BIOS Software Interrupts, cont'd                          |

|----------------------------------------------------------------------|

| INT 14h Serial Communications Service                                |

| Function 00h Initialize Serial Port                                  |

| Function 01h Send Character to Serial Port                           |

| Function 02h Receive Character from Serial Port                      |

| Function 03h Return Serial Port Status                               |

| Function 04h Extended Initialize Serial Port                         |

| Function 05h Extended Serial Port Control Subfunction AL = 00h Read  |

| from Modem Control Register                                          |

| Function 05h Extended Serial Port Control Subfunction AL = 01h Set   |

| Modem Control Register                                               |

| INT 15h Systems Services                                             |

| Function 4Fh PS/2 Keyboard Intercept                                 |

| Function 53h Subfunction AL = 00h APM Installation Check 240         |

| Function 53h Subfunction $AL = 01H$ APM Real Mode Interface          |

| Connect                                                              |

| Function 53h Subfunction $AL = 02h APM 16$ -Bit Protected Mode       |

| Interface Connect                                                    |

| Function 53h Subfunction $AL = 03h APM 32$ -Bit Protected Mode       |

| Interface Connect                                                    |

| Function 53h Subfunction $AL = 03$ APM 32-Bit Protected Mode         |

| Interface Connect                                                    |

| Function 53h Subfunction AL = 04h APM Interface Disconnect 246       |

| Function 53h Subfunction AL = 05h CPU Idle                           |

| Function 53h Subfunction AL = 06h CPU Busy                           |

| Function 53h Subfunction AL = 07h Set Power State                    |

| Function 53h Subfunction $AL = 08h$ Enable Power Management 251      |

| Function 53h Subfunction AL = 09h Restore BIOS Power-On Defaults 252 |

| Function 53h Subfunction AL = 0Ah Get Power Status                   |

| Function 53h Subfunction AL = 0Bh Get PM Event                       |

| Function 53h Subfunction AL = 0Ch Get Power State                    |

| Function 53h Subfunction $AL = 0Dh$ Enable Device Power              |

| Management                                                           |

| Function 53h Subfunction $AL = 80h BH = 7Fh APM Installation$        |

| Check (OEM-Defined APM Functions)                                    |

| Function 53h Subfunction $AL = 80h BH = OEM$ -Defined Function       |

| Code                                                                 |

| Function 80h Device Open                                             |

| Function 81h Device Close                                            |

| Function 82h Process Termination                                     |

| Function 83h Event Wait                                              |

| Function 84h Joystick Support                                        |

| Function 85h SysReq Key Handler                                      |

| Function 86h Wait Function                                           |

| Function 87h Move Extended Memory Block                              |

| Function 88h Return Extended Memory Size                             |

| Function 89h Switch to Protected Mode                                |

| Function 90h Device Busy Loop                                        |

| Function 91h Interrupt Complete                                      |

| Function C0h Return Configuration Parameter                          |

| Function C1h Return Address of Extended BIOS Data Area 269           |

| Chapter 12 BIOS Software Interrupts, cont'd                                        |

|------------------------------------------------------------------------------------|

| INT 15h Systems Software Service, cont'd                                           |

| Function C2h PS/2 Mouse Support                                                    |

| Function C2h Subfunction 01h Reset Mouse                                           |

| Function C2h Subfunction 02h Set Sample Rate                                       |

| Function C2h Subfunction 03h Set Resolution                                        |

| Function C2h Subfunction 04h Return Mouse Type 273                                 |

| Function C2h Subfunction 05h Initialize Mouse Interface                            |

| Function C2h Subfunction 06h Mouse Status or Set Scaling 275                       |

| Function C2h Subfunction 07h Set Mouse Handler Address 277                         |

| Function C3h Fail-Safe Timer Control                                               |

| Function D8h EISA Support                                                          |

| Function D8h Subfunction 00h (80h) Read Slot Configuration                         |

| Information                                                                        |

| Function D8h Subfunction 01h (81h) Read Function Configuration                     |

| Information                                                                        |

| Function D8h Subfunction 02h (82h) Clear EISA CMOS RAM 290                         |

| Function D8h Subfunction 03h (83h) Write to EISA CMOS RAM 291                      |

| Function D8h Subfunction 04h (84h) Read Slot Device Compressed ID 298              |

| INT 16h Keyboard Service                                                           |

| Function 00h Read Character                                                        |

| Function 01h Return Keyboard Status                                                |

| Function 02h Return Keyboard Flags                                                 |

| Function 03h Set Typematic Rate Parameters                                         |

| Function 05h Push Character and Scan Code to Buffer                                |

| Function 10h Enhanced Keyboard Read Character                                      |

| Function 11h Enhanced Keyboard Return Status                                       |

| Function 12h Return Enhanced Keyboard Flags                                        |

| Function E0h Subfunction 00h Get Version Number of BIOS/Flash                      |

| ROM Interface                                                                      |

| Function F0h Set CPU Speed       316         Function F1h Read CPU Speed       316 |

| Function F4h Subfunction 00h Read Cache Controller Status 317                      |

| Function F4h Subfunction 00h Read Cache Controller                                 |

| Function F4h Subfunction 02h Disable Cache Controller                              |

| INT 17h Parallel Port Service                                                      |

| Function 00h Write Character                                                       |

| Function 01h Initialize Parallel Port                                              |

| Function 02h Read Parallel Port Status                                             |

| INT 18h ROM BASIC                                                                  |

| INT 19h Bootstrap Loader                                                           |

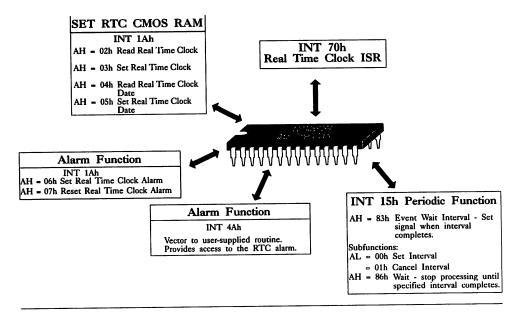

| INT 1Ah Real Time Clock Service                                                    |

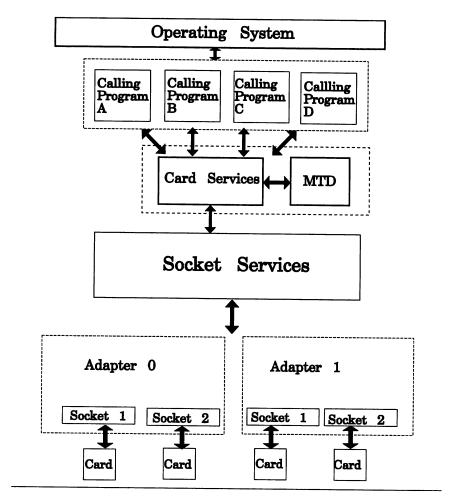

| Socket Services                                                                    |

| Function 00h Return Clock Tick Count                                               |

| Function 01h Set Clock Tick Count                                                  |

| Function 02h Return Current Time                                                   |

| Function 03h Set Current Time                                                      |

| Function 04h Return Current Date                                                   |

|                                                                                    |

# Table of Contents, Continued

#### Chapter 12 BIOS Software Interrupts, cont'd INT 1Ah Real Time Clock Service, c

| h Real Time Clock Service, cont'd                                 |   |

|-------------------------------------------------------------------|---|

| Function 05h Set Current Date                                     | ) |

| Function 06h Set Alarm 339                                        | , |

| Function 07h Reset Alarm 339                                      | , |

| Function 80h Get Adapter Count                                    |   |

| Function 83h Get SS Info 342                                      | 2 |

| Function 84h Inquire Adapter 343                                  |   |

| Function 85h Get Adapter 346                                      |   |

| Function 86h Set Adapter 347                                      |   |

| Function 87h Inquire Window                                       | ) |

| Function 88h Get Window                                           | , |

| Function 89h Set Window 358                                       |   |

| Function 8Ah Get Page                                             |   |

| Function 8Bh Set Page 362                                         |   |

| Function 8Ch Inquire Socket                                       |   |

| Function 8Dh Get Socket                                           |   |

| Function 8Eh Set Socket                                           |   |

| Function 8Fh Get Status                                           |   |

| Function 90h Reset Socket                                         |   |

| Function 95h Inquire EDC                                          |   |

| Function 96h Get EDC                                              |   |

| Function 97h Set EDC                                              | 1 |

| Function 98h Start EDC                                            |   |

| Function 99h Pause EDC                                            |   |

| Function 9Ah Resume EDC                                           |   |

| Function 9Bh Stop EDC                                             |   |

| Function 9Ch Read EDC                                             |   |

| Function 9Dh Get Vendor Info                                      |   |

| Function 9Eh Acknowledge Interrupt                                |   |

| Function 9Fh Get and Set Prior Handler                            |   |

| Function A0h Get and Set SS Addr                                  |   |

| Function A1h Get Access Offset                                    |   |

| Function AEh Vendor-Specific                                      |   |

| Socket Services Error Codes                                       |   |

| Function B1h Subfunction AL = 01/81 PCI BIOS Present              |   |

| Function B1h Subfunction AL = 02/82 Find PCI Device               |   |

| Function B1h Subfunction AL = 03/83 Find PCI Class Code 401       |   |

| Function B1h Subfunction AL = 08/88 Read Configuration Byte 402   |   |

| Function B1h Subfunction $AL = 09/89$ Read Configuration Word 403 |   |

| Function B1h Subfunction $AL = 0A/8A$ Read Configuration          |   |

| Dword 404                                                         |   |

| Function B1h Subfunction AL = 0B/8B Write Configuration           |   |

| Byte                                                              |   |

| Function B1h Subfunction AL = 0C/8C Write Configuration           |   |

| Word                                                              |   |

| Function B1h Subfunction AL = 0D/8D Write Configuration           |   |

| Dword 407                                                         |   |

|                                                                   |   |

### Table of Contents, Continued

| Chapter 12 BIOS Software Interrupts, cont'd   |

|-----------------------------------------------|

| INT 1Bh Ctrl Break 408                        |

| INT 1Ch Periodic Timer Interrupt              |

| INT 1Dh Video Parameter Table                 |

| INT 1Eh Floppy Disk Parameter Table           |

| INT 1Fh Video Graphics Characters             |

| INT 4Ah User Alarm Interrupt                  |

| INT 70h Real Time Clock Interrupt (IRQ8)      |

| INT 71h IRQ9 410                              |

| INT 74h PS/2 Mouse Interrupt (IRQ12)          |

| INT 75h Math Coprocessor Interrupt (IRQ13)    |

| INT 76h Hard Disk Drive Interrupt (IRQ14)     |

| INT 77h Power Down Interrupt (IRQ15)          |

| CI. ( 12 D                                    |

| Chapter 13 Power Management AMIBIOS 413       |

| Chapter 14 EISA Overview                      |

| Chapter 15 8042 Keyboard Controller BIOS 431  |

| Keyboard Controller Functions                 |

| Keyboard Controller and System Interface      |

| Commands to Keyboard Controller               |

| Appendix A AMIBIOS Error Messages 451         |

| Beep Codes                                    |

| AMIBIOS Displayed Error Messages              |

| EISA Error Messages                           |

| ISA NMI Messages                              |

| EISA NMI Error Messages                       |

|                                               |

| Appendix B Upgrading the BIOS 455             |

| Appendix C AMIBIOS History 459                |

| Appendix D AMIBIOS Identification Strings 469 |

| Appendix E Old AMI BIOS POST Checkpoint Codes |

| Acronyms and Abbreviations                    |

| Additional Reading                            |

| Index                                         |

### Preface

*Programmer's Guide to the AMIBIOS* provides extensive technical details about the operation of the BIOS for ISA and EISA systems, specifically the Hi-Flex AMIBIOS. This book does not specifically discuss the IBM BIOS in IBM PC, XT, AT, or PS/2 computers.

#### Organization

| Chapter                                                                                                                                                                             | Contents                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 Introduction<br>Chapter 2 BIOS Features<br>Chapter 3 AMIBIOS Setup (Before 2/91)<br>Chapter 4 Hi-Flex AMIBIOS Setup                                                       | Information useful to the average user<br>of a computer with an AMIBIOS. It is<br>not technically difficult.                                                          |