# ISA and EISA Hi-Flex AMIBIOS Technical Reference

Megatrends

# American Megatrends, Inc.

# **Hi-Flex ISA and EISA AMIBIOS**

# **Technical Reference**

MAN-PR-BIOSTR 8/1/93 © Copyright 1993 American Megatrends, Inc. All rights reserved. American Megatrends, Inc. 6145F North Belt Parkway Norcross, GA 30071

This publication contains proprietary information which is protected by copyright. No part of this publication may be reproduced, transcribed, stored in a retrieval system, translated to any language or computer language, or transmitted in any form whatsoever without the prior written consent of the publisher, American Megatrends, Inc.

#### **Limited Warranty**

No warranties are made, either express or implied, with regard to the contents of this work, its merchantability, or fitness for a particular use.

American Megatrends assumes no responsibility for errors and omissions or for the uses made of the material contained herein or reader decisions based on such use.

#### Limitations of Liability

In no event shall American Megatrends be held liable for any loss, expenses, or damages of any kind whatsoever, whether direct, special, indirect, incidental, or consequential, arising from or arising out of the use or inability to use the contents of this manual.

#### Trademarks

American Megatrends acknowledges the following trademarks:

Intel and Pentium are registered trademarks of Intel Corporation.

AMD is a registered trademark of Advanced Micro Devices, Inc.

Cyrix is a registered trademark of Cyrix Corporation.

DesqView is a registered trademark of Quarterdeck Office Systems, Inc.

MS-DOS, Microsoft Windows, Windows NT, Xenix, and Microsoft are registered trademarks of Microsoft Corporation.

Unix is a registered trademark of American Telephone and Telegraph Company Bell Laboratories. Austek is a trademark of Austek Corporation.

Headland Technologies is a registered trademark of Headland Technologies, Inc.

Weitek is a registered trademark of Weitek Corporation.

IBM, AT, VGA, EGA, XGA, PS/2, MCA, OS/2, and MicroChannel are registered trademarks of International Business Machines Corporation. PC-DOS, XT, and CGA are trademarks of International Business Machines Corporation.

SMC is a registered trademark of SMC Corporation.

Avocet is a registered trademark of Avocet Systems, Inc.

#### **Revision History**

| 4/92<br>10/92     | Initial release.<br>Revised for 6/6/92 core AMIBIOS.                                       |  |

|-------------------|--------------------------------------------------------------------------------------------|--|

| 12/92             | Corrected minor errors.<br>Added APM, PCI, and Socket Service BIOS function documentation. |  |

| 5/24/93<br>8/1/93 | Updated to PCMCIA Version 2.00 Socket Service specifications.                              |  |

# **Table of Contents**

| Chapter 1 Introduc        | tion                                                                               | 1                                      |

|---------------------------|------------------------------------------------------------------------------------|----------------------------------------|

|                           | Parts of the System ROM BIOS                                                       | •••••••••••••••••••••••••••••••••••••• |

|                           | Types of BIOS                                                                      | 7                                      |

|                           | <u>, , , , , , , , , , , , , , , , , , , </u>                                      | /                                      |

| Chapter 2 AMIBIO          | S Features                                                                         | 9                                      |

| -                         | Standard BIOS Features                                                             | ••• >                                  |

|                           | AMIBIOS Setup Features                                                             |                                        |

|                           | AMIBCP-Dependent BIOS Features                                                     | . 14                                   |

|                           |                                                                                    | . 17                                   |

| Chapter 3 System N        | Aemory Map                                                                         | . 31                                   |

| Chapter 4 BIOS Da         | ta Area                                                                            |                                        |

| 1                         |                                                                                    | . 33                                   |

| Chapter 5 BIOS Da         | ta                                                                                 | 30                                     |

|                           | Floppy Disk Drive Parameters                                                       | . 39                                   |

|                           | Hard Disk Parameter Table                                                          | 41                                     |

|                           | Hard Disk Talameter Table                                                          | 45                                     |

|                           | Hard Disk Drive Types                                                              | 48                                     |

| Chapter 6 CMOS R          | AM                                                                                 |                                        |

|                           |                                                                                    | 53                                     |

| Chapter 7 I/O Port        | Addresses                                                                          | 67                                     |

| -                         |                                                                                    | 0/                                     |

| Chapter 8 Power Or        | n Self Test                                                                        | 89                                     |

| -                         | AMIBIOS POST Checkpoint Codes                                                      | 98                                     |

|                           |                                                                                    | 90                                     |

| Chapter 9 Using Int       | errupts                                                                            | 105                                    |

| - 0                       |                                                                                    | 103                                    |

| <b>Chapter 10 BIOS In</b> | terrupts                                                                           | 115                                    |

| -                         | INT 00h Divide by Zero                                                             | 110                                    |

|                           | INT 01h Single Stepping                                                            | 120                                    |

|                           | INT 02h Nonmaskable Interrupt (NMI)                                                | 120                                    |

|                           | INT 03h Breakpoint                                                                 | 120                                    |

|                           | INT 04h Overflow Error                                                             | 121                                    |

|                           | INT 05h Print Screen                                                               | 122                                    |

|                           | INT 06h Invalid Op Code                                                            | 122                                    |

|                           | INT 07h Coprocessor Not Available                                                  | 122                                    |

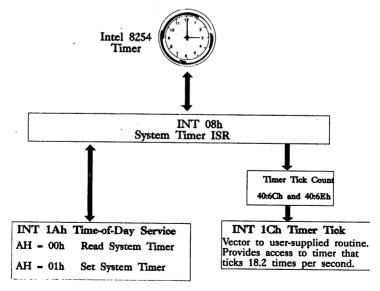

|                           | INT 08h Timer Interrupt (IROO)                                                     | 123                                    |

|                           | INT 08h Timer Interrupt (IRQ0)                                                     | 124                                    |

|                           | INT 09h Keyboard Interrupt (IRQ1)<br>INTs 0Ah Through 0Fh Miscellaneous Interrupts | 125                                    |

|                           | INT 10h Video Service                                                              | 127                                    |

|                           | Function 00b Set Video Mode                                                        | 128                                    |

|                           | Function 00h Set Video Mode                                                        | 129                                    |

|                           | Function 01h Set Cursor Type         Function 02h Set Cursor Position              | 130                                    |

|                           | Function 02h Beturn Cursor Position                                                | 130                                    |

|                           | Function 03h Return Cursor Position                                                | 131                                    |

|                           | Function 04h Return Light Pen Position                                             | 131                                    |

|                           | Function 05h Set Current Video Page                                                | 132                                    |

|                           | Function 06h Scroll Text Upward                                                    | 132                                    |

|                           | Function 07h Scroll Text Downward                                                  | 133                                    |

| Chapter 10 BIOS Interrupts, cont'd         |       |

|--------------------------------------------|-------|

| INT 10h Video Service, cont'd              |       |

| Function 08h Return Character or Attribute |       |

| Function 09h Write Character or Attribute  |       |

| Function 0Ah Write Character               |       |

| Function 0Bh Subfunction 00h Set Palette   | 135   |

| Function 0Bh Subfunction 01h Set Color     |       |

| Palette                                    |       |

| Function 0Ch Write Graphic Pixel           | 136   |

| Function 0Dh Read Graphic Pixel            | 136   |

| Function 0Eh Write Character               | 137   |

| Function 0Fh Return Video Display Mode     | 137   |

| Function 13h Write Character String        | 138   |

| INT 11h Return System Configuration        | 139   |

| INT 12h Return Total Memory Size           | 139   |

| INT 13h Hard Disk Service                  | 140   |

| Function 00h Reset Disk Drive              | 142   |

| Function 01h Return Disk Drive Status      | 143   |

| Function 02h Read Disk Sectors             |       |

| Function 03h Write Disk Sectors            |       |

| Function 04h Verify Disk Sectors           |       |

| Function 05h Format Disk Track             |       |

| Function 06h Format Track and Mark Lead    |       |

| Sectors                                    | 146   |

| Function 07h Format Entire Disk Starting   |       |

| at Specified Cylinder                      | 146   |

| Function 08h Return Disk Parameters        | 147   |

| Function 09h Initialize Hard Disk          |       |

| Controller                                 | 148   |

| Function 0Ah Read Hard Disk Sectors and    |       |

| Error Correction Codes                     | 149   |

| Function 0Bh Write Hard Disk Sectors and   |       |

| Error Correction Codes                     | 150   |

| Function 0Ch Seek Hard Disk Cylinder       | 151   |

| Function 0Dh Reset Hard Disk Controller    |       |

| Function 10h Test Unit Ready               |       |

| Function 11h Recalibrate Hard Disk         | 152   |

| Function 14h Perform Internal Controller   |       |

| Diagnostic                                 | 153   |

| Function 15h Return Drive Type             | 153   |

| INT 13h Floppy Disk Service                | 154   |

| INT 13h Coding Conventions                 | 156   |

| INT 40h Revector for Floppy Functions      | 156   |

| Function 00h Reset Disk Drive              | 156   |

| Function 01h Return Disk Drive Status      |       |

| Function 02h Read Disk Sectors             |       |

| Function 03h Write Disk Sectors            |       |

| Function 04h Verify Disk Sectors           | . 159 |

| Chapter 10 BIOS Interrupts, cont'd                                                    |

|---------------------------------------------------------------------------------------|

| INT 13h Floppy Disk Service, cont'd                                                   |

| Function 05h Format Disk Cylinder                                                     |

| Function 08h Return Disk Parameters 161                                               |

| Function 15h Return Drive Type                                                        |

| Function 16h Disk Media Change Status 163                                             |

| Function 17h Set Floppy Disk Type                                                     |

| Function 18h Set Floppy Disk Type before                                              |

| Format                                                                                |

| INT 14h Serial Communications Service                                                 |

| Serial I/O Ports                                                                      |

| Function 00h Initialize Serial Port 169                                               |

| Function 01h Send Character to Serial Port 171                                        |

| Function 02h Receive Character from                                                   |

| Serial Port                                                                           |

| Function 03h Return Serial Port Status 173<br>Function 04h Extended Initialize Serial |

|                                                                                       |

| Port                                                                                  |

| Subfunction $AL = 00h$ Read                                                           |

| from Modem Control Register 176                                                       |

| Function 05h Extended Serial Port Control                                             |

| Subfunction AL = 01h Write to                                                         |

| Modem Control Register                                                                |

| INT 15h Systems Services                                                              |

| Function 4Fh PS/2 Keyboard Intercept 180                                              |

| Function 53h Subfunction $AL = 00h APM$                                               |

| Installation Check 181                                                                |

| Function 53h Subfunction $AL = 01h APM$                                               |

| Real Mode Interface Connect 182                                                       |

| Function 53h Subfunction $AL = 02h APM$                                               |

| 16-Bit Protected Mode Interface                                                       |

| Connect                                                                               |

| Function 53h Subfunction $AL = 03h APM$                                               |

| 32-Bit Protected Mode Interface                                                       |

| Connect                                                                               |

| Function 53h Subfunction $AL = 03$ APM                                                |

| 32-Bit Protected Mode Interface                                                       |

| Connect                                                                               |

| Interface Disconnect                                                                  |

| Function 53h Subfunction AL = 05h CPU                                                 |

| Idle                                                                                  |

| Function 53h Subfunction AL = 06h CPU                                                 |

| Busy 189                                                                              |

| Function 53h Subfunction $AL = 07h$ Set                                               |

| Power State                                                                           |

| Chapter 10 BIOS Interrupts, cont'd                    |     |

|-------------------------------------------------------|-----|

| INT 15h Systems Services, cont'd                      |     |

| Function 53h Subfunction $AL = 08h$                   |     |

| Enable Power Management                               | 192 |

| Function 53h Subfunction AL = 09h                     |     |

| Restore BIOS Power-On                                 |     |

| Defaults                                              | 193 |

| Function 53h Subfunction AL = 0Ah Get                 |     |

| Power Status                                          | 194 |

| Function 53h Subfunction $AL = 0Bh$ Get               |     |

| PM Event                                              | 195 |

| Function 53h Subfunction $AL = 0Ch$ Get               |     |

| Power State                                           | 196 |

| Function 53h Subfunction AL = 0Dh                     |     |

| Enable Device Power                                   |     |

| Management                                            | 197 |

| Function 53h Subfunction AL = 80h BH =                |     |

| 7Fh APM Installation Check                            |     |

| (OEM-Defined APM Functions)                           | 198 |

| Function 53h Subfunction AL = 80h BH =                |     |

| OEM-Defined Function Code                             |     |

| Function 80h Device Open                              |     |

| Function 81h Device Close                             |     |

| Function 82h Process Termination                      |     |

| Function 83h Event Wait                               |     |

| Function 84h Joystick Support                         |     |

| Function 85h SysReq Key Handler                       |     |

| Function 86h Wait Function                            | 204 |

| Function 87h Move Extended Memory                     | 205 |

| Block                                                 | 205 |

| Function 88h Return Size of Extended                  | 206 |

|                                                       |     |

| Function 89h Switch to Protected Mode                 |     |

| Function 90h Device Busy Loop                         |     |

| Function 91n Interrupt Complete                       | 209 |

| Punction Con Return System Configuration<br>Parameter | 200 |

| Function C1h Return Address of Extended               | 209 |

| BIOS Data Area                                        | 210 |

| Function C2h PS/2 Mouse Support                       |     |

| Function C2h Subfunction 00h Enable or                |     |

| Disable Mouse                                         | 211 |

| Function C2h Subfunction 01h Reset                    |     |

| Mouse                                                 | 212 |

| Function C2h Subfunction 02h Set Sample               |     |

| Rate                                                  | 213 |

| Function C2h Subfunction 03h Set                      |     |

| Resolution                                            | 214 |

|                                                       |     |

.

| Chapter 10 BIOS Interrupts, cont'd       |       |

|------------------------------------------|-------|

| INT 15h Systems Services, cont'd         |       |

| Function C2h Subfunction 04h Return      |       |

| Mouse Type                               | . 214 |

| Function C2h Subfunction 05h Initialize  |       |

| Mouse Interface                          | . 215 |

| Function C2h Subfunction 06h Mouse       |       |

| Status or Set Scaling Factor             | 216   |

| Function C2h Subfunction 07h Set Mouse   |       |

| Handler Address                          | 218   |

| Function C3h Fail-Safe Timer Control     | 219   |

| Function D8h EISA Support                | 220   |

| Function D8h Subfunction 00h (80h) Read  |       |

| Slot Configuration Information           | 221   |

| Function D8h Subfunction 01h (81h) Read  |       |

| Function Configuration                   |       |

| Information                              | 225   |

| Function D8h Subfunction 02h (82h) Clear |       |

| EISA CMOS RAM                            | 231   |

| Function D8h Subfunction 03h (83h) Write |       |

| to EISA CMOS RAM                         | 232   |

| Function D8h Subfunction 04h (84h) Read  |       |

| Slot Device Compressed ID                | 239   |

| INT 16h Keyboard Service                 | 240   |

| Function 00h Read Character              | 240   |

| Function 01h Return Keyboard Status      | 241   |

| Function 02h Return Keyboard Flags       | 241   |

| Function 03h Set Typematic Rate          |       |

| Parameters                               | 242   |

| Function 05h Push Character and Scan     |       |

| Code to Buffer                           | 243   |

| Function 10h Enhanced Keyboard Read      |       |

| Character                                | 243   |

| Function 11h Enhanced Keyboard Return    |       |

| Status                                   | 244   |

| Function 12h Return Enhanced Keyboard    |       |

| Flags                                    | 245   |

| Function F0h Set CPU Speed               |       |

| Function F1h Read CPU Speed              | 246   |

| Function F4h Subfunction 00h Read Cache  |       |

| Controller Status                        | 247   |

| Function F4h Subfunction 01h Enable      |       |

| Cache Controller                         | 248   |

| Function F4h Subfunction 02h Disable     |       |

| Cache Controller                         | 248   |

|                                          |       |

| Chapter 10 BIOS Interrupts, cont'd                  |     |

|-----------------------------------------------------|-----|

| INT 17h Parallel Port Service                       | 249 |

| Function 00h Write Character                        | 249 |

| Function 01h Initialize Parallel Port               | 250 |

| Function 02h Read Parallel Port Status              |     |

| INT 18h ROM BASIC                                   |     |

| INT 19h System Boot Control                         | 252 |

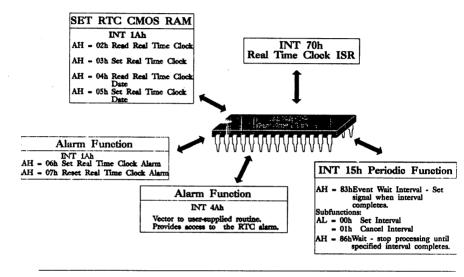

| INT 1Ah Real Time Clock Service                     |     |

| Function 00h Return Clock Tick Count                |     |

| Function 01h Set Clock Tick Count                   | 261 |

| Function 02h Return Current Time                    |     |

| Function 03h Set Current Time                       |     |

| Function 04h Return Current Date                    |     |

| Function 05h Set Current Date                       |     |

| Function 06h Set Alarm                              | 263 |

| Function 07h Reset Alarm                            |     |

| INT 1Ah Socket Services                             | 264 |

| Function 80h Get Adapter Count                      |     |

| Function 83h Get SS Info                            |     |

| Function 84h Inquire Adapter                        |     |

| Function 85h Get Adapter                            |     |

| Function 86h Set Adapter                            | 271 |

| Function 87h Inquire Window                         |     |

| Function 88h Get Window                             |     |

| Function 88h Get Window                             |     |

| Function 89h Set Window                             |     |

| Function 89h Set Window                             |     |

| Function 8Ah Get Page                               |     |

| Function 8Bh Set Page                               |     |

| Function 8Ch Inquire Socket                         |     |

| Function 8Dh Get Socket                             |     |

| Function 8Dh Get Socket                             |     |

| Function 8Dh Get Socket                             |     |

| Function 8Eh Set Socket                             |     |

| Function 8Fh Get Status                             |     |

| Function 90h Reset Socket                           |     |

| Function 95h Inquire EDC                            |     |

| Function 96h Get EDC                                |     |

| Function 97h Set EDC                                |     |

| Function 98h Start EDC       Function 99h Pause EDC |     |

| Function 9Ah Resume EDC                             |     |

| Function 9An Resume EDC                             |     |

| Function 9Ch Read EDC                               |     |

| Function 9Dh Get Vendor Info                        |     |

| Function 9Eh Acknowledge Interrupt                  |     |

| Function 9Fh Get and Set Prior Handler              |     |

| Function A0h Get and Set SS Addr                    |     |

|                                                     |     |

| Chapter 10 BIOS Interrupts, cont'd               |

|--------------------------------------------------|

| INT 1Ah Socket Services, cont'd                  |

| Function A1h Get Access Offset                   |

| Function A1h Get Access Offset                   |

| Function AEh Vendor-Specific                     |

| Socket Services Error Codes                      |

| INT 1Ah PCI Services                             |

| Function B1h Subfunction AL = 01/81 PCI BIOS     |

| Present                                          |

| Function B1h Subfunction AL = 02/82 Find PCI     |

| Device                                           |

| Function B1h Subfunction $AL = 03/83$ Find PCI   |

| Class Code                                       |

| Function B1h Subfunction $AL = 06/86$ Generate   |

| Special Cycle                                    |

| Function B1h Subfunction $AL = 08/88$ Read       |

| Configuration Byte                               |

| Function B1h Subfunction $AL = 09/89$ Read       |

| Configuration Word                               |

| Function B1h Subfunction $AL = 0A/8A$ Read       |

| Configuration Dword 328                          |

| Function B1h Subfunction AL = 0B/8B Write        |

| Configuration Byte                               |

| Function B1h Subfunction $AL = 0C/8C$ Write      |

| Configuration Word                               |

| Function B1h Subfunction $AL = 0D/8D$ Write      |

| Configuration Dword                              |

| INT 1Bh <ctrl> <break></break></ctrl>            |

| INT 1Ch Periodic Timer Interrupt                 |

| INT 1Dh Video Parameter Table                    |

| INT 1Eh Floppy Disk Parameter Table              |

| INT 1Fh Video Graphics Characters                |

| INT 4Ah Alarm ISR 333                            |

| INT 70h Real Time Clock Interrupt (IRQ8)         |

| INT 74h PS/2 Mouse Interrupt (IRQ12)             |

| INT 75h Math Coprocessor Interrupt (IRQ13)       |

| INT 76h AT Hard Disk Drive Interrupt (IRQ14) 335 |

| INT 77h Software Suspend Request (IRQ15) 336     |

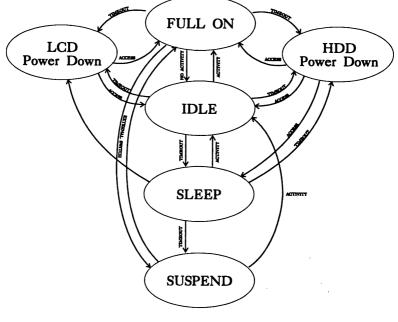

| Chapter 11 Power Management AMIBIOS 337          |

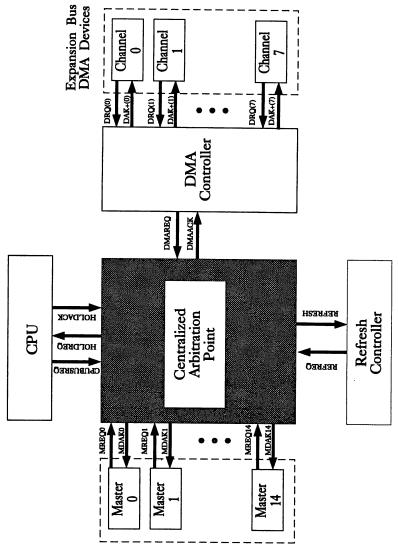

| Chapter 12 EISA Overview                         |

|                                                  |

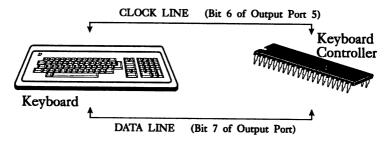

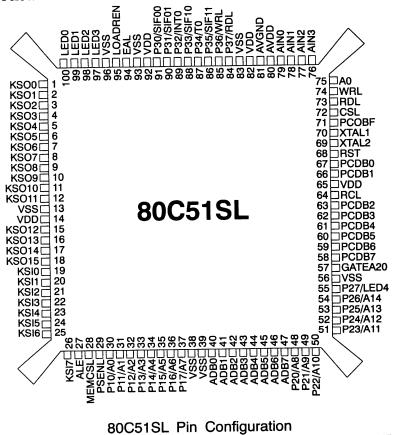

| Chapter 13 Keyboard Controller BIOS 361          |

# Table of Contents, Continued

| Appendix A AMIBIOS Error Messages and Beep Codes | 393 |

|--------------------------------------------------|-----|

| EISA Error Messages                              | 396 |

| ISA NMI Messages                                 | 397 |

| EISA NMI Error Messages                          | 397 |

| Appendix B Upgrading the BIOS                    | 399 |

| Appendix C AMIBIOS History                       | 405 |

| Appendix D Identification Strings                | 417 |

| Glossary                                         | 421 |

| Additional Reading                               | 481 |

| Index                                            | 483 |

#### To the Reader

This manual provides technical details about the operation of the AMIBIOS for ISA and EISA systems. We assume that you are familiar with the Intel x86 architecture, x86 assembler language, and both ISA and EISA system architecture. Common acronyms and abbreviations are listed in the Glossary, which begins on page 421.

#### **Technical Support**

Call American Megatrends Technical Support at 404-246-8600 if you have a problem with any AMIBIOS. The Technical Support Department also operates a Bulletin Board Service. The BBS supplies technical information about all American Megatrends products, including Product Tech Tips, the latest information about chipset-specific BIOS products, and technical documentation.

#### BBS

The American Megatrends BBS permits OEMs, VARs, system integrators, and all customers to access technical information about motherboard, software, and BIOS products. Product Engineering Change Notices, Tech Tips, Technical Notes, and technical manuals are available on the BBS.

#### **Data Transmission Rates**

The BBS automatically handles modems with data transmission rates from 1,200 to 14,400 bps.

If using an HST modem, call 404-246-8780.

If using a non-HST modem, call 404-246-8782.

#### **BBS** Phone Numbers

The following table lists the characteristics of the BBS phone numbers. The BBS requires no parity, 8 data bits, and 1 stop bit.

| Phone Number | Characteristics                                                                                         |  |  |

|--------------|---------------------------------------------------------------------------------------------------------|--|--|

| 404-246-8780 | Supports HST and v.42bis.                                                                               |  |  |

| 404-246-8781 | Supports HST and v.42bis.                                                                               |  |  |

| 404-246-8782 | Dual standard. Can handle 2400 or 9600 bps. Supports v.32bis and v.42bis. Can handle up to 14,400 baud. |  |  |

| 404-246-8783 | Supports v.32bis and v.42bis.                                                                           |  |  |

### Acknowledgments

American Megatrends Senior BIOS engineers Shankar Mandal, Sandip Datta Roy, Sanjeev Kumar, and Debkumar De developed AMIBIOS. Engineers who contributed include Bob Gordon, Jeff Kidd, Charles Hanes, Chip Aaron, John Pennington, Lee Davis, Dick Holmberg, Eddy Quicksall, Will Gysin, Thomas Gilreath, Terry Lauer, Mohan Nair, Sanjay Sehgal, Nandkumar Phadte, and Vivek Saxena. This manual was written by Anindya Mukherjee and Paul Narushoff.

# Chapter 1

# Introduction

The architecture of ISA and EISA systems is layered. The lowest layer is the computer — the hardware itself. The highest layer is the applications software that the user interfaces with. Systems software lies between applications software and hardware.

Systems software can consist of several elements: the operating system kernel, the operating system shell, and additional device drivers. Operating environments (Microsoft® Windows®, for example) exist in a layer between the operating system and applications software, as do multitasking supervisors or DOS extenders like Desqview®.

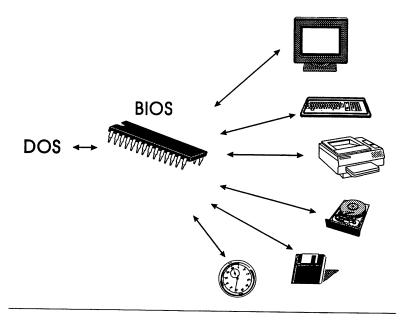

The BIOS (Basic Input/Output System) is a collection of routines between the hardware and the systems software. The BIOS ROM contains hard disk utilities, device drivers, interrupt service routines; and other code and data between the system hardware and the systems software.

### **Types of Systems Discussed**

This manual discusses the AMIBIOS for ISA and EISA systems. These systems contain Intel 80286, 803865X, 80386DX, 80486SX, or 80486DX microprocessors.

It does not discuss IBM® PC, XT<sup>™</sup>, PS/2®, or compatible systems.

# Overview

# In This Chapter

The following topics are discussed in this chapter:

- BIOS as Interface,

- Parts of the ROM BIOS, and

- Types of BIOS.

# The BIOS as Interface

The BIOS is the software layer between the systems software and the hardware in ISA and EISA systems. The BIOS works in two directions.

One part of the BIOS receives and processes requests from programs to perform the standard BIOS I/O services. The mechanism for these requests is called an interrupt, discussed in detail beginning on page 117. Interrupts are invoked by software programs. In an assembler program, the INT mnemonic is followed by an interrupt number that specifies the type of service and a function number that specifies the exact service to be performed. For example:

MOV

AH,00h

; specifies function 00h get ; character from keyboard

INT

16h

; requests INT 16h Keyboard Service

# **BIOS and the Hardware**

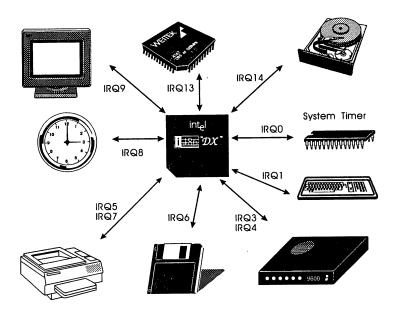

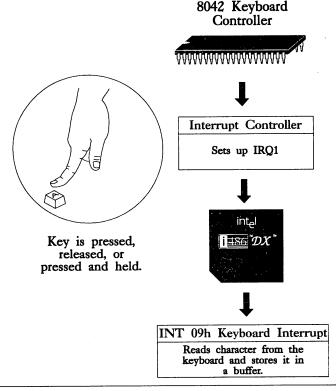

The other side of the BIOS communicates with the hardware (video display, disk drives, keyboard, serial and parallel ports, and so on) in the language and codes used by each device. This side of the BIOS also handles any hardware devicegenerated interrupts. For example, when a key is pressed on the keyboard, a hardware interrupt (IRQ1) is generated. The BIOS INT 09h interrupt service routine is called to handle this interrupt. The following figure illustrates the role that the system BIOS plays.

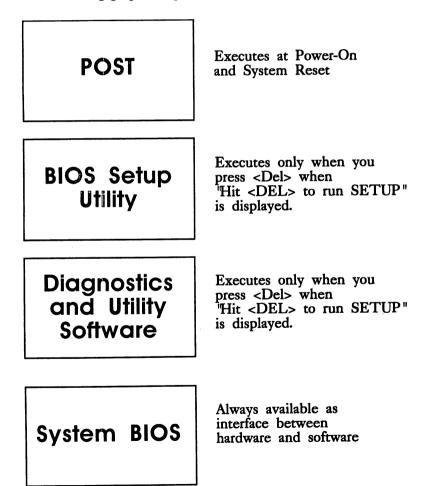

The four system ROM elements in a computer with an AMIBIOS are:

- POST,

- the ROM BIOS itself,

- the hard disk utility programs, and

- the BIOS Setup utility.

The following graphic depicts these elements:

# POST

ROMs includes BIOS Power-On Self Test diagnostic and booting code that tests the system components, initializes certain data structures, and boots DOS. The Power-On Self Test (POST) in the system BIOS performs several functions. POST:

- executes a diagnostic and reliability test of the system, the ROM programs, and system RAM,

- initializes the chips and the standard parts of the computer system and places a record of the system configuration in CMOS RAM and in low system memory,

- sets up the interrupt vector table,

- detects optional equipment in the system, and

- boots the operating system.

BIOS POST is discussed in greater detail beginning on page 90. cont'd

## System BIOS

The BIOS is a part of the code stored in ROM that is in active use the entire time that a computer is on. The ROM BIOS provides the fundamental services needed for the proper operation of the system.

# Hard Disk Utility

The hard disk utilities in the AMIBIOS ROMs include formatting, auto interleave and media analysis.

## **AMIBIOS Setup Utility**

AMIBIOS Setup stores system configuration values in CMOS RAM. The hard disk drive type, type of floppy drives and monitor, and the day, date, and time can be set through Standard CMOS Setup.

Newer versions of the AMIBIOS have Advanced CMOS Setup and Advanced CHIPSET Setup to configure advanced system characteristics, such as RAM and ROM wait states, DMA Clock origination, and memory relocation. In ISA and EISA computers, the types of BIOS (Basic Input Output System) include:

- the system BIOS,

- the video BIOS,

- optional adaptor ROM BIOSes, and

- the keyboard controller BIOS.

This manual describes the system and keyboard controller BIOS features. The video BIOS is best discussed in the context of EGA®, VGA®, and XGA® video standards, which all require a separate BIOS.

## System BIOS

The BIOS tests the system components, loads (bootstraps) the operating system, and remains active for requests by the operating system to activate device drivers that service the hardware components. The BIOS takes the instructions from the operating system and translates these commands to the exact instructions that the hardware itself understands. The BIOS maintains data about various system components. When a component is unable to perform, the BIOS reports it to the operating system.

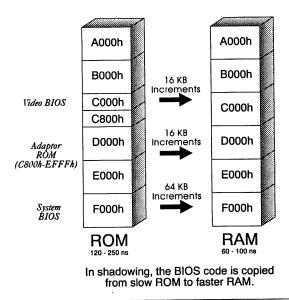

The system ROM BIOS code is 64 KB long and resides at F0000h – FFFFFh in ISA systems. In EISA systems, it is 128 KB long and resides at E0000h – FFFFFh. This area is addressed to ROM but can be shadowed to RAM. ROM operates at about 120 - 180 ns; RAM usually operates at 60 – 100 ns. Shadowing is discussed in detail on page 11.

# Video BIOS

All ISA and EISA systems that use EGA, VGA, or XGA have video BIOSes. The system BIOS video service only handles the most basic video functions. Advanced video modes must be translated via a video BIOS, usually installed on the video adapter card.

# **Keyboard Controller BIOS**

Every ISA and EISA system must also have a keyboard controller BIOS to translate the signals from the keyboard into codes that the BIOS and the system can understand. The keyboard controller BIOS is discussed in detail beginning on page 361.

## Adaptor ROM BIOS

Many adapter cards have code in ROM. For example, ESDI hard disk drive controllers have a ROM that assists in translating this interface to code that the computer can understand and vice versa.

Adaptor ROM resides between C8000h and EFFFFh. This area also can be shadowed in AMIBIOSes to speed the operation of the devices that have adaptor ROMs, provided that the motherboard or chipset used in the system supports adaptor ROM shadowing.

# Chapter 2

# **AMIBIOS Features**

The three types of BIOS features in the AMIBIOS are:

- standard features,

- Setup-dependent features, and

- features dependent on AMIBCP options.

# **Standard BIOS Features**

- automatically detects processor type,

- automatically detects memory size,

- configures non-standard systems,

- supports extended BIOS services,

- supports hardware-specific features,

- peripheral controller support,

- cache controller support,

- parallel and serial port support,

- shadowing,

- diagnostics,

- hard disk utilities, and

- autodetect hard disk.

AMIBIOS Setup features are accessed by pressing Del when

Hit <DEL> if you want to run SETUP (or DIAGS in older BIOS)

# Automatically Detects Processor Type

The BIOS knows whether ar. 80386SX, 80386DX, 80486SX, 80486DX, 80486DX2, Pentium<sup>®</sup>, or other Intel or compatible processor (AMD<sup>®</sup> 386DXL, Cyrix<sup>®</sup> Cx486SLC, Cx486DLC, Cx486S, Cx486S2, or IBM 486SLC or 486SLC2) is present and executes accordingly.

# Automatically Detects Memory Size

AMIBIOS checks system and cache memory and reports the amount on the initial BIOS screen and the BIOS System Configuration Screen. In systems with more than 1 MB, the BIOS reports 384K less RAM than it finds, to account for the address space between 640K and 1024K unavailable to DOS.

# **Configures Non-Standard Systems**

You can configure systems that are missing a keyboard, monitor, or disk drive through AMIBIOS SETUP. Select *Not Installed* as the setting for the missing device in Standard CMOS Setup. All missing device error messages are suppressed, permitting normal boot.

# **Supports Extended BIOS Services**

AMIBIOS includes INT 14h Function 04h Extended Initialize and Function 05h Extended Serial Port Control, a PS/2®compatible BIOS feature.

INT 15h Functions are: C1h and C2h for PS/2-type mouse support, INT 15h Function C3h Fail-Safe Timer Enable, which makes sure a program does not turn off interrupts for too long, INT 15H APM functions, and the EISA AMIBIOS supports INT 15h Function D8h, EISA Configuration (see page 220).

INT 16h support includes several useful functions that no other BIOS has: Function F0h Set CPU Speed, Function F1h Read CPU Speed, Function F4h, Subfunction 00h Read Cache Controller, Subfunction 01h Enable Cache Controller, and Subfunction 02h Disable Cache Controller.

INT 1Ah support includes Card Services, Socket Services, and PCI BIOS functions. Both the ISA and EISA AMIBIOS support the use of hardware interrupt IRQ12 for the mouse.

# Supports Hardware-Specific Features

Many ISA chipsets have paged memory, memory interleaving, EMS support, and power management features. An AMIBIOS for a specific chip must be customized to support some of these features. The BIOS in your computer may have special Setup options to configure these features. You may not be able to access these advanced options, since the manufacturer can customize BIOS Setup to automatically configure them.

# **Peripheral Controller Support**

AMIBIOS has built-in support for National Semiconductor® PC87310, PC87311, and PC87312, C&T® 82C710, 82C711, 82C712, 82C721, and 82C725, VLSI® 82C106 and 82C107, Intel® 82341, and other peripheral controllers.

# **Cache Controller Support**

AMIBIOS has built-in support for Intel C6, Headland Technologies<sup>®</sup> HT44, Austek, and other standalone cache memory controllers. Many chipsets have integrated cache controllers.

# Parallel and Serial Port Support

AMIBIOS supports up to four serial ports and four parallel ports. The fourth parallel port is not supported if PS/2-type mouse support is enabled.

# Shadowing

Shadowing copies the BIOS from ROM to RAM to improve system performance. In a system with no shadow option, the ROM BIOS is executed from relatively slow ROM (150 - 250 ns). The BIOS executes much faster when the ROM BIOS is copied to RAM (60 - 100 ns) and the system is instructed to access the BIOS from RAM. In most cases, system BIOS shadowing should never be turned off.

# System BIOS ROM Shadowing

The system BIOS resides in the 64 KB address space between F0000h and FFFFFh in ISA systems (and in the 128 KB space between E0000h and FFFFFh in EISA systems). The system BIOS shadow feature is often automatically enabled by the AMIBIOS. If not, it is an option on Standard CMOS Setup or Advanced CMOS Setup screens that should always be enabled to enhance BIOS performance.

# High Memory

# Adaptor ROM Shadow

The area between C8000h and EFFFFh in ISA systems (and C8000h – DFFFFh in EISA systems) is available for use by other ROM devices. Often, the hard disk drive controller ROM is stored here. Many network cards also use this space. AMIBIOS allows this area to be shadowed from ROM to RAM to speed access to the code in this area.

# EGA and VGA RAM Shadow

Video ROM shadowing can often speed execution in two ways: running the video BIOS from 16-bit instead of 8-bit memory, and running the video BIOS from fast RAM instead of relatively slow ROM.

The memory space from C0000h – C7FFFh is reserved for video ROM. Often, only the EGA BIOS (C0000h - C3FFFh), accessed through an 8-bit bus, is located in this area. The relatively slow execution of this device driver from ROM makes the video I/O slow. AMIBIOS allows you to map this space to system RAM, where it executes about twice as fast.

Video ROM shadowing copies the video ROM from C0000h-C7FFFh to RAM. Memory from C0000h – DFFFFh can be accessed on the 16-bit expansion slot. Any 8-bit I/O memory in that space is automatically disabled.

# Diagnostics

Older AMIBIOS included hardware diagnostic routines. All recent AMIBIOS include only hard disk drive utilities.

# Hard Disk Utilities

The Hi-Flex AMIBIOS, available since early 1991, provides several hard disk utilities, including format, auto interleave, and media analysis.

# Autodetect Hard Disk

AMIBIOS Setup in newer AMIBIOS products reads and reports configuration information for SCSI, IDE, and other non-ST512 hard disk drives.

The following AMIBIOS Setup utility features are only available in the Hi-Flex AMIBIOS (available since early 1991) with Advanced CMOS Setup.

| Type of Feature | Setup Options                                                                                                                                                                                                                                                          |   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Memory Features | Above 1 MB Memory Test                                                                                                                                                                                                                                                 |   |

|                 | Executes the POST memory routines on the RAM above 1 MB (if present on the system). If disabled, the BIOS only checks the first 1 MB of RAM.                                                                                                                           |   |

|                 | Memory Test Tick Sound                                                                                                                                                                                                                                                 |   |

|                 | Turns the ticking sound on or off.                                                                                                                                                                                                                                     |   |

|                 | Memory Parity Error Check                                                                                                                                                                                                                                              |   |

|                 | Enables or disables parity error checking for all system RAM.                                                                                                                                                                                                          |   |

|                 | Hard Disk Type 47 RAM Area                                                                                                                                                                                                                                             |   |

|                 | Specifies the type 47 data storage area – 0:300h in low<br>system RAM or in the top 1 KB of memory, starting a<br>address 639K or 511K (depending on the amount of<br>base memory). Type 47 data is stored in shadow RAM<br>shadowing is enabled.                      | t |

|                 | Fast Gate A20 Option                                                                                                                                                                                                                                                   |   |

|                 | Fast Gate A20 is a hardware circuit that enables Gate A20 faster. The BIOS controls access to this circuitry. Address Gate A20 in the Intel x86 architecture controls access to memory addresses above 1 MB by enabling disabling access to processor address line 20. |   |

|                 | Some programs both enter protected mode and use the CMOS RAM Shutdown byte to return to real mode through the BIOS. For these programs, Gate A20 must be constantly enabled and disabled by the keyboard controller, which is a slow process.                          |   |

# AMIBIOS Setup Features, Continued

| Type of Feature                     |   | Setup Options                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Memory<br>Control             | - | <b>Internal Cache Memory</b> appears only on 80486-based systems. It enables or disables access to the 8 KB internal cache in the microprocessor.                                                                                                                                                              |

|                                     | • | <b>External Cache Memory</b> appears only on systems that<br>have a caching scheme external to the CPU. This option<br>enables or disables the testing and autosizing of cache<br>memory in POST.                                                                                                              |

| Keyboard and<br>Mouse Control       | • | Typematic Rate Programming                                                                                                                                                                                                                                                                                     |

| Features                            |   | Typematic Rate Programming enables or disables the Typematic Rate Delay and Typematic Rate options.                                                                                                                                                                                                            |

|                                     | - | Typematic Rate Delay (milliseconds) and<br>Typematic Rate (Characters per Second)                                                                                                                                                                                                                              |

|                                     |   | Typematic Rate Delay and Typematic Rate control the<br>speed at which a keystroke is repeated. The character<br>associated with the keystroke is repeatedly displayed<br>when a key is pressed and held down. After the<br>Typematic Rate Delay, the character repeats at a rate set<br>by the Typematic Rate. |

|                                     | - | System Boot Up Num Lock                                                                                                                                                                                                                                                                                        |

|                                     |   | You can turn off the Num Lock function when the system is powered on. You can use both sets of arrow keys on the keyboard when the Num Lock function is turned off.                                                                                                                                            |

|                                     | - | Mouse Support Option                                                                                                                                                                                                                                                                                           |

|                                     |   | Enables support for a PS/2-type mouse or pointing<br>device. If this option is disabled, the BIOS does not<br>reserve the top 1 KB of the DOS applications area<br>memory (639K or 511K depending on the amount of<br>base memory) for the extended BIOS Data Area.                                            |

| Message Display<br>Control Features | • | Hit <del> Message Display</del>                                                                                                                                                                                                                                                                                |

|                                     |   | Disabling this option prevents <i>Hit <del> to run Setup</del></i> , from appearing when the system boots.                                                                                                                                                                                                     |

|                                     | - | Wait for <f1> if Any Error</f1>                                                                                                                                                                                                                                                                                |

|                                     |   | Disabling this option eliminates the need for user responses to Press $\mathbb{F}1$ to continue.                                                                                                                                                                                                               |

| Type of Feature    |   | Setup Options                                                                                                                           |

|--------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------|

| Coprocessor Enable |   | Numeric Processor                                                                                                                       |

| Features           |   | Enable BIOS testing for a math coprocessor.                                                                                             |

|                    | - | Weitek® Processor                                                                                                                       |

|                    | } | Enable BIOS testing for a Weitek math coprocessor.                                                                                      |

| Boot Up Options    |   | Floppy Drive Seek at Boot                                                                                                               |

|                    |   | This option performs a Seek on drive A: at system boot.<br>The default is Disabled for a faster boot.                                   |

|                    | - | System Boot Up Sequence                                                                                                                 |

|                    |   | The system can boot first from drive A: or drive C:.                                                                                    |

|                    | • | System Boot Up Speed                                                                                                                    |

|                    |   | Sets the speed at which the system boots.                                                                                               |

| Speed Control      | • | Turbo Switch Function                                                                                                                   |

|                    |   | Enables the system turbo (processor speed switching) switch, if this switch is supported in hardware.                                   |

| Security Features  | • | Password Check Option                                                                                                                   |

|                    |   | The password option prevents unauthorized system boot or AMIBIOS Setup use.                                                             |

|                    | - | <b>Boot Sector Virus Protection</b>                                                                                                     |

|                    |   | Newer AMIBIOS products automatically report when<br>any program attempts to format or write to the boot<br>sector on a hard disk drive. |

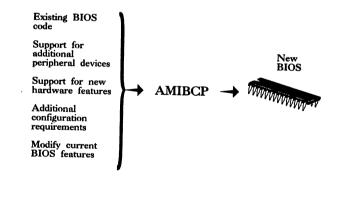

The Hi-Flex AMIBIOS has many other features that are actually options set by the system manufacturer via AMIBCP (BIOS Configuration Program). This BIOS has been available since early 1991.

Before AMIBCP, most AMIBIOS features had to be individually customized by American Megatrends. With AMIBCP, the system manufacturer can customize the BIOS, resulting in much faster system development and a much greater degree of freedom in adding or changing system features.

AMIBCP controls which of the five Setup screens appear on the Setup menu, the options that appear in the Setup menus, and the settings that each option can be configured to. AMIBCP configures the implementation of processor speed switching, cache memory control, the turbo switch option, and cache memory controller implementation, as well as many other BIOS features. The following graphic illustrates how AMIBCP is used.

# AMIBCP Options that affect BIOS Setup Options

The following BIOS features can be configured or disabled by the OEM or system manufacturer through AMIBCP:

- Halt on Error During POST,

- Initialize CMOS RAM at Every Boot,

- Keyboard Controller Output Pin 23, 24 Blocked,

- Mouse Support in BIOS and Keyboard Controller,

- Wait for <F1> In Case of POST Error,

- Display Floppy Error During POST,

- Display Video Error During POST, and

- Display Keyboard Error During POST.

The following BIOS features appear on the AMIBIOS Setup menu screen. All options may not appear in the AMIBIOS Setup utility screen in your computer because they can be turned on and off by the OEM before the system is sold. Some of the above options are only implemented in certain types of systems. For example, the *Power Management BIOS Setup Option* only appears in battery-backed portable, notebook, handheld, and other computers that have power management features.

- CMOS Setup Option,

- Advanced CMOS Setup Option,

- Advanced CHIPSET Setup Option,

- Power Management BIOS Setup Option,

- Peripheral Setup Option,

- BIOS Setup Defaults Auto Configuration Option,

- Power-On Defaults Auto Configuration Options,

- Change Password Options, and

- Hard Disk Utility Option.

# Speed Selector and Cache Enable Keychord

You can define any unused keystroke combination (keychord) using AMIBCP to configure keyboard speed switching and enable or disable cache memory via a keychord. The following table shows the default settings.

| Feature                                                                        | Default Keychord                                           |

|--------------------------------------------------------------------------------|------------------------------------------------------------|

| High speed                                                                     | <ctrl><alt><gray +=""></gray></alt></ctrl>                 |

| Low speed                                                                      | <ctrl><alt><gray -="">.</gray></alt></ctrl>                |

| Enable cache memory <ctrl><alt><shift> <gray +=""></gray></shift></alt></ctrl> |                                                            |

| Disable cache memory                                                           | <ctrl><alt><shift> <gray -=""></gray></shift></alt></ctrl> |

### Software I/O Delay

If the software delay is 0 (the default value), it specifies a fixed delay of 15  $\mu$ seconds. It can be set anywhere from 0 to 255 units. Each nonzero unit adds a fixed delay value to the processor speed. This option may be set as follows:

| If the system speed is | select |

|------------------------|--------|

| 16                     | 10     |

| 20                     | 12     |

| 25                     | 14     |

| 33                     | 18     |

#### **Power-On Delay**

This option specifies a short delay when power is turned on to allow the power supply output to stabilize. This parameter can be set to 0 - 255 seconds. The default is 0 seconds in an AMIBIOS based on the 6/6/92 core BIOS and 2 seconds in an AMIBIOS based on the 12/12/91 core BIOS.

## **Refresh Value**

This is the value used to program the refresh timer. This parameter sets the refresh value for system RAM. The default is 18, which translates to 15  $\mu$ seconds. The range of values is 0 – 255.

# Serial and Parallel Ports 1 – 4

Any of the I/O ports can be set to a beginning I/O port address defined by the OEM. The range of valid values is from 00000h - FFFFFh. The default starting I/O ports are:

| Port            | Default Starting I/O Port |

|-----------------|---------------------------|

| Serial Port 1   | 3F8h                      |

| Serial Port 2   | 2F8h                      |

| Serial Port 3   | 3E8h                      |

| Serial Port 4   | 2E8h                      |

| Parallel Port 1 | 3BCh                      |

| Parallel Port 2 | 378h                      |

| Parallel Port 3 | 278h                      |

| Parallel Port 4 | None                      |

Parallel Port 4 is not supported if PS/2-type mouse support is enabled.

# Speed Switching, Turbo Switch, Cache Control

Four BIOS features are implemented via 8042 pins, chipsetspecific internal registers, or I/O ports. The following table lists these BIOS features and the possible methods used to implement the feature via AMIBCP. A discussion of the specific means of implementation follows this table.

| Feature                    | 8042 pin | Internal<br>registers | I/O Ports |

|----------------------------|----------|-----------------------|-----------|

| Clock Switching            | Yes      | Yes                   | Yes       |

| Cache Control              | Yes      | Yes                   | Yes       |

| Turbo Switch<br>Input Pin  | Yes      | No                    | No        |

| Memory<br>Controller Reset | Yes      | No                    | No        |

# Implementation Methods Are Not Mutually Exclusive

If a keyboard pin implements processor speed switching, another keyboard pin can be used to implement cache control, or turbo switch, or memory controller reset.

If special I/O ports are used to implement speed switching, other I/O ports can also be used to implement cache control.

# **Using Internal Registers**

If processor speed switching or cache control is implemented via internal registers, the implementation method must be specific to the system architecture and to the particular chipset used in the system.

# **Processor Speed Switching**

Systems using the Hi-Flex AMIBIOS allow the end user to change the processor speed using the keychord <Ctrl> <Alt> <Gray +> (low to high) and <Ctrl> <Alt> <Gray -> (high to low). These default keychords and the transitions they cause can be changed using AMIBCP.

A *speed switching method* must be specified in AMIBCP for the BIOS to recognize that a keychord causes a speed change. AMIBCP supports three speed switching methods. Any deviations from these methods may require BIOS customization. These methods are:

- using an 8042 pin,

- using internal registers, or

- using I/O ports.

Any of these three methods can be used to implement processor speed switching in a system with an AMIBIOS.

# Processor Speed Switching Via an 8042 Pin

If the system has a Keyboard Controller AMIBIOS (version F or later), speed switching can be implemented using an 8042 pin to toggle the clock speed. The options:

|          | No Speed switching through Keyboard Controller |

|----------|------------------------------------------------|

| <b>—</b> | Pin 23, 24 High means High Speed               |

|          | Pin 23, 24 Low means High Speed                |

|          | Pin 23 High means High Speed                   |

|          | Pin 23 Low means High Speed                    |

|          | Pin 24 High means High Speed                   |

|          | Pin 24 Low means High Speed                    |

|          | Pin 27 High means High Speed                   |

| •        | Pin 27 Low means High Speed                    |

|          | Pin 28 High means High Speed                   |

|          | Pin 28 Low means High Speed                    |

|          | Pin 29 High means High Speed                   |

| •        | Pin 29 Low means High Speed                    |

|          | Pin 30 High means High Speed                   |

|          | Pin 30 Low means High Speed                    |

# 8042 Pin — Method of Operation

If No Speed switching through Keyboard Controller is chosen, the BIOS does not recognize any keychord to toggle system speed through the keyboard controller. If one of the fourteen pin options is chosen, the BIOS toggles the voltage level of the chosen pin. The voltage level change switches the system speed if the appropriate hardware is implemented on the motherboard.

For example, if *Pin 23 High means High Speed* is chosen, the BIOS toggles the voltage level of 8042 pin 23 when the processor speed switching keychord is pressed. If the pin level is High, the speed is set High. If the pin level is Low, the speed is set to Low. 8042 Pins 23, 24, 27, or 28 cannot be used if the BIOS has PS/2 mouse support.

#### **Processor Speed Switching Via Internal Registers**

Some chipsets allow speed switching to be implemented via chipset registers. The routine to toggle the speed is activated within the BIOS. The speed switching keychord toggles the system speed. This method can be enabled or disabled through AMIBCP.

#### Processor Speed Switching Via I/O Ports

Speed switching can also be accomplished using specially designated port address(es) via AMIBCP. To use this method, the port addresses, port data values, and port mask values must be specified for both the high and low speed.

The port value is read and ANDed with the mask value. The new value is ORed with the data value. The final value is written back to the port.

### Processor Speed Switching Via I/O Ports, cont'd

#### Example

Assume the port address for high speed is 1234h. Bit 7 of the value read should be 0 to toggle the speed Low. When the speed switching keychord is pressed, the BIOS reads the port value as FFh.

The mask value is ANDed with the port value (7Fh). The new value is 7Fh.

Bit 7 is now 0. The BIOS ORs the I/O port contents with the data value (00h), producing a final value (7Fh) that is written back to port 1234h. The speed toggling hardware knows that bit 7 set to 0 means Low speed.

### **Assumed Speed Switching Conditions**

It is assumed that the decoding circuitry and the functional toggling circuitry are provided on the motherboard. The BIOS reads and writes to the specified ports when the speed switching keychord is pressed. The actual speed change circuitry must be implemented in the motherboard design.

Both High speed and Low speed I/O ports should allow read and write operations and are limited to a four-digit hex address.

cont'd

#### **Cache Control Options**

Systems using the Hi-Flex AMIBIOS allow the end user to enable or disable the system cache memory using the keychord <**Ctrl>** <**Alt>** <**Shift>** <**Gray +>** (disabled to enabled) and <**Ctrl>** <**Alt>** <**Shift>** <**Gray ->** (enabled to disabled). These default keychords and the transitions they cause can be changed using AMIBCP.

For the BIOS to recognize that a keychord causes a cache enable or disable change, a *cache control method* must be specified, and the OEM can choose a method via AMIBCP. Three methods are supported in AMIBCP. Any deviations from these methods may require BIOS customizations. These methods are:

- a pin on the 8042 keyboard controller,

- chipset internal registers, or

- specially assigned I/O ports.

#### Cache Control Options, cont'd

#### Using a Pin on the 8042 Keyboard Controller

If the system has a Keyboard Controller AMIBIOS (version F or later), cache control can be implemented via an 8042 pin for the cache memory status. The options are:

- No Cache Control through Keyboard Controller

- Pin 23, 24 High means Cache ON

- Pin 23, 24 Low means Cache ON

- Pin 23 High means Cache ON

- Pin 23 Low means Cache ON

- Pin 24 High means Cache ON

- Pin 24 Low means Cache ON

- Pin 27 High means Cache ON

- Pin 27 Low means Cache ON

- Pin 28 High means Cache ON

- Pin 28 Low means Cache ON

- Pin 29 High means Cache ON

- Pin 29 Low means Cache ON

- Pin 30 High means Cache ON

- Pin 30 Low means Cache ON

If No Cache Control through Keyboard Controller is chosen, the BIOS does not recognize any keychord to toggle the cache memory status. If an 8042 pin option is chosen, the BIOS toggles the voltage level of the chosen pin. The different pin voltage levels change cache memory status, provided the appropriate hardware is implemented on the motherboard.

For example, if *Pin 23 High means Cache ON* is chosen, the BIOS toggles the voltage level of 8042 pin 23 when the cache control keychord is pressed. If the pin level is High, cache is enabled. If the pin level is Low, cache is disabled. Pins 23, 24, 27, or 28 cannot be used if PS/2-type Mouse Support is present in the BIOS.

cont'd

#### Cache Control Options — Using Internal Registers

Some chipsets permit cache control to be implemented via registers internal to the chipset. If this method is chosen, the routine to toggle the cache is activated inside the BIOS. The appropriate keychord toggles the cache status. This method is enabled via AMIBCP.

#### Using I/O Ports

Cache control can also be implemented via designated I/O port addresses. To use this method, the port addresses, port data values, and port mask values must be specified for both cache enable and cache disable. The port value is read and ANDed with the mask value. The new value is ORed with the data value. The final value is written back to the port.

#### Example

The port address for cache enabled is 1234h. To disable cache, bit 7 of the value read should be 0.

When the cache disable keychord (usually **Ctrl** Alt **Shift** -) is pressed, the BIOS reads the port value as FFh. The mask value is ANDed with the port value (7Fh). The new value is 7Fh. This makes bit 7 equal to 0. Now the BIOS ORs the contents of the I/O port and the data value (00h). The final value (7Fh) is written to port 1234h. The cache status hardware knows that bit 7 set to 0 means cache disabled.

#### Cache Memory Enable Hardware Must be Present

The cache memory enable decoding circuitry and functional toggling circuitry must be present on the motherboard. The BIOS reads and writes to the specified ports when the cache control keychord is pressed. The cache memory status must be implemented in the motherboard design. Both cache enable and disable I/O ports should allow read and write operations and are limited to a four-digit hex address.

#### **Turbo Switch 8042 Pin Options**

Systems using the Hi-Flex AMIBIOS support a turbo switch that allows you to toggle the system speed. If the system has an American Megatrends Keyboard Controller BIOS (version F or later), the system speed can be toggled via an 8042 pin. If the CPU is in protected mode, (most probably because QEMM, Microsoft Windows, DesqView, or EMM386 is running), the turbo switch operation is automatically disabled to prevent conflicts.

The Turbo Switch 8042 Pin options are:

- No Turbo Switch Input Pin through Keyboard Controller

- Pin 27 High means High Speed

- Pin 27 Low means High Speed

- Pin 28 High means High Speed

- Pin 28 Low means High Speed

- Pin 29 High means High Speed

- Pin 29 Low means High Speed

- Pin 30 High means High Speed

- Pin 30 Low means High Speed

- Pin 31 High means High Speed Pin 31 Low means High Speed

- Pin 33 High means High Speed

- Pin 33 Low means High Speed

If No Turbo Switch Input Pin through Keyboard Controller is chosen, the BIOS notes which keyboard controller pin is chosen as the turbo pin and continually monitors this pin. When the pin status changes, the BIOS switches the processor speed.

For example, if Pin 28 High means High Speed is chosen, the BIOS monitors the voltage level of 8042 pin 28 constantly. When the turbo switch is pressed, it changes the processor speed. If the pin level is High, the speed is set High. If the pin level is Low, the speed is set to Low.

#### Note: Pins 27 and 28 cannot be used if PS/2-type Mouse Support is enabled. Of course, the same 8042 pin cannot be used for speed switching or cache control.

cont'd

#### **Memory Controller Reset Options**

The Intel 82335SX chipset requires that the memory controller be reset every time the system is rebooted. Memory controller reset can be implemented via the AMIBIOS using an 8042 pin.

This option can be used if the system has an American Megatrends Keyboard Controller BIOS (version F or later). The three options are:

- No Reset Available through Keyboard Controller

- Reset through Pin 23

- Reset through Pin 24

If No Reset Available through Keyboard Controller is chosen, the only way to reset the memory controller chip is to physically power down the system.

If an 8042 pin option is chosen, the BIOS toggles the voltage level of the 8042 pin and the memory controller is reset, permitting continued operation.

For example, if *Reset through Pin 23* is chosen, the BIOS toggles the voltage level of pin 23 of the 8042.

Note: An 8042 pin cannot be used for memory controller reset if PS/2-type mouse support is present in the BIOS. Also, the same 8042 pin cannot be used for memory controller reset and speed switching or cache control.

# **Chapter 3**

# **System Memory Map**

The following table shows the use of the first megabyte of memory.

| Address Range    | Length    | Description                                                                                                                                                                                                    |

|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000000 - 0002FFh | 768 bytes | BIOS Interrupt Vector Table                                                                                                                                                                                    |

| 000300 – 0003FFh | 256 bytes | BIOS Stack Area                                                                                                                                                                                                |

| 000400 – 0004FFh | 256 bytes | BIOS Data Area                                                                                                                                                                                                 |

| 000500 – 09FFFFh | 640 KB    | Applications Memory, used by the<br>operating system, device drivers,<br>TSRs, and all DOS applications.                                                                                                       |

| 0A0000 – 0BFFFFh | 128 KB    | Video Buffer (EGA and VGA).                                                                                                                                                                                    |