This bicentennial edition of the Proceedings of the 1976 National Computer Conference is dedicated to the memory of

# THOMAS JEFFERSON

who wrote,

I have sworn upon the altar of God eternal hostility against every form of tyranny over the mind of man.

**AFIPS** CONFERENCE PROCEEDINGS

Member National Bicentennial Service Alliance

June 7-10, 1976 New York City, New York The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1976 National Computer Conference or the American Federation of Information Processing Societies, Inc.

> Library of Congress Catalog Card Number 55-44701 AFIPS PRESS 210 Summit Avenue Montvale, New Jersey 07645

© 1976 by the American Federation of Information Processing Societies, Inc., Montvale, New Jersey 07645. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publisher.

Printed in the United States of America

# Preface

by CARL HAMMER Conference Chairman Sperry Univac Washington, DC

This is the second time that I have had the privilege of serving the computing community by assuming a role of major responsibility in a National Computer Conference. Dr. Harvey Garner, General Chairman of the First National Computer Conference, asked me in the fall of 1972 to manage the Science and Technology Program for "his" "73 NCC in New York. Three years later, during the Nation's Bicentennial Year, I have returned to serve as Conference Chairman of "my own" "76 NCC.

This conference was carefully planned as a profound educational experience for all in attendance. We used an innovative approach throughout to make it a Landmark Event long to be remembered. Our programmatic activities include many unusual events such as hands-on demonstrations in computer networking, student computer projects from all over the country, computer graphics art exhibits from all over the world. We obtained some entirely new materials for our science film theater and we tailored special programs for the convenience of the handicapped.

The preparations for this conference commenced in the fall of 1974. We recruited a talented and dedicated team of professional volunteers to help us plan and manage it. The members of this Conference Steering Committee were our brains—and often also our arms and legs. It was *their* unbounded enthusiasm and *their* unflagging spirit which put this magnificent show on the road. More than once many of them toiled around the clock, or gave up weekends and even holidays. The community owes them much for their dedication to the cause...

The transient nature of even the most successful conferences is not likely ever to change. But some of them, including these National Computer Conferences, make a permanent contribution in terms of the archival records of their Proceedings. Here we capture for posterity the most current reports on recent achievements and new applications, on advances at the frontiers of computer science and technology. We are justifiably proud of this volume which contains the papers that were selected for delivery at this conference. We acknowledge with deeply felt gratitude the leadership role of our program chairman, Dr. Stanley Winkler, who structured this exciting program and who assembled these proceedings. We who worked with him on the colossal task of designing this meaningful and balanced program will never forget this experience which has enriched our lives and strengthened many personal bonds as well.

We have striven to give this conference and these proceedings a quality which is appropriate for the occasion. As our country prepares for her bicentennial celebration we are also observing the hundredth birthday of the telephone without which interactive computing and distributed networks would be inconceivable. We remember with nostalgia the First (Inaugural, one might say) Joint Computer Conference held twenty-five years ago in Philadelphia; hopefully our efforts will be judged worthy of its great tradition and of all past FJCCs, SJCCs and NCCs. Another milestone comes to mind for 1951: During that memorable year the first commercially built computer was delivered to the U. S. Bureau of the Census. 1776, 1876, 1951 were evidently years in which men of great vision pioneered unforgettable events with much impact. If indeed the "Past is Prologue," we should forever be motivated and inspired by this rich legacy of our nation and the computing profession.

For developing the stimulating materials which comprise these proceedings we are deeply indebted to our stalwart program chairman, Dr. Stanley Winkler. We are grateful to the circa two thousand persons who contributed to this effort by writing or reviewing these papers, or by participating in the program sessions as organizers, discussants and speakers. We thank all Conference Steering Committee members for giving so unstintingly of their time and resources; we also thank their employers or sponsors for allowing them to draw so heavily on their resources. We are also grateful for the support received from the AFIPS staff who most graciously coped with our many idiosyncrasies and scheduling difficulties. Finally, it is a pleasure to acknowledge the guidance we received from the NCC Committee and Board. The names of all who took part in this herculean effort are recorded in this monument to their tenacity and endurance. This was truly a team effort and it was well worth it.

As we commemorate the first twenty-five years of electronic data processing we observe that the introduction of computers into our society has already caused profound changes in everyone's life style. Digital communications today provide public access to the power of computers as readily as the earlier telephone facilitated human dialogue. Global communications systems span the earth as we probe the depths of our solar system and even of the universe. Electronic miniaturization is revolutionizing entire industries and radically new concepts of electronic systems architecture are evolving. Computers have become a new source of power, facilitating the transition from traditional management systems to those of a society which is data and information rich. Yet, as these Proceedings establish so well, we are still at the very threshold of electronic invention and innovation!

As we continue along a path of near-exponential progress—and there is little reason to doubt that we will do so for quite some time—the pervasiveness of electronic systems and their impact on societal structures is bound to exceed our cumulative experience with all earlier technological developments by several orders of magnitude. Whatever one cares to read into such prophecies, human values and the attainable quality of life for all mankind will and must emerge as the ultimate beneficiaries. Perhaps this is the greatest reward which posterity can bestow on us as we place this volume into the public domain. Hopefully the concepts and results espoused herein will help liberate mankind from the self-imposed yokes of rote and drudgery, ushering in a brighter future that knows how to make human use of human beings. . . .

# CONTENTS

| Preface     | v |

|-------------|---|

| Carl Hammer |   |

# INTRODUCTION

| A view of the world of computing as seen at the 1976 National Computer Conference | 1         |

|-----------------------------------------------------------------------------------|-----------|

| Stanley Winkler                                                                   |           |

| Conference maketh a ready man or, twenty-five years in the better joints          | 7         |

| Herbert R. J. Grosch                                                              |           |

| Computer prehistory and history in Central Europe                                 | 15        |

| H. Zemanek                                                                        |           |

| Early computers in Europe                                                         | <b>21</b> |

| Richard Williams                                                                  |           |

# COMPUTERS AND PEOPLE

| SOCIETAL CONCERNS                                                   |     |

|---------------------------------------------------------------------|-----|

| The U.K. privacy white paper 1975                                   | 33  |

| A. S. Douglas                                                       |     |

| Human and organizational implications of computer privacy           | 39  |

| Jerry M. Rosenberg                                                  |     |

| A control systems model of privacy                                  | 45  |

| John Salasin                                                        |     |

| Computer security—A survey                                          | 53  |

| Peter S. Browne                                                     |     |

| Computer abuse perpetrators and vulnerabilities of computer systems | 65  |

| Donn B. Parker                                                      |     |

| Effective safeguards for computer system integrity                  | 75  |

| Norman R. Nielsen, Brian Ruder and David R. Brandin                 |     |

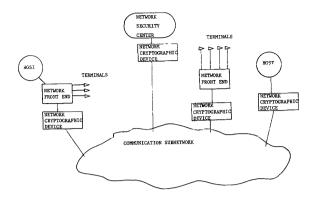

| A centralized approach to computer network security                 | 85  |

| Frank R. Heinrich and David J. Kaufman                              |     |

| Computer network cryptography engineering                           | 91  |

| Harrison R. Burris                                                  |     |

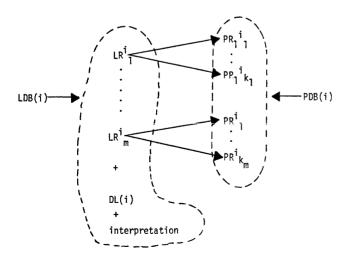

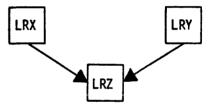

| The application of cryptography for data base security              | 97  |

| Ehud Gudes, Harvey S. Koch and Fred A. Stahl                        |     |

| Multiuser cryptographic techniques                                  | 109 |

| Whitfield Diffie and Martin E. Hellman                              |     |

| Cryptography using modular software elements                                                                                                            | 113         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Herbert S. Bright and Richard L. Enison<br>Analysis of secret functions with application to computer cryptography                                       | 125         |

| Ingemar Ingemarsson                                                                                                                                     |             |

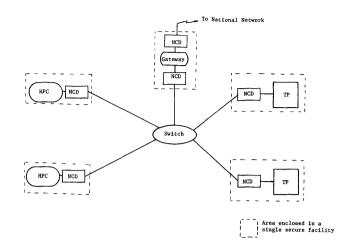

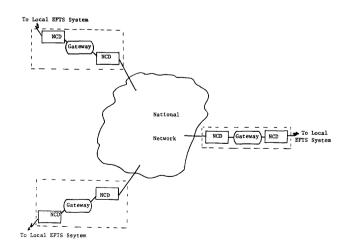

| A secure, national system for electronic funds transfer<br>D. Kaufman and K. Auerbach                                                                   | 129         |

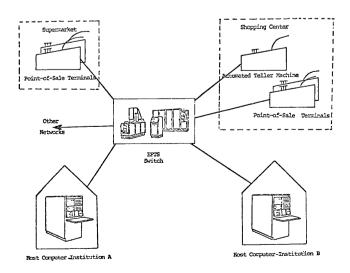

| Design considerations for electronic funds transfer switch system development<br>Joseph P. Mazzetti                                                     | 139         |

| Are computers ready for the checkless society?                                                                                                          | 147         |

| Frank Backman                                                                                                                                           |             |

| THE COMPUTER PROFESSION                                                                                                                                 |             |

| Personware                                                                                                                                              | 157         |

| From data entry supervisor to data entry specialist                                                                                                     | 161         |

| Carolyn M. Dunning                                                                                                                                      |             |

| A modern beginning programming course<br>Roy F. Keller                                                                                                  | 165         |

| Instructional computer systems for higher education<br>Charles J. Prenner and Alfred Z. Spector                                                         | 171         |

| ADP training systems—Organization-wide training for increased productivity<br>Jack L. Stone and Alexander P. Grant                                      | 179         |

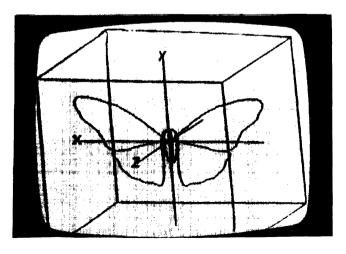

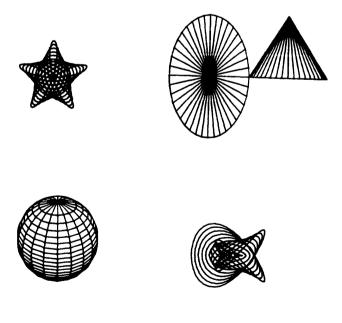

| Teaching art through computer graphics                                                                                                                  | 185         |

| Joseph Scala                                                                                                                                            | 101         |

| Artists and computers Patsy Scala                                                                                                                       | 191         |

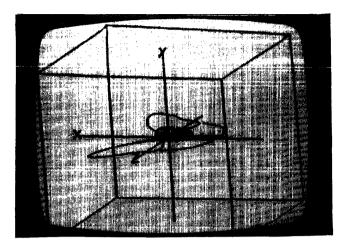

| The digital component of the circle graphics habitat<br>Thomas A. DeFanti                                                                               | 195         |

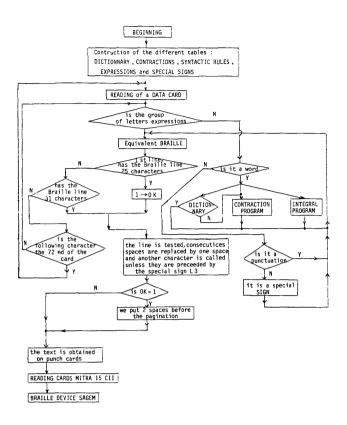

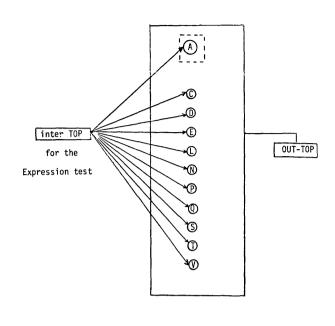

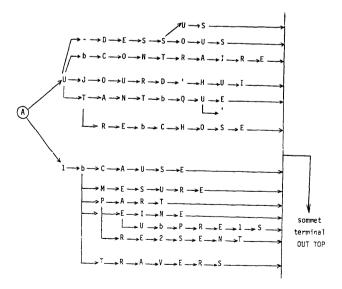

| Braille grade II translator program                                                                                                                     | 205         |

| Monique Truquet                                                                                                                                         |             |

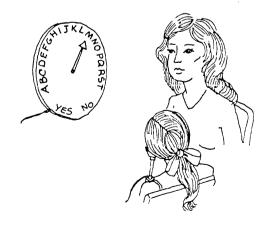

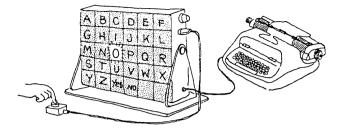

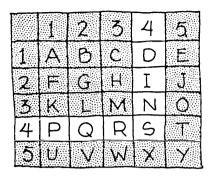

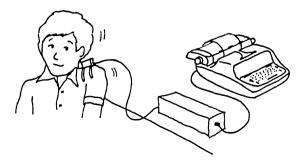

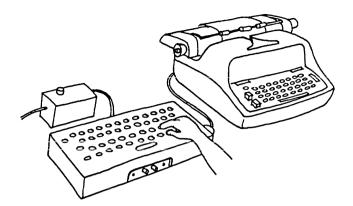

| Interfacing computers for the physically handicapped—A review of international approaches<br>Gerald A. Raitzer, Gregg C. Vanderheiden and Craig S. Holt | 209         |

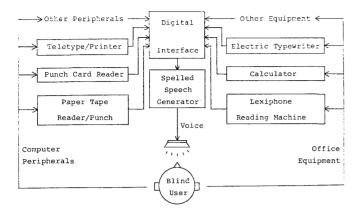

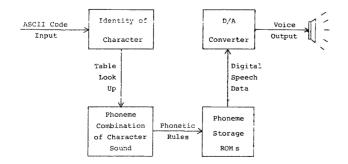

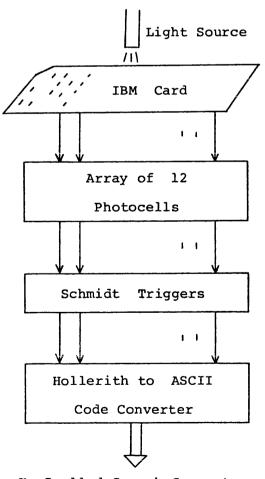

| The spellex system of speech aids for the blind in computer applications<br>Ching Y. Suen, Michael P. Beddoes, and James C. Swail                       | 217         |

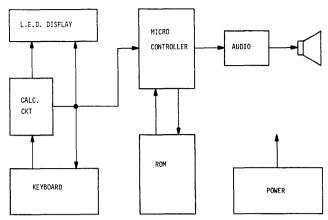

| Development of a hand-held talking calculator for the blind                                                                                             | <b>22</b> 1 |

| R. E. Savoie, J. S. Brugler and J. C. Bliss                                                                                                             |             |

| ISSUES IN COMPUTING                                                                                                                                     |             |

| Survey of public attitudes toward computers in society                                                                                                  | 227         |

| David H. Ahl                                                                                                                                            |             |

| Survey of public access to computing<br>Carol H. Kastner and William G. Underhill                                                                       | <b>23</b> 1 |

| Building your own computer                                                                                                                              | 235         |

# APPLICATIONS SERVING PEOPLE

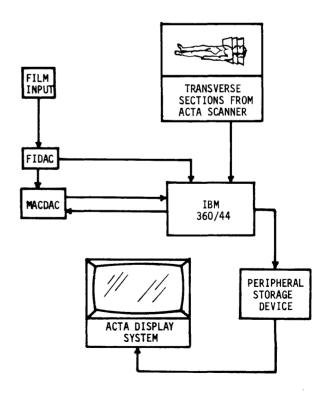

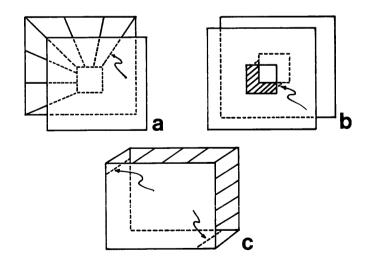

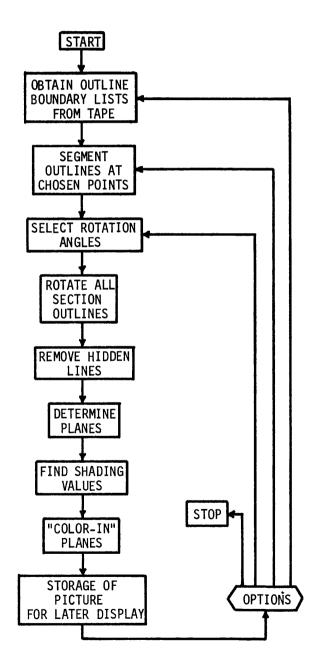

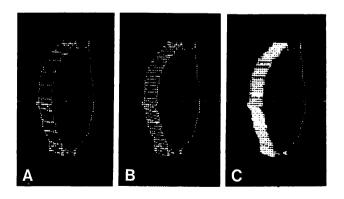

| THREAD (three-dimensional reconstruction and display) with biomedical applications in neuron   |            |

|------------------------------------------------------------------------------------------------|------------|

| ultrastructure and computerized tomography                                                     | 241        |

| John C. Mazziotta and H. K. Huang                                                              |            |

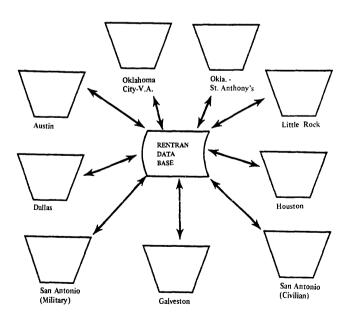

| Regional kidney transplant matching—The Rentran interactive approach                           | <b>251</b> |

| David J. Mishelevich, Peter Stastny, R. Gail Ellis, and Susan G. Mize                          |            |

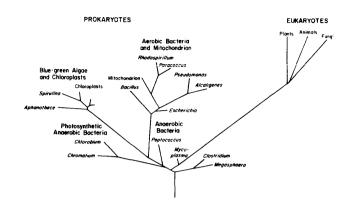

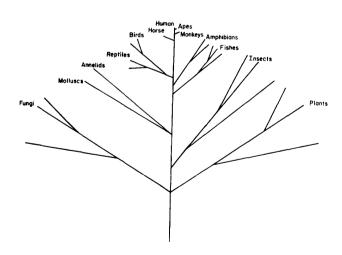

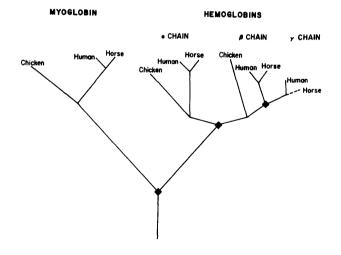

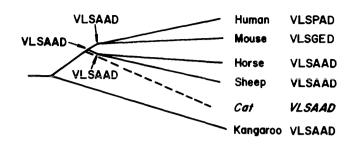

| Data base for protein sequences                                                                | 261        |

| M. O. Dayhoff, W. C. Barker, R. M. Schwartz, B. C. Orcutt, and L. T. Hunt                      |            |

| From text to structured information—Automatic processing of medical reports                    | 267        |

| Lynette Hirschman, Ralph Grishman and Naomi Sager                                              |            |

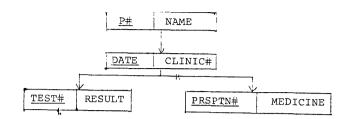

| Design considerations of a database system in a clinical network environment                   | 277        |

| Shi-Kuo Chang, M. O'Brien, J. Read, R. Borovec, W. H. Cheng and J. S. Ke                       |            |

| Correct problem statements in biomedical data processing                                       | 287        |

| N. I. Moiseeva, M. Yu. Simonov and V. M. Sysuev                                                |            |

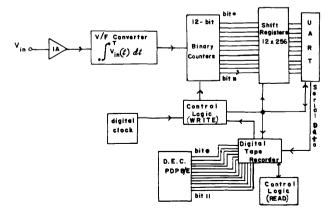

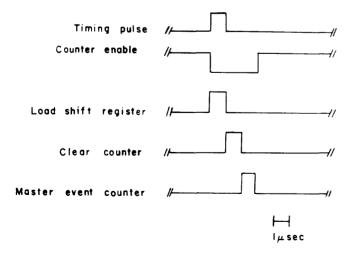

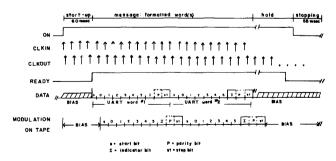

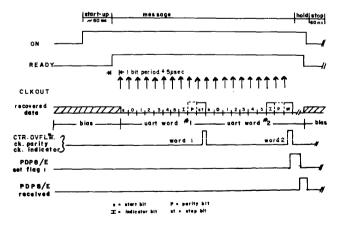

| An adaptable, modular data-collection system suitable for scientific experimentation-Analog to |            |

| digital transformation, short-term digital storage, formatted digital tape-recording, and      |            |

| computer entry of experimental data                                                            | 295        |

| Harold H. Shlevin                                                                              |            |

| Classification of personal information for privacy protection purposes                         | 301        |

| Rein Turn                                                                                      |            |

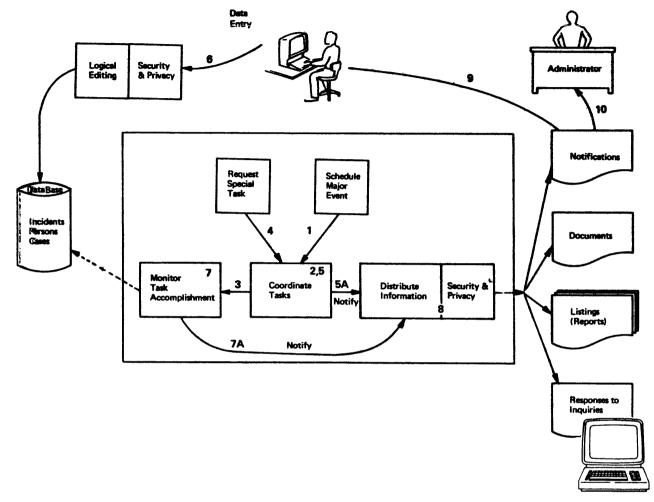

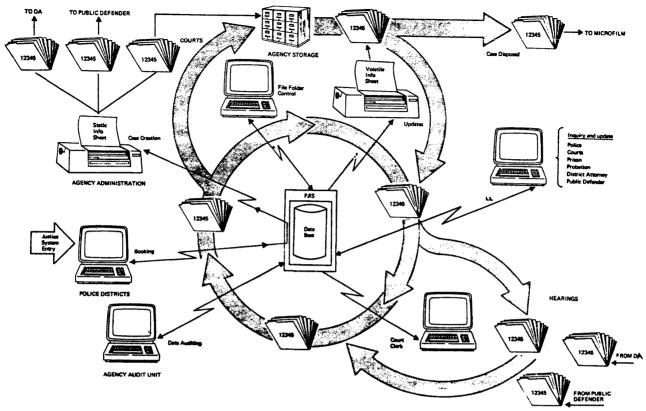

| Philadelphia justice information system                                                        | 309        |

| Irving J. Chasen                                                                               |            |

| Computers in architecture                                                                      | 315        |

| Genevieve Greenwald-Katz                                                                       |            |

# SYSTEMS

| COMPUTER SYSTEMS                                                                               |     |

|------------------------------------------------------------------------------------------------|-----|

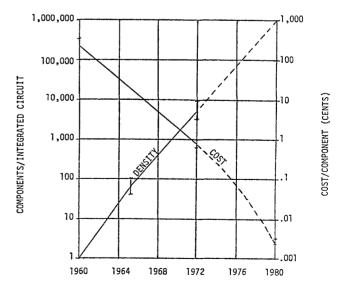

| Prospective capabilities in hardware                                                           | 323 |

| Margaret K. Butler                                                                             |     |

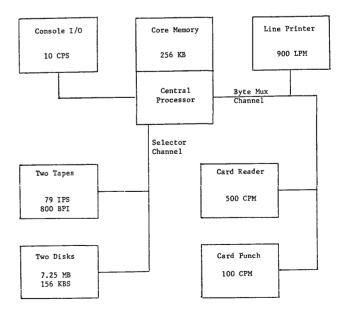

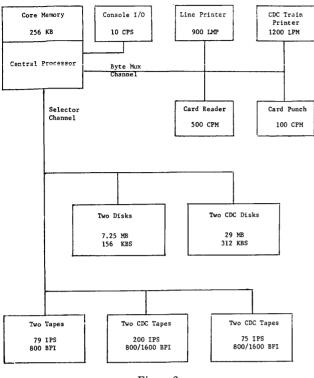

| An evaluation of the East German RYAD 1040 system                                              | 337 |

| Robert A. Koenig                                                                               |     |

| MagicScore bowling scorer—A microprocessor application for fun and profit                      | 341 |

| Reg A. Kaenel                                                                                  |     |

| QLISP—A language for the interactive development of complex systems                            | 349 |

| Earl D. Sacerdoti, Richard E. Fikes, Rene Reboh, Daniel Sagalowicz, Richard J. Waldinger       |     |

| and B. Michael Wilber                                                                          |     |

| User interface design issues for a large interactive system                                    | 357 |

| Richard William Watson                                                                         |     |

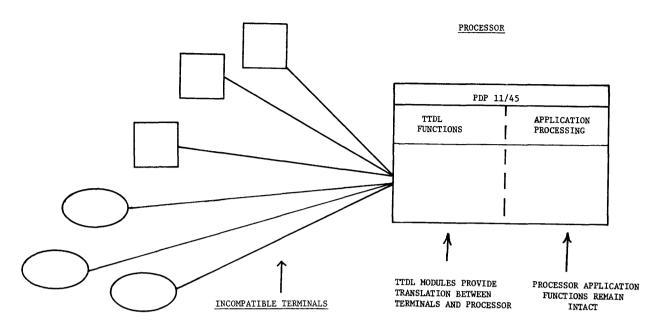

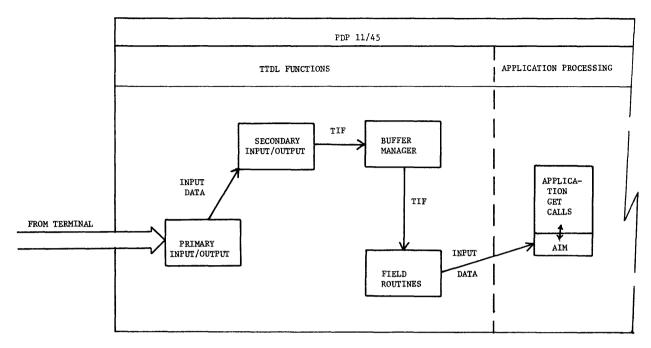

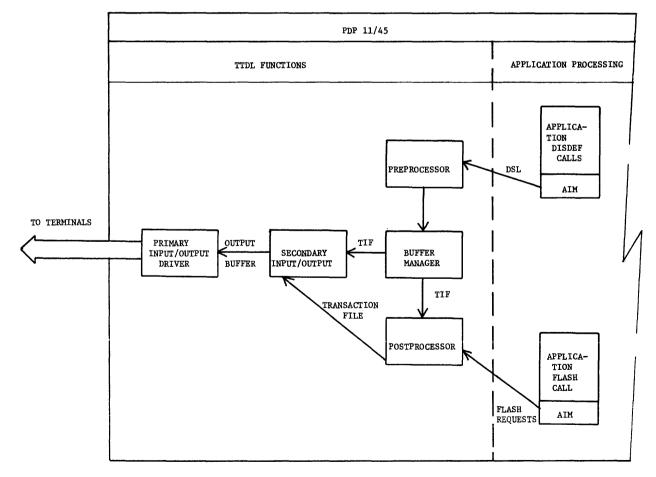

| Terminal transparent display language (TTDL)                                                   | 365 |

| Carl E. Krebs, C. Bumgardner and T. Northwood                                                  |     |

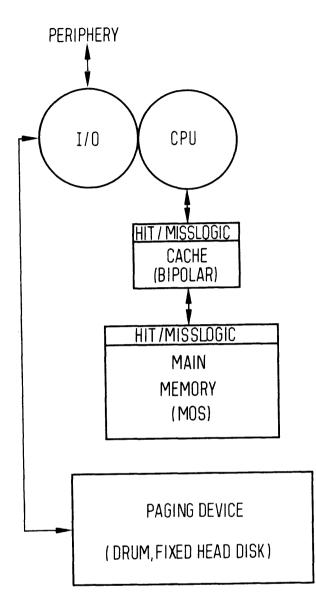

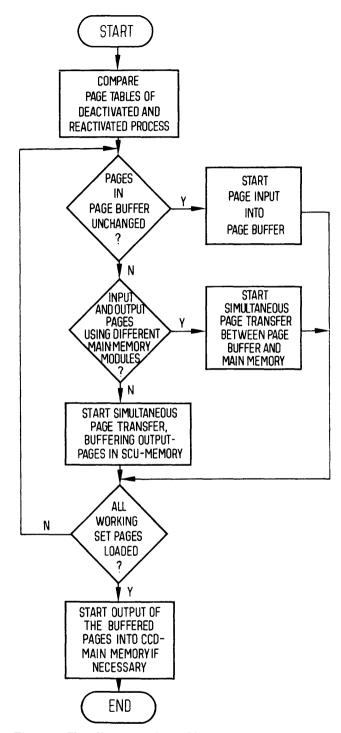

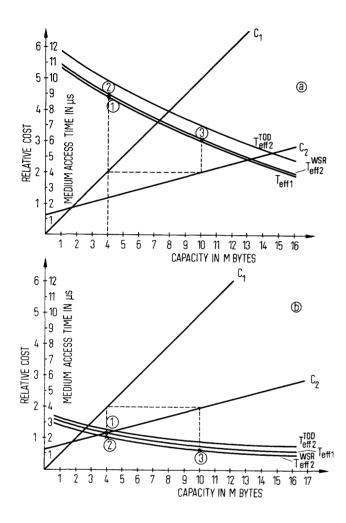

| Working set restoration—A method to increase the performance of multilevel storage hierarchies | 373 |

| Peter Schneider                                                                                |     |

|                                                                                           | 0.01 |

|-------------------------------------------------------------------------------------------|------|

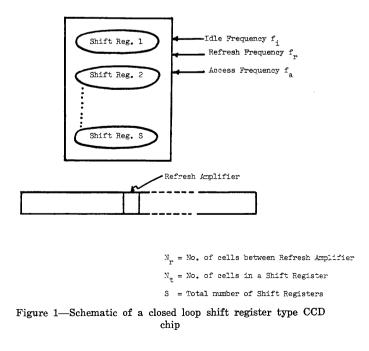

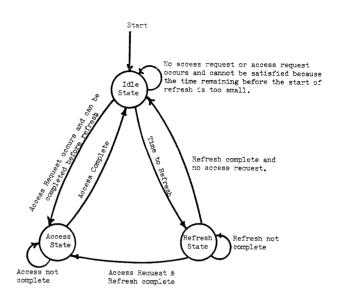

| Performance and power dissipation analysis for CCD memory systems                         | 381  |

| Intelligent memory                                                                        | 393  |

| Murray Edelberg and L. Robert Schissler                                                   |      |

| Approaches to computer reliabilityThen and now                                            | 401  |

| Algirdas Avizienis                                                                        |      |

| Failure-tolerant parallel programming and its supporting system architecture              | 413  |

| K. H. Kim and C. V. Ramamoorthy                                                           |      |

| SYSTEMS MANAGEMENT                                                                        |      |

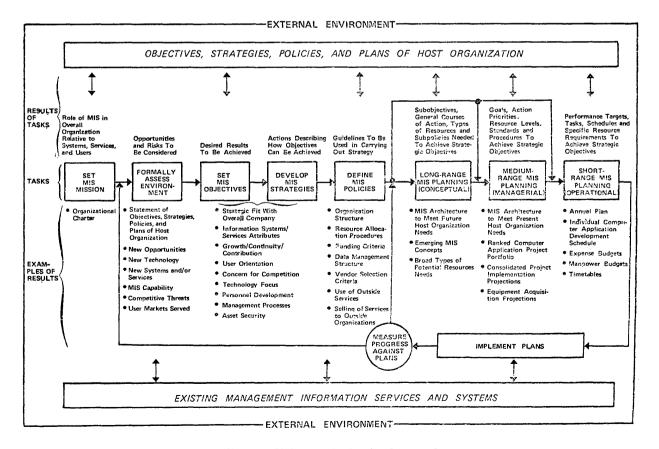

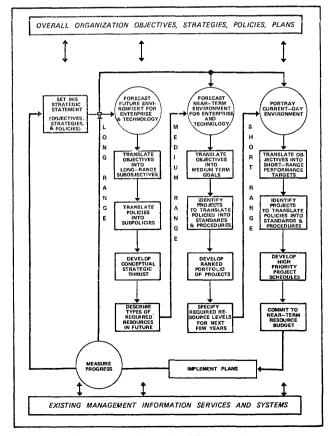

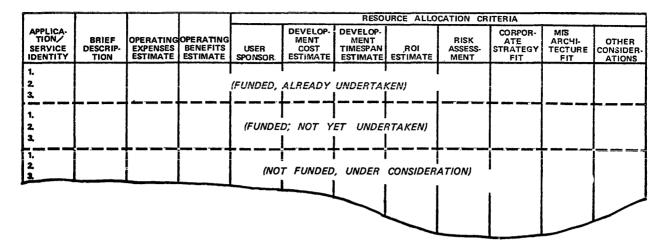

| Strategic planning for MIS—A conceptual framework                                         | 425  |

| Ephraim R. McLean and John V. Soden                                                       |      |

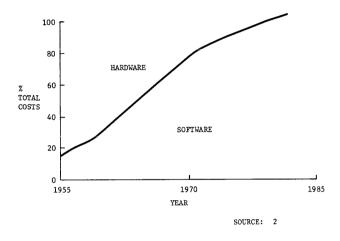

| The economics of software quality assurance                                               | 433  |

| David S. Alberts                                                                          |      |

| Implementation of quality control in software development                                 | 443  |

| Frank Tsui and Lew Priven                                                                 |      |

| A computer performance prediction model                                                   | 451  |

| Robert W. Otto and Mark Auerbach                                                          |      |

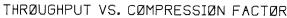

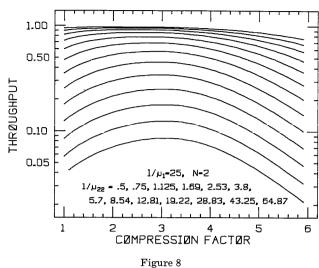

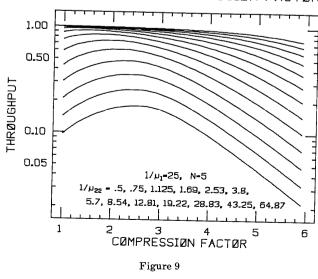

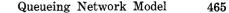

| A queueing network model for the effect of data compression on system efficiency          | 457  |

| NETWORKING                                                                                |      |

| The Federal Communications Commission and major policy matters affecting computer         |      |

| communication                                                                             | 467  |

| Frank J. Martin, Jr.                                                                      |      |

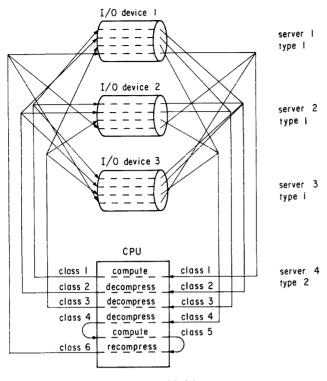

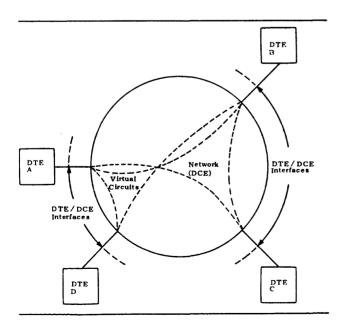

| A new communication protocol for accessing data networks—The international packet-mode    |      |

| interface                                                                                 | 477  |

| A. Rybcznski, B. Wessler, R. Despres and J. Wedlake                                       |      |

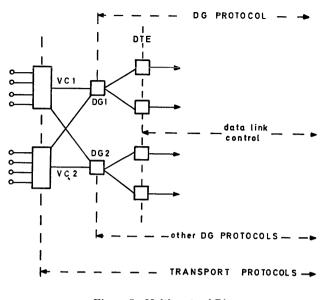

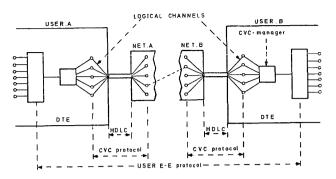

| Virtual circuits vs. datagrams technical and political problems                           | 483  |

| Louis Pouzin                                                                              |      |

| Network access techniques—A review                                                        | 495  |

| Robert Rosenthal                                                                          |      |

| The Rand intelligent terminal agent (RITA) as a network access aid                        | 501  |

| Robert H. Anderson and James J. Gillogly                                                  |      |

| Network interface systems—An evaluation by simulation                                     | 511  |

| Joe B. Wyatt and Vincent I. Polley                                                        |      |

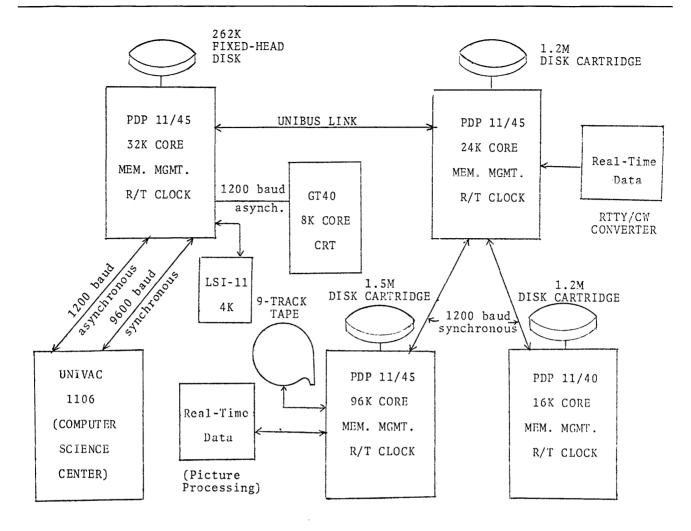

| An overview of the distributed computer network                                           | 523  |

| David L. Mills                                                                            |      |

| A network-oriented multiprocessor front-end handling many hosts and hundreds of terminals | 533  |

| W. F. Mann, S. M. Ornstein, and M. F. Kraley                                              |      |

| Design issues for mixed media packet switching networks                                   | 541  |

| D. Huynh, H. Kobayashi and F. F. Kuo                                                      |      |

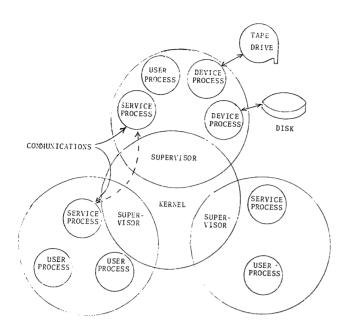

| A perspective on network operating systems                                                | 551  |

| Stephen R. Kimbleton and Richard L. Mandell                                               |      |

| A high-level framework for network-based resource sharing                            | 561 |

|--------------------------------------------------------------------------------------|-----|

| Factors in interprocess communication protocol efficiency for computer networks      | 571 |

| Carl A. Sunshine                                                                     | 011 |

| Performance of file directory systems for data bases in star and distributed network | 577 |

| Wesley W. Chu                                                                        | 011 |

| On measurement facilities in packet radio systems                                    | 589 |

| Fouad A. Tobagi, Stanley E. Lieberson and Leonard Kleinrock                          | 000 |

| Monitoring and access control of the London node of ARPANET                          | 597 |

| Adrian V. Stokes, David L. Bates and Peter T. Kirstein                               |     |

|                                                                                      |     |

| BUSINESS AND INDUSTRY SYSTEMS                                                        |     |

| Office automation project—A research perspective                                     | 605 |

| Howard Lee Morgan                                                                    |     |

| Evaluating the impact of office automation on top management communication           | 611 |

| James H. Carlisle                                                                    |     |

| The evolving market for word processing and typesetting systems                      | 617 |

| J. Christopher Burns                                                                 |     |

| The computer as a tool in the processing of text for periodical publications         | 625 |

| William J. Hammond                                                                   |     |

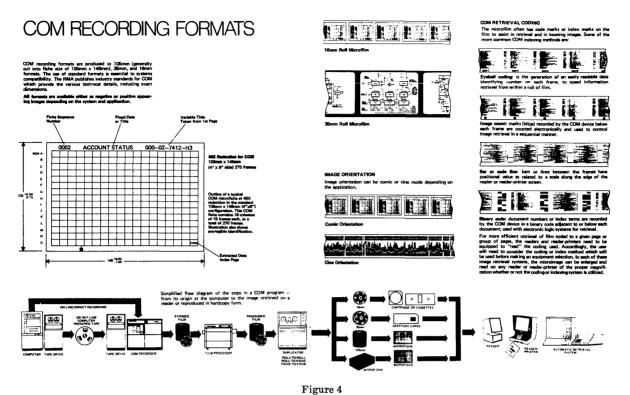

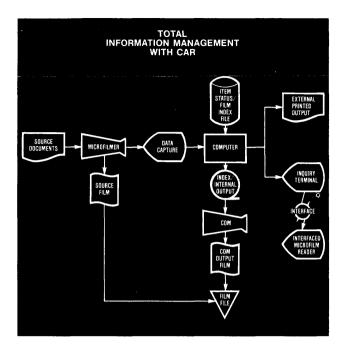

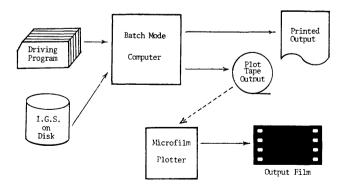

| The integration of microfilm and the computer                                        | 627 |

| Dennis R. Neary, Terrence H. Coyle and Don M. Avedon                                 |     |

| The AIDUS system—Automated capture, update and republication of maintenance manuals  | 639 |

| Arnold K. Griffith                                                                   |     |

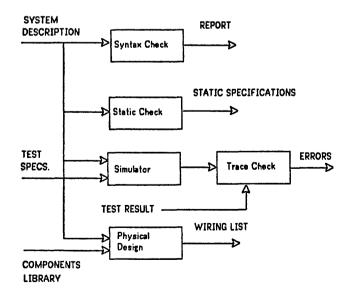

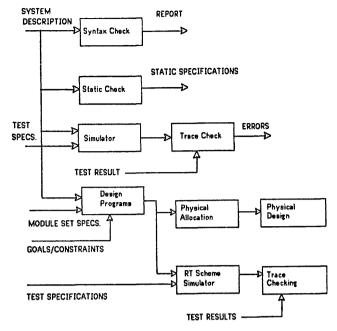

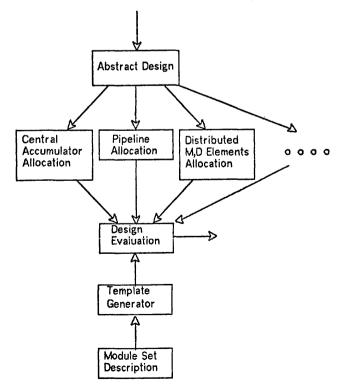

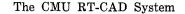

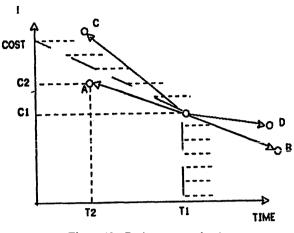

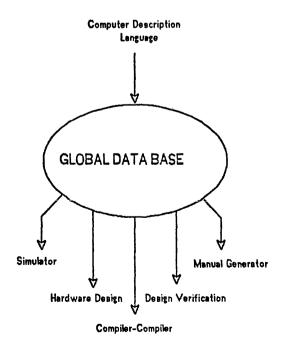

| The CMU RT-CAD system—An innovative approach to computer aided design                | 643 |

| Daniel P. Siewiorek and Mario R. Barbacci                                            |     |

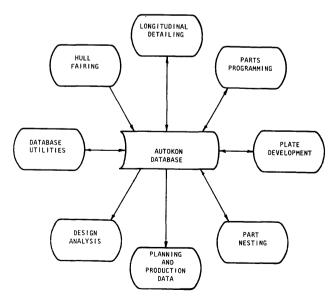

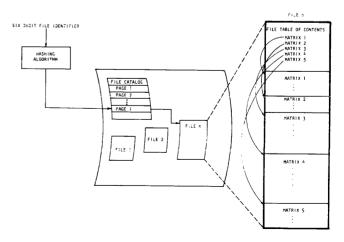

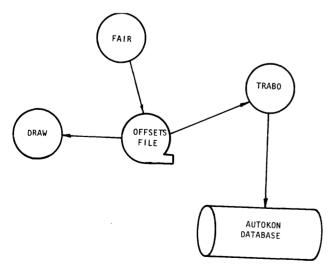

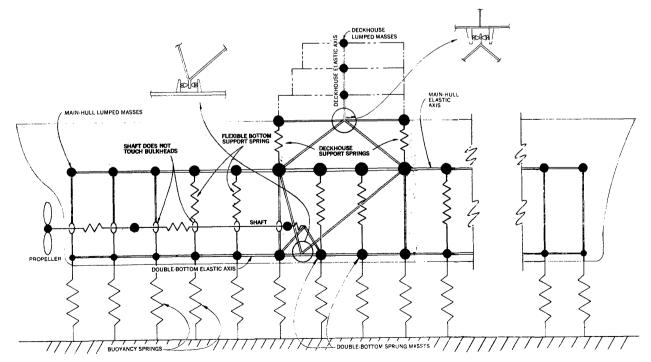

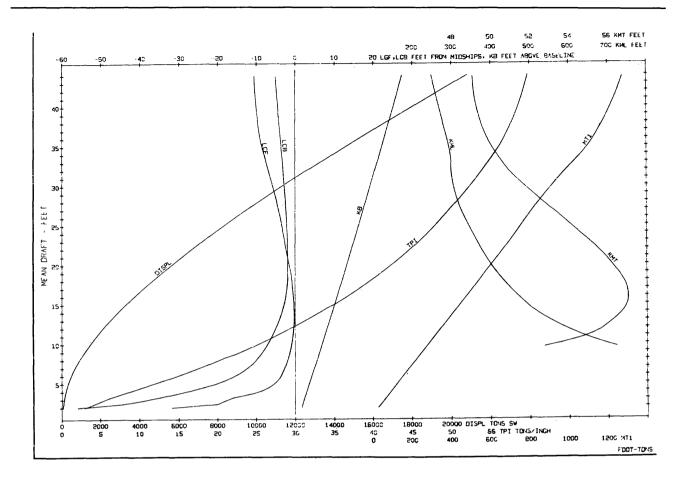

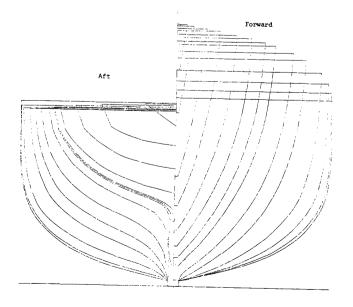

| Some computer-related advancements for enhancing U.S. shipyard productivity          | 657 |

| Richard B. Wise and Douglas Martin                                                   |     |

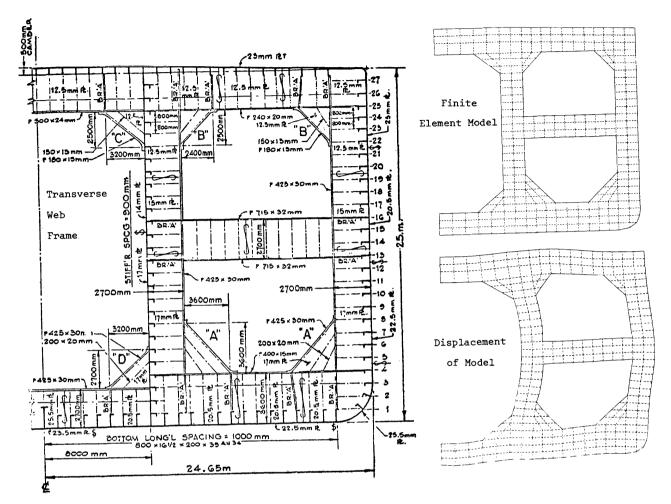

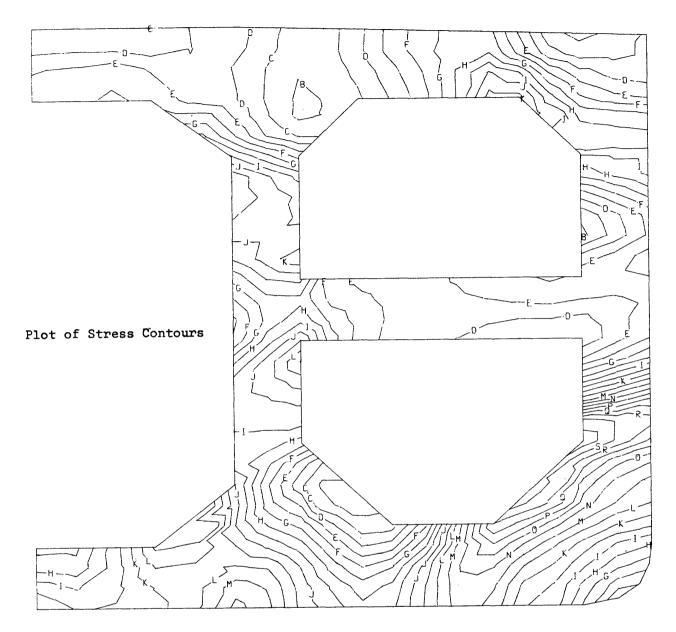

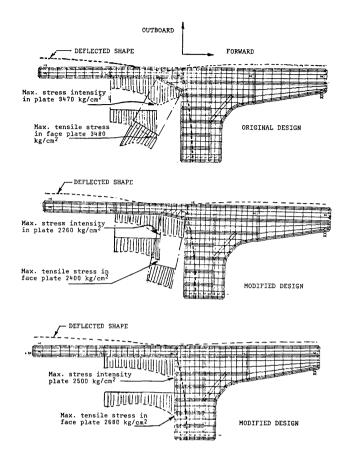

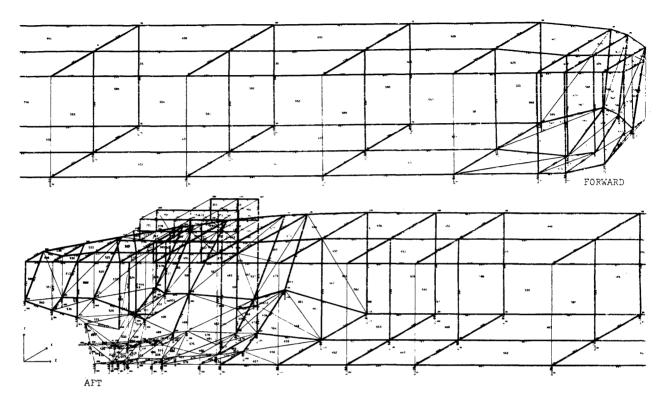

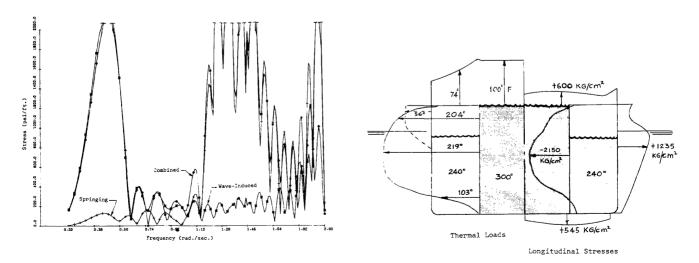

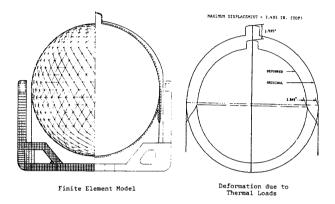

| Computer analysis and evaluation of marine structures                                | 671 |

| Donald Liu and Matias E. Wojnarowski                                                 |     |

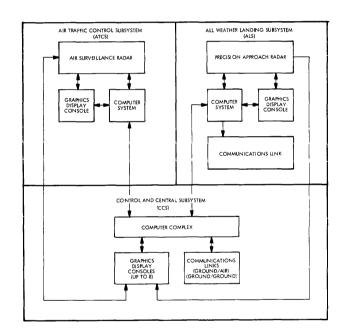

| Evolution of automation in terminal air traffic control                              | 683 |

| Howard R. McGlauflin                                                                 |     |

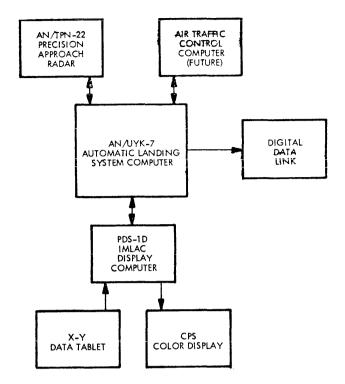

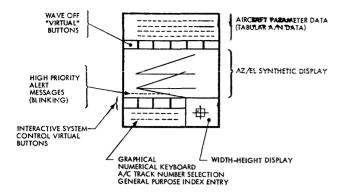

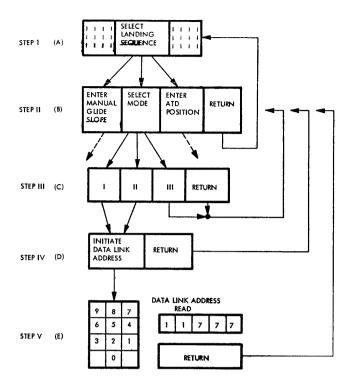

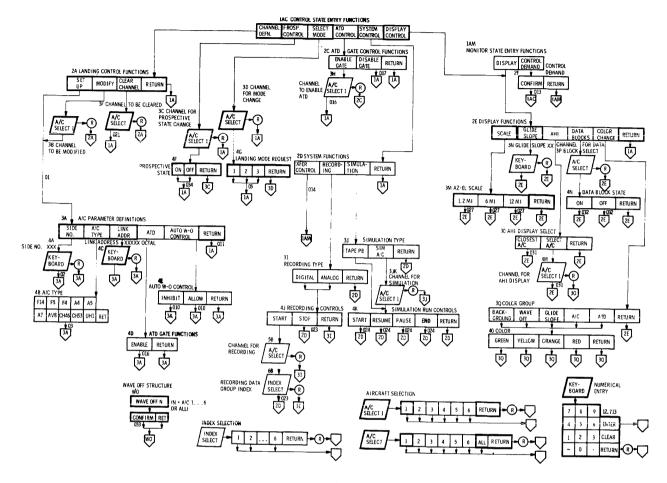

| Computer graphics in an automatic aircraft landing system                            | 689 |

| E. H. Reitan and S. H. Saib                                                          |     |

| Libraries and the implications of computer technology                                | 701 |

| Murray Turoff and Marion Spector                                                     |     |

| The expanding role of on-line interactive searching                                  | 709 |

| Vivian S. Sessions                                                                   |     |

# SCIENCE AND TECHNOLOGY

# COMPUTER AND DATA BASE ARCHITECTURE

| Developing application oriented computer architectures on general purpose microprogrammable |     |

|---------------------------------------------------------------------------------------------|-----|

| machines                                                                                    | 715 |

| Tomlinson Gene Rauscher and Ashok Kumar Agrawala                                            |     |

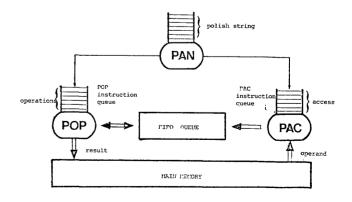

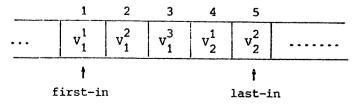

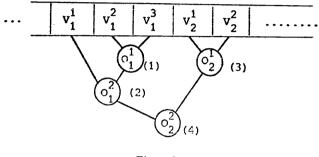

| A pipeline polish string computer<br>Gerard G. Baille and Jean P. Schoellkopf                | 723        |

|----------------------------------------------------------------------------------------------|------------|

|                                                                                              | 799        |

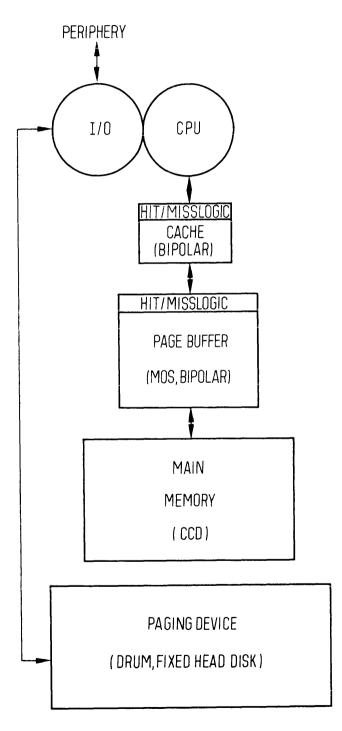

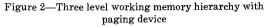

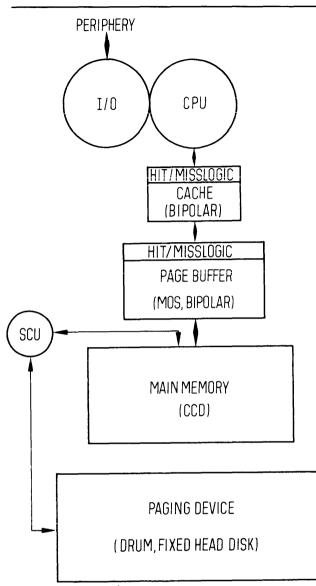

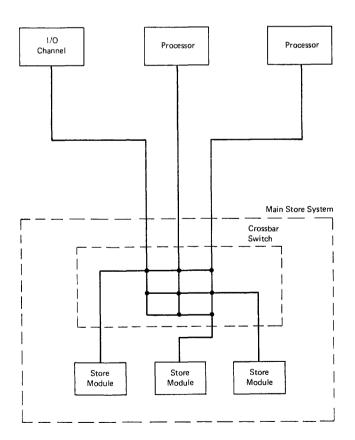

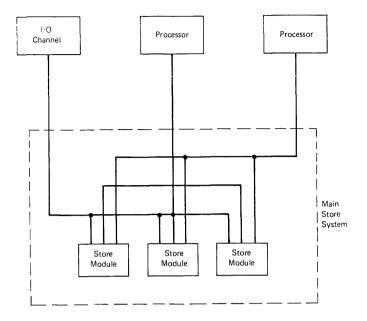

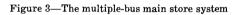

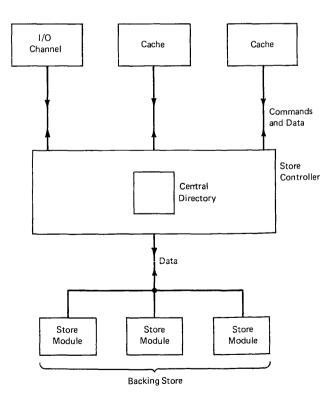

| Evolution of computer memory structure                                                       | 733        |

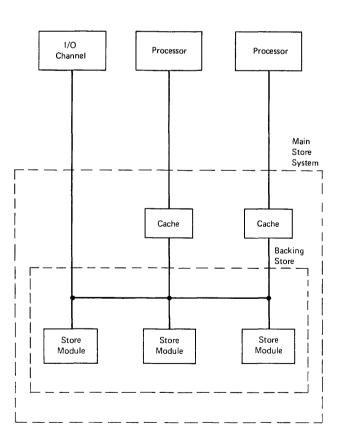

| Cache system design in the tightly coupled multiprocessor system                             | <b>749</b> |

| C. K. Tang                                                                                   |            |

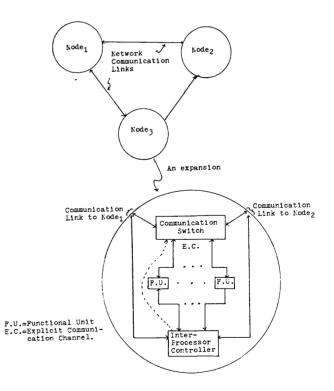

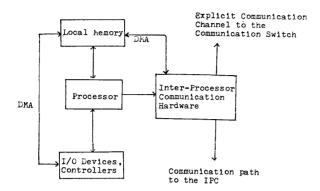

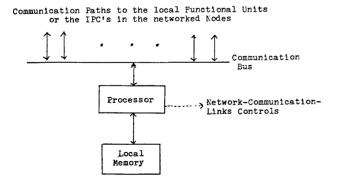

| Coupling small computers for performance enhancement                                         | 755        |

| Fernando C. Colon, Robert M. Glorioso, Walter H. Kohler, and Dominic W. Li                   |            |

| The CERF computer system                                                                     | 765        |

| Neil Wilhelm, David Pessel and Charles Merriam                                               |            |

| A parallel processor for evaluation studies                                                  | 769        |

| Gary J. Nutt                                                                                 |            |

| Asynchronous speed-independent arbiter in a form of a hardware control module                | 777        |

| H. Sechovsky and S. Jura                                                                     |            |

| Log-sum multipler                                                                            | 783        |

| J. P. Agrawal and V. U. Reddy                                                                |            |

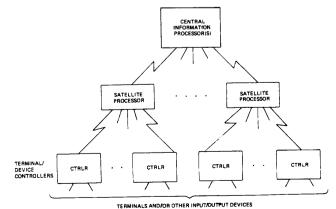

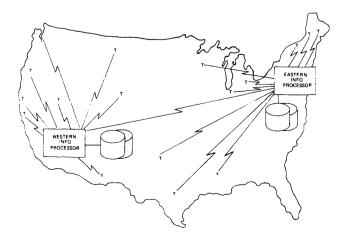

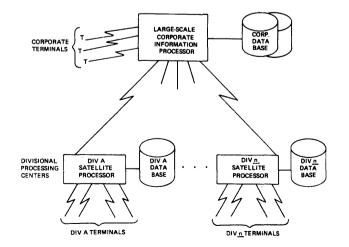

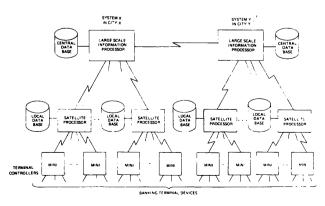

| Distributed information systems                                                              | 789        |

| Grayce M. Booth                                                                              |            |

| Error detection in data base systems                                                         | 795        |

| Michael Hammer                                                                               |            |

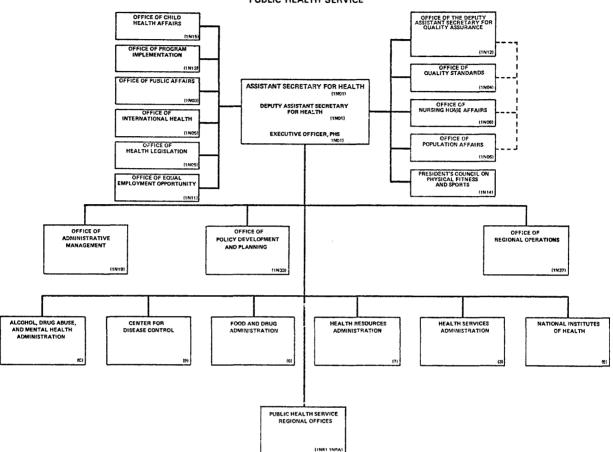

| A framework for federal health data collection                                               | 803        |

| N. Phillip Ross and Meyer Katzper                                                            |            |

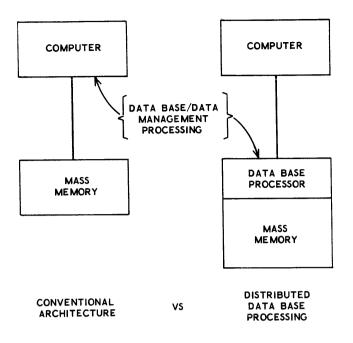

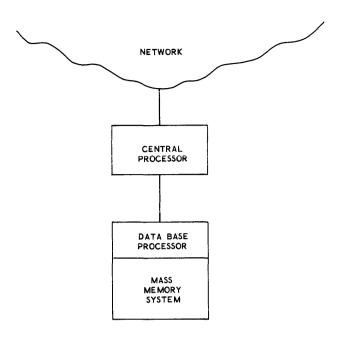

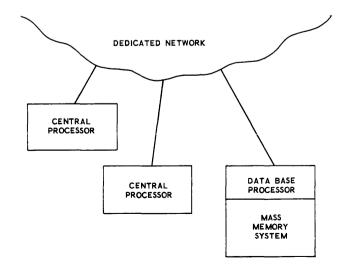

| Data base processor technology                                                               | 811        |

| Donald R. Anderson                                                                           |            |

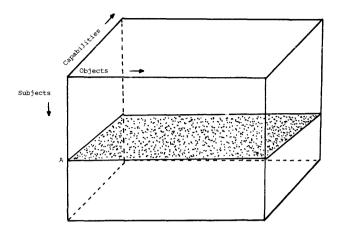

| Integrity aspects of a shared data base                                                      | 819        |

| Eduardo B. Fernandez and Rita C. Summers                                                     | 010        |

| Designing optimal data structures                                                            | 829        |

| Larry Clough, William D. Haseman and Yuk Ho So                                               | 020        |

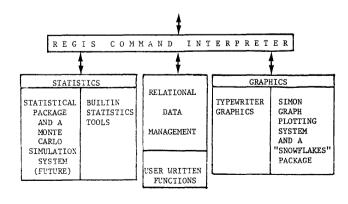

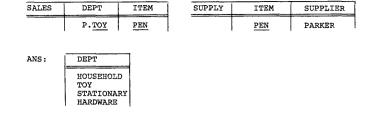

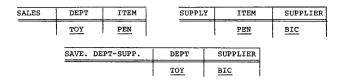

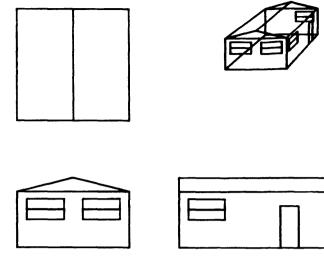

| REGIS—A relational information system with graphics and statistics                           | 839        |

| J. D. Joyce and N. N. Oliver                                                                 | 000        |

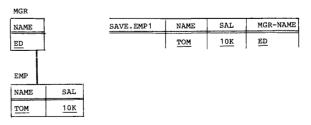

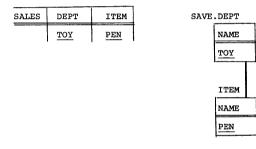

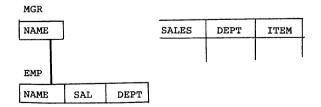

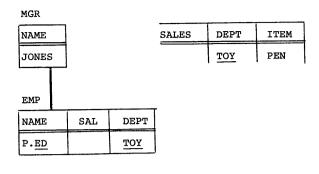

| Query-by-example—Operations on hierarchical data bases                                       | 845        |

| Moshé M. Zloof                                                                               | 040        |

| A virtual memory system for a relational associative processor                               | 855        |

| S. A. Schuster, E. A. Ozkarahan and K. C. Smith                                              |            |

| Managing the census data base—Data description, acquisition, and manipulation                | 863        |

| Jay-Louise Weldon                                                                            |            |

| Defining management's information needs                                                      | 869        |

| Trevor John Bentley                                                                          | 000        |

| Managerial response to an information system                                                 | 877        |

| Roy H. Igersheim                                                                             | 011        |

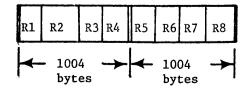

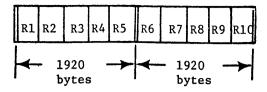

| Transaction queueing and cylinder logic access in the Time, Inc. magazine/book/record system | 883        |

| Carl R. Gerami, T. Russell Shields and Richard J. Weiland                                    | 000        |

•

| SOFTWARE                                                                                                                                               |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

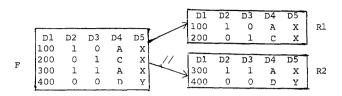

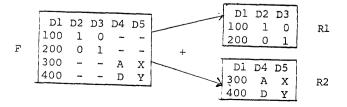

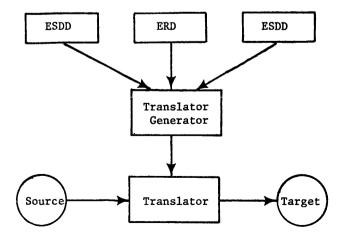

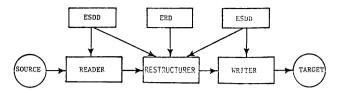

| Generalized software for translating data<br>Edward W. Birss and James P. Fry                                                                          | 889  |

| Experiments with a symbolic evaluation system                                                                                                          | 899  |

| Some experience with DAVE—A Fortran program analyzer<br>Leon J. Osterweil and Lloyd D. Fosdick                                                         | 909  |

| A dynamic (FORTRAN) programming system<br>Julius A. Archibald, Jr.                                                                                     | 917  |

| GPMX—A portable general purpose macro processor adapted for preprocessing Fortran<br>Robert C. Gammill                                                 | 927  |

| COMPUTER SCIENCE                                                                                                                                       |      |

| An experiment comparing Fortran programming times with the software physics hypothesis<br>R. D. Gordon and M. H. Halstead                              | 935  |

| Representations of networks                                                                                                                            | 939  |

| A practitioner's guide to the state of large scale network and network-related problems<br>Fred Glover and Darwin Klingman                             | 945  |

| Low-cost residue number systems for computer arithmeticBehrooz Parhami                                                                                 | 951  |

| Very fast computation of polynomial remainder sequence coefficient signs<br>James R. Pinkert                                                           | 957  |

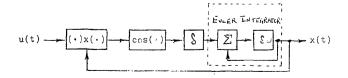

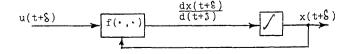

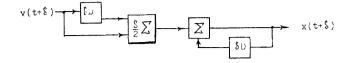

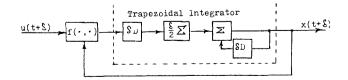

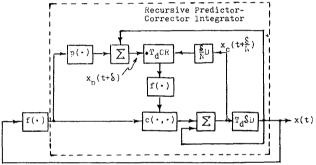

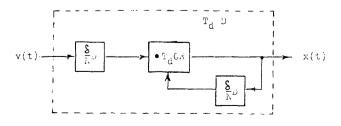

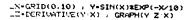

| System theoretic implications of numerical methods applied to the solution of ordinary differential                                                    |      |

| equations<br>T. G. Winderknecht and H. D'Angelo                                                                                                        | 963  |

| Memory conserving efficient methods for solving large sets of stiff differential equations<br>Gruia-Catalin Roman, David Garfinkel and Carl B. Marbach | 973  |

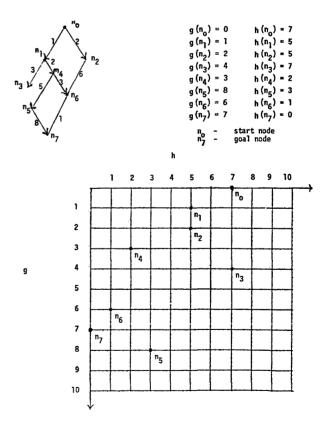

| A geometric analysis of heuristic search                                                                                                               | 979  |

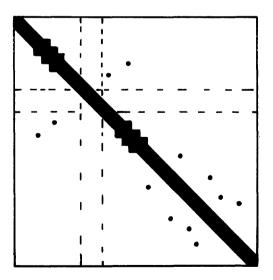

| Another algorithm for reducing bandwidth and profile of a sparse matrix                                                                                | 987  |

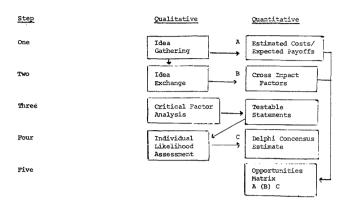

| Business opportunity analysis                                                                                                                          | 995  |

| A "unique number" generator<br>Armen Nahapetian                                                                                                        | 999  |

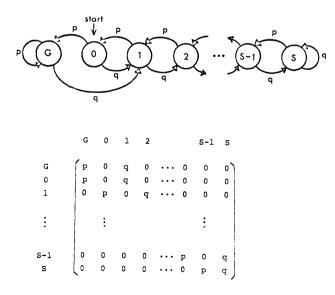

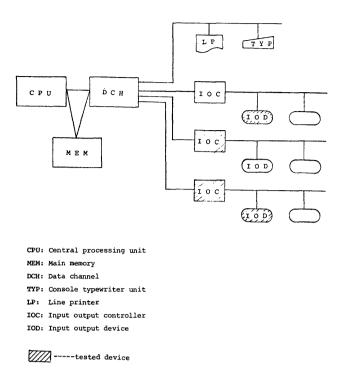

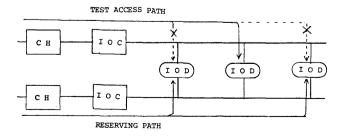

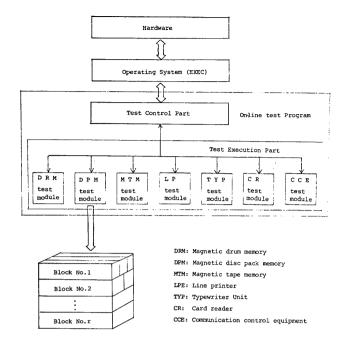

| An on-line test program for peripheral devices<br>Akira Taneda, Hikaru Oku and Daiji Namba                                                             | 1001 |

| Structure of the ELF operating system<br>David L. Retz and Bruce W. Schafer                                                                            | 1007 |

| Elements of a planning and modeling system                                                                                                             | 1017 |

| APPLICATIONS OF COMPUTER SCIENCE                                                                                                                       |      |

| Analysis of "natural" language discourse                                                                                                               | 1027 |

.

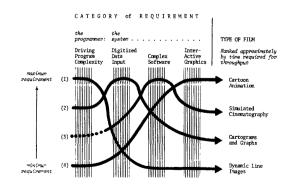

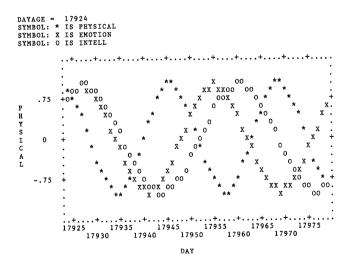

| Computer animated film systems—A rat's nest of trade-offs           | 1035 |

|---------------------------------------------------------------------|------|

| Bruce Cornwell and Katharine Cornwell                               |      |

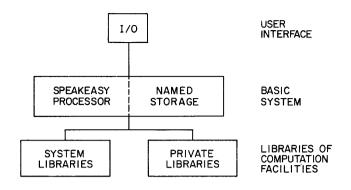

| Speakeasy—A window into a computer                                  | 1039 |

| Stan Cohen                                                          |      |

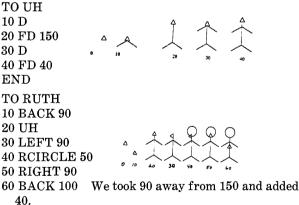

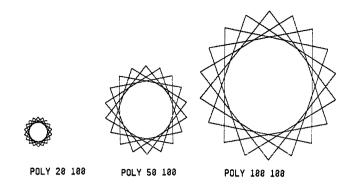

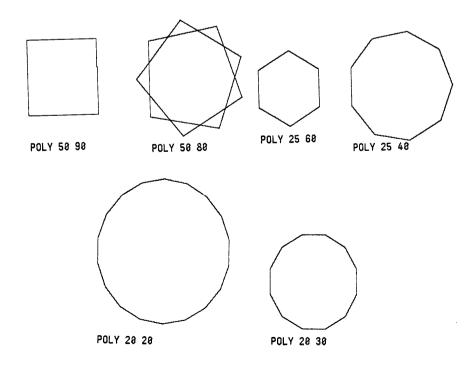

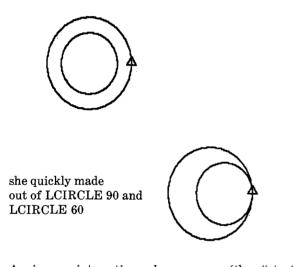

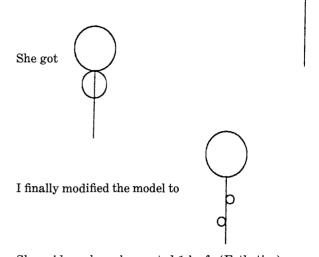

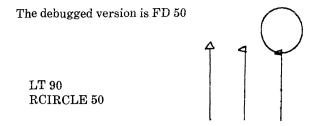

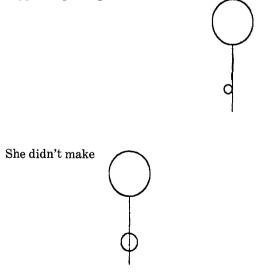

| A case study of a young child doing turtle graphics in LOGO         | 1049 |

| Cynthia J. Solomon and Seymour Papert                               |      |

| Feature selection for binary data—Medical diagnosis with fuzzy sets | 1057 |

| James C. Bezdek                                                     |      |

| Procedural representation in a fuzzy problem-solving system         | 1069 |

| Richard A. LeFaivre                                                 |      |

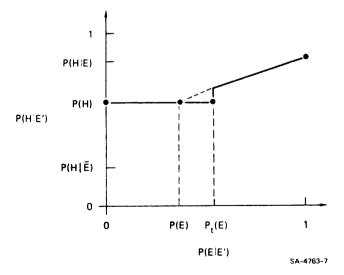

| Subjective Bayesian methods for rule-based inference systems        | 1075 |

| Richard O. Duda, Peter E. Hart and Nils J. Nilsson                  |      |

INTRODUCTION

# A view of the world of computing as seen at the 1976 National Computer Conference

by STANLEY WINKLER IBM Corporation Gaithersburg, Maryland

## ABSTRACT

The twenty-fifth anniversary of joint computer conferencing and the bicentennial of the United States of America are celebrated during this 45th in a series of joint conferences. The Conference also commemorates the 25th anniversary of the introduction of commercial computing. The state of the computer profession and industry is mirrored in the conference program and these conference proceedings are a selected distillation of the program. The spirit of the American Revolution is reflected in the attention given to Computers and People in general and Societal Concerns in particular. About one third of the Conference is devoted to Computers and People and the remaining two thirds is divided almost equally between Systems and Science and Technology. The quality, scope and diversity of the papers in this volume, as they represent the state-ofthe-art today, augurs well for the future.

# INTRODUCTION

June 7, 1976, the opening day of this Conference, is the 200th anniversary of the introduction, by Richard Henry Lee, of the resolution for independence of the United States of America. It is, thus, proper in a bicentennial year that we recognize this connection with the American Revolution, and the dedication to Jefferson provides that recognition. However, in dedicating this volume to the memory of Thomas Jefferson, I also hoped to invoke that fierce spirit of the man who swore eternal hostility against tyranny over the mind of man. As we look at the state of our profession in the mirror of this conference, it is easy to see a maturity in the realm of technological capability. The equivalent maturity in the understanding of social impacts and public policy direction is not so easy to detect. Perhaps it is appropriate to recall the dictum of Norbert Wiener who wrote, ". . . danger to society is not from the machine but from what man makes of it."1

During our conference, we celebrate not only the nation's bicentennial, but also the 25 year anniversary

of joint conferencing and the 25th anniversary of the introduction of commercial computing. On December 10-12, 1951, a relatively homogenous group met in Philadelphia to discuss the characteristics and performance of ten working, large-scale electronic digital computers. In many ways it was a remarkable meeting as may be seen from the contents of that first proceedings.<sup>2</sup> The Keynote Address for 1951 by W. H. MacWilliams of the Bell Telephone Laboratories is a very interesting sketch of the past, present and future of the computing industry as seen in 1951. The last two papers in that first program were a discussion of the applicability of transistors to digital computation, by J. H. Felker and a forecast of the future by J. W. Forrester. Elsewhere in this volume. Herb Grosch provides us with an highly personal view of that first conference and the succeeding twenty-five years of joint computer conferencing in which he captures the gestalt of these conferences.<sup>2</sup>

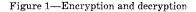

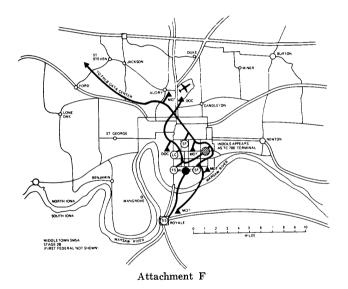

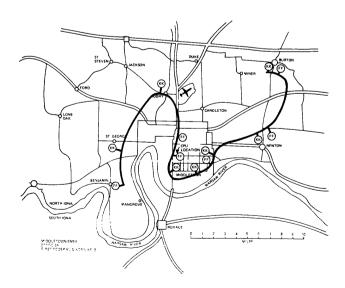

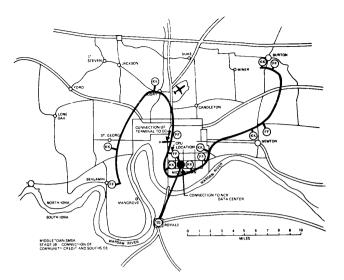

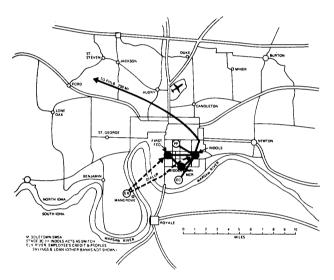

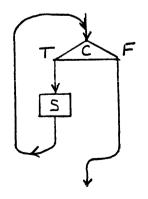

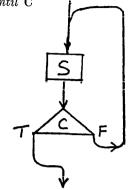

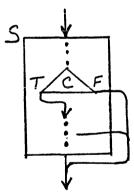

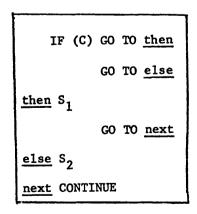

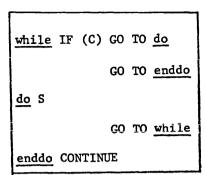

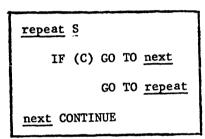

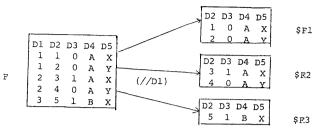

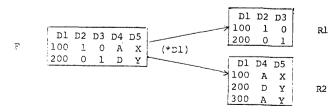

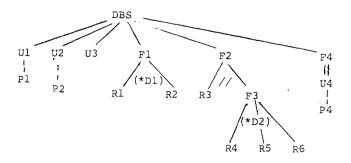

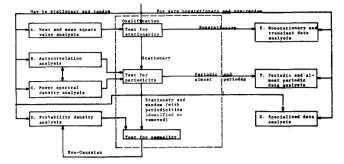

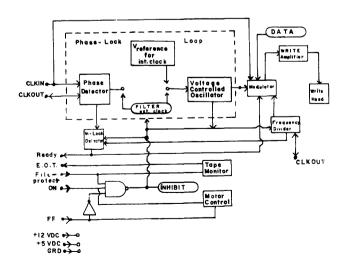

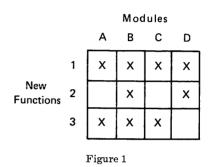

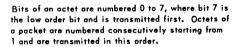

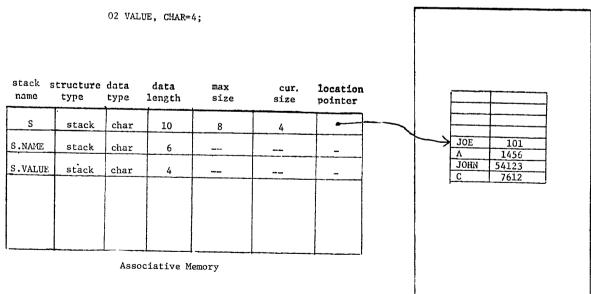

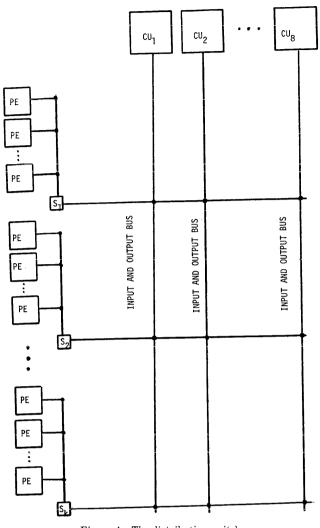

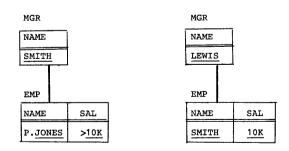

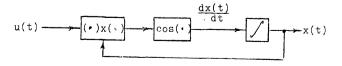

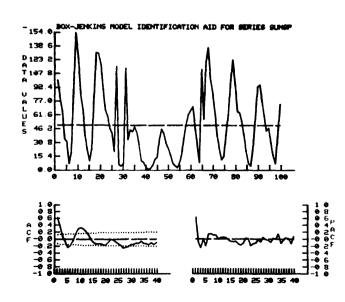

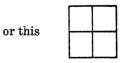

The program for this 45th Conference is structured into three areas. Each in a sense is a conference within the conference and each area is further divided into four affinity groupings or tracks. These are shown in the Conference-at-a-Glance which is reproduced here as Figure 1. The program is intended to mirror the current state of our profession and industry and this volume of conference proceedings is a selected distillation of the program.

# PAST IS PROLOGUE

As everyone knows, the digital computer did not arrive from outer space in 1951. The story of the steady progression of machines from the Jacquard loom, the Babbage Analytic Engine, the Hollerith Electric Tabulating Machine, the IBM Electronic Multiplier and the ENIAC to present computer systems is familiar. In this volume, Professor Heinz Zemanek recounts the less known tale of pre-computer history in Central Europe.<sup>\*</sup> The reader will discover that Jacquard had predecessors and that the 1890 Austrian Census used punched cards. This event had been made

#### PLENARY SESSIONS

The '76 NCC will include four special plenary sessions open to all conference attendees. Each will be held in the Grand Ballroom of the New York Hilton Hotel and will feature major presentations on issues of particular relevance to the computing field, and to concerned members of the business community and the general public.

#### Keynote Address

Monday, June 7 10:15 a.m. J. Paul Lyet Chairman of the Board Sperry Rand Corporation

#### International Plenary Session

Monday, June 7 1:15 p.m. Chairman: Bob O. Evans President IBM System Communications Division Session Participants Professor A. S. Douglas, University of London Dr. Anatoly A. Dorodnicin, Academician and Director of Computer Systems, USSR Academy of Sciences, Moscow Dr. Heinz Zemanek, Director of IBM Laboratory, Vienna Shiro Omata, President, Nippon Univac Kaisha, Ltd., Tokyo The Computer Profession Tuesday, June 8 1:15 p.m. Chairman: Dr. Ruth M. Davis

Director, Institute for Computer Sciences and Technology National Bureau of Standards Featuring: AFIPS Presidential Address Dr. Anthony Ralston

#### **Public Policy and Computers** Wednesday, June 9

1:15 p.m. Chairman: Janice C. Lipsen President, Counselors for Management, Inc. Featured Address To be Announced

|   | AT A GLANC                                                                                     | /C 1                                                                             | 2                                                                |                                                                                                    | 3                                                        | 4                                                                           | 5                                                |  |  |  |

|---|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

|   |                                                                                                | MONDAY A                                                                         |                                                                  | TUESDAY                                                                                            | TUESDAY                                                  |                                                                             |                                                  |  |  |  |

| _ |                                                                                                | 2:30 pm - 4:00 pm                                                                | 4:15 pm - 5:45 pm                                                | 8:30 am -                                                                                          | 10:00 am                                                 | 10:15 am - 11:45 am                                                         | 2:30 pm - 4:00 pm                                |  |  |  |

|   | A<br>SOCIETAL                                                                                  | Saul Padwo                                                                       | A1-2                                                             | 2 •                                                                                                |                                                          | DATA S                                                                      | ECURITY                                          |  |  |  |

|   | CONCERNS<br>Sutton, NYH                                                                        | WORLD ENVIRONMENT FOR DATA<br>PROCESSING                                         |                                                                  | Eldred C. N<br>DATA SECU<br>THE DOD                                                                |                                                          | Rein Turn A4<br>DATA<br>CRYPTOGRAPHY                                        | Naomi Seligman A<br>DATA SECURITY IN<br>INDUSTRY |  |  |  |

|   | B                                                                                              | B1                                                                               |                                                                  |                                                                                                    | B3                                                       | •                                                                           | PIONEER DAY                                      |  |  |  |

|   | COMPUTER<br>PROFESSION<br>Royal B, AM                                                          | Margaret Fox<br>25 YEARS OF JOINT<br>COMPUTER<br>CONFERENCING                    | Walter Anderson<br>INFORMATION<br>PROCESSING IN<br>THE YEAR 2000 | Anita J. Coc<br>COMPUTIN<br>EUROPE                                                                 | G IN                                                     | John G. Brainerd B4<br>ORIGINS OF ENIAC                                     | Herman Goldstine B<br>DEVELOPMENT OF<br>ENIAC    |  |  |  |

|   | C<br>ISSUES IN                                                                                 | C1<br>Ronald A, Frank                                                            | H. W. Bomzer                                                     | 2 •                                                                                                |                                                          | PUBLIC ACCESS                                                               | TO COMPUTER                                      |  |  |  |

|   | COMPUTING<br>Imperial B, AM                                                                    | ROLE AND<br>OBLIGATIONS OF THE<br>TRADE PRESS                                    | DATA PROCESSING<br>CAREER PATHS                                  | Janet Kiehl<br>PUBLIC AT<br>TOWARD C                                                               | C3<br>TITUDES<br>COMPUTERS                               | Evelyn R. Murphy C4<br>PERSONAL<br>COMPUTERS                                | David H. Ahl<br>PUBLIC ACCESS TO C               |  |  |  |

|   | APPLICATIONS                                                                                   |                                                                                  | D1-2                                                             | 2 •                                                                                                |                                                          | CRIMINAL JUS                                                                | TICE SYSTEMS                                     |  |  |  |

|   | SERVING<br>PEOPLE<br>Grand Ballroom<br>East, NYH                                               | Genevieve Greenwa<br>COMPUTERS IN A                                              | THE ALEME                                                        | Bernice Pantell D3-4<br>THE ALEMEDA COUNTY LAW ENFORCEMENT<br>SYSTEM OF THE FUTURE AND USE OF CRIM |                                                          |                                                                             |                                                  |  |  |  |

|   | E<br>COMPUTER                                                                                  | COMPUTER SYSTEM DESIGN                                                           |                                                                  |                                                                                                    |                                                          |                                                                             |                                                  |  |  |  |

|   | SYSTEMS<br>Grand Ballroom<br>West, NYH                                                         | John C. Davis<br>STORAGE SYSTEMS                                                 | E1-2                                                             | 2 Nancy Betz<br>INTERACTI<br>SYSTEMS                                                               |                                                          | Stephen S. Yau E4<br>COMPUTER SYSTEMS<br>RELIABILITY AND<br>MAINTAINABILITY | Gerald Estrin<br>MODULAR COMPUTE                 |  |  |  |

|   | F                                                                                              | • COMPUTER                                                                       |                                                                  | SYSTEN                                                                                             | SYSTEM MANAGEMENT AND PLANNING                           |                                                                             |                                                  |  |  |  |

|   | SYSTEMS<br>MANAGEMENT<br>Mercury, NYH                                                          | John V. Soden<br>LONG-RANGE PLANNIN<br>USAGE IN LARGE ORGA                       |                                                                  | REQUIREM<br>ESSENTIAL                                                                              | F3-4<br>ENTS AND WORKLOAD<br>ELEMENTS OF                 | David S. Alberts Fi<br>ECONOMICS OF<br>SOFTWARE QUALITY<br>ASSURANCE        |                                                  |  |  |  |

| 5 | G<br>NETWORKING<br>Imperial A, AM                                                              | Peter E. Jackson G1<br>LEGAL & REGULATORY<br>TRENDS IN COMPUTER<br>COMMUNICATION | Ira Cotton G2<br>PROTOCOLS FOR<br>COMPUTER<br>NETWORKS           | 2 Franklin F. I<br>PACKET RA<br>SATELLITE<br>NETWORKS                                              | ADIO &                                                   | Robert E. Kahn G4<br>PROGRESS IN PACKET<br>NETWORK INTER-<br>COMMUNICATION  |                                                  |  |  |  |

|   | H<br>BUSINESS AND                                                                              | H1                                                                               | Ha                                                               | 2 •                                                                                                | WORD                                                     | PROCESSING &                                                                | OFFICE AUTOM                                     |  |  |  |

|   | INDUSTRY<br>SYSTEMS<br>Georgian B, AM                                                          | Carol Johnson<br>ENHANCING LIBRARY<br>SYSTEMS                                    | Greg E. Mellen<br>AIR TRAFFIC<br>CONTROL                         | Harvey L. P.<br>COMMUNIC<br>COMPUTEF<br>PROCESSIN                                                  | ATIONS,<br>AS & WORD                                     | David Farber H4<br>COMPUTERIZED<br>MESSAGE SYSTEMS                          | Howard L. Morgan<br>WORD PROCESSING 8            |  |  |  |

|   | 1                                                                                              | I1<br>Noah S. Prywes                                                             | Liba Svobodova                                                   | 2 •                                                                                                |                                                          | COMPUTER A                                                                  | RCHITECTURE                                      |  |  |  |

|   | COMPUTER &<br>DATA BASE<br>ARCHITECTURE<br>Georgian A, AM                                      | IMPACT OF AUTO.<br>OF SYST. DESIGN<br>ON DATA BASE<br>ARCHIT.                    |                                                                  | Yaohan Chu<br>HIGH LEVEL LANGUAGE<br>ARCHITECTURE                                                  |                                                          | I3-4<br>E COMPUTER                                                          | Anne M. Gulick IS<br>MULTIPROCESSING             |  |  |  |

| í | J                                                                                              | Margaret Butler J1 Alan G. Merten J2                                             |                                                                  | 2 •                                                                                                | s                                                        | OFTWARE DESIG                                                               | N & ENGINEERI                                    |  |  |  |

|   | SOFTWARE<br>Trianon, NYH                                                                       | SOFTWARE SHARING                                                                 | Edward You<br>STRUCTUR                                           |                                                                                                    | Raymond T. Yeh<br>SOFTWARE ENGINEE<br>EXPECT IN THE NEXT |                                                                             |                                                  |  |  |  |

|   | к                                                                                              |                                                                                  | K1-2                                                             | 2                                                                                                  | КЗ                                                       | К4                                                                          |                                                  |  |  |  |

|   | COMPUTER Nathaniel Macon<br>SCIENCE COMPUTER ARITHMETIC AND NUMERICAL<br>Gramercy, NYH METHODS |                                                                                  | James S. Ke<br>TECHNOLO<br>FORECASTI                             | GICAL                                                                                              | Joyce A. Amenta<br>SOFTWARE<br>FOR                       | Murray Turott<br>IMPLEMENTATION OF<br>CONFERENCING SYST                     |                                                  |  |  |  |

| B3<br>Anita J. Cochran                                                              | •                                                                           | PIONEER DAY                                                                                   | •                                                                            |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| COMPUTING IN<br>EUROPE                                                              | John G. Brainerd B4<br>ORIGINS OF ENIAC                                     | Herman Goldstine B5<br>DEVELOPMENT OF<br>ENIAC                                                | Richard E. Merwin B6<br>POST-ENIAC<br>TRANSFER OF<br>TECHNOLOGY              |  |  |  |  |

| •                                                                                   | PUBLIC ACCESS                                                               | TO COMPUTERS                                                                                  | •                                                                            |  |  |  |  |

| Janet Kiehl C3<br>PUBLIC ATTITUDES<br>TOWARD COMPUTERS                              | Evelyn R. Murphy C4<br>PERSONAL<br>COMPUTERS                                | David H. Ahl<br>PUBLIC ACCESS TO CO                                                           | C5-6<br>MPUTER POWER                                                         |  |  |  |  |

| •                                                                                   | CRIMINAL JUST                                                               | TICE SYSTEMS                                                                                  | •                                                                            |  |  |  |  |

| Bernice Pantell<br>THE ALEMEDA COUNTY<br>SYSTEM OF THE FUTUR                        | Thomas J. Madden<br>CRIMINAL JUSTICE INF<br>AND USE OF CRIMINAL             | D5-6<br>ORMATION SYSTEMS<br>RECORDS                                                           |                                                                              |  |  |  |  |

| COMPUTER SYS                                                                        | STEM DESIGN                                                                 |                                                                                               | •                                                                            |  |  |  |  |

| Nancy Betz E3<br>INTERACTIVE<br>SYSTEMS                                             | Stephen S. Yau E4<br>COMPUTER SYSTEMS<br>RELIABILITY AND<br>MAINTAINABILITY | Gerald Estrin<br>MODULAR COMPUTER                                                             | E5-6<br>DESIGN                                                               |  |  |  |  |

| SYSTEM MANA                                                                         | GEMENT AND                                                                  | PLANNING                                                                                      | •                                                                            |  |  |  |  |

| Edward O. Joslin<br>ECONOMIC REQUIREME<br>ANALYSIS: ESSENTIAL I<br>SYSTEMS ANALYSIS |                                                                             | David S. Alberts F5<br>ECONOMICS OF<br>SOFTWARE QUALITY<br>ASSURANCE                          | David S. Alberts F6<br>FUTURE DIRECTIONS<br>IN SOFTWARE<br>QUAL. ASSUR.      |  |  |  |  |

| Franklin F. Kuo G3<br>PACKET RADIO &<br>SATELLITE<br>NETWORKS                       | Robert E. Kahn G4<br>PROGRESS IN PACKET<br>NETWORK INTER-<br>COMMUNICATION  | Louis Pouzin G5<br>INTERACTIONS BE-<br>TWEEN PRIVATE &<br>PUBLIC DATA NET-<br>WORKS IN EUROPE | G6<br>(SEE "SECURITY<br>IN COMPUTER<br>NETWORKS"<br>ABOVE.)                  |  |  |  |  |

| • WORD                                                                              | PROCESSING &                                                                | OFFICE AUTOMA                                                                                 | TION .                                                                       |  |  |  |  |

| Harvey L. Poppel H3<br>COMMUNICATIONS,<br>COMPUTERS & WORD<br>PROCESSING            | David Farber H4<br>COMPUTERIZED<br>MESSAGE SYSTEMS                          | Howard L. Morgan<br>WORD PROCESSING & 0                                                       | H5-6<br>OFFICE AUTOMATION                                                    |  |  |  |  |

| •                                                                                   | COMPUTER AF                                                                 | CHITECTURE                                                                                    | •                                                                            |  |  |  |  |

| Yaohan Chu<br>HIGH LEVEL LANGUAGE<br>ARCHITECTURE                                   | COMPUTER                                                                    | Anne M. Gulick 15<br>MULTIPROCESSING                                                          | Tomlinson Rauscher 16<br>DEVEL. APPLIC.<br>ORIENTED COMPUTER<br>ARCHITECTURE |  |  |  |  |

| • \$(                                                                               | SOFTWARE DESIGN & ENGINEERING                                               |                                                                                               |                                                                              |  |  |  |  |

| Edward Yourdon<br>STRUCTURED DESIGN                                                 | J3-4                                                                        | Raymond T. Yeh<br>SOFTWARE ENGINEERI<br>EXPECT IN THE NEXT D                                  |                                                                              |  |  |  |  |

| К3                                                                                  | K4                                                                          |                                                                                               | K5-6                                                                         |  |  |  |  |

| James S. Ketchel<br>TECHNOLOGICAL<br>FORECASTING                                    | Joyce A. Amenta<br>SOFTWARE<br>FOR<br>SYSTEMS                               | Murray Turoff<br>IMPLEMENTATION OF C<br>CONFERENCING SYSTE                                    |                                                                              |  |  |  |  |

| ARTIFICIAL IN                                                                       | ITELLIGENCE                                                                 |                                                                                               | •                                                                            |  |  |  |  |

L3-4 Marvin Minsky & L5 Seymour Papert ARTIFICIAL INTELLI-GENCE & EDUCATION

L5

Leonard Friedman L6

THE PRESENT AND FUTURE OF MOBILE ROBOTS

5

6

4:15 pm - 5:45 pm

A5 Dennis K. Branstad A6 SECURITY IN COM-PUTER NETWORKS

٠

TUESDAY AFTERMOON

Royal A, AM NYH - NEW YORK HILTON

APPLICATIONS

OF COMPUTER SCIENCE

٠

Saul Amarel & Edward Feigenbaum APPLIC. OF ARTIFICIAL INTELL. TO SCIENCE & MEDICINE

CONFERENCE AT A GLANCE

COMPUTERS AND PEOPLE

SCIENCE AND TECHNOLOGY

SYSTEMS

1

2

3

4

AM . AMERICANA

Figure 1-Conference at a Glance

L1-2

Iris Kameny

INFERENCE SYSTEMS AND SPEECH RECOGNITION AND UNDERSTANDING

|                      | CONFERENCE A                                              | TAGLANCE (contin<br>7                                                                                 | ued)<br>8                                                              | 9                                                               | 10                                                                                                                          | 11                                                                                                                                              | 12                                                                          | 13                                                                            | 14                                                 |  |

|----------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------|--|

|                      |                                                           | WEDNESDA                                                                                              | MORNING                                                                | WEDNESDAY                                                       | AFTERNOON                                                                                                                   | THURSDAY MOINING                                                                                                                                |                                                                             | THURSDAY AFTERNOON                                                            |                                                    |  |

|                      |                                                           | 8:30 am - 10:00 am                                                                                    | 10:15 am - 11:45 am                                                    | 2:30 pm - 4:00 pm                                               | 4:15 pm - 5:45 pm                                                                                                           | 8:30 am - 10:00 am                                                                                                                              | 10:15 am - 11:45 am                                                         | 2:30 pm - 4:00 pm                                                             | 4:15 pm - 5:45 pm                                  |  |

| <b></b>              | A                                                         | •                                                                                                     | PUBLIC POLI                                                            | CY ISSUES I                                                     | •                                                                                                                           | •                                                                                                                                               | PUBLIC POLI                                                                 | CY ISSUES II                                                                  | •                                                  |  |

|                      | SOCIETAL<br>CONCERNS<br>Sutton, NYH                       | Frank D. De George A7<br>WELFARE PAYMENTS<br>AND THE COMPUTER                                         | Marilyn E. Courtot A8<br>DATA BANKS IN<br>THE FEDERAL<br>ESTABLISHMENT | Anthony J. Patinella A9<br>EFTS: THE POLICY<br>QUESTIONS        | William R. Weber A10<br>EFTS: IMPLEMENTA-<br>TION PROBLEMS                                                                  | Neal Gregory A11<br>DATA COMMUNICA-<br>TION POLICY                                                                                              | Francis Gregory A12<br>PRIVACY: THE POLICY<br>QUESTIONS                     | John Salasin<br>PRIVACY: THE PSYCHO<br>SOCIOLOGICAL IMPLIC                    | A13-14<br>LOGICAL &<br>ATIONS                      |  |

| ۳                    | B<br>COMPUTER<br>PROFESSION<br>Royal B. AM                | • COMPUT                                                                                              | RS AND THE PH                                                          | IYSICALLY HAND                                                  | ICAPPED .                                                                                                                   | B11                                                                                                                                             | B12                                                                         | B13                                                                           |                                                    |  |

| AND PEOP             |                                                           | Robert Gildea B7<br>COMPUTERIZED<br>BRAILLE<br>TRANSLATION                                            | Steven L. Jamison B8<br>COMPUTERS AND<br>SIGN LANGUAGE                 | Harry G. Hedges B9<br>COMMUNICATION<br>AIDS FOR THE<br>NON-ORAL | Harry G. Hedges B10<br>READING MACHINES<br>FOR THE BLIND                                                                    | Gopal K. Kapur<br>EXECUTIVE MANAGE-<br>MENT MUST BECOME<br>INVOLVED                                                                             | Roy F. Keller<br>CONCEPTS IN PRO-<br>GRAMMING AND ADP<br>INSTRUCTIONAL SYS. | Louise Etra<br>COMPUTER ART:<br>NEW BREED OF<br>ARTIST TECHNICIAN             | Patsy Scala<br>ARTISTS & THEIR<br>USE OF COMPUTERS |  |

| RS                   | c                                                         | • INDU                                                                                                | STRY & UNIVER                                                          | SITY RELATIONS                                                  | HIPS •                                                                                                                      | •                                                                                                                                               | SOFTWARE P                                                                  | RODUCTIVITY                                                                   | •                                                  |  |

| COMPUTERS AND PEOPLE | ISSUES IN<br>COMPUTING<br>Imperial B, AM                  | Marshall C. Yovits C7<br>INDUSTRY NEEDS &<br>VIEWS OF COMPUTER<br>SCIENCE GRADUATES                   | Marshall C. Yovits C8<br>COMPUTER SCIENCE<br>GRADUATES &<br>INDUSTRY   | Marshall C. Yovits<br>INDUSTRY AND UNIVE<br>PROBLEMS AND SOLU   | C9-10<br>RSITY —<br>TIONS                                                                                                   | C9-10 Lloyd Baldwin C11 Eugene I. LowenthalC1<br>PRODUCTIVITY PAY-<br>BACK FROM PACKAGED GUAGES FOR SOFT.<br>APPLICATION SOFT. WARE DEVELOPMENT |                                                                             | Larry A. Weike C13-14<br>QUALITY AND PERFORMANCE<br>MEASUREMENTS FOR SOFTWARE |                                                    |  |

|                      | D<br>APPLICATIONS                                         | •                                                                                                     | MEDICINE AND                                                           | HEALTH CARE I                                                   | •                                                                                                                           | MEDICINE AND HEALTH CARE II                                                                                                                     |                                                                             |                                                                               |                                                    |  |

|                      | SERVING<br>PEOPLE<br>Grand Ballroom<br>East, NYH          | The Thelma Estrin D7 Robert S. Ledley D8<br>COMPUTERS AND COMPUTERIZED                                |                                                                        | Richard Shepard<br>BIOMEDICAL DATA BA                           | D9-10<br>SES                                                                                                                | David J. Mishelevich D11-12 Berrice J. Proctor<br>TOWARD THE INTEGRATED HOSPITAL<br>INFORMATION SYSTEMS MEDICINE                                |                                                                             | D13-14<br>N IN CLINICAL                                                       |                                                    |  |

|                      | E<br>COMPUTER                                             | •                                                                                                     | MICROPRO                                                               | CESSORS                                                         | •                                                                                                                           | •                                                                                                                                               | MINICON                                                                     | APUTERS                                                                       | •                                                  |  |

|                      | SYSTEMS<br>Grand Ballroom<br>West, NYH                    | Reg E. Kaenel<br>UNDERSTANDING AND<br>MICROPROCESSORS                                                 | E7-8                                                                   | Barry R. Borgerson<br>MICROPROCESSOR SY                         | STEMS                                                                                                                       | S. Ron Oliver<br>MINIS VS. MAXIS                                                                                                                | E11-12                                                                      | Carol Erown<br>USING MINIS IN LARGE<br>SMALL BUSINESSES                       | E13-14<br>AND                                      |  |

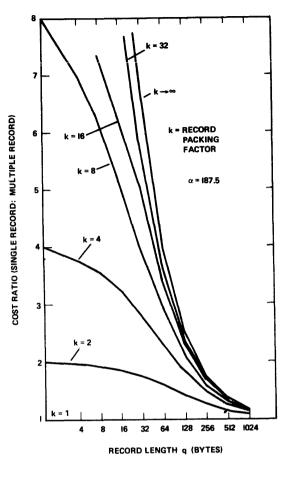

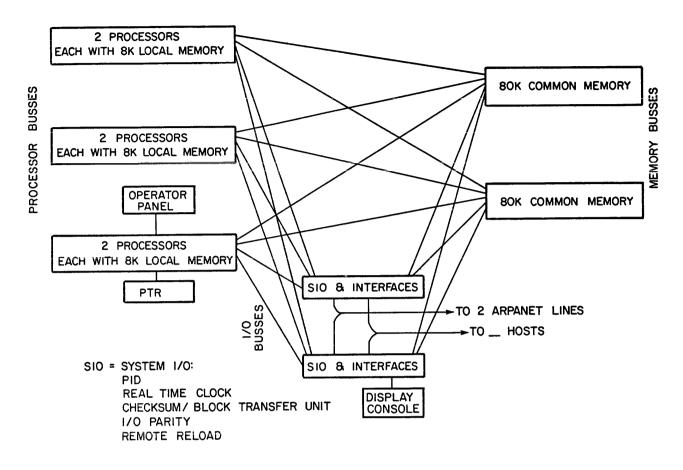

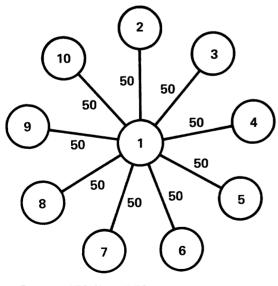

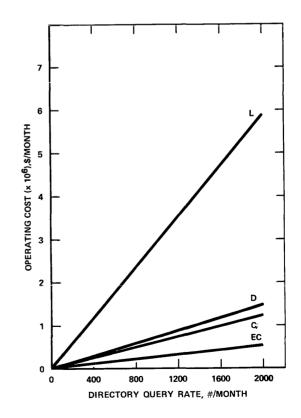

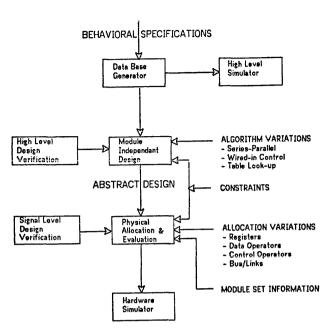

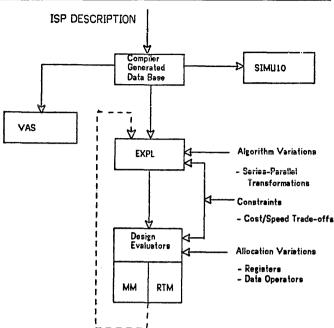

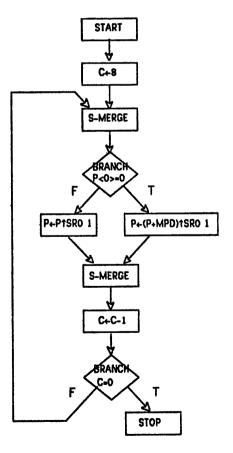

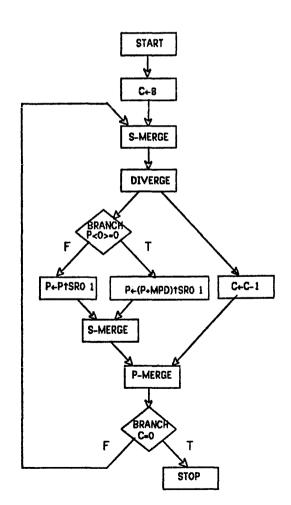

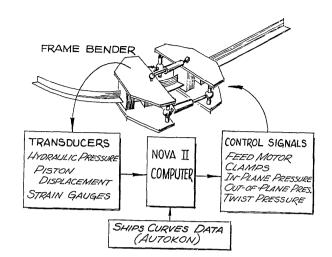

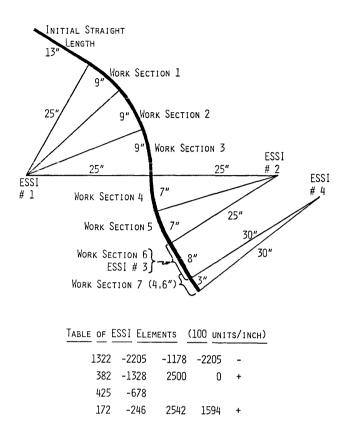

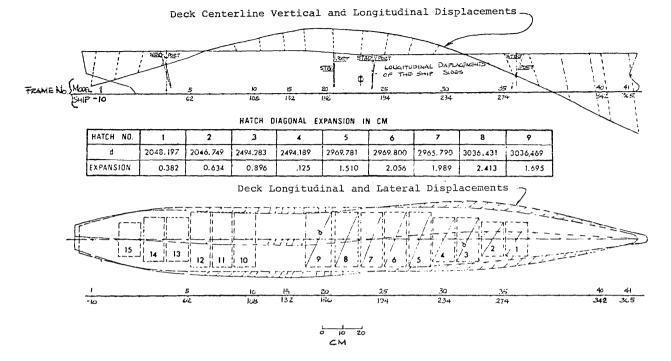

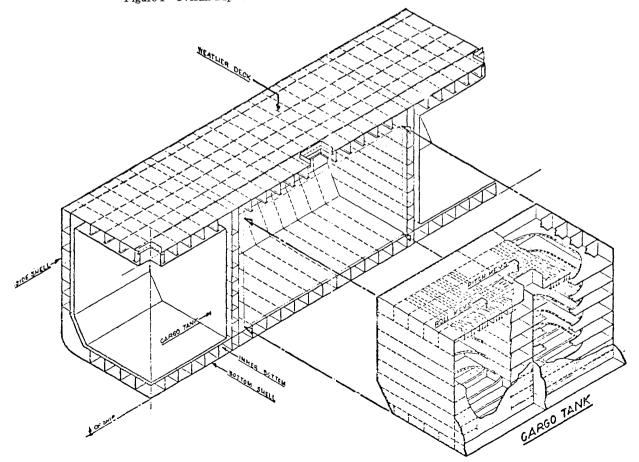

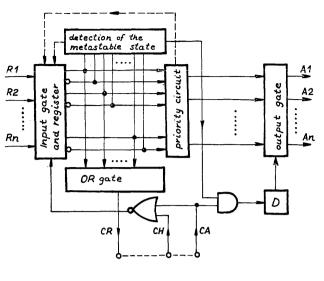

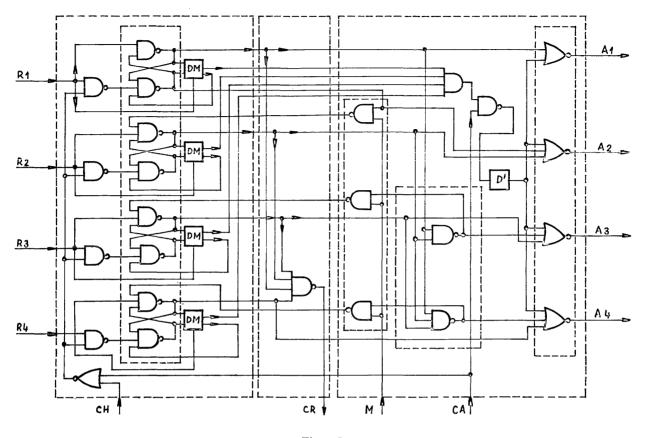

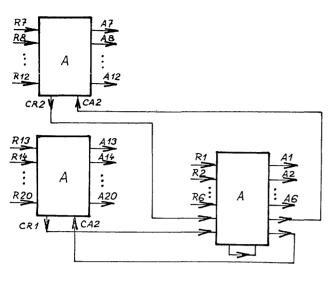

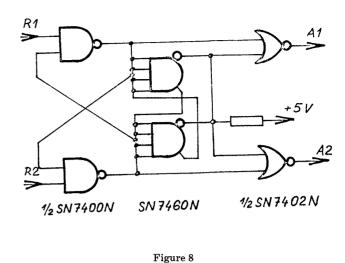

|                      | F                                                         | COMPUTE                                                                                               | R SYSTEM PERFO                                                         | DRMANCE & EVA                                                   | LUATION I .                                                                                                                 | COMPUTER                                                                                                                                        |                                                                             |                                                                               |                                                    |  |