## Proceedings of the

# WESTERN JOINT COMPUTER CONFERENCE

February 26-28, 1957 Los Angeles, Calif.

Sponsors:

THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS **Committee on Computing Devices** THE ASSOCIATION FOR COMPUTING MACHINERY

# PROCEEDINGS OF THE WESTERN JOINT COMPUTER CONFERENCE

PAPERS PRESENTED AT THE JOINT IRE-AIEE-ACM COMPUTER CONFERENCE LOS ANGELES, CALIF., FEBRUARY 26-28, 1957

Sponsors

THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices THE ASSOCIATION FOR COMPUTING MACHINERY

> Published by The Institute of Radio Engineers I East 79th Street, New York 21, N. Y. for the Joint Computer Committee

#### ADDITIONAL COPIES

Additional copies may be purchased from the following sponsoring societies at \$4.00 per copy. Checks should be made payable to any one of the following societies:

> INSTITUTE OF RADIO ENGINEERS 1 East 79th Street, New York 21, N. Y.

AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS 33 West 39th Street, New York 18, N. Y.

ASSOCIATION FOR COMPUTING MACHINERY 2 East 63rd Street, New York 21, N. Y.

Copyright © 1957 THE INSTITUTE OF RADIO ENGINEERS

#### LIST OF EXHIBITORS

| ALADDIN RADIO INDUSTRIES, INC<br>AMP, INC<br>AUTONETICS<br>BENDIX COMPUTER DIVISION<br>BERKELEY DIVISION OF BECKMAN INSTRUMENTS | Los Angeles, Calif.<br>Harrisburg, Pa.<br>Downey, Calif.<br>Los Angeles, Calif. |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| INC                                                                                                                             | Richmond, Calif                                                                 |

| C. P. CLARE & CO                                                                                                                | Chicago, Ill.                                                                   |

| COLEMAN ENGINEERING CO., INC                                                                                                    | Los Angeles, Calif.                                                             |

| COMPUTER CONTROL CO., INC                                                                                                       | Wellesley, Calif.                                                               |

| ELECTRODATA DIVISION OF BURROUGHS CORP                                                                                          | Pasadena, Calif.                                                                |

| ELECTRONIC ASSOCIATES.                                                                                                          | Long Branch, N. J.                                                              |

| ELECTRONIC ENGINEERING CO. OF CALIF                                                                                             | Los Angeles, Calif.                                                             |

| ENCYCLOPEDIA BRITANNICA                                                                                                         | Los Angeles, Calif.                                                             |

| ENGINEERED ELECTRONICS CO                                                                                                       | Santa Ana, Calif.                                                               |

| FERRANTI ELECTRIC, INC.                                                                                                         | Brooklyn, N. Y.                                                                 |

| FRIDEN CALCULATING MACHINE CO., INC                                                                                             | San Leandro, Calif.                                                             |

| G. M. GIANNINI & CO., INC                                                                                                       | Monrovia, Calif.                                                                |

| HUGHES AIRCRAFT CO                                                                                                              | 57                                                                              |

| INTERNATIONAL BUSINESS MACHINES CORP                                                                                            | New York, N. Y.                                                                 |

| LIBRASCOPE, INC.                                                                                                                | Glendale, Calif.                                                                |

| F. L. MOSELEY CO                                                                                                                | Pasadena, Calif.                                                                |

| G. E. MOXON SALES.                                                                                                              | San Mateo, Calif.                                                               |

| NORDEN-KETAY CORP.                                                                                                              | Gardena, Calif.                                                                 |

| PERLMUTH INSTRUMENTS ENTERPRISES                                                                                                | Los Angeles, Calif.                                                             |

| RAMO-WOOLDRIDGE CORP                                                                                                            | Los Angeles, Calif.                                                             |

| J. B. REA COMPANY, INC                                                                                                          | Santa Monica, Calif.                                                            |

| REMINGTON-RAND.                                                                                                                 | New York, N. Y.                                                                 |

| T. LOUIS SNITZER CO                                                                                                             | Los Angeles, Calif.                                                             |

| SOROBAN ENGINEERING, INC                                                                                                        | Melbourne, Fla.                                                                 |

| SPRAGUE ELECTRIC CO                                                                                                             | North Adams, Mass.                                                              |

| STROMBERG CARLSON                                                                                                               | San Diego, Calif.                                                               |

| TELEMETER MAGNETICS, INC                                                                                                        | Los Angeles, Calif.                                                             |

| UNDERWOOD CORP                                                                                                                  | Long Island City, N. Y.                                                         |

| JOHN WILEY AND SONS, INC                                                                                                        | New York, N. Y.                                                                 |

#### NATIONAL JOINT COMPUTER COMMITTEE

#### Chairman

M. M. Astrahan International Business Machines Corp. San Jose, California

#### **IRE** Representatives

D. Haagens Underwood Corporation Long Island City, New York

L. Nofrey Marchant Research, Inc. Oakland, California

N. H. Taylor M.I.T. Lincoln Laboratories Lexington, Massachusetta

W. S. Speer Norden-Ketay Corporation Gardena, California

#### Vice-Chairman

N. H. Taylor M.I.T. Linco'n Laboratories Lexington, Massachusetts

#### **AIEE** Representatives

J. G. Brainerd University of Pennsylvania Philadelphia, Pennsylvania

D. C. Ross International Business Machines Corp. Poughkeepsie, New York

F. Kalbach Burroughs Corporation Pasadena, California

H. F. Mitchell, Jr. Sperry Rand Corporation Los Angeles, California

#### ACM Representatives

S. Fernbach University of California Berkeley, California

G. W. King International Telemeter Corp. Los Angeles, California A. Perlis Carnegie Tech. Pittsburgh, Pennsylvania

F. M. Verzuh Massachusetts Institute of Technology Cambridge, Massachusetts

#### **Ex Officio Representatives**

J. W. Carr III (ACM) University of Michigan Ann Arbor, Michigan J. Noe (IRE-PGEC) Stanford Research Institute Menlo Park, California

E. L. Harder (AIEE) Westinghouse Electric Corp. East Pittsburgh, Pennsylvania

#### **Headquarters Representatives**

L. G. Cumming The Institute of Radio Engineers New York, New York J. Moshman Bell Telephone Laboratories Murray Hill, New Jersey

R. S. Gardner American Institute of Electrical Engineers New York, New York

### WESTERN JOINT COMPUTER CONFERENCE COMMITTEE

| Chairman                                                                             | J. L. Barnes, Systems Laboratories Corp.                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Associate Chairman                                                                   | W. F. Gunning, Beckman Instruments, Inc.                                                                                                                                                                                                                         |

| Secretary                                                                            | W. S. Speer, Norden-Ketay Corp.                                                                                                                                                                                                                                  |

| Publication Committee, Chairman                                                      | G. W. King, International Telemeter Corp.                                                                                                                                                                                                                        |

| Finance Committee, Chairman                                                          | W. H. Ware, The RAND Corp.<br>T. O. Ellis, The RAND Corp.<br>K. W. Uncapher, The RAND Corp.                                                                                                                                                                      |

| Technical Program Committee                                                          |                                                                                                                                                                                                                                                                  |

| Chairman<br>Applications Paper Review<br>Digital Paper Review<br>Analog Paper Review | <ul><li>L. G. Walters, Aeronutronic Systems, Inc.</li><li>M. J. Mendelson, Norden-Ketay Corp.</li><li>C. L. Wanlass, Aeronutronic Systems, Inc.</li><li>I. Pfeffer, Ramo-Wooldridge Corp.</li></ul>                                                              |

| Local Arrangements Committee                                                         |                                                                                                                                                                                                                                                                  |

| Chairman<br>Printing, Sub-Chairman                                                   | E. Tomash, Telemeter Magnetics, Inc.<br>R. Singman, Sperry Rand Corp.<br>R. Bohrer, Sperry Rand Corp.                                                                                                                                                            |

| Registration                                                                         | A. C. Bellanca, Telemeter Magnetics, Inc.<br>J. Tupac, The RAND Corp.<br>J. Seidman, National Cash Register Co.                                                                                                                                                  |

| Exhibits, Sub-Chairman                                                               | <ul><li>N. Potter, Douglas Aircraft Company</li><li>G. P. West, Ramo-Wooldridge Corp.</li><li>D. Weinberg, Ramo-Wooldridge Corp.</li><li>E. Ward, Ramo-Wooldridge Corp.</li></ul>                                                                                |

| Public Relations, Sub-Chairman                                                       | S. D. Wanlass, Aeronutronic Systems, Inc.<br>R. Rodrigues, Aeronutronic Systems, Inc.                                                                                                                                                                            |

| Trips<br>Women's Activities<br>Computer Mailing List, Sub-Chairman                   | <ul> <li>J. F. Donan, Clary Corporation</li> <li>V. Clark, Systems Laboratories Corp.</li> <li>W. A. Farrand, North American Aviation, Inc.</li> <li>L. Kilpatrick, North American Aviation, Inc.</li> <li>I. Marshall, North American Aviation, Inc.</li> </ul> |

#### MEMORIAL TO JOHN VON NEUMANN

The 1957 Western Joint Computer Conference herewith honors the memory of Dr. John Von Neumann. One of the world's greatest mathematicians in our age, Johnny, as we admiringly called him, made many basic contributions to both the theory and practice of electronic digital computers. While we are sad when we think of the tragic loss from his early death, we recall with much pleasure the brilliant and beautiful example which he set us in his work. Let us emulate his humble behavior, his clear logic, and his deep penetration as we carry on the important work on automatic computation.

#### FOREWORD

For a number of years the East and West Coasts have been the setting for Joint Computer Conferences, sponsored by the Institute of Radio Engineers, the American Institute of Electrical Engineers, and the Association for Computing Machinery, where designers, users, and other interested personnel exchange information on electronic computing equipment. As in the past, a balance between analog and digital computing techniques is maintained. The theme this year is

"Techniques for Reliability."

JOHN L. BARNES Conference Chairman

ţ

#### TABLE OF CONTENTS

| Introductory Remarks                                                                                                    | 9     |

|-------------------------------------------------------------------------------------------------------------------------|-------|

| Keynote Address-Techniques for Reliability in Computers for Weapon Control                                              | 10    |

| Computers with European AccentsArthur L. Samuel                                                                         | 14    |

| Reliability from a System Point of View                                                                                 | 18    |

| Design of Experiments for Evaluating ReliabilityJohn Hoffmann                                                           | 20    |

| Reliability and the Computer                                                                                            | 27    |

| A Digital System Simulator                                                                                              | 31    |

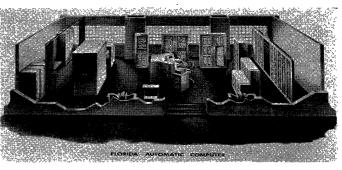

| A New Input-Output Selection System for the Florida Automatic Computer (FLAC)                                           | 37    |

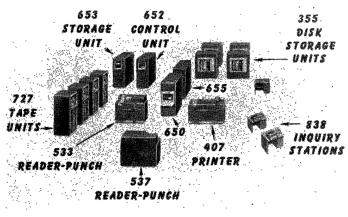

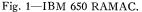

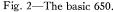

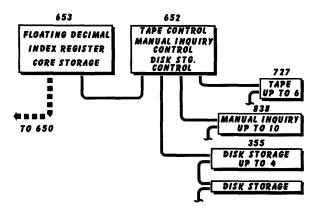

| The IBM 650 RAMAC System Disk Storage OperationDavid Royse                                                              | 43    |

| The IBM 650 RAMAC Inquiry Station Operation                                                                             | 49    |

| An RCA High-Performance Tape-Transport System                                                                           | 52    |

| A Medium-Speed Magnetic Core Memory                                                                                     | 57    |

| Millimicrosecond Transistor Current Switching Techniques                                                                | 68    |

| The Utilization of Domain-Wall Viscosity in Data-Handling Devices                                                       | 73    |

| Reliability in Business Systems                                                                                         | 81    |

| On Prediction of System Performance from Information on Component PerformanceJoan R. Rosenblatt                         | 85    |

| Evaluation of Failure Data                                                                                              | 94    |

| Accuracy Control Systems for Magnetic-Core Memories                                                                     | 105   |

| Design of a Basic Computer Building Block                                                                               | 110   |

| Error Detection in Redundant Systems                                                                                    | 115   |

| Analog Logarithmic and Antilogarithmic Circuits Using Switching Transistors                                             | 121   |

| High-Speed Digital-to-Analog Conversion by Integration of a Variable-Rate Pulse Train                                   | 128   |

| A Reliable Method of Drift Stabilization and Error Detection in Large-Scale Analog Computers                            | 133   |

| A New Method of Verifying Analog Computer Problems and Performances                                                     | . 138 |

| The Lincoln TX-2 Computer Development                                                                                   | 143   |

| A Functional Description of the Lincoln TX-2 ComputerJ. M. Frankovich and H. P. Peterson                                | 146   |

| The Lincoln TX-2 Input-Output SystemJames W. Forgie                                                                     | 156   |

| Memory Units in the Lincoln TX-2                                                                                        | 160   |

| Transistor Circuitry in the Lincoln TX-2                                                                                | 167   |

| Diagnostic Techniques Improve Reliability                                                                               | 172   |

| Error Detection and Error Correction in Real-Time Digital Computers                                                     | 179   |

| The FORTRAN Automatic Coding SystemJ. W. Backus, R. J. Beeber, S. Best, R. Goldberg, L. M. Haibt, H. L. Herrick,        | 188   |

| The Interpretation and Attainment of Reliability in Industrial Data SystemsBruce K. Smith                               | 198   |

| Accuracy Control in the RCA Bizmac System                                                                               | 202   |

| Continuous Computer Operational Reliability                                                                             | 207   |

| Field Performance of a New Automatic Fault-Locating MeansJ. F. Scully and L. P. Colangelo                               | 211   |

| The Variable Word and Record Length and the Combined Record Approach on Electronic Data-Processing Systems Neal J. Dean | 214   |

| Empirical Explorations of the Logic Theory Machine: A Case Study in HeuristicA. Newell, J. C. Shaw, and H. A. Simon     | 218   |

| Programming the Logic Theory Machine                                                                                    | 230   |

.

# Introductory Remarks

EDWARD P. COLEMAN<sup>†</sup>

HAT does reliability mean? It is not strange to find that the term "reliability" means many things to many people. However, we hope to illuminate a number of these meanings which relate to the art, science, and industry of computing. Typical of many definitions in use today is the following:

"Reliability is the probability of a system performing its purpose adequately for the period of time intended under the environmental conditions encountered."

In introducing the subject, one should speak briefly of some of the past and present trends in reliability. First, we mention the concept of improvement of reliability by the detection of unreliability. In order to isolate, examine, and improve reliability of a system, the reliability engineer puts his best efforts on the unreliability problem. He studies the failures in the system for it is only through corrective action on failed elements in a given system that significant improvement can be made. This technique is an old problem to quality control engineers, who have worked out many standard procedures for detecting unreliability based upon the Shewhart Control Chart and other fundamental contributions of the last quarter of a century.

A second concept, which is almost an economic derivative of the first, is that of improvement of reliability by the prevention of unreliability. Significant advances in reliability procedures are being made today, many of which have as their underlying principle the prevention of unreliability before hardware is put into production.

The placement of emphasis on unreliability appears to be a negative approach, which is standard practice in quality control organizations and which uses this socalled negative approach. In the quality control division of manufacturing industries, parts may be classified as "defective" or "nondefective." At the end of any such inspection, the number of defective parts are counted. If the number of defective parts exceeds a predetermined allowable number, the production process is halted, and

† Univ. of Calif., Los Angeles, Calif.

it may not be resumed until the assignable cause for defective products is found and removed. Thus, the tradition in quality control of "detecting defects" and "preventing defects" seems to have a continued longevity in modern reliability techniques.

This point suggests what might appear to be a paradox. As an organization approaches its objective of the total prevention defects, it would appear to have less and less work to do in the future and ultimately none at all. This kind of thinking has manifested itself in industrial organizations in many forms. It has caused some quality administrators to not proceed first directly to the most important reliability problems. Moreover, it has caused some to attempt to build beautiful and permanent procedures for processing unreliability information. One moment of reasoning will show that reliability engineers are needed most where the going is most difficult and where reliability is least predictable. It goes against better nature to leave a beautiful, consistent, and predictable process with little or no unreliability and proceed to one which is ugly, inconsistent, and unpredictable; but this is the lot of the modern reliability engineer.

There are many terms being used today in reliability considerations. Let us list a few of these:

- *Physical Terms*—Part, item, subassembly, assembly, and system.

- Merit Terms—The term reliability itself as applied to general effectiveness of system. Reliability in supporting equipment and in operations. Minimum acceptable reliability and mean-time to failure.

- Mathematical Terms—Risk, hypothesis, test, random variable, probability, population parameter, sample, and statistic.

- Acceptance and Control Terms—Quality characteristic, rational subgroup, attributes, variables, process average quality, sampling plan, sample size, and operating characteristics function.

We first turn our attention to the fundamental concepts of reliability and then to the various details of the problem.

## Keynote Address—Techniques for Reliability in Computers for Weapon Control

JAMES M. BRIDGES<sup>†</sup>

HE RAPID advances made in computer developments during the past few years have had a profound effect upon the security and economy of the country and upon all our lives. Today, the influence of the high-speed, high-capacity computing machine is being felt throughout our total society: in industry, commerce, science, education, medicine, and in many other areas of human existence and progress. The most significant use of the computer, however, in this era of international instability, is its vital role in maintaining our national security.

Because of my association with the Department of Defense, I am naturally most interested in those computer applications which are of the greatest importance to our defense. I wish I could discuss in detail all the different ways in which various kinds of computing machines are being used throughout the military organization. Since that would not be appropriate here, I am going to limit my remarks to the types of computers used for the dynamic control of weapons and weapons systems.

Since the computer is now essential to the effective performance of all modern weapons and weapons systems, it is obvious that a very high level of reliability is essential. I can assure you that we in the Department of Defense consider that the theme "Techniques for Reliability" is completely appropriate for this Joint Computer Conference.

I shall begin my discussion by presenting a little more detail on the widespread usage of computers in weapon control, together with a few highlights of their developmental history. Perhaps I should make it clear at this point that I use the expression "weapons and weapons system control" to include all computers involved in direct control of weapons such as guns, missiles, torpedoes, rockets, bombs, or aircraft and those involved in such functions as tracking, threat evaluation, and weapon assignment.

Although computing machines have received much publicity over the past few years, I seriously doubt that the vital role they have played in the development of military weapons is generally appreciated.

It is probably not widely known that the fire of naval and army artillery was being controlled with computing devices even before World War I started. I doubt if many appreciate the fact that the precision and capabilities of these weapon control computers have advanced steadily since Hannibal Ford started development of his first computer for naval fire control in 1915, until today practically every offensive or defensive weapon depends for its effective operation upon one or more of these computing devices, some very simple and others even more complex than the largest machines in commercial use today.

On one end of the size-complexity scale is the tiny computer that is packed into the nose of a mediumcaliber bullet to compute the point in space with respect to an air target at which detonation should occur. On the other end of this scale are the huge digital computers in the ground environment of the air defense system, which employ tens of thousands of electron tubes and occupy thousands of square feet of floor space. Between these two extremes of size and complexity are scores of different kinds and sizes of computers, each performing a specific function in the dynamic control of some weapon or weapons system. Although the performance, complexity, and packaging requirements of these many types of control computers differ widely, the need for a high degree of precision and operating reliability is common to all.

Until very recently, all these diversified weapon control computers were of the analog type. Although much development work has been done on digital weapon control computers, to my knowledge there is no digital weapon control computer in actual military service operation.

Because the history of weapon control is truly the history of analog computer development, it may be of interest to review very briefly some of the development highlights. As I mentioned before, the history of the fire-control computer in this country started in 1915 when Hannibal Ford began to develop the first computer to control naval surface-to-surface guns. His early computers, known as "rangekeepers," represented the first application of precision analog techniques to the solution of the gun fire-control problem.

At the conclusion of World War I, the need for control of surface guns against aircraft became apparent, and Ford again pioneered with the development of the first antiaircraft-gun fire-control system. This system, completed in 1926, was designed to handle aircraft having a maximum speed of 95 knots.

The computation in these early analog computers was performed entirely with mechanical cams, differentials, multipliers, component solvers, and integrators. With the exception of the electrical contact-type servos, the reliability of these mechanical analog computers was controlled almost entirely by the mechanical designer

<sup>†</sup> Office of the Assistant Secretary of Defense, Washington, D. C.

and the people in the machine shop. Improvements in the performance of these computers were obtained over the years through a better mathematical understanding of the dynamic fire-control problem and more precision in the design and production of the various mechanical components. In service, the reliability of these mechanical computers was very good.

Just prior to World War II, a basic advance was made in analog computer technology—the introduction of the electrical-electronic computer. These computers used electrical components such as shaped potentiometers, electrical resolvers and synchros, and the servomechanisms were electrically driven with vacuum-tube amplifiers. This new concept resulted in the more rapid solution of the fire-control problem and some reduction in size, weight, and manufacturing cost. Unfortunately, these computers were much less reliable than their mechanical predecessors, primarily because of the poor reliability of the amplifiers. The reasons for this are clear now, although they were not at that time. The problem was twofold. First, the amplifiers were designed by engineers with little background of experience in the design of electron-tube devices and, second, the pressure of war and the rapid changes in requirements did not permit redesign to improve reliability before attempting production. Some of these computers, extremely promising in concept and basic performance, never reached service use because their electronic amplifiers were so unreliable. I might add that even more developmental failures in fire-control computers occurred during World War II because of a reverse situation in which experienced electronics companies tried to design fire-control systems without the necessary background in the basic fire-control problem. The lessons learned were very expensive, but they helped to establish one of the fundamental principles of the modern reliability concept. We know now that to develop a satisfactory and reliable military device requires a thorough understanding of the operational area involved as well as experience in the design techniques employed.

After the basic electrical analog principles were first developed, improvements in analog computers for weapon control came about largely through improved reliability, reduced size, and increased precision of the computing components and, most significantly, as a result of a more sophisticated and scientific understanding and treatment of servomechanism design.

World War II and its forced-draft research and development effort, together with the development of firecontrol radar and more advanced weapons, pushed computer development forward rapidly. Before the war was over, the control of guns, aircraft, bombs, torpedoes, mines, rockets, and even guided missiles was being accomplished with the aid of analog computers.

Near the close of the war, a most significant weapon control concept was developed—the integrated firecontrol system. Prior to this development, it was the practice for military agencies to build up a fire-control system from various pieces procured separately from different companies. As the speed and maneuverability of targets increased, with a corresponding increase in the performance and complexity of a weapon control system, it became necessary to develop the entire system under one system engineering management. The integrated weapon control system, now a more or less uniformly accepted concept, resulted in improved performance and substantial savings in size and weight. This principle of integrated system design must be given careful consideration in all future weapon control developments.

Between World War II and the beginning of the Korean conflict in 1950, the Military Services embarked upon a new era of weapon development generally based upon the kind of war that might be fought in 1960. Development programs which offered only marginal improvement in performance over World War II devices were discontinued, and emphasis in air defense was placed on weapons capable of engaging targets of near-sonic or supersonic velocity in mass saturation attacks. Guns gave way to guided missiles; manual control of interceptor aircraft was considered obsolete and the lethality of nuclear weapons was multiplied many times over.

Requirements for computers for the dynamic control of these new warfare concepts advanced rapidly, and a new kind of computer emerged, one which had the functions of keeping track of a multiplicity of targets, evaluating their threat to certain defended areas, assigning defensive weapons to individual targets and, in some cases, controlling the weapons themselves. The successful instrumentation of a computer to perform this complex of operational functions indicated the desirability if not the necessity—of going to digital techniques.

This was the beginning of the era of "push-button warfare," and with it began a rapid transition in engineering thinking from analog to digital computers for weapon control. There was a lot of opposition to this on the part of many knowledgeable people in the weapon control field, both in the military and outside, most strongly pressed by those involved in airborne weapon control. It was argued that a digital computer of the size and complexity of the then current general-purpose machines could not possibly be condensed into a size and weight that could go into any aircraft. Furthermore, it was argued, even if by some miracle of engineering it could be so compressed, such a machine would contain so many vacuum tubes and other electronic components that it would be completely unreliable in service. (I might add that some of these thoughts are still prevalent among military people.) However, with the promise of more reliable computer components, such as semiconductors and magnetic devices, this opposition gradually softened and a few visionary people throughout the military departments initiated experimental developments of weapon control systems around digital techniques.

Looking at the weapon control picture today, I believe that the change to digital computing techniques is desirable and inevitable. In view of the rapidly increasing complexity of weapons of all kinds, I am convinced that digital methods offer the greatest promise for solving the control problems. Furthermore, the state of the electronic component art justifies the development of digital devices for all new weapon control programs. I believe that, in the future, analog weapon control will play a minor role in the support of digital systems.

I doubt that it is fully appreciated in the weapon control field that the digital computer promises many advantages over the analog device in addition to its greater performance capabilities. By the very nature of its instrumentation, the digital computer has far greater flexibility than an analog device; as a result, a single basic computer design, with only minor modifications, can be applied to the solution of a number of different weapon control problems. This capability has very significant implications with regard to standardization of design, which would result in economy of engineering effort, improved reliability, and enhanced production and logistic posture.

Another advantage that is of some significance in these times of steadily increasing cost of national defense is the fact that a digital computer is considerably cheaper to manufacture and will require less skilled labor. Also, the lead time to get a newly developed digital computer into production should be much less than for an analog device.

To substantiate these advantages, I have some comparative information on an airborne digital computer which is now entering pilot production as a direct replacement for an analog computer in an existing bombing-navigation system. It is estimated that the quantity production cost of this digital computer will be about 40 to 50 per cent less than that of the analog computer it replaces. Capital equipment required for production of the digital computer is expected to be reduced by 70 per cent; the requirement for skilled manufacturing labor should be reduced by almost 70 per cent, and the lead time for new production is expected to be reduced by 60 to 70 per cent.

These many potential improvements in the digital weapon control computer are very attractive. But there is a matter of major concern to many military people and systems engineers, which could seriously delay the widespread application of digital computers in weapon systems; that is the fear that system reliability may be seriously decreased. The reliability of electronic devices has not acquired a good reputation among military people, and they know that digital computers are electronic equipments.

I also share this concern, not because the reliability of digital computers cannot be made as good as, or better than, the best analog device now in service, but because, in entering this new field of digital technology, we may not fully use the knowledge of weapon control systems engineering and equipment reliability which has been developing in the electronics and weapons system industry.

The relatively new field of digital computers has been built up primarily around the requirements of the general-purpose machine. As in any new and highly specialized branch of engineering, there is a tendency here that a tightly bound group of specialists may develop, speaking its own language and tending to some extent to break away from other branches of the electronics industry. This has the effect of decreasing the interchange of technical experience—a potentially serious deterrent to both the reliability and systems performance of digital computers in weapon control systems.

As weapon and target capabilities have increased, the basic weapon control problem has changed little. The problem has become more complex and the requirements for solution more exacting, but the fundamental principles are the same. The only thing we are doing differently with digital techniques is to solve an old problem with new mechanization. We can waste a lot of time and engineering resources in this inevitable transition from analog to digital computing techniques if we do not make maximum and continued use of the weapon control know-how that has been built up in this country over the past quarter of a century.

We can suffer even greater losses if the proven reliability concepts and techniques established through years of hard work and cooperative effort on the part of industry and the military departments are not applied to the fullest extent in the military digital-computer field. After all, to obtain reliability, the techniques which must be applied in design, test, manufacture, operation, and maintenance are no different for a digital computer than for any other military electronic device of comparable complexity. Unquestionably, such methods as self-checking, which can be applied so readily to digital computers, will greatly assist in service maintenance, but they will not improve the operational reliability of a weapon system such as a guided missile or a highperformance interceptor aircraft.

With present techniques and components, I am convinced that we can design digital weapon system computers which will be more reliable than the best electronic equipment now in service. In a progress report on reliability of military electronic equipment, given before the Third National Symposium on Reliability and Quality Control on January 14, 1957, I used data on a digital bombing computer as an example of reliability improvement made over the past year. This kind of reliability can be achieved, however, only when the basic design of a device is thoroughly engineered for reliability and adequately tested before production is initiated.

Many times in the past two years I have discussed the basic steps in design, testing, production, procurement, maintenance, and use that are required to obtain a highly reliable military electronic device. I need not repeat these in detail here since they have been published widely in the technical press. But I do want to emphasize that the reliability of any electronic equipment is critically dependent upon the design engineer. If computer designers do not take into proper account the engineering principles controlling reliability, which are now well known, designs will very likely be unreliable in service, regardless of how sophisticated the logic may be and in spite of anything that can be done in the production line or by maintenance. Reliability can be controlled in manufacture and it can be maintained in service, but it can be established only by sound basic engineering in design.

One of the most promising techniques for obtaining reliability in digital computers appears to be the exploitation of their basic inherent flexibility to develop standardized designs of system building blocks. The basic geometry of many weapon control problems is quite similar and can be solved by proper system grouping of similar computer elements. Such a standardized design would make it unnecessary to develop a completely original computer for every new weapon system project and would permit the use of standard computer elements of proven reliability—reliability which could be brought to a very high level through extensive engineering, testing, reengineering, and continued production.

It may be argued that such a philosophy would seriously impede the advancement of digital computer technology. I do not agree. The real advance of digital computers in the weapon control field is going to result from more sophisticated weapon system engineering, advances in logic and improved component parts, not from a continued redesign of circuits and packaging.

At any given time, the same component parts are available to all computer designers—or, at least, they should be. Once circuits and packaging techniques, developed around these components to perform a particular computer function, have demonstrated a high degree of reliability, these circuits and packaging designs should be standardized and used in all applications to weapon control computers where an unacceptable compromise of weapon system performance would not result. Obviously, as new and improved components or techniques become available, new standardized designs should be developed around them. These designs, when proved to be better than those already in existence, should be adopted immediately.

In summarizing the advantages that can accrue to the military users from a design standardization program (some of which I have already mentioned), these factors are significant. The amount of engineering effort, cost and time required to develop a new weapon system would be substantially lessened. Also, the cost of production could be reduced because larger quantities of similar items could be manufactured, thus permitting the utilization of more economical manufacturing processes such as automatic assembly. Furthermore, the lead time required to get a newly designed weapon control system into production would be shorter. Another advantage to be gained from such a standardization program would, of course, consist of improvements in logistics, supply, and service maintenance.

I urge that those who are engaged in the development of digital computers for military weapons systems give careful consideration to this challenging problem of establishing and maintaining design standardization in this field. I can assure you that my office will make every effort to assist in bringing such a standardization philosophy into being as early as possible.

Another important need in connection with reliability in weapon systems employing digital computers is for increased emphasis on systems engineering. At present, digital computers are being developed to work in weapons systems in which other major system components were designed to function with analog computers. The input and output elements of these systems are analog and must be converted to operate with a digital computer. These conversions are costly in equipment complexity and they penalize over-all system reliability. Much more emphasis is needed on the development of various weapon system elements specifically designed to operate in a digital environment so that these costly conversions will not be necessary.

The last technique for reliability that I will present is simplicity. This, again, is a reliability axiom which is not unique to the digital computer field—but I suspect that it may be more difficult to achieve in this field than in other areas of military electronics. By careful design of logic and programming, much can be done to simplify the computer instrumentation in a weapon control system. We must have very careful systems engineering to make certain that we have the simplest system possible and that some of the solutions in the over-all weapon control problem cannot be obtained satisfactorily with less complexity and more reliability by using analog techniques.

In summarizing I would like to present these pertinent conclusions.

1) Because computers are vital to the operation of every modern weapon and weapons system, an extremely high level of operational reliability in these deyices is absolutely mandatory.

2) The trend in weapon control is definitely toward the digital computer, because of its greater flexibility and higher accuracy and its advantages of lower cost, better producibility, shorter lead time, and lower requirements for skilled manufacturing labor.

3) The cooperative effort of the military departments and industry must be directed toward the immediate goal of standardizing the design of digital computer functional building blocks for application to weapon systems.

4) The successful use of digital techniques in weapon control will depend to a large extent upon the application of combined experience in weapon control and digital technology.

5) The techniques for obtaining reliability in a digital computer are fundamentally the same as for any other electronic equipment of similar complexity. The principles for obtaining reliability of military electronics equipment through sound design, testing, and production controls are now fairly well established and should be applied to the fullest extent in new computer designs.

6) Careful attention should be given to systems engineering in the development of a weapon system employing digital computers to ensure that all system components are designed so as to minimize conversion of information between analog and digital forms.

7) Careful consideration should be given to logical design to obtain optimum simplicity of equipment design. Analog techniques should be employed for mechanizing functions where they are best for the purpose. In closing, I would like to emphasize that they who are working in this relatively new field of digital computers have a great obligation in the defense of the country.

Many of the computing devices which are being designed are absolutely essential to military weapons and weapons systems, and they will become progressively more important as the capability and complexity of these systems continue to advance.

Although the challenge of making these new devices sufficiently reliable to be acceptable for military applications is great, there is a substantial background of knowledge and experience in reliability engineering to draw upon.

I see no reason why these new devices should not be completely reliable as they first become available to the using military services. If they are not, the future of digital computers for the dynamic control of weapons may be seriously affected.

### Computers with European Accents ARTHUR L. SAMUEL<sup>†</sup>

S THIS is a luncheon talk, it should contain some humor but there is really nothing very funny about some of the European computer developments which are offering competition to certain unnamed American firms that are trying to peddle their wares in Europe. One of these competing computers, known as the GAMMA 3, is manufactured in France by an organization known as Compagnie des Machines Bull. Compagnie Bull has some 350 of the GAMMA 3 machines in the field. It is primarily a plugboard machine with 64 single-address instructions and can be compared in a general way with the IBM 604, although, more strictly speaking, it occupies a position intermediate between the 604 and the 650, particularly when an 8000-word drum extension unt is attached. The interesting features of this machine are not, however, the size, speed, or relative cost, which after all are quite comparable with American developments, but rather the extensive use of techniques which have never found wide acceptance in the United States. This refers particularly to the use of electromagnetic delay lines as storage elements, and a number of other techniques, the use of which has enabled this moderately small organization to compete with organizations many times its size. This is a virility which belies the all-too-prevalent impression of French decadence.

The same company has recently announced a complete data processing system called the GAMMA 60 which includes a central processing unit with magnetic corestorage. The peripheral equipment includes magnetic drums, magnetic tape units, both card and paper tape readers and punches, lined printers, etc., all under internal stored program control.

Professor F. C. Williams of Manchester University has made many contributions to the computing art, perhaps the most well-known being the cathode-ray storage system to which his name is customarily attached. He has gathered around him at the University a small group of very competent men who have made and are continuing to make substantial contributions. The main location of the Ferranti Company happens to be in Manchester, and, as one might expect, a cooperative arrangement has developed in which Ferranti contributes to the support of a computer project at the University. It profits, in turn, by the developments made there, and manufactures commercial computers embodying some of the University's developments. Several machines of a first design, known as the MARK I, have been made and are in operation at such diverse places as Toronto. Canada, and Rome, Italy. This computer was followed by the MARK I STAR, and more recently the Ferranti Company has announced a new large-scale computer known as the Ferranti MERCURY Computer. This is a high-speed computer, using floating point, with a

<sup>†</sup> Internat'l Business Machines Corp., Poughkeepsie, N. Y.

1024-word core memory, a 16,000-word drum, and 7 index registers and is quite comparable with the larger machines made in this country. A weakness of this, as well as of nearly all other European computers, is its dependence on punched paper tape as the primary input and output medium. This observation may, however, be biased because no one in the United States appears to have produced paper-tape equipment equivalent to that manufactured by the Ferranti Company. Several MERCURY machines are being constructed at the present time. One of the first machines is to go to Manchester University. A second is to go to the Norwegian Research Institute for Defense; a third will be installed at a Computing Center now being planned for the University of London, while Oxford University is getting a fourth. Mr. Brian Pollard, who is in charge of this activity at Ferranti, tells me that they have orders for 17. Altogether, there are some ten different industrial concerns in Great Britain making computers and they are reported to have orders for over 84 large computers on their books at the present time.

During the same symposium, Mr. Bill Elliott covered up a similar display of the letter "F" on the Ferranti PEGASUS Computer, or FPC, by saying that it stood for "Fast." Incidentally, the letter "P" originally stood for "Package." This was later changed to PEGASUS when the Ferranti Company waxed poetic and decided to name all of their computers after stellar constellations.

The Ferranti computer FPC I (to differentiate it from the FPC 3, a commercial version) is an amazingly fast computer in terms of its ability to get work done, although it is basically a small, fairly low-speed machine. These computers are currently being produced; 30 are on order, 2 have been delivered to customers, and one has been installed in a company-operated Computing Center at 21 Portland Place in London.

Most of the computers of Europe are binary rather than decimal. For example, the Swedish Board for Computing Machinery, after first building a relay computer called the BARK, later designed and built an electronic machine called the BESK. As originally built, the BESK was a 40-bit, parallel, asynchronous computer using Williams tube storage; in concept, very much like the Princeton machine.

However, here the resemblance ends. The construction details, the exact circuitry, and all the many different features which give a machine its character were distinctly original. Some of the more original features of this machine are the use of a dielectric paper tape reader which operates at 400 characters a second, and an unusual record for economy in the use of vacuum tubes to achieve the desired results with, of course, an astounding record for reliability. They quote figures like 85 per cent good time on a three-shift basis.

For years the Swedish Board for Computing Machinery has been living on year-by-year appropriations, not unlike the situation confronting certain government-

supported activities in this country. Possibly for this reason the situation became critical roughly a year ago and almost the entire engineering staff left in a body and joined an industrial organization known as Atvidabergs Industries. Dr. Havermark tells me that the present staff consists of 35 members, these being 13 mathematicians, 11 engineers for running and maintenance, 3 keypunch operators, and 8 employees for general administration. This group at Åtvidabergs is now busily engaged in building a copy of the BESK to be called the FACIT which will form the nucleus of a second computer center in Sweden. This machine is an exact copy and, consequently, incorporates all of the improvements which have been made to the original BESK in the last three years, such as the use of a 1024-word magnetic core memory. In addition to this work at Åtvidabergs, the BESK is being copied elsewhere in Sweden and in several different places in Europe. The Svenska Aeroplan AB, known as the SAAB, had, prior to the trouble at the Board, arranged to build a copy for their own use to be called SARA. Another, to be known as the SMIL is under construction at the University of Lund, although this is a stripped down version without core storage.

The Danish Academy for Technical Science is planning a copy of the BESK for their Institute of Computing Machinery, which is to be called the DASK. The Board for Mathematical Machines of the Royal Norwegian Council for Scientific and Industrial Research has also been considering a BESK to supplement the small magnetic drum computer called the NUSSE which was completed in 1953. However, the most recent information seems to indicate that the Norwegian Defense Research Institute is purchasing a Ferranti MERCURY and this may obviate the need for a BESK.

Over-all developments in Europe are following an amazingly similar course to that pursued in the United States, with some striking differences in timing. Many of the earlier machines were built by schools, others by government laboratories—perhaps rather more in proportion than here—and very few by industry. These machines were all plagued by difficulties of completion similar to those experienced in the United States. Recently, industrial concerns have been entering the field in Europe so that there are appearing a number, or are shortly to appear a surprisingly large number, of different machines, some of which are decimal.

Elliott Brothers in Great Britain had early exploited the possibilities of using nickel delay lines for storage and had built a computer known as the NICHOLAS using these lines. As a result of this work, this company was commissioned by the NRDC (the National Research Development Corporation) to build a small computer. This computer, known as the 401, was unique at the time, for its use of a limited number of differently designed package units. After making three copies of the 401, the Elliott organization has gone ahead with a more pretentious design for commercial applications which is now being marketed as the 405 series of machines and for which there are said to be a dozen orders.

Having successfully launched the PEGASUS and the 405, the NRDC is now turning its attention to commercial data processing assemblies, with the word "assembly" used advisedly.

It has contracted elsewhere for the design of an alltransistor-driven core logic and core-store data processing assembly in which the main feature will be a marshalling yard for information external to the computer. The strategic object of this will be to provide a device to which a number of independent keyboard operators can send information in an uncorrelated fashion. This is still in an early stage.

The main preoccupation of the Manchester University group at present is with the input-output facilities of the computer which, as I have indicated, follow European rather than American practice. For example, the Manchester Group has found that a fair proportion of the results printed by their MARK I computer had to be subsequently plotted. They are, therefore, building a cathode-ray plotter which is 80 per cent completed. This plotter uses a 9-inch tube for visual observation and a second tube to be photographed by an automatic camera. Each coordinate of the beam is specified by the least significant 8 digits of a 10-bit word, thus providing a 256  $\times$  256 array of dots which may be used.

Not content with this unit only, they are also building a roughly 10-inch square electroluminescent matrix panel which will plot an array of  $512 \times 512$  points using the power law voltage characteristic of the phosphor to provide the discrimination. They hope to use direct contact photography for recording.

For high-speed numerical output, they are building magnetic tape units which operate at a maximum rate of 1000 characters a second, each character consisting of five binary digits. The magnetic head actually consists of two heads, one for writing and one for reading, separated by 20 mils, the read head being of the static reading variety. Characters are recorded on the tape at a fixed packing density of 50 per inch independent of the tape speed.

Using this same magnetic reading head, they are also constructing a tape editing unit entirely transistorized, with an input power of less than 10 watts, which can be used at teleprinter speeds of approximately 6.7 characters per second.

Turning to storage devices, the Manchester group has obtained a magnetic tape drive unit built by the Pye Company which drives the tape in either direction at a maximum speed of 100 inches a second. They intend to use addressed records, each containing 1280 digits, with the records sequentially addressed and provisions being made to exclude automatically imperfect regions of the tape.

This group is also turning to evaporated ferromagnetic films as a storage medium and they have built an evaporation unit which has all necessary facilities for rotating large substrates at elevated temperatures, etc.

The Manchester group attaches a great deal of importance to its autocoding system which they expect will virtually replace direct coding at a maximum expense for the worst possible case of a factor of 2 in computational speed. They have written a translation program which they liken to the IBM FORTRAN system and they are attempting a general program which will automatically solve any linear second order partial differential equation by finite difference techniques. All in all, this is quite an ambitious program for a small group at a University, but this is the way things are done in England.

Professor Wilkes at Cambridge University built the first modern stored-program computer in England, known as the EDSAC I. This computer is still in operation after many years of useful service, but its days are now numbered, since Professor Wilkes and his able associates are in the midst of building a second computer, the EDSAC II. In fact, that portion of EDSAC II which has been completed has been linked up with a temporary decoder using an abbreviated order code, and this is actually operating. Since this is a portion of the II machine, and since like all machines only 80 per cent completed, Professor Wilkes, in the true British tradition of understatement, calls this machine EDSAC 1.5. Professor Wilkes' group has programmed and has in operation an interpretative routine which will accept program codes for EDSAC I and will execute them faster than they can be run on EDSAC I. A problem in stellar structure is in process on EDSAC 1.5 which is similar to the problem that Hoyle and Haselgrove have just been doing on a 704 in Pasadena.

EDSAC II uses the microprogramming technique in its decoder which came out of the Cambridge work and has been described in the literature. The computer employs a rather unique packaging arrangement in which all of the components for each stage of the arithmetic unit are contained in one pluggable unit. Forty of these units are used to make up the 40-bit accumulator and a substantial number of the same units are used in various other parts of the machine. In terms of order complexity and speed, this machine compares favorably with the better commercial machines. The EDSAC 1.5 will remain in its present form for two or three months when they will begin to install the EDSAC II control matrix.

Professor Biermann of Gottingen is an astrophysicist, and he and his able technical leader, Dr. Heinz Billing, at the Max Planck Institute, have built a series of computers known as the G1, the G1-A, the G2, and now the G3. The G1 is a small drum machine and has piled up an impressive record of 28,000 hours of operation with 82.3 per cent of this as useful time. The G1-A, a modernized version of this machine, is ready for its trial runs. This machine is controlled by photoelectrically read paper tape. Their second machine, the G2, has also been in operation for some time, although it is at the moment down for a general overhaul. However, the G3 is currently of the greatest interest. This is a parallel 40-bit binary machine with floating point arithmetic, designed, as were all of the Gottingen machines, for scientific computing. It will have a core memory for 4096 words and will have adequate indexing features for automatic address modifications. Incidentally, this machine uses a whole word for each instruction, thus reversing the previous practice almost universal in Europe up to now of following the Institute for Advanced Study's practice of confining each instruction to a half word. Wired microprogramming is to be extensively applied in this machine and they are, at the moment, entirely revising their projected order code in an attempt to make it especially efficient for the use of computer programs.

The Max Planck Institute Computer group in Gottingen is shortly to move to Munich. This will make Munich quite an important center as far as computers are concerned since one machine, the PERM, constructed at the Munich Institute of Technology, is already located in this city.

The PERM, a parallel magnetic drum machine, is a cooperative venture between the Electrical Engineering Department under Professor Piloty and the Mathematical Department under Professor Sauer, now Chancellor of the Institute. This is a fine example of a fast drum machine which, with some projected improvements, will become a very good machine indeed. Their drum, which runs at 15,000 rpm, is extremely quiet. At the moment they are just recovering from troubles with the contacts on their pluggable units, these being ordinary tube sockets which had to be replaced—quite a formidable task for such a small group.

One other group in Germany deserves special mention, this being the Institute for Practical Mathematics at Darmstadt under Professor Walther. Their machine, the DERA, a magnetic drum machine operating in floating decimal, is complete as far as construction is concerned and is now going through the final debugging stage. This group has also recently acquired a commercial machine of American design but manufactured in Germany. Work at these three places in Germany has been supported by the German government. A much larger number of universities are shortly to get computers of commercial manufacture. Some of these will be of foreign design, some even of foreign manufacture, but a substantial number of German firms are currently entering the computing field.

The firms of Siemens and Halske in Munich, and Standard Electric of Stuttgart (actually an affiliate of an American firm) are reported to be building transistorized computers. Two firms of the A.E.G. group, Olympia-Werke at Wilhelmhaven, and Telefunken at Backnang, are developing electronic computers. The firm of Zuse KG in Hunfeld, after a successful experience in producing relay machines, is now accepting orders for their Z-22, an electronic computer, about equal to its G1-A.

The ERMETH Computer which was designed at the Swiss Federal Institute of Technology is also a magnetic drum machine, decimal with floating point, which is currently running with a 400-word drum, although ultimately intended to operate with a 10,000-word drum which is currently not in operation because of magnetic head difficulties.

In Holland the Mathematical Center under Dr. van Wijngaarden and the P.T.T. have done work that is particularly worthy of mention. At the P.T.T. a group under Dr. van der Poel has designed a drum computer, called ZEBRA, based on the principles published by Dr. van der Poel. The S.T. & C. organization in England is building several of these machines; the first one should be completed during the next few months. Dr. van der Poel's ideas were quite novel when first proposed, and have been used in the Zuse machine.

There are some transistorized computers in Europe, such as the all-transistor machine built by E. H. Cooke-Yarborough at Harwell in England. There are perhaps a half a dozen other places in Europe where transistor computers are in operation or in an advanced stage of construction. Most of these are rather small experimental machines, and almost without exception they are rather slow by American standards. Transistor production in Europe has lagged behind that in the United States. This is particularly true with respect to high-frequency units, and this lack of transistors has inhibited their extensive use.

There are many other machines that should be mentioned, for example, the work done in the government laboratories in Great Britain, such as the National Physical Laboratories. Their first attempt, known originally as the ACE, was used as a basic design for the machine now being manufactured by the English Electric Company as the DEUCE. Meanwhile, the N.P.L. is going ahead with a new ACE machine which will be several times as fast as the DEUCE.

Europe is perhaps behind the United States in computer developments and we need fear no immediate reversal in relative positions. However, there are many clever people in Europe; they have a tradition in England of achieving a lot with a little, in Germany of thoroughness, and in France of mathematical intuition, to name but three countries. These people are not going to permit us to continue in undisputed mastery of this expanding field. We can expect many new ideas to come from Europe. European accents, this time in computing, may again be heard in this country. European concerns, particularly those in England and in Germany, are known to be looking with envious eyes to the American market and it may not be long before they are offering their wares at prices which will be highly competitive.

### Reliability from a System Point of View

ALEXANDER W. BOLDYREFF†

**THE DEVELOPMENT** of complex electronic and electromechanical systems during the past fifteen years has been guided primarily by considerations of improved performance.

In this development, perhaps the most outstanding factor has been a systematic effort to minimize human error by a maximum utilization of automatic or semiautomatic devices.

While the progress in this direction has been truly remarkable, it has been achieved at the expense of ever increasing complexity and cost.

A few examples will illustrate this point:

1) Number of vacuum tubes on one destroyer:<sup>1</sup>

| Year                     | Numbe <del>r</del><br>of Tubes |  |

|--------------------------|--------------------------------|--|

| <br>1937<br>1944<br>1952 | 60<br>850<br>3200              |  |

2) A modern mobile search radar for ground defense is composed of:

| 500  | vacuum tubes |

|------|--------------|

| 2000 | resistors    |

| 1500 | capacitors   |

300 transformers

as a part of a complete itemization of more than 20,000 replacement parts.

3) The Norden bombsight of World War II could be carried by one man and cost 2500 dollars. The computing bombsights of today weigh between one and two thousand pounds and cost more than a quarter million dollars.

It is not surprising to find associated with this growth in complexity an alarming rate of failure of equipment, and an ever increasing requirement for inspection and maintenance.

Thus, during World War II more aircraft were lost due to deterioration than were lost in combat.<sup>2</sup> Again, quoting from World War II experience:3

1) Sixty per cent of the British radars shipped to the Far East were found defective on arrival. Of the

† The RAND Corp., Santa Monica, Calif., and Univ. of Calif., Los Angeles, Calif.

<sup>1</sup> Prog. Rep. on "Reliability of Electronic Equipment," by the Ad Hoc Group on Reliability of Electronic Equipment for the Com-

Ad Hoc Group on Reliability of Electronic Equipment for the Com-mittee on Electronics of the Research and Development Board, EL 200/17, vol. 1 and 2; February 18, 1952. <sup>2</sup> D. C. Kennard, discussion of paper by J. M. Frankland on "Cri-teria for Specifications," Res. and Dev. Board, Shock and Vibration Bull. No. 17, March, 1951. <sup>8</sup> R. R. Carhart, "The General Problem of Reliability in Missile Systems," The RAND Corp., paper S-4; July 9, 1951.

remaining 40 per cent, arriving in operating condition, half deteriorated on the shelf.

For a set of U.S. bombsights, 60 per cent failed as 2) a result of poor packaging and rough handling, 15 per cent failed due to improper maintenance and overhaul, another 10 per cent of the failures were attributed to poor design.

The situation is no better today, and acceptable performance standards for complex electronic equipment are possible only at the cost of extensive repair and maintenance facilities. For military electronics, an estimate of the maintenance bill is from ten to one hundred times the cost of original equipment. Considering the number and the caliber of technicians required to service adequately existing electronic equipment, it does not seem possible that, if the present trends continue, the training of technicians can keep in step with the demands for their services, particularly in the event of total mobilization.4

The seriousness of the reliability problem has been thoroughly recognized now for a number of years. A great deal of work has been done to acquire a better understanding of this problem. Various methods of improving reliability have been advocated during the past nine or ten years.

It has been pointed out<sup>5</sup> that in the case of aircraft, after nearly half a century of experience, suitable reliability was attained only through redundant design; so that in case of failure of one component, another could be substituted in its place. In this way, even though some kind of failure (requiring emergency service outside the normal maintenance routine) may occur in aircraft every seven and a half hours of flying, the ratio of failure to disaster is ten thousand to one. This ratio is one to one for the systems which are serial in nature, such that the failure of any one component leads to system failure, as, for example, in the case of guided missiles.

Considering the complexity of many systems in use today or in the process of development, it is not surprising that a great deal of emphasis has been placed on the importance of component reliability.6-8

<sup>4</sup> G. B. Devey, "Reliability in electronic equipment," PRoc. IRE, vol. 38, pp. 344-345; April, 1950. <sup>5</sup> L. N. Ridenour, "The Philosophy of Guided Missile Design," Res. and Dev. Board, Shock and Vibration Bull. No. 18; August, 1951.

<sup>&</sup>lt;sup>6</sup> R. Lusser, "A Study of Methods for Achieving Reliability of Guided Missiles," USNAMTC Tech. Rep. 75; July 10, 1950.

<sup>7</sup> R. Lusser, "General Specifications for the Safety Margins Required for Guided Missile Components," USNAMTC Tech. Rep.

<sup>84;</sup> July 10, 1951. 8 R. Lusser, "The Statistical Aspects of Reliability," Electronic Applications Reliability Rev. RETMA, no. 2; 1953.

Particularly noteworthy in this connection are the ARINC Study, the Signal Corps-Cornell University Program, the Vitro Study, the Bell Laboratories Studies, the RETMA, the JETEC, the AGREE, etc.<sup>9</sup>

At the same time, a great deal of effort has been and is being expended on component testing and inspection before they are employed in complex systems. But while all this is highly necessary, it may be far from sufficient to insure sufficiently high reliability of a complex highperformance system.

Let us define reliability as the probability of failurefree operation, for a specified length of time, in a specified environment.

For a serial system of n components, such that the failure of any one component causes system failure, it is possible to estimate the system reliability in terms of the (geometric) mean component reliability.

Consider a system of 500 components. For systems with reliabilities of 0.70 and 0.95, the mean component reliabilities are 0.99929 and 0.99995, respectively. Thus, it may be argued that the reliability of a system can be increased from 0.70 to 0.95 by an improvement in mean component reliability of only 0.07 per cent. But, of course, this reasoning is misleading. Component improvement means decreasing the probability of failure. In the example under discussion, to improve system reliability from 0.70 to 0.95, we would have to decrease the probability of component failure from 0.00071 to 0.00005, and this means that we must eliminate more than 90 per cent of failures for components which are already highly reliable. To do this for each of the very many different components of many complex systems now in the process of design is patently impossible, even at a prohibitive cost in time and money.

Let us return to the definition of reliability. To be operationally significant, this definition must be quantitative; *i.e.*, the reliability of various components, or systems, must be represented by a number. For vacuum tubes, this is frequently expressed in terms of mean life to failure. Unfortunately, this quantity is not a characteristic constant. Thus, a vacuum tube may have a mean life of 10,000 hours in ground equipment, 2500 hours in aircraft, and 13 minutes in a missile.

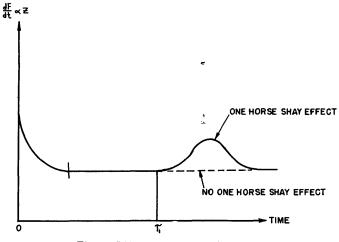

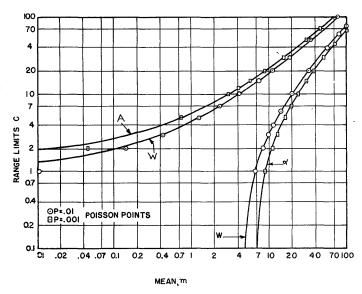

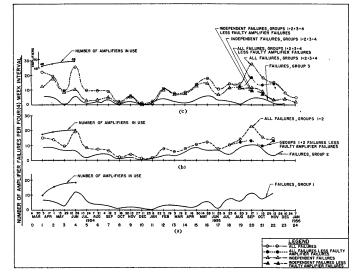

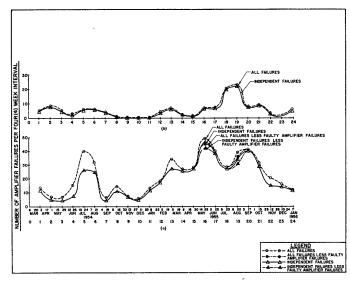

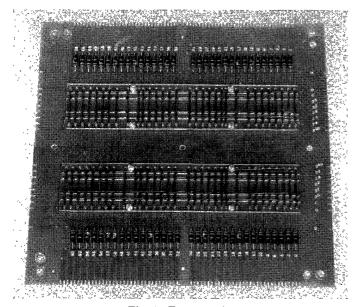

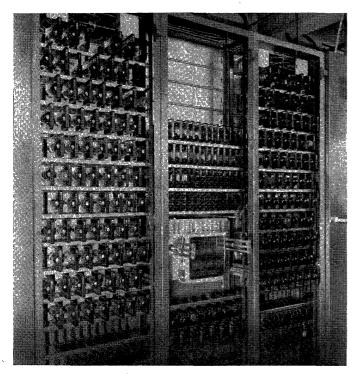

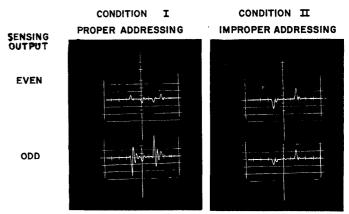

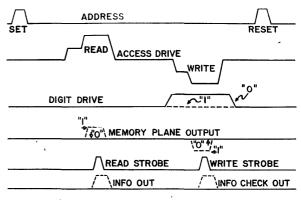

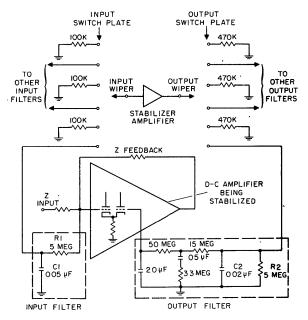

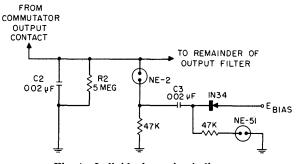

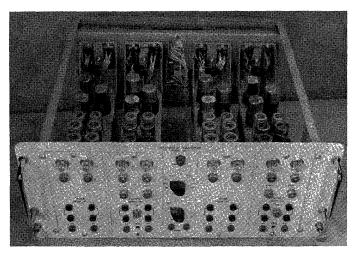

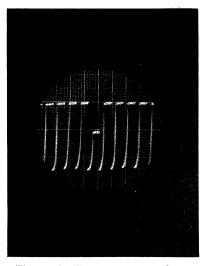

It is, therefore, impossible to speak of the component reliability without specifying the particular system in which it is employed, as well as the way in which the system is going to be used. And this includes the handling, packing, transportation, and storage, as well as the operational use. Certainly the rest of the system constitutes an important, sometimes the most important, part of the environment in which a given component must operate.