## WESTERN JOINT COMPUTER CONFERENCE

February 7-9, 1956

San Francisco, Calif.

Sponsors:

THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices THE ASSOCIATION FOR COMPUTING MACHINERY THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers

## PROCEEDINGS OF THE WESTERN JOINT COMPUTER CONFERENCE

PAPERS PRESENTED AT THE JOINT ACM-AIEE-IRE COMPUTER CONFERENCE, SAN FRANCISCO, CALIF., FEBRUARY 7–9, 1956

Sponsors

THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices THE ASSOCIATION FOR COMPUTING MACHINERY THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers

> Published by the American Institute of Electrical Engineers 33 West 39th Street, New York 18, N. Y. for the Joint Computer Committee

## ADDITIONAL COPIES

Additional copies may be purchased from the following sponsoring societies at \$3.00 per copy. Checks should be made payable to any one of the following societies:

AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS 33 West 39th Street, New York 18, N. Y.

ASSOCIATION FOR COMPUTING MACHINERY 2 East 63d Street, New York 21, N. Y.

> INSTITUTE OF RADIO ENGINEERS 1 East 79th Street, New York 21, N. Y.

> > Copyright 1956

THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS

## Foreword

The ninth Joint Computer Conference which was the fourth Western Meeting under joint sponsorship, was held for the first time in San Francisco this year. The change in the site for this Western Meeting from Los Angeles to San Francisco bespeaks the increased activity and interest in computers on the West Coast.

More emphasis was placed this year than at the past few conferences on the strictly engineering phases of computers. Thirty-eight technical papers were presented, with parallel sessions being used on four occasions. As has become the custom, exhibits of computer systems and components formed a part of the conference program together with a number of inspection trips to local computer installations. The registration of over 1,000, as well as members of the public, was able to inspect exhibits in 39 booths prepared by 25 companies prominent in the computer field.

.

Oliver Whitby Conference Manager Joint Computer Committee of the AIEE-IRE-ACM

Secretary-Treasurer: M. M. Astrahan

Representing AIEE

ROBERT R. BENNETT J. G. BRAINERD

D. C. ROSS P. L. MORTON

**Representing IRE**

DANIEL HAAGENS W. F. GUNNING

J. R. WEINER, Chairman—East OLIVER WHITBY, Chairman—West

**Representing ACM**

C. W. ADAMS J. BARNES

•

D. H. LEHMER H. F. MITCHELL, JR.

**Ex-Officio Representatives**

E. L. HARDER, AIEE

J. H. FELKER, IRE-PGEC

A. S. HOUSEHOLDER, ACM

## **Conference Management Committees**

| Conference Manager OLIVER WHITBYStanford Research Institute                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Secretary-Treasurer                                                                                                                                      |  |

| J. W. HAANSTRA                                                                                                                                           |  |

| Technical Program                                                                                                                                        |  |

| B. J. BENNETT Stanford Research Institute                                                                                                                |  |

| Publications                                                                                                                                             |  |

| A. S. HOAGLAND, ChairmanUniversity of California, Berkeley<br>GORDON MORRISONUniversity of California, Berkeley                                          |  |

| Exhibits                                                                                                                                                 |  |

| G. E. HULSTEDE, ChairmanPacific Telephone & Telegraph Co.<br>H. K. FARRARPacific Telephone & Telegraph Co.                                               |  |

| Publicity                                                                                                                                                |  |

| D. C. HOLMES, ChairmanShell Development<br>BILL EISENLORDShell Development                                                                               |  |

| Registration                                                                                                                                             |  |

| H. W. HARRISON, ChairmanNACA Ames Aerodynamics Laboratories<br>ALAN VOORSANGERSperry-Rand Corporation<br>JACK MAUGHMERUniversity of California, Berkeley |  |

| Hotel Arrangements                                                                                                                                       |  |

| DEXTER STONER, ChairmanPacific Gas & Electric Co.<br>DENNIS FINNIGANStanford Research Institute<br>A. M. PETERSONStanford University                     |  |

| Trips                                                                                                                                                    |  |

| L. C. NOFREY, ChairmanUniversity of California, Radiation<br>WARREN STUVENUniversity of California, Radiation                                            |  |

.

## LIST OF EXHIBITORS

| AIRCRAFT-MARINE PRODUCTS, INC                                      | Harrisburg, Pa.       |

|--------------------------------------------------------------------|-----------------------|

| AMPEX CORPORATION                                                  | Redwood City, Calif.  |

| BECKMAN INSTRUMENTS, INC., Berkeley Division                       | Richmond, Calif.      |

| BENSON-LEHMER CORPORATION                                          |                       |

| BURROUGHS CORPORATION                                              | Philadelphia, Pa.     |

| BURROUGHS CORPORATION, Electronics Instrument Division             | Philadelphia, Pa.     |

| CANNING, SISSON & ASSOCIATES                                       | Los Angeles, Calif.   |

| DENNISON MANUFACTURING COMPANY                                     | Framingham, Mass.     |

| E E C O PRODUCTION COMPANY                                         | Los Angeles, Calif.   |

| ELECTRO DATA CORPORATION.                                          |                       |

| ELECTRONIC ASSOCIATES, INC                                         | Long Branch, N. J.    |

| ENCYCLOPEDIA BRITANNICA                                            | San Francisco, Calif. |

| FRIDEN CALCULATING MACHINE COMPANY, INC                            | Los Angeles, Calif.   |

| HUGHES AIRCRAFT COMPANY<br>INTERNATIONAL BUSINESS MACHINES CORP    | Culver City, Calif.   |

| INTERNATIONAL BUSINESS MACHINES CORP                               | New York, N. Y.       |

| LIBRASCOPE, INC.                                                   |                       |

| LITTON INDUSTRIES                                                  |                       |

| MOSELEY (F. L.) COMPANY                                            |                       |

| MOXON (G. E.) SALES                                                | Culver City, Calif.   |

| NORTH AMERICAN AVIATION, INC.                                      | Los Angeles, Calif.   |

| REA (J. B.) COMPANY, INC                                           | Santa Monica, Calif.  |

| REMINGTON-RAND CORPORATION                                         | New York, N. Y.       |

| SPRAGUE ELECTRIC COMPANY                                           |                       |

| SOROBAN ENGINEERING, INC<br>THE PACIFIC TELEPHONE AND TELEGRAPH CO | Melbourne, Fla.       |

| THE PACIFIC TELEPHONE AND TELEGRAPH CO                             | San Francisco, Calif. |

| THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS                     |                       |

| THE ASSOCIATION FOR COMPUTING MACHINERY                            |                       |

| THE INSTITUTE OF RADIO ENGINEERS                                   | New York, N. Y.       |

|                                                                    | •                     |

|                                                                    |                       |

| Co | n | te | n | ts |

|----|---|----|---|----|

|    |   |    |   |    |

| Keynote Address                                                                                                                                                                                                                                                                                                                                                                              |                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Computers—From Youth to ManhoodNorman H. Taylor                                                                                                                                                                                                                                                                                                                                              | 1                          |

| Programming and Coding<br>Gestalt Programming: A New Concept in Automatic ProgrammingDouglas T. Ross<br>A Truly Automatic Computing SystemMandalay Grems, R. E. Porter<br>Lincoln Laboratory Utility Program System (Abstract)H. D. Bennington, C. H. Gaudette<br>An Automatic Supervisor for the IBM 702Bruse Moncrieff                                                                     | 5<br>10<br>21<br>21        |

| Auxiliary Equipment                                                                                                                                                                                                                                                                                                                                                                          |                            |

| Magnetic Recording Head Design       A. S. Hoagland         A Terminal for Data Transmission Over Telephone Circuits       Enoch B. Ferrell         The Use of the Charactron With ERA 1103       Ben Ferber         A New Tape Handler for Computer Applications       R. M. Brumbaugh                                                                                                      | 26<br>31<br>34<br>36       |

| Machine Design                                                                                                                                                                                                                                                                                                                                                                               |                            |

| Requirements for a Rapid Access Data File.       George Eisler         Engineering Design of a Magnetic-Disk Random-Access Memory.       T. Noyes, W. E. Dickinson         Print I—A Proposed Coding System for the IBM Type 705.       R. W. Bemer         The IBM Type 705 Autocoder.       Roy Goldfinger         Program Interrupt on the Univac Scientific Computer.       Jules Mersel | 39<br>42<br>45<br>49<br>52 |

| Systems                                                                                                                                                                                                                                                                                                                                                                                      |                            |

| A Pulse-Duration-Modulated Data-Processing SystemJ. R. Lowe, J. P. Middlekauff<br>A PDM ConverterW. R. Arsenault<br>An Improved Multichannel Drift-Stabilization SystemP. G. Pantazelos<br>Combined Analogue and Digital Computing Techniques for the Solution of Differential Equations<br>P. A. Hurney                                                                                     | 53<br>57<br>62<br>64       |

| Design, Programming, and Coding                                                                                                                                                                                                                                                                                                                                                              |                            |

| An Experimental Monitoring Routine for the IBM 705                                                                                                                                                                                                                                                                                                                                           | 68                         |

| Computer Design to Facilitate Linear Programming                                                                                                                                                                                                                                                                                                                                             | 70<br>75<br>77             |

|                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| Scientific Application<br>Using a Variable-Word-Length Computer for Scientific Calculation                                                                                                                                                                                                                                                                                                   |                            |

| Unusual Problems and Their Solutions by Digital Computer Techniques                                                                                                                                                                                                                                                                                                                          | 77<br>79<br>82<br>86       |

| Applications                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| Applications of the Small Digital Computer in the Aircraft Industry         H. M. Livingston, E. L. Lyons           Traffic Simulator with a Digital Computer         S. Y. Wong           Integrated Data Processing with the Univac File Computer         R. P. Daly           A Fixed-Program Data Processer for Banking Operations         Jack Goldberg                                 | 89<br>92<br>95<br>99       |

| Circuits                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| The Logical Design of a 1-Microsecond Parallel Adder, Using 1-Megacycle Circuitry                                                                                                                                                                                                                                                                                                            | 100                        |

| The Transfluxor       A. Weinberger, J. L. Smith         J.A. Rajchman, A. W. Lo         Bilateral Magnetic Selection Systems for Large-Scale Computers (Abstract).         A. H. Sepahban         The Megacycle Ferractor (Abstract).         T. H. Bonn                                                                                                                                    | 103<br>109<br>118<br>118   |

| RCA BIZMAC System                                                                                                                                                                                                                                                                                                                                                                            |                            |

| Purpose and Application of the RCA BIZMAC System                                                                                                                                                                                                                                                                                                                                             | 119                        |

| W. K. Halstead, J. W. Leas, J. N. Marshall, E. E. Minett<br>Functional Organization of Data in the RCA BIZMAC System                                                                                                                                                                                                                                                                         | 124                        |

| A. D. Beard, W. K. Halstead, J. F. Page<br>The RCA BIZMAC System Central. J. L. Owings<br>Characteristics of the RCA BIZMAC Computer.                                                                                                                                                                                                                                                        | 126                        |

| Programming the Variable-Item-Length RCA BIZMAC Computer                                                                                                                                                                                                                                                                                                                                     | 133                        |

| L. S. Bensky, T. M. Hurewitz, R. A. C. Lane, A. S. Kranzley                                                                                                                                                                                                                                                                                                                                  | 137                        |

|                                                                                                                                                                                                                                                                                                                                                                                              |                            |

Page

# **Computers**—From Youth to Manhood

## NORMAN H. TAYLOR

OU are very kind to honor me with the invitation to speak here today, and it is a pleasure to be here. I always appreciate a good excuse for leaving my overcoat and galoshes behind in Boston and coming out to sunny California. Furthermore, we are beginning to realize that although Boston is still of course the hub of the universe, nevertheless there are some pretty good ideas generated out here on the West Coast; and I hope I shall not return to New England without a few dozen of them in my carpet-bag.

At the first Joint Computer Conference in 1951 at Philadelphia, the computer industry was turning a corner. You might say that after a well-protected infancy, it was putting on short pants and getting outdoors and the neighbors were beginning to be aware of it. The machines, like some children I know, could be made to put on their "company manners" when their rich uncles came around, but this was all too often the result of intensive grooming and stern disciplinary measures behind the scenes. Our audience, while sympathetic and hopeful, still could not help feeling skeptical, and some may even have feared that we were raising a little monster who would turn out to be more of a liability than an asset.

Five rapid years of growth have served to vindicate our claims of 1951. I could easily spend an hour giving you chapter and verse on this, but suffice it to say that more than 75 large machines are in full-scale useful operation, and hundreds of smaller machines are doing important jobs for office and industry. The attendance figures at these professional conferences should be some sort of index; there were 880 of you at that first conference in 1951, now we are holding two conferences a year, and the 1955 Eastern Joint Computer Conference alone had approximately 2,000 people in attendance. This Western Joint Computer Conference and its counterpart, the Eastern Joint Computer Conference, will undoubtedly set a new record.

Thus, I think we can say that the computer business is getting out of its childhood, and putting on long pants. Adolescence is upon us, and although some of us, I am sure, look back with a certain nostalgia on the happy childhood days, nevertheless, like good parents we cannot shirk the problems of the present, and must try as best we can to prepare for the future. By and large, we are proud, you and I, of what we've done so far. But no engineer worth his salt is going to devote his time to admiring his past work. What the good engineer lives for, the air he breathes and the meat he eats, is the challenge of new problems. It is not too much to say that without new problems he suffocates and starves, and professionally he might as well be dead. If there were an engineer's Bible, I think this ought to be one of the two great commandments, so, using this text, my little sermon today is going to deal with the problems ahead of us. Please note that I'm presenting problems and asking questions, not trying to give you the answers. Even if I thought I knew a few of them, I'd be spoiling your fun, and that would be a dismal thing to do! I'll save my clairvoyance act for private chats, where I won't be embarrassed by seeing it in print and having to eat it five years later. You fellows are the ones who will have to answer these questions, just as today you have given us answers to some of the questions asked five years ago.

Let me return now and then to that notion of looking at computers as children that we've raised—it isn't really a bad analogy, if I don't squeeze it too hard; you know how children outgrow things, first their shoes, then their pants, then their coats, and so on. Or how a boy's mind in a way outgrows his body, and he imagines himself beating up all the tough guys in the neighborhood and fascinating all the pretty girls. Well, our computers have had and are still having just this sort of growing pain, the parts like arithmetic element, memory, and terminal equipment don't keep pace with each other, and we haven't yet got a mature, harmonious, balanced system. Until recently, our worst shortcoming has been the size, reliability, and speed of central memories; and we have put a lot of effort into improving them. The magneticcore memory which has come out of this is now fairly well accepted as the central high-speed element of presentday machines, and is probably the largest single change of these past few years. Even so, we haven't quite caught up with arithmetic element speeds; the logical structure of most machines has been aimed at using memory time and capacity to the hilt. Elaborate buffer memories serve the purpose of emptying and filling the high-speed memory, and tricky instructions use other hardware to do jobs that might be done in the central memory if its time weren't so valuable.

At that, we haven't yet exploited magnetic-core memory to the full; the 64 by 64 memory plane is now pretty common, but one naturally asks the question, how much bigger can you build it? Preliminary work leads us to believe that the 64 by 64 plane can be extended to 128 by 128 and probably to 256 by 256 without any serious loss in speed or reliability. If this expectation becomes a reality, we shall have a 256 by 256 by 36 memory, that is to say, 2.5 million bits of storage with 6 to 7 microseconds random access. Surely this will be a handy tool for the future. How shall we use it? It certainly ought

Full text of the keynote address presented at the Western Joint Computer Conference, San Francisco, Calif., February 7, 1956.

NORMAN H. TAYLOR is with the Lincoln Laboratory of the Massachusetts Institute of Technology, Lexington, Mass.

The author wishes to acknowledge the helpful suggestions of W. A. Hosier in the preparation of this address.

to affect our present concept of providing large buffers feeding a small high-speed memory; it has about the capacity of eight conventional magnetic drums. Does this mean that drums are obsolescent?

But can the memory designer relax? Is he going to be free of demands for more speed and capacity from the direction of the arithmetic element? Vacuum tubes have been for several years the principal limitation on arithmetic element speed: we have pushed adders up to 1 or 2 megacycles, and with multipliers it is commonly felt that a law of diminishing returns sets in somewhere in the region of 1/2 to 1 microsecond per bit. I think the memory people, with the 6-microsecond memories, have provided, potentially at least, a good match for such circuits in speed and reliability.

But what about the future? Surface barrier transistors already give promise of operating at 5 megacycles in arithmetic and switching operations. What will come with the new gaseous diffused or drift transistors? I'm afraid the answer is inevitable: Memory will lag behind and the race will be on again. Why all this speed? Do we really need it? We are already being pressed to design larger and faster machines to tackle problems that are bulky and complex and have to be solved quickly. One way or another, I'm sure we'll try it. But if we had speed an order of magnitude over what we've got now, couldn't we do more time-sharing and substitute speed for equipment? Surely if something like this can be done, machines will be simpler, smaller, less expensive, and more reliable. This is a problem for the logical designer.

I have dwelt here on a few aspects of the internal consti ution of computers. In our analogy to the child, these would be his health, growth, and internal development. These are going well, with good momentum. I don't think we have any cause to fear that these children of ours are sickly or stunted. But as we all know, this is, if anything, the small end of the problem of rearing children: as they grow up, they leave more and more their old sheltered environment; they must be educated, they must (usually) do useful work, they must gradually accept more responsibility. I'm sure this isn't all, but these three requirements give me a convenient handle for the remaining things I have to say. Let's talk about this subject of useful work.

You can divide work roughly into two kinds: the kind that deals with symbols which you might call "whitecollar work," and the kind that deals with matter and energy, which I suppose you would call manual labor or something like that. The kind of work that deals with people I don't feel has got into the picture yet. When we ask a computer to do the first kind of work, we call it data-processing; when it does the second kind, the current terminology would seem to be "automation." I am aware that the last word is often used more loosely, and that the dividing line between the two kinds of work is fuzzy in spots, nevertheless the division is a help in thinking about the problems, because the problems in the two cases are essentially different, and since there is no better word for the second kind, call it automation. Data-processing deals with symbols, and symbols for the most part are discontinuous, discrete things: they come in chunks, and are grist for the digital computer mill. We are getting high-speed printers to grind them out. If we can get high-speed readers of print to grind them in without going through the clumsy media of punched cards or paper tape or the volatile and intangible medium of magnetic tape, we shall have gone a long way toward making the "white-collar" boys happy. So much for data-processing. Let's consider automation.

This field sometimes is referred to as real-time control, and it is quite a different story from data-processing. It seems to me to be the most challenging area of the future, heavy with problems, but also glittering with promised rewards The newspapers say it's here already, quoting from Mr. Kenney in the *Christian Science Monitor*.<sup>1</sup>

"In this contemporary fantastic era of research and automation, people today are better fed, clothed, housed, heated, cooled, propelled, entertained, and defended than at any time in all history.

The Alice in Wonderland, razzle-dazzle of new methods and processes are zooming living conditions and industrial activities into a never-never land undreamed of a decade ago and even today are leaving the most dramatic prognosticators almost baffled in attempts to describe what is coming up in the future.

#### COMPUTER SETS PACE,

"One of the most dramatic and important developments in the automation field is the computer. It is often called the electronic 'brain.' The computer can do just that at enormous speeds. It can add, subtract and multiply, etc. ........."

This puts me in mind of an experience we had with radar during the war, which some of you may have heard of: The Admiral on one of our battleships, flagship of a task force in 1942, didn't put much stock in the reports of his radar man. But one night the radar man called up to flag pilot, saying, "Carrier Saratoga 2,000 yards off the starboard bow." The Saratoga in some aspects gave a characteristic double-humped blip on an A-scope that an experienced operator could easily identify. But the Admiral knew different. "You're crazy as Hell," he said, "The Sara's been off the port bow all night." But the radar man stuck to his guns, so the Admiral finally had a blinker message flashed, asking the ship to identify herself, and, sure enough, damned if it wasn't the Saratoga off the starboard bow. Well, that really converted the Admiral to electronics. So much so, that when the radar man a half hour later said, "Destroyer 4,000 yards dead ahead," the Admiral asked, "What's its number?"

I'm sure you can see the moral for us computer engineers in this little tale. If we're not well aware of our limitations and can't explain them intelligibly to others, we're likely from time to time to be asked to bite off more than we can chew. And believe me, in this automation field we have plenty of limitations at the present time. For one thing, the computer is no longer operating in a vacuum. It's got to operate in somebody else's system, and if you just try to plop the computer into the middle of the system the odds are about 99 to 1 you can't make it work. You've got to study the whole problem and probably re-engineer a large fraction of the system before you reach any sort of harmonious solution. And this process has to be detailed and careful, not general or hasty. For the engineer on this sort of job, a fast, reliable central computer is not enough: he must take off the blinders and look at a whole new group of problems; in short, we need systems engineers.

For another thing, the sort of information that the system feeds to the computer is not usually a nice choppedup bunch of easily-digitized symbols. It is on the other hand usually a nasty continuous rope of information from something like a thermocouple, a strain gauge, or a radar set; these analogue inputs are apt to be as embarrassing as a long continuous piece of spaghetti if we can't devise ways of handling them. What I'm asking you is this, have we put enough effort into analogue-to-digital conversion devices?

Not only does our young computer have to learn how to simplify information so that he can comprehend it, he also has to learn to be discriminating, to tell the truth from lies, to tell the important from the trivial. This is the noise problem. It's almost negligible when you're dealing with symbols, but when sensitive analogue measuring instruments and transmission lines from remote places come into the picture, it can become pretty bothersome. Communications engineers over the years have devised means, such as statistical processes, for coping with noise. We are likely to need closer liaison with them, and doubtless will have to help to extend their work.

Finally, of course, this computer out in the world of work not only requires eyes and ears and a central nervous system, as it were; it also must have muscles and tools. The azimuth and elevation of a gun, the force of a hammer blow, the degree of opening of a valve, the current in a welding arc—here we are again with physical variables, continuous functions, analogue devices. So here we require digital-to-analogue converters and servomechanisms. Are we attacking these problems as hard as we ought to be?

Return for a moment to the problems of the adolescent child, in particular, education. For a digital computer, this means one thing: programming. This area of programming is a complex problem. I would like to be able to make a few sage comments and dispose of it quickly, but I cannot. I have talked with several program people in an attempt to define just what basic problems they have which might be relieved by machine organization or electronic aid. I have been unable to recognize any single great weakness but here are some of the problems that could be relieved.

In an automatic control system the efficiency desired in a program is high. Many parts of programs run over and over again. The program must be written to accomplish its results in a period of time compatible with the demands of the system which is under control.

The program must be versatile; it must take into account the human monitor when he acts, yet proceed according to the established routines when he does not. It must be flexible. As we learn about new variables pertinent to a given problem we advertise that our generalpurpose computer can take these into account by a simple change in program. The program must be written to allow such program changes without a complete rewrite for the problem.

The cost of such programs is high, and time to get them is long. It may surprise you to learn that, in general, the cost of programming a computer for an automation job is roughly the same as the cost of the machine. The cost is justifiable and defendable, but I feel sure that I should ask the question: What are we going to do about simplifying the process? Some advances have been made by using the computer itself to do the bookkeeping tasks and program assembly, register assignment, and the like. What else can it be used for?

In the strictly mathematical area the language needed to express procedure to the machine is fairly well understood and can be generalized and automatized. This is not true in all areas. Can we learn enough about the problems in automatic control to express the variables so that the machine can understand without being given every detail?

Our childhood analogy here becomes tantalizing. As the child grows he learns. After having solved one problem he uses the previous knowledge to attack a new problem. Can we design a machine to learn? Enough work has gone into this to show that the road is hard. The present crop of computers are fast and frisky, but they have the intelligence of an earthworm. I shall not pursue this further, lest I be quoted to my sorrow.

When I compared our situation with these fledgling machines of ours to that of parents with children about to be thrust out to take their place in the adult social fabric, I mentioned one last aspect of the situation; the need for gradual increase of responsibility. No one expects a callow youth to be running much of a show on his own; for a long time he inevitably relies on the supervision and judgment of more experienced hands. In the computer's case, the experienced hands can only be human beings, and the early automation systems are going to require extensive human monitoring. To be sure, in the fullness of time we may hope to build such sound judgment into some of these systems that they can tick along unattended all by themselves, but that day, the day of the truly automatic "no hands" system, is not yet. The need to know what is going on is more than just curiosity; it is part of the evolution towards complete automation and provides the means of correcting and improving our understanding of present concepts. Human judgment is needed in the more complex 1956 central systems for several reasons. First, in order to be completely automatic one has to understand a process with all possible contingencies well enough to tell a computer how to respond in any combination of events. Second, many people have to be confident that this situation does,

in fact, exist. There are other problems too, but these two alone demand an adequate monitoring system and my question to this conference is: How do we provide adequate monitoring systems to help our computer through adolescence?

How can the important Charactron and Typotron display tubes which are now available best be used on this problem? More important: What information must be presented to the human monitor, and in what form? Have you looked in a modern airplane cockpit lately? This is a good example of the monitoring problem with literally hundreds of meters, scopes, lights and knobs. We have so much information to give to the monitor that we ask: How can he absorb it all? Once he has received intelligent and accurate information and made a decision he must make this known to the system. What techniques can be used for this? The famed pushbutton certainly is effective, but has limitations of speed and accuracy. Certain electronic aids, such as the photoelectric pickup, have shown promise. Here is an area where new ideas and ingenuity are welcome.

Could we possibly consider using human voice to talk back to a computer to tell it what to do? How difficult would this be? The telephone people are considering voice-operated dialing. Why not talk to the computer in some similar way?

Another suggestion, less ambitious, proposes that a manual typewriter be used and the computer be programmed to decode the English language for its instructions.

#### Conclusion

I have posed some difficult problems to accomplish the education, and to increase the usefulness, and responsibility of our adolescent computers.

In 1951, the coming childhood of these infant computers seemed fraught with problems, but we have conquered most of them with determination and enthusiasm. Now in 1956 we have added to that determination and enthusiasm the confidence that the child is healthy and growing and fairly well accepted in society.

If you step back and look at it with a prospective of a few hundred years it seems to me that this being in on the childhood and adolescence of the digital computer art is a rare privilege which most of us here are sharing. Haven't you ever wished that you'd been living back in the days when some of the great sweeping syntheses were made that changed man's viewpoint and ways of thinking? I mean, for example, Faraday's discovery of magnetic induction, Maxwell's mathematical handling of radiation, Descartes' analytical geometry or Newton and Leibniz's early calculus, or, in our own time, relativity, quantum theory and all that has proceeded from them. There was always a time, but it had to be just one time and for rather few interested people, when these concepts were hot off the griddle and were the meat of red-blooded arguments, then, for all time to come, they got taken for granted and salted away in textbooks. Now I'm not flattering myself into believing that digital techniques are as far-reaching as Maxwell's equations (or as neat either), but I do believe they will have many unforeseen consequences that none of us dreamed of when we started playing with them, and for digital techniques the time is now, the people are you, and who knows, Joe Doakes' principle of binary substitution may be something your grandchildren will sweat over in first-year graduate courses!

And thus it is, gentlemen, that I am sure these precocious adolescents of ours are here to stay and to make their presence increasingly felt, it is up to you and me to make first-class citizens out of them.

#### Reference

1. AUTOMATION WIDENS VISTAS OF RESEARCH POTENTIALITIES, H. C. Kenney. The Christian Science Monitor, Boston, Mass., Jan. 4, 1956, p. 16.

## Gestalt Programming: A New Concept in Automatic Programming

## **DOUGLAS T. ROSS**

Synopsis: In any human endeavor there are three major phases: conception, expression, and execution. Gestalt programming is an attempt to make these three phases as nearly identical to each other as possible with respect to computer programming. In this paper the word Gestalt is used to mean a concept of a task to be performed by a computer. In a Gestalt system of programming, the Gestalt, or idea, is expressed simply and unambiguously in a special language, rather than through the laborious assembling of machine codes. pseudocodes, subroutines, etc. Using a Gestalt system, the expression itself in effect ties together integrated units of computer behavior, which function singly or in interrelation, to achieve the desired effect. The purpose of a Gestalt system is to facilitate the transmission of general ideas as in a conversation, between a human and a computer, so that the maximum use of their respective capabilities can be made.

After presenting the abstract theory of Gestalt programming this paper discusses several Gestalt systems in use today at the Massachusetts Institute of Technology (MIT) and describes briefly the types of computer hardware which are best suited to this application.

AS computer techniques have developed over the last few years, there has been a growing trend toward more sophisticated methods for connecting the human, who states the problem, to the computer, which is to solve the problem. Great strides in automatic coding schemes and algebraic coding schemes have been made, and the feasibility and value of these techniques are now well established.

Out of this trend has come, as a natural consequence of the maturing technology, a desire to use computers for solving problems which cannot be completely specified in terms which the computer can handle. This type of problem is united with automatic problem stating, referred to in the foregoing, in the general problem of using humans and computers together to solve problems. In the one case, the goal is to state the problem so that the computer can execute the solution, and in the other case, the goal is not only to state the problem to the computer, but also to assist the computer in obtaining the solution. In both cases, the human and the computer do only those parts for which they are best suited.

If the human and computer are to work together to solve a problem, there must be some means provided for the transmission of ideas or results between the two, since the contributions of each will depend upon the actions of the other. There is no known way in which ideas can be transmitted directly, so that an intermediate stage of expressing the idea in some language is always required. A language consists of two parts; a vocabulary and a set of syntactical rules. An idea is then transmitted by transmitting the expression of the idea; i.e., a sequence of words from the vocabulary. The final stage in the transmission is recognition by the receiver.

A major problem, then, in using humans and computers together is to choose an appropriate language for the interchange of ideas. This language must bridge the gap between the fundamentally incompatible characteristics of the two parties. The human is quick-witted but slow, while the computer is slow-witted but extremely fast.

Most people connected with the computer business seem to be superbly equipped for voluble discussion on any topic. It would therefore appear at first that the language should be chosen for the convenience of the slow-witted computer. Such is definitely not the case, however, because once the computer has been given a language, it becomes a very formidable associate, firing questions and answers at a rate which very quickly becomes alarming to the human. For this reason the first rule in establishing a language is that it must be as natural and convenient as possible for the human to use, not only in the interest of reliability, but for psychotherapeutic reasons as well. Programmers with persecution complexes are already far too numerous.

Since the language is to be used for the transmission of ideas, the most natural way to obtain convenience for the human is to have the language operate entirely at the idea or concept level. In other words, the language should be designed so that general statements can be made easily by the human, with the computer itself filling in the necessary details. This concept should work in the other direction too, i.e., the statements made by the computer to the human should be pertinent digests at the idea level, and not detailed reports.

In order to use the human and computer together efficiently, a statement in the language must lead to direct and immediate recognition and reaction. This may be accomplished by designing the language so that when a statement expressing an idea is made, the receiving party, human or computer, is able to recognize immediately the elemental concepts which are to be united to give the desired idea.

A word already exists which carries all of the connotations of simultaneity and sudden bringing-together of basic units into a single entity or pattern, and that word is "Gestalt" as it is used in the Gestalt theory of psychology. Since there is no single word in the existing computer terminology which works both ways between human and computer, and includes the connotations of being at a high level of communication and implicitly including active execution, the word Gestalt will be borrowed from psychology, and will be used in this paper with very nearly the same meaning in connection with computer programming.

The decision to introduce this new word is not capricious in any way, but is made to facilitate the presentation, and to assist in the establishment of a new emphasis and point of view with respect to the general problem of the interconnections between humans and computers. The actual material discussed in this paper is, for the most part, not new, but the way in which it is discussed is new. This new approach has been found to be very fruitful and clarifying, and is the primary motivation for this paper.

Although the idea of using humans and computers together to solve problems is relatively new, enough examples have been developed by various groups throughout the United States to demonstrate that these techniques show considerable promise. After mentioning a number of applications, (some of which have not yet been tried), to motivate the discussion, this paper considers in some detail the various stages involved in designing computer systems of this type by solving a hypothetical example. The abstract structure of such systems is then outlined, using the example for illustration. Finally several systems in

DOUGLAS T. Ross is with the Massachusetts Institute of Technology, Cambridge, Mass.

daily use at MIT are described, and some concluding remarks about the probable impact of these techniques upon computer technology are made.

### **Conversation Versus Communication**

A suitable definition of the word Gestalt as it applies to computer programming is that it is a concept of a task. This definition is meant to imply that the Gestalt is not the task itself nor even how the task is to be performed, but merely the idea or concept of that task. For example a Gestalt might be "Integrate f(x)," and this idea certainly is not equivalent to the task of integration nor does it tell how the integration is to be performed. The more specific Gestalt "Integrate f(x) using Simpson's rule" still does not prescribe detailed steps of applying Simpson's rule to the particular function in question.

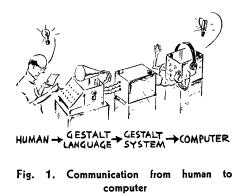

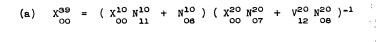

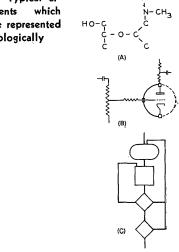

Fig. 2. Communication from computer to human

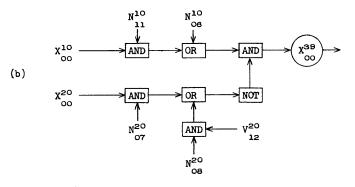

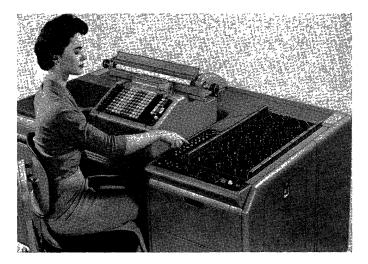

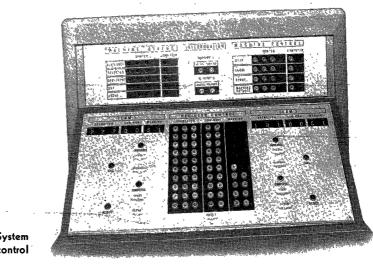

Fig. 1 shows schematically how a Gestalt is transmitted from the human to the computer. The human simply expresses his idea by pushing buttons which correspond to words or phrases in a special language, the Gestalt language. The Gestalt system then translates the expression into terms which the computer can understand, and the computer can then proceed with the execution of the task.

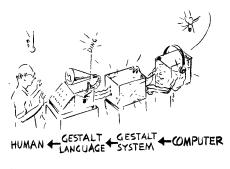

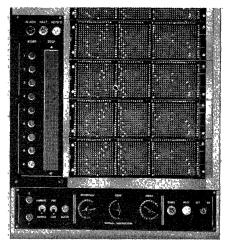

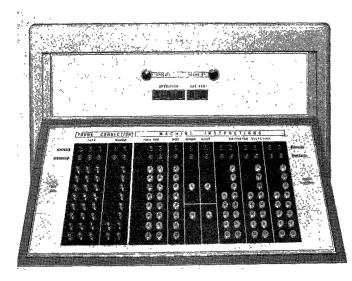

Fig. 2 shows the analogous situation from the computer to the human. By means of the Gestalt system the computer's idea is expressed in a special language which the human can easily understand. The human is then prepared to perform the task required by the computer.

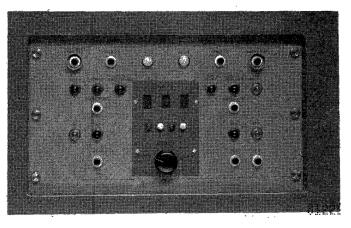

These two illustrations show the process of communication from the human to the computer and communication from the computer to the human. If the human and computer are to work together to solve the problem, the intermediate languages and translating systems must be designed not merely for the purpose of communication, but for the convenience of fluent conversation. In other words, as Fig. 3 shows, the solution to the problem will, in general, be found only by a more or less extended conversation between the two working as a team, work being divided up so that optimum efficiency and reliability are achieved.

The remarkable flexibility of modern computers makes it possible for them to assume many guises. When more than one role is assumed by a computer in the solution of a problem, it sometimes becomes difficult to talk about the general aspects of that solution because the same mechanism has such different characteristics. This is guite definitely the case when Gestalt programming is discussed, because the computer serves in two capacities; one with respect to stating the problem and one with respect to solving the problem. In this paper the word "computer" usually means the aspect of the computer which is concerned directly with the problem to be solved. The term "Gestalt system" usually means the set of computer programs which aid in the stating of the problem by performing the necessary translation between the Gestalt language and the computer, as shown in the aforementioned illustrations. Often, however, the meaning of Gestalt system is expanded to include the Gestalt language and the physical representation of that language as well, as in the statement, "This problem can be solved by the design of an appropriate Gestalt system." The context makes clear which is intended.

## Applications

Before developing the theory of Gestalt programming, several examples of problems will be presented which require or could greatly benefit from the use of human participation. It should be borne in mind, however, that although it is

Fig. 3. Solution by conversation

problems such as these which have led to the concept of Gestalt programming, many problems which at present are not considered to require human participation could more effectively be attacked through the use of these techniques.

In almost any control application of computers, whether air-traffic control or automatic factory control, it is necessary to have at least human monitoring with the ability to make sudden changes in the computing scheme. This type of application usually places high priority on reliability and speed.

Large-scale data-reduction problems, basically automatic, often require a human choice between several alternate procedures, a choice dependent in a complex and sometimes whimsical way upon a number of intermediate results. Often partial results can be salvaged from an otherwise worthless set of data, providing appropriate techniques are chosen. By using an appropriate Gestalt system and human participation, these results can be obtained at almost normal processing speed.

Even in strictly computational work a human could greatly expedite the obtaining of solutions if the proper techniques are used. For example, in the solution of complicated partial differential equations or in linear programming problems and game theory, it seems probable that methods could be devised whereby the human could "steer" the computer directly to the solution, rather than obtaining an enormous mesh of solutions, most of which are not of real interest. This type of operation could very well be instrumental in the application of computers to aid in management decisions. A properly designed language would allow executives to converse with the computer directly and without costly delays.

Perhaps the most intriguing application of human participation in this sense is the use of a Gestalt system in experimental programming, since such a system can be used to generate other Gestalt systems. By experimental programming is meant the programming of a large, complicated program for which the basic steps in the solution are not known. As the programming develops, the programmer must be able to do his design work at the concept level, leaving to the Gestalt system all of the details of translating his growing concepts into actual computer behavior.

Additional applications for humancomputer team work can easily be found, but this brief listing should serve to show that the possible uses cover a wide range of problems. This paper does not treat programming details, for these will vary widely for each application, but does try to establish the general problems which are common to all of these applications. In addition to recognizing these problems, a general methodology or plan of attack for solving them is formulated.

#### Example of Gestalt System Design

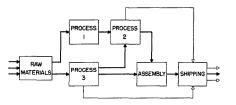

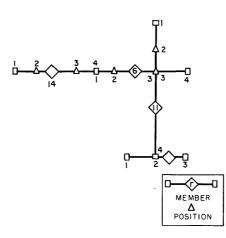

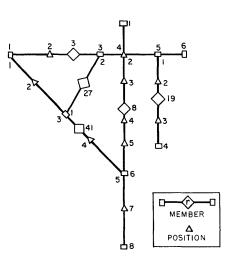

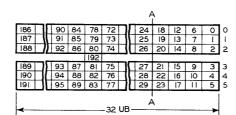

The general principles of the design of a Gestalt language are best illustrated by carrying a single example through all of the various stages. Consider the case of an automatic factory whose main features are shown in Fig. 4. Three main processes are involved, followed by an assembly process. These processes are flanked by a raw materials input section and a shipping output section. Besides the primary product, it may be desired to ship directly the outputs from processes two and three. The main duty of operating this factory is to be the responsibility of a computer, but a human operator is to be in charge of setting the requirements for the various stages and overseeing the entire operation.

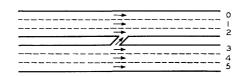

Present-day computers are not equipped for oral input so that some means other than a spoken language must be used to enable the operator to converse with the computer. Written languages using an intermediate medium such as punched tape or cards have long been used for communicating with computers, but a closer approach to the ease, speed, and flexibility of a spoken language can be achieved by letting each word or phrase which is to be used be represented by a single unique switch or push button. A statement is then "spoken" by pushing appropriate buttons.

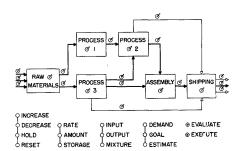

Fig. 4. Diagram of automatic factory

In the automatic factory it will at times be necessary for the operator to refer to each part of the diagram of Fig. 4. The easiest way to do this is to construct a panel with a toggle switch associated with each part as shown in Fig. 5. Now assume that the statements about the factory which the operator must make are of the form: "Increase, decrease, hold, or set the rate, amount, or storage of the input, output, or mixture of the products at the points indicated by switches which are on." The facilities for making such statements are shown in Fig. 5, where the circles connected by lines indicate push buttons with mechanical linkages so that only one button in the column can be pushed at any one time. Provisions should also be made for specifying numerical quantities so that a particular rate or amount can be specified. This facility might be in the form of keyboards or perhaps dials which can be set.

To continue the example, a statement of the foregoing form may be a demand, meaning that the computer is to jeopardize the efficient operation of other sections of the factory, if necessary, in order to comply with the statement. On the other hand, the operator may wish the computer to adjust the factory gradually to comply with the statement, but at all times maintain previous requirements; i.e., the statement is a goal toward which the computer should strive. Finally, the operator may have an estimate from a market survey, that a certain product may be in greater demand soon, so he wishes the computer to adjust the factory toward this tentative condition if it can do so with no loss of efficiency at any point. These three qualifications may be placed on the general statement by pressing one of the buttons labelled demand, goal, or estimate. In other words, the meaning of the statement expressed in the other buttons is modified by these buttons as in a language: e.g., "Run to the store, slowly."

Another whole level of meaning is made possible by considering the computer to be able to simulate the factory as well as control it. The general statement, modified as shown, may be further modified by requesting the computer either to evaluate the effect of the statement, by simulation, or to execute the statement by controlling the factory. This is assumed to be the final modification of the statement so that, the words evaluate and execute are associated with special buttons called activate buttons.

The panel should be wired so that the computer does not look at any of the buttons until one of the activate buttons has been pushed. At this time all of the items necessary to express the idea have been pushed so that when the computer looks at the buttons it is immediately confronted with a complete Gestalt. For example the Gestalt might be, "Evaluate the effect of a demand for an increase in the amount of output from process 2."

The completed panel, shown in Fig. 5, is the physical representation of the Gestalt language for this example. That it does in fact constitute a language may be seen by noting that it does have both a vocabulary and grammatical rules. The vocabulary consists of the various buttons and keyboards, and the rules are contained in the mechanical linkages of the columns of buttons and the fact that buttons modify the meanings of other buttons.

The corresponding language from the computer to the human will not be given in detail. It probably would consist of graphical displays, numerical displays, flashings of indicator lights, and audible alarms. The indicator lights probably would be located in the control panel beside the toggle switches to give them easily understood meanings. For example, the computer might reply to the foregoing Gestalt by saying that if the amount of output from process 2 is increased by demand, the rate of mixture at process 3 must be increased, which will require an increase in one of the raw materials. This Gestalt might be shown by lights at process 3 and the raw material arrow, and a graph showing the dependence of these quantities on the amount of increase at process 2. The computer would not only be able to answer questions posed by the operator but could ask policy-type decisions on operating the factory when two

Fig. 5. Gestalt language for automatic factory

equally efficient modes of operation were discovered by the computer. Naturally the computer would keep track of all inventories and would request new supplies of raw materials whenever necessary, with sufficient lead time to maintain operation.

Note that the Gestalt language in both directions has been designed for the convenience of the human operator. In this way the human can always keep his thinking at the problem level and never has to be concerned with how a given task is to be accomplished. Because the language is more a human than a computer language, there is a routine but complicated translation to be done before the computer can actually use the language. This translation is the job of the Gestalt system proper, which is mechanized as a computer program on the same computer which controls the factory. Besides the major job of translating between the Gestalt language and the basic computer characteristics, the Gestalt system also must check statements made by the operator for consistency and completeness. In other words, the Gestalt system supplements the mechanical linkages and layout of the push buttons in ensuring that the rules of the language are obeyed. In this way any ambiguous statements made by the operator are caught before they are acted upon and, in the other direction, the computer cannot speak gibberish.

## Principles of Gestalt System Design

With the experience of the example given in the foregoing, the basic principles of designing Gestalt systems can briefly be summarized. The general field to which the system is to be applied may be considered as a topic for conversation between the human and the computer. Usually this topic will be a broad generalization of the problem which initiates the interest in a Gestalt system. In the example, the topic would be control of an automatic factory. At the present state of the art, it is essential that the scope of discussion about a topic be limited to only those aspects which are of immediate interest; in the example, the scope is restricted to the particular factory.

The topic for conversation is broken down into the finest logical divisions necessary to cover the entire scope unambiguously and with a minimum of rules for combination. In the example these divisions are the words, numbers, and locations which were assigned buttons and the various basic units of the computer to human language. All of these various types of basic units will be called items, and the complete set of items forms the vocabulary of the Gestalt language. Thus a Gestalt is expressed in this language by combining items according to syntactical rules. In particular, an item may modify other items. A welldesigned language will have a proper balance between items with very specific meanings, to give entry to broad areas of discussion, and items with very general meanings and thus high modifying potentialities, so that a very large and comprehensive body of Gestalts can be expressed with very little equipment.

When a Gestalt language is being designed, the items are always chosen for the convenience of the human, the goal being to have a language which is as natural to use as is possible. This statement may lead to the question why the language should not be English since that is certainly the most natural for the human. This question is clearly answered by the automatic factory example, since obviously it is more natural to select a switch associated with a box or line in a diagram than to try to describe that box by an English phrase. A similar remark applies to the computer-to-human language because a graph or diagram often conveys a complicated idea more readily than a description.

One basic principle on the choice of items cannot be overemphasized, and that is that their meanings must be unique. In other words, a button labelled "increase" must never result in a decrease as a result of modification by another item. Note that this requirement of uniqueness of meaning of individual items does not conflict with previous statements that the meaning of an item is modified by another item, since the modification is an elaboration of meaning, not a change of meaning. For a complicated problem it is often very difficult to find the minimum set of items which completely cover the scope with absolutely invariant meanings, but it is foolhardy to stop short of this goal since the only way to have a workable system is to have the human remember the pathological cases, which defeats the fundamental principle of having the human always think only at the problem level.

## Implementing a Gestalt System

The considerations of the previous section have shown that the special Gestalt language is designed entirely on the basis of the problem and the convenience of the human. Once this language has been designed the human is allowed to discuss the problem only in that language so that, in effect, a part of the programming of the problem has been accomplished by programming the human. Note that this is not purely a characteristic of Gestalt languages, since every time any coding scheme or particular computer is applied to a problem, a large number of possible solutions are automatically eliminated by the characteristics of the computer or coding scheme. The aspect which is characteristic of Gestalt languages is that ideally, at least, the programming of the human is entirely beneficial.

The next step, and it is by no means a trivial one, is to program the computer so that it can converse in the Gestalt language as well, i.e., to construct the Gestalt system proper. Because the language was designed for the convenience of the human, it is usually a difficult programming task, but since everything is well defined, it can always be done.

Almost every recognized programming technique can be used to advantage in the realization of Gestalt systems. On the other hand, as might be expected, the peculiar problems which arise often lead to new techniques, or to strong desires for modification of computer logic itself. The cross-fertilization between advanced programming techniques and computer design will be more and more fruitful as these applications expand.

The final important part of the implementation of a Gestalt is the choice of a suitable medium to represent the language. The automatic factory example has already shown the advantages of diagrams and push buttons, but each problem will have its own most appropriate media. The governing criteria on the choice of representations are the rate at which the conversation is to take place and the complexity of the Gestalts when expressed as statements in the Gestalt language.

For low rates of conversation and very complex expressions, the standard inputoutput media, such as punched tapes or cards and high-speed printers, are probably most appropriate. The spectrum of possibilities also includes intervention switch devices for high rates of conversation. These devices, of which toggle switches and activate buttons are examples, are all characterized by the fact that a unique binary digit accessible to the computer is set to a 0 or a 1 by the setting of the device. Finally, at the ultrahigh conversation rate, there are such mechanisms as steering wheels and joysticks whose positions can be sensed by the computer. For the computer-to-human vocabulary there is a large number of audible and visual indicators, and, of course, the highspeed, very flexible oscilloscope-type output tubes.

In many applications it is desirable to give the human a variety of media for expressing the same Gestalt so that he may choose the most convenient at the time. In all cases, whatever medium is used, the principle of uniqueness should always be observed and the rules of syntax should be positively included by either mechanical or programmed interlocks.

The major steps in the design of Gestalt systems are summarized in the following. In any particular application the considerations of the various sections would undoubtedly be intermingled, but this listing can be used as a check-list summary of the basic points.

Steps in Design of Gestalt System

From the problem: Pick a topic for conversation. Restrict the scope of discussion.

- Design the Gestalt language: Choose items which cover the scope. Define rules of syntax for combining items.

- Design the Gestalt system: Determine rate of conversation. Choose unique representations for items. Establish interlocks by programs or linkages.

## Present-Day Examples of Gestalt Systems

There is, of course, a growing number of computer systems which have many of the attributes which have been discussed. In general, however, most of these systems operate at medium to low rates of conversation. Three systems which operate at high rates and are in daily use on the MIT Whirlwind I computer will be briefly described to illustrate more concretely than the applications cited previously, that these techniques are not futuristic in any way, but are sound, practical investments for today.

## THE COMPREHENSIVE SYSTEM

The MIT comprehensive system (CS), with the topic of "operating a computing facility," has elaborate utility programs, as well as automatic programming aids, under intervention-switch control. In this system Gestalts from the human to the computer may be expressed either in typewritten form, using appropriate mnemonic codes, or by pushing sequences of buttons. These Gestalts automatically call in any one of many programming systems including the CS system for the Whirlwind computer, several simulated computers used in academic courses in programming, a system for programming the Univac Scientific 1103 computer, and

## THE AUTOMATIC TROUBLE LOCATOR

The automatic trouble locator program, with the topic of "maintaining a computing facility," is a good example of humans and computers working together. This program is primarily under intervention-switch control and automatically operates the marginal checking equipment of the Whirlwind I computer. The human sets up the general sequence of tests which are to be made by expressing his desires to the computer. The computer then proceeds with the tests, and, since the computer does not have facilities for visual input, it may ask the human to look at the wave forms at critical points, which are displayed on a monitoring scope. The operator need only tell what general type of wave form is being displayed and then the computer proceeds with the analysis. If the computer encounters a marginal piece of equipment, it types out English phrases telling which individual tubes or components require replacement, and then tells how long it took to do the job by a phrase such as "That only took 2 minutes and 33 seconds, are you sure you did it right?", which must be acknowledged by the Gestalt "Yes" before the checking can continue.

The Gestalt system approach will probably find its widest application, at least initially, in the development of similar elaborate systems for greatly improved routine operation and maintainance of other computing facilities. Experience has shown that the results are well worth the effort of devising such systems.

## DATA REDUCTION AND EXPERIMENTAL PROGRAMMING •

The third Gestalt system in use at MIT is one whose topic is "automatic reduction of armament test data and experimental programming for armament control." This system is the one which has led to the analysis of this paper and is being developed for the Air Force Weapons Guidance Laboratory by the Servomechanisms Laboratory, MIT, using the Whirlwind I computer as a research tool.

This system is so designed that it includes all of the facilities of the MIT comprehensive system. Besides the comprehensive system vocabulary, this system has a large and growing vocabulary of items represented by uniquely assigned push buttons and switches. The rules of syntax which must be remembered by the human are almost entirely conjunctive in nature, the other syntactical rules being inherent in mechanical and programmed interlocks. Any syntactical error, i.e., a meaningless or contradictory combination of switches set by the human, is immediately followed by a unique and explanatory alarm. Conversely, any meaningful statement is properly understood by the computer. The computer-to-human vocabulary primarily uses output oscilloscope displays to express Gestalts, but indicator lights and audible alarms are used where appropriate. The rules of syntax are almost entirely programmed into the computer, i.e., the computer cannot speak gibberish or give misleading information.

Every item in each vocabulary requires a section of programming in the Gestalt system, some absurdly simple and some extremely elaborate. The combined sections are much too large to fit into the magnetic core memory of the computer, so that an essential part of the system is a control program which establishes the proper connections between the various program sections. This facility is so designed that individual sections can be changed easily at any time using the comprehensive system, and still mesh properly with all other sections.

This Gestalt system also has a logging program which provides a written record of the complete conversation between human and computer. This log can also be played back by the Gestalt system, the computer simulating the human actions for rerun purposes. In this way, an interrupted conversation can automatically be resumed.

In operation this system is designed so that the human can interject comments or questions into the computer's operation almost instantaneously and at any time. Some alarm conditions are automatically corrected, with suitable indication, and various types of trouble-shooting can automatically be carried out by the computer on request.

This Gestalt system is in a continual state of flux and improvement. As soon as a new feature is completed, it is usually obsolete in terms of future plans. There are an amazing number of challenges which appear with each new phase, but the results are rewarding. One of the biggest deterrents to progress is the large amount of work involved in changing the Gestalt system program to correspond to the change of vocabulary required to include some new feature. It is hoped that a solution to this difficulty will be found by writing a program to generate translation programs which will translate from statements in arbitrary Gestalt languages into selections of computer behavior.

The goal of the experimental programming phase of this work is to allow the programmer to alter drastically his planned attack on a very large and complex problem, and try out the new solution within a matter of days, while the new approach is fresh in his mind. All too often a volatile thought pattern disappears in the months of arduous toil required to program a complex problem using ordinary techniques. It is unlikely that present and future problems being considered at the Servomechanisms Laboratory could be solved with limited manpower without the use of these techniques.

#### **Concluding Remarks**

It seems appropriate to close this paper by again acknowledging the very real debt which is owed to all of the various schools of computer programming for substantial contributions upon which this paper is based. The emergence and development of these various techniques in the past several years have established firmly the intellectual climate necessary for continued expansion in these directions. There are several groups in the United States which for some time have been developing systems for using computers which have many, if not all, of the attributes of Gestalt programming systems as defined here. The purpose of this paper has been to try to establish the outlines of the abstract structure of this type of system. It is hoped that this analysis will prove useful to all who are interested in connecting humans and computers by clarifying the problems and relationships involved.

In its full generality Gestalt programming is not just a computer technique, but is a problem-solving technique, i.e., a point is reached where it is difficult to tell which is more important, the human, the problem, or the computer. The extension of these techniques and concepts is sure to have a profound influence on the design and operation of future computers, so much so that it seems probable that the term "com-

puter" for describing these mechanisms will become less and less appropriate. The day is fast approaching, if it is not already here, when the arithmetic capabilities of a machine will be its least valuable attributes. If the logical trend toward more and more elaborate systems of this type continues, the primary attribute of a computing machine will be its flexibility in the most general sense. Even if significant advances in the speed of computer elements can be achieved, these gains will be swiftly swallowed up if the logical design of these machines is not advanced to fit the peculiar requirements of these techniques, to obtain the same results with much fewer operations.

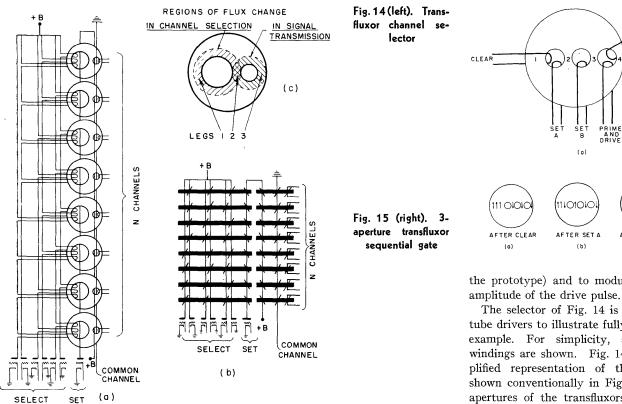

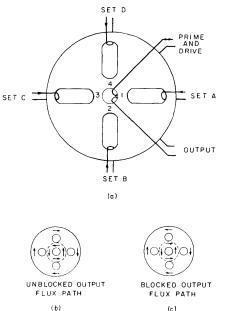

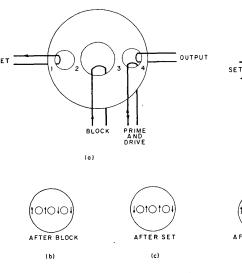

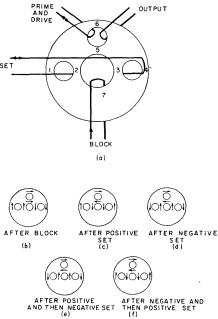

At the present state of the art, these future developments can only be sensed in a most intuitive way, although, for example, the growing concept of a microprogrammed computer appears to be a well-founded first step. Continued and rapid advance in these directions both in programming techniques and in computer design, can only be achieved by building on experience gained in studies using present-day facilities. It is hoped that the presentation of these ideas will encourage the participation of other groups in this fascinating line of endeavor.