# adaptec

ر نفه بر براند در را

> > ٠.

# AHA-1540A/1542A User's Manual

# Preface

#### FCC Compliance

This equipment generates and uses radio frequency energy and if not installed and used properly, that is, in strict accordance with the manufacturer's instructions, may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class B computing device in accordance with the specifications of Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference in residential installation. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause interference to radio or television equipment reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

Reorient the receiving antenna

Relocate the computer with respect to the receiver

Move the computer away from the receiver

Plug the computer into a different outlet so that computer and receiver are on different branch circuits

If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission helpful:

"How to Identify and Solve Radio-TV Interference Problems" This booklet is available from the U.S. Government Printing Office, Washington, D.C. 20402, Stock No. 004-000-00345-4.

Warning: This equipment has been certified to comply with the limits for Class B computing device, pursuant to Subpart J of Part 15 of FCC Rules. Only peripherals (computer input/output devices, terminals, printers, etc.) certified to comply with the Class B limits may be attached to this computer. Operation with non-certified peripherals is likely to result in interference to radio and TV reception. Also this equipment must be used with shielded power cables and shielded I/O cables.

#### AHA-1540A and AHA-1542A Industry PC/AT-to-SCSI Host Adapter User's Manual and Specification Copyright 1989 Adaptec, Inc. All Rights Reserved

Reproduction or use, without express written permission from Adaptec, Inc. and/or its licensor, of any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Adaptec, Inc. assumes no liability resulting from any errors or omissions in this manual, or from the use of the information contained herein.

| 1.0 Introduction                         | .1-         | 1        |

|------------------------------------------|-------------|----------|

| 1.1 Document Scope                       |             |          |

| 1.2 Purpose                              |             |          |

| 1.3 Features                             |             |          |

| 1.4 Product Specifications               | .1-2        | 2        |

| 1.5 Reference Documents                  | .1-4        | 4        |

|                                          | • -         | •        |

| 2.0 Host Adapter Architecture            | .2-         | 1        |

| 2.1 Hardware                             | .2-         | 1        |

| 2.1.1 Bus Master DMA                     | 2-          | 1        |

| 2.1.2 SCSI Protocol Chip                 |             | 1        |

| 2.1.3 8-Bit Memory                       | .2-         | 1        |

| 2.1.4 Block Diagram                      | 2-1         | 2        |

| 2.2 Firmware                             |             |          |

| 2.2.1 Multithreaded Operation            |             |          |

| 2.2.1.1 Mailboxes                        | 2-4         | 4        |

| 2.2.1.2 Command Control Block            |             |          |

| 2.2.1.3 Command Descriptor Block         |             |          |

| 2.2.1.4 Principles of Operation          | 2-0         | 6        |

| 2.2.1.5 Task Queueing                    | 2           | 7        |

| 2.2.2 Single Threaded Operation          | 2-          | <b>'</b> |

|                                          | . 4 -       | '        |

| 3.0 Installation                         | 3-          | 1        |

| 3.1 Unpacking and Inspecting             |             |          |

| 3.2 Installation                         | 3_          | 1        |

| 3.2.1 System Configuration               | 3_          | 1        |

| 3.2.2 Hardware Setup                     | ີ 3_'       | 2        |

| 3.2.3 Checklist                          | 3_          | Δ        |

| 3.2.4 Operation Using the BIOS under DOS | 3_          | Δ        |

| 3.3 Jumper Configuration                 | ່.ງ⊸<br>ຊ_  | 5        |

| 3.3.1 Jumper Block J1                    | 3_          | 6        |

| 3.3.1.1 SCSI Synchronous Negotiation     |             |          |

| 3.3.1.2 Diagnostic Jumper                |             | 6        |

| 3.3.1.3 SCSI Parity                      |             | 6        |

| 3.3.2 SCSI Address                       | · · · · · · | 7        |

|                                          |             |          |

| 3.3.3 DMA Channel                        |             |          |

| 3.3.4 AT Interrupt Channel.              |             | 9<br>1 0 |

| 3.3.5 DMA Transfer Speeds                | . 3-1       | 10       |

| 3.3.6 AT BIOS Wait State                 |             |          |

| 3.3.7 AT Port Address                    |             |          |

| 3.3.8 AT BIOS Address                    | . 2 - 1     | 11       |

| 3.3.9 Front Panel LED                    | .3-         | 11       |

| 3.3.10 LA Enable Jumper                  | .3-         | 12       |

| 3.3.11 Auxiliary Jumpers                 | .3-         | 12       |

| 3.3.12 BIOS Enable/Disable               | .3-         | 12       |

| 3.3.13 SCSI Terminators                  |             |          |

| 3.3.14 SCSI Terminator Power             | .3-         | 13       |

adaptec

# Table of Contents

| 2.4 FL (1) D'I and Controller Lucrosom (ALLA 1542A Oct.)           | 2 12                        |

|--------------------------------------------------------------------|-----------------------------|

| 3.4 Flexible Diskette Controller Jumpers (AHA-1542A Only)          |                             |

| 3.4.1 Flexible Diskette Controller Secondary Address               | 3-13                        |

| 3.4.2 Flexible Diskette Controller Enable                          | 3-13                        |

| 3.4.3 Flexible Diskette Controller Interrupt Channel               | 3-13                        |

| 3.4.4 Flexible Diskette Controller DMA Request Channel             | 3-14                        |

| 3.4.5 Flexible Diskette Controller DMA Acknowledge Channel         | $\frac{3}{2} \frac{14}{14}$ |

| 5.4.5 FIEXIDIE DISKELLE CONTIONEL DIVIA ACKNOWICIGE Champer        | 5-14                        |

| 40 Handware Functional Description                                 | A 1                         |

| 4.0 Hardware Functional Description                                |                             |

| 4.1 Overview                                                       | .4-1                        |

| 4.2 I/O Port Interface                                             | .4-1                        |

| 4.2.1 Control and Status Port                                      |                             |

| 4.2.2 Command and Data Port                                        | .4-4                        |

| 4.2.3 Interrupt Flag Port                                          |                             |

| 4.3 Reset Overview                                                 |                             |

| 4.3.1 Hard Reset Operations                                        |                             |

| 4.3.1 That Reset Operations                                        | .4-/                        |

| 4.3.2 SCSI Reset Operations                                        | .4-/                        |

| 4.3.2.1 SCSI "Soft" Reset Option                                   | .4-8                        |

| 4.3.2.2 SCSI "Hard" Reset Option                                   | .4-9                        |

|                                                                    |                             |

| 5.0 Firmware Functional Description                                | .5-1                        |

| 5.1 Host Adapter Command Overview                                  | .5-1                        |

| 5.1.1 Host Adapter Operation Codes                                 |                             |

| 5.1.1.1 No Operation                                               |                             |

| 5.1.1.2 Mail Box Initialization                                    |                             |

|                                                                    |                             |

| 5.1.1.3 Start SCSI Command                                         | .3-3                        |

| 5.1.1.4 Start PC/AT BIOS Command                                   |                             |

| 5.1.1.5 Host Adapter Inquiry                                       | .5-3                        |

| 5.1.1.6 Enable Mailbox Out Available Interrupt                     | .5-4                        |

| 5.1.1.7 Set Selection Time-out                                     | .5-4                        |

| 5.1.1.8 Set Bus-On Time                                            |                             |

| 5.1.1.9 Set Bus-Off Time                                           |                             |

| 5.1.1.10 Set Transfer Speed                                        |                             |

|                                                                    |                             |

| 5.1.1.11 Return Installed Device                                   |                             |

| 5.1.1.12 Return Configuration Data                                 | .3-8                        |

| 5.1.1.13 Enable Target Mode Command                                | .5-8                        |

| 5.1.1.14 Return Setup Data                                         | .5-9                        |

| 5.1.1.15 Write Adapter Channel 2 Buffer                            | .5-11                       |

| 5.1.1.16 Read Adapter Channel 2 Buffer                             | 5-12                        |

| 5.1.1.17 Write Adapter FIFO Buffer                                 | 5-12                        |

| 5.1.1.18 Read Adapter FIFO Buffer                                  | 5.12                        |

| 5.1.1.10 Reau Audpier FIFO Durier                                  | 5 12                        |

| 5.1.1.19 Echo Command Data                                         |                             |

| 5.2 Mailbox Command Overview                                       |                             |

| 5.2.1 Mailbox-Out Definition                                       |                             |

| 5.2.2 Mailbox-In Definition                                        |                             |

| 5.3 Command Block Definition                                       | 5-19                        |

| 5.3.1 Scatter Gather Definition                                    |                             |

| 5.4 Description of Operation                                       | 5-26                        |

| 5.4.1 Execution of Initiator Mode Operations                       | 5_27                        |

| 5.4.2 Execution of Target Mode Operations                          | 5 70                        |

| 5.4.2 Execution of Target Mode Operations                          | 5 70                        |

| 5.4.2.1 Target Mode with a Prepared CCB                            | 5-28                        |

| 5.4.2.2 Target Mode Without a Prepared CCB                         | 5-28                        |

| 5.5 DMA Channel Initialization With the Host Adapter BIOS Disabled | .5-29                       |

| 5.6 Interrupt Initialization                                       | . 5-29                      |

ii

# **Table of Contents**

| 6.0 Single-Threaded Software Interface               | 6-1         |

|------------------------------------------------------|-------------|

| 6.1 Single Threaded BIOS Command Interface           | .6-1        |

| 6.2 BIOS Command Execution Using Interrupt 13        | .6-2        |

| 6.2.1 Physical to Logical Translation                |             |

| 6.2.2 BIÓS Command Return Codes                      | 6-3         |

| 6.3 BIOS Disk Commands                               |             |

| 6.3.1 Reset Disk Subsystem                           |             |

| 6.3.2 Read Status of Last Operation                  | .6-5        |

| 6.3.3 Read Desired Sectors Into Memory               | 6-6         |

| 6.3.4 Write Desired Sectors From Memory              | .6-6        |

| 6.3.5 Verify Desired Sectors                         | .6-6        |

| 6.3.6 Identify SCSI Devices                          | 6-7         |

| 6.3.7 Read Drive Parameters                          | .6-7        |

| 6.3.8 Initialize Drive Pair Characteristics          | 6-8         |

| 6.3.9 Seek                                           | 6-8         |

| 6.3.10 Alternate Disk Reset                          | 6-8         |

| 6.3.11 Test Drive Ready                              | 6-9         |

| 6.3.12 Recalibrate                                   | 6-9         |

| 6.3.13 Read DASD Type                                | 6-9         |

|                                                      |             |

| 7.0 Device Drivers                                   | 7-1         |

| 7.1 PC/AT BIOS                                       |             |

| 7.1.1 Initialization                                 |             |

| 7.1.2 System Boot                                    |             |

| 7.1.3 Hard Disk I/O                                  | 7-2         |

| 7.2 XENIX/UNIX                                       |             |

| 7.3 DOS Driver                                       |             |

| 7.3.1 DOS Driver Support of Virtual Mode             |             |

| 7.4 AHA-1540 On-board Utilities                      | 7-4         |

|                                                      | 1 -         |

| 8.0 SCSI Features                                    | 8-1         |

| 8.1 SCSI Description Initiator Mode                  |             |

| 8.1.1 Linked SCSI Commands                           | 8-2         |

| 8.1.2 Zero Latency Read Operation                    | 8-2         |

| 8.1.3 SCSI Messages                                  | 8-3         |

| 8.2 SCSI Description, Target Mode                    | 8-3         |

| 8.2.1 Initiator Conformance Level Requirements       | 8-3         |

| 8.2.2 Support of Synchronous Transfer                |             |

| 8.2.3 SCSI Target Operation in Processor Target Mode | 8-4         |

| 8.2.3.1 Test Unit Ready                              | 8-5         |

| 8.2.3.2 Request Sense                                |             |

| 8.2.3.3 Inquiry                                      |             |

| 8.2.3.4 Send                                         |             |

| 8.2.3.5 Receive                                      |             |

| 8.2.4 Incorrect Length Management                    |             |

|                                                      | .0-7        |

| 9.0 Floppy Disk Interface                            | <b>9</b> _1 |

| Jor Hoppy Disk Interface                             |             |

# **Table of Contents**

| 10.0 Problem Determination                                |      |

|-----------------------------------------------------------|------|

| 10.1 Self Diagnostic Capability                           |      |

| 10.2 Indicators                                           |      |

| 10.3 Problems Detected During Operation                   | 10-2 |

| 10.3.1 HA Status Error Indications and Corrective Actions | 10-3 |

| 10.3.2 SCSI Error Indications and Corrective Actions      | 10-5 |

| 10.4 Problems Detected During Installation                | 10-7 |

| 11.0 Glossary                                             | 11-1 |

| Appendix A AHA-1540 System Timing Diagram                 | A-1  |

| Appendix B Connector Pin Out                              | B-1  |

| Appendix C Product Comparison and Compatibility           |      |

٠

# Section One

# **1.1 DOCUMENT SCOPE**

This manual provides the information required to install and program the AHA-1540A and the AHA-1542A Intelligent Host Adapters in AT bus-based systems.

#### **1.2 PURPOSE**

The Adaptec AHA-1540A and AHA-1542A provide a powerful multitasking interface between the Industry Standard Architecture (PC/AT compatible) bus and the Small Computer System Interface (SCSI) bus. The AHA-1540A/1542A are high performance intelligent host adapters supporting a maximum asynchronous SCSI rate of 2.0 MBytes/second and a synchronous transfer rate of 5 MBytes/second. The AHA-1540A/1542A support multithreaded I/O operations, allowing simultaneous operations on multiple targets/LUNs. Disconnect/Reconnect support maximizes bus utilization for multiple target systems. Target mode operation allow the AHA-1540A and AHA-1542A to receive information from other host adapters. Scatter-gather allows high-performance even in systems with fragmented memory buffers.

The Adaptec AHA-1540A/1542A provides a solution for system applications requiring very high performance, configuration flexibility and multithreaded I/O capability, and system redundancy. The Adaptec BIOS also allows the AHA-1540A/1542A to be used in place of a standard hard disk controller. The AHA-1540A host adapter provides only the high performance host adapter circuitry. The AHA-1542A host adapter provides identical host adapter circuitry, but adds an IBM compatible flexible diskette controller to the circuit board.

## 1.3 AHA-1540A/1542A PRODUCT FEATURES

- High performance Bus Master DMA with selectable or programmable data rates of up to 10 MBytes/second.

- 16- and 8-bit transfers

- Odd and Even starting address transfers and odd or even data lengths

- Maximum synchronous SCSI transfer rate of up to 5.0 MBytes/second

- Asynchronous and synchronous peripherals supported simultaneously

- Programmable AT bus burst transfer on and off time

- Jumper selectable DMA channel for bus arbitration (channels 0,5,6,7)

- Jumper selectable interrupt channels (IRQ 9, 10, 11, 12, 14, 15)

- True multithreaded operation supporting up to 255 tasks simultaneously

- Programmable mailbox architecture

- Adaptec BIOS for standard hard disk emulation

- Jumper selectable I/O port address

- Internal and external SCSI connectors

- Initiator and Target modes of operation fully supported

- On-board flexible diskette controller (AHA-1542A only)

- Scatter-gather

# Section One

# Introduction

#### **1.4 PRODUCT SPECIFICATIONS**

• Physical Dimensions:

Length : 13.25 " Width : 4.125" Height : 0.5"

Standard PC/AT<sup>™</sup> compatible form factor

• Power Requirements:

+5.0 +/- 0.25 Volts at 2.1 Amps maximum.

• Environmental Requirements:

**Temperature 0-60 degrees C** (operating or storage)

• Reliability Information

Mean Time Between Failures: 15000 hours (calculated per Mil Handbook 217E, ground benign, 40 °C)

Mean Time Between Failures: TBD hours (experimental)

Mean Time to Repair: 30 minutes

• Industry Standard Architecture Interface

Standard PC/AT bus electronic and physical interface.

Driver output:

|                   |      | 0 volts   |      |            | IOL:              | 24 ma. |

|-------------------|------|-----------|------|------------|-------------------|--------|

| V <sub>OH</sub> : | min: | 2.4 volts | max. | 5.25 volts | I <sub>OH</sub> : | 8 ma.  |

Receiver Input

| V <sub>IL</sub> : | 0.8 volts |

|-------------------|-----------|

| V <sub>IH</sub> : | 2.0 volts |

Connector configuration as specified by IBM PC/AT Technical Reference Manual or manual of Industry Standard Architecture host computer.

• SCSI Interface:

**Electrical Interface:**

As specified by ANSI X3.131-1986 for single-ended operation.

| Minimum driver output:                                 | 48 m                 | nilliamps, s                      | inking @ 0.5 volts |                               |

|--------------------------------------------------------|----------------------|-----------------------------------|--------------------|-------------------------------|

| Signal true:<br>Signal false:<br>Input hysteresis:     | min:<br>min:<br>min: | 0 volts<br>2.0 volts<br>0.2 volts | max:<br>max:       | 0.8 volts<br>5.25 volts       |

| Terminator Power voltage:<br>Terminator Power current: | min:<br>min:         | 4.25 volts<br>800 ma.             | max:<br>max:       | 5.25 volts<br>1.5 amp (fused) |

#### Internal connector:

Unshrouded 50-pin header, compatible with unshielded alternative 1 connector as specified in ANSI X3.131-1986 Figure 4-1

For connector pin out, see Appendix B.

Partial list of compatible connector plugs (for reference only):

| Manufacturer | Model | Part Number |

|--------------|-------|-------------|

| 3-M          | N.A.  | 3425-6000   |

| T&B Ansley   | N.A.  | 609-5000M   |

| Molex        | N.A.  | 15-29-8505  |

Cable for internal SCSI connector should be good quality 50 conductor flat cable with 26 or 28 gauge conductors and a characteristic impedance (Z<sub>0</sub>) of  $100 \pm 10 \ \Omega$ . Cable shielding is necessary if extremely noisy circuitry or extremely noise sensitive circuitry is present inside the host computer frame.

#### External connector:

Shielded 50-pin connector as specified in ANSI X3.131-1986, Figure D-4.

For connector pin out, see Appendix B.

Partial list of compatible connector plugs or cable assemblies (for reference only):

| Manufacturer | Model                    | Part Number     |

|--------------|--------------------------|-----------------|

| Amphenol     | N.A.                     | 200-1M115-02003 |

| •            | (Mates with 57-BC50B-AM) | 200)            |

| AMP          | Champ                    |                 |

|              | Plug                     | 554953-1        |

|              | Cover                    | 554946 - x(1-2) |

|              | Ferrule                  | 554725 - x(1-6) |

Cable for external SCSI connector should be good quality 100% shielded round cable with 25 twisted pairs. Each pair should have a characteristic impedance (Z<sub>0</sub>) between 90 and 135  $\Omega$ . Wire gauge may be 26 or 28 AWG. All pairs should have the same impedance and should have the same delay per length of cable. Cables meeting these requirements will normally operate correctly in any SCSI configuration and should normally meet all FCC requirements.

• Floppy Disk Interface

Standard Floppy Disk electronic and physical interface:

Driver output:

| V <sub>OL</sub> : | min:   | 0 volts   | max. | 0.5 volts  | IOL: | 60 ma. |

|-------------------|--------|-----------|------|------------|------|--------|

| V <sub>OH</sub> : | open o | collector | max. | 5.25 volts | IOH: | .1 ma. |

Receiver Input

Tied to +5 volt supply through 150  $\Omega$  resistors. Schmidt Trigger with 0.8 volts hysteresis V<sub>T</sub>.: max 1.0 volts V<sub>T+</sub>: min 1.4 volts

Connector:

Unshrouded 34-pin header.

For connector pin out, see Section 9.1

Partial list of compatible connector plugs (for reference only):

| Manufacturer | Model | Part Number |

|--------------|-------|-------------|

| 3-M          | N.A.  | 3414-6000   |

| T&B Ansley   | N.A.  | 609-3400M   |

Cable for floppy connector should be good quality 34 conductor flat cable with 28 gauge conductors. Addressing of the second drive may be generated by twisting connector signals 10 through 16 or by changing jumpers in the floppy disk drives.

• Meets radiation limits specified for a Class B computing device in accordance with the specifications in Subpart J of Part 15 of FCC Rules. See FCC Compliance notes and recommendations in preface of this document.

# **1.5 REFERENCE DOCUMENTS**

- IBM PC/AT Technical Reference Manual

- Small Computer System Interface, ANSI X3.131-1986, American National Standards Institute

- Adaptec AĤA-1540A/AHA-1542A Host Adapter Installation Guide

## 2.1 HARDWARE

#### 2.1.1 Bus Master DMA

The AHA-1540A/1542A controls the host AT bus as a master and transfers data directly to and from main system memory. This implementation is known as Bus Master DMA. Bus Master DMA greatly reduces the host software overhead because the host CPU is no longer required to maintain the DMA channel's address pointers and word counts. Bus Master DMA also reduces the number of interrupts generated per I/O command. The Adaptec AIC-560L is the DMA controller.

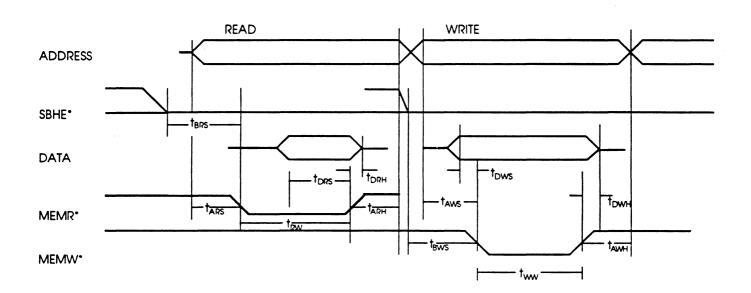

Adaptec's implementation of Bus Master DMA can achieve a 10 MB/second burst data rate. This speed is especially valuable in multitasking systems where the tasks execute on a time shared basis. Appendix A shows a diagram of the timing required to achieve the DMA rates that are supported by the AHA-1540A/1542A.

The AHA-1540A/1542A DMA hardware will handle both odd-byte and odd-memory address data transfers with no performance degradation.

## 2.1.2 SCSI Protocol Chip (AIC-6250)

The AHA-1540A/1542A utilizes the AIC-6250 SCSI protocol chip to maximize the SCSI bus utilization. The AIC-6250 is an Adaptec VLSI device which allows the AHA-1540A/1542A to achieve greater than 2.0 MBytes/Sec asynchronous SCSI data transfer rates, and up to 5.0 MBytes/second synchronous transfer rates. The AIC-6250 will also enable the AHA-1540A/1542A to operate as both an initiator and as a target device.

Through a 16-bit host interface, the AIC-6250 reduces bus busy time during data transfer by bursting data across the AT bus at up to 10 MBytes/second. The AIC-6250 has separate data busses for the local microprocessor and for the system data bus. This further increases the performance of the AHA-1540A/1542A by reducing the overhead associated with SCSI commands.

#### 2.1.3 8 Bit Memory

During normal DMA operations, nearly all transfers to and from memory are 16 bit transfers. At the very end, or the very beginning of an odd address boundary, an 8 bit transfer on the upper data bits (D8-D15) will occur according to the AT bus architecture. Some memory in the I/O space, such as video RAM, is 8 bits only and always transfers data only on the lower data bits (D0-D7). The AHA-1540A/1542A will transfer 16 bit or 8 bit memory in the address space between 0A0000 hex and 0BFFFF hex depending on the signal line MEM16 on the AT bus. If this signal is active, 16 bit memory is assumed, and if inactive 8 bit memory is assumed. Outside of this address space 16 bit memory is always assumed.

# Section Two

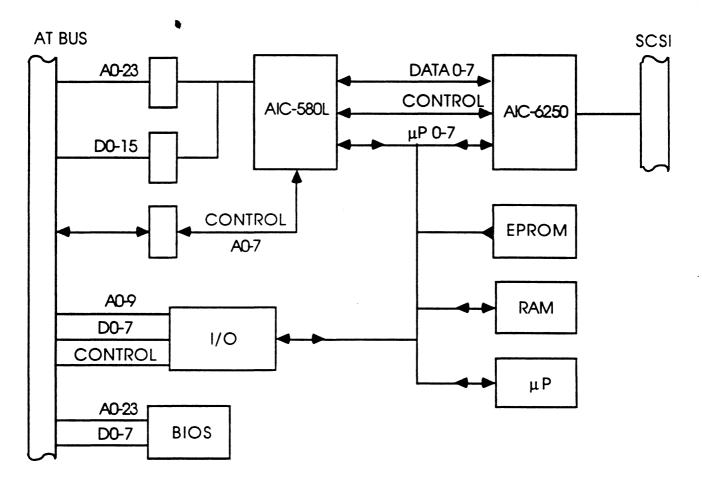

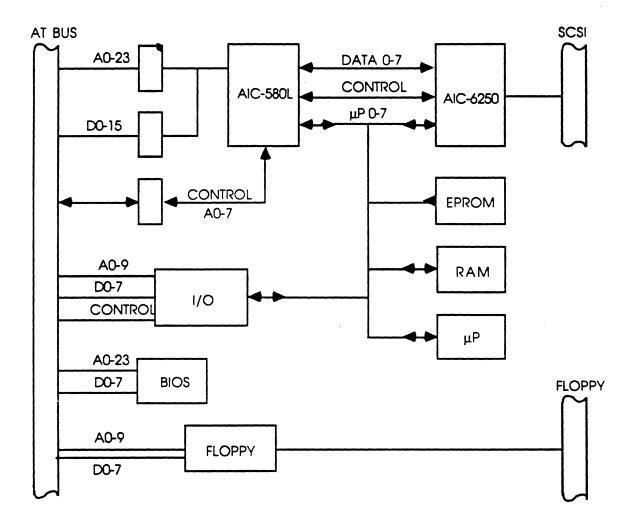

# 2.1.4 Hardware Block Diagram

# **BLOCK DIAGRAM OF AHA-1540A**

AHA-1540A/1542A

## **BLOCK DIAGRAM OF AHA-1542A**

# Section Two

# 2.2 FIRMWARE

The AHA-1540A/1542A supports multithreaded SCSI initiator operation through a simple mailbox protocol. The firmware accepts as many Command Control Blocks (CCB's) as required and executes them from its local RAM. The firmware controls all of the SCSI activity that a task may require. This includes: Arbitration, Selection, Disconnection, Reconnection, and Command completion.

Using the same mailbox protocol, the AHA-1540A/1542A can operate as a Processor type device serving as a multitasking target to other initiators. This feature allows high bandwidth communication between multiple hosts.

In addition, the AHA-1540A/1542A firmware cooperates with the BIOS installed on the host adapter to emulate the standard DOS BIOS calls. This allows booting operations and the execution of standard DOS operations from attached SCSI disks, allowing the SCSI subsystem to completely replace the usual internal disk functions.

#### 2.2.1 Multithreaded Operation

A multiuser, multitasking operating system issues a large number of I/O tasks in a rapid sequence. The architecture of the AHA-1540A/1542A makes management of this activity very easy and straightforward for the operating system and its associated I/O drivers. This section briefly explains the interaction between the system and the AHA-1540A/1542A required to accomplish an I/O task.

#### 2.2.1.1 Mailboxes

The AHA-1540A/1542A uses a mailbox architecture for task communication between the host and host adapter. This allows the host adapter to perform multithreaded operations with a minimum of host intervention. The mailboxes are located in main system memory. Each mailbox entry is four bytes long. After power up sequencing, host initialization procedures, and the boot procedure are completed, the host issues an initialization command to inform the host adapter of the mailbox location. There are always an equal number of Outgoing Mailboxes (MBO) and Incoming Mailboxes (MBI). MBIs are located immediately after the MBOs. A typical mailbox structure is shown below:

| Dase A | الر<br> |               | _     |   |

|--------|---------|---------------|-------|---|

| + 0    | CMD     | CCB 4 Pointer | мво   | 0 |

| + 4    | CMD     | CCB 2 Pointer | мво   | 1 |

| + 8    | 00      | Free Entry    | мво   | 2 |

| +12    | CMD     | CCB 3 Pointer | · MBO | 3 |

| +16    | 00      | Free Entry    | MBI   | 0 |

| +20    | Status  | CCB 1 Pointer | MBI   | 1 |

| +24    | 00      | Free Entry    | MBI   | 2 |

| +28    | 00      | Free Entry    | MBI   | 3 |

|        |         |               | -     |   |

Base Adr

# Section Two

In this example there are four MBOs and four MBIs. The first byte of each MBO contains the MBO Command byte. The remaining three bytes point to a Command Control Block (CCB). The CCB provides all the rest of the information needed to complete a task. A MBO is available to accept a new entry if the first byte is zero.

The first byte of each MBI contains the status of a completed task. The remaining three bytes point to the CCB of the completed task. An MBI is free if the Status byte is zero. Mailboxes may point to CCB's controlling initiator tasks, controlling target tasks, or controlling error recovery tasks.

#### 2.2.1.2 Command Control Block

A Command Control Block provides the information required to control a SCSI command sequence. The block contains pointers to the data area to be used by the command. It contains areas for presenting status of both the host adapter and the addressed SCSI device. In addition, it contains the SCSI Command Descriptor Block defining the action to be taken by the addressed SCSI device. An error information buffer area is also provided.

A Command Control Block is also used to service an operation requested by another initiator when the AHA-1540A/1542A is being addressed as a SCSI Processor device.

The CCB is defined completely in Section 5.

A typical CCB is shown below:

| Byte | 0   | Command Control Block Opcode   |             |              |     |  |

|------|-----|--------------------------------|-------------|--------------|-----|--|

| , -  | +1  | Tar/Init                       | Data Out    |              | LUN |  |

|      | +2  |                                | nmand Leng  | gth = m      |     |  |

|      | +3  | Returned Sense Info Length = n |             |              |     |  |

|      | +4  | Data Length (MSB,MID,LSB)      |             |              |     |  |

|      | +7  | Data Pointer (MSB,MID,LSB)     |             |              |     |  |

|      | +10 | Link Pointer (MSB,MID,LSB)     |             |              |     |  |

|      | +13 | Command Link ID                |             |              |     |  |

|      | +14 | Host Status                    |             |              |     |  |

|      | +15 | Target Status                  |             |              |     |  |

|      | +16 | Reserved                       |             |              |     |  |

|      | +17 | Reserved                       |             |              |     |  |

|      | +18 | SCSI Command Bytes (m Bytes)   |             |              |     |  |

| 18 - | + m | Allocate                       | d for Sense | Data ( n Byl | es) |  |

# 2.2.1.3 Command Descriptor Block

The Command Descriptor Block (CDB), a part of the Command Control Block, is a standard format command packet that is transmitted to the addressed SCSI device. It contains all the command information required by the SCSI device to perform the desired operation. The Command Descriptor Block contains the command Operation Code followed by a Logical Unit Number (LUN), command parameters if required, and a control byte. A typical Group 0 six byte CDB is shown below:

| BIT<br>BYTE | 7                           | 6        | 5 | 4                           | 3 | 2 | 1    | 0    |

|-------------|-----------------------------|----------|---|-----------------------------|---|---|------|------|

| 0           | Operation Code              |          |   |                             |   |   |      |      |

| 1           | LUN                         |          |   | Logical Block Address (MSB) |   |   |      |      |

| 2           | Logical Block Address       |          |   |                             |   |   |      |      |

| 3           | Logical Block Address (LSB) |          |   |                             |   |   |      |      |

| 4           | Transfer Length             |          |   |                             |   |   |      |      |

| 5           | Vendo                       | r Unique | R | eserved                     |   |   | Flag | Link |

Please refer to the SCSI specification ANSI X3.131, the Common Command Set (CCS) revision 4B, and the SCSI 2 draft for additional information on Command Descriptor Blocks.

# 2.2.1.4 Principles of Operation

At power-up, the host must inform the host adapter of the location and number of mailboxes. To start a task, the host builds a CCB and stores its memory address into a free mailbox. A non-zero Mailbox Out command byte is then written to indicate that the mailbox entry is full and valid. The host then writes to an I/O port (defined in section 4) to indicate that the host adapter should scan the MBO area. When a full MBO is found, the host adapter copies the mailbox's CCB pointer into its internal RAM and clears the Mailbox entry by writing a zero to the MBO command byte. This frees the MBO so that it can be used to start another task.

After completing a task, the host adapter scans the MBI area for a free mailbox. When one is found, it is updated with the task's completion status and CCB pointer. The CCB pointer identifies the completed task. A MBI Stored interrupt is generated to notify the host that a task has been completed. The host scans the MBI area searching for a non-zero Status byte. When one is located, the host obtains the CCB pointer and frees the MBI by writing a zero into the Status byte. The host then examines the contents of the CCB to determine that the command was successfully completed. The freed MBI can now be used to indicate the completion of another task. The host adapter fills the MBI area and scans the MBO area in a round robin fashion. If the host saves the position of the last active MBI entry, it can determine the MBI of a new entry immediately without searching, since a new entry will be in the next MBI location.

The host adapter transmits a new MBO Available or MBI Full interrupt to the host whenever all non-Mailbox interrupts have been cleared and serviced by the host. The host should analyze the interrupts and clear them as soon as possible so that the host adapter can post any new interrupts quickly. The host adapter will not wait until an interrupt can be transmitted to the host before processing an MBO entry or creating a new MBI entry. Thus, in processing a single MBI

# Section Two

interrupt, the host may find several MBI entries waiting by the time the interrupt processing is finished. Similarly, a later MBI interrupt for the last of the later MBI entries may find nothing to service because the MBI entry was examined and processed as a result of the first MBI Full interrupt. If the interrupts are reset quickly by the host, the probability of an interrupt occurring when no MBI entry is available is much lower, providing an important performance improvement. If the MBI entries are emptied by the host in a round-robin order, the scan for the next full entry is very simple, since it is always the next MBI entry in the Mailbox area.

# 2.2.1.5 Task Queueing

Multiple tasks may be started against a target/LUN or against multiple targets/Logical Units. Since only one task can be active against any one given LUN at a time, all other tasks for the same LUN are queued. Other LUN's may have active tasks at the same time.

The host adapter dequeues on a first in, first out (FIFO) basis for each target/LUN combination. However, due to the optimization algorithm used by the host adapter, a task may sometimes be started earlier in spite of it's late entrance in the queue on multiple target/LUN systems. Task queueing should not be used where changes in the order of command execution may cause data integrity failures.

#### 2.2.2 Single-Threaded Operation

A host adapter BIOS is provided to emulate the standard hard disk BIOS and boot functions. With this BIOS, the host adapter can be used in lieu of a standard hard disk controller on any ISA compatible system.

The BIOS is compatible with the standard hard disk BIOS. This allows DOS to access up to two hard disk devices on the SCSI bus without a driver. All normal I/O functions are supported including system booting. Single threaded operation and multithreaded operation do not operate simultaneously. Single threaded operation cannot be requested until all multithreaded operations are completed. Similarly, all multithreaded operations must be complete before a single threaded operation can be requested. For most multitasking operating systems, such as Xenix and OS/2, single threaded operation is normally used only for the early part of the boot operation, after which multithreaded drivers take over all control of the SCSI operations.

# 3.1 UNPACKING AND INSPECTION

The carrier is responsible for damage incurred during shipment. In case of damage, have the carrier note the damage on both the delivery receipt and the freight bill, then notify your freight company representative so that the necessary insurance claims can be initiated.

After opening the shipping container, use the packing slip to verify receipt of the individual items listed on the slip. Retain the shipping container and packing material for possible later reuse should return of the equipment to the factory necessary.

CAUTION: THE AHA-154XA IS CAREFULLY DESIGNED TO RESIST THE EFFECTS OF STATIC ELECTRICITY. HOWEVER, LIKE ALL ELECTRONIC EQUIPMENT, IT CAN BE DAMAGED OR ITS LIFE CAN BE SHORTENED BY UNUSUAL STATIC DISCHARGES. PLEASE TAKE THE PROPER PRECAUTIONS WHEN HANDLING THE BOARD. KEEP THE BOARD IN ITS CONDUCTIVE WRAPPING UNTIL IT IS READY TO BE INSTALLED IN YOUR SYSTEM. BE SURE THAT THE HOST COMPUTER AND THE PERSONNEL HANDLING THE BOARD ARE PROPERLY GROUNDED WHILE INSTALLING THE BOARD.

## 3.2 INSTALLATION

The following section details the installation procedure for the Adaptec AHA-1540A/1542A AT to SCSI host adapter. The installation of the board consists of setting the various on-board jumpers, preparing the SCSI devices, installing the correct terminations, inserting the board into a full-length AT compatible connector, and connecting a SCSI cable from the on-board connector to a SCSI target.

NOTE: The system must be turned off during the installation procedure.

## 3.2.1 System Configuration

The DOS operating system and the standard AT BIOS support two hard disk drives, drive C: and drive D:. If two standard hard disk drives are installed, they are the only hard disk drives accessible from the operating system. If one standard hard disk drive is installed, the AHA-154XA BIOS allows DOS to access the SCSI drive with the Target:LUN address of 0:0 as the second of the two supported drives (drive D:). If no standard hard disk drives are installed, the AHA-154XA BIOS allows DOS to access the SCSI drive with the address of 0:0 as the first of two supported drives (drive C:) and the SCSI drive with the address of 0:1 or 1:0 as the second of the drives (drive D:). System booting is performed from the floppy drive if a floppy diskette is installed. If no floppy is installed, system booting is attempted from the drive chosen as drive C: through the above process, whether the drive is a standard hard disk or a SCSI hard disk. The AHA-154XA BIOS fully supports the extended partitioning capabilities of DOS 3.3 for up to two drives. The AHA-154XA BIOS only supports the AHA-154XA if its I/O Port Address is set to 330h.

# Section Three

Adaptec provides a special DOS driver for the AHA-154XA that allows the support of up to 24 physical or logical devices under DOS. Many other operating systems, including SCO Xenix and Unix, do not have this limitation and will allow the access of any number of attached SCSI devices.

The term "standard hard disk" refers to the disks attached to the system by a standard ISA disk controller. These standard hard disks can be set to the "Installed" or "Not Installed" state by the SETUP program that is supplied with each ISA host computer. The SETUP program allows the user to select the number of standard hard disks that are recognized by the system regardless of whether or not they are physically installed.

#### 3.2.2 Hardware Setup

Several preparatory steps must be taken to install the host adapter in the host computer. The initialization jumpers must be correctly placed in the AHA154XA. The SCSI Bus terminators must be installed in the correct SCSI devices. Finally, the correct SCSI addresses must be assigned to each peripheral device.

The Adaptec AHA-1540A/1542A 16-Bit AT bus to SCSI bus Host Adapter has been designed to operate as shipped in the majority of AT class computers. The host adapter's jumper settings should almost always remain in their original default positions. Refer to section 3.3 if conflicting memory or port assignments require that the host adapter jumpers be reconfigured. The AHA-1540A/1542A is shipped with the following default settings:

| SCSI Address            | 7         |

|-------------------------|-----------|

| SCSI Parity             | Enabled   |

| Terminators             | Installed |

| Terminator Power        | Supplying |

| Synchronous Negotiation | Disabled  |

| DMA Channel             | 5         |

| Interrupt Channel       | 11        |

| AT Port Address         | 330H      |

| AT BIOS Address         | ODCOOOH   |

| LA Enable Jumper        | Installed |

#### Termination

The SCSI bus must be terminated correctly to assure proper operation. The first and last physical SCSI devices on the SCSI cable must have terminators installed. All other SCSI devices must have terminators removed. The host adapter is shipped with terminators already installed at locations RN3, RN4, and RN5. The internal and external connectors connect to the same SCSI bus, so both internal and external cabling must be considered in determining where terminators are installed.

If only one cable (either internal or external) is connected to the host adapter, the terminators must remain installed in the host adapter. Terminators must also be installed on the device at the farthest end of the cable from the host adapter. Terminators must be removed from all other attached SCSI devices.

# Section Three

If both an internal and an external cable are connected to the host adapter, remove the terminators on the host adapter and install terminators on the devices at the farthest end of each cable. Terminators must be removed from all devices except the device at the end of each cable. The instruction manuals for each SCSI device will indicate how the terminators can be removed or replaced.

## Addressing

The SCSI target address for each SCSI device to be attached must be selected by setting the proper jumpers or switches on the device. If the SCSI device is a hard disk that is to be used as the boot disk, it must have the Target Identifier (SCSI Address) set to zero and the Logical Unit Number set to zero. SCSI Addresses 0 and 1 should be reserved for SCSI hard disk drives. SCSI Address 2 is often used for tape devices. Each installed peripheral must have a different Target Identifier. The host adapter's default address is 7. Duplicate SCSI Addresses will cause errors that are extremely difficult to identify. Any jumpers that control operating modes must also be properly set. If there is a jumper that enables synchronous transfer negotiation, the jumper should be set to enable negotiation. Check the SCSI drive or controller to ensure that Parity Checking is enabled. If Parity checking on the device is disabled or not supported, the jumper at location J8 of the host adapter should be removed. Parity checking should only be enabled if all SCSI devices support it.

#### Installation Procedure

Now that the host adapter and the devices to be installed have been properly prepared, the devices should be installed in the following manner:

#### 1) Turn OFF the power to the computer system.

2) Remove the system cover according to the directions of the computer manufacturer.

3) If only an external SCSI subsystem is to be used, no internal cabling is required. If an internal SCSI peripheral is to be used, install a 50 pin SCSI ribbon cable to the host adapter. This cable must be oriented correctly. Pin 1 of the SCSI cable is designated by a red stripe. Multi-color 50 pin ribbon cables signify pin 1 with a brown color. Pin 1 on the host adapter 50 pin SCSI header is located on the left hand side, farthest from the installation bracket and is designated by the words PIN 1 on the board adjacent to the header. After locating pin 1 on the host adapter and on the SCSI cable, carefully insert the connector located at the end of the long end of the cable into the host adapter connector. After ensuring that all pins are lined up and that the pin 1 orientation is correct, firmly seat the connector to the board. If it is ever necessary to remove the cable, gentle prying with a small thin-bladed screwdriver may be required.

4) After installing the SCSI cable, the host adapter can be installed in any one of the adapter slots in the host computer.

5) If an internal SCSI device is to be used, it should be installed in the drive bays in accordance with the directions on the peripheral. The proper power supply must be connected to the SCSI peripheral device.

6) The 50 pin SCSI ribbon cable can now be attached to each SCSI device. Refer to the device's installation instructions to ensure proper pin 1 orientation. Pin 1 orientation must be consistent throughout the system. Keep the ribbon cable neatly dressed away from the ventilation slots in the computer system. Keep the ribbon cable dressed away from possible electrical noise sources or noise sensitive components, particularly large microprocessors, memory boards, switching power supplies, and analog data acquisition boards. If the internal

# \*Section Three

configuration requires the cable to come near noise sensitive circuits, make sure that the cable crosses the boards at right angles and is near the noise sensitive circuits for the shortest distance possible.

7) Carefully reinstall the cover of the computer.

8) If an external SCSI subsystem is to be installed, it can now be cabled to the External SCSI Connector projecting from the shielding bracket on the back of the AHA-154XA Host Adapter. The proper shielded SCSI cable must be used for proper operation. The external connector on the AHA-1540A/1542A is a D shell connector that ensures correct pin 1 orientation on the host adapter. The subsystem, cables, and SCSI terminators must be installed in accordance with the directions provided with the external SCSI subsystem. The addresses selected for external SCSI devices must not overlap with the addresses of the host adapter or any other SCSI devices attached internally.

# 3.2.3 Checklist

Before applying power to your system, the following items should be completed and checked:

- 1. 50 pin SCSI ribbon cable is connected to the host adapter with proper pin 1 orientation.

- 2. The host adapter is firmly seated in the host computer's adapter slot.

- 3. The correct SCSI addresses are selected on all attached SCSI devices. Address 0 is reserved for the boot hard disk and address 1 is used for a second hard disk.

- 4. The correct operating modes are selected on all attached SCSI devices.

- 5. Terminators are installed or removed on the drives and host adapter as required.

- 6. External SCSI devices are properly installed and cabled.

# 3.2.4 Operation Using the BIOS Under DOS

To bring up the system for the first time with the host adapter installed, insert a bootable system diskette in drive A:, and close the door. After the system initialization and power-up diagnostics have completed, system error messages, such as "SYSTEM CONFIGURATION CHANGED, RUN SETUP" and prompts on how to continue, may be displayed. After following the instructions displayed on the screen, the system will boot from the flexible diskette drive.

Run your SETUP program to configure the system as required. Remember that a SCSI drive can only be used as a boot device if both standard hard disks are mapped out. When the SETUP parameters have been defined, follow the directions on the screen to re-initialize the system.

Most SCSI drives are shipped from the factory with a complete low-level format. A few SCSI drives and most bridge controllers, including the CCS compatible Adaptec ACB-4525Z, require a low-level SCSI format operation before they will operate. Section 7.4 describes how the low-level format utility that is available in the Adaptec BIOS Utilities should be used to format such SCSI devices.

Run the DOS FDISK program to partition the disk for the number of cylinders to be used by DOS. When using DOS 3.2 or under, it is generally a good idea to select 1 less cylinder than the maximum allowable per partition according to DOS. This eliminates the possibility of exceeding the 32 MB limit. Activate the first DOS partition before leaving the FDISK program if it is to be the boot partition. If you are not sure if a DOS partition exists, use the menu entry in FDISK to display partition data.

# Section Three

After the DOS partition has been created and activated, the drive is ready for a DOS FORMAT. Refer to the DOS manual for the format options that are available. If the system is going to boot from a SCSI disk, it is usually easiest to transfer the hidden system files to that disk during the FORMAT.

CAUTION: IF THE DRIVE YOU ARE USING WAS PREVIOUSLY FORMATTED OR PARTITIONED WITH A DIFFERENT HOST ADAPTER OR DISK CONTROLLER, A DOS PARTITION MAY ALREADY EXIST. IF SUCH A PARTITION DOES EXIST IT SHOULD BE DELETED AND RE-CREATED USING THIS HOST ADAPTER. IF THIS PRECAUTION IS NOT FOLLOWED, ERRATIC SYSTEM OPERATION MAY RESULT.

The host adapter and SCSI disks are now ready for normal operation. The host adapter's BIOS performs the necessary initialization procedures during the boot operation. This procedure is described in section 6.1.1

#### 3.3 Jumper Configuration

All of the jumpers have been preset at the factory to ensure proper system operation with the majority of AT bus systems. This information is provided to help the OEM or system integrator to configure the system properly if other option boards present conflicts.

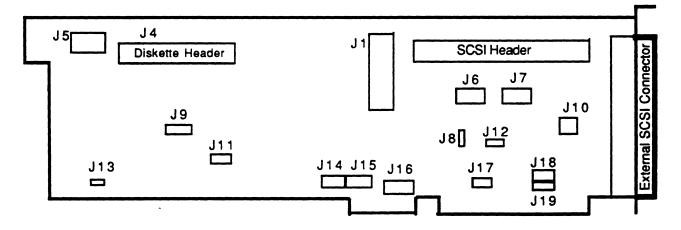

The following diagram shows the approximate location of the various customer configurable items on the AHA-1540A/1542A. Listed after the diagram are the functions, defaults, and set-up options for each jumper.

Jumper locations:

AHA-1540A/1542A

## 3.3.1 Jumper Block J1

Jumper block J1 is shown below:

|       | J1 |   |                                             |

|-------|----|---|---------------------------------------------|

| Pin 1 | 0  | 0 | Synchronous Transfer                        |

|       | 0  | 0 | Diagnostics                                 |

|       | 0  | 0 | SCSI Parity                                 |

|       | 0  | 0 | SCSI Address                                |

|       | 0  | 0 | SCSI Address                                |

|       | 0  | 0 | SCSI Address                                |

|       | 0  | 0 | DMA Channel J14 and J15 must also be set.   |

|       | 0  | 0 | DMA Channel — J14 and J15 must also be set. |

|       | 0  | 0 | Interrupt Channel-                          |

|       | 0  | 0 | Interrupt Channel J16 must also be set.     |

|       | 0  | 0 | Interrupt Channel                           |

|       | 0  | 0 | DMA Transfer Speed                          |

|       | 0  | 0 | DMA Transfer Speed                          |

|       |    |   |                                             |

Jumper block J1 is the large vertically oriented block of jumpers located near the center of the host adapter. Pin pair 1 is the topmost pair of pins.

## 3.3.1.1 SCSI Synchronous Negotiation

Pin-pair 1 of jumper block J1 is the synchronous negotiation enable jumper. The AHA-1540A/1542A will initiate SCSI synchronous negotiation during initialization, or after a SCSI reset if this jumper is installed. If the jumper is not installed, the AHA-1540A/1542A will still support synchronous SCSI transfers, but a different SCSI device must initiate the negotiation. **Default is jumper removed, synchronous negotiation initiation disabled.** If any attached SCSI devices support synchronous transfer, the initiation of negotiation should be enabled by both the AHA-154XA and the attached devices to fully implement the SCSI synchronous negotiation protocol.

## 3.3.1.2 Diagnostic Jumper

Pin-pair 2 of jumper block J1 is a factory diagnostic jumper. This jumper is reserved for Adaptec use and must not have a jumper shunt installed. If this jumper is installed, the firmware will loop through the power on diagnostics, preventing normal operation. Default is jumper removed.

## 3.3.1.3 SCSI Parity

Pin-pair 3 of jumper block J1 is the parity enable/disable jumper. The SCSI parity checking is disabled if this jumper is installed. The default is parity checking enabled.

# Installation

## 3.3.2 SCSI Address

Pin-pairs 4, 5, and 6 of jumper block J1 define the SCSI address. The SCSI address is selected according to the following table. The default address is 7.

|            | J 1    |        |        |   |          |         |         |

|------------|--------|--------|--------|---|----------|---------|---------|

| Pin 1      | 0<br>0 | 0<br>0 |        |   |          |         |         |

|            | 0      | 0      |        |   | Pin-pair | SCSI    |         |

| Pin-pair 4 | 0      | 0      | SCSI 0 |   | 456      | Address |         |

| Pin-pair 5 | 0      | 0      | SCSI 1 |   | 000      | 7       | Default |

| Pin-pair 6 | 0      | 0      | SCSI 2 |   | хоо      | 6       |         |

|            | 0      | 0      |        |   | oxo      | 5       |         |

|            | 0      | 0      |        |   | ххо      | 4       |         |

|            |        |        |        |   | OOX      | 3       |         |

|            | 0      | 0      |        |   | хох      | 2       |         |

|            | 0      | 0      |        |   | O X X.   | 1       |         |

|            | 0      | 0      |        |   | XXX      | 0       |         |

|            | 0      | 0      |        | 1 |          |         | •       |

|            | 0      | 0      |        |   |          |         |         |

X = Jumper Installed

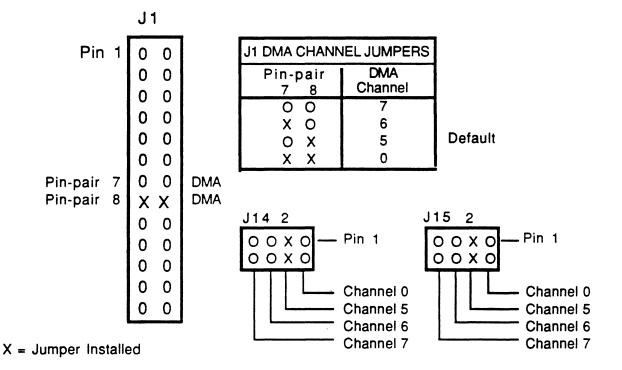

## 3.3.3 DMA Channel

There are three jumper blocks involved in selecting the DMA channel. These are J1, J14, and J15. The DMA channel selection jumpers consist of pin pairs 7 and 8 located in the large block of jumper pins J1. The DMA channel reported to the AT during the Return Configuration command is set by these jumpers according to the following table. **Default is DMA channel 5**.

Jumper set J14 selects the DMA REQ signal to be used by the AHA-1540A/1542A according to the following table. This jumper set is located near the bottom center of the host adapter. Pin pair 1 is the right most pair of pins.

#### The default is DMA Request 5.

Jumper set J15 selects the DMA ACK signal to be used by the AHA-1540A/1542A according to the following table. This jumper set is located near the bottom center of the host adapter. Pin pair 1 is the right most set of pins. The default is DMA Acknowledge 5.

# Section Three

There are four DMA channels that may be chosen for use by the AHA-1540A/AHA-1542A, channels 0, 5, 6, and 7. The DMA channel is set up by using the three jumper blocks and pin-pairs previously described. The jumper settings for each channel are shown below:

adaptec

## 3.3.4 AT Interrupt Channel

There are two jumper blocks involved in selecting the AT interrupt channel. These are J1 and J16. The AT interrupt channel jumpers consist of pin pairs 9, 10, and 11 in the large block of jumper pin pairs J1. The interrupt channel reported to the AT during the Return Configuration Command is set by these jumpers according to the following table. The default is interrupt channel 11.

Jumper set J16 selects the AT interrupt channel to be used by the AHA-1540A/1542A. This jumper set is located near the bottom center of the host adapter. Pin pair 1 is the right most pair of pins. The interrupt channel used is set according to the following table. The default interrupt channel is 11.

|                           | J1         |                        |                        |                      |  |

|---------------------------|------------|------------------------|------------------------|----------------------|--|

| Pin 1                     | 0 0        |                        | J1 INTERRUPT           | CHANNELS             |  |

|                           | 0 0        |                        | Pin-pair<br>9 10 11    | Interrupt<br>Channel |  |

|                           | 0 0<br>0 0 |                        | 000                    | 9                    |  |

|                           | 0 0        |                        |                        | 10<br>11             |  |

|                           | 0 0<br>0 0 |                        |                        | 12<br>14             |  |

|                           | 0 0        |                        | xox                    | 15                   |  |

| Pin-pair 9<br>Pin-pair 10 | 0 0<br>X X | Interrupt<br>Interrupt | J16 3                  |                      |  |

| Pin-pair 11               |            | Interrupt              | 0 0 0 X 0<br>0 0 0 X 0 |                      |  |

|                           | 0 0        |                        |                        |                      |  |

|                           | 0 0        |                        |                        | IRQ 10               |  |

| X = Jumper I              | nstalled   |                        | IRQ 12                 |                      |  |

AHA-1540A/1542A

**IRQ** 15

# 3.3.5 DMA Transfer Speed Default

Pin-pairs 12 and 13 of jumper block J1 set the default DMA transfer speed. Installing jumper shunts as shown below will set any of 4 default DMA transfer speeds. (See Appendix A for system timing requirements.) The default speed is selected after power on or after a hard reset occurs. This speed may also be tuned to allow for the fastest possible transfer (minimum bus on time) for any particular system by using the Host Adapter command Set Transfer Speed. The Host Adapter Command overrides the jumper settings. This command is detailed in section 5. The default is no jumper installed.

|                      |          | J1          |             |                                          |            |            |            |              |         |

|----------------------|----------|-------------|-------------|------------------------------------------|------------|------------|------------|--------------|---------|

| Pir                  | ו 1      | 0<br>0      | 0<br>0      |                                          |            |            |            |              |         |

|                      |          | 0           | 0           |                                          | Pin-<br>12 | pair<br>13 |            | VA<br>beed   |         |

|                      |          | 0<br>0<br>0 | 0<br>0<br>0 |                                          | O<br>X     | 00         | 5.0<br>5.7 | MB/s<br>MB/s | Default |

|                      |          | 0           | 0           |                                          | O<br>X     | X<br>X     | 6.7<br>8.0 | MB/s<br>MB/s |         |

|                      |          | 0           | 0<br>0      |                                          |            |            |            |              |         |

| Pin-pair<br>Pin-pair | 12<br>13 | 0<br>0      | 0<br>0      | DMA Transfer Speed<br>DMA Transfer Speed |            |            |            |              |         |

X = Jumper Installed

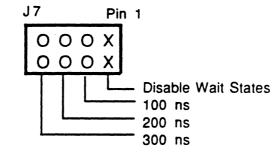

#### 3.3.6 AT BIOS Wait State

Jumper block J7 allows IOCHRDY on the AT bus to be driven not active during BIOS reads. The time may be set to 100ns, 200ns, 300ns, or the function may be disabled. The default is Wait State Disabled.

X = Jumper installed

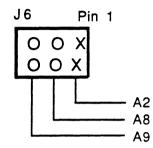

#### 3.3.7 AT Port Address

The starting address of the block of four I/O ports required by the AHA-1540A/1542A is selected by the jumpers in jumper block J6. Pin pair 1 is the right most pair of pins. The default address is 0330H. That port address is required by the BIOS. Other valid port addresses are 334H, 330H, 234H, 230H, 134H, and 130. These port addresses may be used by device drivers and operating systems that support multiple host adapters. The default address is 330H.

|    | AT Port Address |    |         |         |  |  |  |

|----|-----------------|----|---------|---------|--|--|--|

| A9 | A8              | A2 | Address |         |  |  |  |

| 0  | 0               | 0  | 334H    |         |  |  |  |

| 0  | 0               | X  | 330H    | Default |  |  |  |

| 0  | Х               | 0  | 234H    |         |  |  |  |

| 0  | Х               | Х  | 230H    |         |  |  |  |

| Х  | 0               | 0  | 134H    |         |  |  |  |

| Х  | 0               | Х  | 130H    |         |  |  |  |

Default is 330H X Jumper Installed

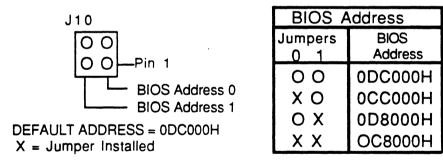

#### 3.3.8 AT BIOS Address

The starting address of the block of address space reserved for the Adaptec BIOS is selected by the jumper pins located in J10. The default address is ODCOOOH. This address must not conflict with any other BIOS or decoded address space in the system.

## 3.3.9 Front Panel LED Connector

J5 is the front panel LED header. Pins 1 and 4 are connected to the same 220 ohm pull up resistor and pins 2 and 3 are pulled low by the same LED driver whenever the on board LED is on. This allows the Front Panel LED cable to be plugged in with either orientation. The driver is specified to pull 24 milliamps through the LED. J5 is located near the top left of the host adapter.

# Section Three

# 3.3.10 LA Enable Jumper (AHA-W1542A Only)

Note: This jumper exists only on the early production units. These are easily identified by a label on the board that has a model number of AHA-W1542A. Standard production AHA-1540A and AHA-1542A boards do not have this jumper.

When J8 is installed, address drivers LA17 - LA19 are enabled. When not installed these address lines are not driven. Some computers, especially 80386 based machines, short address lines LA17 and SA17, LA18 and SA18, and LA19 and SA19 together. If your computer system shorts these lines then remove jumper J8. Default is jumper installed.

CAUTION: INCORRECT INSTALLATION OF THIS JUMPER MAY NOT RESULT IN IMMEDIATE SYSTEM PROBLEMS. IF IT IS NECESSARY TO CHANGE THE STATE OF THIS JUMPER AFTER THE SYSTEM HAS BEEN CONFIGURED, THE SCSI HARD DISK MUST ALSO BE RE-FORMATTED. CONTACT THE COMPUTER SYSTEM MANUFACTURER IF THERE IS ANY DOUBT ON HOW THE SYSTEM IMPLEMENTS THESE ADDRESS LINES.

#### 3.3.11 Auxiliary Jumpers

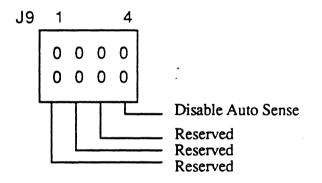

Installation of a jumper shunt on pin pair 4 of jumper block J9 will disable the automatic request sense function on the AHA-1540A/1542A. If the automatic Request Sense function is enabled, it may additionally be disabled on a command by command basis using the Request Sense Allocation Length Field of the CCB (see Section 5.3). All other pins-pairs on jumper block J9 are reserved for future use.

# 3.3.12 BIOS Enable/Disable

Only one host adapter BIOS should be enabled in any host system. That BIOS allows DOS to access up to two SCSI drives on the host adapter having a port address of 330H. Any other host adapters installed in the system must have their BIOS disabled. In addition, certain operating systems may require that the BIOS be disabled. The enabling of the BIOS is controlled by jumper J11, near the bottom left of the host adapter. When the jumper is installed on J11 the BIOS is enabled. When the jumper is removed, the BIOS is disabled and will not respond to host reads. The default is jumper installed.

#### 3.3.13 SCSI Terminators

RN3, RN4, and RN5 are the SCSI terminators. If the AHA-1540A/1542A is not the first or the last SCSI device in a string of SCSI devices, or if in-line terminators are used, then all of these resistor networks must be removed. More information is provided in section 3.2.2 about the proper use of the SCSI terminators. The default is terminators installed.

#### 3.3.14 SCSI Terminator Power

Fuse F1 controls the terminator power. If another SCSI device is supplying terminator power, then F1 may optionally be removed. No more than 5 SCSI devices should be configured to supply terminator power to a single SCSI bus. The default is F1 installed with the AHA-1540A/1542A supplying terminator power. The terminator power is protected with a 1.5 amp fuse to prevent short circuits from burning SCSI cables. The terminator power is additionally protected from terminator power back-flow with a low voltage-drop diode so that the SCSI bus will continue to operate even if one or more SCSI host adapters is powered down.

#### **3.4 FLEXIBLE DISKETTE CONTROLLER CONFIGURATION JUMPERS (AHA-1542A ONLY)**

#### 3.4.1 Flexible Diskette Controller Secondary Address

Jumper J12, located near the center right of the host adapter, controls the selection of the flexible diskette controller secondary address. When J12 is installed, the flexible diskette controller will respond to I/O addresses 370-377. When not installed, the flexible diskette controller will respond to I/O addresses 3F0-3F7. The default is no jumper installed.

#### 3.4.2 Flexible Diskette Controller Enable

Jumper J13, located near the bottom left of the host adapter, enables or disables the flexible diskette controller. When this jumper is installed, the flexible diskette controller will respond to host reads and writes. When not installed, the flexible diskette controller will not respond to any signal. The default is jumper installed.

#### 3.4.3 Flexible Diskette Controller Interrupt Channel

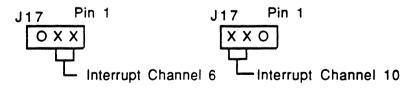

Jumper block J17, located near the bottom right of the host adapter, sets the interrupt channel for the flexible diskette controller. The default is interrupt channel 6.

X = Jumper Installed

# Section Three

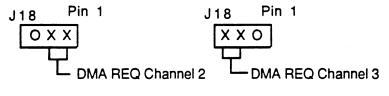

#### 3.4.4 Flexible Diskette Controller DMA Request Channel

Jumper J18, located near the bottom right of the host adapter, selects the DMA Request channel for the flexible diskette controller. Jumper J19, the DMA Acknowledge jumper, must be set to the same position. Default is DMA channel 2.

X = Jumper Installed

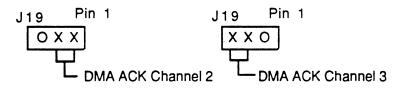

#### 3.4.5 Flexible Diskette Controller DMA Acknowledge Channel

Jumper J19, located near the bottom right of the host adapter, selects the DMA acknowledge channel for the flexible diskette controller. Jumper J18, the DMA Request jumper, must be set to the same position. Default is DMA channel 2.

X = Jumper Installed

# Hardware Functional Description

#### 4.0 HARDWARE FUNCTIONAL DESCRIPTION

#### 4.1 HARDWARE OVERVIEW

This section provides a description of the AHA-1540A/1542A hardware functional interface to the PC/AT host software.

The hardware consists of a custom SCSI protocol chip, the AIC-6250, a FIFO buffer, a set of I/O ports, and a controlling microprocessor.

The DMA control logic on the host adapter controls the AT bus arbitration and data transfer hand shaking. During DMA data transfers, the AHA-1540A/1542A becomes a bus master. The DMA logic supports both odd and even starting addresses. For odd starting addresses, the first transfer will be an 8-bit transfer. Thereafter, 16 bit transfers will be used to complete the data transfer. Odd-byte transfers, and the the last transfer of an even number of bytes to an odd address are treated in a similar manner.

The SCSI port is controlled by the AIC-6250, an Adaptec SCSI protocol device which supports arbitration, selection, and reselection with a minimum of processor intervention. This VSLI device also supports target mode and synchronous SCSI transfers.

#### **4.2 I/O PORT INTERFACE**

The I/O port interface consists of three address locations. These three port addresses are decoded in the AT I/O address space. They form the primary communications channel between the host and the host adapter. The I/O ports are 8 bits wide. The base port is for control and status, the second port for command and data transfer, and the third port for interrupt flags.

## I/O PORT INTERFACE BIT DEFINITION

#### **PORT ADDRESS = BASE + 0**

#### WRITE: Control Register

| Bit 7 | Hard Reset (HRST)      | Bit 7 | Self Test in Progress (STST)           |

|-------|------------------------|-------|----------------------------------------|

| Bit 6 | Soft Reset (SRST)      | Bit 6 | Internal Diagnostic Failure (DIAGF)    |

| Bit 5 | Interrupt Reset (IRST) | Bit 5 | Mailbox Initialization Required (INIT) |

| Bit 4 | SCSI Bus Reset (SCRST) | Bit 4 | SCSI Host Adapter Idle (IDLE)          |

| Bit 3 | Reserved (0)           | Bit 3 | Command/Data Out Port Full (CDF)       |

| Bit 2 | Reserved (0)           | Bit 2 | Data In Port Full (DF)                 |

| Bit 1 | Reserved (0)           | Bit 1 | Reserved (Undefined)                   |

| Bit 0 | Reserved (0)           | Bit 0 | Invalid H A Command (INVDCMD)          |

#### adaptec

**READ:** Status Register

# **PORT ADDRESS = BASE + 1**

| WRITE: Command / Data Out RE. | AD: Data | In |

|-------------------------------|----------|----|

|-------------------------------|----------|----|

| Bit 7 | Command/Data Out Bit 7 | Bit 7 | Data | In Bit 7 |

|-------|------------------------|-------|------|----------|

| Bit 6 | " Bit 6                | Bit 6 | **   | Bit 6    |

| Bit 5 | " Bit 5                | Bit 5 | +1   | Bit 5    |

| Bit 4 | " Bit 4                | Bit 4 | "    | Bit 4    |

| Bit 3 | " Bit 3                | Bit 3 | **   | Bit 3    |

| Bit 2 | " Bit 2                | Bit 2 | 11   | Bit 2    |

| Bit 1 | " Bit 1                | Bit 1 | 11   | Bit 1    |

| Bit 0 | " Bit 0                | Bit 0 | **   | Bit 0    |

#### **PORT ADDRESS = BASE + 2**

| WRITE: | Reserved, do not write | READ: | Interrupt Flags            |

|--------|------------------------|-------|----------------------------|

| Bit 7  |                        | Bit 7 | Any Interrupt              |

| Bit 6  |                        | Bit 6 | Reserved                   |

| Bit 5  |                        | Bit 5 | Reserved                   |

| Bit 4  |                        | Bit 4 | Reserved                   |

| Bit 3  |                        | Bit 3 | SCSI Reset Detected (SCRD) |

| Bit 2  |                        | Bit 2 | HA Command Complete (HACC) |

| Bit 1  |                        | Bit 1 | MBO Empty (MBOÅ)           |

| Bit 0  |                        | Bit 0 | MBI Full (MBIF)            |

#### 4.2.1 Control and Status Port

Writing a one to the bits of the Control Port initiates certain special host adapter operations. There is no requirement to return the bits to the zero state, since they are reset automatically after the requested operation is initiated. Read operations to the Status port address return host adapter status information.

Base+0 Port, Write: Host Adapter Control Port.

Bit 7 Hard Reset (HRST): The setting of the Hard Reset bit to one forces the host adapter into a state identical to a normal power on state. Diagnostic functions are executed and all status for ongoing SCSI operations is lost. A Reset Condition is generated on the SCSI bus. While the reset is being processed, the Self Testing in Progress bit (Host Adapter Status Port bit 7) is set. When the reset is complete, that bit is reset and the Mailbox Initialization Required bit (Host Adapter Status Port bit 5) and the SCSI Host Adapter Idle bit (Host Adapter Status Port bit 4) are set, indicating that the AHA-154XA mailbox structure must be re-initialized and that no other operations are active on the host adapter. See section 4.3, describing the overall reset structure.

- Bit 6 Soft Reset (SRST): The Soft Reset bit clears all ongoing SCSI and host adapter commands. All Command Control Blocks are abandoned and all queued commands are abandoned. Mailbox In and Mailbox Out entries must be cleared by the host. No diagnostic functions are executed. No Reset Condition is generated on the SCSI bus. The Mailbox Initialization Required bit (Host Adapter Status Port bit 5) and the SCSI Host Adapter Idle bit (Host Adapter Status Port bit 4) are set when the reset processing is completed. This indicates that the AHA-154XA Mailbox structure must be re-initialized and that no other operations are active on the Host Adapter. See section 4.3, describing the overall reset structure.

- Bit 5 Interrupt Reset (IRST): The setting of this bit clears the interrupt port of all bits that have been set and resets the interrupt line. The host adapter manages the interrupt presentation to minimize the possibility of incorrectly resetting an interrupt. MBOE and MBIF interrupts are presented immediately unless an SCRD or HACC interrupt has not yet been cleared. An SCRD or HACC will only be presented after any interrupt bit has been cleared and DF is zero, indicating an operation is fully completed. The prompt resetting of MBOE and MBIF interrupts minimizes the chance of a reset of one also resetting the other. Host programs should, however, be aware that there is a small chance of falsely resetting a new MBIF reset while clearing an MBOE interrupt. This can be resolved by periodically scanning the MBI entries when activity is expected on the host adapter or by not enabling the MBOE interrupt.

- Bit 4 SCSI Bus Reset (SCRST): The setting of this bit causes a SCSI Bus Reset to be generated on the SCSI bus. The SCSI Bus Reset is triggered at the time the SCRST bit is set to one and raises the RST line on the SCSI Bus for the architected 25 microsecond period. The reset is managed as a SCSI Soft Reset and will allow partially completed operations to continue after the reset occurs. See section 4.3, describing the overall reset structure.

- Bits 0-3 Reserved: Reserved bits must be set to zero to avoid compatibility problems with future extensions of the Control Register.

#### Base+0 Port, Read: Host Adapter Status Port

- Bit 7 Self Testing in progress (STST): This bit, when one, indicates that the host adapter is performing self-initialization and internal diagnostics. The bit is asserted after a power-on or hard reset (Control Port Bit 7 HRST = 1). When diagnostic operation is complete, the STST bit is set to zero and bit 5 or bit 6 is set to indicate the successful or unsuccessful completion of the diagnostics. If bit 7 remains on, it indicates that the initialization or diagnostic could not be completed. The error condition can be determined as described in section 10. In most cases, bit 6 (DIAGF) will be set to indicate that an internal diagnostic failure occurred.