# EtherLink II Adapter Technical Reference Manual

A Member of the EtherLink Product Family

Copyright © 3Com Corporation, 1988. All rights reserved. 3165 Kifer Road Santa Clara, California 95052-8145 Printed in the U.S.A.

Manual Part No. 4185-01 Published January, 1989

# **Copyright Statement**

No part of this manual may be reproduced in any form or by any means or used to make any derivative (such as translation, transformation or adaption) without permission from 3Com Corporation, by the United States Copyright Act of 1976, as amended.

# Disclaimer

3Com makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. 3Com shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Contents

#### **Chapter 1: Introduction**

#### **Chapter 2: Applicable Documents**

#### **Chapter 3: General Description**

Gate Array 3-1 Decoding 3-1 Packet Transfers 3-1 Programmable Options 3-2 Arbitration 3-3 FIFO Logic 3-3 LAN Chips 3-3 LAN Controller 3-3 Transceiver 3-4 RAM 3-4 Segments 3-4 EPROM 3-4 Ethernet Address 3-4

#### **Chapter 4: Configuration Data**

I/O Base Address 4-1 LAN Controller 4-1 Ethernet Address PROM Bytes 31-16 4-1 Ethernet Address PROM Bytes 15-0 4-1 Gate Array 4-1 Memory Address Mapping 4-2 EPROM 4-2 RAM 4-2 Interrupt Channels 4-2 DMA Channels 4-2 DIX/BNC 4-2

#### Chapter 5: Data Transfer

Control Blocks 5-1 DMA Controller 5-1 Page Start Register 5-1 Page Stop Register 5-1 Drq Timer Register 5-1 GA (Gate Array) Configuration Register 5-2 Control Register 5-2 Status Register 5-3 DMA Address Registers 5-3 Register File Access 5-4 Programmed I/O 5-4 DMA Transfer 5-4 Single Byte Mode 5-4 Demand Mode 5-4 Drq Timer 5-5 Memory Mapped 5-5 Word Instructions 5-5 FIFO Configurations - (Selected in GA Control Register) 5-6 Parallel Configuration 5-6 Serial Configuration 5-6

#### Chapter 6: Initialization

Power Up Reset 6-1 Software Reset 6-1 Software Reset Programming Sequence 6-2

#### Chapter 7: I/O Address Map

Ethernet Address PROM Bytes 31-16 7-1 Ethernet Address PROM Bytes 15-0 7-2 LAN Controller 7-2 Gate Array 7-3

#### **Chapter 8: Memory Address Map**

EPROM 8-1 RAM 8-1 Vector Pointer 8-1

#### **Chapter 9: Jumper Position Equates**

#### Chapter 10: Gate Array Descriptions

Gate Array Register Definitions 10-1 Page Start Register 10-1 Page Stop Register 10-1 Drq Timer Register 10-2 Base Configuration Register 10-2 EPROM Configuration Register 10-3 GA Configuration Register 10-4 Control Register 10-5 Memory Bank Select 10-5 Status Register 10-7 Interrupt/DMA Configuration Register 10-8 DMA Address Register 10-8 DMA Address Register LSB 10-9 Vector Pointer Register 2 10-10 Vector Pointer Register 1 10-10 Vector Pointer Register 0 10-10 Register File Access MSB 10-11 Register File Access LSB 10-11 I/O Signal Names 10-12 I/O Signal DC Parameters 10-13

#### Chapter 11: Power Requirements

+ 5 Volts Current Requirements 11-1 Quiescent Mode 11-1 Receive Mode 11-1 Transmit Mode 11-1 +12 Volts Current Requirements 11-1 Quiescent Mode 1 11-2 Quiescent Mode 2 11-2 Receive Mode 11-2 Transmit Mode 11-2 Power Dissipation 11-2

#### **Chapter 12: Operational Specifications**

DC Voltage Margin 12-1 +5 Voltage Margin 12-1 +12 Voltage Margin 12-1

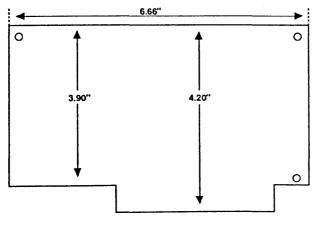

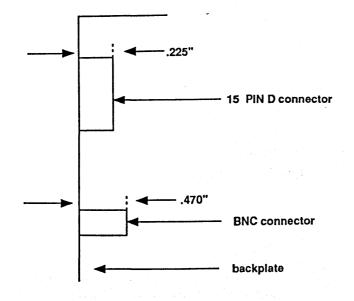

#### Chapter 13: Physical / Mechanical Specifications

Mechanical Specification 13-1 Backplate Mechanical Dimensions 13-1 Environment Characteristics 13-2 Shock & Vibration 13-2 Drop Tests 13-2 Humidity 13-2 Salt Spray 13-2

#### **Chapter 14: Agency Approvals**

#### Appendix A: Recommended Guidelines for Operation

Transmitter Deadlock A-2 Receiver Anomalies A-2 Receive Status Byte Check for Invalid Data in Packet A-2 Bytes Shifted Within Packet Header A-2 Bytes Shifted Within Packet Data A-3 Operational Constraints A-3 Capability to Use NIC Remote DMA Facility Not Implemented A-3 Required NIC Programming Sequences A-4 Ninth Byte Corruption of Transmitted Packets A-5

#### **Appendix B: Programming Sequences**

Initialization Programming Sequence B-1 EtherLink II Gate Array Accesses (I/O Base Address + 400h) B-1 EtherLink II LAN Controller (Jumpered I/O Base Address) B-2 Transmit Sequence B-3 Receive Sequence B-3

EtherLink II: Introduction

1-1

# **Chapter 1: Introduction**

This document provides information about the programming requirements of the gate array on the EtherLink II network adapter. The EtherLink II adapter is a high-performance, multi-packet buffering, low-cost Ethernet adapter, designed to operate in IBM PC, PC AT, and compatible personal computers. The gate array is the central source for the operation of the adapter by connecting directly to the PC bus interface and the adapter's buses. The gate array, composed of 16 registers, is subdivided into control registers (used for data transfers), configuration registers (used for establishing address assignments), and status registers (used for providing information to the software).

The software, by programming the gate array registers, determines the best suited operating parameters for the adapter operating environment. The operating parameters determine the connectivity for data transfers (memory mapped, DMA transfers) and transceiver connections (external, on-board). The data transfer parameters are programmable to support a variety of PC data transfer methods (DMA, programmed I/O, either byte or word, and memory-to-memory transfers). The DMA data transfer supports single byte and demand mode with the ability to personalize the number of bytes transferred to the personal computer.

The gate array also provides software programmable options that play a key role in reducing the time required to configure the EtherLink II adapter. The software programmable options are the DMA channels, interrupt channel, and transceiver type.

EtherLink II: Applicable Documents

# **Chapter 2: Applicable Documents**

#### EtherLink II Installation Guide

The *EtherLink II Installation Guide* provides detailed information about the operation of the EtherLink II adapter. Topics that are explained are installation, diagnostics, software installation, cabling, adapter configurations, and support.

IEEE 802.3 Specification

#### **Technical Reference**

Advanced Peripherals IEEE 802.3 Local Area Network Guide, published by National Semiconductor Corp., National part number 550083-001).

Technical Reference Personal Computer, published by IBM Corp., IBM part number 6322507.

Technical Reference Personal Computer AT, published by IBM Corp., IBM part number 6230070.

Technical Reference Personal System/2, Model 30, published by IBM Corp.

**General Description**

# **Chapter 3: General Description**

This section provides an overview of the component blocks that comprise the EtherLink II adapter. The major functions of each block are described.

# Gate Array

#### Decodina

All I/O addresses used by component blocks (LAN controller registers, Ethernet address PROM, gate array registers, interrupt sharing) on the adapter are decoded by the gate array. The I/O decoding logic uses the full 16-bit I/O address bus. This guarantees that the EtherLink II does not conflict with other adapters that do a partial (< 16 bits) decode.

Memory address decoding for the EPROM and for the static RAM during memory-mapped data transfers are decoded by a circuit in the gate array. The memory decoding logic uses the full 20-bit memory address bus. This full 20-bit decode provides a unique address for adapter memory components.

#### Packet Transfers

Transmit packets are "downloaded" (data transferred from the PC to the adapter) to the boardresident RAM by using either the DMA controller in the gate array or by programming the adapter for memory map mode. The gate array DMA controller supports handshaking with a motherboardresident DMA controller (8237), using either single-byte or demand-mode transfers. The gate array DMA controller also interfaces to program transfer instructions (byte or word). Instructions supported are outb, outw, rep outsb, rep outsw.

Receive packets are "uploaded" (data transferred to the PC from the adapter) from the board-resident RAM by using either the DMA controller in the gate array or by programming the adapter for memory-map mode. The gate array DMA controller supports handshaking with a motherboardresident DMA controller (8237), using either single-byte or demand-mode transfers. The DMA controller also interfaces to program transfer instructions (byte or word). Instructions supported are inb, inw, rep insb, rep insw.

# **Programmable Options**

#### Interrupts

There are four (4) programmable interrupt channel options (2, 3, 4, 5). Following a power up condition, the output drivers (irq2, irq3, irq4, irq5) remain in the "off state" until programmed to the "on state." The output driver "on state" is defined as sinking current (driving the line to a logical zero < 0.4V) during interrupt request activity. The output driver does not have an "on state" that sources current. The source current for the line is provided by a discrete pull-up resistor.

The output drivers are returned to the "off state" during a software reset. The "off state" is defined as not sinking current (Ima). The line is driven to a logical one by the pull-up resistor. This DOES cause a low to high transition on the assigned interrupt line to the interrupt controller (8259) located on the motherboard. It is RECOMMENDED that you disable the interrupt channel assigned to the adapter in the interrupt controller during software reset.

The programmable interrupt lines support either dedicated interrupt operation or interrupt sharing. Dedicated interrupts are assigned to only one adapter at a time. Interrupt sharing allows multiple adapters to "drive" the same interrupt line.

#### **DMA Channels**

There are three (3) programmable direct memory access (DMA) channel options (1, 2, 3). Following a power up condition, the output drivers (drq1, drq2, drq3) remain in the "off state" until programmed to the "on state." The output driver "on state" is defined as either sinking current (driving the line to a logical zero < 0.4V) during non-DMA activity or sourcing current (driving the line to a logical one > 2.4V) during DMA activity. There are no conditions during the "on state" that cause the output driver not to drive the line.

The output drivers are returned to the "off state" during a software reset. The "off state" is defined as not sinking or sourcing current. The line is "floating" (unless the motherboard provides line termination resistors). This "floating" condition may cause a DMA request to the DMA controller (8237). It is advisable to disable the DMA controller during software reset.

#### DIX/BNC

The selection between using the onboard transceiver (BNC) or using an external transceiver (DIX, 15-pin connector) is programmable. The power-up condition causes the onboard transceiver to be selected (default). Bit 1 in the Control Register determines the transceiver mode.

The adapter is capable of delivering +12V @ 0.5A to either the BNC OR DIX port. It is recommended that the following conditions never exist:

- Attaching an external transceiver with the onboard transceiver selected (this may overload the +12V fuse.)

- Selecting the onboard transceiver while having an external transceiver attached (another overload condition for the fuse).

Requests for access to the board resident RAM (local packet buffer) are arbitrated by logic in the gate array. The LAN controller requests the bus to store packets it receives from the network in the receive packet segment of the local packet buffer, and retrieve packets from the transmit segment of the local packet buffer for transmission to the network.

Requests are prioritized with the LAN controller given the highest priority. LAN controller requests cause the current cycle to the local packet buffer to complete, then control is given to the LAN controller.

### FIFO Logic

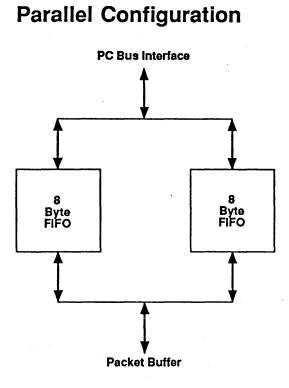

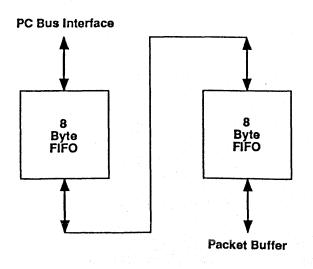

To compensate for the bus latency due to the LAN controller operation, a first in, first out (FIFO) circuit is implemented in the gate array. This FIFO allows the simultaneous transfer of data to the host processor in addition to data transfers to the local packet buffer from the LAN controller. The FIFO can be configured into a two 8-byte parallel operation or a single 16-byte serial configuration.

# LAN Chips

#### LAN Controller

#### **Data Conversion**

The LAN controller reads byte parallel data from the local packet buffer during packet transmission, and converts that data to bit serial information for the encoder. For receive packets, the LAN controller receives bit serial data from the decoder and generates byte parallel data to the local packet buffer.

#### **Packets**

Transmit packets that are assembled in the local packet buffer (transmit segment) are **retrieved** by the LAN controller and passed to the encoder block. The data is passed to the encoder in the following sequence: 8 bytes of preamble (inserted by the LAN controller), destination address (6 bytes), source address (6 bytes), packet data (up to 1500 bytes) read from the local packet buffer, and 4 CRC bytes (generated by the LAN controller).

On receive packets, the LAN controller strips the preamble from the packet and checks the CRC bytes. The data written into the local packet buffer by the LAN controller is header information (4 bytes), packet data field (1500 max), and CRC bytes (4).

#### **CRC Generate/Check**

Cyclic redundancy check (CRC) is used to determine the validity of the transmitted data. The CRC bytes are appended to the packet by the transmitting LAN controller and checked by the receiving LAN controller. These CRC bytes are used in conjunction with the data in the packet to determine an error.

It is not correct to assume that a CRC error indicates a transmitter problem. A method to determine whether the transmitter has sent an error packet or the receiver CRC checker is defective is to accept error packets, then read the packet from the local packet buffer and perform a software CRC check, and then compare the results against the CRC bytes in the packet buffer.

#### Encoder/Decoder

The link between the transceiver (the component block that is attached to the coax) and the LAN controller (the component block that interfaces to the gate array) is the encoder/decoder component block. The encoder/decoder supplies all the timing clocks used for passing data between the LAN controller and the transceiver.

The packet information on the coax is encoded using the Manchester encoding scheme. Encoded packets, combining data and clocks, are derived from this component block, and received packets are separated into data and clock information by the decoder. Data passed to/from the transceiver is in the form of differential signal levels, with data passed to/from the LAN controller in the form of the signal levels.

#### Transceiver

An onboard transceiver capable of driving "thin Ethernet" coax is provided as a standard configuration on the EtherLink II adapter. Functions of the transceiver include transmitting packets onto the coax, receiving packets from the coax and detecting collisions when multiple transceivers are transmitting simultaneously.

# RAM

The adapter uses static RAM for the board-resident packet buffer. The standard configuration is a single 8K x 8 device with an option to increase to a single 32K x 8 device. Software has direct access to the RAM through the host's memory address space (when configured in memory mapped mode). Indirect software access to the RAM data is through the FIFO logic. There are four address options for locating the RAM in host memory addressable space. The selected address is shared between the RAM and the EPROM.

NOTE: Selection of RAM vs. EPROM is controlled by bit 3 of the GA Configuration register.

#### Segments

The RAM is divided into transmit buffer space and receive buffer space. Using the standard RAM configuration of 8K, the transmit space is 1.5K (one maximum size packet) and the receive space is 6.5K.

# **EPROM**

The adapter provides a socket for an 8K x 8 EPROM. A jumper-selectable memory address defines the EPROM segment within the ROM address space in the personal computer. The memory address is shared with the RAM during memory-mapped data transfer mode.

NOTE: Selection of RAM vs. EPROM is controlled by bit 3 of the GA Configuration register.

# **Ethernet Address**

The Ethernet address block consists of a 32 x 8 PROM. The PROM contains the Ethernet address of the adapter in the first six locations. All 32 locations are accessible, with only the first six locations having a definition. Information in the PROM is accessed through the I/O address space.

EtherLink II: Configuration Data

4-1

# **Chapter 4: Configuration Data**

This section defines the configuration options that EtherLink II offers and the method used for setting these options.

# I/O Base Address

The adapter requires a contiguous block of 16 (xx0 -xxF) I/O locations where xx equals the I/O base address. The address block assigned to the adapter is jumper settable (1 of 2 jumpers on the adapter). There are eight possible options (350, 330, 310, 300, 2E0, 2A0, 280, 250), with only one jumpered at any given time.

# LAN Controller

The I/O registers in the LAN controller reside at the jumpered I/O base address. The registers share the I/O addresses with the Ethernet Address PROM. The information is "windowed" into the address space controlled by the Control Register bits 2, 3. Bits 2, 3 of Control Register are initialized to window the high-order bytes of the Ethernet Address PROM.

# Ethernet Address PROM Bytes 31-16

The high-order bytes of the PROM share the I/O address space with the LAN controller registers and the low-order bytes of the Ethernet Address PROM. The information is "windowed" into the address space controlled by bits 2, 3 of the control register. Bits 2, 3 of Control Register are initialized to window the high-order bytes of the Ethernet address PROM.

# Ethernet Address PROM Bytes 15-0

The low-order bytes of the PROM shares the I/O address space with the LAN Controller registers and the high-order bytes of the Ethernet Address PROM. The information is "windowed" into the address space controlled by bits 2, 3 of Control Register 2. Bits 2, 3 of Control Register 2 are initialized to window the high-order bytes of the Ethernet Address PROM.

# Gate Array

The registers in the gate array are located at the base I/O address + 400h (if the base address is jumpered to 300h, then the gate array is at 700h). This requires the personal computer in which the adapter is installed to have I/O addressing capability to 70Fh.

# **Memory Address Mapping**

The adapter memory can be mapped into the host's address space. When mapping is selected, the adapter requires a contiguous block of 8K (1FFFh) locations. The address assigned to the adapter is jumper settable. There are four possible options (DC000, D8000, CC000, C8000) with only one jumpered at any given time.

### **EPROM**

The adapter provides support for an 8Kbyte EPROM. The EPROM is located in the personal computer's ROM memory address space. The exact memory address of the EPROM is determined by the memory address jumper setting. The memory address selected for the EPROM is shared with the RAM, with selection controlled by the GA Configuration register.

#### RAM

The adapter provides support for up to 32Kbytes of static RAM. The RAM is located in **the** personal computer's ROM memory address space. The exact memory address of the RAM is determined by the memory address jumper setting. The memory address selected for the RAM is shared with the EPROM, with selection controlled by the GA Configuration register.

# Interrupt Channels

There are four interrupt channel options available (irq2-irq5). The interrupt options are software programmable via the Interrupt/DMA Configuration Register bits 4-7. The IDC is part of the gate array register set.

# **DMA Channels**

There are three DMA channel options available (drq1-drq3). The DMA channel options are software programmable via the Interrupt/DMA Configuration Register bits 0-3. The IDC is part of the gate array register set.

# DIX/BNC

The adapter supports either "thin Ethernet" via an onboard transceiver or "thick Ethernet" via an AUI/ external transceiver. The DIX/BNC option is software programmable via Control Register 2 bit 1.

EtherLink II: Data Transfer

This section defines the data transfer methods that the EtherLink II adapter supports.

# **Control Blocks**

#### **DMA Controller**

A high-performance DMA controller is built into the EtherLink II gate array. The DMA controller is used to deliver received packet data from the board resident packet buffer to the PC bus interface in an upload operation. It also controls the transfer of information from the PC bus interface to the local packet buffer in a download operation.

#### **Page Start Register**

The function of the Page STart Register (PSTR) is to define the starting address of the board resident packet buffer designated for received packets from the network.

The page start register (PSTR) in the gate array MUST be programmed with the exact value used for the LAN controller page start register (PSTART).

#### **Page Stop Register**

The purpose of the Page StoP Register (PSPR) is to define the end address within the board-resident packet buffer for receive packets from the network.

The Page StoP Register (PSPR) in the gate array MUST be programmed with the exact value used for the LAN controller page stop register (PSTOP).

#### **Drq Timer Register**

This register is used to control the number of bytes to be transferred between the system memory and the gate array DMA controller during demand mode DMA transfers. The gate array DMA controller will de-assert the DMA request signal on the PC bus interface when the count has been decremented to zero. The DMA request signal will be reasserted (provided terminal count has not been reached) AFTER the appropriate DMA acknowledge has been de-asserted by the system DMA controller. This allows other peripherals a chance to gain DMA access. It is recommended that the value loaded into the drq timer register does not cause the PC bus DMA transfer to exceed the refresh rate (15us).

# **GA (Gate Array) Configuration Register**

With the standard RAM configuration of 8K, bit 0 MUST be programmed to a logical one. With the 32K RAM configuration, bit 0 MUST be programmed to a logical zero. The rationale for different values based on the RAM configuration is due to different pin assignments between the 8K device and the 32K device. Pin 26 is chip select (positive true) on the 8K device and address line 13 on the 32K device.

### **Control Register**

Three bits in this register are related to the DMA transfer. These bits control the starting/stopping of the DMA controller, the direction of the DMA transfer, and the FIFO configuration.

#### Start DMA

Programming the start DMA bit to a logical one (positive true logic) causes the DMA controller to move data between the PC bus interface and the board resident packet buffer. The start DMA bit may be asserted coincident with the DMA direction bit. Prior to asserting the start DMA bit, the DMA address registers should be programmed with the address of the data in the packet buffer to be transferred by the DMA controller.

Programming the start DMA bit to zero (off) should only be done AFTER the transfer is complete. During a download operation (transfer ROM the system memory to the packet buffer) the high to low transition of start DMA bit causes the FIFO to be flushed of any residual data (residual data is less than 8 bytes). The DMA in progress bit in the status register is set "on" (a logical one) indicating a flush operation. It is ILLEGAL to change the value of the DMA address register during the time of a flush.

#### **DMA** Direction

Controls the direction of the DMA transfer. Setting the bit to a logical one moves data to the board resident packet buffer (a download operation). Setting the bit to a zero moves data from the board resident packet buffer to the system memory buffer (an upload operation). The DMA direction bit may be asserted simultaneously with the start DMA bit. It is ILLEGAL, however, to change the DMA direction bit after the start DMA bit is asserted.

Follow this programming sequence to initiate a change in the DMA transfer direction:

- 1. De-assert the start DMA bit.

- 2. Poll the DMA in-progress bit in the status register for a zero (loop until zero).

- 3. Assert start DMA bit with the new DMA direction value.

#### 16-Byte Select (Double Buffer Select)

This bit controls the configuration of the FIFOs. The default configuration is two 8-byte FIFOs operating in parallel. Programming the bit to a one concatenates the two 8-byte FIFOs to form a FIFO depth of 16 bytes.

#### **Status Register**

Status information on the current operation is provided to the software via bits 3, 4, 5, 6, 7 in the status register. Status information is available to the software as long as the start DMA bit in the control register is asserted (logical one). Clearing the status register is done by EITHER an I/O write (no specific data value is needed on the PC data bus since the gate array decodes only the address) or by programming the start DMA bit in the control register to zero (off).

#### **Data Port Ready**

The function of this bit is to indicate when the FIFO(s) is ready to receive data from the PC bus or deliver data to the PC bus. For a download transfer (PC to adapter), the FIFO(s) is immediately ready for receiving data (when the start DMA bit is asserted). For an upload operation (adapter to PC), the data port ready bit is asserted after 8 bytes are loaded into the FIFO (if 16 bytes equal zero) or after 16 bytes are loaded into FIFOs (if 16 byte select equals one).

#### **Data Port Underflow**

This status bit indicates that the gate array detected that an I/O read was issued to the register files address, but the DMA controller had not yet loaded the register file(s) with data from the board-resident packet buffer.

#### **Data Port Overflow**

This status bit indicates that the gate array detected that an I/O write was issued to the register files address with the register files full. This overflow condition can occur only when the PC bus I/O access exceeds the DMA controller access speed.

#### DMA Terminal Count (T/C)

Asserted by the gate array to indicate that a the PC bus signal (terminal count T/C) pulsed. The DMA controller will continue to transfer data until it receives a terminal count pulse OR the start DMA bit in Control register is de-asserted.

#### **DMA In Progress**

The DMA in progress status bit is set to a one by the DMA controller logic in the gate array. The primary purpose of this status bit is to allow the software to determine the completion of the flush operation during a download operation. During the flush operation it is ILLEGAL for the software to change the value of the DMA address registers.

#### **DMA Address Registers**

The DMA address registers consist of two (2) 8-bit registers (DMA address MSB, DMA address LSB) capable of addressing 64Kbytes of board-resident packet buffer. The DMA address registers are used only by the gate array DMA controller to store (download) or retrieve (upload) data to/from the packet buffer. The DMA address registers MUST be loaded by software prior to setting the start DMA bit in the Control register. The value in the DMA address registers CANNOT be altered after the start DMA bit is set. You MUST initiate a DMA "shutdown" to change the value in the DMA address registers to zero and verifying that the DMA in progress bit in the starts register is also zero.

Using the standard RAM configuration of 8Kbytes, the DMA address MSB and the LAN controller page start register MUST be loaded by software with a value of 20h.

#### **Register File Access**

Two consecutive I/O addresses are assigned to the register files. Byte instructions (inb, outb, ...) can be issued to either address, but word instructions (inw, outw, etc.) MUST be issued to the lower address.

# **Programmed I/O**

Data can be exchanged between the register files and the PC data bus under software programmed I/ O control. The number of bytes to be transferred for each burst is limited to 8 (if Control register bit 5 is zero) or 16 bytes (if Control Register bit 5 is a one). In either case, bit 7 (Data Port Ready) in the Status register MUST be checked after EACH burst transfer. During program I/O data transfers, the number of bytes transferred SHOULD be divisible by 8 to allow the data to be burst aligned. This alignment allows a demand mode DMA transfer(s) following a programmed I/O transfer, without having to reprogram the gate array (the gate array will continue where the program I/O ended). However, additional programming may be required to start the DMA controller on the motherboard.

# **DMA Transfer**

The EtherLink II supports a variety of DMA data transfer methods along with the handshake protocols. Described below are some of the DMA transfer methods that the EtherLink II adapter supports.

#### Single Byte Mode

A DMA data transfer mode supported by the EtherLink II adapter. Programming the DMA controller on the motherboard for single-byte mode causes it to transfer ONLY one byte per DMA session. The DMA controller on the adapter is armed with multiple bytes available but will deliver a byte of data for each I/O read or write signal that it receives. It should be noted that each byte transferred in this mode has the overhead of re-arbitrating for the bus (lots of time loss).

#### **Demand Mode**

A method of data transfer supported by the EtherLink II Ethernet adapter. Demand mode is a DMA data transfer between the DMA controller on the motherboard and the DMA controller on the EtherLink II Ethernet adapter. Data transfer is started by the DMA controller on the adapter by rising the drq (DMA request) signal on the PC bus. The DMA controller on the motherboard responds by asserting the dack (DMA acknowledge) signal on the PC bus. The DMA controller on the motherboard proceeds with asserting the I/O read OR I/O write PC bus signal. The DMA controller on the adapter responds with a new byte of data for each I/O read OR I/O write signal it receives. The transferring of data continues as long as the drq signal is active.

# **Drq Timer**

Controls the number of bytes to be transferred during a demand mode DMA transfer. The drq x (x equals the DMA channel assigned to the adapter) PC bus signal is asserted and data is transferred until the value loaded into the drq timer register has been decremented to zero. The drq signal is de-asserted once the drq timer register reaches zero and reasserted after the appropriate **da**ck (DMA acknowledge) signal is de-asserted, indicating this DMA data transfer session has gracefully terminated. This sequence allows other adapters/devices the opportunity for DMA service.

# **Memory Mapped**

The EtherLink II adapter has the capability of "mapping" the board resident packet buffer into the personal computer's memory address space. The memory address is user determined by the position of the J1 jumper. The J1 jumper offers four possible addresses (dc000, d8000, cc000, c8000). The address selected by the J1 jumper also determines the address for the bootable EPROM socket. Memory-mapped mode is selected by setting the GA Configuration register to a value of 49h. Resetting memory-mapped mode is done by either resetting the system (power up reset) or executing an instruction at an address that matches the value in the vector pointer registers.

# Word Instructions

The EtherLink II adapter supports word I/O accesses to the register files (FIFO). The register files are the only register that can be accessed with a word instruction. The word access should be addressed to the lower address of the register files (base address + 40Eh). The Data Port Ready bit in the status register MUST be checked after four words (8 bytes) in parallel register file configuration or after eight words (16 bytes) in serial register file configuration.

# FIFO Configurations - (Selected in GA Control Register)

# **Serial Configuration**

EtherLink II: Initialization

6-1

# **Chapter 6: Initialization**

# **Power Up Reset**

| I/O Address | Gate Array Register | Data Value |

|-------------|---------------------|------------|

| base + 400h | Page Start          | 00         |

| base + 401h | Page Stop           | 00         |

| base + 402h | Drg Timer           | 00         |

| base + 403h | Base Configuration  | ww         |

| base + 404h | PROM Configuration  | xx         |

| base + 405h | GA Configuration    | 00         |

| base + 406h | Control Register    | 0A         |

| base + 407h | Status Register     | уу         |

| base + 408h | Int/DMA Register    | 00         |

| base + 409h | DMA Address MSB     | 00         |

| base + 40Ah | DMA Address LSB     | 00         |

| base + 40Bh | Vector Pointer 2    | 00         |

| base + 40Ch | Vector Pointer 1    | 00         |

| base + 40Dh | Vector Pointer 0    | 00         |

| base + 40Eh | Register File LSB   | ZZ         |

| base + 40Fh | Register File MSB   | ZZ         |

ww = dependent on position of J2 jumper

xx = dependent on position of J1 jumper

yy = gate array revision code

zz = unknown data until DMA transfer started

# **Software Reset**

A software reset is initiated by setting bit 0 in the Control register (base address + 406h) to a logical one. A software reset emulates all properties of a hard reset (power on initialization) except that the configuration registers (base, PROM) are not reloaded. The configuration registers retain their previously loaded values. A reset condition continues to exist until the software reset bit is de-asserted (a logical zero). It is the responsibility of the driver software to de-assert the software reset bit after a time duration which provides reasonable assurance that the condition(s) that caused the reset to be issued has been cleared. The gate array (after the de-assertion of the software reset bit) registers are reset to the values in the following table.

| I/O Address | Gate Array Register | Data Value |

|-------------|---------------------|------------|

| base + 400h | Page Start          | 00         |

| base + 401h | Page Stop           | 00         |

| base + 402h | Drg Timer           | 00         |

| base + 403h | Base Configuration  | ++         |

| base + 404h | PROM Configuration  | ++         |

| base + 405h | GA Configuration    | 00         |

| base + 406h | Control Register    | 0A *       |

| base + 407h | Status Register     | уу         |

| base + 408h | Int/DMA Register    | уу<br>00   |

| base + 409h | DMA Address MSB     | 00         |

| base + 40Ah | DMA Address LSB     | 00         |

| base + 40Bh | Vector Pointer 2    | 00         |

| base + 40Ch | Vector Pointer 1    | 00         |

| base + 40Dh | Vector Pointer 0    | 00         |

| base + 40Eh | Register File LSB   | ZZ         |

| base + 40Fh | Register File MSB   | ZZ         |

|             | 1                   |            |

++ = retains data value

yy = gate array revision code

zz = register file pointer is reset to byte 0 of the register file. Residual data will exist in the register file.

\* = contains data value OB during software reset bit asserted.

# **Software Reset Programming Sequence**

The software reset bit takes precedence and will abruptly end any operation in progress. The RECOMMENDED value to activate the assertion of the software reset is 03 (the on-board transceiver select bit and the software reset bit).

Asserting bits in the Control register and de-asserting the software reset bit REQUIRES two sequential program instructions. You issue the first instruction to de-assert the software reset bit and the second instruction to assert the desired bits. A simultaneous assertion of bits along with the deassertion of the software reset bit results in a Control register of 0A.

EtherLink II: I/O Address Map

7-1

# Chapter 7: I/O Address Map

| Address Range                                                        | Control Register<br>Bits 3, 2        | Assignments                                                                                                       |

|----------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Base Address<br>Base Address<br>Base Address*<br>Base Address + 400h | 0, 0<br>0, 1<br>1, 0<br>x, x<br>1, 1 | LAN Controller<br>Ethernet PROM Bytes 0 - 15<br>Ethernet PROM Bytes 16 - 31<br>Gate Array Registers<br>Unassigned |

\* = default power-on value x = don't care

# **Ethernet Address PROM Bytes 31-16**

| Address Decode                                                                                                                                                                                                                                                                                                                          | Control Register<br>Bits 3, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Assignments                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| base address<br>base address + 1h<br>base address + 2h<br>base address + 3h<br>base address + 3h<br>base address + 4h<br>base address + 5h<br>base address + 6h<br>base address + 7h<br>base address + 8h<br>base address + 9h<br>base address + 9h<br>base address + Bh<br>base address + Ch<br>base address + Eh<br>base address + Fh | 1, 0<br>1, 0 | byte 16<br>byte 17<br>byte 18<br>byte 19<br>byte 20<br>byte 21<br>byte 22<br>byte 23<br>byte 24<br>byte 25<br>byte 26<br>byte 27<br>byte 28<br>byte 29<br>byte 30<br>byte 31 |

EtherLink II: I/O Address Map

# Ethernet Address PROM Bytes 15-0

7-2

| Address Decode                                                                                                                                                                                                                                                                                                                                               | Control Register<br>Bits 3, 2                                | Assignments                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| base address<br>base address + 1h<br>base address + 2h<br>base address + 2h<br>base address + 3h<br>base address + 4h<br>base address + 5h<br>base address + 6h<br>base address + 7h<br>base address + 8h<br>base address + 9h<br>base address + 9h<br>base address + Bh<br>base address + Ch<br>base address + Dh<br>base address + Eh<br>base address + Fh | 0, 1<br>0, 1<br>0, 1<br>0, 1<br>0, 1<br>0, 1<br>0, 1<br>0, 1 | Ethernet<br>Station<br>Address<br>byte 2<br>byte 3<br>byte 4<br>byte 5<br>byte 6<br>byte 7<br>byte 8<br>byte 9<br>byte 10<br>byte 11<br>byte 12<br>byte 13<br>byte 14<br>byte 15 |

# **LAN Controller**

.

| Address Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Control Register<br>Bits 3, 2                                | Assignments                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| base address<br>base address + 1h<br>base address + 2h<br>base address + 2h<br>base address + 3h<br>base address + 4h<br>base address + 5h<br>base address + 6h<br>base address + 7h<br>base address + 8h<br>base address + 8h<br>base address + 8h<br>base address + 8h<br>base address + 10<br>base address + 10 | 0, 0<br>0, 0<br>0, 0<br>0, 0<br>0, 0<br>0, 0<br>0, 0<br>0, 0 | CR<br>PSTART<br>PSTOP<br>BNDY<br>TPSR<br>TBCR0<br>TBCR1<br>ISR<br>RSAR0<br>RSAR1<br>RBCR0<br>RBCR1<br>RCR<br>TCR<br>DCR<br>IMR |

EtherLink II: I/O Address Map

# Gate Array

| Address Decode                                                                                                                                                                                                                                                                                                                                                                               | Control Register<br>Bits 3, 2                                | Assignments                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| base address<br>base address + 401h<br>base address + 402h<br>base address + 403h<br>base address + 404h<br>base address + 405h<br>base address + 406h<br>base address + 407h<br>base address + 408h<br>base address + 409h<br>base address + 40Bh<br>base address + 40Bh<br>base address + 40Ch<br>base address + 40Dh<br>base address + 40Eh<br>base address + 40Eh<br>base address + 40Eh | X, X<br>X, X<br>X, X<br>X, X<br>X, X<br>X, X<br>X, X<br>X, X | PSTR<br>PSPR<br>DQTR<br>BCFR<br>PCFR<br>GACFR<br>CTRL<br>STREG<br>IDCFR<br>DAMSB<br>DALSB<br>VPTR2<br>VPTR1<br>VPTR0<br>RFMSB<br>RFLSB |

$\mathbf{x} =$ don't care

# **Chapter 8: Memory Address Map**

# EPROM

| Address         | Туре | Description               |

|-----------------|------|---------------------------|

| DC000 - DDFFF*  | R    | Estart Address            |

| D8000 - D9FFF*  | R    | Estart Address            |

| CC000 - CDFFF*  | R    | Estart Address            |

| C8000 - C9FFF*  | R    | Estart Address            |

| x1FFE - x1FFF** | R    | Base Configuration Enable |

\* Address decoded in conjunction with PROM configuration jumpers and GA Config register bit 3.

\*\* Reading the last 2 bytes of the PROOM address space returns the value of the GA Base Configuration register. Allows Startup PROM code to determine the adapters' Base Address.

x = selected address range (only values D or C are valid)

# RAM

| Address       | Туре | Description |

|---------------|------|-------------|

| DC000 - DDFFF | R    | RAM Address |

| D8000 - D9FFF | R    | RAM Address |

| CC000 - CDFFF | R    | RAM Address |

| C8000 - C9FFF | R    | RAM Address |

One of these address ranges is selected in conjunction with PROM configuration jumpers and GA Configuration register bit 3.

# **Vector Pointer**

The value loaded into these registers are compared against PC bus address bits 19-0. If a compare occurs DURING a memory read (-Smemr asserted), the memory-mapped mode is reset (GA Configuration bit 3). The suggested value for the vector pointer registers is the interrupt vector address issued during the "soft boot sequence" (Alt-Ctrl-Del).

EtherLink II: Jumper Position Equates

# **Chapter 9: Jumper Position Equates**

| J1 Jumper Position | Memory Addresses           |  |  |

|--------------------|----------------------------|--|--|

| 1                  | Disabled (Factory Setting) |  |  |

| 2                  | DC000 - DDFFF              |  |  |

| 3                  | D8000 - D9FFF              |  |  |

| 4                  | CC000 - CDFFF              |  |  |

| 5                  | C8000 - C9FFF              |  |  |

| J2 Jumper Position | Jumper Position Gate Array Addresses |           |  | I2 Jumper Position Gate Array Addresses I/O Base Addresses |  |  |  |

|--------------------|--------------------------------------|-----------|--|------------------------------------------------------------|--|--|--|

| 1                  | 300 - 30F (Factory Setting)          | 700 - 70F |  |                                                            |  |  |  |

| 2                  | 310 - 31F                            | 710 - 71F |  |                                                            |  |  |  |

| 3                  | 330 - 33F                            | 730 - 73F |  |                                                            |  |  |  |

| 4                  | 350 - 35F                            | 750 - 75F |  |                                                            |  |  |  |

| 5                  | 250 - 25F                            | 650 - 65F |  |                                                            |  |  |  |

| 6                  | 280 - 28F                            | 680 - 68F |  |                                                            |  |  |  |

| 7                  | 2A0 - 2AF                            | 6A0 - 6AF |  |                                                            |  |  |  |

| 8                  | 2E0 - 2EF                            | 6E0 - 6EF |  |                                                            |  |  |  |

EtherLink II: Gate Array Descriptions

10-1

# Chapter 10: Gate Array Descriptions

# **Gate Array Register Definitions**

# Page Start Register

Base + 400h (read/write access)

The Page STart Register (PSTR) is an 8-bit read/write register. The value written into PSR determines the most significant byte of the starting address for receive packets in the local RAM. The data value loaded into PSTR MUST match the data value loaded into the Edlc Page Start register. The recommended value to load in the page start registers is 26h (h = hex). A page start register value of 26h segments the packet buffer into six pages (256 bytes/page) of transmit space for one maximum size Ethernet packet.

| PSTR Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|------------|-----|-----|-----|-----|-----|-----|----|----|

| AdrMSB Bit | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 |

The value loaded in this register sets the beginning of the receive segment of the board resident packet buffer. Receive packets are placed in the packet buffer specified starting at the address specified by the value loaded in this register. The most significant address bit is A15 and the least significant is A8. See Recommended Adapter Memory Configuration on next page.

# Page Stop Register

#### Base + 401h (read/write access)

The Page StoP Register (PSPR) is an 8-bit read/write register. The value written into **PSPR** determines the most significant byte of the ending address for receive packets in the **local RAM**. The data value loaded into PSPR MUST match the data value loaded into the Edlc Page **Stop** register. The recommended value to load in the page stop registers is 40h (h = hex). A page stop register value of 40h segments the packet buffer into 26 pages (256 bytes/page) of receive space for a variety of Ethernet packet sizes. The most significant address bit is A15 and the least significant is A8.

| PSPR Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|------------|-----|-----|-----|-----|-----|-----|----|----|

| AdrMSB Bit | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 |

The value loaded in this register sets the ending address for the receive segment of the **bo**ard resident packet buffer. Receive packets are placed in the packet buffer up to the address specified by the PSPR register. See Recommended Adapter Memory Configuration on next page.

# **Recommended Adapter Memory Configuration**

With the standard 8K memory size, the adapter sees the memory starting at address 2000h so that an 8K page is 2000h-3FFFh. The recommended register values are:

NIC TPSR = 20hNIC PSTART = 26hNIC PSTOP = 40hGA PageStart = 26hGA PageStop = 40h

This yields the following partitioning of the buffer space:

Transmit buffer becomes:  $2000h - 2600h = 256 \times 6 = 1536$  bytes Receive buffer becomes:  $2600h - 4000h = 256 \times 26 = 6656$  bytes

This allows transmit space for one full size 802.3 packet and receive space for four full size packets.

#### **Drq Timer Register**

#### Base + 402h (read/write access)

The DrQ Timer Register (DQTR) is an 8-bit read/write register. The value (binary weighted) written into DQTR determines the number of bytes to be transferred during a DMA burst. Transfer Time must be less than system refresh time. The recommended value to load into the DQTR is:

# of bytes transferred + transfer overhead = < 15uS (which is the system memory refresh rate)

The value loaded into the Drq Timer register MUST meet the following conditions:

- 1. Be a multiple of 4 (i.e., 4, 8, 24, 32, etc.)

- 2. If the value is greater than or equal to 12, then bit 5 (16 byte select/double buffer select) in the Control register must be set.

| DQTR Bit  | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|-----------|---|---|---|-----|-----|-----|-----|-----|

| Timer Bit |   |   |   | tb4 | tb3 | tb2 | tb1 | tb0 |

| Bit                                  | Symbol | Description                                                                                                             |

|--------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 |        | not used<br>not used<br>not used<br>timer bit 4 (MSB)<br>timer bit 3<br>timer bit 2<br>timer bit 1<br>timer bit 0 (LSB) |

EtherLink II: Gate Array Descriptions

10-3

## **Base Configuration Register**

#### Base + 403h (read only)

The Base ConFiguration Register (BCFR) is an 8-bit read-only register. The value written into BCFR during initialization (power up) determines the I/O base address of the adapter. To change the I/O base address loaded into the base configuration register requires you to power down the computer, change the position of the jumper (J2), and power up the computer.

| BCFR Bit         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| I/O Base Address | 300 | 310 | 330 | 350 | 250 | 280 | 2A0 | 2E0 |

| Bit | Symbol | Description                         |

|-----|--------|-------------------------------------|

| 7   | 300    | i/o base address option 7 (default) |

| 6   | 310    | i/o base address option 6           |

| 5   | 330    | i/o base address option 5           |

| 4   | 350    | i/o base address option 4           |

| 3   | 250    | i/o base address option 3           |

| 2   | 280    | i/o base address option 2           |

| 1   | 2A0    | i/o base address option 1           |

| 0   | 2E0    | i/o base address option 0           |

# **EPROM Configuration Register**

Base + 404h (read only)

The PROM ConFiguration Register (PCFR) is an 8-bit read-only register. The value written into PCFR during initialization (power up) determines the memory base address of the adapter. To change the memory base address loaded into the PROM configuration register requires you to power down of computer, change the position of the jumper (J1), and power up the computer.

| PCFR Bit       | 7     | 6     | 5     | 4     | 3 | 2 | 1 | 0 |

|----------------|-------|-------|-------|-------|---|---|---|---|

| Memory address | DCXXX | D8XXX | CCXXX | C8XXX | 0 | 0 | 0 | 0 |

| Bit                                  | Symbol                                                    | Description                                                                                                                              |

|--------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | DCXXX<br>D8XXX<br>CCXXX<br>C8XXX<br>0<br>0<br>0<br>0<br>0 | memory address option<br>memory address option<br>memory address option<br>memory address option<br>zero<br>zero<br>zero<br>zero<br>zero |

10-4

**GA Configuration Register** Base + 405h (read/write) The GA ConFiguration Register (GACFR) is an 8-bit read/write register. The majority of **the** bits in the register are initialized during the execution of a software initialization routine.

| GACFR Bit     | 7   | 6   | 5   | 4    | 3    | 2    | 1    | 0    |

|---------------|-----|-----|-----|------|------|------|------|------|

| Configuration | nim | tcm | ows | test | rsel | mbs2 | mbs1 | mbs0 |

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | nim    | (Nic Int Mask). A positive true signal used to block the propagation of interrupts from the LAN Controller to the interrupt controller (8259). LAN Controller generates interrupts for receive packets, transmit packets.                                                                                  |

|     |        | 0 = pass interrupts (power up state)<br>1 = block interrupts                                                                                                                                                                                                                                               |

| 6   | tcm    | (Terminal Count Mask). A positive true signal used to block the setting of<br>a DMA complete interrupt generated by the DMA controller in the gate<br>array. The gate array generates an interrupt upon receiving a terminal<br>count pulse from the PC bus interface during a DMA transfer.               |

|     |        | 0 = pass interrupts (power up state)<br>1 = block interrupts                                                                                                                                                                                                                                               |

| 5   | ows    | (0 Wait State). Used to allow the assertion of the zero wait state signal during I/O accesses to only registers in the gate array.                                                                                                                                                                         |

| 4   | test   | (TEST). For use ONLY by the gate array vendor. Setting this bit causes the counters in the gate array to count at a rate of 10Mbs.                                                                                                                                                                         |

| 3   | rsel   | (RAM Select). Used to map the packet buffer into system memory address space. The position of the J1 (memory) MUST be positioned in one of the four pre-determined address options (DC000, D8000, CC000, C8000) in conjunction with setting this bit to determine the memory address of the packet buffer. |

| 2   | mbs2   | (Memory Bank Select 2).*                                                                                                                                                                                                                                                                                   |

| 1   | mbs1   | (Memory Bank Select 1).*                                                                                                                                                                                                                                                                                   |

| 0   | mbs0   | (Memory Bank Select 0).*                                                                                                                                                                                                                                                                                   |

\* See Memory Bank Select on next page.

EtherLink II: Gate Array Descriptions

The mbs bits are applicable ONLY during memory-mapped mode. The software is required to set the appropriate bits to select 8K segments of the packet buffer. Using the standard packet buffer configuration of 8K, the mbs0 bit is set. Using the 32K option, the 8K, 16K, 24K, 32K configurations are software selectable. Segments above 32K are not a selectable option.

#### **Memory Bank Select**

The mbs bits are applicable ONLY during memory-mapped mode. These three bits determine which 8K window of adapter memory appears in the host address space at the location selected by jumper1 on the card. The three bits, mbs 2-0 are equivalent to adapter address bits A15-13.

An adapter with a 32K memory\* has four 8K windows that can be selected. A standard adapter with an 8K memory has only one possible window and, due to hardware considerations, this must be the second 8K starting at 2000h in the adapter memory space.

#### **8K Configuration**

| Memory Access | msb2 | msb1 | msb0 | Adapter Start Address |

|---------------|------|------|------|-----------------------|

| 1st 8K        | 0    | 0    | 1    | 2000h                 |

#### 32K Configuration\*

| Memory Access | msb2 | msb1 | msb0 | Adapter Start Address |

|---------------|------|------|------|-----------------------|

| 1st 8K        | 0    | 0    | 0    | 0000h                 |

| 2nd 16K       | 0    | 0    | 1    | 2000h                 |

| 3rd 24K       | 0    | 1    | 0    | 4000h                 |

| 4th 32K       | 0    | 1    | 1    | 6000h                 |

\* Adapters with 32K memory are not currently available from 3Com (December 1988.)

EtherLink II: Gate Array Descriptions

# Control Register Base + 406h (read/write access)

·

| CR Bit  | 7     | 6    | 5    | 4     | 3    | 2    | 1    | 0   |

|---------|-------|------|------|-------|------|------|------|-----|

| Control | start | ddir | bsel | share | eahi | ealo | xsel | rst |

| Bit | Symbol                                   | Description                                                                                                                                                                                                                                                                                                                                      |

|-----|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | start                                    | (START). Used to start the DMA controller in the gate array. Prior to setting this bit, the DMA address registers should point to the starting address of the packet buffer from which a data transfer will begin.                                                                                                                               |

| 6   | ddir                                     | (DMA DIRection). Used to set the direction of the data transfer between<br>the gate array and the PC bus interface. The setting of this bit may occur<br>simultaneously with the Start bit. It is ILLEGAL to change the DMA<br>Direction bit after the Start bit is programmed to the active state (a logical<br>one).                           |

|     |                                          | 0 = upload (packet buffer to system)<br>1 = download (system to packet buffer)                                                                                                                                                                                                                                                                   |

| 5   | dbsel                                    | (Double Buffer SELect). Used to connect the two 8-byte FIFOs in a serial configuration.                                                                                                                                                                                                                                                          |

| 4   | share                                    | (interrupt SHARE). Used to select the interrupt sharing capability of the adapter. Interrupt sharing allows multiple adapters that have implemented interrupt sharing hardware to share a common interrupt channel to generate interrupts. Adapter configured for interrupt sharing CANNOT exist on the same channel with a non-sharing adapter. |

|     |                                          | 0 = non-sharing interrupt channel<br>1 = sharing interrupt channel                                                                                                                                                                                                                                                                               |

| 3   | eahi                                     | (Ethernet Address HIgh) used to "window" the Ethernet Address PROM bytes 31-16 into the I/O base address. This bit is set active following a power-up condition or a software reset.                                                                                                                                                             |

| 2   | ealo                                     | (Ethernet Address LOw). Used to "window" the Ethernet Address PROM bytes 15-0 into the I/O base address. Bytes 5-0 of the Ethernet address PROM contain the station address of the adapter.                                                                                                                                                      |

| 1   | xsel                                     | (Xcvr Select). Used to select the transceiver type on the adapter.                                                                                                                                                                                                                                                                               |

|     | an a | 1 = on-board transceiver (BNC), default<br>0 = external transceiver (DIX)                                                                                                                                                                                                                                                                        |

| 0   | rst                                      | (Software ReSeT). Used to emulate a power up reset. The reset initializes the gate array and the LAN Controller registers.                                                                                                                                                                                                                       |

|     |                                          | 0 = software reset inactive<br>1 = software reset active                                                                                                                                                                                                                                                                                         |

Status Register Base + 407h (read only) The Status Register (STREG) is an 8-bit, read-only register. The bits in this register provide information on the progress or completion status of the present operation.

| STREG Bit       | 7     | 6    | 5    | 4   | 3   | 2    | 1    | 0    |

|-----------------|-------|------|------|-----|-----|------|------|------|

| Operaton Status | dprdy | uflw | oflw | dtc | dip | rev2 | revl | rev0 |

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | dprdy  | (Data Port ReaDY). This status bit indicates that the register files are<br>ready for data transfer. During a download operation (system to adapter),<br>the register files are "flushed" when the Start bit in the Control register is<br>de-asserted by the software. During an upload operation, the register files<br>end the data transfer by either receiving a terminal count (during DMA<br>transfers) or when the Start bit in the Control register is de-asserted by the<br>software. |