MULTIPROCESSING SUPPORT FOR THE STD BUS PARALLEL INTERFACES BOOST WINCHESTER ACCESS TIME ELECTRONIC IMAGING '85 SHOW PREVIEW

X

381

38134

4

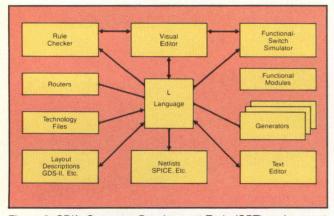

# TOOLS TO SUPPORT 100,000-GATE DESIGNS

Gould. . . Innovation and Quality in Image Processing

# Before you say, "It can't be done," check out these stories.

You may be surprised.

Gould's powerful IP8000 image processor is changing imaging improbabilities to startling realities with high-resolution answers for a world of applications.

# ESL explores better data integration with IP8000.

Patrick Hu, ESL product manager, commented, "Gould's IP8000 is perfect-fit hardware for our IDIMS digital data integration system. With the IP8000 as the IDIMS display, we can now offer the most advanced interactive digital image manipulation system available world-wide."

# McDonnell Douglas improves flight simulation training with IP8000.

"Real time image processing is crucial to our radar display simulator," says Dennis Gawera, McDonnell Douglas systems manager. "Gould was the only company that could give us the custom line rates we needed to interface with flight hardware."

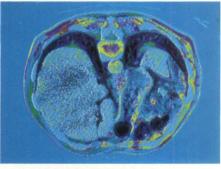

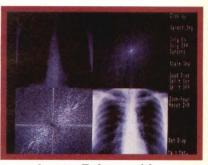

# Johns Hopkins detects cell changes in early cancer with IP8000.

Quantitative Cytopathology Laboratories chief, Norman J. Pressman, Ph.D., states, ". . . aided by the IP8000 processor, qualitative visual interpretation of cell and tissue patterns is taking

Invasive cancer cell of the lung

a powerful stride forward in early cancer detection and diagnosis. And earlier treatment, of course, means the opportunity to save more lives."

# Gould provides full system support.

Nuclear

enlargement

Complete support is available for the IP8000 System including Gould's Library of Image Processing Software (LIPS). Support also includes full installation, documentation, user training, and on going field maintenance. For more information contact:

> Gould Inc., Imaging and Graphics Division 46360 Fremont Boulevard, Fremont, CA 94538 USA Telephone (415) 498-3300 • TWX (910) 338-7656

European Headquarters Tegernseer Landstrasse 161, D-8000 Munchen 90, West Germany Telephone (089) 6-92-79-06 Telex 5218078-GOUI D

Circle 8

Simulated experimenta high-resolution radar display.

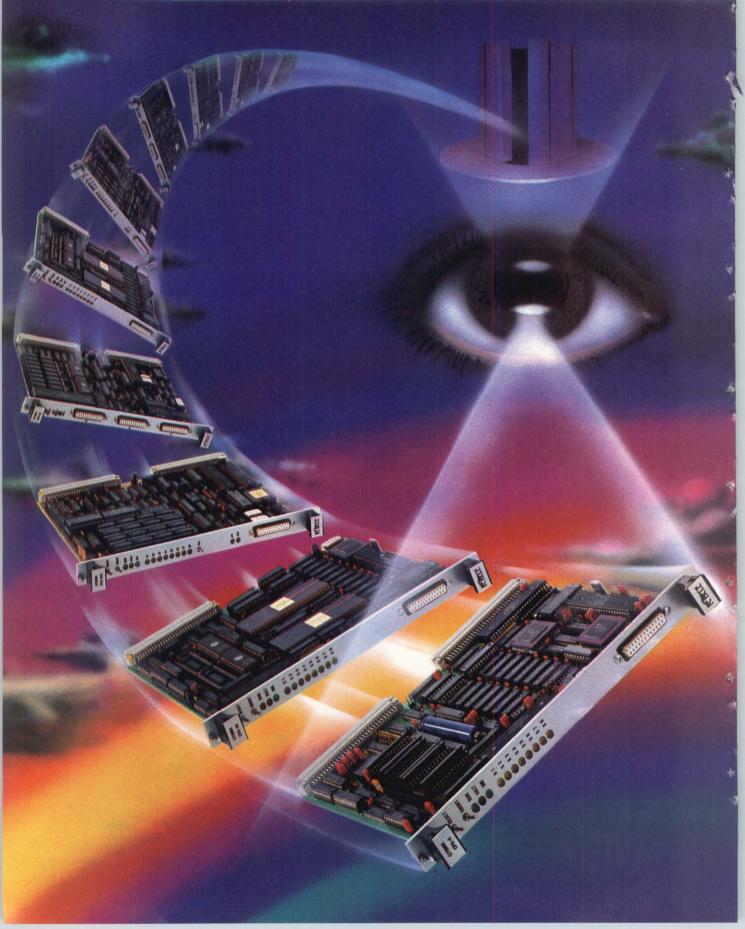

# Datacube presents

The most powerful family of video image processors. Choose modules that match your real-time image processing requirements.

MAXbus;" the video interconnect standard, gives you flexibility to expand your MaxVideo system.

...........

...............

............

anten anten

-----

-----

Write or call today.

and the second second

......

......

-----

# DATACUBE

Datacube, Inc. 4 Dearborn Road, Peabody, MA 01960 (617) 535-6644

Circle 10

# "NO WAIT STATE"

# Force's "NO WAIT STATE"-OF-THE-ART CPU-4 features the 68010 at 12.5MHz with 128KBytes of SRAM for your high speed applications.

Proven speed superior in benchmarks, the CPU-4 is ideal for high performance VMEbus applications. In fact, the "NO WAIT STATE" CPU-4 holds its own against 68020 CPU products operating with several wait states!

Addition of the CPU-4 to Force's distinguished product family, designed and manufactured with years of VMEbus board engineering and production experience, assures you of a reliable, available, high performance CPU. CPU products available include:

CPU-1 The World's most popular and Series universal VMEbus CPU featuring 8/10MHz 68000, 128/512KBytes DRAM, 3 serial ports, RTC, and more. Over 6000 sold worldwide.

OF - THE - AR

CPU-2 A highly versatile CPU incorpo-Series rating the 8/10MHz 68010 with true ''Dual Ported RAM'' from 128KBytes up to 1MByte, multi protocol communications controller, floppy disk controller, PIT, and RTC. CPU-3 The World's first UNIX\* VMEbus Series board incorporating the 68010 CPU, 68451 MMU, and 68450 DMAC, 4 level bus arbiter, and serial I/O on one double Eurocard, 32 or 128K Bytes, zero wait state, SRAM CACHE mode operation

**CPU-4** Additional features to those **Series** already mentioned include, a 68450 DMAC, 1 serial port, 2 parallel ports, RTC, and a floppy disk controller option.

# **NEW PRODUCT ADDITIONS**

### DRAM-E3M1+E3S3

The 1MByte DRAM master operates stand-alone or with multiple 3MByte slaves offering optimum performance in 32 bit data/32 bit address, Byte parity check environments. Typical access time is 65ns (write) and 240ns (read) with parity generation.

### CMC-1

As an intelligent monochrome or color controller for raster scan terminals, this stand-alone VMEbus board offers interfaces for keyboard, lightpen, 2 serial ports and 1 Centronics parallel port.

### **ASCU-1/2**

This new breed of high performance advanced system controller handles all exception signals on the VMEbus and contains powerful I/O devices such as a serial interface, Centronics parallel interface, 4 level bus arbiter, RTC, and GPIB interface (ASCU-2).

<sup>•</sup>If the VMEbus boards you purchase aren't designed and manufactured by FORCE, chances are they aren't "NO WAIT STATE"-OF-THE-ART.

Call Force Computers today, the VMEbus specialist!

\*Unix is a registered trademark of AT&T

FORCE COMPUTERS INC.

Phone (408) 354-3410 1

FORCE COMPUTERS GmbH

Telefon (0 89) 6 09 20 33 2 Telex 5 24 190 forc-d

FORCE COMPUTERS FRANCE

3

Telefax (089) 6 09 77 93

727 University Ave. Los Gatos, CA 95030

Tlx 172465 Telefax (408) 3957718

Daimlerstraße 9 D-8012 Ottobrunn

11, Rue Casteja

F-92100 Boulogne

by RECE

© Copyright 1985

For US, Canada and Mexico Circle 1 on Reader Inquiry Card For International Countries Circle the Office Number Closest to You

# **DIGITAL DESIGN**

15

27

50

Pcs link to analyzers

Electronic Imaging '85 Preview

| 17 | Systems / UNIX And 68020 Team Up On CPU Designs                                                                                                 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | Imaging / Image Processing Tools For Personal Computers                                                                                         |

| 21 | <b>Communications /</b> ISDN Promise Emerges With Silicon,<br>Standards                                                                         |

| 23 | <b>Design Tools</b> / Analog And Digital Accelerators Speed<br>Simulation • Personal Computers Mate With Analyzers<br>For Increased Flexibility |

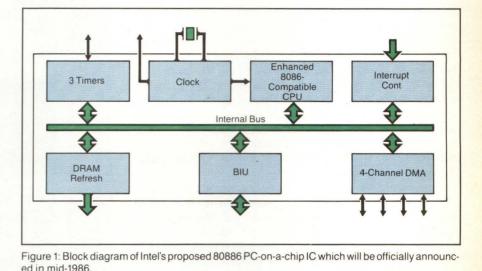

| 29 | ICs / Reducing The IBM PC/AT To A Chip Set                                                                                                      |

|    |                                                                                                                                                 |

TECHNOLOGY TRENDS

Software / CAE Techniques Migrate To Software

SEPTEMBER 1985

VOL. 15 NO. 9

108 Advertiser Index

60 High-Performance Winchesters

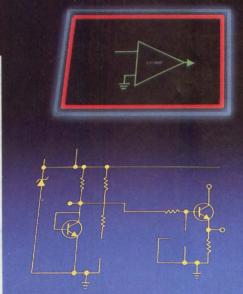

# ON THE COVER

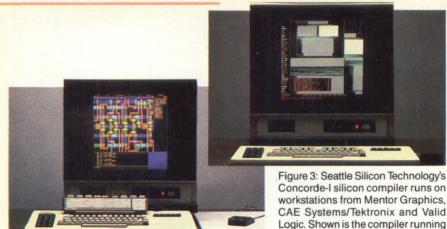

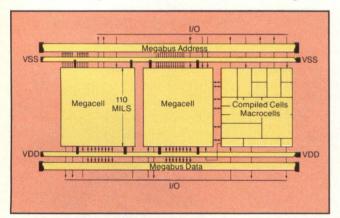

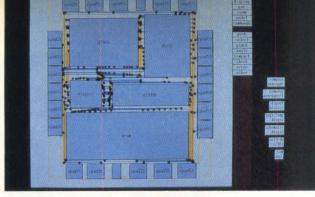

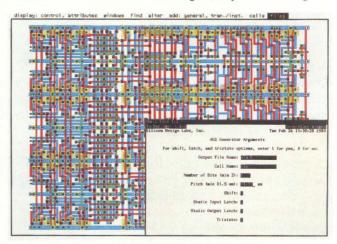

Silicon compilers dramatically reduce the time and training necessary to design complex, application-specific integrated circuits. The Concorde VLSI Compiler from Seattle Silicon offers a broad choice of digital and analog compilers to automate the design of CMOS chips. The compiler is currently integrated into CAE software on workstations from Valid Logic Systems, Tektronix CAE Systems and Mentor Graphics.

Published monthly thirteen times a year with two issues in November. Subscription rates for non-qualified subscribers (US and Canada) — \$40/yr; foreign — surface mail — \$550/yr; airmail — \$85/yr. Single copies — \$4. Copyright 1985 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, Berkshire Common, Pittsfield, MA 01201 ISSN 0147-9245.

# 11 Editor's Comment 13 Hotline 89 New Product Focus 93 New Products

Engineering

Silicon Compilers Silicon compilation ushers in the next era in system design.

# TABLE OF CONTENTS

# FEATURES

DESIGN TECHNOLOGY

# Managing The VLSI Explosion With Silicon Compilation

COURTESY SILICON DESIGN LABS

by Ronald Collett

Over the next three years, as higher integration levels form the foundation of system design, the magnitude of the VLSI problem will become apparent. This will necessitate the use of silicon compilers.

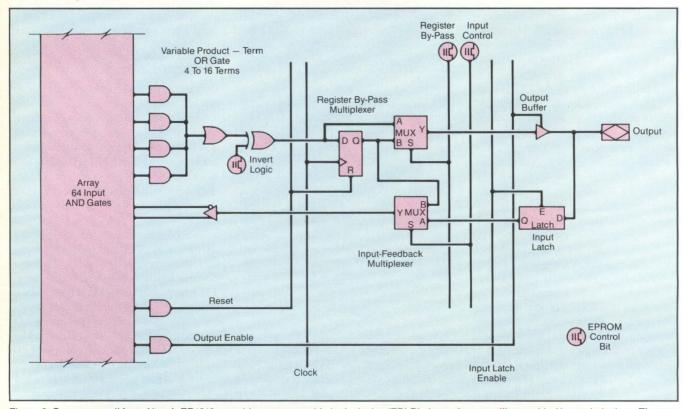

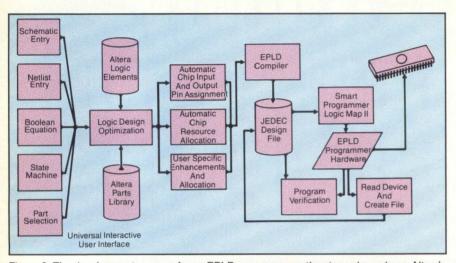

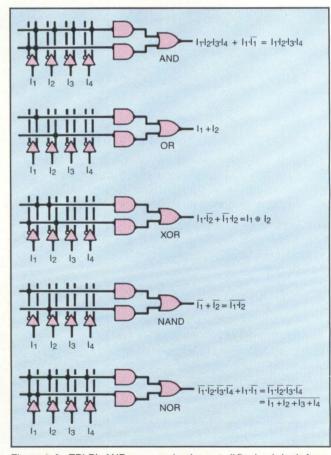

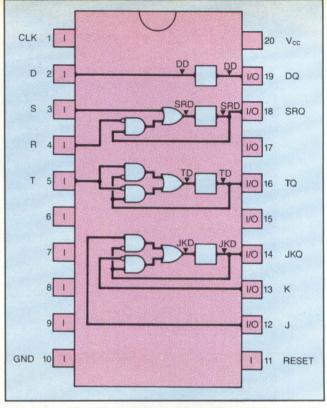

# Part 2: Erasable Programmable Logic Devices Implement A Variety Of Functions

# by Clive McCarthy

Aided by personal computer design and a versatile structure, EPLDs offer a straightforward answer to many design requirements.

### ELECTRONIC IMAGING

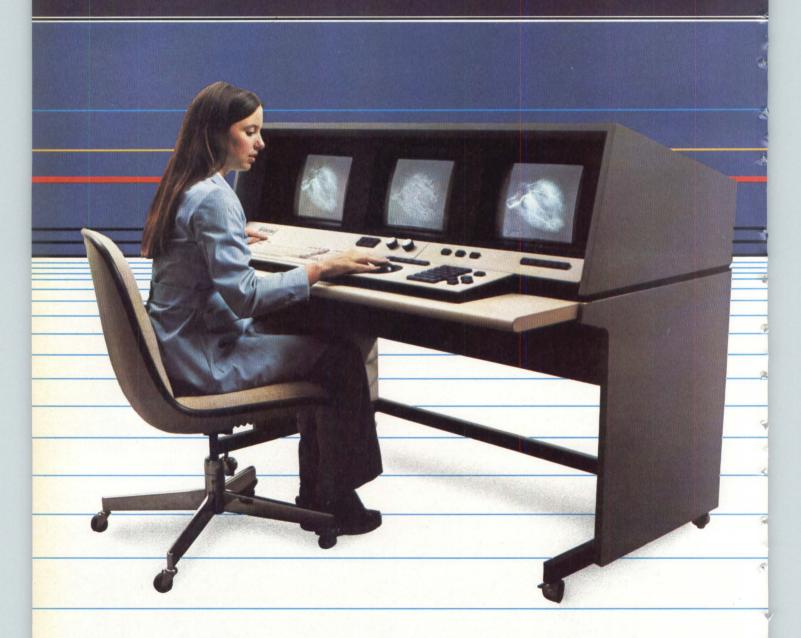

# Electronic Imaging '85: Digitizing The World

### by Andrew Wilson

The second international Electronic Imaging show, to be held October 8-10 in Boston, will feature products ranging from image capture devices, image processors to image displays. At the same time, the Electronic Imaging conference will discuss the latest developments in imaging technology.

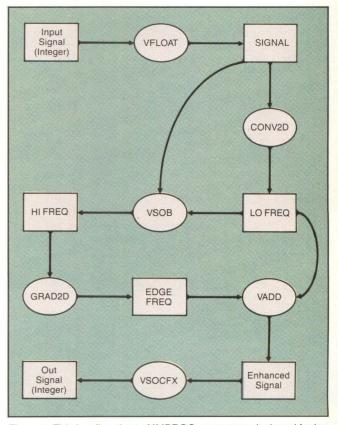

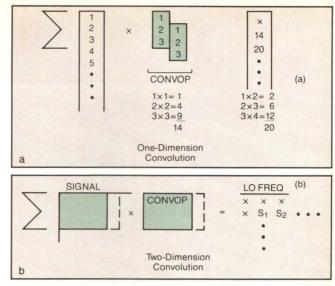

## Preprogrammed Algorithms Ease Development of Imaging Software

by William Smith

By using preprogrammed algorithms instead of writing original code for complex mathematical functions, engineers working in an applications development environment can concentrate on problem solving and be more productive.

## SYSTEMS ARCHITECTURE

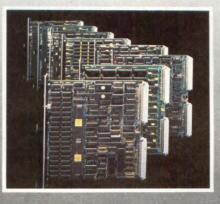

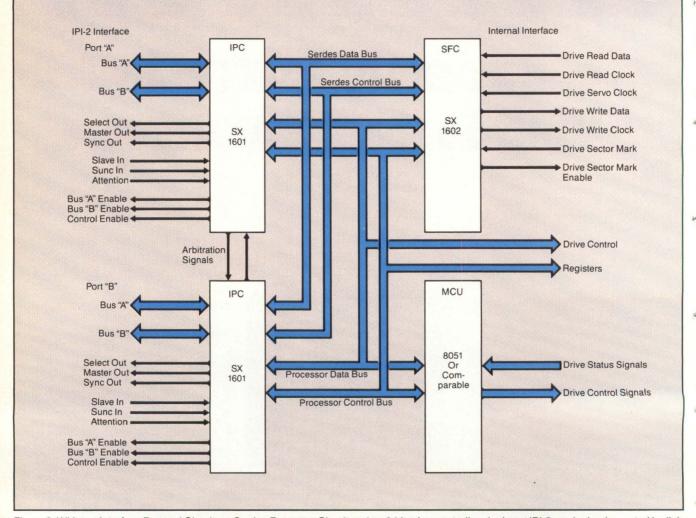

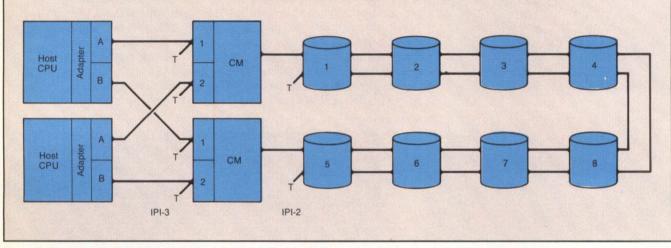

# **Options Increase For Effective Use of High-Performance Winchesters**

### by Julie Pingry

Combined with IPI-2, IPI-3 or enhanced SMD interfaces, sophisticated disk technology may now be put to full use; but testing, design for the application, controller choices and software drivers are still key.

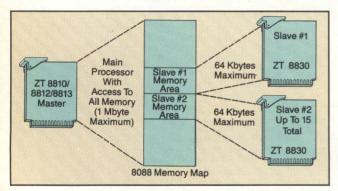

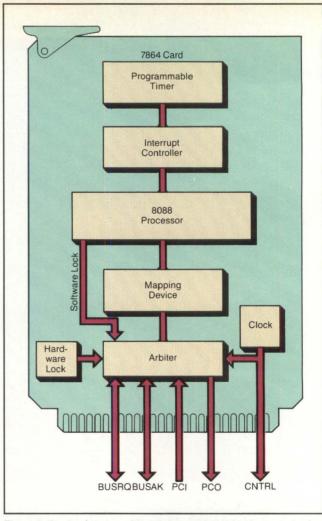

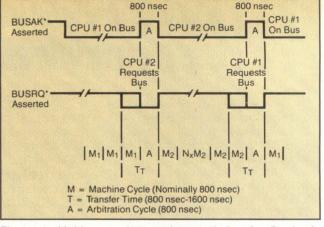

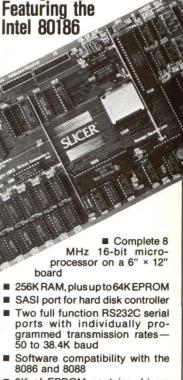

# 16-Bit Multiprocessing STD Bus Challenges High-End Solutions

by Dave Wilson

Through the support of 16-bit processors and multimaster support, the STD will continue to hold the low-end processor control market and will grow into the low-end minicomputer market.

## SEMICONDUCTOR TECHNOLOGY

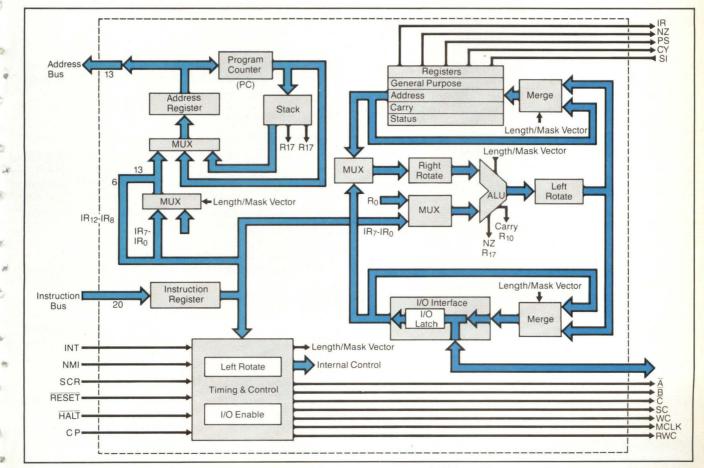

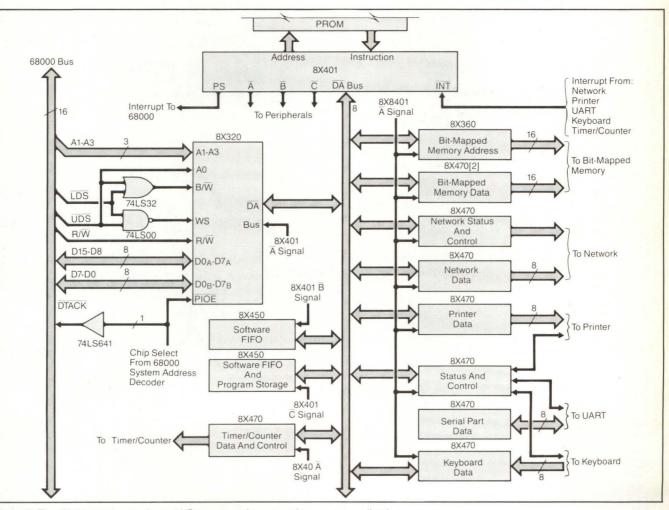

# Microcontroller Eases I/O Processing Burden

by Sunil Baliga, Gregory Goodhue and Jesse Jenkins

As power increases in personal computers, greater burden is put on the main system microprocessor. The 8x401, implemented as an I/O processor, can help relieve some of this increased burden on host processors, improving overall system performance as well as price/performance ratio.

# Vista-IPS

IMAGE PROCESSING DEVELOPMENT SOFTWARE

Industrial image processing: detection of fault in electrical connecto

If you are developing image processing techniques, then you should know about Vista-IPS<sup>™</sup> for:

- remote sensing

- industrial inspection data compression

- infra red

- sonar

- X-ray

and many other applications.

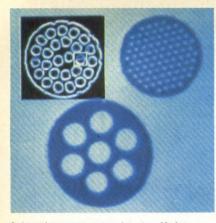

Information extraction from Landsat satellite images: Death Valley, California

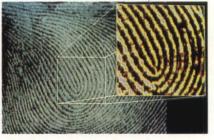

Edge information extracted from a fingerprint image

Call Logica Inc at 1900 Avenue of the Stars Suite 840 Los Angeles, CA 90067 Tel. (213) 551-0660

Outside USA, Vista-IPS is sold under the name LUCID!"Call Logica UK at +44 1 637 9111 or your local Logica office.

Circle 5

DIGITAL DESIGN will reprint any article from past or present issues. Reprints are custom printed. Minimum order: 1,000 copies. Purchase order or letter of authorization required.

Allow one month from receipt of order for delivery, unless previously arranged and confirmed.

Advertisements alone can also be reprinted. Call (617) 232-5470, and ask for reprints.

# **DIGITAL DESIGN**

| Editor in Chief                                                                                                                                                                                                                                                                                                                                                      | John Bond                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Managing Editor                                                                                                                                                                                                                                                                                                                                                      | Debra A. Lambert                                                                                                                                                                                                                                                                                                         |

| Technology Trends                                                                                                                                                                                                                                                                                                                                                    | Julie Pingry.<br>Senior Editor                                                                                                                                                                                                                                                                                           |

| Features:                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                          |

| Semiconductor Technolo                                                                                                                                                                                                                                                                                                                                               | Dave Wilson.<br>Executive Editor                                                                                                                                                                                                                                                                                         |

| Electronic Imaging                                                                                                                                                                                                                                                                                                                                                   | Andrew Wilson<br>Senior Technical Editor                                                                                                                                                                                                                                                                                 |

| Design Technology                                                                                                                                                                                                                                                                                                                                                    | Ronald E. Collett<br>Senior Technical Editor                                                                                                                                                                                                                                                                             |

| Systems Architecture                                                                                                                                                                                                                                                                                                                                                 | Brita Meng.<br>Technical Editor                                                                                                                                                                                                                                                                                          |

| New Products Editor                                                                                                                                                                                                                                                                                                                                                  | Terri Lamneck                                                                                                                                                                                                                                                                                                            |

| West Coast Technical Edite<br>(408) 356-0405                                                                                                                                                                                                                                                                                                                         | ors Gregory MacNicol<br>Joe Asec                                                                                                                                                                                                                                                                                         |

| Copy Editor                                                                                                                                                                                                                                                                                                                                                          | Sherri Mack                                                                                                                                                                                                                                                                                                              |

| Editorial Assistant                                                                                                                                                                                                                                                                                                                                                  | Tia Partin                                                                                                                                                                                                                                                                                                               |

| Contributing Editor                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                          |

| Carries And Diseaster                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                          |

| Senior Art Director<br>Advertising Production Ma                                                                                                                                                                                                                                                                                                                     | Tilly Berenson                                                                                                                                                                                                                                                                                                           |

| Advertising Production Ma                                                                                                                                                                                                                                                                                                                                            | Tilly Berenson<br>Inager Martha Watjen                                                                                                                                                                                                                                                                                   |

| Advertising Production Ma<br>Production Director                                                                                                                                                                                                                                                                                                                     | Tilly Berenson<br>nager Martha Watjen<br>Paul Dadarria                                                                                                                                                                                                                                                                   |

| Advertising Production Ma                                                                                                                                                                                                                                                                                                                                            | Tilly Berenson<br>nager Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf                                                                                                                                                                                                                              |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician                                                                                                                                                                                                                                                                           | Tilly Berenson<br>nager Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour                                                                                                                                                                                                            |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician                                                                                                                                                                                                                                                         | Tilly Berenson<br>nager Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King                                                                                                                                                                                          |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director                                                                                                                                                                                                                                   | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull                                                                                                                                                                                 |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant                                                                                                                                                                                       | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo                                                                                                                                                                  |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant                                                                                                                                                                                       | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg. Peter Michel                                                                                                                                      |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant<br>Research Carolyn                                                                                                                                                                   | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg, Peter Micheli<br>Hugh J. Dowling                                                                                                                  |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant<br>Research Carolyn<br>Circulation Director<br>Circulation Supervisor                                                                                                                 | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg, Peter Michell<br>Hugh J. Dowling<br>Nancy McPherson                                                                                               |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant<br>Research Carolyn<br>Circulation Director<br>Circulation Supervisor                                                                                                                 | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg, Peter Michell<br>Hugh J. Dowling<br>Nancy McPherson<br>iam Hlister. Kelly Kudlate                                                                 |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant<br>Research Carolyn<br>Circulation Director<br>Circulation Director<br>Circulation Supervisor<br>Circulation Staff Miri<br>Reader Service (413) 499-<br>Marketing/Sales Specialist    | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg. Peter Michell<br>Hugh J. Dowling<br>Nancy McPherson<br>iam Hlister. Kelly Kudlate<br>2550 Terri Giroux                                            |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant<br>Research Carolyn<br>Circulation Director<br>Circulation Supervisor<br>Circulation Staff Miri<br>Reader Service (413) 499-<br>Marketing/Sales Specialist<br>Executive Administrator | Tilly Berenson<br>Martha Watjen<br>Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg. Peter Micheli<br>Hugh J. Dowling<br>Nancy McPherson<br>iam Hlister. Kelly Kudlate<br>2550 Terri Giroux<br>Krickett Cunningham<br>Suzanne Levecque |

| Advertising Production Ma<br>Production Director<br>Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician<br>Marketing Director<br>Promotion Manager<br>Marketing Assistant<br>Research Carolyn<br>Circulation Director<br>Circulation Director<br>Circulation Supervisor<br>Circulation Staff Miri<br>Reader Service (413) 499-<br>Marketing/Sales Specialist    | Paul Dadarria<br>William Manning Jr.<br>Don Schaaf<br>Jan B. Seymour<br>Charlotte King<br>Elaine Bull<br>Sharon Lembo<br>Wulfsberg, Peter Micheli<br>Hugh J. Dowling<br>Nancy McPherson<br>iam Hlister. Kelly Kudlate<br>2550 Terri Giroux<br>Krickett Cunningham<br>Suzanne Levecque                                    |

President. Ronald W. Evans Publisher. James R. DiFilippo

Associate Publisher Terry L. Willins

### Advertising Sales

Northeast: Charles C. Boyd (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue. Boston. MA 02215

Middle Atlantic/Southeast: Richard V Busch (609) 921-7763, 40 Stony Brook Lane. Princeton. NJ 08540

Central: Mike Prewitt (714) 851-8550, 2041 Business Center Dr. Suite 206. Irvine, CA 92715

Northwest: Carole Sacino. Diane Ross (408) 356-0405, 15951 Los Gatos Blvd., Suite 7. Los Gatos. CA 95030

Southwest: Thomas A Stillman (714) 851-8550. 2041 Business Center Dr., Suite 206, Irvine, CA 92715

National Recruitment Sales: Brenda Stillman (714) 851-8550. 2041 Business Center Dr. Suite 206. Irvine. CA 92715

National Postcard Sales: Lisa Rendini (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue. Boston. MA 02215

National List Rental Sales: Deb Goldstein (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

SEPTEMBER 1985 E DIGITAL DESIGN

... and the winner is HITACHI®

for the newest technological advance in RGB color monitor history...

Our square cornered, 15", compact and affordable, hi-resolution flicker-free desk top... Model **HM 4615**

HITACHI, the world leader in technology has done it again with the entirely new and innovative HM 4615 RGB Color Monitor.

New Hitachi gun and yoke technology brings a sharper focus and convergence to your picture; a new LSI for our Video Amplifier requires only one third the space of previous models making the HM 4615 extremely compact.

Square corners provide greater viewing area and  $1024 \times 800$  hi-resolution is standard with  $1280 \times 1024$  available as an option.

The Hitachi HM 4615 is economically priced, ideally suited for CAD-CAM and other desk top computer graphics systems. It carries worldwide approvals, including FCC, UL, CSA, and VDE.

For more information contact Hitachi America Ltd.

50 Prospect Avenue Tarrytown, NY 10591-4698 (914) 332-5800

950 Elm Avenue San Bruno, CA 94066 (415) 783-8400

The Image Speaks for Itself

Circle 12

# VME Packaging — The Hybricon Precedent

There's more...a lot more... than tough specifications behind Hybricon's VME/Eurocard packaging.

Hybricon approaches design objectives from a different perspective...the **user's** viewpoint. This focus has already provided users of our standard and custom Multibus, DEC and Versabus systems with a tangible competitive edge. Hybricon's comprehensive VME/ Eurocard line is made entirely in the U.S.A. Unique **practical** features are combined with Hybricon quality...quality that justifies our full **five year warranty**. Send for full information on Hybricon VME packaging systems...you'll find that we've been listening to you.

# Hybricon Gives <u>You</u> The Edge.

- Card cages (19" and custom) up to triple widths.

- Hybricon card cages accommodate all popular extractors.

- Fast and flexible custom design service.

- All popular card sizes in stock.

- All wire-wrap panels available in standard, high density, and new pin grid arrays.

- Sealed five-layer rigid backplanes.

- External power takeoffs for up to 50 amps.

- Hybricon interconnect boards allow backplane end stacking/coupling.

# Hybricon

410 Great Road Littleton, MA 01460 (617) 486-0311 TWX 710-347-0654

Circle 11

ELL US YOUR THOUGHTS Forum – your inputs help keep the magazine interesting and vital to the

**design community.** So let us know how we're doing and how we can serve you better in the future. We want to know what you like or dislike about *Digital Design*, the subjects you'd like to see us address, how you feel about the problems you face every day as design professionals.

If you have thoughts your peers should know about, put them in a letter in *Digital Design*. Have your say in *your* magazine! Send letters and comments to: Editor, *Digital Design*, 1050 Commonwealth Ave., Boston, MA 02215.

### EDITORIAL AND SALES OFFICES

DIGITAL DESIGN, 1050 Commonwealth Avenue, Boston, MA 02215, Telephone: (617) 232-5470

### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215, (617) 232-5470. Brian Rowbotham, Chairman; Ronald W. Evans, President; Charles Benz, Vice President.

### **EXPOSITIONS GROUP**

AT

CA

AT

AT

Morgan-Grampian Expositions Group, 1050 Commonwealth Avenue, Boston, MA 02215 (617) 232-EXPO. The following is a list of conferences produced by the Expositions Group:

| E West      | CADC   |  |

|-------------|--------|--|

| ADCON West  | ATE C  |  |

| E Northwest | CADC   |  |

| EEast       | Electr |  |

|             |        |  |

CADCON East ATE Central CADCON Central Electronic Imaging

14

極

In addition to DIGITAL DESIGN, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronics Test

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronics Times • What's New in Electronics • What's New in Computing • Business Computing and Communications • Communications Systems Worldwide.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral manufacturers integrating OEM's and commercial end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

**VRPA** JABP

### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach oid address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

Circulation Department, **DIGITAL DESIGN**, Berkshire Common, Pittsfield, MA 01201

Subscription rates: non-qualified subscribers (US and Canada) — \$40/yr; foreign — surface mail — \$50; air mail — \$85. Single copies — \$4.

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by Morgan-Grampian Publishing Co. for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$2.00 per copy, plus \$.25 per page is paid directly to CCC, 21 Congress St., Salem, MA 01970. 0147-9245/84 \$2.00 + \$.25.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

SEPTEMBER 1985 I DIGITAL DESIGN

· A'A .

# Panasonic **Industrial Company**

- To find out more about what's behind our compact data displays, just call or write for our complete brochure. Panasonic Industrial Company, Computer Components Division, Data Display Department, One Panasonic Way, Secaucus, NJ 07094. (201) 392-4849.

And what's in back is a tightly designed chassis that offers you a range of compact displays to meet nearly any space limitations you set. You get the reduced circuit board area you want from compacts that also feature great reliability with minimal servicing. Of course, our compacts don't sell on size alone. They offer exceptional performance along with accessible controls and uncomplicated installation. All at affordable prices. And, to ensure quality control and long life, nearly every component is manufactured by our parent company, Matsushita Electric. Whatever your requirements, we can meet

- local engineering support

- precision video circuits

- active high voltage regulation on some models

mid to super high resolution grades • 5" to 17" monochrome and 9" to 19"

color displays

15" and 17" monochrome page readers

frame-mounted, fully enclosed cabinet or

them by offering:

frameless kit

# We run with a great crowd.

# Complete hardware/software compatibility.

Talk about easy interfacing. You can take a ZETA 824 or ZETA 836 plotter and plug it into virtually any computer made.

What's more, you'll be ready to run because our plotters understand a variety of computer protocols. Select the model for your application then just plug in and plot.

In fact, we're a plug compatible replacement for many plotters from HP, CalComp and Tektronix. Some models of our plotter can even run directly from your IBM cluster controller. Now that's easy interfacing.

When it comes to your favorite application packages, you'll be on safe ground too. Packages such as CADAM, TechniCAD, Euclid, P-CAD, AutoCAD and many more.

# *The most productive plotter for the money.*

You'll be getting the highest output plotters for the money with our new ZETA 824CS and ZETA 836CS. More

mix

MANICOLE

finished plots. More productivity. Plus, these "D" and "E" format plotters let you run either single sheet or roll media.

# Easy-to-use touch controls.

Your time is valuable. So we've made our touch controls simple – yet powerful. Set speed, pen pressure, liquid ink parameters, electronic limit sensing, windowing, scaling – all at the touch of a finger, Self-test and diagnostic plots too. Let us show you dozens of other time-saving operations in a brief demonstration.

# Plotter specialists.

We've been designing hardware interfaces, plotting language emulators and high performance pen plotters for over 14 years. Nicolet also provides you with worldwide sales and service support.

Give us a call. See how easy it is to join the crowd.

Call (415) 372-7568. Nicolet Computer Graphics Division, 777 Arnold Drive, Martinez, CA 94553 TWX 910-481-5951

Computer Graphics Division

CADAM is a trademark of CADAM, Inc. TechniCAD is a trademark of Tektronix, Inc. Euclid is a trademark of MATRA DATAVISION, Inc. P-CAD is a trademark of Personal CAD Systems. AutoCAD is a trademark of Autodesk, Inc.

**Circle 18 on Reader Inquiry Card**

# EDITOR'S COMMENT

# **Open Systems Close Up**

On the surface, the concept of an open systems architecture would appear to be the panacea that all board level manufacturers and systems integrators are looking for. But what exactly is an open systems architecture? My definition includes the following two points. First, the specifications for building to a particular system should be publically available. Second, no license fee or royalties should be imposed on either manufacturers or end users to build a product to meet that specification.

Those companies that do not support these two points are committing marketing suicide by alienating both third party vendors who may actually widen a customer base anyway and, worse still, the OEM who may perceive that legal wrangling and letters from faceless lawyers are something that they would rather not deal with – opting for alternative solutions instead.

Open systems architectures are a good idea. They should, theoretically, allow a vendor to mix and match a variety of products to configure a system. Unfortunately, some open systems architectures may be only partially open. Or, they may start out open, then close. For example, take Pro-Log's new multimaster scheme for the STD bus. A good idea, no doubt, but the scheme is patented and, at the time of writing, no other vendor can build product to the scheme. Good for Pro-Log. Bad for the systems integrator.

Intel also has created unnecessary paperwork by charging a one time fee for builders of Multibus I and II boards in order to protect their patent rights. It might be a good mechanism to find out where their competition is, but what other good does it do?

Digital Equipment Corp. recently entered the fray with a law suit against Emulex of Costa Mesa, CA. DEC seeks an injunction against further marketing, manufacturing, selling and distribution of Emulex's disk controllers that use DEC's MSCP (mass storage control protocol) or that plug into DEC's SBI, CMI, Unibus and Q-Bus for its VAX, MicroVAX and PDP-11 computer systems. DEC claims that Emulex has infringed its patents and seeks treble damages.

In an open reply, Emulex chairman Fred Cox said that he believes that the industry will be chagrined by DEC's intent to limit its competition in the add-on market by obtaining patents apparently intended for this specific purpose. I agree with Mr. Cox. Depriving OEMs of the opportunity to enhance their DEC systems with more cost-effective peripherals offered by other vendors is not in the best interests of anyone in the industry – even DEC.

Meanwhile, over in the VME camp, vendors and customers are having no such problems with license fees, letters from corporate lawyers or lawsuits. As a result, the VME vendors may be integrating all the way to the bank with a lot of their competitor's business. One can only wish them the best of luck.

### - Dave Wilson, Executive Editor

1

# OBIGFORIDEA WGTIZER?

Now you can put together a system that's big enough to fit even the biggest ideas. Introducing the MM 1812 from Summagraphics.

This latest addition to our long line of digitizers has a full 18" x 12" active area to give architects, PCB designers and mechanical engineers all the room they need to construct large-scale plans. In fact, the 1812 can handle the A-3 size paper used by many European businesses.

All electronics on the 1812 are contained on a singleprinted circuit grid to insure repeatable, reliable, precise performance. Electromagnetic technology provides the user with selectable resolution up to 1016 lines per inch. There's even a choice of three input devices. A four-button cursor, three-button "mouse-like" cursor, or the fingertip control offered by a new, high reliability stylus.

Plus, the 1812 is compatible with other Summagraphics RS-232-C Universal Input Output Format tablets like Summagrid,<sup>™</sup> Supergrid <sup>™</sup> and Microgrid.<sup>™</sup>

Now you can be sure there'll be enough room to draw on, when you draw on the MM 1812. From Summagraphics. The first name in digitizers.

For more information contact Summagraphics Corporation, 777 State Street Extension, P.O. Box 781, Fairfield, CT 06430. Telephone: (203) 384-1344. Telex: 96-43-48. European Sales Office, Newbury, England. Telephone: 0635-32257.

Summachaphics

F

Draw on our experience.

Summagrid, Supergrid and Microgrid are trademarks of Summagraphics Corporation.

# HOTLINE

3

()re

2

R

<u>GaAs DEVICES MOVE TO LSI-LEVELS OF INTEGRATION</u> The last quarter of this year will find Gigabit Logic (Newbury Park, CA) introducing a 1 Kbit GaAs SRAM, and Vitesse Electronics (Camarillo, CA) announcing GaAs multipliers and A/D flash converters; Triquint Semiconductor (Beaverton, OR) plans to introduce a 500-2000 gate array family.

<u>APOLLO OFFERS OPEN-ARCHITECTURE COMMUNICATIONS PROGRAM</u> Apollo Computer (Chelmsford, MA) has announced a set of communications links to extend the DOMAIN system's resource sharing architecture. The links, available for IBM's SNA computers, IBM's personal computers (and hardware compatibles) and DEC's VAX computers, allow transparent access to data and resources from a DOMAIN system.

LARGE AREA, FLEXIBLE, 0.015" THICK LCD A flexible plastic LCD material has been introduced by Polaroid (Cambridge, MA). The lightweight, 0.015" thick material can be custom produced up to 16" wide and in virtually unlimited length for computer displays.

20,000-GATE GATE ARRAY IN 1.25-MICRON GEOMETRY Honeywell's Digital Product Center (Colorado Springs, CO) will market a 20,000-gate CMOS gate array. The part was developed by ETA Systems for the ETA-10 supercomputer, which is planned for delivery in 1986.

<u>ALTERNATE SOURCE AGREEMENTS FOR ASICS</u> Motorola (Phoenix, AZ) and NCR (Dayton, OH) have signed a co-development and alternate source agreement that includes both CMOS gate arrays and standard cells.

<u>SIX-CHIP IMAGING SYSTEM</u> Sharp Corp. (Paramus, NJ) has announced a complete color imaging system based on five ICs. Based on a 386  $\times$  488 CCD, the four support chips include a color signal separator, clock generators and clock drivers which provide direct RGB output. Sony (Paramus, NJ) will also debut a single-chip color CCD sensor soon.

<u>HIGH FIDELITY FRAME GRABBER</u> Shintron (Cambridge, MA) has introduced a color  $768 \times 505 \times 8$ -bit frame grabber for image processing. Features include a high 13.5 MHz sampling rate, in-built timebase correction and, later this year, a MicroVAX II interface.

<u>DEVELOPMENT TOOLS FOR THE 80C51</u> Oki Semiconductor (Sunnyvale, CA) has introduced a set of development tools for the 80C51 intended for use on personal computers. A VAX version of the set will be available soon.

COLOR PALETTE AND CONVERTERS COMBINE ON VIDEO DAC Brooktree (San Diego, CA) has announced a triple 4-bit D/A converter with on-board RAM that operates at a conversion speed of 125 MHz. The BT451 features an on-board multiplexer.

<u>WORLD'S LARGEST CCD AREA ARRAY IMAGER</u> Tektronix (Beaverton, OR) has announced a 2048  $\times$  2048 CCD area array designated the TK2048M with a dark current of 10 nA/cm<sup>2</sup> and a charge transfer efficiency of greater than 0.99999.

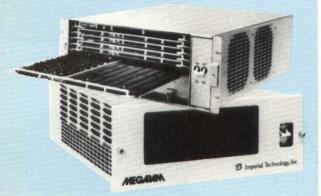

HARDWARE FOR INTERACTIVE WARPING Megavision (Santa Barbara, CA) has demonstrated the PDF processor for interactive warping on the 1024XM. The processor is an optional feature to the 1024 image processor which allows global and recursive computations to be offloaded from the 1024.

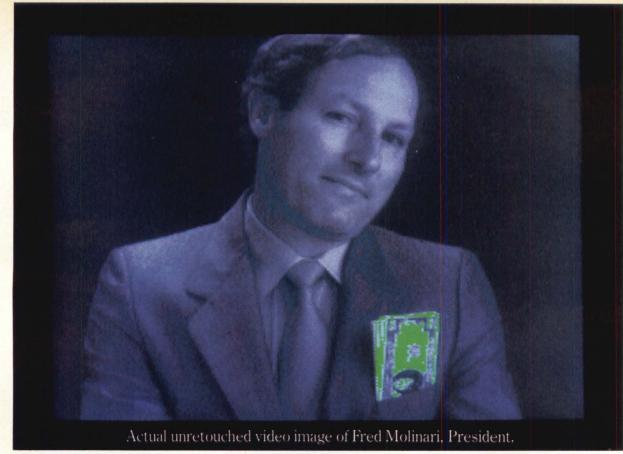

# "It's easy to spot the difference between our IBM PC-based frame grabber and the others."

High performance and affordable cost, just \$1495 for a single plug-in board.

LUT's

Unlike other video I/O systems, the new DT2803 provides real-time image capture capabilities, digitizing a 6-bit video field every 1/30 second. An on-board, memory-mapped, dual-ported frame store memory (256  $\times$  $256 \times 8$ ) makes it ideal for the IBM PC's 64K buffer size. And for real number crunching,

the DT2803's external ports interface to high speed co-processors.

With our software package, VIDEOLAB,<sup>™</sup> the DT2803 is easy to use for image operations like averages, histograms, and convolutions.

So, if your application is manufacturing/automatic inspection, robotics, or medical research,

False Color

**SPECIFICATIONS: DT2803** A/D Input RS-170 (CCIRR), 6-bits at 5MHz Frame Grab 1/30 (1/25) second per field 8, 64 × 8 input; 4, 256 × 12 output D/A Output 64 colors × 64 intensities, R-G-B; 64 grey levels, monochrome Frame Memory  $256 \times 256 \times 8$  (2-bits for graphic overlays)

Call for our new 576 pg. catalog/ our new high perhandbook or see it in Gold Book 1985. formance video I/O

board will really open your eyes-at an unbeatable price.

Call (617) 481-3700

World Headquarters: Data Translation, Inc., 100 Locke Dr., Marlboro, MA 01752 (617) 481-3700 TIx 951 646. European Headquarters: Data Translation, Ltd., 13 The Business Centre, Molly Millars Lane, Wokingham Berks, RG112QZ, England TIx: 851849862 (#D) In Canada: (416) 625-1907 IBM PC is a registered trademark of IBM. VIDEOLAB is a registered trademark of Data Translation, Inc.

# **TECHNOLOGY TRENDS**

## SOFTWARE

.

# CAE Techniques Migrate To Software Engineering

Computer-aided engineering has become standard for hardware designers. But software engineers, for the most part, have not been able to take advantage of CAE. Conventional tools no longer provide effective support for developing complex systems, and the conventional process has become inefficient due to time-to-market concerns.

Several companies have manufactured software development systems, combining editors, compilers and debuggers into one package. For example, Promod's (Laguna Hills, CA) ProMod engineering environment operates independently of the target system and language. The environment aids structural analysis, system and program design by automatically creating program modules and checking highlevel interface descriptions. It prepares documentation and cross-referenced lists for data, data types and functions.

The Language Development System (LANDS) from Tektronix (Beaverton, OR), part of the company's CAE 2000 workstation product family, is a development toolkit for Pascal and C and popular target processors. A Language Directed Editor intercepts syntax errors in the source file during the editing session. Software configuration and interfaces for prototype hardware, such as low-level code generation and hardware initialization reset, are handled by a tool called the 3 Integration Control System. The LANDS debugger allows debug operations to be performed at the compiler source level during real-time program execution.

Both of these software development systems are available for the VAX; Pro-Mod runs on the IBM PC/XT/AT as well. According to Dave Sharon, marketing manager for software design tools at Tektronix, maintaining a consistent approach, as well as consistent compo-

nents for such tools, is important. Supporting multiple languages on systems such as LANDS will result not only in higher productivity and reliability, but also in a faster language learning curve for programmers.

On the other hand, Rational (Mountain View, CA) has introduced the Rational R1000 Development System, a specialpurpose hardware and software system designed to develop and to maintain large, complex software written in Ada. The R1000 is a universal host with a validated DOD compiler. Like the interactive support provided by CAD/CAM systems for circuit design, the R1000 offers incremental checking of software code for error detection and correction.

A core editor, through an Ada-like command language, invokes compilers, debuggers and object editors similar to an operating system. The difference is that the core editor can automatically sense and switch modes within the next layer of tools. The object editors provide semantic and syntactic checking, correction and completion.

A database directory containing information such as variables and data types of previously compiled programs enables incremental compilation on the R1000. This facility makes recompilation of entire programs after new edits unnecessary; only new additions to the program must be compiled during debugging. Changing pointers in the directory allows new program patches to be spliced into the old program. A software management tool tracks subsystem interfaces for

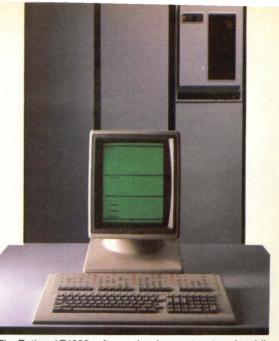

The Rational R1000 software development system, in addition to a specialized processor, has a full-screen, multiple window terminal.

later linkage.

Rational's design of the R1000 processor is a departure from other software development tools. The processor's architecture is optimized for traversing large data structures, making the machine essentially a specialized Ada engine. A 128-bit CPU splits control words so that type checking and addition are performed simultaneously instead of serially. Virtual memory is handled at the microcode and hardware level, rather than by the operating system. In addition, data packing and unpacking also occurs at the hardware level.

The success of the Rational system may depend more on whether companies using Ada believe that the \$595,000 list price is worth the added hardware and software features. With the refinement of Ada compilers for computers such as the VAX, companies may decide to forego the expense of the R1000 in favor of previously invested work, time and money on those computers. In addition, back-end compilers to tailor code to different microprocessors do not yet exist for the system.

The availability of the R1000 and software development tools such as ProMod and LANDS indicates that software engineers are finally able to take advantage of CAE to ease software development during complicated programming efforts. The built-in intelligence of these tools allows software developers to concentrate more on programming and less on paperwork.

-Meng

1. High Speed (MicroCAD Software)

2. Dual Display Modes (Energraphics Software)

3. Simplified Processing (AutoCAD Software)

4. 9 Bit Planes (Courtesy WSI Inc., Bedford, MA)

5. 16.8M Color Shades (Courtesy Catherine Del Tito, Wave Graphics)

4

High Resolution (Courtesy University of North Carolina at Chapel Hill, Depts of Computer Science and Radiology)

# Six reasons why professionals continue to choose Vectrix for quality IBM XT/PC graphics.

Even though IBM offers a color graphics card, professionals still choose Vectrix. It's not surprising. Especially once they've seen us in action. Professionals know that our VX/PC Board Set delivers the quality and performance they need for serious color graphics.

The VX/PC Board Set provides advanced features that help simplify sophisticated graphics design. Besides displaying 512 simultaneous colors from a palette of 16.8 million, the VX/PC supports an extensive library of on-board graphics macros for ease of programming and fast design, as well as full emulation of the IBM color card. And, an on-board 16-bit microprocessor frees your computer to concentrate on other tasks.

But that's not all. Our 9 bit planes

add an extra dimension of sharpness and clarity to your image that must really be seen to be appreciated. That's why it's not surprising to see Vectrix color cards in applications such as medical imaging, weather satellite data mapping, computer aided design and drafting, and graphics arts, to name a few. What you will find most surprising, however, is the price. Our VX/PC Board Set was designed with the OEM

in mind. So when comparing the performance of Vectrix with the competition, check the price too. You'll like what you see. For more information, contact Vectrix Corporation, 2606

Branchwood Drive, Greensboro, North Carolina 27408. Phone (919) 288-0520. Telex 574417.

Distributor inquiries welcome. Inquire about our new Pepe Graphics Board Set

Seeking distributor(s) in Germany and Austria

IBM XT, IBM AT, and IBM PC are trademarks of International Business Machines Corporation, White Plains, NY. MicroCAD is a trademark of Imagimedia Technologies, Inc., San Francisco, CA.

AutoCAD is a trademark of AutoDesk, Inc., Sausalito, CA. EnerGraphics is a trademark of Enertronics Research, Inc., St. Louis, MO.

# **TECHNOLOGY TRENDS**

### SYSTEMS

# **UNIX And 68020** Team Up On CPU Designs

C ince its introduction, the Motorola **2**68020 has been one of the more widely accepted 32-bit microprocessors. Recently, a range of boards and systems have been introduced. Motorola was the first, announcing its VME131 board. Since then, it has been joined by Charles River Data Systems (Framingham, MA) with its Universe 32 system and associated 68020 Versabus board, Dual Systems (Berkeley, CA) with its VMPU-32 module, Ironics (Ithaca, NY) with the IV-3201 VME CPU board and the Multibus-based MAP-2000 from Matrox (Quebec, Canada). Force Computer (Los Gatos, CA), has a 68020 board that will be announced next month. Most companies have taken full advan-

tage of the VLSI devices offered by Motorola. In addition to the 68020, many manufacturers have elected to use the MMB memory management unit (until the 68851 is in full production) and the 68881 floating point unit. In most cases, vendors offer 12 MHz versions of the 68020. Although some claim to offer 16 MHz devices, the faster part is not yet

widely available and supplies of products based on it are limited.

Even though some vendors are distinguishing their product by the processor's raw clock speed (16 MHz vs. 12 MHz), system software, operating systems and compilers actually dictate system performance. UNIX, for example, is already offered by many vendors who support or plan to support it in the near future. Which version they choose and how their hardware supports the operating system is open to a number of different interpre-

tations. AT&T's System V 2.2 enjoys a number of advantages over the earlier

System V 2.0. The swappingbased memory manager has been replaced by a demand-paged memory manager. Paging allows fuller use of existing hardware by allowing execution of programs much larger than the main memory and gives a higher degree of multiprogramming.

Bucking the popular trend to use Motorola's MMB, Charles River Data Systems has elected to design its own segmented memory management unit rather than a demand-paged memory management unit. Its Universe 32 is currently supported by the company's own version of AT&T's System V, called UN/System V or UNOS, a UNIX-compatible realtime operating system kernel. In 1986 the company plans to offer an operating system to support demand-paged virtual memory management.

Similarly, Motorola (Tempe, AZ) whose VME CPU board includes the MMB will not have UNIX V 2.2 on a system product until the end of March 1986. However, its first UNIX port (a swapping port) will be released in two months.

Dual Systems, whose plans also include UNIX V Version 2.2, is planning to commence full production of its VME line later this year. The new modules include a 68020 CPU board, a system controller/arbiter, a 2 Mbyte memory board, an I/O processor, a tape controller and an SMD disk controller.

Although the UNIX operating system

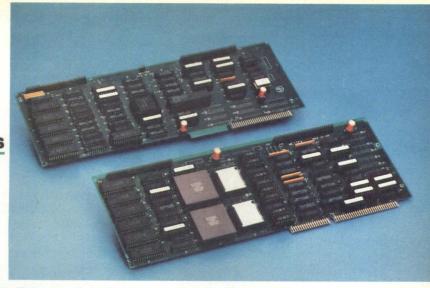

A number of vendors now offer 68020-based

CPU boards. In many designs, manufacturers have used Motorola's MMB for page memory management until the 68851 single-chip MMU becomes available (Photo courtesy Dual Systems).

is being ported to many of the newer 68020 designs, many applications have more typically demanded a real-time operating system like PDOS or OS/9 that does not have UNIX's overhead.

Clearly, those systems that do support UNIX (Version 2.2 or Berkeley 4.2) are targeted towards the development environment in which tools such as compilers demand larger memory sizes. Of the other 68020 systems that have been announced, Altos Computer Systems (San Jose, CA) claims its 3086 machine will support System V 2.2 starting this month. NCR (Dayton, OH) will also begin shipping its Tower 3232, which supports System V 2, in October. With all of this design activity surrounding the 68020, plenty of hardware is at last available. Software support; however, still appears to be somewhat lacking.

-D. Wilson

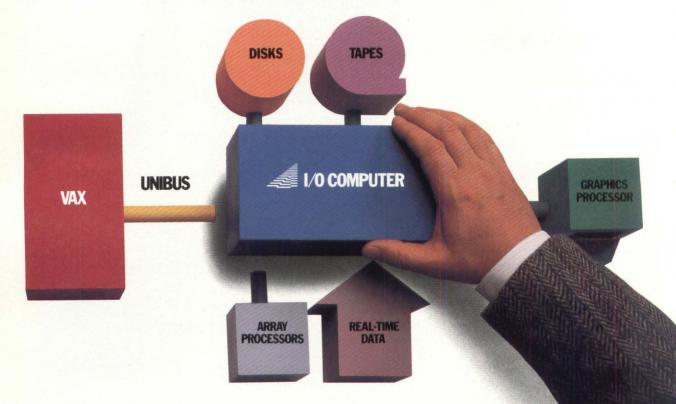

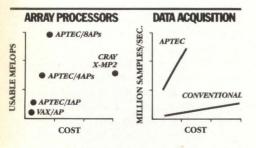

# THE MOST SIGNIFICANT BREAKTHROUGH IN VAX SYSTEM PERFORMANCE SINCE THE ARRAY PROCESSOR.

Introducing the Aptec 2400 I/O Computer – a new *class* of computer that can increase the throughput of VAX-based systems as much as 40X. Simply. And economically.

By eliminating the I/O bottlenecks that limit performance, the Aptec I/O Computer makes your peripherals work faster and more efficiently. Including disks and tapes, APs, graphics/image processors, and special purpose devices.

It lets you achieve true supercomputer performance with any VAX by allowing efficient integration of multiple array processors.

And, the Aptec I/O Computer permits dramatic new levels of performance in real-time data acquisition and analysis.

Not since the array processor has any development done so much to boost the performance of minicomputer systems.

Here's how it works: The Aptec I/O Computer creates an independent, 24 MB/sec, FILES-11 I/O environment that allows VAXshared peripherals to transfer data at full speed, free from VAX bandwidth limitations.

From 1 to 200 MB of high speed memory is directly accessible by your attached peripherals and VAX.

And, the Aptec I/O Computer provides the intelligence to control peripherals, data transfers and peripheral computations – with minimal involvement of the VAX CPU, the VMS operating system or the Unibus.

Circle 69 on Reader Inquiry Card

Peripheral operations become more efficient. Attached processors work at peak efficiency. And your VAX is free to provide better service to your on-line users.

Learn how the Aptec 2400 I/O Computer can unleash the performance potential of your VAX system. For the complete story on this exciting new class of computer, write or call Aptec today.

**IPTEC**

YSTEMS

Aptec Computer Systems, Inc. 10180 SW. Nimbus Ave. Portland, OR 97223 (503) 620-9840 Telex 467167

VAX, Unibus and FILES-11 are registered trademarks of Digital Equipment Corp. © Copyright 1985 Aptec Computer Systems, Inc.

### **TECHNOLOGY TRENDS**

### \* IMAGING

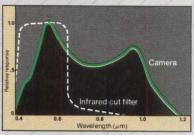

# Image Processing Tools For Personal Computers

Decreasing costs of semiconductor memory coupled with advances in VLSI processors has led to a proliferation of imaging products. Many of these, based on the IBM and other personal computers, will be on display next month at the 1985 Electronic Imaging Conference and Exhibition (p. 50). Indeed, the market potential of such systems is leading both start-up and established imaging companies to introduce a greater variety of products in the area of image processing.

NCR Corp. (Fort Collins, CO) will introduce a development system for the company's Geometric Arithmetic Parallel Processor (GAPP) chip (*Electronic Imaging*, January 1985, p. 66). The GAPP PC development system is composed of two parts. The first is a hardware board compatible with the IBM PC I/O bus. It contains a  $12 \times 12$  array of processor elements implemented with two GAPP devices. The second part is a software package which allows the user to program the GAPP array in a high-level language and to debug a program interactively.

The GAPP Simulator/Assembler package is composed of two utilities which operate under the UNIX or VAX/ VMS operating systems. The first utility is the assembler, GAPASM, which translates GAPP instruction mnemonics and address specifications into binary object code suitable for downloading into a control state. The simulator, GAPSIM, is an interactive package that enables the user to execute GAPP programs and to view the contents of GAPP RAM and the state of the processor element registers in order to verify or debug the program. At Ariel Corp. (New York, NY) another IBM PC peripheral has been introduced to perform Fast Fourier Transforms (FFTs). Plugging into expansion slots of the IBM PC/XT/AT, the PCFFT board performs FFTs using routines callable in either interpreted or compiled Basic, IBM Pascal or Fortran, Lattice C or Turbo Pascal. Operating on 16-bit integer data, the PCFFT transforms arrays of up to 2048 complex points in less than 20 msec. Other standard algorithms include forward and inverse FFTs, Hamming Windows and Power Spectral Density functions.

In the past, one of the limiting factors of such hardware has been the lack of software that can easily be used to generate image processing routines. Now, two companies have introduced packages which allow image processing functions to be generated rapidly.

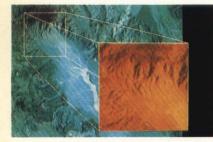

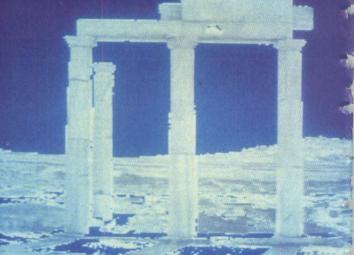

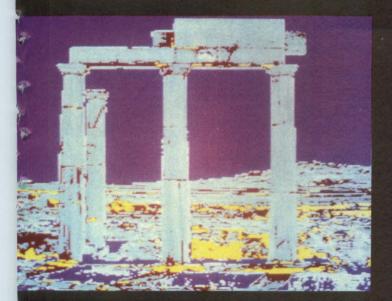

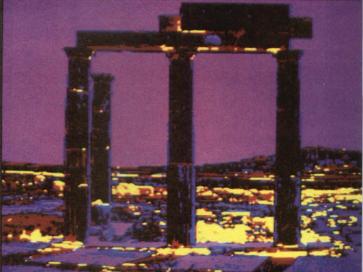

The first, from Quantitative Technology Corp. (Beaverton, OR) is called the Math Advantage (p. 57) and consists of a set of computationally intensive routines which can be linked together to perform many scientific functions. Running on over 20 types of computers, the 180 routines can be called from the user's program in either C or Fortran. In a typical image processing environment, an edge enhancement program can be realized in approximately 20 lines of code as opposed to the 150-200 lines of Fortran that Infrared LANDSAT images of Los Angeles, illustrating a multiple thresholding operation assigning four colors to represent the 40 grey levels of data. The second image assigns green to the same data while the last image is a modified subtraction of the first two images to detail mountains, freeways and shallow water areas.

would normally be needed.

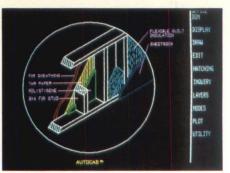

The Picture Database Management System, PICDMS III, from MIB Chock (Santa Monica, CA) can be used with PC-DOS systems for image processing and model building in either two or three dimensions. In a similar manner to the QTC system, the PICDMS gives the systems integrator a simplified way of defining a variety of operations on a picture database. Examples of possible operations include the detection of objects or edges of objects, contrast sharpening, pattern recognition and classification, histograms and statistical analysis. First shown at the 1985 SIGGRAPH show, the PICDMS II currently runs under CP/M on the Apple II+ as well as MS-DOS. The MS-DOS version can be supplied with either color or character graphics. PICDMS III requires an additional PL/1 compiler to implement the programs that it generates.

-A. Wilson

# **Our new CRTs** are quite a handful.

# Introducing Litton's 1" tube.

Now let's see. What could you use a miniature CRT for?

How about a helmet-mounted display.

A compact film recorder.

A hybrid typesetter.

Or a compact display inside a crowded tank.

Litton's L-4272 cathode ray tube is the newest sub-miniature on the market.

And one of the best.

It's made by the leader of high resolution, high precision CRT's. Litton's reliable CRT products have been used in everything from advanced reconnaissance systems to sophisticated photocomposition machines.

The L-4272 is ruggedized, so it'll survive inside a tank, an aircraft or any

vehicle using forward-looking infrared systems.

And it's a high performer. Spot size is 0.0008 inch. Brightness is 100 footlamberts with standard 525 line TV raster at 30 Hz filling the useful screen.

You can buy it as a stand-alone item or with a small coil and magnetic shield.

To get the small picture, contact Litton Electron Devices Division, 1215 S. 52nd Street, Tempe, AZ 85283. Phone (602) 968-4471. TWX: 910-950-0149.

Litton Electron Devices

Circle 48

# **Emerges With Silicon, Standards**

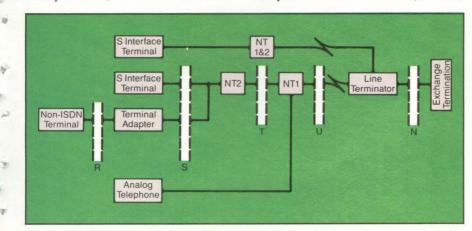

n all-digital communication network may be some time off, but as international standards are set, some IC manufacturers are ready to produce products. Specifications for parts of the Integrated Services Digital Network (ISDN) are already firm, and others are well underway in the CCITT. The ISDN reference model encompasses three main interfaces defined in the reference model: S, T and U and secondary R and N interfaces, as shown in Figure 1.

2

4

At present, most of the silicon development is for the S interface to the terminal equipment and for the U interface to the network. Specifications for the U interface are not complete, but Mitel (Kanata, Ontario, Canada), Harris Semiconductor (Ft. Lauderdale, FL) and Intel (Santa Clara, CA) have U interface ICs in development. AMD (Sunnyvale, CA) and Intel are developing chips for the S interface.

The U interface description has been widely debated; whether to use a two-

wire or a four-wire scheme is the main question. Four-wire cabling is used for the S interface, so having both S and U be four-wire would improve portability. And although most current telephone connections use 2-wire lines, cross talk is a problem. To solve that problem, an echocancellation technique will become standard. Intel, Harris and Mitel digital line interface transceiver ICs all employ echocancelling.

Data rates of up to 160 Kbits/sec can be achieved with the transceiver ICs; this is the Basic Rate for ISDN service. Channels within this bandwidth are two 64 Kbit/sec B channels for transmission and a D channel for control (commonly called 2B + D). A broadband Primary Service is also proposed in current ISDN documents for a T1 equivalent at 1.544 Mbits/sec. This would provide users 23 B channels and a 64 Kbit/sec D channel.

ICs for the S interface from both AMD and Intel are scheduled for introduction this year. Others like Motorola (Phoenix,

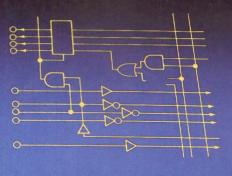

Figure 1: The ISDN scheme for transmitting a variety of video, data and voice services includes three major points of interface where silicon will aid development: S, T and U. The R is used only to interface non-ISDN terminals to a terminal adapter at the S interface and N is part of the network rather than the subscriber equipment.

DIGITAL DESIGN SEPTEMBER 1985

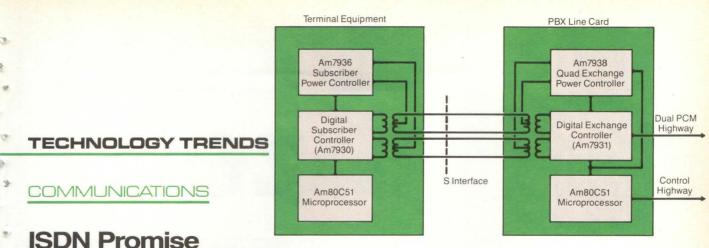

Figure 2: AMD's ISDN products are highly integrated, to allow easy implementation of both the terminal and the PBX equipment needed for ISDN compatibility. Power controllers are bipolar and subscriber and exchange controllers are CMOS.

AZ) will produce S chips in the future. S interfaces between the user equipment and the customer-premises switch, so these ICs will be used in PBX, terminal and digital telephone systems implementing ISDN. Up to eight terminal devices can be connected to one S interface; one which is used as master.

The most highly integrated S interface proposed, AMD's Am79C30 digital subscriber controller includes codec, transceiver, tone generator and formatter functions. In most other ISDN implementations, three or four ICs will be used for these functions. A companion IC for the PBX line card, the Am79C31 digital exchange controller terminates the fourwire line from each 73C30. In addition to these CMOS parts, AMD is introducing bipolar power controllers for ISDN telephones (Am7936) and exchanges (Am7938). These four ICs, the 79C30 and 7936 on the terminal or phone side, the 79C31 and 7938 on the PBX side and a microprocessor (Intel 80C51 is suggested) on each side (Figure 2) can implement a basic S interface.

Intel ISDN ICs will be designated the 29C53 for the four-wire S interface and the 29C55 for two-wire ISDN U circuits. High-voltage power circuits are not available with Intel's technology, however. Two Intel products already in production, the 29C51 programmable feature-control combo and the 2952 line card controller are designed to operate on a PBX line card and will accommodate ISDN. Called a subscriber line data link (SLD) architecture, this scheme requires three wires. -Pingry An advanced SCSI 3½-inch Winchester Disk Controller...

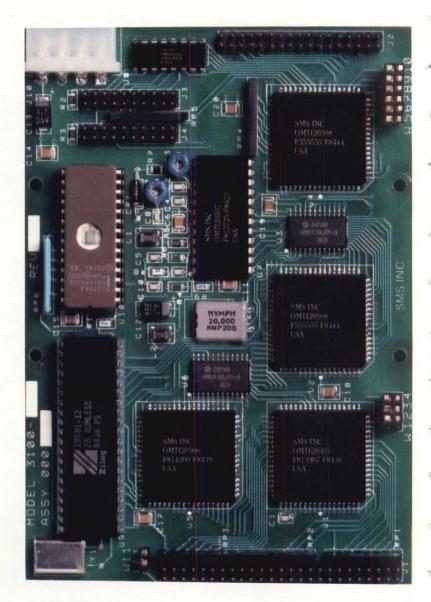

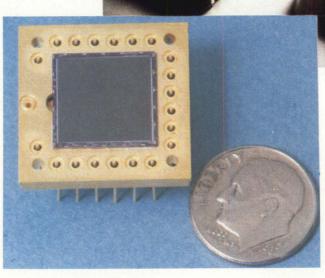

# Introducing the OMTI 3100

The OMTI 3100 SCSI Intelligent Winchester Disk Controller is designed to attach up to two drives on a 3½-inch footprint PC board to the SCSI (Small Computer System Interface) bus.

The OMTI 3100 supports the industry standard ST506/412 disk drive interface for 3½-inch and 5¼-inch Winchester disks.

The host interface is the popular SCSI bus which connects through host adapters to a wide variety of system architectures for mini and micro computers. SCSI includes a high level command set which protects system software from changes as future generations of disk drives are added to the I/O configuration.

The OMTI 3100 uses our advanced VLSI chip set to implement the most compact SCSI to ST412 disk controller available today. Only ten IC's are used on the OMTI 3100 and six of the ten are proprietary to SMS.

The OMTI 3100 controller provides consecutive sector (or non-interleaved) data transfer and multisector buffering (2Kbytes) between host and peripherals. It transfers a full track in one single disk revolution and transfers data on the SCSI bus at up to 1.2 Megabyte per second.

To find out more about the little hard disk controller that offers OEM's a big performance advantage, call SMS.

The advanced OMTI 3100 is one of many finely engineered SMS components. Scientific Micro Systems, Inc. manufactures a wide range of disk and tape controllers for SCSI, PC/XT and AT compatibles, Multibus\*, Q-bus and Unibus\*\* configurations.

# Actual Size

339 North Bernardo Avenue P.O. Box 7777 Mountain View, CA 94039 (415) 964-5700 TWX 910-379-6577 TELEX 17-2555

SALES OFFICES: Seattle, WA (206) 883-8303; Boston, MA (617) 246-2540; Atlanta, GA (404) 296-2029; Morton Grove, IL (312) 966-2711; Melrose Park, IL (312) 345-5320; Arlington, TX (817) 429-8527; Laguna Hills, CA (714) 643-8046; Greensboro, NC (919) 292-8072; Mountain View, CA (415) 964-5700; Philadelphia, PA (215) 860-8626. DISTRIBUTORS: United States-Arrow Electronics, Inc. (516) 694-6800; Canada-Allan Crawford Associates Ltd. (416) 890-2010 \* Trademark of Intel Corporation \*\* Trademark of Digital Equipment Corporation

# **TECHNOLOGY TRENDS**

DESIGN TOOLS

# Analog And Digital Accelerators Speed Simulation

Verifying whether a design functions properly is among the most costly and time-consuming stages of the design cycle. This is especially apparent with analog circuits and large digital systems. Logic simulators and analog simulators, such as SPICE, running on mainframes provide an alternative to breadboarding,

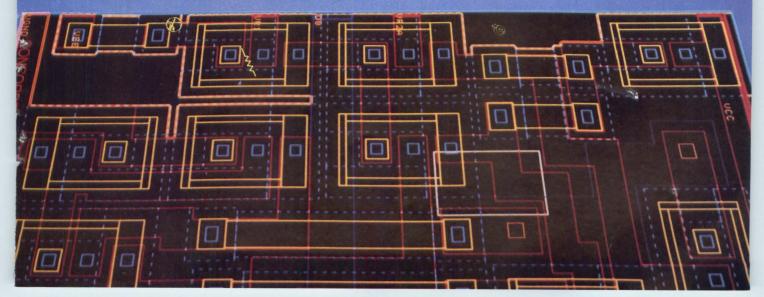

Figure 1: Shiva Multisystems' SX Series SPICE accelerators execute simulations at speeds ranging from 20 to 100 times faster than a VAX 11/780. The machines' performance is a result of PowerSPICE, a relaxation-based SPICE algorithm, and SPICEngine, a parallel processing number crunching computer. To the circuit designer, the PowerSPICE interface appears identical to traditional SPICE programs. but even mainframes get bogged down with large designs. This has prompted the development of hardware accelerators for both analog simulation and digital simulation.