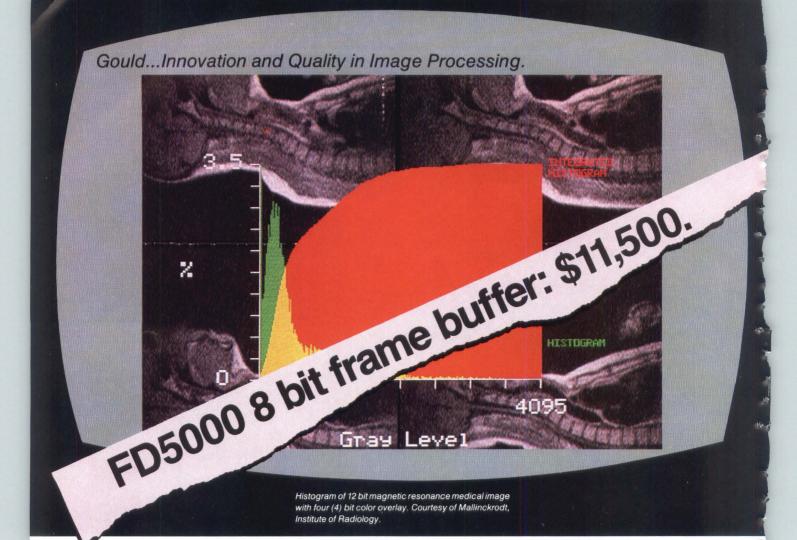

Gould's FD5000 Image Processor Introduces a Whole New Idea:

### Performance and Economy.

An image processor can be expensive.

Unless it's the FD5000. For \$11,500, you can purchase an 8 bit frame buffer with driver software. And the system doesn't stop there. As your needs expand, so will the FD5000 to a full 32 bit image processing system for advanced applications.

Check these basic and optional features:

#### Flexible Architecture:

Two 12 bit deep images or three 8 bit images with 4 bits of color or monochrome overlay provide monochrome, pseudocolor, and true color.

#### 60Hz Flicker-Free Display:

Bright, flicker-free image display at 60Hz; 30Hz for image processing and real time input.

#### Feedback Processor:

Five times faster than host-based operations for convolutions, digital filtering, interactive math, regions of interest, and recursive filtering.

#### 1024<sup>2</sup> × 32 Bit Memory Arrays:

Optional memory configuration provides user choice of image size and processing precision to display through 512<sup>2</sup> viewport.

#### MINI-LIPS Image Processing Software:

Interactive keyboard control; prompts for filters, real-time math, Look-Up Tables, histograms, geometric operations, utilities, and image storage; demo programs include source code.

#### The Closer Look:

The FD5000 will minimize the load on your host CPU and your processing staff. Peripheral or stand alone configurations are available.

#### Give Us A Call:

We'll be happy to discuss your application needs and the FD5000 at your convenience.

#### Gould Inc., Imaging and Graphics Division

46360 Fremont Boulevard, Fremont, CA 94538 USA Telephone (408) 263-7155 • TWX (910) 338-7656

#### European Headquarters Tegernseer Landstrasse 161,

D-8000 Munchen 90, West Germany Telephone (089) 6-92-79-06 Telex 5218078-GOUI D

## Our new 128 Family gives your computer 20/20 vision.

Introducing the first family of frame grabbers: The Datacube 128 Family of full function, single boards for real-time image acquisition and color display.

Our new IVG-128, for example, instantly turns any IBM PC into an economical, multi-feature image processing system.

Our VVG-128 double high Eurocard for the VMEbus tames the harshest machine vision and inspection environments.

While our VG-128 for the Multibus and iLBX bus provides on-board arbitration logic for fast video data transfers between two host CPUs.

Each 128 Family board provides reliable, real-time digital video for machine vision inspection, teleconferencing, medical imaging, surveillance, and many other applications.

And each Datacube 128 Family board bears a striking family resemblance to each other.

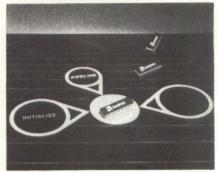

The  $384H \times 512V \times 8$ -bit frame store's throughput rate matches solid state CCD camera outputs exactly. Enhanced video input phase lock loop for rock-steady picture stability.

Digitizing, storage and display for one high-resolution image or two medium resolution images under software control.

And the ability to lock three boards together for true color RGB applications.

Each 128 Family board also gives you 7.16 MHz 8-bit digitization. Multiple banks of input and output look-up tables. And red, green and blue outputs.

All as standard features. All on a single board. And all for an incredible grabber of a price. Just \$2,995.

To get your new 128 Family album of products, write: Datacube Incorporated, 4 Dearborn Road, Peabody, MA 01960. Or call (617) 535-6644 today. Western Sales Office: Tel. (408) 737-9978.

DALAGABE

Circle 4

# Sorry, Intel. You missed the bus.

Critical decisions for the likes of nextgeneration factory and office automation systems couldn't wait for the arrival of what would turn out to be merely a muchpatched, already-dead-end bus structure. Wouldn't wait. Not when VMEbusbased products were readily available helping advanced 8/16/32-bit systems to hit the market. Running. Reliably. Without the risk of obsolescense. Compare. Then get up and go with VMEbus.

#### **BUS COMPARISON**

|                  | ISSUE                                                | VMEsystem                                                                                                                                                                                                                                                                                                                                                                                                            | MULTIBUS® II                                                                                                                                                                                                                        | COMMENTARY                                                                                                                                                                                |

|------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| al issues        | Specification Quality,<br>Stability, Standardization | VMEbus spec available since 1981. Rev. C is a<br>standard of clarity for the industry, very stable,<br>and available now. VMXbus Rev. B available now;<br>VMSbus completely specified, with Rev. B avail-<br>able in July 85.<br>IEEE P1014 and IEC 47B committees have<br>completed their work. Final approval expected<br>later this year. VMXbus and VMSbus have been<br>proposed to the IEC for standardization. | Various bus specifications available in draft form<br>since late 1983. Complete draft has never been<br>published for serial bus, ISSB **.<br>IEEE Committee began work on Multibus* II in<br>1984. No known submission yet to IEC. | VMEbus IEEE activity represents the first time<br>that the IEEE requested a committee be formed<br>to standardize a microcomputer bus structure.                                          |

| Commercia        | Proprietary Constraints                              | Nonel                                                                                                                                                                                                                                                                                                                                                                                                                | Intel trademarks: iLBX, IPSB, ISBX, ISSB,<br>Multibus*, Multichannel<br>Intel patents: pending on Multibus* II I<br>Copyrights: entire Multibus* II spec document<br>Licensing: by Intel, with fee required.                        | VMEsystem totally free of patent, trademark,<br>copyright, and trade secret restrictions. It is truly<br>an open system, with unimpeded public access.                                    |

| Com              | Number of Vendors and<br>Compatible Products         | Over 150 announced VME vendors with over 700<br>compatible products, encompassing boards,<br>systems, packaging, and software.                                                                                                                                                                                                                                                                                       | Less than 10 vendors with announced products.<br>Intel is the only <i>major</i> vendor with board-level<br>products. (Three Intel board designs announced.)                                                                         | VMEbus supported worldwide by Motorola,<br>Mostek, Signetics/Philips, Thomson, Plessey, an<br>many, many others. AT&T has selected VMEbus<br>for its first line of board-level products.  |

| Technical Issues | Bus Timing                                           | All VMEsystem buses are asynchronous, except<br>for VMSbus (which by its very nature must be<br>synchronous). Asynchronous timing allows bus<br>performance improvements as chip technology<br>improves.                                                                                                                                                                                                             | IPSB " is synchronous, fixed at 10 MHz clock.<br>Performance cannot be improved without increas-<br>ing this clock rate, instantly obsoleting all pre-<br>existing product.                                                         | VMEsystem architecture allows smooth growth a<br>technology improves. Today's technology exceed<br>10 MHz clock of Multibus* II. (E.g., 12.5 MHz<br>and 16.0 MHz parts in M68000 Family.) |

|                  | Interrupt Protocol                                   | VMEbus interrupt handling may be either<br>centralized or distributed. Direct interrupts are<br>provided to handle on up to 7 prioritized levels,<br>with location monitors allowing any number of<br>virtual interrupts.                                                                                                                                                                                            | iPSB ** interrupt latency is unbounded, and no<br>priority override is allowed.                                                                                                                                                     | VMEbus interrupt protocol provides much greate<br>flexibility and performance and is better suited<br>for real-time applications.                                                         |

|                  | Multiplexing                                         | Completely non-multiplexed VMEbus address<br>and data lines, along with separate address and<br>data strobes, allow data transfer rates in single<br>transfers to approach block transfer rates. This<br>also supports performance improvements with<br>address pipelining features of modern processors.                                                                                                            | IPSB <sup>IN</sup> single cycle data transfer rate is only half<br>that of block transfer rate, since address and data<br>lines multiplexed. Address pipelining not supported.                                                      | Clear performance advantage for VMEbus.                                                                                                                                                   |

|                  | Serial Bus Protocol                                  | Sender Self-Check for VMSbus     Collision-Tolerant                                                                                                                                                                                                                                                                                                                                                                  | CRC ERROR checking     CSMA/CD protocol. (Complete iSSB**     specification has never been published.)                                                                                                                              | VMSbus message rate stabilizes under heavy usage. CSMA/CD declines under heavy usage.                                                                                                     |

|                  | Bus Support Chips                                    | Nine defined, six presently available, with samples<br>for additional three in 3Q 85. Presently sole-<br>sourced from either Motorola or Signetics/Philips<br>(depending on chip).                                                                                                                                                                                                                                   | iPSB " design requires LSI support. Two chips pres-<br>ently defined, sole-sourced from Japanese vendor.<br>The chip implementing the complex message-<br>passing protocol is not yet available.                                    | VMEsystem is far ahead with available support LSI.                                                                                                                                        |

#### Available products comparison.

VMEbus is the most advanced, widely-used and supported 8/16/32-bit bus architecture in the world. Bar none.

With it, users have the unmatched flexibility and versatility of over 150 manufacturers worldwide, with proven track records, offering a wide variety of 700-plus VMEbus-compatible products. Compare:

MULTIBUS\* II VMEbus

Source: The customers.

#### One-on-one design-in help.

In person or on the phone, anywhere in the US or Canada, you can get an engineerto-engineer update on all the new VMEbus products fitting your unique designs.

Call toll-free any weekday, 8 a.m. to 4:30 p.m. MST. If the phone call can't cover your needs, we'll have a local field application engineer drop by and ease your movement from concept to solid configuration. And get you to market. Faster. VMEbus. No other bus even comes close. For additional information on VMEbus products, fill out and send the coupon

to Motorola Semiconductor Products, Inc., P.O. Box 20912, Phoenix, AZ 85036.

MULTIBUS is a registered trademark of Intel Corporation. iSSB, iLBX, iPSB and iSBX are trademarks of Intel Corporation

To: Motorola Semiconductor Products, Inc., P.O. Box 20912, Phoenix, AZ 85036 Please send me additional information on VMEbus products.

|     | Title       |       |             |

|-----|-------------|-------|-------------|

|     | Company     |       |             |

| 42  | Address     |       |             |

| TIE | City        | State | Zip         |

|     | Call Me ( ) |       |             |

|     |             |       | 241DD080085 |

# **DIGITAL DESIGN**

17

19

AUGUST 1985 VOL. 15 NO. 8

52 VLSI advances graphics processors

69

Controlling laser printers

| 15 | Hotline                                                                        | 89          | New Products        |

|----|--------------------------------------------------------------------------------|-------------|---------------------|

| 34 | Imaging / High-Speed D/A<br>Applications • Range Of<br>Artificial Intelligence |             |                     |

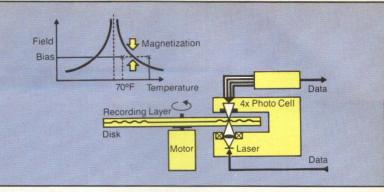

| 31 | <b>Peripherals</b> / Thermo-Mag<br>High-Capacity, Low-Cost                     |             |                     |

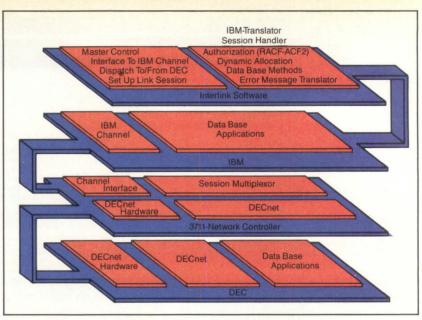

| 30 | <b>Communications</b> / Access<br>Many Forms                                   | s To SNA F  | rom LANs Takes      |

| 27 | Systems / Supercompute                                                         | er Exploits | Parallel Processing |

|    | IC Design                                                                      | 0           |                     |

ICs / Modular Packaging Points To Denser Systems

**Design Tools** / Programming Silicon Compilers For

**TECHNOLOGY TRENDS**

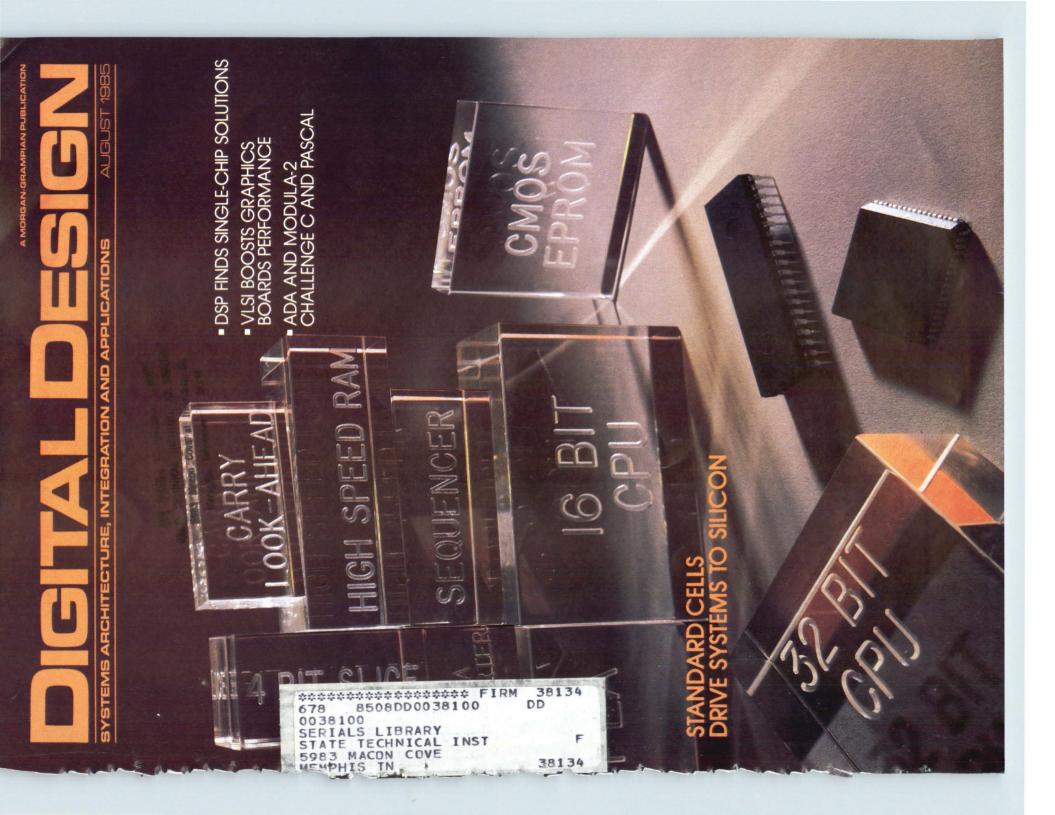

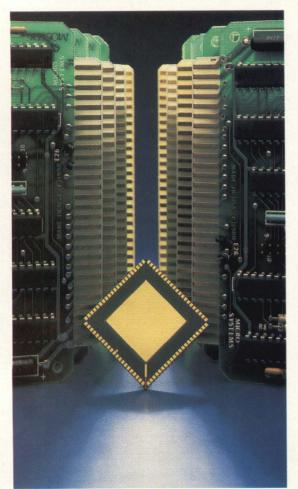

#### ON THE COVER

83

87

**Reader Service**

**New Product Focus**

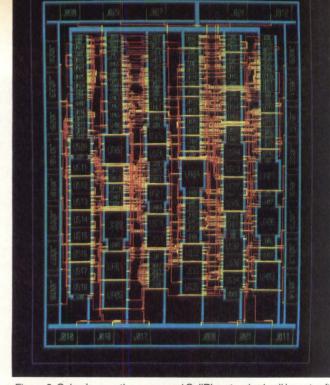

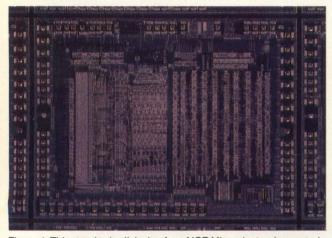

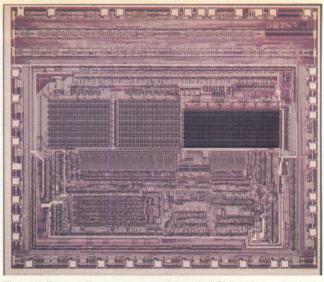

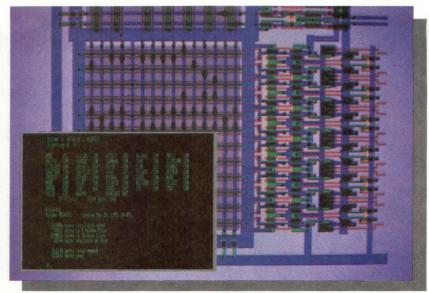

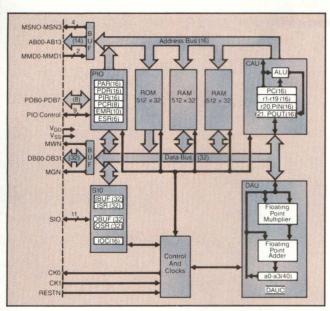

Systems once demanding 50 to 100 ICs can now be implemented on a single chip with standard cell technology. Many semiconductor vendors are introducing 2-micron CMOS libraries that provide 20 to 50 MHz system frequencies. As a result, standard cell technology meets both the performance and functionality requirements of many applications. Developed by WaferScale Integration, the cover illustrates the numerous VLSI functions in the firm's cell library.

100

Published monthly thirteen times a year with two issues in November. Subscription rates for non-qualified subscribers (US and Canada) — \$40/yr; foreign — surface mail — \$50/yr; airmail — \$85/yr. Single copies — \$4. Copyright 1985 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, Berkshire Common, Pittsfield, MA 01201 ISSN 0147-9245.

Advertiser Index

4

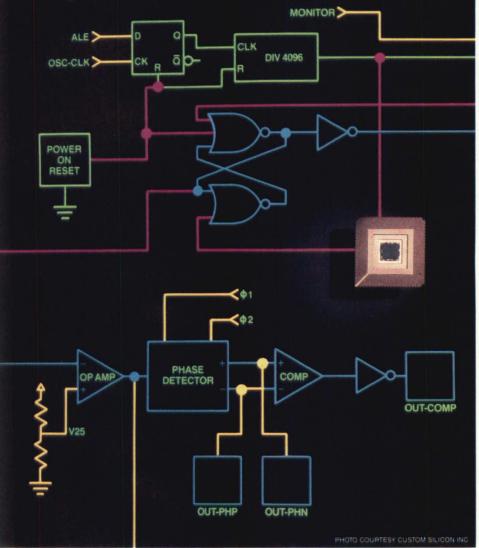

VLSI functions together with analog cells yield single chip systems.

### FEATURES

COURTESY GE CALMA

#### DESIGN TECHNOLOGY

#### 36

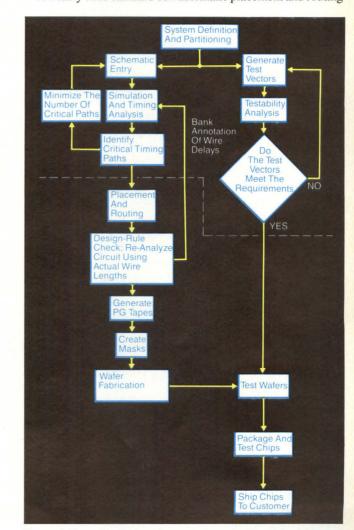

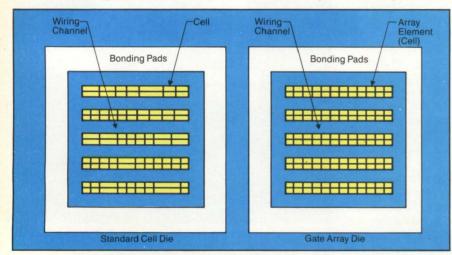

#### Standard Cells Pave Road To Systems On Silicon

#### by Ronald Collett

TABLE OF CONTENTS

Standard cell libraries are expanding to include core processors, analog and LSI functions. Meanwhile, vendors are developing tools to support the design of systems on a chip.

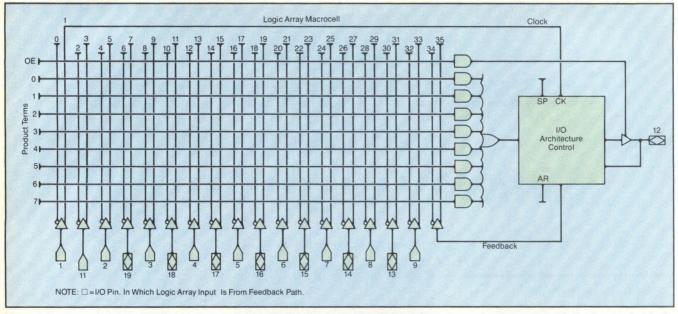

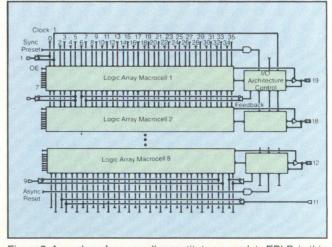

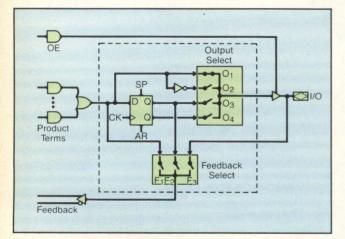

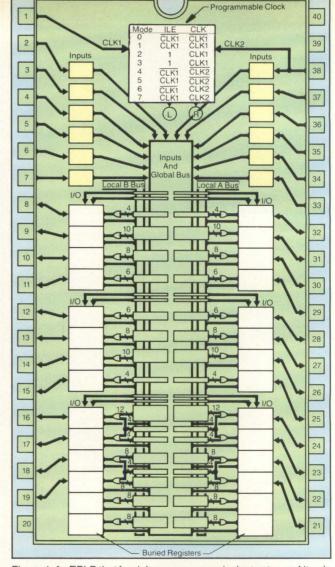

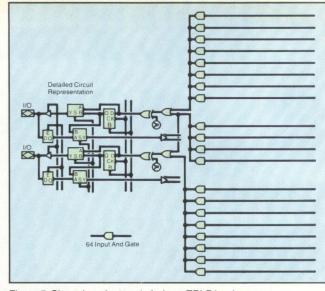

#### Part 1: Erasable Programmable Logic Devices Simplify Logic Design

by Clive McCarthy

EPLDs are surfacing as an alternative to gate arrays and other ASICs. The new generation of EPLDs offers both higher densities and increased performance.

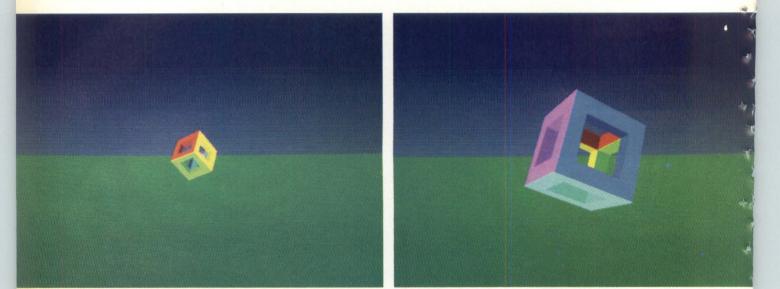

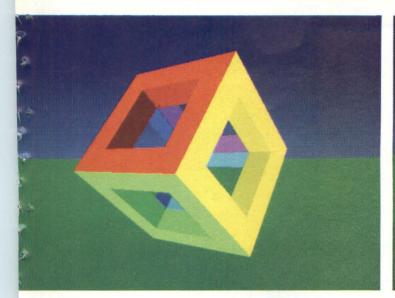

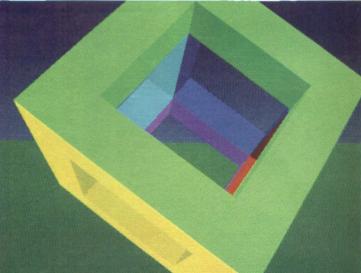

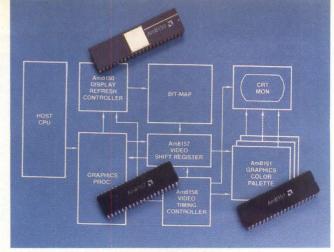

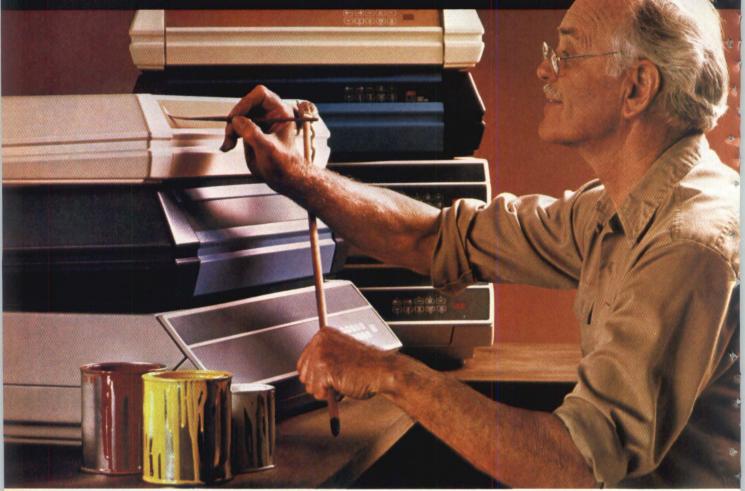

#### ELECTRONIC IMAGING

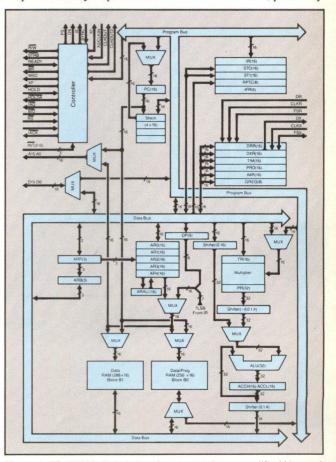

#### High-Resolution Graphics - Implementing Software In Silicon

by Andrew Wilson

Using high-resolution memories and VLSI processors, computer graphics has finally evolved to the point where previously compute-intensive functions can be carried out at minimal cost.

#### SEMICONDUCTOR TECHNOLOGY

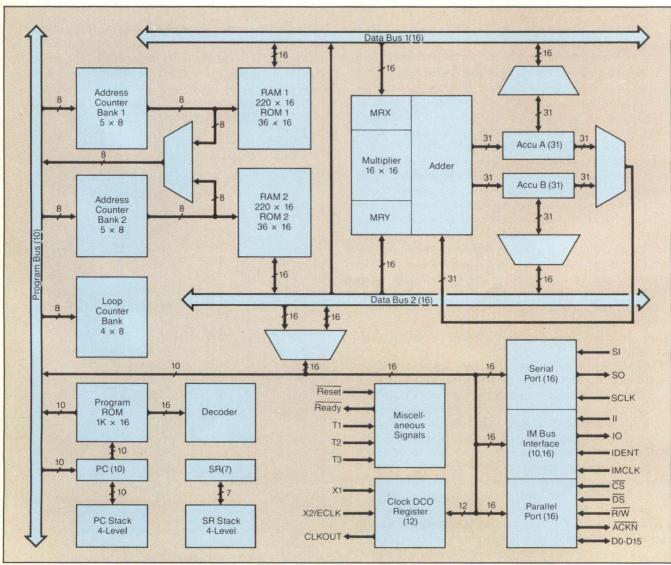

#### Single-Chip Digital Signal Processors Challenge Multichip Solutions

#### by Dave Wilson

Through the integration of Harvard architectures, fast multipliers and flexible I/O structures, single chip DSPs continue to present the systems designer with a less expensive, fully functional alternative.

#### SYSTEMS ARCHITECTURE

#### **Outward Appearances Disguise Laser Printer Capabilities**

#### By Joe Aseo

Most laser printers use one of a few engines and thus have similar specifications, but the printer controller and software are the factors that really determine system capabilities.

#### Ada And Modula-2: True Systems Languages?

#### by Brita Meng

Ada and Modula-2, both based on Pascal, are strongly typed modular languages that emphasize program segmentation and data abstraction. Standardization and flexibility differentiate use of the two as well as compiler cost and availability.

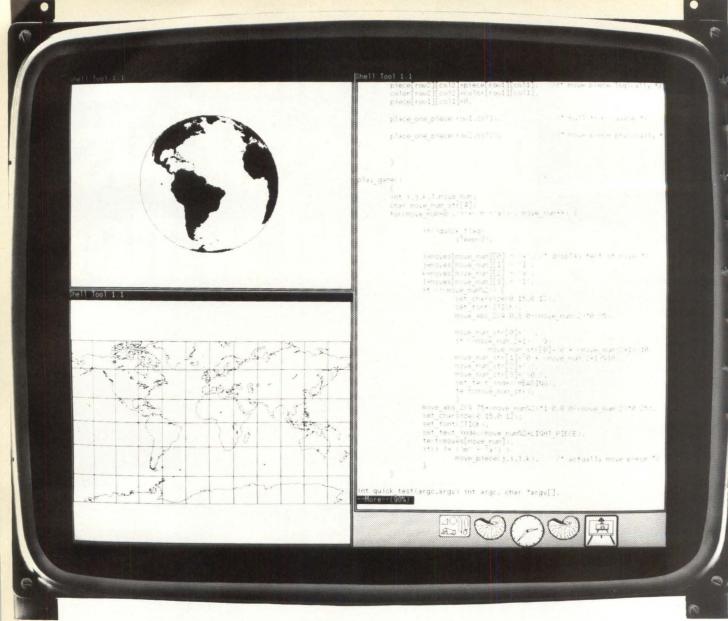

# **PRO/VENIX in the Laboratory**

# Give Intelligent People Powerful Tools and They'll Work Wonders.

PRO/VENIX,\* Digital's enhanced UNIX\* product for the Professional\* Workstations, has everything you need to design sophisticated laboratory systems and applications. It has the basic features you expect from a UNIX product. Like System V compatibility. Berkeley enhancements. And multiuser and multitasking support.

But you didn't get where you are by relying only on the basics. And that's why PRO/VENIX offers intelligent enhancements.

**Realtime Interface.** Whether laboratory data acquisition or process control, PRO/VENIX has unique capabilities that let you create the environment you need. Pre-emptive priorities. Interprocess communication. Shared data segments. Asynchronous I/O. And process timing with suspension units as small as 1/60th of a second.

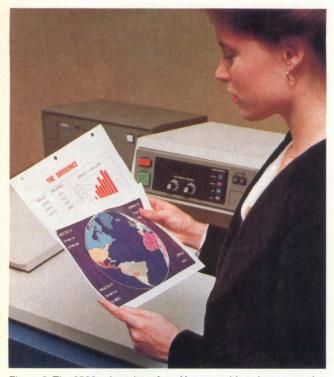

High-resolution Color Graphics. Powerful ideas warrant powerful presentations. PRO/VENIX offers a Graphics Kernel System (GKS), utilities, and libraries that let you create graphics from the UNIX shell or from an application.

Ethernet Communications. Your PRO/VENIX resources can be shared in distributed computing or Local-Area Network environments with the Professional Ethernet Controller. XNS\* and TCP/IP\* protocols let your Professional become a full-featured distributed UNIX workstation.

Powerful tools are useless without a strong company that can deliver service, support, and long-term commitment. The Digital Commitment – 87,000 people in over 660 engineering, service, sales, and manufacturing facilities worldwide devoted to delivering high-quality products and service.

Call 1-800-DIGITAL Ext. 695 for more information on PRO/VENIX Workstations.

Isn't it time you had tools powerful enough to create the UNIX applications you envision?

Copyright 1985. All rights reserved. PRO/VENIX is a member of Digital's family of ULTRIX products. VENIX is a trademark of VenturCom, Inc. Professional, Digital, and the Digital logo are trademarks of Digital Equipment Corporation. UNIX is a trademark of Bell Laboratories. XNS and TCP/IP are trademarks of Xerox Corporation.

Circle 5

# Trackballs. Flexibility at your fingertips.

When you need to get your hands on a top quality, high reliability, long life, smooth performing trackball, where can you turn for help?

Fortunately there is a solution right at your fingertips...trackballs from Measurement Systems.

You can achieve super-fast cursor movement on a CRT display and precise positioning too with a variety of ball sizes ranging from 1.5 to 3.5 inch diameter. We can offer two or three axes, a variable pulse rate output, digital outputs, low profile housing, a variety of interface options and much more.

Call or write for our new catalog illustrating our trackball products as well as our joystick and handgrip controls.

Measurement Systems, Inc. 121 Water Street, Norwalk, CT 06854, U.S.A. (203) 838-5561

Circle 11

# REPRINTS

**DIGITAL DESIGN** will reprint any article from past or present issues. Reprints are custom printed. Minimum order: 1,000 copies. Purchase order or letter of authorization required.

Allow one month from receipt of order for delivery, unless previously arranged and confirmed.

Advertisements alone can also be reprinted. Call (617) 232-5470, and ask for reprints.

### DIGITAL DESIGN

| Editor in Chief                              | John Bond                                                     |

|----------------------------------------------|---------------------------------------------------------------|

| Managing Editor                              | Debra A. Lambert                                              |

| Technology Trends                            | Julie Pingry,<br>Senior Editor                                |

| Features:                                    |                                                               |

| Semiconductor Technolo                       |                                                               |

| Electronic Imaging                           | Executive Editor<br>Andrew Wilson,<br>Senior Technical Editor |

| Design Technology                            | Ronald E. Collett,                                            |

| Systems Architecture                         | Senior Technical Editor<br>Brita Meng,<br>Technical Editor    |

| New Products Editor                          | Terri Lamneck                                                 |

| West Coast Technical Edito<br>(408) 356-0405 | rs Gregory MacNicol<br>Joe Asec                               |

| Copy Editor                                  | Sherri Mack                                                   |

| Editorial Assistant                          | Tia Partir                                                    |

| Contributing Editor<br>Peripherals           | Bob Hirshor                                                   |

| Directory Editor                             | Dawn Bursk                                                    |

| Senior Art Director                          | Tilly Berensor                                                |

| Advertising Production Ma                    | nager Martha Watjer                                           |

| Production Director                          | Paul Dadarria                                                 |

| Graphics: Supervisor<br>Sr. Technician       | William Manning Jr<br>Don Schaa                               |

| Marketing Director                           | Charlotte King                                                |

| Promotion Manager                            | Elaine Bul                                                    |

| Marketing Assistant                          | Sharon Lembo                                                  |

| Research Carolyn                             | Wulfsberg, Peter Michel                                       |

| Circulation Director                         | Hugh J. Dowling                                               |

| Circulation Supervisor                       | Nancy McPherson                                               |

| Circulation Staff                            | Miriam Hliste                                                 |

| Reader Service (413) 499-2                   | 2550 Terri Giroux                                             |

| Marketing/Sales Specialist                   | Krickett Cunninghan                                           |

| Executive Administrator                      | Suzanne Levecque                                              |

|                                              |                                                               |

| Corp. Services Administrat                   | tor Janet R. Pit                                              |

Caroline Chesnut, Tyrone Simpson, Mal Rankin, Debra James

> President, Ronald W. Evans Publisher, James R. DiFilippo Associate Publisher Terry L. Willins

#### **Advertising Sales**

Northeast: Charles C. Boyd (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic/Southeast: Richard V. Busch (609) 921-7763, 40 Stony Brook Lane, Princeton, NJ 08540

Central: Mike Prewitt (714) 851-8550, 2041 Business Center Dr., Suite 206, Irvine, CA 92715

Northwest: Carole Sacino, Diane Ross (408) 356-0405, 15951 Los Gatos Blvd., Suite 7, Los Gatos, CA 95030

Southwest: Thomas A. Stillman (714) 851-8550, 2041 Business Center Dr., Suite 206, Irvine, CA 92715

National Postcard Sales: Lisa Rendini (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

National List Rental Sales: Deb Goldstein (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215 ... and the winner is HITACHI®

for the newest technological advance in RGB color monitor history...

Our square cornered, 15", compact and affordable, hi-resolution flicker-free desk top... Model **HM 4615**

HITACHI, the world leader in technology has done it again with the entirely new and innovative HM 4615 RGB Color Monitor.

New Hitachi gun and yoke technology brings a sharper focus and convergence to your picture; a new LSI for our Video Amplifier requires only one third the space of previous models making the HM 4615 extremely compact.

Square corners provide greater viewing area and  $1024 \times 800$  hi-resolution is standard with  $1280 \times 1024$  available as an option.

The Hitachi HM 4615 is economically priced, ideally suited for CAD-CAM and other desk top computer graphics systems. It carries worldwide approvals, including FCC, UL, CSA, and VDE.

For more information contact Hitachi America Ltd.

50 Prospect Avenue Tarrytown, NY 10591-4698 (914) 332-5800

950 Elm Avenue San Bruno, CA 94066 (415) 783-8400

Circle 12

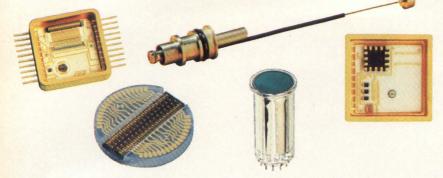

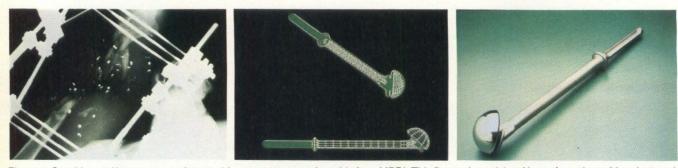

# **IR** detectors

Cincinnati Electronics provides superior performance, high reliability, and on-time delivery in a broad range of custom and standard indium antimonide (InSb) IR detectors and custom hybrid focal plane assemblies.

Our InSb photovoltaic (PV) detectors for the 1 to 5.5 micron range provide optimum sensitivity with responsivities greater than 3.2 Amps/Watt at  $\lambda_p$ . We design, develop and fabricate economical single elements for test and evaluation as well as linear arrays with discrete or multiplexed outputs in a variety of configurations.

Our IR detectors are proven in tactical applications (high volume and custom assemblies), commercial IR imaging systems, IR astronomy, and a variety of laboratory uses.

Twenty years of innovative research has earned us recognition as the leading supplier of InSb IR detectors. Write or call to discuss your IR detector requirements. Cincinnati Electronics Corp., 2630 Glendale-Milford Road, Cincinnati, Ohio 45241. Tel. 513-733-6100. An equal opportunity employer.

#### Probeye<sup>®</sup> Detector/Dewar Assembly

Glass dewar assembly houses a 6-element monolithic detector array, used in the Hughes Probeye<sup>®</sup> Thermal Video System. We offer a complete capability in high volume fabrication and testing of commercial IR detector assemblies.

Detector and Microcircuit Devices Laboratories A Member of the Aerospace Division.

Circle 9

TELL US YOUR THOUGHTS bigital Design is your forum—your inputs help keep the magazine interesting and vital to the

**design community.** So let us know how we're doing and how we can serve you better in the future. We want to know what you like or dislike about *Digital Design*, the subjects you'd like to see us address, how you feel about the problems you face every day as design professionals.

If you have thoughts your peers should know about, put them in a letter in *Digital Design*. Have your say in *your* magazine! Send letters and comments to: Editor, *Digital Design*, 1050 Commonwealth Ave., Boston, MA 02215.

#### EDITORIAL AND SALES OFFICES

DIGITAL DESIGN, 1050 Commonwealth Avenue, Boston, MA 02215, Telephone: (617) 232-5470

#### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215, (617) 232-5470. Brian Rowbotham, Chairman; Ronald W. Evans, President; Charles Benz, Vice President.

#### **EXPOSITIONS GROUP**

AT

CA

AT

AT

Morgan-Grampian Expositions Group, 1050 Commonwealth Avenue, Boston, MA 02215 (617) 232-EXPO. The following is a list of conferences produced by the Expositions Group:

| E West      | CADCON East        |

|-------------|--------------------|

| DCON West   | ATE Central        |

| E Northwest | CADCON Central     |

| E East      | Electronic Imaging |

|             |                    |

In addition to DIGITAL DESIGN, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronics Test

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronics Times • What's New in Electronics • What's New in Computing • Business Computing and Communications • Communications Systems Worldwide.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral manufacturers, integrating OEM's and commercial end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

**∛BPA** ABP

#### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

Circulation Department, **DIGITAL DESIGN**, Berkshire Common, Pittsfield, MA 01201

Subscription rates: non-qualified subscribers (US and Canada) – \$40/yr; foreign – surface mail – \$50; air mail – \$85. Single copies – \$4.

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by Morgan-Grampian Publishing Co. for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$2.00 per copy, plus \$.25 per page is paid directly to CCC, 21 Congress St., Salem, MA 01970. 0147-9245/84 \$2.00 + \$.25.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

AUGUST 1985 I DIGITAL DESIGN

1. High Speed (MicroCAD Software)

0

2. Dual Display Modes (Energraphics Software)

3. Simplified Processing (AutoCAD Software)

4. 9 Bit Planes (Courtesy WSI Inc., Bedford, MA)

5. 16.8M Color Shades (Courtesy Catherine Del Tito, Wave Graphics)

High Resolution (Courtesy University of North Carolina at Chapel Hill, Depts of Computer Science and Radiology)

What you will find most surprising,

in mind. So when comparing the

performance of Vectrix with the

competition, check the price

too. You'll like what you see. For more information, contact

Vectrix Corporation, 2606

however, is the price. Our VX/PC

Branchwood Drive, Greensboro,

288-0520. Telex 574417.

North Carolina 27408. Phone (919)

Board Set was designed with the OEM

# Six reasons why professionals continue to choose Vectrix for quality IBM XT/PC graphics.

Even though IBM offers a color graphics card, professionals still choose Vectrix. It's not surprising. Especially once they've seen us in action. Professionals know that our VX/PC Board Set delivers the quality and performance they need for serious color graphics.

The VX/PC Board Set provides advanced features that help simplify sophisticated graphics design. Besides displaying 512 simultaneous colors from a palette of 16.8 million, the VX/PC supports an extensive library of on-board graphics macros for ease of programming and fast design, as well as full emulation of the IBM color card. And, an on-board 16-bit microprocessor frees your computer to concentrate on other tasks.

But that's not all. Our 9 bit planes

add an extra dimension of sharpness and clarity to your image that must really be seen to be appreciated. That's why it's not surprising to see Vectrix color cards in applications such as medical imaging, weather satellite data mapping, computer aided design and drafting, and graphics arts, to name a few.

IBM XT, IBM AT, and IBM PC are trademarks of International Business Machines Corporation, White Plains, NY

MicroCAD is a trademark of Imagimedia Technologies, Inc., San Francisco, CA. AutoCAD is a trademark of AutoDesk, Inc., Sausalito, CA.

EnerGraphics is a trademark of Enertronics Research, Inc., St. Louis, MO.

Distributor inquiries welcome.

**Circle 55 on Reader Inquiry Card**

# THERE'S A LOT OF POTENTIAL LOCKED INSIDE EVERY MICROVAX II.

Our complete line of high performance storage and communications products unlocks the processing power of DEC's new MicroVAX II.

Emulex products operate transparently to MicroVMS so as to permit ease of implementation and use. Furthermore, thanks to our accomplishments in advanced VLSI technology, you get superior performance and compactness.

**MICRO PERIPHERALS.** The new Emulex QD01/D disk controller is a dual size board that's packed with capabilities. And with it, you get all the features of Mass Storage Control Protocol (MSCP). It controls up to two ST506 drives with a 2MB peak Q-bus transfer rate. Features include a 10K Byte data buffer, 22-bit addressing and 1:1 interleave.

The Emulex QT12 tape controller is also dual size and ideal for backup of micro peripherals. Through firmware, it operates transparently to the driver. It has a QIC2 interface to operate with 51/4" footprint 1/4"

Shown, left to right: SC03/MS disk controller, UC03 host adapter, TC03 tape controller, CS02 communications multiplexer and QD01/D disk controller. multiplexers. Our high-performance CS02 doubles line capacity by putting 16 async lines in the space DEC uses for eight. The CS02 runs at up to 38.4 K baud per line and incorporates a 256-character FIFO buffer for fast, sure data transfers. For flexible configuration, the CS02 is RS-423

and RS-232C compatible.

THE KEY TO LARGE PERIPHERALS. Emulex's SC03/MS disk controller incorporates a fully transparent set of firmware which has the features of MSCP. It interfaces to industry-standard SMD drives, handling disk transfer rates of up to 1.8MB/sec.

Our tape drive story is equally impressive. Three Emulex controllers —TC02, TC03 and TC05—are fully compatible with DEC TS drivers.

With the TC02, you can take advantage of start/stop drives and streamers with 1600 bpi at 125 ips, or up to 6250 bpi at 25 ips. Formats available include NRZI, P.E., and GCR. Data rates can be as high as 200,000 characters/sec.

The new TC03 tape controller has all the features of the TC02 and also offers a large (3.5 KB) data buffer and block mode DMA for increased data throughput. It's also compatible with up to four Pertec industry-standard drives.

The TC05 handles 55 ips tape speeds, 8000 bpi densities on a Sentinel drive, and features a 3.5KB buffer.

For a choice of micro storage products, start with the Emulex UC03 host adapter to interface your MicroVAX II with SCSI-based micro controllers. The UC03 supports multiple peripherals simultaneously through a complete family of Emulex micro controllers. These include disk, magnetic tape and optical disk.

Emulex's unique solutions for MicroVAX II extend to packaged micro subsystems.

The Emulex Decathlon can accommodate three 514 " peripherals in rack-mount or tower packages. It provides a selection of both Winchester drives from 36-110MB (formatted) and 14 " tape streamers up to 60MB. The Emulex Medley incorporates a Winchester (up to 110MB) and back-up streamer (up to 110MB) in a rack-mount compact package. Whatever storage medium you choose, Emulex has the perfect package for you.

#### EMULEX. YOUR KEY RESOURCE.

We can unlock the power of DEC's MicroVAX II. And our broad product line can also add new power to your high end LSI-11, Micro PDP-11, PDP-11 and VAX systems. Improved performance and unique features are yours in a full range of DEC system storage and communications enhancements.

Unchain DEC's machines for enhanced capabilities now. For product or sales information, call tollfree 1-800-EMULEX3. In California, call (714) 662-5600. Or write: Emulex Corporation, 3545 Harbor Blvd., P.O. Box 6725, Costa Mesa, CA 92626.

Circle 15

DEC, Q-bus, MicroVAX II, TS, MicroVMS, VAX, LSI-11, PDP-11 and Micro PDP-11 are trademarks of Digital Equipment Corporation. Sentinel is a trademark of Control Data Corporation.

U.S. Regional Offices: Anaheim, CA (714) 385-1685; Schaumburg, IL (312) 490-0050; Roswell, GA (404) 587-3610; Nashua, NH (603) 882-6269. International Offices: Australia, Eastwood, N.S.W. (02) 858-4833; Canada, Mississauga, Ontario (416) 673-1211; France, Montrouge (1)735-7070; United Kingdom, Bracknell, Berkshire (344) 484234; West Germany, Munich (089) 304051.

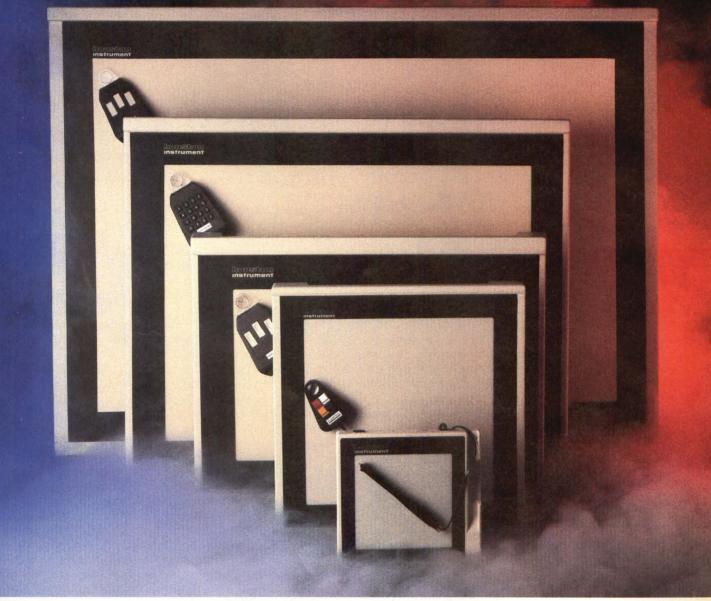

# GOOD LOOKS RUN IN THE FAMILY.

#### LEXIDATA'S LEX 90 FAMILY OF HIGH-PERFORMANCE DISPLAY PROCESSORS.

Lexidata's monitor enclosure design features a unique tilt and swivel movement with smooth and easy operation. All monitor connections and peripheral power supplies are located in the enclosure's base. LOOKING GOOD. The LEX 90<sup>™</sup> family is a good family to know. It's as advanced in a business sense as it is technologically. And what it has, compared to what it costs, makes it look very good indeed. For example:

Its software architecture is compatible both within the family

and with our popular Series 3000 line. So performance upgrades are easy and economical. And software investments are well protected.

Every LEX 90 model has the same basic components which use the latest bit-slice technology for rapid execution of complex calculations and set-up times.

The family's flexibility allows you to buy only the functionality you need now, and gives you the ability to add on later as required.

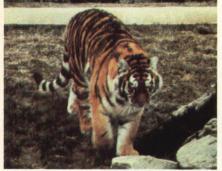

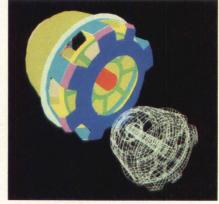

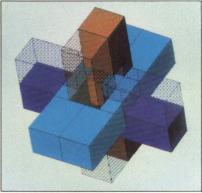

Exclusive SimulRes functionality allows simultaneous display of

A tiger shows off its "true colors" with the LEX 90 True Color display system from Lexidata.

8-bit color lookup table for each color. And where you're looking for high performance with high resolution, there's a LEX 90 model that can support up to 24 planes of 1280x1024 display memory at 60Hz non-interlaced refresh. The extraordinary solid modeling display capability of our patented SOLIDVIEW<sup>™</sup> technology is available in a 640x512 version. And for petrochemical applications, there's GEOVIEW,<sup>™</sup> a threedimensional geological interpretation package. On-board diagnostics, based on a 6801 micro-

processor, help maximize uptime. And the unique tilt-and-swivel movement of our monitor allows smooth and easy operation of your display. Of course, the

entire family is

LEX 90's SimulRes enables the designer to mix theory with reality by allowing the simultaneous display of a wireframe model with the real-life product. (Courtesy of PDA Engineering)

640x512 and 1280x1024 images on the same screen. A True Color configuration offers two buffers of 640x 512x24 with an

USA 01865. TWX: 710-34 KINGDOM call: Lexidata Ltd., Hook (025672) 3411 In FRANCE call: Lexidata SARL, Rungis (1) 686-56-71. In JAPAN call: Lexidata Technical Center, Tokyo 486-0670.

SOLIDVIEW, Lexidata's patented technology for the display of solid models, is available as an option on selected LEX 90 display processors. Its translucent shading pattern allows you to see inside your solid model.

compatible with a variety of leading application software packages and minicomputers. Which makes everyone look even better.

For a good look at the LEX 90 family and its expanding capabilities, call us at 1-800-472-4747. In Massachusetts, call (617) 663-8550. Or write: Lexidata<sup>™</sup> Corporation, 755 Middlesex Turnpike, Billerica, Massachusetts

USA 01865. TWX: 710-347-1574. In UNITED

LOOKING GOOD

Copyright 1985 Lexidata Corporation. All rights reserved. LEX 90 and GEOVIEW are trademarks of the Lexidata Corporation. SOLIDVIEW is a trademark of the Lexidata Corporation and is covered by U.S. Patent No. 4,475,104. Lexidata is a trademark of the Lexidata Corporation.

**Circle 10 on Reader Inquiry Card**

### HOTLINE

MOTOROLA ARRAYS ON MENTOR VIA EDIF DATABASES Using EDIF physical databases, users of Mentor workstations will be able to directly download Motorola's 2- and 3-micron HCMOS Macrocell Array libraries from Motorola's mainframe.

20,000-GATE GATE ARRAY IN 1.5 MICRON GEOMETRY NEC Electronics is sampling the  $\mu$ PD 65200 19,551-gate gate array. Fabricated in 1.5 $\mu$ m geometry using CMOS-4, internal gate delays are 0.5 nsec. The seven other CMOS-4 ICs in the family have fewer gates.

SUN FIRST TO RUN P-CAD PORTED TO UNIX 4.2 Personal CAD Systems' simulation, PC board and PLD design and layout software has been ported to UNIX 4.2, and Sun is the first to run all of the P-CAD UNIX programs.

TWO FIRMS AIM TO REDUCE THE PC AT TO A FEW CHIPS Zymos announced a 4-chip version of the IBM PC AT: the 80286, 80287, 8042 and a standard cell. At the same time, the start-up Chips & Technologies is aiming to produce an AT in a 20-chip set.

HARDWARE MODELING, NETWORKING FOR VALID Valid now has a 68020 workstation upgrade and supports DECnet-TCP/IP networking. In addition, a hardware modeling and simulation accelerator called Realmodel, Teradyne's Lasar Version 6 logic simulation and ECAD's Dracula IC layout verification will run on Valid systems.

FUJITSU MASK-PROGRAMMABLE CMOS ROMS DEBUT IN US Two Fujitsu MB8300 series ROMs will be sold in the US. A 1 Mbit ROM and a 256K static ROM are initial offerings; both are TTL-compatible and organized  $\times 8$ .

DG JOINS FORCES WITH THREE DESIGN AUTOMATION FIRMS Data General has invested in Cericor, and DG Eclipse MV and DS workstations will run Cericor's CDA-5000. DG's DS is also the base for RDS' AutoMate PC board design workstation. And Viewlogic's Workview software is available on the DG/One personal computer.

THREE IMAGE PROCESSING PACKAGES ANNOUNCED The first, Math Advantage from QTC, features 180 math routines callable from C or Fortran. The second, PICDMS III from MIB Chock, runs under PC-DOS for image processing and 2D or 3D model building. The third, announced by Process Software, is VIOS, with edge enhancement, differencing and integration for Datacube QVG systems.

CAE SYSTEMS RUNS ON MICROVAX II, HAS ADDED TOOLS Besides running on the MicroVAX II, CAE Systems has added an integrated simulator, MultiSim, and a layout editor called LEIA. Third party offerings include ECAD's Dracula II IC layout verifier and Seattle Silicon's Concorde module generator.

1.25 MICRON HCMOS GATE ARRAYS IN DEVELOPMENT Using TRW's HCMOS process, Custom MOS Arrays will develop and produce 1.25-micron gate arrays with 500 to 25,000 gates, up to 330 pins and 0.9 nsec typical gate delays.

VTI SILICON COMPILER, TOOLS AVAILABLE ON DAISY VLSI Technology's IC design and silicon compiler tools have been ported to Daisy Concurrent Chipmaster and Siliconmaster workstations.

# THE GATE TO A Smarter std bus.

STD BUS has always been a smart choice for flexible, cost-effective Z80<sup>®</sup> systems. And now, Mostek has made it smarter still. By adding a proprietary gate array to provide more intelligence to your system.

Our family of intelligent STD boards all feature a Z80 processor, DMA controller and on-board memory. And our custom gate array, which took three man years to develop. But that's where the similarity ends. Because we've provided different features on each board to make sure you get the best possible performance from each.

For example, we've got intelligent serial boards for short (250 feet) and long (1 mile) communication distances. We have another that implements the IEEE 488 General Purpose Interface Bus standard with speeds up to 300 Kbytes/second. And an IPIO with 32-bits of parallel I/O, suitable for high-speed control and data transfer.

The point is, Mostek designed these to be the most sophisticated STD BUS boards available today. Which is one more way in which we show our continuing commitment to STD BUS.

So to give your system some extra smarts, contact Mostek Corp., 1215 W. Crosby Road, MS1051, Carrollton, Texas 75006, or call 1-800-635-0200. In Texas, 1-214-466-8801. In Europe, (32) 02/762.18.80. In Japan, 03/496-4221. In the Far East (Hong Kong), 5.681.157-9.

Z80 is a registered trademark of Zilog, Inc.

#### TECHNOLOGY TRENDS

1

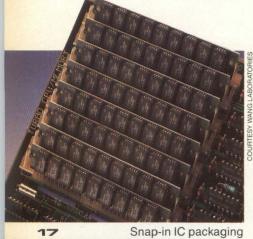

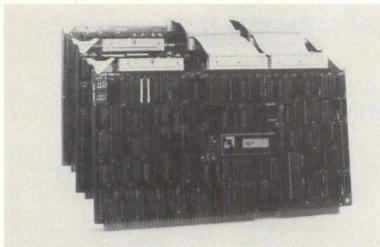

**Modular Packaging** Points To Denser Systems

he ability to upgrade systems with improved components or more memory has been hampered by the need to completely rework the PC boards. To overcome this, a module and socket packaging scheme has been developed by Wang (Lowell, MA), Molex (Lisle, IL) and Texas Instruments (Dallas, TX) that provides upgradable, dense circuitry. The Single In-Line Memory Module (SIMM) is a baby board onto which single in-line packages are surface mounted; two of these modules snap into a SIMM socket (Figure 1) which is wave soldered onto the main board.

A need for denser memory in Wang's Office Assistant was the impetus for the project. Texas Instruments (TI) provided surface mount expertise to create a leadless edge-card module from Wang's SIP package. Molex worked with Wang to make the pluggable socket. In addition to increasing density, using SIMM provides easy field or customer upgrade and repair. The project was initiated under full public disclosure, and others have joined. Shortly after the initial design, AMP (Harrisburg, PA) also began making a SIMM socket; besides TI, Toyocom (Tokyo, Japan) is in production with components and modules to fit the design. AMP's socket, though form and fit compatible with Molex's, uses a different design. It may be advisable to qualify them separately on both cost and performance.

The Molex SIMM socket uses zero insertion force (ZIF) contacts to hold baby boards in place; these allow up to 25 matings. Pegs are used to ensure proper placement of the socket on the motherboard and a rib and slot arrangement assures that the module boards load correctly into the socket. At present, no second source is available with this design. All SIMM modules hold up to nine ICs; though initially used for RAM, other ICs like I/O, logic or hybrids could be used on the module baby boards.

with an edge connector and plugged into the SIMM socket.

-

1144 -

TAAAA

CARAGE CARAGE CARAGE

.....

......

-----

Figure 1: This Molex Single In-Line Memory Module socket acts as a connector for a high-density

IC packaging system. Two baby boards with nine ICs each are SIMMs. Using plastic leaded chip carriers, even memory ICs can be mounted on standard epoxy-glass substrate baby PC boards

.....

.....

....

....

-ALAA

Plastic leaded chip carrier packaging has allowed lower costs as well as the ability to mount the components on standard epoxy-glass substrate baby PC boards. According to Wang, 1 Mbit DRAM density is available for the price of a 256K DRAM. Yield of surface mounting also improves with the smaller boards.

Two baby boards with nine 64K RAM ICs surface mounted to it plugged into one SIMM socket provide 512K of RAM (with eight chips used as storage). Mounting requires 60 holes on the PC board; the individual packages are surface mounted to baby boards. This is much easier to install than 18 discrete 64K chips in DIP packages, which would demand drilling and routing to 288 holes. For upgrading, 256K RAM chips could be mounted on the standard baby board and inserted into the same socket. The modules were designed to accommodate 1 Mbit and 4 Mbit parts as well. SRAM and DRAM modules are now in production.

According to Jim Clayton, principal microelectronic engineer at Wang's IC Technology R&D group, the major advantage this scheme provides is convenience and low risk for introducing surface mounted components into products. One problem manufacturers have had with surface mounted components is that a board generally is not all surface mounted, but also includes leaded components wave soldered into throughholes. Mixing of surface mount and leaded components means two soldering operations and generally low yields. With the SIMM scheme, surface-mount and through-hole components are on separate boards. SIMM sockets use throughholes, like the other components on the main board; components are surface mounted only on separate baby board modules. The Molex socket is made of a material that will withstand the temperatures used in surface mount soldering if that is desired.

The initial Wang design, in production since late 1983, has evolved from a leaded ceramic module to the PLCC on edgeconnector module scheme. Modules in sockets of the Office Assistant stand at 90° from the motherboard; a product to come out soon uses SIMM sockets that hold modules at about a 25° angle (Figure 2), and work is underway to improve on that. By increasing the angle, board-to-board spacing could be improved from 0.9" to 0.5". Wang has also reported work on increasing the pin count of the connector from the current 30 pins. To further increase density, double sided baby boards might be used. This would provide 18 ICs in one module and up to 36 per socket.

Many major computer firms are evalu-

# When you're ready for the brilliance of color, we'll be there.

Now you can have the beauty and precision of color graphics for business, engineering and scientific applicationsat much less cost than ever before! Qume's new QVT 511GX<sup>™</sup> terminal provides flicker-free, non-interlaced raster scan graphics, with a selection of up to eight colors from a palette of 64. The QVT 511GX is fully compatible with the Tektronix 4105 and accepts all of its software, including PLOT 10 packages. It can also be used in Tektronix 4010, 4100 and 4110 series environments. and works beautifully with the Tektronix 4695 color graphics copier. What's more, it conforms to both ANSI X3.64 and ISO 6429 protocols for text editing. A mouse device, capacitive keyboard, and advanced ergonomic design are all standard.

The QVT 511GX measures up to Qume's exceptional standards for performance, quality control, and reliability. And it's backed by our experience and resources as an ITT company. So whatever your applications, we'll be there with a dazzling display of technical support.

For full details on the new QVT 511GX and Qume's other graphics and alphanumeric terminals, or our full line of daisywheel printers and disk drives, call (800) 223-2479. Or write Qume Corporation, 2350 Qume Drive, San Jose, CA 95131.

Circle 45

ektronix 4105, 4010, 4100, 4110, and PLOT 10 are registered rademarks of Tektronix Inc. ANSI is designed to American Autonal Standards Institute, Inc., ANSI X3.64-1979 guidelines. SO is designed to the International Standards Organization, SO 6429 guidelines.

#### TECHNOLOGY TRENDS/ICs

ating the concept for packaging memory and other functions. The field upgrade and service are a major impetus for Apple Computer (Cupertino, CA) choosing SIMM for memory in an upcoming product. Space saving is another important aspect for personal computers. Apple will use the 25° angle version to allow the low-profile keyboard to fit easily over the CPU. Northern Telecom's Bell Northern Research (Mountain View, CA) is evaluating the scheme for packaging codecs and other circuits; each line of the Meridian SL1 PBX could be implemented in a module. Here, the angled modules will fit into the board-to-board spacing.

One concept that designer Jim Clayton of Wang suggested is that logic modules in a SIMM configuration could act as instant gate arrays. To implement a complex function immediately while it is in

Figure 2: This Wang board shows an array of SIMMs in their sockets standing at an angle to reduce board-to-board spacing. The board shown will be used in a product to be announced soon. Since the module baby boards are not soldered in, customers can change and upgrade the system themselves without waiting for a repairman or an entire board to swap.

the process of being designed into a single chip, baby boards with ICs to provide the desired functions could be plugged into a few sockets.

Another possibility is to use the scheme for personalizing compatibility; each user of a standard peripheral could implement an interface for a different system by plugging in different modules. Molex literature suggests that standard products could easily be customized by providing a SIMM socket and plugging in the appropriate modules. The density and upgradability will make SIMM an attractive scheme for minicomputer and peripheral makers, with the socket serving as a connector.

-Pingry

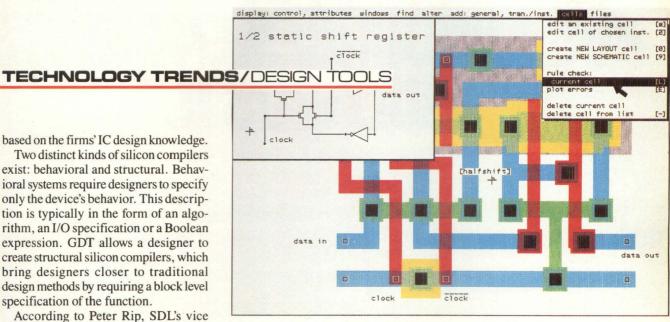

#### DESIGN TOOLS

### Programming Silicon Compilers For IC Design

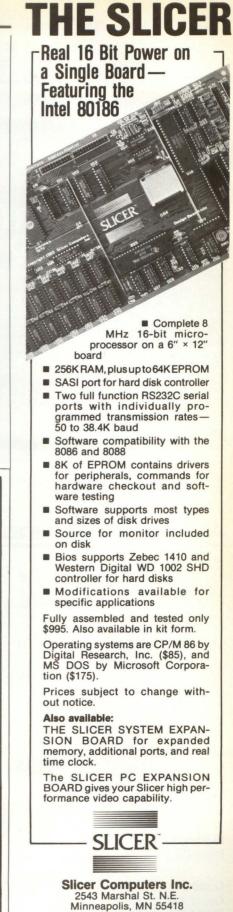

Only a few companies offer silicon compilation tools which allow system designers to rapidly generate custom ICs. One recent entry into this arena is Silicon Design Labs (SDL) (Liberty Corner, NJ) with a product for IC designers rather than system architects. The SDL software, called Generator Development Tools (GDT), allows IC designers to create customized silicon compilers by incorporating their own IC design knowledge into the compiler.

The primary difference between a silicon compiler built using SDL's software and other, off-the-shelf silicon compilers is the user's design expertise built into the tools. Competitors like Silicon Compilers Inc. (SCI) (San Jose, CA), Metalogic (Cambridge, MA) and Seattle Silicon (Seattle, WA) offer turnkey systems

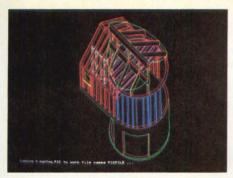

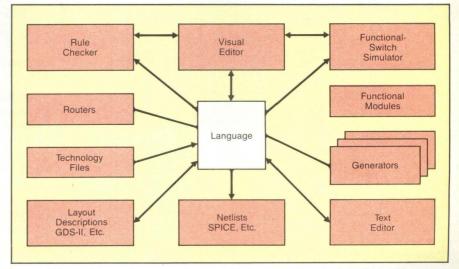

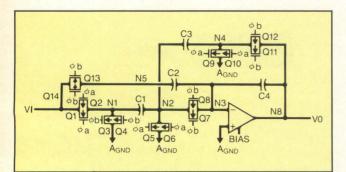

Figure 1: Customizing a silicon compiler with SDL's Generator Development Tools is done in an environment that includes interfaces to standard layout descriptions and common netlist formats. The L language is the heart of the development system.

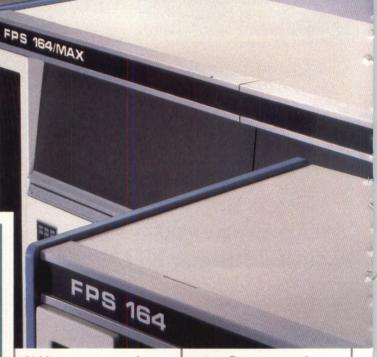

# THE FPS 64-BIT FAMILY: CONSIDER WHY THE MOST ACCESSIBLE SUPERCOMPUTERS MAY BE THE FASTEST WAY TO DO YOUR JOB.

The new 38 MFLOPS FPS-264, with 64-bit accuracy, large storage, and architecture refined to achieve a high percentage of its peak speed. For many applications, it can provide half the performance of the most popular supercomputer. Its moderate price and exceptional support liberates supercomputing from the realm of major corporate investment and puts it within practical reach of departments and teams.

FPS 264

when you get a supercomputer up and running is as important as how fast it runs. When you look beyond peak computing speeds to the practical realities of compute-intensive analysis and simulation, odds are that nothing else can take your job from start to finish as fast as the FPS

64-bit supercomputer family. Here's why:

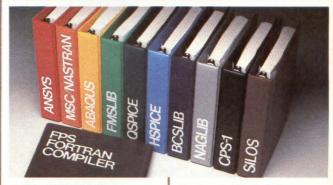

1. FPS protects and utilizes your existing software resources. FPS offers you an exceptional, proven software tool set. If your investment in FOR-TRAN is typical, the FPS Compiler will alone be a compelling advantage.

2. More applications software than for any other comparable com**puter.** Compare quantity and quality of compatible third party software packages—for structural analysis, circuit design, reservoir simulation, fluid flow analysis, chemistry and much more—and the FPS advantage widens.

3. The FPS 64-bit family makes supercomputing speeds affordable at the department level. Even teams with remote access to Crays<sup>®</sup> and Cybers<sup>™</sup> are

#### S U P E R C O M P U I E R S

comprehensive tools of its kind.

likely to find that the advantage of immediate, local access is well worth the sacrifice of standing in line for the "fastest" machines.

(Pr

System prices start at \$300,000 (U.S.) for the 11 MFLOPS FPS-164. The new 38 MFLOPS FPS-264, starting at \$640,000, achieves 4-5 times the speed of the FPS-164 on many applications programs. The multiple parallel processing units and peak 341 MFLOPS of the FPS 164/ MAX can run many matrix computations faster than supercomputers, for less than one-tenth the price.

#### **Family Specifications**

|                                   | FPS-264                                                                                 | FPS-164/MAX                                             | FPS-164                                                 |

|-----------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Peak speed,<br>MFLOPS             | 38                                                                                      | 33-341                                                  | 11                                                      |

| Dynamic range                     | 2.8 x 10 <sup>-309</sup><br>to 9.0 x 10 <sup>+307</sup>                                 | 2.8 x 10 <sup>-309</sup><br>to 9.0 x 10 <sup>+307</sup> | 2.8 x 10 <sup>-309</sup><br>to 9.0 x 10 <sup>+307</sup> |

| Word size                         | 64 bits                                                                                 | 64 bits                                                 | 64 bits                                                 |

| Main memory<br>capacity           | 4.5 MWords                                                                              | 15 MWords                                               | 7.25 MWords                                             |

| Maximum disk<br>storage capacity  | 16 Gbytes                                                                               | 3 Gbytes                                                | 3 Gbytes                                                |

| Precision                         | 15 decimal digits                                                                       | 15 decimal digits                                       | 15 decimal digits                                       |

| Vector registers                  | 4 x 2K                                                                                  | 124 x 2K (max.)                                         | 4 x 2K                                                  |

| Scalar registers                  | 64                                                                                      | 184 (max.)                                              | 64                                                      |

| Host interfaces                   | IBM, DEC                                                                                | IBM, DEC, Sperry                                        | , Apollo                                                |

| Program Develop-<br>ment Software | FORTRAN Compiler, Overlay Linker, Assembler, Object<br>Librarian, Interactive Debugger. |                                                         |                                                         |

#### **Family Performance Measures**

|                                                 | FPS-264 | FPS-164         | MAX   | FPS-164 |

|-------------------------------------------------|---------|-----------------|-------|---------|

|                                                 |         | 15 accelerators |       |         |

| Peak MFLOPS                                     | 38      | 341             | 33    | 11      |

| Peak MOPS                                       | 190     | 1705            | 165   | 55      |

| Peak MIPS<br>(Instructions are<br>multi-parcel) | 19      | 5.5             | 5.5   | 5.5     |

| Typical MFLOPS,<br>LINPACK<br>Benchmark         | 9.9     | 20.0            | 6.0   | 2.6     |

| Whetstones, KWIPS<br>(64-bit)                   | 19,000  | 5440            | 5440  | 5440    |

| 1000x1000 matrix<br>multiply, seconds           | 53      | 10              | 66    | 189     |

| \$K/MFLOPS (system price/peak speed)            | \$17K   | \$2.5K          | \$12K | \$27K   |

4. The FPS family is expandable. Proven dependable. Wellsupported. In other words, a safe, farsighted investment. You can upgrade your existing FPS computer, or evolve from one level of performance to another, with minimal disruption. And you can bank on a record of reliability that begins with exhaustive manufacturing testing and extends to our 30 field office service facilities worldwide.

The FPS optimizing FORTRAN-77 Compiler lets you easily adapt code to FPS' pipelined architecture in a form that is nearly as efficient as hand-coded assembly language. With extensions for asynchronous I/O and for enhancing compatibility with other compilers, it is one of most

> Ask your local Floating Point sales representative to help you develop your own strategy for accessible supercomputing. Contact Floating Point Systems, Box 23489,

Portland, OR 97223. Telex 360470 FLOATPOINBEAV. Sales offices worldwide. Call (800) 635-0938.

#### THE PROVEN POWER IN ACCESSIBLE HIGH-SPEED COMPUTATION.

Cray is a registered trademark of Cray Research, Inc., Minneapolis, MN. Cyber is a trademark of Control Data Corporation. Copyright © 1985, Floating Point Systems. All rights reserved. FPS SEC5227-1

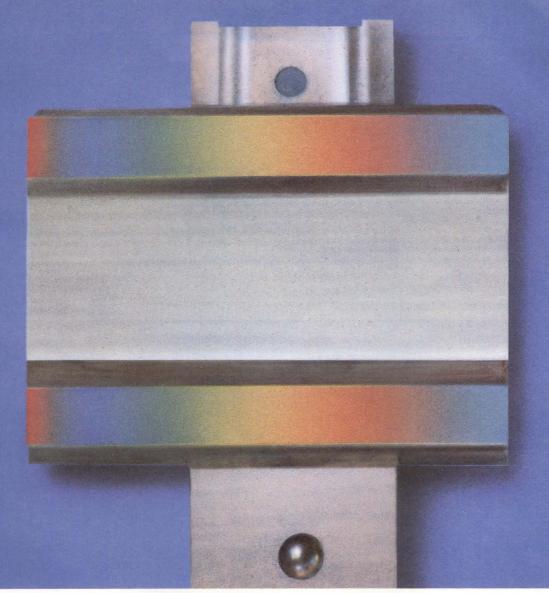

# **The Convergence Factor.**

Convergence: the single most critical factor in color CRT

critical factor in color Critical factor in color Critical factor in color Critical performance. Until now, Delta-gun tubes were the best way to achieve near perfect convergence, but only with costly adjustment electronics. costly adjustment electronics. Meanwhile, many in-line tubes are plagued by perceptible misconver-gence. Which can lead to poor picture quality. A poor quality image for your product. And poor, bleary-eyed operators. The Panasonic achievement:

low cost in-line color CRTs with better-than-Delta convergence performance.

Without complex adjustment electronics . . . and none of the convergence drift inherent in active correction systems. At last, high resolution in-line tubes with stable performance that stands up to the ravages of time and tough office/industrial environments.

The achievement of Panasonic high resolution in-line color CRTs.

How did we do it? With a preconverged in-line tube/yoke combination unlike any other. Our precision S/ST (saddle/saddle toroidal) deflection yoke is ideally matched to each tube, for near perfect convergence, high repeat-ability and stability over a wide range of operating conditions. We combine it with a specially-designed OLF (overlapping field lens) gun and unitized grid con-struction, providing spot unifor-mity across the entire screen and near-Delta resolution. The result: a triumph over the convergence factor. Find out what it can do for your next color ter-

convergence factor. Find out what it can do for your next color ter-minal or monitor, and ask about our full line of quality color and monochrome CRTs. Write or call: Panasonic Industrial Company, Computer Components Division, One Panasonic Way, Secaucus, N.J. 07094; (201) 348-5278.

**Circle 49 on Reader Inquiry Card**

Figure 2: L-Editor, an interactive graphical editor, is the primary means of viewing the output of generators written in L. Its role is to aid in the development of module generators. Multiple windows and pull-down menus are among its features.

president of marketing, merchant and captive semiconductor manufacturers are among the potential users that will benefit from GDT. NCR Microelectronics (Fort Collins, CO), one of SDL's first customers, has been a beta site for the product. The two companies also have an agreement involving the licensing of SDL's silicon compilation technology to NCR in exchange for NCR's CMOS fabrication processes.

ŵ

An important aspect of any new CAD/ CAE tool is how well it integrates into existing design environments. With this in mind, SDL designed a software package that translates layout and netlist data to and from various standard formats. For example, layouts can be output in GDS-II or CIF format, and netlists can be put in SPICE format. GDT is written in C, developed under UNIX and runs on workstations from Apollo (Chelmsford, MA) and Sun Microsystems (Mountain View, CA).

GDT is comprised of the L compiler and its routers, a graphical editor with an interactive rule checker and a mixedmode switch/logic simulator. The heart of the Generator Development Tools is L, a proprietary layout description language. Hierarchical descriptions of IC layouts, layout generators and circuit/logic elements are created with L.

On the lowest level, the language describes geometric objects such as polygons, rectangles and lines. Geometric objects are included in L to allow the designer to enter geometric constructs but are not the preferred working level. Higher level electrical objects such as wires, contact cuts, terminals and transistors provide a more powerful means to build a generator. Designers lay out handcrafted ICs by directly placing and interconnecting these circuit primitives. This is done with either the graphical editor or the text editor.

Since the tools are based on a hierarchical language, creating layouts and layout generators can be done in a structured fashion. The basic building block in L is a cell containing wires, polygons and transistors. Cells can contain calls to other cells, and generators can call other generators. L also has automatic routing statements that call various routers to wire cells together. The particular router accessed depends on the configuration of the module being generated.

L-Editor and L-Simulator are the other parts of the tool set. L-Editor is an interactive graphical editor that also does rule checking and logical simulation of L files. It reads all L language constructs and is used to view the output of generators written in L. L-Editor has an interactive interface to L-Simulator. An eventdriven logical simulator, L-Simulator can mix switch simulation of individual transistors with functional simulation of arbitrarily sized logical blocks. The complexity of these blocks ranges from transistors to VLSI functions.

When using GDT, generators can be built from the top down or the bottom up or a combination of the two styles. Top down design begins with blocks interconnected using L-Editor and described functionally via L-Simulator. High-level design verification is then performed by executing test vectors with L-Simulator. As the design progresses, functional blocks are given more detail. The procedure continues until the blocks can be replaced with low-level circuit generators.

Bottom up design can be done in several ways. One method uses L-Editor. The procedure entails drawing the layouts, simulating the circuit and running a design rule check. Timing verification is then performed by passing the netlists to a timing simulator.

When using silicon compilers built with GDT, as with other structural compilers, the designer's primary task is to define the functional blocks necessary to implement the device. By inputting the chip's architectural specification and letting the machine generate the logic and layout, the system architect is removed from lower level design tasks. The main advantage of a custom-built compiler is that a particular IC designer's expertise may be built into the system.

# THE MOST SPECTACULAR BUS ANNOUNCEMENT SINCE MULTIBUS II.

INTEL CORP.

SHIP TO:

Advanced Systems Inc. 77 Industry Drive San Francisco, CA 94108

Attention: Mark Dickerson (415)445-3000

da.

VENDOR MU ABOVE MEN DENCE, INV WHEN BETU

SHIPPING MEMO NO.

| 1 | 1 | 12 | 1 |

|---|---|----|---|

| 0 |   | V  |   |

|   |   |    |   |

| ITEM | QUANTITY | UNIT               | INTEL PART NO. | DESCRIPTION                      |  |  |

|------|----------|--------------------|----------------|----------------------------------|--|--|

| 1    | 10       | deringen tallestre |                | iSBC 286/100 SMHz MBII CPU board |  |  |

| 2    | 2        | anne. Airea        |                | iSBC MEM/312 512 Kbyte Mem board |  |  |

| 3    | 4        |                    |                | iSBC MEM/310 1 Mbyte Mem board   |  |  |

| 4    | 2        | -                  |                | iSBC MEM/320 2 Mbyte Mem board   |  |  |

| 5    | 2        | minitia contan     |                | iSBC MEM/340 4 Mbyte Mem board   |  |  |

| 6    | 10       | -                  |                | iSBC CSM/001 Cent. Serv. Module  |  |  |

| 7    | 1        |                    |                | iRMX 86II R.O RMX86 MBII R-t OS  |  |  |

| 8    | 5        | -                  |                | iSBC PKG/609 9 slot cardcage &   |  |  |

|      |          |                    |                | PSB backplane                    |  |  |

| 9    | 5        | -                  |                | iSBC PKG/903 3 slot iLBXII       |  |  |

|      |          | and the set        |                | backplane                        |  |  |

| LO   | 1        | ARTING COUNTY      |                | iSDM 286 R.O 286 System Debug Mo |  |  |

You've heard the announcements about MULTIBUS II specs.

But now there's an even more spectacular announcement:

The first wave of MULTIBUS II products is here.

Take the 286/100 Single Board Computer. It's the first commercially available 286based board that runs at 8

### **HIPPING MEMO**

April 12, 1985

CODE 0404 348 DIVISION / DEPT.

#### EFERENCE THE D. ON ALL CORRESPON-S, PACKING LISTS, ETC. G MATERIALS TO INTEL.

MHz. It also introduces the iLBX II<sup>™</sup> interface and is iSBX<sup>™</sup> compatible.

Then there's our family of cached-based memory boards, from ½ to 4 MB, which give zero wait state performance over the iLBX II bus. And because the boards are configured in software, there are no jumpers. Anywhere.

There's software support, too, with the iRMX<sup>™</sup>86 MULTIBUS II support package. It supports the same tools, languages and utilities as the

iRMX 86 operating system. And for software development support, the iSDM 286 System Debug Monitor is also available. So you'll be up and running in no time with products based on the advanced MULTIBUS II architecture. We designed the

32-bit MULTIBUS II architecture to give you a quantum leap in performance where you need it: in a multiprocessing environment.

To get such radically improved performance we had to redefine bus architectures with radically advanced concepts.

Like distributed arbitration. It breaks the bus access bottleneck and helps maximize system level performance for multiprocessing environments.

And we're taking a unique approach to interprocessor communication. It's called message passing. It'll free up © 1985 Intel Corporation the CPU from bus management tasks and put it back to work on your application.

And the MUITIBUS II architecture has the reliability to back up that performance reliability that surpasses everything else commercially available.

How?

By being the first open systems bus to incorporate parity protection on address, data and control lines. By being the only bus that allows every board to perform self-test.

Even the 32-bit bus inter-

face is reliable. It not

only fits onto one

DIN connector, but

it's been designed

to be integrated

onto one VLSI chip.

And that's more

reliable than two

or three or more. But the most important feature of MULTIBUS II is

that Intel and other manufacturers are already working on dozens more MULTIBUS II products.

Just the kinds of products you need to meet the needs of your market.

For complete information, call us toll free at (800) 538-1876. Or write Intel Corporation, Lit. Dept. W225, 3065 Bowers Avenue, Santa Clara, CA 95051.

So don't miss this bus. Because you could have a short ride on any other.

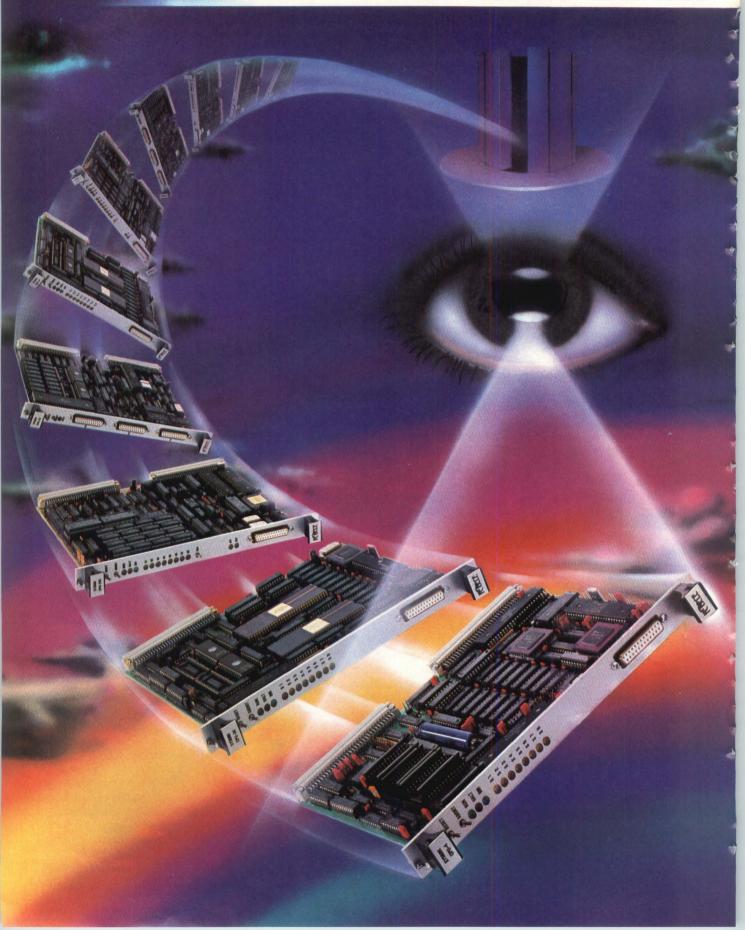

# ONLY EKONIX®

# DOES SO MUCH IN HIGH PERFORMANCE DIGITAL IMAGING CAMERAS.

EIKONIX

EIKONIX\*high-performance digital imaging cameras offer unique capabilities that clearly distinguish them from all others.

CCD or Photodiode Technology

Only EIKONIX offers a choice of high-resolution cameras employing either linear CCD (charge-coupled device) or photodiode technology. In fact, EIKONIX offers the highest-resolution CCD camera available anywhere, with up to 20 million pixels per image (4096 x 5200). You can choose the economy and low-light capabilities of a CCD

and low-light capabilities of a CCD camera, or the greater dynamic range of a photodiode camera, *without sacrificing high resolution*.

#### Color or Monochrome

Only EIKONIX has a family of high-resolution cameras available for either monochrome (256 gray-scale levels) or color (a palette of 16 million colors) applications.

#### More User Control

Only EIKONIX cameras use a precision stepping-motor/lead-screw/ ball-slide stage mechanism, which provides precise positioning of the array and eliminates one-dimensional

smearing. In addition, this mechanism allows asynchronous operation, so the user can control both scan speed and data collection rate. This eliminates the need for a separate "frame grabber" or dedicated processor, and frees the host computer for multi-tasking.

#### Buy Just What You Need

Only EIKONIX' broad product line lets OEMs and end users match needs precisely. Configurations range from bare-bones digital camera heads through complete image acquisition subsystems, including cameras, light sources, control electronics, imaging software, and interfaces for many widely used computers (including most DEC and Multibus-based systems).

#### **More Applications**

Only EIKONIX offers the performance and flexibility to handle the broadest range of the most demanding applications, including mapping, engineering drawing digitizing, graphic arts, CAD/ CAM input, office automation, X-ray storage and analysis, textile pattern design,

geological imaging, communications, animation and microscopy.

#### **EIKONIX Know-How**

Only EIKONIX digital imaging products are backed by our 17 years of experience in matching advanced electro-optical technology to a widening world of applications.

To find out what we can do to support your digital imaging applications, contact EIKONIX, 23 Crosby Drive, Bedford, MA 01730, (617) 275-5070.

A KODAK COMPANY Circle 56 on Reader Inquiry Card

Copyright 1985 EIKONIX® Corporation. DEC is a trademark of Digital Equipment Corporation. Multibus is a trademark of Intel Corporation.

#### **TECHNOLOGY TRENDS**

SYSTEMS

Y

塘

### Supercomputer Exploits Parallel Processing

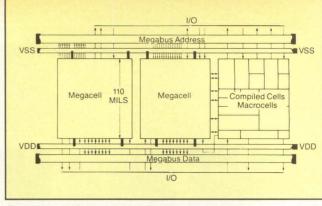

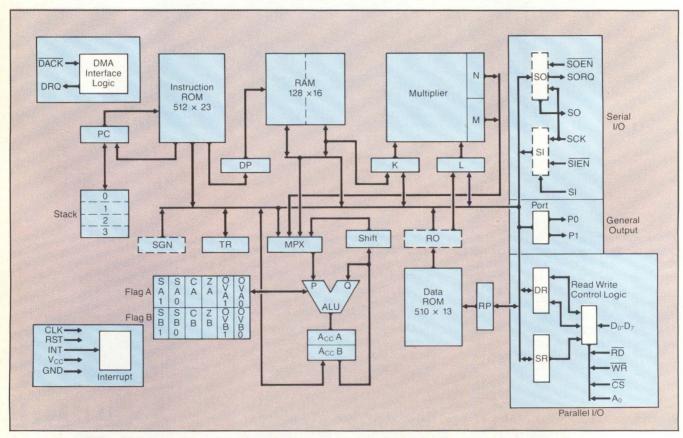

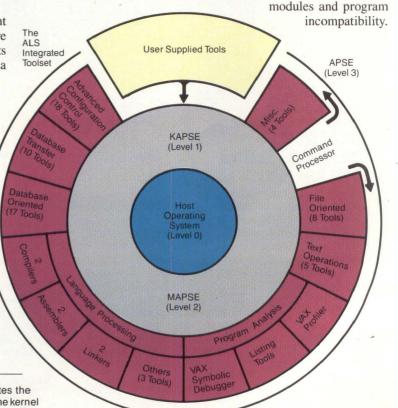

As the cost of processing elements decreases, it is possible to build computer systems with a number of processors sharing the burden of executing complex programs efficiently. Alliant Computer Systems Corp. (Acton, MA) has combined three forms of parallel processing, increasing not only system throughput but also program execution speed in the FX series of computers. This combination shows why there is some confusion when describing the sorts of architectures currently on the market.