NOW ELECTRO INCLUDING IMAGI

VME BUS CHALLENGES MULTIBUS I AND MULTIBUS II

TEST DRIVING A SILICON COMPILER

STREET.

PRINTED CIRCUIT BOARD DESIGN

FIRM

38134

00

EMPH

38134

T

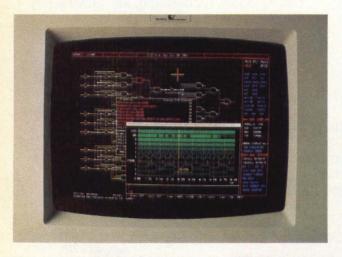

MICROSTORAGE GRAPHICS ARCHITECTURE

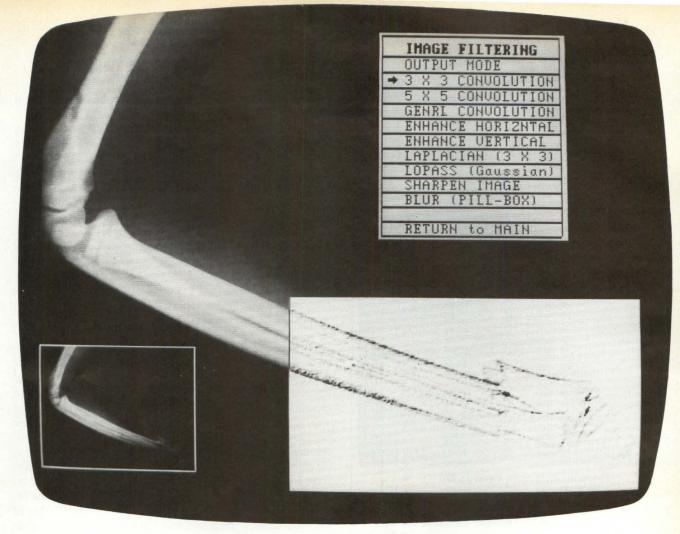

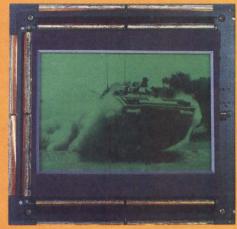

# A clear difference in real-time **Image Processing**

Whether you need a turn-key system or a peripheral to connect to your computer, the **TRAPIX**<sup>M</sup>**5500** Image Processors have been carefully designed to meet your specific needs. They're compact and rugged enough to withstand most hostile environments, yet they carry a commercial price tag and are backed by a full year factory warranty — the best in the industry. They don't require special power or air conditioning and they use standard programming languages and operating systems — features designed to make them easy to ownanduse

It's both flexible and expandable. Even the smallest TRAPIX™ 5500 is a full-function, image processor that can grow to meet your future requirements. Its modular design and Q-bus/Unibus architecture let you develop cost-effective solutions for any image processing application. To tailor your own solution, simply select any subset of the following capabilities:

#### **Image Acquisition**

- Monochrome, binocular, color or

- multispectral input

- Camera, CCD, infrared or video tape Line scan or array to 2048 x 2048

#### Analog or digital to 12.5 MHz 8-, 10- or 12-bit digitization

- Image Storage/Retrieval

- Up to 16 mbytes of dual ported image memory

- From one to 32 bits per pixel

Images to 4096 x 4096 pixels

- Real time disk storage up to 6800 images

#### Image Processing/Analysis

- Real-time logical, arithmetic processing

- Convolution, warping, and FFT Morphological, machine vision processing

- Continuous interpolated magnification/minification

- High-speed vector generation

- User-programmable 32-bit signal processor (TMS-320)

- Real-time histogram generator

- Computing/Networking

Standalone with internal LSI-11 or MicroVAX

- Bus-connected to any Q-Bus or Unibus computer

- Easily interfaced to non-DEC computers

#### Ethernet, DECnet, IEEE 488

- Software

- · Proven library of ready-to-use image

- processing and analysis functions Turn-key and custom software availability

- Support for Fortran, C, Pascal and

- assembly language

RT-11, TSX-Plus, RSX-11M, VAX/VMS, UNIX

As you can see, the **TRAPIX™ 5500** offers a clear solution to your image processing requirements. For more information or applications assistance, call or write RCI.

Registered trademarks: UNIX: Bell Laboratories, Ethernet: Xerox, TSX-Plus: S&H Computer Systems, VMS, RSX-11, RT-11, LSI-11, MicroVAX, DEC, DECnet: Digital Equipment.

COGNITION CONCEPTS, IN 924 Incline Way, P. O. Box 8510, Incline Village, Nevada 89450 (702) 831-0473 Telex: 753168 **INNOVATORS IN IMAGE PROCESSING**

Circle 2 on Reader Inquiry Card

# Now your computer can have 20/20 vision.

### Now with real time image processing and IBM PC compatibility.

a and a

Datacube continues to be the single source leader in image processing and graphics for your Multibus, Q-Bus, and now IBM PC's. Solutions are available from single boards to fully integrated systems.

Resolutions range from 320H x 240V to 1400H x 1100V with pixel depths from 1 to 24 bits.

The new SP-123 offers advanced signal processing of high resolution black & white or full color images at the rate of 14 megapixels per second.

The new IVG-128 is a complete video acquisition and display module on a single IBM PC compatible card. It features input & output look up tables, an 8-bit digitizer, and RGB 8-bit outputs.

The new DC-1000 and DC-1500 systems are complete workstations capable of video acquisition and image processing.

Datacube products provide reliable vision and real time image processing for robotics, medical imaging, surveillance, inspection, teleconferencing, animation, etc. And at surprisingly low prices.

Call or write for our new Product Guide of Multibus, Q-Bus, and IBM PC compatible boards and systems. Datacube Incorporated, 4 Dearborn Road, Peabody, MA 01960, Telephone: (617) 535-6644. Western Sales Office: Telephone: (408) 737-9978.

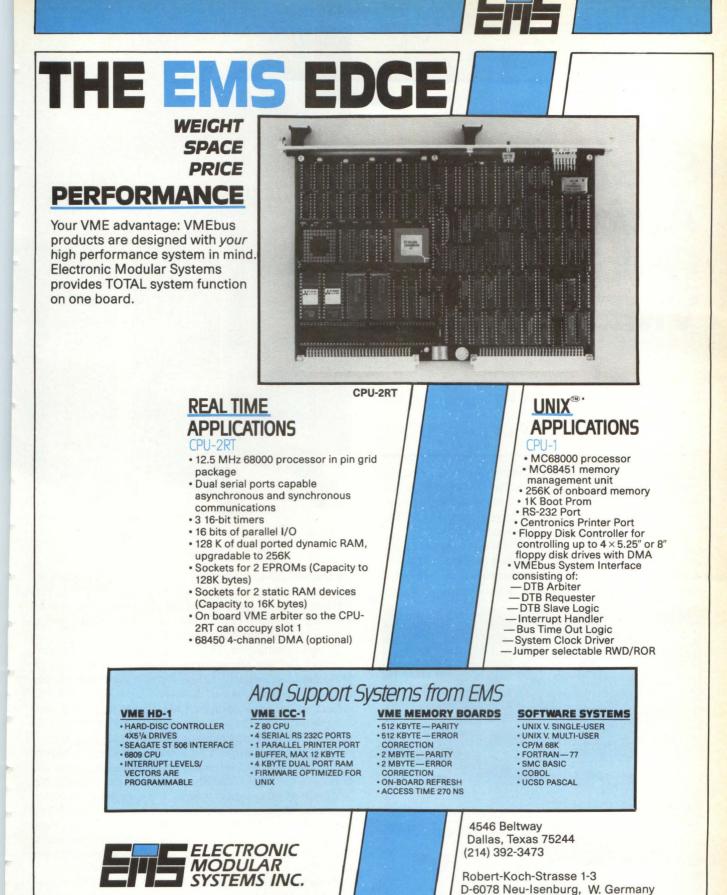

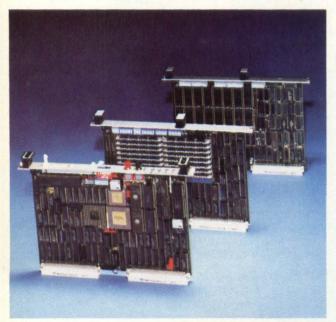

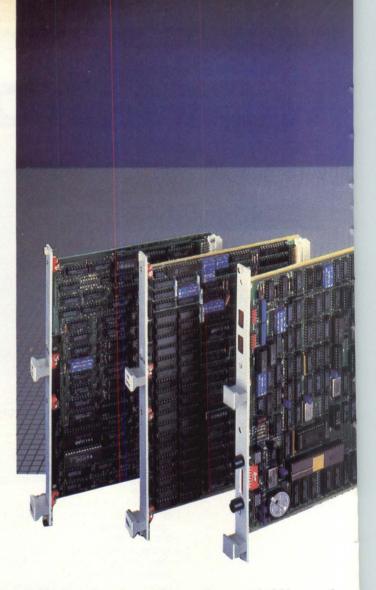

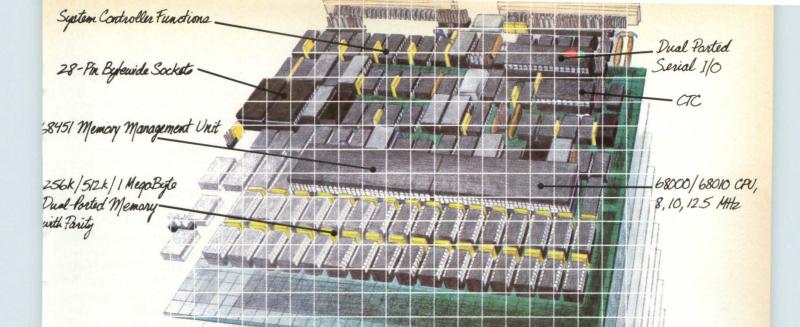

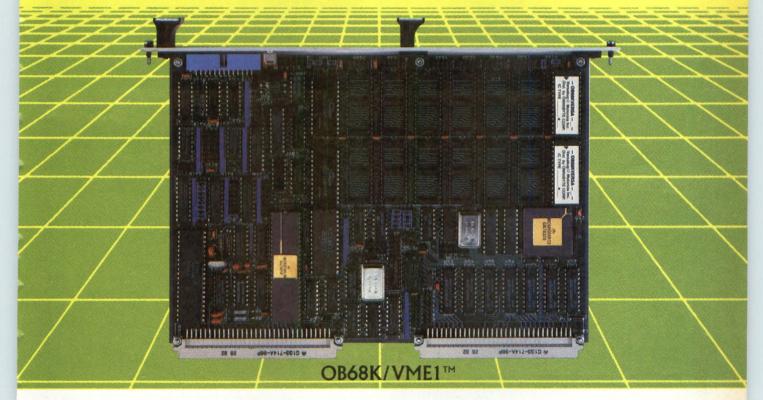

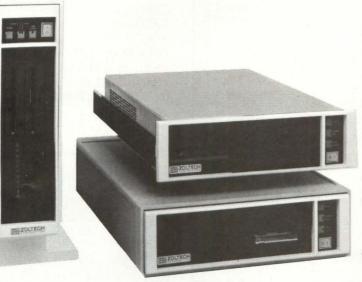

# FORCE COMPUTERS System 68000 VMEbus

# Single board solutions for 16/32 bit "open systems" in industrial, business, and scientific environments

If your application requires advanced technology available in production quantities if quality, reliability, and price/performance ratio are the major criteria for supplier selection – then compare our product portfolio with other alternatives.

- Three CPU's for most applications from intelligent I/O controllers to multiuser/ multitasking environments with powerful UNIX\* or real time operating software PDOS\* and up to 1M byte of on-board memory: CPU-1B, CPU-2, CPU-3.

- Two DRAM Boards: 512KB and 2MB; two SRAM Boards: 128KB and 512KB. RAM/ROM Board: 512KB (max.); DRAM-1, DRAM-2, SRAM-1/2, RR-1/S/E

- Mass memory interface boards with either direct control of up to seven drives (WFC-1) or intelligent VMEbus interface to SASIbus with DMAC (SASI-1).

- Six-channel serial I/O board with Multi-Protocol-Communications-Controller (SIO-1).

- 32-channel parallel I/O boards either optically isolated (1000V) with DMAC (OPIO-1) or TTL-level with 64 mA drive capability signals (PIO-1).

- Intelligent high resolution graphics subsystem (master/slave) with resolution of 1024 x 1024 pixels and up to 12 bits of pixel depth. Powerful graphics operation through local 68000 MPU in parallel with 7220 graphics controller(s) GDC-1M/1S.

- Winchester/Floppy drive modules with up to 80 M bytes: WFMOD-20/80.

- Auxiliaries: Backplanes, chassis, power supplies.

- A variety of Software Products, e.g.:

PDOS\* Real-Time, Multi-Tas

- Real-Time, Multi-Tasking, with Basic interpreter, Pascal, Fortran 77, and C Compilers.

COHERENT\* – UNIX\* V.7 compatible with C Compiler, Pascal and Fortran 77 in preparation.

- UNIX\* System V, Multi-User, Multi-Tasking.

- In development: memory boards with byte parity and 32 bit addressing; dedicated LAN-Controller; high performance communication I/O.

Supported by a worldwide network of distributors and representatives, FORCE Computers is recognized by its customers (and competitors) as the leading supplier of 68000/VMEbus board products.

\*PDOS is a trademark of Eyring Research, COHERENT is a trademark of Mark Williams Co., UNIX is a trademark of AT&T.

Consider, compare, and contact: FORCE COMPUTERS, INC.

# **DIGITAL DESIGN**

MAY 1985 VOL. 15 NO. 5

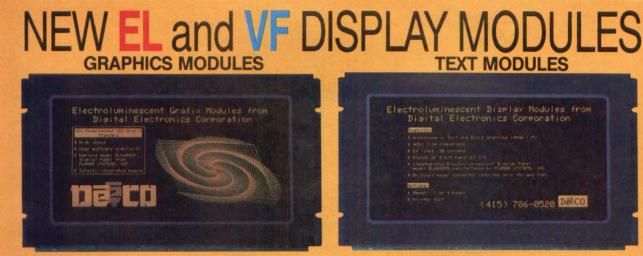

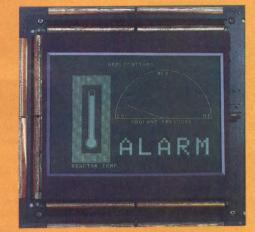

ICs improve graphics displays

#### **TECHNOLOGY TRENDS**

1 CAD / Designing ICs With A Silicon Compiler • Gate Array Design Update — Design Verifier Flags Potential Problems

22 Software / PC-Based Software Produces High Resolution Graphics Files

24 ICs / 64K X 1 SRAMs Vie For DRAM Applications

26 **Communications** / Options Multiply For High Speed Unibus Communication • Fiber Optic Transmission Schemes Expand Standard Local Area Network Possibilities

| 10 | Editor's Comment      | 100 | <b>New Products</b> |

|----|-----------------------|-----|---------------------|

| 12 | Hotline               | 123 | New Literature      |

| 30 | Product Index         | 124 | Calendar            |

| 81 | <b>Reader Service</b> | 124 | Advertiser Index    |

| 94 | New Product Focus     |     |                     |

|    |                       |     |                     |

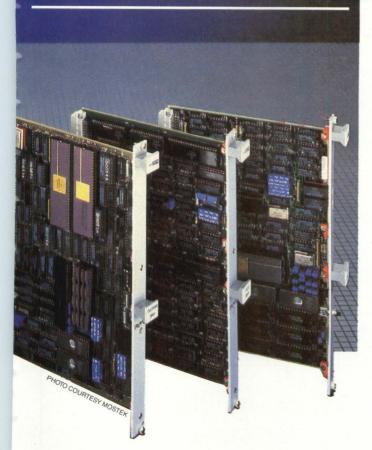

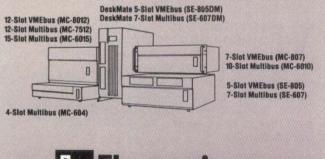

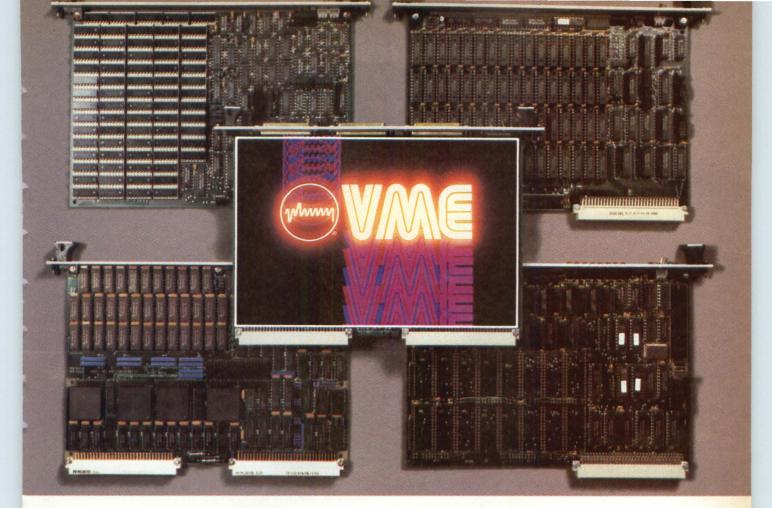

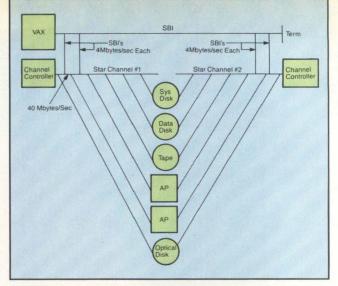

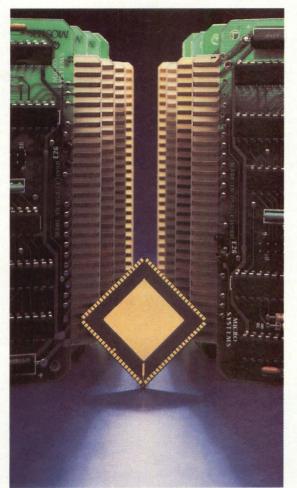

#### ON THE COVER

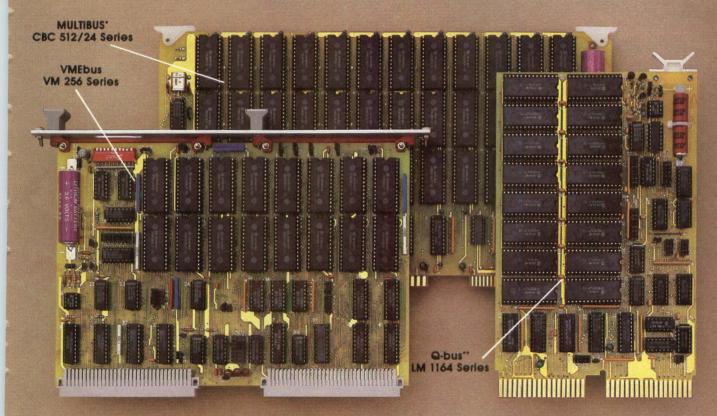

Currently the only widely supported 32-bit bus structure, the VME bus, is being considered by many systems integrators as a logical 32-bit upgrade solution to their existing Multibus designs. The front cover this month depicts three new products from Motorola Microsystems including a 68020-based CPU board. Photo courtesy Motorola Microsystems, Inc.

Published monthly thirteen times a year with two issues in November. Subscription rates for non-qualified subscribers (US and Canada) — \$40/yr; foreign — surface mail — \$50/yr; airmail — \$85/yr. Single copies — \$4. Copyright 1985 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, Berkshire Common, Pittsfield, MA 01201 ISSN 0147-9245.

53

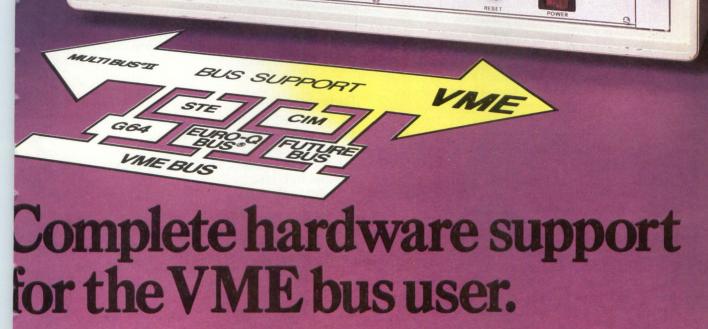

34 Systems Architect's Guide A tremendous number of vendors have endorsed the VME bus over the past six months.

#### FEATURES

#### Systems Architect's Guide To The VME Bus

by Dave Wilson

At the present time, only a few buses can support 32-bit processors — VME, Multibus II, NU Bus and Futurebus. Of these, only one CPU board is available on the Multibus II, none on NU Bus or Futurebus while VME sports over 30.

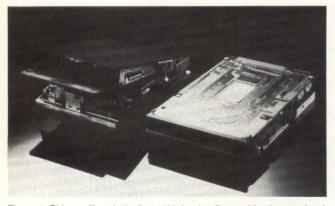

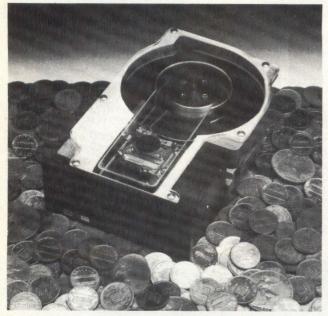

#### Little Drives That Can

by Bob Hirshon

Mass memory devices fitting the 31/2" form factor have emerged to fill the demands of designers who need to get the most out of every cubic centimeter.

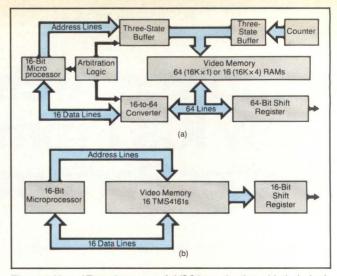

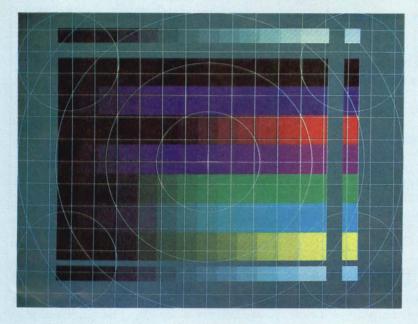

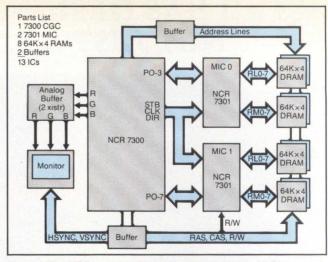

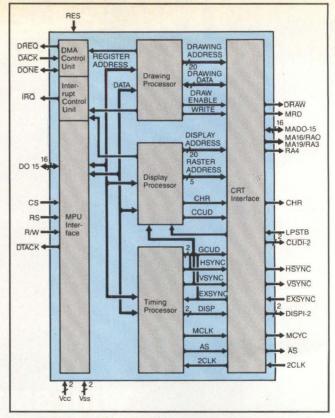

#### Graphics Architecture – New ICs Promise Better Performance

by Gregory MacNicol

Driven by user demands for faster, smaller, more capable and less expensive computer graphic systems, semiconductor manufacturers are introducing chips that provide rapid bit-mapped medium to high resolution displays.

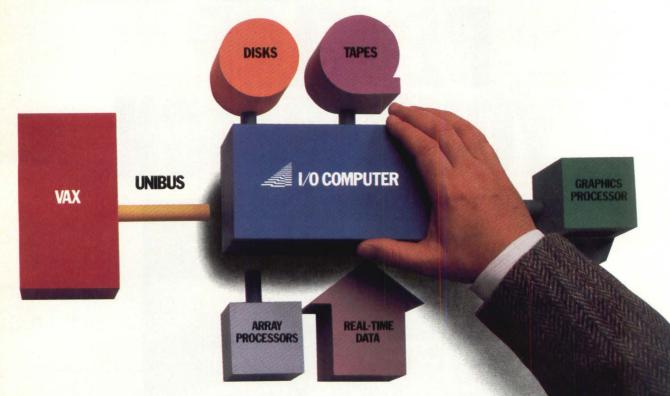

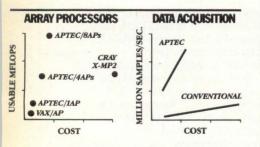

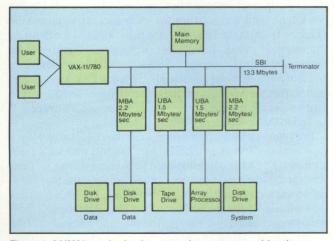

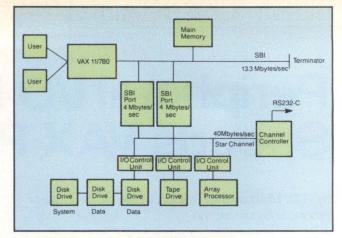

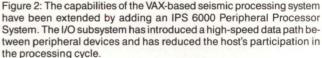

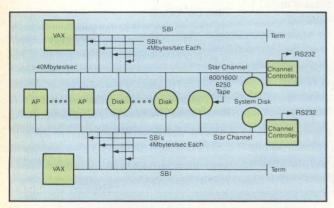

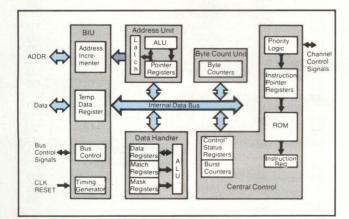

#### Peripheral I/O Processor Speeds VAX Performance

by H.D. Meitzen and Delbert L. Taylor

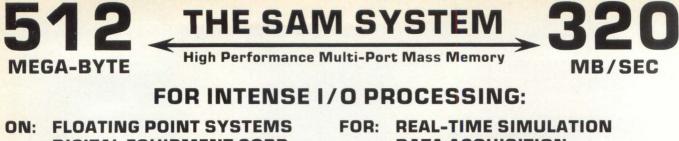

The optimum computer system for work such as seismic processing, signal processing in data communications, and real-time graphics combines a multiuser interactive environment for controlling data processing with an I/O subsystem that permits peripheral devices to exchange data at very high speeds with minimal attention from the host.

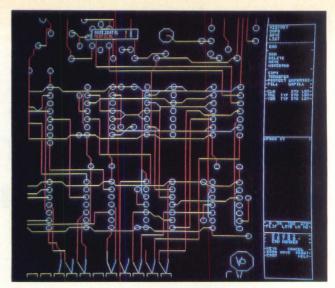

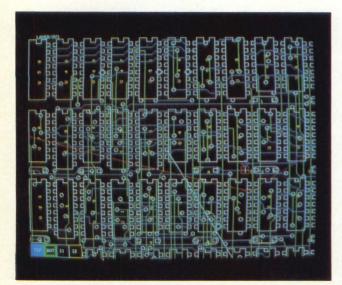

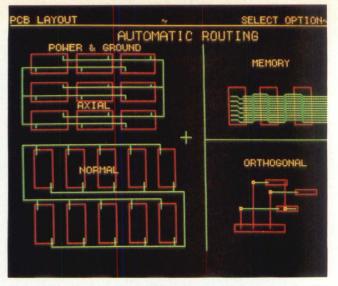

#### Printed Circuit Board Design Demands Versatile Integrated Tools

#### by Julie Pingry

Board design programs need flexibility and interactive features to accommodate mixing TTL with ECL, CMOS and discrete analog devices on increasingly dense and large boards.

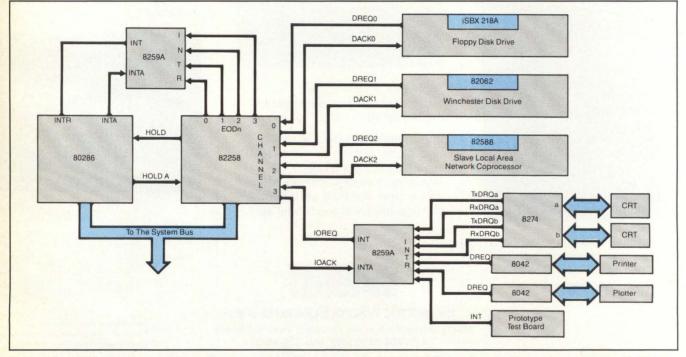

#### DMA Controller Relieves Host Of I/O Management

by Scott Searcy

I/O subsystems for high-performance computers must not only process and transfer large amounts of data, but also interface to a large number of peripheral devices.

### LET RETICON PUT THE VISION INTO YOUR NEXT DESIGN.

Because we offer the broadest range of image sensors available—from linear to area and circular arrays—it's easier for you to find the right one for your application. And in case you can't, we're prepared to put our experience and expertise to work for you in developing a cost-effective custom configuration that meets your needs. Thousands of EG & G RETICON solid state image sensors are already in use in applications such as page and character scanning, spectroscopy, robotics, and non-contact inspection instruments. Contact us today for complete information. At RETICON, the solution to your imaging application is within sight. Sunnyvale, CA 94086-4197 (408) 738-4266 Chicago (312) 640-7713; Boston (617) 745-7400; Japan 03-343-4411; England (0734) 788666; Germany (089) 92692-666.

**Circle 6 on Reader Inquiry Card**

#### **DIGITAL DESIGN**

| Editor in Chief                                                                                   | John Bond                                         |  |  |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| Managing Editor                                                                                   | Debra A. Lambert                                  |  |  |  |

| News Julie Pin                                                                                    |                                                   |  |  |  |

| Features:                                                                                         |                                                   |  |  |  |

| Semiconductor Technolo                                                                            | Dave Wilson,<br>Executive Editor                  |  |  |  |

| Electronic Imaging                                                                                | Andrew Wilson,                                    |  |  |  |

| Design Technology                                                                                 | Senior Technical Editor<br>Ronald E. Collett,     |  |  |  |

| Systems Architecture                                                                              | Senior Technical Editor<br>Brita Meng,            |  |  |  |

| Oystenis Arenicetare                                                                              | Technical Editor                                  |  |  |  |

| New Products Editor                                                                               | Terri Lamneck                                     |  |  |  |

| Western Technical Editors<br>(408) 356-0405                                                       | Gregory MacNicol<br>Joe Aseo                      |  |  |  |

| Copy Editor                                                                                       | Sherri Mack                                       |  |  |  |

| Directory Editor                                                                                  | Dawn Bursk                                        |  |  |  |

| Editorial Assistant                                                                               | Tia Partin                                        |  |  |  |

| Contributing Editors:<br>Electronic Imaging<br>Peripherals                                        | Hugh Aldersey-Williams<br>Bob Hirshor             |  |  |  |

| Senior Art Director                                                                               | Tilly Berenson                                    |  |  |  |

| Advertising Production Ma                                                                         | nager Martha Watjen                               |  |  |  |

|                                                                                                   |                                                   |  |  |  |

| Production Director                                                                               | Paul Dadarria                                     |  |  |  |

| Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician                                          | William Manning Jr.<br>Don Schaaf<br>Paul Christo |  |  |  |

| Marketing Director                                                                                | Charlotte King                                    |  |  |  |

| Promotion Manager                                                                                 | Elaine Bull                                       |  |  |  |

| Marketing Assistant                                                                               | Sharon Lembo                                      |  |  |  |

| Research Carolyn                                                                                  | Wulfsberg, Peter Micheli                          |  |  |  |

| Circulation Director                                                                              | Hugh J. Dowling                                   |  |  |  |

| Circulation Supervisor Maggie Hayes-Mivil                                                         |                                                   |  |  |  |

| Circulation Staff                                                                                 | Miriam Hlister,<br>Nancy McPherson                |  |  |  |

| Reader Service (413) 499-                                                                         | 2550 Terri Giroux                                 |  |  |  |

| Direct Mail                                                                                       | Deborah Goldstein                                 |  |  |  |

| Executive Administrator                                                                           | Suzanne Levecque                                  |  |  |  |

| General Administration Janet Pitt<br>Deanna Richardson, Nancy Deveau<br>Debra James, Karen Bowmar |                                                   |  |  |  |

President, Ronald W. Evans

Publisher, James R. DiFilippo

#### **Advertising Sales**

Northeast: Terry L. Willins (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic/Southeast: Richard V. Busch (609) 921-7763, 40 Stony Brook Lane, Princeton, NJ 08540; Pamela S. Fedor (201) 741-5784, 700 River Road, Fair Haven, NJ 07701

Midwest, South Central: Hank Bean, Rob Robinson (312) 794-1515, Edens East Office Center, 6200 N. Hiawatha, Suite 215, Chicago, IL 60646

Northwest: Carole Sacino, (408) 356-0405, 15951 Los Gatos Blvd., Suite 7, Los Gatos, CA 95030

Southwest: Mike Prewitt, (714) 851-8550, 2041 Business Center Dr., Suite 206, Irvine, CA 92715

National Postcard Sales: Jon Binder (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

MAY 1985 I DIGITAL DESIGN

# **32 BIT TECHNOLOGY FROM A 2 BIT START-UP?**

### **ABSOLUTELY!**

We're Goodspeed Systems. And although we're new on the scene, we've been doing big things. We took an exciting new chip set — National's 32000 Series — and created a 32-bit single board computer. The GS-32 delivers true *32/32* performance — plus some big advantages no one else can match:

**The Time Advantage:** We can shorten your time to market with our tested, proven boards. The GS-32 is available now; there's no wait for the 32-bit power you need today.

**The Design Advantage:** Our flexible, fully socketed design offers 32-bit processing, up to 2 MB memory, I/O and mass storage interfacing, *all on a*

single board. It's ready to plug in or expand to your specs. Software options scaled to your application level, too. Now you can have 32-bit performance without a workstation or even card cage.

**The Price Advantage:** The GS-32 delivers full 32-bit performance at a fraction of the cost of bussed systems. Our price-to-power ratio is unmatched. And that means it can slash *your* overall system costs for that competitive edge.

The GS-32 from Goodspeed Systems. The little company with the big board. If you're ready for 32-bit technology, call for the name of your representative:

#### 1-800-243-8160

**GOODSPEED** SYSTEMS 23 Main Street, P.O. Box 29, East Haddam, CT 06423

**Circle 8 on Reader Inquiry Card**

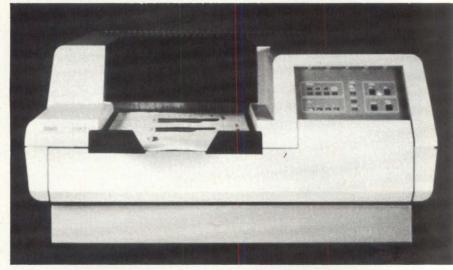

#### EVERYONE IS TALKING ABOUT OPTICAL DISK TECHNOLOGY. ALCATEL THOMSON GIGADISC DELIVERS IT!

Gigadisc, the new laser memory system developed for low-cost storage of large quantities of data is proving itself in field applications worldwide.

If you require a high-capacity random access memory which includes non-erasable removable media with excellent archival properties, Gigadisc is the right product for you. To maintain the lead in today's competitive market, you need the Gigadisc to deliver an attractive system offering low-cost on-line and off-line storage.

Features like one gigabyte-per-side capacity, random data retrieval, SCSI interface and a fieldproven design make Gigadisc one of the most appealing laser optical memory products available today.

> In the U.S.A. call (213) 543-5537 In France call (1) · 630 · 24 · 72

licatel nomson GIGADISC

Circle 7 on Reader Inquiry Card

### REPRINTS

**DIGITAL DESIGN** will reprint any article from past or present issues. Reprints are custom printed. Minimum order: 1,000 copies. Purchase order or letter of authorization required.

Allow one month from receipt of order for delivery, unless previously arranged and confirmed.

Advertisements alone can also be reprinted. Call (617) 232-5470, and ask for reprints.

#### EDITORIAL AND SALES OFFICES

DIGITAL DESIGN, 1050 Commonwealth Avenue, Boston, MA 02215, Telephone: (617) 232-5470

#### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215, (617) 232-5470. Brian Rowbotham, Chairman; Ronald W. Evans, President; Charles Benz, Vice President.

#### **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 1050 Commonwealth Avenue, Boston, MA 02215 (617) 232-EXPO. The following is a list of conferences produced by the Expositions Group:

ATE West CADCON West ATE Northwest ATE East CADCON East ATE Central CADCON Central Electronic Imaging

In addition to DIGITAL DESIGN, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronics Test • Computer & Electronics Marketing

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronics Times • What's New in Electronics • What's New in Computing • Business Computing and Communications • Communications Systems Worldwide.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral manufacturers integrating OEM's and commercial end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

ABP **VRPA**

#### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

Circulation Department, **DIGITAL DESIGN**, Berkshire Common, Pittsfield, MA 01201

Subscription rates: non-qualified subscribers (US and Canada) – \$40/yr; foreign – surface mail – \$50; air mail – \$85. Single copies – \$4.

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by Morgan-Grampian Publishing Co. for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$2.00 per copy, plus \$.25 per page is paid directly to CCC, 21 Congress St., Salem, MA 01970. 0147-9245/84 \$2.00 + \$.25.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

MAY 1985 I DIGITAL DESIGN

# Sell someone a Genicom 3000, and it may be some time before you hear from them again.

From offices to factories across the country-hour after hour, day after day-Genicom 3000 printers have been proving their quality and reliability under even the toughest conditions for years.

The result has been a large number of very satisfied customers, which means a large number of satisfied OEM's. But durability is only part of the Genicom 3000 printer advantage.

The Genicom 3000 family of printers offers multimodel flexibility combined with single design simplicity to give OEM's real dollar savings with price/ performance matching for every customer. Parts

**GENICOM** 3404

# Genicom 3000 printer reliability can keep a customer happy for years.

commonality. Easier servicing. Single source supply. Plus you can select speeds from 180-500 cps draft/EDP, 45-100 cps NLQ, single or multi-

mode printing, automatic sheet feeders, document inserters, multi-color printing and graphics, plus more. There's such a diversity of models, features and options, you can choose just the right printer and you don't have to pay for things you don't need.

See how long you can keep your customers satisfied...with the long lasting, field proven printers that have earned the respect of OEM's nationwide-the Genicom 3000 family.

(PRO) (LAN) (PON) (LAN) (LAN)

Genicom Corporation, One General Electric Drive, Waynesboro, VA 22980 In Virginia, call 1-703-949-1170 For the solution to your printing needs call TOLL FREE 1-800-437-7468 **Circle 57 on Reader Inquiry Card**

#### EDITOR'S COMMENT

#### **DIGITAL reDESIGN**

A s promised last month, this is our first issue incorporating *Electronic Imaging* into *Digital Design*. The merger effects a number of important changes in this magazine.

To accommodate additional graphics and imaging articles, along with our usual subjects, the feature section of *Digital Design* has been divided into four subsections: Electronic Imaging, Systems Architecture, Semiconductor Technology and Design Technology. The systems, semiconductor and design sections are what we have been doing all along; imaging is new.

Although graphics, array processing and much of the other coverage in *Electronic Imaging* fall within our normal purview, articles with a purely imaging cast are new to *Digital Design*. To help us keep it all sorted out, Andrew Wilson, Executive Editor of *Electronic Imaging*, will be responsible for the expanded graphics and imaging coverage.

Systems architecture covers our traditional computer-related subjects. That includes computer systems, peripherals, buses, communications and expanded software coverage. Technical Editor Brita Meng will be in charge of the section.

Because semiconductor advances make most systems progress possible, *Digital Design* has always provided IC coverage. Now we are formalizing it with a feature section devoted exclusively to semiconductor technology. Our Executive Editor, David Wilson, is responsible for this section of the magazine.

In the past, *Digital Design* has offered a great deal of design coverage such as PC board and gate array design, workstations and development systems. Because of the importance of these topics to design engineers, a section of the magazine is now devoted to design technology. Senior Technical Editor Ron Collett is responsible for the section.

Each of the feature sections will have at least one article per issue and often more. Our goal is to provide balanced editorial every issue. To ensure that balance, the Technology Editors in charge of each of the four sections will continually track their segments of the industry, keeping up to date on the latest technology.

All of the Technology Editors have degrees in either Electrical Engineering or Semiconductor Physics. But despite their broad knowledge of the industry, they know that they can't do it all themselves. So they will be looking for help in the form of good contributed articles.

We've made a few other changes as well. Last month you saw the replacement of Departments with Technology Trends and the addition of New Product Focus reports. Now the whole news section of the magazine has been redesigned to pick up many of the visual elements of *Electronic Imaging*.

For example, Update has been replaced with Hotline (as in *Electronic Imaging*) to underline the immediacy of news in that section. Technology Trends has picked up the graphics style of *Electronic Imaging*'s news section but otherwise remains the same as established last month. Staying on top of the news is Senior Editor Julie Pingry's responsibility, although much of the input will come from the Technology Editors.

All of these changes represent a commitment to our readers. We are trying to provide the best written, most balanced design editorial package in the industry. Let us know how you feel about it.

# An Array Processor this fast and flexible can't sell for only \$4100.

The imaging requirements of a geophysical research project at sea demanded intense mathematical calculations. An array processor was the

answer

But space aboard the ship's computer was limited. Only a single Multibus\* slot remained.

Marinco engineers, driven by necessity, pushed beyond the horizons of conventional array processor design.

#### A Single Board

They discovered how to shrink circuits to a single board — and to do so without sacrificing performance.

In fact, they enhanced it. Keeping signals within a single board actually made significant speed gains. Then they added other performance enrichments such as memory mapping and an auxiliary port for direct high speed I/O. Easy to Program

Perhaps as important, the board is easy to program, even for someone with only high-level language experience. Standard routines may be adapted. Or new ones created. Marinco's assembler automatically generates the microcode and tracks the 48-bit control word.

MARINCO

.............................

US and foreign patents pending. Multibus is a trademark of Intel Corp.

### Marinco makes it possible!

**Imaging Productivity**

The speed and flexibility of the APB-3000 series can dramatically increase your imaging productivity. Use it for coordinate transformation, hidden line removal, vector-toraster conversion, interpolation, image enhancement and many other operations.

**Very Low Price**

Even with all these advantages, Marinco innovations make it possible to offer the Multibus version for only \$4100, quantity one, U.S. price. IBM PC and PC AT versions are also available.

Can an array processor this fast and flexible really sell for such a low price?

Thanks to practical demands and Marinco innovations, it can. Call us toll-free for details.

Specifications

Program Memory 2K X 48-bits Data Memory 8K words Data Word 24 bits long, 8-bit exponent, 16-bit mantissa (floating pt.) or 16 bits (integer).

Marinco Computer Products 9940 Barnes Canyon Road San Diego, CA 92121 619-587-0461 1-800-421-4807 in Calif. 1-800-421-4808 Telex 3719117

A HELIONETICS COMPAN

Circle 17 on Reader Inquiry Card

#### HOTLINE

32-BIT BIT-SLICE ADDED TO STANDARD CELL LIBRARY Wafer Scale Integration is slated to announce the addition of a 15 MHz 32-bit CMOS bit-slice processor to their standard cell library at the Custom Integrated Circuit Conference in Portland, OR this month. In the third quarter, WSI plans to offer the processor as a standalone chip.

EDIF VERSION 1.0 RELEASED The Electronic Design Interchange Format (EDIF) specification is now available to industry. EDIF can be used as a standard interface between engineering, design, test and manufacturing tools. The first meeting of the EDIF Users' Group will be June 27 during the Design Automation Conference in Las Vegas.

STRETCHED DISK FACILITY OPERATIONAL The process development and pilot production plant for 3M's stretched disks has begun operation. Stretched disks promise higher recording capacity than floppy disks, yet use flexible media to circumvent the high cost and fragility of rigid disks. Current  $5\frac{1}{4}$ " versions hold about 12 Mbytes and may reach 100 Mbytes.

FAULT-TOLERANT SYSTEM ANNOUNCED BY IBM The System/88 is IBM's first faulttolerant computer; the system is supplied by Stratus Computer under an agreement for IBM to buy and resell some Stratus products. The System/88 is based on Stratus 32 processors and software.

<u>8086/8088 FAMILIES IN CHMOS</u> Intel has announced that their 8086/8088 microcomputers and peripherals will be produced in CHMOS. 80C86 and 80C88 parts will be fully compatible with the existing NMOS versions. Samples of the CHMOS kits are available now, and quantity production is scheduled for fourth quarter.

THREE GAAS VENTURES TAKE-OFF Gallium arsenide manufacturing plants have recently been completed by Honey well and Ford Microelectronics. Tektronix introduced its first GaAs product in December 1984, but has just formed a subsidiary for GaAs IC marketing and manufacturing called TriQuint Semiconductor. The Honey well line is expected to be in full production by July, and Ford is shooting for the third quarter.

BOTH 4.2 AND SYSTEM V UNIX PORTED TO APOLLO Apollo Computer Inc. has become the first computer manufacturer to offer both Berkeley 4.2 and System V UNIX on a 32-bit workstation. The twin port, called Domain/IX, allows users to run either 4.2 or System V or both simultaneously on the same node.

MAINFRAME LINES TO VIE FOR IBM MARKET Both National Advanced Systems and Burroughs have introduced new mainframe computer lines. These come in the wake of IBM's Sierra and appear aimed at the same markets.

# DON'T LET SPEED Slow you down.

The Mostek BiPort FIFO takes your processor out of the loop.

Until now, buffering two devices with different data rates meant one of two things. Either extra hardware design effort. Or software loops to slow your processor down while it's waiting for a peripheral or a coprocessor to be available.

But now there's a better way. The BiPort<sup>™</sup> FIFO from Mostek. You can do away with the need for extra hardware design and software loops, and let your processor operate at its optimal performance level.

Our MK4501 is a 12.5 MHz CMOS device with access times as fast as 65 ns. It can handle asynchronous and simultaneous reads and writes from each respective port. And its 512 x 9 architecture is fully expandable by word width or depth. It even has a retransmit capability.

There's nothing quite like it. Except our MK4511. The MK4511 is similar, but has the added advantage of being a true dual-port RAM that's randomly-accessible for bi-directional applications.

So put a speedy end to your interface problems. Call or write Mostek for more details. Mostek Corp., 1215 W. Crosby Road, MS1051, Carrollton, Texas 75006, 214/466-7479. In Europe, (32) 02/762.18.80. In Japan, 03/496-4221. In the Far East (Hong Kong), 5.681.157-9.

BiPort is a trademark of Mostek Corp.

#### **TECHNOLOGY TRENDS**

#### CAD

#### Designing ICs With A Silicon Compiler

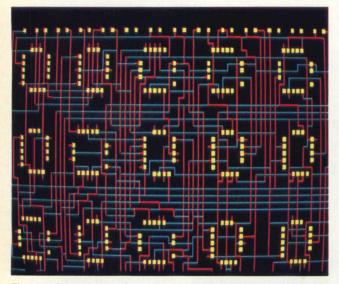

Digital Design is currently implementing a crosspoint switch onto a gate array. (See *Digital Design*, January, February, March 1985). In addition to the gate array design, we recently implemented the same circuit using a silicon compiler from Silicon Compilers Inc. (SCI) of San Jose, CA.

#### Genesil System Description

The Genesil silicon compiler system hardware consists of a VAX 11/750, 4 Mbytes of main memory, 450 Mbytes of Winchester disk storage, a 1600 bpi tape drive, four 1024  $\times$  780 color terminals and a mouse. System software includes packages for function synthesis (i.e, the compiler), auto place-and-route, functional simulation, timing analysis and geometric layout.

Integrated circuits are designed with the Genesil silicon compiler using a hierarchical set of objects: chip-set, chip, module and block. Blocks, the most primitive objects, are synthesized according to the needs of the user. Modules are composed of blocks and other modules; chips are modules that have bonding pads, and chip-sets are collections of chips.

The first step in the design process is to select a generic type of function from the function set menu. Next, the block is tailored to the design's requirements by selecting the electrical and functional parameters necessary to implement a specific instance of that function. Genesil automatically flags electrical, timing and clocking violations and prevents blocks violating these rules from being synthesized.

Once the block is defined, Genesil compiles three distinct views: the geometric view (i.e., the actual transistor layout), the timing model and the functional model. These models can be used for immediate verification by the system's timing analysis and functional simulation

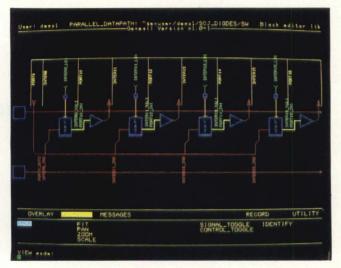

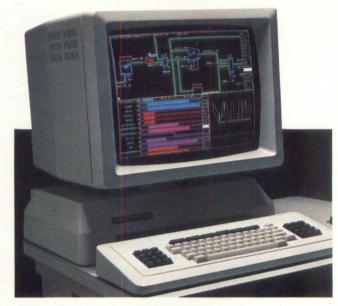

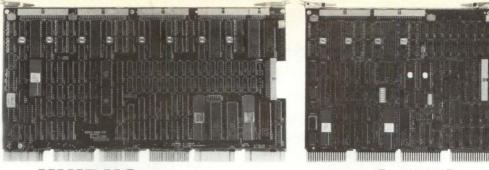

Figure 2: After exploring several architectural possibilities, *Digital Design* and the SCI Applications Engineers concluded that this would be the best implementation of the crosspoint switch. The final design consists of two data paths, an 8to-1 by 4 mux and a decoder PLA. In this schematic, only the data path is shown.

- 32 inputs organized as 8 groups of 4-bit buses.

- 32 outputs organized as 8 groups of 4-bit buses.

- 3 control lines to select the active input group.

- 3 control lines to select the active output group.

- Clock, power and ground pads.

- During any clock cycle, there is one path active from one input group to one output group.

Figure 1: As opposed to specifying a design in terms of logic elements, silicon compilation is based on the high level architecture of the design. The architectural specification is made up of inputs, outputs, control lines, clock, power and ground. The specification shown illustrates the parameters of *Digital Design*'s digital crosspoint switch.

subsystems. Based on *Digital Design*'s gate array design experience, separating timing from simulation is far more efficient than performing the two analyses concurrently.

After verification is complete, the circuit undergoes place-and-route. Routing priorities can be assigned to various signals so that critical paths are made as short as possible. No other user input is required. All bus signals are routed together, providing for a more efficient chip layout and maintaining bus timing integrity. The router also sizes power and clock lines to minimize resistances. At the same time. Genesil checks that interconnects will be able to maintain proper current densities and signal levels. After the chip is automatically placed and routed, the circuit is again simulated and its timing verified using actual wire delays.

Preparation for tooling is the final stage of the silicon compilation design cycle. In readying the chip for fabrication, Genesil produces a magnetic tape containing a layout optimized for a specific foundry fabrication line. At present, Genesil can generate NMOS designs. However, SCI will shortly introduce software that allows designers to build CMOS devices.

Genesil automatically generates a full report of the design that includes detailed manufacturing instructions. In addition, the designer can produce timing data sheets at any level from block to chip-set, document ROM and PLA truth tables, and generate hard copies of block, mod-

# A CRASH COURSE IN DISK AND DRIVE TESTING:

#### **Disk Testing**

ADE RVA instruments will show you how to test excessive acceleration, flatness, radial waviness, datum positioning, axial run-out and thickness.

#### Head/Assembly Testing

ADE RVA instruments give you advanced instruction on head positioning accuracy, head motion studies, dynamic flight characteristics, pitching and rolling.

ADE RVA instruments maintain quality control from design through production. Only ADE systems can measure dynamic displacements from tenths of microinches to thousandths of an inch from 0 to 50 KHz frequency response.

-----

Spindle Testing

Learn the nuances of testing axial and radial runouts, bearing quality, axial/radial acceleration, non-repetitive runout, radial resonance, wobble, and high frequency vibration.

#### ADE Corporation

77 Rowe Street Newton, MA 02166 Telephone: (617) 969-0600 Telex: 922415

Circle 29 on Reader Inquiry Card

#### TECHNOLOGY TRENDS/CAD

ule and chip specifications.

#### Taking Genesil For A Test Drive

Like most engineers given a design task, we were accustomed to working with gates, registers and multiplexers. Despite a clear understanding of how the chip was intended to function, we did not attack the design from a system level approach. Instead we began describing the circuit at a detailed level (i.e., flip-flops and multiplexers). This was the wrong route to follow because the silicon compiler's strength is in removing the designer from specifying logic.

To exploit Genesil's power, we began to formulate the crosspoint switch's architectural, or block level, description. A specification emerged based on the switch's inputs, outputs, control lines, clock, power and ground (Figure 1). Once described at this level, several architectural possibilities were proposed. The most efficient solution seemed to be a 4-bit parallel data path structure. The switching function would be accomplished by a general input port, a general output port and a tri-state bus connecting the input and output stages. In addition, a programmable logic array (PLA) would be used to decode the input control lines. The decode mechanism configures the switch for routing signals between the input and output stages. This architecture was entered, compiled and plotted for silicon area in less than one hour.

Since the circuit was not yet simulated, the design was far from complete. However, we did have the die size, performance and propagation delay data necessary to make informed trade-off decisions. Of paramount importance is whether this implementation of the crosspoint switch satisfies cost and performance requirements dictated by the design specification.

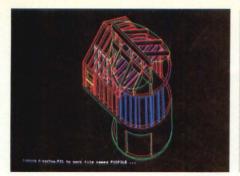

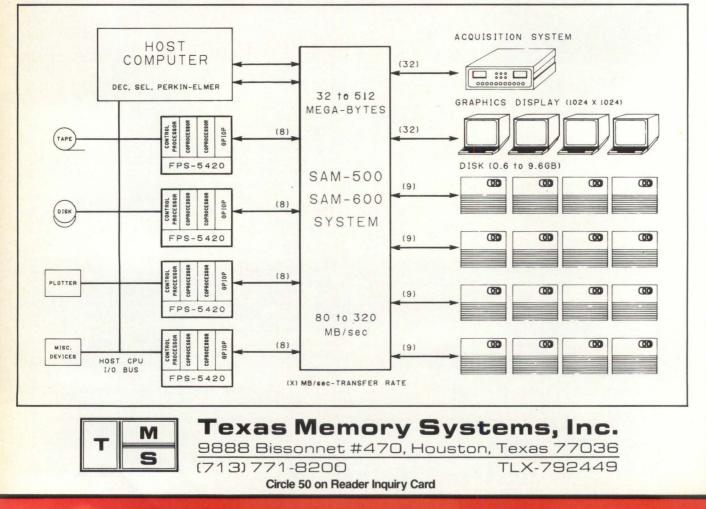

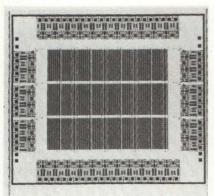

In discussing how to reduce die area with several SCI system engineers, an input multiplexing scheme using random logic, (i.e., four 8-to-1 multiplexers) emerged. Genesil's function set includes Figure 3: The layout of the crosspoint switch indicates that the die size is 297.3  $\times$  277.9 mils. This rather large area is due to the high I/O pin

count; bonding pad sizes are fixed by the chip manufacturer. The active part of the die consumes only 5% of the total silicon area. Implementing the crosspoint switch in two separate chips might be a better solution.

SELECT\_PAGE

desal

random logic. Other building blocks found in Genesil that were unnecessary for this design include RAMs, ROMs, FIFOs, Stacks, 4- to 32-bit wide data paths, ALUs and Barrel Shifters. Since the input stage uses multiplexers, the remainder of the data path must handle output multiplexing and latching (**Figure 2**). In this instance, splitting the output muxing into two sections provided increased floorplanning flexibility. The resulting crosspoint switch architecture consists of two data paths, an 8-to-1 by 4 (depth) mux and a decoder PLA (**Figure 2**).

After entering the architectural modifications, the chip was again compiled. In conjunction with compilation, the new architecture was combined with a standard pad ring, routed and plotted (Figure 3). It took three hours to input the updated architecture and pad ring, to compile and to route. Naturally, before transforming the design to silicon, the switch would undergo more simulation and timing analysis.

The circuit uses 891 transistors. Comparing overall die size to active area (**Figure 3**) shows very inefficient silicon usage. The "core," or active area, is less than 5% of the total chip size. Actual chip size is dictated by the bonding pad size. Implementing the design on two chips instead of one would reduce the number of pads on each chip. Each of the resulting ICs would be approximately onefourth the size of the present implementation. Moreover, two smaller devices would be less costly than one larger part. Of course, if decreased chip count is the ultimate system goal, the single chip route would be followed.

UTILITY

The primary advantage of silicon compilation is the speed it provides for custom IC design. The entire implementation of this chip, including exploration, took only five hours. In addition, this technology offers the ability to explore alternate architectures rapidly. Analyzing size and power consumption of several different implementations of the same design offers the designer tremendous leverage throughout the design cycle. As a result, architectural creativity is maximized.

At the same time, however, a silicon compiler is a sophisticated tool that demands an experienced system design engineer. In order to utilize the full power of Genesil, the designer must be intimately familiar with system design considerations. Although Genesil can be used by logic designers, an understanding of system design is needed to exploit the silicon compiler's capabilities. A true systems architect would be the best candidate to use Genesil.

-Collett

#### Our Smart-Frame<sup>™</sup> will put you in touch.

One of the easiest ways to interact with a computer is through a touch activated display. One that lets you merely point your finger at what you want your computer to do.

With touch, even the most complex application can become user friendly. And less susceptible to user error.

But the advantages of the highly reliable infrared touch input systems have been overshadowed by cost. Placing them out of the range of medium to low-cost turnkey systems manufacturers.

Which is the main reason Carroll Touch completely redesigned its line of touch input products.

We call it Smart-Frame™. Because it contains a powerful microprocessor built into the frame. And because it uses scanning infrared technology—a touch technology which is incredibly reliable, rugged, accurate, and fast. A technology Carroll Touch pioneered and refined.

As a result of the Smart-Frame design, Carroll Touch units contain 45 percent fewer components than before. Which means the cost to you is about 50 percent lower too.

We think that's pretty smart. And Carroll Touch did it just so you could get in touch. Today.

In Touch with Technology

P.O. Box 1309 Round Rock, Texas 78680 512/244-3500, Telex 881906

**Circle 1 on Reader Inquiry Card**

#### TECHNOLOGY TRENDS/CAD

#### GATE ARRAY DESIGN UPDATE

#### Design Verifier Flags Potential Problems

igital Design published a three-part series on designing a digital crosspoint switch using a CMOS gate array in January, February and March of this year. The vendors participating in the project are LSI Logic (Milpitas, CA), Valid Logic Systems (San Jose, CA) and Datacube (Peabody, MA). LSI is supplying its cell library; Valid's contribution is the Scaldsystem workstation; and Datacube designed the circuit. Since the project was still underway when Part III went to print, progress reports will be published periodically. This update focuses on the network summary generated by LSI Logic's Design Verifier.

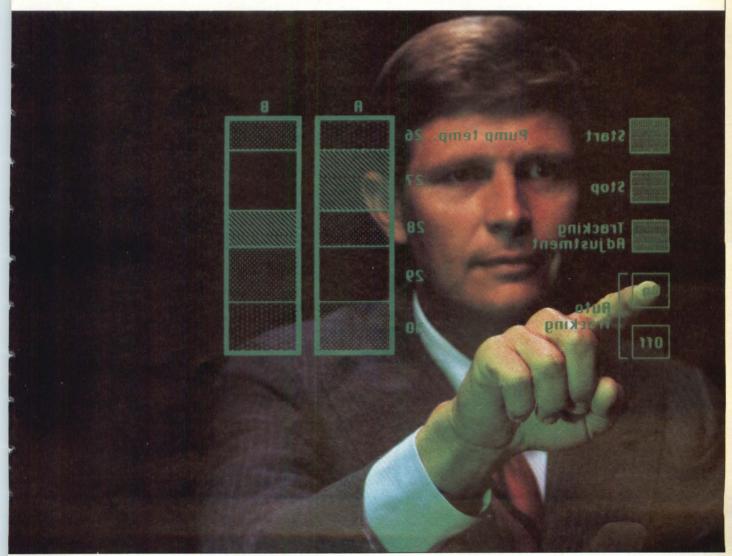

The Design Verifier, highlighted in Part II, runs on Valid's Scaldsystem. Its purpose is twofold: to provide the designer with statistically based interconnect wiring delays for simulation and to generate a network summary. The information compiled in the network sumValid Logic's Scaldsystem workstation is being used to implement

a CMOS gate array supplied by LSI Logic. Valid recently unveiled a new model of the Scaldsystem with color display. Valid's primary competitors, Daisy (Mountain View, CA) and Mentor Graphics (Beaverton, OR), also offer color displays.

mary includes network connectivity, number of gates used, number of bonding pads required, number of I/O pins required and percentage of interconnect wires that can be automatically routed.

After entering the schematic and compiling the logic, the designer invokes the Design Verifier. The most difficult step in using this tool is choosing the right gate array. LSI Logic offers three array families: the LL3000, the LL5000 and the LL7000. The LL5000 Series satisfies our performance requirements, so a partic-

| 1 |                                                                |               |                                                 |                   |  |  |

|---|----------------------------------------------------------------|---------------|-------------------------------------------------|-------------------|--|--|

|   | LDS DESIGN VERIFIER (VALID) NETWORK SUMMARY                    |               |                                                 |                   |  |  |

|   | COMP. NAME:                                                    | DIGDES        | TECHNOLOGY TYPE: CMC                            | Address of Subar. |  |  |

|   | ARRAY SIZE (FAMILY):<br>Tue Apr 2 16:26:43 1985                | LSI5140       | LIBRARY REV.: 2.17 (10/1<br>VERIFIER REV.: 84.C | (4.26             |  |  |

|   | NUMBER OF CELL TYPES:                                          | 11            | NUMBER OF CELLS USED:                           | 569               |  |  |

|   | NUMBER OF GATES USED:<br>ARRAY USAGE (PERCENT):                | 1263<br>98.17 | GATE USAGE (PERCENT):                           | 39.13             |  |  |

|   | NUMBER OF INPUT PINS:                                          | 42            | NUMBER OF OUTPUT PINS:                          | 32                |  |  |

|   | NUMBER OF BIDIRECT. PINS:                                      |               | NUMBER OF INTERNAL PADS:                        | 6                 |  |  |

|   | NO. OF ADD. Vpp PADS:                                          | 3             | NO. OF ADD. V <sub>ss</sub> PADS:               | 1                 |  |  |

|   | NO. OF REQ. V <sub>ss2</sub> PADS:                             | 2             | TOTAL NO. OF SIGNAL PINS:                       | 74                |  |  |

|   | ***NOTE: TOTALS DO NOT INCLUDE PREASSIGNED POWER PADS AND PINS |               |                                                 |                   |  |  |

|   | TOTAL ARRAY PADS USED:                                         | 116           | AVAILABLE CHIP PADS:                            | 92                |  |  |

|   | PACKAGE PINS USED:                                             | 78            |                                                 | 88                |  |  |

|   | CELL INPUTS TO VDD:                                            | 0             | CELL INPUTS TO Vss:                             | 0                 |  |  |

|   | NUMBER OF SIGNAL NETS:                                         | 537           |                                                 | 88                |  |  |

|   | AVERAGE PINS/NET:                                              | 3.600         | MAXIMUM PINS/NET:                               | 65                |  |  |

|   | WIREABILITY MEA                                                | SURE FOR      | AUTOMATIC LAYOUT: 88.68%                        |                   |  |  |

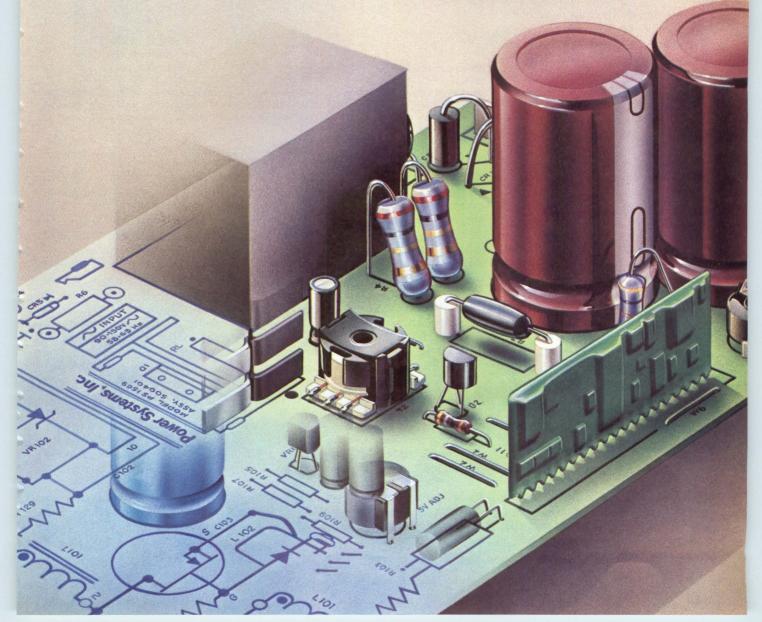

Figure 1: The output of LSI Logic's Design Verifier provides a complete summary of the circuit's physical requirements. Of primary importance are wireability, number of chip pads and I/O requirements. In this instance, the LL5140, a 1404-gate chip, was the target array loaded into the Design Verifier.

ular chip in that family must be selected. Since only a preliminary estimate of the circuit's size is available, picking the proper array is done by trial and error. The crosspoint switch (**Figure 3**) has an estimated gate count of 1400 gates. Among the various arrays in the LL5000 family, the LL5140, a 1404-gate chip and the LL5220, which has 2224 gates, potentially satisfy the circuit's requirements.

Both devices were input to the Design Verifier. Each run executed in less than two minutes; the results are given in **Figures 1** and **2**. As shown, the switch uses 1263 gates. Even more important is wireability measure, which indicates whether a particular chip meets the needs of the design. This percentage is calculated as a function of number of gates used, average pins per net (i.e., average fanout per node) and number of signal nets, excluding outputs.

Other information gleaned from the summary includes the number of additional  $V_{DD}$  and  $V_{SS}$  pads, a comparison of total number of chip pads to number of array pads actually consumed and maximum pins per net. Extra  $V_{SS}$  and  $V_{DD}$  pads are necessary because certain buffers in the circuit require added current drive capability.

Several problems with our design are flagged by the Design Verifier. The most

# At last, convincing hard copy from your high resolution display.

Presenting the Honeywell VGR 5000. It delivers true-to-life hard copy from a slew of video sources including 60 Hz noninterlaced displays with 1280 x 1024 resolution.

It interfaces directly with the video display using simple BNC cables. No CPU time or special software required.

It even provides copy from monochrome or RGB displays in just 14 seconds. And when you examine the contrast, density, and gray scale qualities of its hard copy, you'll see something you don't usually see from a video graphic recorder:

Every last detail.

For information contact Bob Shipman, (303) 773-4651, Honeywell Test Instruments Division, Box 5227, Denver, CO 80217-5227.

Together, we can find the answers.

© 1985 Honeywell Test Instruments Division

#### TECHNOLOGY TRENDS/CAD

critical problem is a need for 116 array pads (i.e., bonding pads). Neither the LL5140 nor the LL5220 have enough bonding pads for this circuit configuration. Only 92 pads are available in the LL5140 and 114 are provided in the LL-5220. Therefore, the design must be modified.

One solution is to use internal buffers drawing less current. LSI Logic offers several different buffers. The high current driving (8 mA) buffers originally used require twice as many I/O pads and more power and ground pads than 4 mA buffers. Changing to these low current buffers will reduce the number of pads needed by about 30.

A second problem is routing the chip. Assume for the moment that the number of pads will be reduced to 86. At first glance it appears that the LL5140 would be the best choice. But using the LL5140, the autorouter can make only 88.68% of the connections. Since the LL5220 is a much larger device, the autorouter can perform 100% of the routing. The issue is whether to manually route the remaining connections of the LL5140 or use the LL5220.

Each solution has a drawback. Manually routing the chip could require many Figure 3: This schematic illustrates the basic operation of the crosspoint switch: any input signal (10-17) can be routed to any output (Q0-Q7). In the actual design, there are eight 4-bit wide inputs and eight 4-bit wide outputs.

additional man-hours to complete – if 100% routing is possible at all. On the other hand, the LL5220 is more costly,

| LDS DESIGN VERIFIER (VALID) NETWORK SUMMARY                                                          |                     |                                                                                                                      |                         |  |  |  |

|------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| COMP. NAME:<br>ARRAY SIZE (FAMILY):<br>Tue Apr 2 16:14:35 1985                                       | DIGDES<br>LSI5220   | LIBRARY REV.: 2.17 (10/1                                                                                             | DS5K<br>15/84)<br>Q4.26 |  |  |  |

| NUMBER OF CELL TYPES:<br>NUMBER OF GATES USED:<br>ARRAY USAGE (PERCENT):                             | 11<br>1263<br>62.54 | NUMBER OF CELLS USED:<br>GATE USAGE (PERCENT):                                                                       | 569<br>56.79            |  |  |  |

| NUMBER OF INPUT PINS:<br>NUMBER OF BIDIRECT. PINS:<br>NO. OF ADD. VDD PADS:<br>NO. OF REQ. VSS PADS: | 42<br>0<br>3<br>2   | NUMBER OF OUTPUT PINS:<br>NUMBER OF INTERNAL PADS:<br>NO. OF ADD. V <sub>SS</sub> PADS:<br>TOTAL NO. OF SIGNAL PINS: | 32<br>6<br>1<br>74      |  |  |  |

|                                                                                                      |                     |                                                                                                                      | 114<br>110              |  |  |  |

| CELL INPUTS TO V <sub>10</sub> :<br>NUMBER OF SIGNAL NETS:<br>AVERAGE PINS/NET:                      | 0<br>537<br>3.600   | CELL INPUTS TO V <sub>ss</sub> :<br>NO. OF UNC. CELL OUTPUTS:<br>MAXIMUM PINS/NET:                                   | 0<br>88<br>65           |  |  |  |

| WIREABILITY MEASURE FOR AUTOMATIC LAYOUT: 100.00%                                                    |                     |                                                                                                                      |                         |  |  |  |

Figure 2: Since only 88.68% of the LL5140's interconnections can be autorouted, as shown in **Figure 1**, the Design Verifier was run a second time with the LL5220, a 2224-gate chip. Although the autorouter can make all of the interconnections, there are too few chip pads to accommodate the design.

and using it wastes approximately 700 gates. These gates could be utilized if more logic were put onto the chip, but this may also create problems. Additional logic, in this instance, demands more bonding pads. Moreover, adding circuitry not part of the original design specification would require spending more time on the project. The upshot would be an extension of an already delinquent project's design cycle.

The ideal solution would be to use an 1800-gate array, but LSI Logic does not offer such a chip in the LL5000 Series. Problems of this nature are discussed at length in Part I (January 1985).

The next update report will cover which array is to be used and the basis on which that decision is made. Details on the feasibility of manually routing the LL5140 or simply using an LL5220 will be provided. Timing verification and simulation results will also be included. -Collett

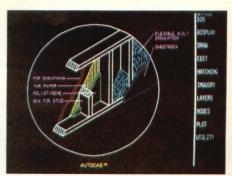

1. High Speed (MicroCAD Software)

2. Dual Display Modes (Energraphics Software)

3. Simplified Processing (AutoCAD Software)

4. 9 Bit Planes (Courtesy WSI Inc., Bedford, MA)

5. 16.8M Color Shades (Courtesy Catherine Del Tito, Wave Graphics)

High Resolution (Courtesy University of North Carolina at Chapel Hill, Depts of Computer Science and Radiology)

# Six reasons why professionals continue to choose Vectrix for quality IBM XT/PC graphics.

Even though IBM offers a color graphics card, professionals still choose Vectrix. It's not surprising. Especially once they've seen us in action. Professionals know that our VX/PC Board Set delivers the quality and performance they need for serious color graphics.

The VX/PC Board Set provides advanced features that help simplify sophisticated graphics design. Besides displaying 512 simultaneous colors from a palette of 16.8 million, the VX/PC supports an extensive library of on-board graphics macros for ease of programming and fast design, as well as full emulation of the IBM color card. And, an on-board 16-bit micro-

IBM XT, IBM AT, and IBM PC are trademarks of International Business Machines Corporation, White Plains, NY MicroCAD is a trademark of Imagimedia Technologies, Inc., San Francisco, CA. AutoCAD is a trademark of AutoDesk, Inc., Sausalito, CA.

EnerGraphics is a trademark of Enertronics Research, Inc., St. Louis, MO.

processor frees your computer to concentrate on other tasks.

But that's not all. Our 9 bit planes

add an extra dimension of sharpness and clarity to your image that must really be seen to be appreciated. That's why it's not surprising to see Vectrix color cards in applications such as medical imaging, weather satellite data mapping, computer aided design and drafting, and graphics arts, to name a few. however, is the price. Our VX/PC Board Set was designed with the OEM

What you will find most surprising,

in mind. So when comparing the performance of Vectrix with the competition, check the price too. You'll like what you see. For more information, contact Vectrix Corporation, 2606

Branchwood Drive, Greensboro, North Carolina 27408. Phone (919) 288-0520. Telex 574417.

Distributor inquiries welcome.

Circle 55 on Reader Inquiry Card

#### **TECHNOLOGY TRENDS**

#### SOFTWARE

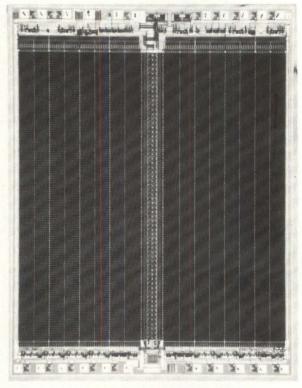

#### PC-Based Software Produces High Resolution Graphics Files

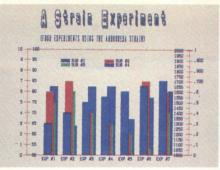

High quality presentation graphics displays such as scientific plots require high resolution. Although scientific calculations are often performed on personal workstations, the graphics resolution of the IBM PC is not adequate to create accurate detail. A software package from Scientific Endeavors (Kingston, TN) produces complex scientific plots on the IBM PC.

Called GraphiC, the software is a set of C programs for creating plots, graphs and text for scientific and engineering applications. Although the program runs on a PC, the resultant graphics are not limited to the IBM PC display resolution. For high resolution display, the software can create a display list output file for driving Tektronix-compatible output devices. This is useful for entering and previewing scientific data or formulas on the PC, then displaying the results on plotters or high resolution display devices that read Tektronix files.

This software directly addresses the needs of scientific environments. These settings require high quality graphics images but may mainly use limited resolution computer hardware. However, many academic, scientific and industrial organizations do have access to devices that read Tektronix graphics files. Therefore, the authors of GraphiC turned to the IBM PC for program and graph development and to Tektronix format for intermediary display files. This combination creates the accurate plots and displays needed while allowing users to manipulate information on their personal workstations.

GraphiC is modeled around DISSPLA

Figure 1: GraphiC can display a 3D plot with

hidden line removal and text like this one in approximately 10 seconds. Though the program runs on an IBM PC, display list output files are in Tektronix format for high resolution display and printing or plotting.

from ISSCO (San Diego, CA). The GraphiC package is a collection of graphics routines written in C. Users can write simple C programs and use the graphics subroutines for creating complex plots. Hidden line and 3D routines are standard (Figure 1). All plots are created with the Tektronix format 4096  $\times$  3120 pixel resolution. In addition to graphics capabilities, GraphiC also has 10 fonts, four of which are simultaneously available. Greek letters and math symbols are available in two fonts. Unlimited levels of superscripts and subscripts may be employed. All font heights are continously variable.

5

O.

-0.5

10

-dXIS

Features of GraphiC include the ability to zoom, shrink and shift. Routines are available for creating linear, log, semilog, log-log, 3D and contour plots. An error file is created during execution for debugging. If a plot requires a font not on the current disk, the letters would not be seen, and a file indicating a file not found would be created. GraphiC can reconstruct any Tektronix file from another computer, providing the entire plot was created in graphics mode. One of the useful features of GraphiC is the ability to print plots on popular dot matrix printers. A C. Itoh or Epson printer can print a  $96 \times 144$  pixel per inch image, whereas an Okidata yields somewhat lower resolution.

GraphiC is designed for use with several compilers; however, the DeSmet compiler is recommended. Complete source code is provided so the end user can create and modify programs. If the user's system has an 8087 installed, which is highly recommended, the software will access and utilize its capabilities. The result is faster execution of arithmeticintensive graphics such as 3D.

The software was tested at *Digital Design* using the DeSmet compiler. A program was written to display a 3D plot on the PC and create a Tektronix file. The file was then displayed on a Qume QVT-211GX terminal, which has 4010/4014 capability. The resolution quality of the Qume was excellent. A complex 3D display using an 8087 took approximately 10 seconds.

-MacNicol

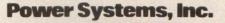

## For 13 years some of the biggest names in the business have been bringing us their toughest power supply requirements.

Why? Because we work with them, beyond their specifications. Quickly. Effectively. Creatively.

How? By being highly sensitive to their needs. By working closely with them to develop the power supply that meets both their specifications and their system's requirements. By valueengineering our design before production to insure a cost-effective product. By carefully balancing materials and manpower to maintain flexibility.

PSI is committed to meeting International Safety requirements. We have developed a Safety Certification Package with all the data and specs needed to obtain approval from UL, CSA, and VDE, and other certifying organizations. And we are authorized to self-certify power supplies.

Whether your power supply requirements are simple or complex, bring them to us. Power Systems, Inc. Where powerful solutions are everyday achievements.

To find out why Power Systems, Inc. should be your power supply vendor, contact: Power Systems, Inc., 12 Tobey Road, Bloomfield, Connecticut 06002, Tel. (203) 243-0357, TWX 710-425-8778

**Circle 19 on Reader Inquiry Card**

#### **TECHNOLOGY TRENDS**

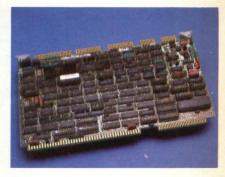

#### 64K × 1 SRAMs Vie For DRAM Applications

The increasing size of main memory in multiprocessor systems demands that memory ICs be small, fast and inexpensive. Static random-access memories (SRAMs) are small and fast, and require no refresh circuitry. However, high prices have kept SRAMs out of most main memory applications, where dynamic random-access memories (DRAMs) are preferred. SRAMs have become specialpurpose devices used primarily by systems architects requiring low power consumption, high speed, board space savings or ease of use.

Nevertheless, companies such as Fairchild Camera and Instrument Corp. (Puyallup, WA), Hitachi (San Jose, CA) and Inmos (Colorado Springs, CO) are very optimistic about the future for the new generation of 64K SRAMs. According to Dan Pichulo, SRAM product marketing manager at Hitachi, SRAMs organized as  $64K \times 1$  lend themselves to several applications.

One possible use of these devices is as the main memory for either mainframe computers or superminicomputers. High performance machines demanding very fast access times may find CMOS SRAMs comparable in speed to ECL memories, without the problem of high power dissipation. Richard Phlegar, memory products planning manager at Fairchild's Memory and High Speed Logic Unit, believes that SRAMs with the ×1 organization are particularly well suited to error detection and correction in mainframes and minicomputers. However, unless the costs of SRAMs decrease, a main memory using SRAMs may not be forthcoming in the near future.

The good access speeds of SRAMs may also make the devices viable as fast

Fairchild's new CMOS 64K × 1 SRAM offers

access times of 45, 55 or 70 nsec with maximum active power consumption of 70 mA. To keep die size small, NMOS is used for the memory cell and peripheral support circuitry is processed in CMOS. This combination of CMOS and NMOS is also used by Hitachi and Inmos in their 64K  $\times$  1 SRAM parts.

writeable control stores for software. A nonvolatile memory such as a ROM can take up to 150 nsec to access the software program; for some users, this may not be fast enough. Present  $64K \times 1$  SRAMs have access speeds between 45 nsec and 70 nsec. In addition, the CMOS SRAM can almost function as a nonvolatile memory due to its low power requirements – a battery would maintain the current necessary to retain memory.

By far the largest potential applications for the  $64K \times 1$  SRAM are cache and buffer memories for high performance systems. The mismatch between microprocessor speed and DRAM memory speed has caused systems architects to rely on caches in order to minimize frequency of access to main memory. With new MOS SRAMs offering higher speeds and lower power dissipation, the switch from ECL parts to SRAMs for cache memory applications will certainly continue.

Fairchild, Inmos and Hitachi have taken similar manufacturing approaches to their  $64K \times 1$  SRAMs: the memory cell is processed in NMOS and the peripheral support circuitry is CMOS. Kirk MacKenzie, Vice President of Marketing and Sales at Quasel Inc. (Santa Clara, CA) approves of the mixed process devices, saying that it may be the most cost-effective way to produce low power, high speed SRAMs. NMOS allows a higher density storage element and enables a smaller die size than a fully CMOS SRAM. CMOS peripherals reduce power dissipation problems. In addition, CMOS circuits are more resistant to soft errors.

Even with the access time improvements made on MOS SRAMs, several supercomputer and superminicomputer manufacturers still feel that the new generation of  $64K \times 1$  devices are simply not fast enough. They would like to see the larger SRAMs comparable in access time to smaller SRAMs such as the 16K  $\times 1$ , which can now reach speeds of 25 nsec. If SRAM manufacturers can push the  $64K \times 1$  SRAM to those times, then perhaps systems architects for those larger systems will view the device as a better upgrade.

-Meng

# We run with a great crowd.

### Complete hardware/software compatibility.

Talk about easy interfacing. You can take a ZETA 824 or ZETA 836 plotter and plug it into virtually any computer made.

What's more, you'll be ready to run because our plotters understand a variety of computer protocols. Select the model for your application then just plug in and plot.

In fact, we're a plug compatible replacement for many plotters from HP, CalComp and Tektronix. Some models of our plotter can even run directly from your IBM cluster controller. Now that's easy interfacing.

When it comes to your favorite application packages, you'll be on safe ground too. Packages such as CADAM, TechniCAD, Euclid, P-CAD, AutoCAD and many more.

### *The most productive plotter for the money.*

You'll be getting the highest output plotters for the money with our new ZETA 824CS and ZETA 836CS. More

MANDOLET

ktronix

recision

finished plots. More productivity. Plus, these "D" and "E" format plotters let you run either single sheet or roll media.

#### Easy-to-use touch controls.

Your time is valuable. So we've made our touch controls simple – yet powerful. Set speed, pen pressure, liquid ink parameters, electronic limit sensing, windowing, scaling – all at the touch of a finger, Self-test and diagnostic plots too. Let us show you dozens of other time-saving operations in a brief demonstration.

#### Plotter specialists.

We've been designing hardware interfaces, plotting language emulators and high performance pen plotters for over 14 years. Nicolet also provides you with worldwide sales and service support.

Give us a call. See how easy it is to join the crowd.

Call (415) 372-7568. Nicolet Computer Graphics Division, 777 Arnold Drive, Martinez, CA 94553 TWX 910-481-5951

Computer Graphics Division

CADAM is a trademark of CADAM, Inc. TechniCAD is a trademark of Tektronix, Inc. Euclid is a trademark of MATRA DATAVISION, Inc. P-CAD is a trademark of Personal CAD Systems. AutoCAD is a trademark of Autodesk, Inc.

**Circle 18 on Reader Inquiry Card**

#### **TECHNOLOGY TRENDS**

#### COMMUNICATIONS

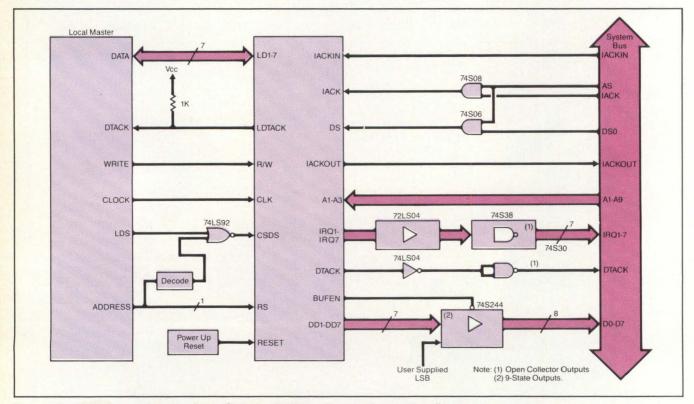

#### Options Multiply For High Speed Unibus Communication

single Unibus board may now provide 1 Mbit/sec or faster data communication for DEC minicomputers. The DMZ 32 from Digital Equipment Corp. (Maynard, MA) provides a 1.544 Mbit/sec T1 trunk for 24 multiplexed lines; it comprises a distribution panel and a Unibus module. DEC is also manufacturing a 1 Mbit/sec interface board for links to AT&T's Datakit Virtual Circuit Switch. The KMS11-K will be offered by AT&T Technologies (Morristown, NJ). For host-to-host links, Advanced Computer Communication (Santa Barbara, CA) offers the ACP 6100 (Figure 1) for nonmultiplexed T1 connection.

AT&T's Datakit-to-Unibus board will provide a multiplexed channel between computer and data switch. This board will operate at 1 Mbit/sec, not the 320 Kbits/sec of products linking AT&T 3B computers to Datakit. Initially, AT&T will use the KMS11-K internally for telephone company links. Distributors of Datakit as a twisted-pair local area network will also offer the board.

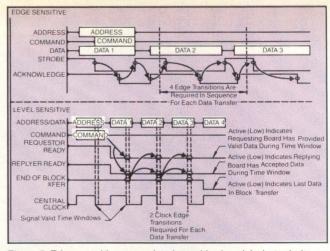

Although the DEC and the ACC boards both have Unibus and T1 interfacing, they serve different purposes. T1 speed is used on DEC's product as a trunk for multiplexing up to 24 lower speed lines, while ACC uses the entire channel for a single 1.544 Mbit/sec link. The DMZ 32 is an extension of DEC's asynchronous multiplexer line (*Digital Design*, March 1985), in which distribution panels are used for multiplexing and demultiplexing channels (**Figure 2**). A

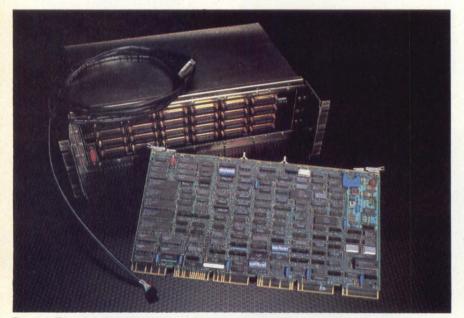

Figure 2: T1 speed of 1.544 Mbits/sec is used as a trunk to multiplex up to 24 channels in the DEC DMZ 32. T1 and Unibus interfaces share on-board RAM. The distribution panel in the background handles multiplexing and demultiplexing of individual lines.

Figure 1: Host-to-host communication at 1.544 Mbits/sec is provided by ACC's ACP 6100 Unibus board. A four-bus architecture is used to achieve such high speed.

DMZ 32 panel may be next to the computer or remote, connected by two cables for the T1 link. The Unibus board at the host contains RAM shared by the Unibus and the 1.544 Mbit/sec T1 line.

An active distribution panel manages the individual terminal lines. Maximum speed on each line is 19.2 Kbits/sec. The DMZ 32 provides modem control and split baud rate on all lines. The system also has DMA capability on transmit. The board architecture speeds communication functions, and the distribution panel off-loads line handling.

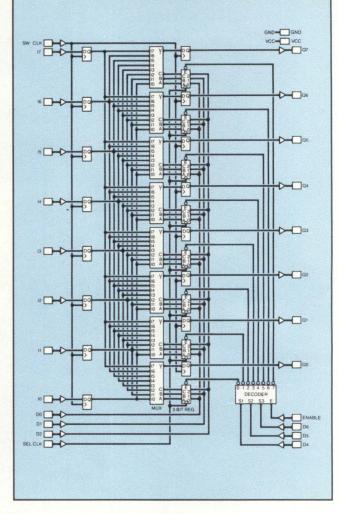

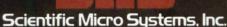

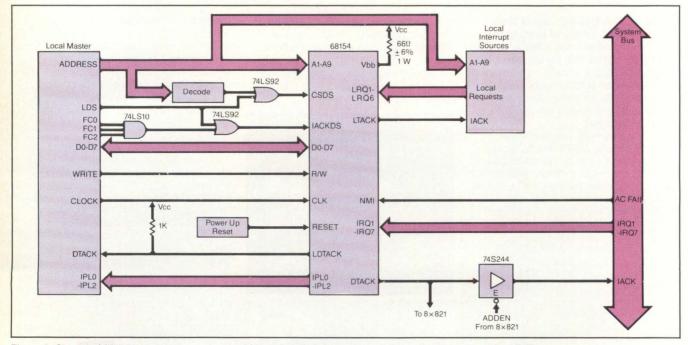

With the ACC front-end processor board, Unibus computers can transmit and receive one full-duplex channel of HDLC at 1.544 Mbps. While the DEC board uses shared RAM between the Unibus and the T1 interface, the ACP 6100 centers around a four-port DRAM array surrounded by four 68000 microprocessor buses (**Figure 3**).

Each bus in the "Quadbus" system is independent and electrically isolated, resulting in high throughput and minimum waiting for bus access. RAM access is made central to the system, not the microprocessor bus, since memory is what peripherals need. Individual bus segments are connected or disconnected according to bus activity.

In addition to the 68000 CPU bus (CBUS), there is a peripheral bus (PBUS), a DMA bus (DBUS) and a Unibus (UBUS). Three-state buffers isolate each bus from memory signals. An 8409 provides DRAM timing and control. Ar-

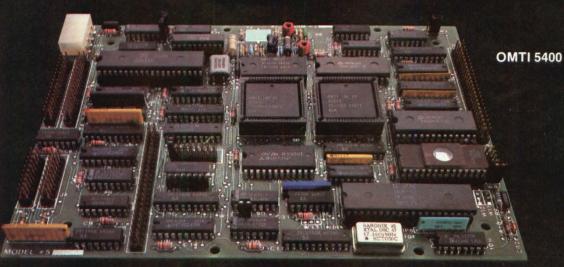

# WINCHESTER, FLOPPY AND TAPE All on one board

Our OMTI 5400 SCSI (SASI) controller offers Winchester, floppy and tape support all on a single 5¼" footprint PC board. By using our proprietary VLSI chip technology, we were able to squeeze all these functions onto a board size that most controller companies are still using for single function controllers. This means increased capability and improved cost-effectiveness in your application.

As a forward-looking OEM, you want multifunction SCSI (SASI) data controllers that meet your needs today and can meet the challenges of future developments in peripheral device technology. As you would expect, we've applied our new technology to meet these challenges in a whole family of SCSI (SASI) data controllers, the OMTI Series 5000.

OMTI 5100 Winchester

> OMTI 5300 Winchester plus Tape

OMTI 5200 Winchester plus Floppy

#### UNBEATABLE FLEXIBILITY

Our OMTI Series 5000 family of SCSI (SASI) controllers supports industry standard ST506/412 5<sup>1</sup>/<sub>4</sub>" fixed and removeable Winchester disks, 5<sup>1</sup>/<sub>4</sub>" and 8" floppy disks and QIC-02 compatible streaming tape. Each controller is SCSI (SASI) compatible to protect your software from change as you add next generation disk and tape technologies. And they are all second-sourced to guarantee availability.

#### **HIGH PERFORMANCE**

The Series 5000 controllers provide consecutive sector, noninterleaved data transfer and multisector buffering between host and peripherals. In addition, our data buffer supports simultaneous transfers between Winchester and streaming tape for fast image backup operation. No other manufacturer offers you performance like this!

#### EASY TO USE

Our high-level SCSI (SASI) command set off-loads your host CPU. Only one command is required to completely backup or restore Winchester data to and from tape, all without host intervention. Separate host-initiated commands allow selective file backup and restore. A sophisticated 32-bit ECC and automatic error retry means that reliable data is always available to the host. Finally, automatic Winchester flaw management handling prevents disk defects from corrupting your system.

To learn more about the OMTI Series 5000 data controllers, please contact us for additional information.

**OMTI Products Division**

339 N. Bernardo Avenue, Mountain View, CA 94043 (415) 964-5700

SALES OFFICES: Seattle, WA (206) 883-8303; Boston, MA (617) 246-2540; Atlanta. GA (404) 296-2029; Morton Grove, IL (312) 966-2711; Melrose Park, IL (312) 345-5320; Arlington, TX (817) 429-8527; Laguna Hills, CA (714) 643-8046; Greensboro, NC (919) 292-8072; Mountain View, CA (415) 964-5700; Philadelphia, PA (215) 860-8626. DISTRIBUTORS: United States-Arrow Electronics, Inc. (516) 694-6800; Canada-Allan Crawford Associates Ltd. (416) 678-1500; International-Prima International (408) 732-4620.

Circle 61 on Reader Inquiry Card

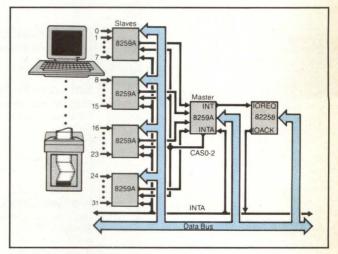

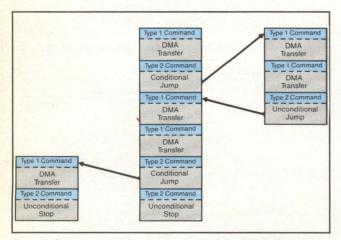

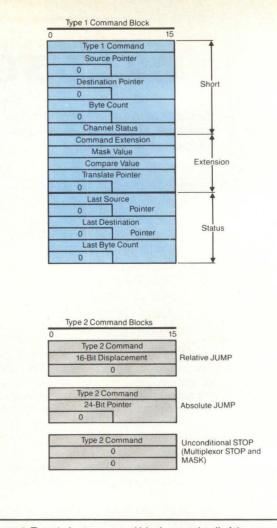

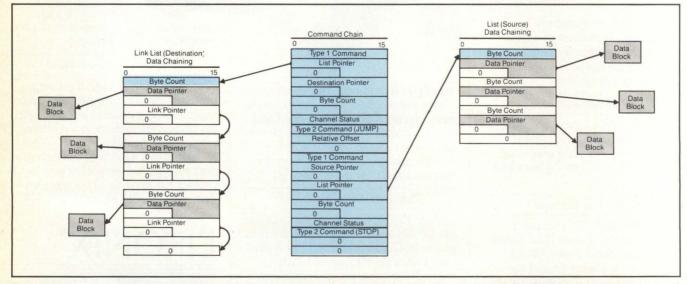

#### TECHNOLOGY TRENDS/COMMUNICATIONS