# YM3613B

### Digital Audio Interface Transmitter (DIT)

#### **OUTLINE**

The YM3613B is an LSI device used for signal processing in order to output Voice Digital signals of a CD player to the external world. Digital signal output to the external world enables Digital Audio Interface Format signals to be output without requiring a special externally-mounted circuit. This YM3613B has a built-in PLL (Phase-Locked Loop) circuit, which synchronizes the sampling frequency that is input to this LSI device to 44.1KHz.

#### **FUNCTIONS AND FEATURES**

- 1) Reference clock output and internally required Timing signals can all be generated by merely connecting a liquid crystal.

- 2) The YM3613B has a function for switching the format of the 16-bit serial Voice signal input, so that the data can be output using the Digital Audio Interface format regardless of whether it was input started from the MSB or LSB.

- 3) Its built-in PLL circuit outputs clocks of a central 8.6436MHz frequency in accordance with the input frequency of the WCI pin.

- 4) The YM3613B outputs the External Digital signals of the Digital Audio Interface format.

- 5) The Subcode input terminal permits Subcode data to be read automatically.

- 6) Since the "Q" bit of Subcode data is subjected to a CRC (Cyclic Redundancy Code) check, the Channel status of the Digital Audio Interface is affected only when the CRC check on the "Q" bit tests positive.

- 7) Silicon gate CMOS construction (low power consumption)

- 8) 24-pin Dual-Inline Package (DIP)

- 9) +5V power supply

#### -NIPPON GAKKI CO., LTD.-

| V636 | 6カタログ                  |

|------|------------------------|

| CAT  | ALOG No. : LSI-2136131 |

|      | 1987.4                 |

ł

**YM3613B**

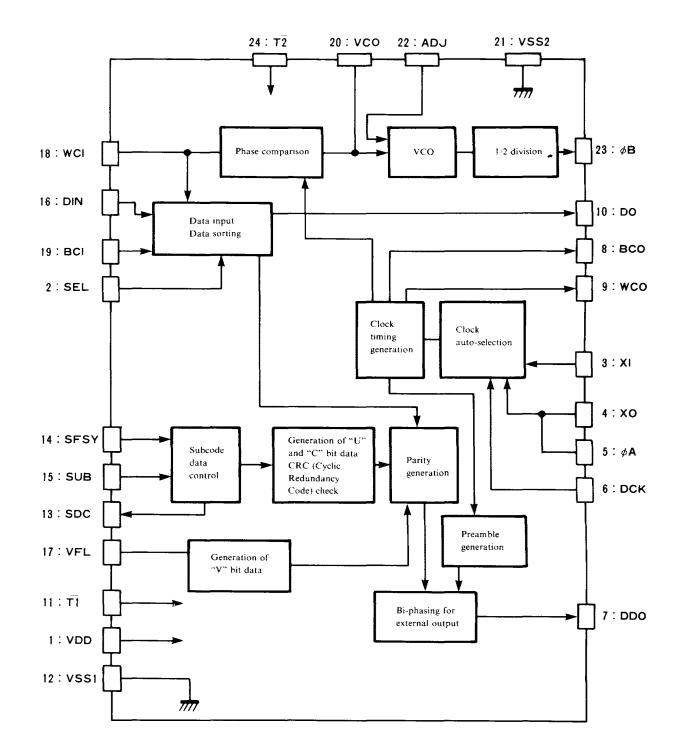

#### BLOCK DIAGRAM

### YM3613B

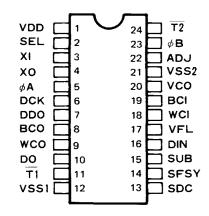

#### ■ PIN ASSIGNMENT DIAGRAM

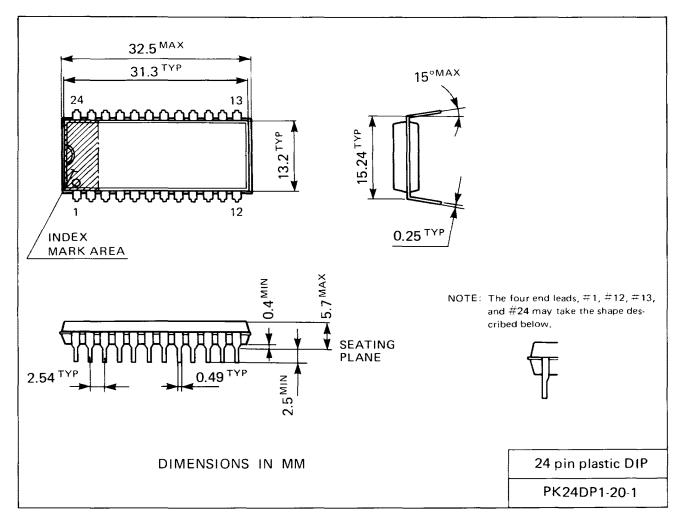

#### **EXTERNAL DIMENSIONS**

#### **TABLE OF PIN FUNCTIONS**

The asterisk in the I/O column indicates that the terminal is pulled-up internally.

| Pin<br>No. | Pin<br>Name | 1/0 | Function                                                                                                                                                         |  |  |  |

|------------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | VDD         |     | System power supply (+5V)                                                                                                                                        |  |  |  |

| 2          | SEL         | *   | Switches the data input to the DIN pin to MSB-first or LSB-first format.<br>"H": MSB first "L": LSB first                                                        |  |  |  |

| 3          | XI          | I   | Connection (input) pin for the crystal oscillating element (16.9344MHz)                                                                                          |  |  |  |

| 4          | хо          | 0   | Connection (output) pin for the crystal oscillating element.                                                                                                     |  |  |  |

| 5          | øA          | 0   | Output for crystal oscillation (16.9344MHz).                                                                                                                     |  |  |  |

| 6          | DCK         | *   | External clock input. Switching from the crystal clock is automatically performed.                                                                               |  |  |  |

| 7          | DDO         | 0   | Outputs Bi-Phase signals for external digital output.                                                                                                            |  |  |  |

| 8          | BCO         | 0   | Timing clocks for the DO pin. DO output data changes at the rise or fall of BCO. (2.8224MHz)                                                                     |  |  |  |

| 9          | wco         | 0   | Indicates the L or R channel and is synchronized to DO output.<br>"H": L channel. "L": R channel.                                                                |  |  |  |

| 10         | DO          | 0   | Serially outputs 16-bit Voice data starting from the MSB.                                                                                                        |  |  |  |

| 11         | T1          | *!  | Used for checking the internal circuitry and is not to be connected.                                                                                             |  |  |  |

| 12         | VSS1        |     | System GND.                                                                                                                                                      |  |  |  |

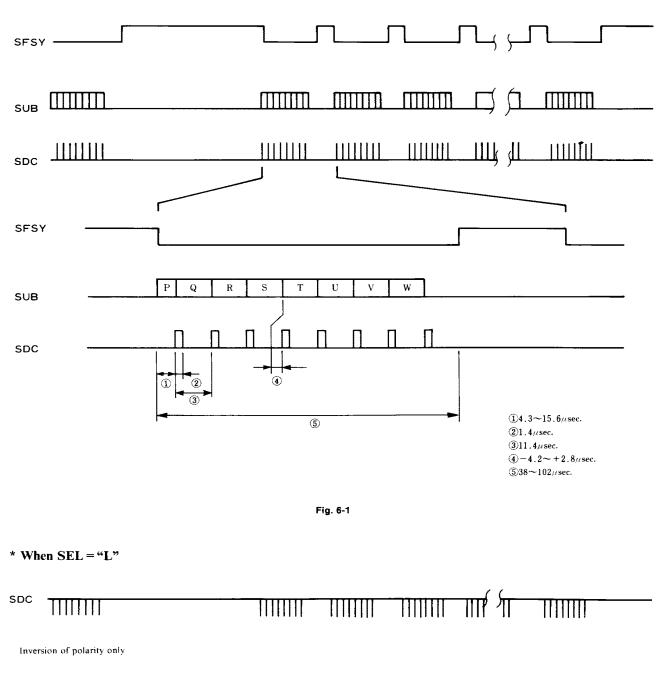

| 13         | SDC         | 0   | Timing clock for reading the Subcode data.<br>Eight clocks are output after SFSY goes "L".                                                                       |  |  |  |

| 14         | SFSY        | *!  | Indicates the presence of Subcode data at the SUB pin. When SFSY = "L", it indicates the leading bit of the Subcode data.                                        |  |  |  |

| 15         | SUB         | *   | Subcode data input. Serially inputs Subcode data in a "P"-"W" sequence.                                                                                          |  |  |  |

| 16         | DIN         | 1   | 16-bit Serial data input.                                                                                                                                        |  |  |  |

| 17         | VFL         | 1   | Indicates the presence/absence of errors in Voice data that was input from the DIN pin.                                                                          |  |  |  |

| 18         | WCI         | 1   | Indicates the L or R channel synchronized to the input Voice data of the DIN pin. "H": L channel. "L": R channel.                                                |  |  |  |

| 19         | BCI         | I   | Input Voice Data Timing clocks of the DIN pin.<br>The Voice data is input at the rising edge of BCI when SEL = "H" or at the falling edge of BCI when SEL = "L". |  |  |  |

| 20         | vco         | 1/0 | Externally-mounting capacitor pin for the internal VCO circuit.                                                                                                  |  |  |  |

| 21         | VSS2        |     | GND for the VCO circuit. To be connected in common with VSS1, since it is not commonly connected in the LSI.                                                     |  |  |  |

| 22         | ADJ         | 1   | Used for adjusting the VCO oscillating frequency. Not to be connected.                                                                                           |  |  |  |

| 23         | øB          | 0   | Clocks for VCO output. (8.643MHz)                                                                                                                                |  |  |  |

| 24         | T2          | *1  | Used for checking the internal circuitry, and is not to be connected.                                                                                            |  |  |  |

#### DESCRIPTION OF PINS

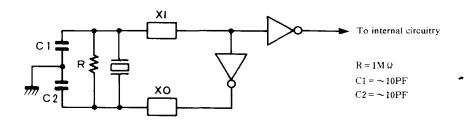

1) Clock Oscillation If a crystal oscillator

If a crystal oscillator element (16.9344MHz) is connected between the X1 and X0 pins, it will oscillate.

If clocks (5.6448MHz) are input to the DCK pin, the switching from the oscillating frequency of the crystal clock will be automatically performed and the clock will operate on the clock frequency of the DCK pin.

In case the DCK pin will not be used, leave it disconnected or fix it to "H". Leave the crystal oscillating element connected, even while the clock of the DCK pin will be operating.

2) SEL Pin Functions

ł

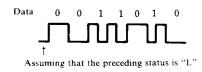

The SEL pin will go "H" or "L" according to the Serial Voice Data Format of the data that is input to the DIN pin. If SEL is not connected, SEL will be set to "H" by an internal pull-up resistor. The only pins that will be affected by the SEL pin are the DIN, SDC, and BCI pins. Other pins will give no appearance of changing.

• When SEL = "H"

Figs. 5 and 6-1 show the case where the SEL pin is "H".

The input data of the DIN pin is input at the rising edge of BCI, the DIN pin will assume a negative logic state, and the DO pin will assume a positive logic state.

#### • When SEL = "L"

Figs. 5 and 6-2 show the case where the SEL pin is "L".

The input data of the DIN pin is input at the falling edge of BCI, and both the DIN and DO pins will assume a positive logic state.

WCI will change at the rise of BCI.

The output timing of SDC is constant irrespective of "H" or "L" of SEL. But its polarity will be inverted.

3) Data Input Pins: BCI, DIN, and WCI The operating clock for the data output of the DO, BCO, DDO, and WCO pins is different from that of data input of the BCI, DIN, and WCI pins. The BCI clock can be freely set if WCI and WCO are properly synchronized and 16 bits of L/R channel data is available.

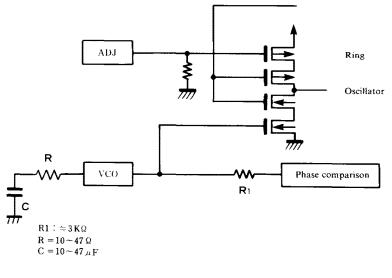

#### 4) VCO-Related Pins

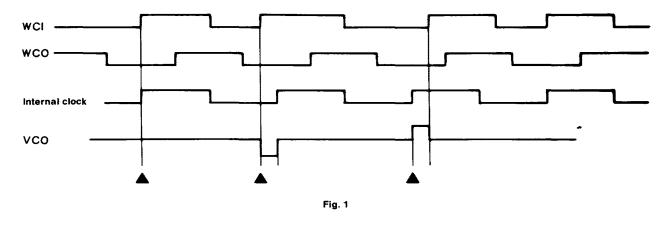

In case of 50% duty, the phase difference between WCO and the internal clock is about  $180^{\circ}$  off when SEL is "H", or about  $90^{\circ}$  off when SEL is "L".

The VCO oscillating frequency will change so that a phase comparison of WCI and  $\blacktriangle$  will produce equivalent phases. The oscillating frequency will rise when the WCI phase is delayed, and will fall when the WCI phase is advanced. When their phases are equal, the VCO oscillating frequency of the  $\emptyset$ B pin will become 8.6436MHz.

Be sure not to connect the ADJ pin (it is not particularly required for adjustment).

#### **TIMING CHARTS**

(1) Output

Fig. 3

**NOTE 1:** DDO is the bi-phase output. Thus, if the data of one data bit is "0", the DDO status will not change; if it is "1", its status will change. This situation is represented in Fig. 3 by a broken line. The solid line indicates the points where the status will always change.

- **NOTE 2:** Preamble "M" indicates that the data is for the L channel, whereas Preamble "W" indicates it is for the R channel. "M" and "W" will appear alternately; once every 192 times, however, "B" will appear instead of "M" to indicate the beginning of a block.

- **NOTE 3:** The "V" bit is called the Validity flag, and reflects the value input from the VFL pin.

- NOTE 4: The "U" bit is called User data. Among the Subcode data "P" to "W" which is input from the SUB pin, only "P" is compulsorily set to "1" so that serial output of "1, Q, R, S, T, U, V, and W is performed (see Fig. 4).

Sub code sync word Q1 R1 S1 T1 U1 V1 W1 Q2 R2 S2 T2 U2 V2 W2 1165 1 Q96 R96 S96 T96 U96 V96 W96 Û Ð  $Q_1 \quad R_1 \quad S_1 \quad T_1 \quad U_1 \quad V_1 \quad W_1$ Fig. 4

- NOTE 5: The "C" bit is called Channel Status and comprises 192 bits. Only when the Control bit of the Channel Status tests positive for a CRC check, the four Control bits ("Q" bits) within the Subcode will be copied. (From Preamble "B", sequentially from the 0th to the 3rd) the 8th "C" bit will be compulsorily set to "1" to indicate that the Category Code is CD. All other bits will be set to "0".

- **NOTE 6:** The "P" bit is the Parity bit and employs even parity. The "P" bit will thus change so that the quantity of "1's" in the data will total an even number.

- (2) Input

#### \* When SEL = "H"

| BCI            | www      | www.       | mmmm                      | www.www    | www    | MMMMM  | mmm       | ហហា       |

|----------------|----------|------------|---------------------------|------------|--------|--------|-----------|-----------|

| DIN            | DATA 0   | ww14]13]   | DATA 1<br>211110987654321 | 1-16       |        | DATA 2 | 5 4 3 2 1 |           |

| WCI            | <u>1</u> |            | ch                        |            | L      | ch     |           |           |

| VFL            |          |            | V1                        |            |        | V2     | X         |           |

| DO             |          | MSB DATA 0 | LSB                       | MSB        | DATA 1 | LSB    |           |           |

| WCD<br>44.1KHz |          |            | ━\                        |            |        |        |           |           |

| DDO            |          | LSB        | DATA 0                    | MSB VeUC P | LSB    | DATA   | <u>M</u>  | SB V1UC P |

|                |          | Preamble M |                           | Pream      | nble W |        |           |           |

#### \* When SEL = "L"

<sup>BCI</sup> WWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWWW

| DIN | 1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 w | [ - 1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

|-----|--------------------------------------|--------------------------------------|

| WCI | <b>—</b>                             |                                      |

|     |                                      |                                      |

Fig. 5

- NOTE 1: The above timing charts are standard examples. The broken line within the figure indicate the sections in which the changing point of the data cannot be clearly shown. BCI, DIN, WCI, and VFL operate on a different clock than DO, WCO, DDO, and BCO.

- **NOTE 2:** Within the broken-line section, if the VFL pin is set "H" for an interval longer than one BCI1 clock, the Validity flag of DDO will become "H".

## YM3613

\* When SEL = "H"

Fig. 6-2

#### ■ ELECTRICAL CHARACTERISTICS

#### 1. Absolute Maximum Ratings

| Item                  | Symbol | Rating          | Units |  |

|-----------------------|--------|-----------------|-------|--|

| Supply voltage        | VDDVSS | -0.3~+7.0       | v     |  |

| Input voltage         | Vı     | Vss-0.3~Vdd+0.5 | V     |  |

| Operating temperature | Тор    | -20~+75         | °C    |  |

| Storage temperature   | Tstg   | $-50 \sim +125$ | °C    |  |

#### 2. Recommended Operating Conditions

| Item           | Symbol  | Min. | Min. Typ. |     | Units |

|----------------|---------|------|-----------|-----|-------|

| Supply voltage | VDD-VSS | 4.5  | 5.00      | 5.5 | v     |

#### 3. Electrical Characteristics

| Item                      | Symbol | Conditions                       | Min.       | Тур. | Max. | Units |

|---------------------------|--------|----------------------------------|------------|------|------|-------|

| Operating current         | ldd    | $V_{DD} = 5V$<br>fc = 16.9344MHz |            | 10   | 18   | mA    |

| High-level output voltage | Vон    | Іон = 0.4mA                      | 4.0        |      |      | v     |

| Low-level output voltage  | Vol    | IoL=2mA                          |            |      | 0.4  | v     |

| High-level input voltage  | Viн    | XI pin excluded<br>XI pin        | 2.0<br>3.0 |      |      | v     |

| Low-level input voltage   | VIL    |                                  |            |      | 0.8  | v     |

| Input leakage current     | ILK    | VI = 5V                          |            |      | 10   | μA    |

NOTE: The analog VCO pin and the ADJ pin are excluded.

The specifications of this product are subject to improvement changes without prior notice.

| <br>AGENCY |  |

|------------|--|

|            |  |

|            |  |

|            |  |

|            |  |

|            |  |

#### **NIPPON GAKKI CO., LTD** Address inquiries to: **Electronic System Division** 203, Matsunokijima, Toyooka-mura, Toyooka Factory Iwata-gun, Shizuoka-ken, 438-01 Electronic Equipment business section Tel. 053962-3125 Tokyo Office 3-4, Surugadai Kanda, Chiyoda-ku, Tokyo, 104 Ryumeikan Bldg. 4F Tel. 03-255-4481 Osaka Office 1-16, Shin-ashiyashimo, Suita-shi, Osaka, 565 Tel. 06-877-7731 U.S.A. YAMAHA International Corp. 6600 Orangethorp Ave. Buena Park California 90620

0.2K-0510 C Delated in Janan 87. 4 NO DATE 007690 YR