# Foundation Series 2.1i Quick Start Guide

Setting Up the Foundation Tools

**Foundation Overview**

**Basic Tutorial**

**Glossary**

**Index**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479;

5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

## **About This Manual**

This guide should be used as the initial learning tool for designers who are unfamiliar with the features of the Foundation series software.

#### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URL.

| Resource             | Description/URL                                                                                                                                                                                                                                                 |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                           |  |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools Search this database using the search function at http://support.xilinx.com/support/searchtd.htm                                                                                              |  |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                     |  |  |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |  |  |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                |  |  |

| Tech Tips            | Latest news, design tips, and patch information on the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                   |  |  |

#### **Manual Contents**

This guide covers the following topics.

- Chapter 1, "Setting Up the Foundation Tools," gives instructions for installing Foundation 2.1i and provides you with information about the type of computer you need to successfully implement your designs.

- **Chapter 2**, "Foundation Overview," looks in-depth at the capability and flexibility of the Foundation software.

- **Chapter 3**, "Basic Tutorial" provides a step-by-step example explaining how to use the basic Foundation tools.

- **Appendix A**, "Glossary," defines some of the commonly used terms in this Guide.

#### **Conventions**

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

## **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

\textbf{File} \rightarrow \textbf{Open}

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

· Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on | off}

```

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on | off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block name loc1 loc2 . . . locn;

```

#### **Online Documents**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Contents**

| Manual                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                              |

| s                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                              |

| Setting Up the Foundation Tools                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                              |

| Supported Platforms and Machine Requirements  Memory Requirements for Xilinx Architectures  Running Setup  Network Compatibility  Obtaining and Setting Up Licenses  Upgrading an Existing License  Customer Service | 1-2<br>1-3<br>1-4<br>1-4<br>1-5<br>1-7                                                                                                                                                                                                                                                                                                                       |

| Foundation Overview                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                              |

| Design Flows                                                                                                                                                                                                         | 2-2<br>2-2<br>2-3<br>2-6<br>2-6<br>2-7<br>2-8<br>2-9                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                      | Additional Resources Manual Contents  Typographical Online Documents  Setting Up the Foundation Tools Installation Notes Supported Platforms and Machine Requirements Memory Requirements for Xilinx Architectures. Running Setup Network Compatibility Obtaining and Setting Up Licenses. Upgrading an Existing License Customer Service. Technical Support |

| Instantiating LogiBLOX and CORE Generator Modules         | . 2-10 |

|-----------------------------------------------------------|--------|

| Accessing the Design Entry Tools                          | . 2-11 |

| Using the Design Implementation Tools                     |        |

| Translate                                                 |        |

| MAP (FPGAs)                                               | . 2-13 |

| Place and Route (FPGAs)                                   |        |

| CPLD Fitter (CPLDs)                                       |        |

| Configure (FPGAs)                                         |        |

| Bitstream (CPLDs)                                         |        |

| Interpreting the Reports                                  |        |

| Translation Report                                        | . 2-16 |

| Map Report (FPGAs)                                        |        |

| Place and Route Report (FPGAs)                            |        |

| Pad Report (FPGAs)                                        |        |

| Fitting Report (CPLDs)                                    |        |

| Post Layout Timing Report                                 |        |

| Asynchronous Delay Report                                 |        |

| Selecting Options                                         |        |

| Using Constraint Files                                    | . 2-19 |

| Design, Netlist, and User Constraints                     | . 2-19 |

| Using the Xilinx Constraints Editor                       | . 2-20 |

| Creating a User Constraint File                           | . 2-20 |

| Static Timing Analysis                                    |        |

| Static Timing Analysis after Synthesis (HDL Only)         | . 2-21 |

| Static Timing Analysis after Map (FPGAs Only)             | . 2-21 |

| Static Timing Analysis after Place and Route (FPGAs Only) | . 2-22 |

| Summary Timing Reports                                    | . 2-22 |

| Detailed Timing Analysis                                  | . 2-23 |

| Creating Simulation Files                                 | . 2-24 |

| When Can Simulation Data be Created?                      | . 2-24 |

| Creating Functional Simulation Data                       | . 2-25 |

| Creating Timing Simulation Data                           | . 2-26 |

| HDL Simulation                                            | . 2-26 |

| Downloading a Design                                      | . 2-27 |

| Creating a PROM                                           |        |

| In-Circuit Debugging                                      |        |

| Re-Entrant Routing (FPGAs)                                | . 2-28 |

## **Chapter 3** Basic Tutorial

| Getting Started                                     | 3-1  |

|-----------------------------------------------------|------|

| Design Description                                  | 3-2  |

| Starting the Project Manager                        | 3-3  |

| The Project Manager                                 | 3-5  |

| Project Libraries                                   | 3-7  |

| Schematic Design Entry                              |      |

| Starting the Schematic Editor                       | 3-9  |

| Manipulating the Screen                             | 3-10 |

| Adding a Library Component                          | 3-11 |

| Correcting Mistakes                                 |      |

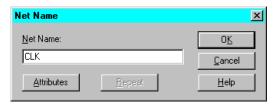

| Drawing and Labeling Nets                           | 3-13 |

| Saving the Schematic                                |      |

| HDL-Based Design Entry                              |      |

| Adding a File to the Design                         | 3-14 |

| Correcting Syntax Errors                            |      |

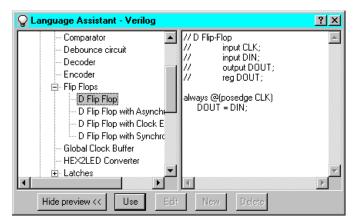

| Using the Language Assistant                        |      |

| Design Description                                  |      |

| Synthesis                                           |      |

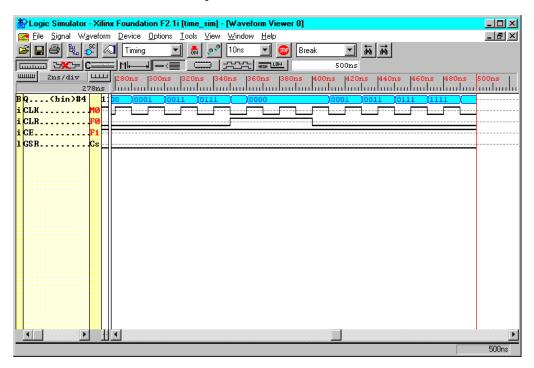

| Functional Simulation                               |      |

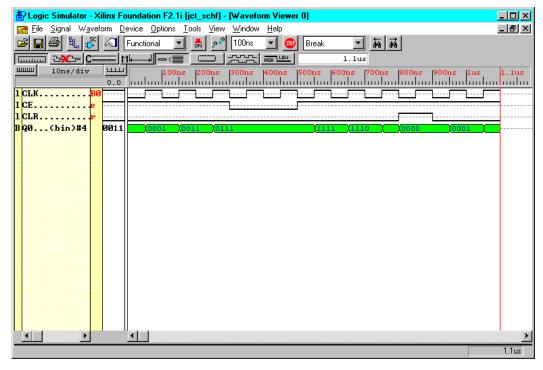

| Starting the Logic Simulator                        |      |

| Performing Simulation                               |      |

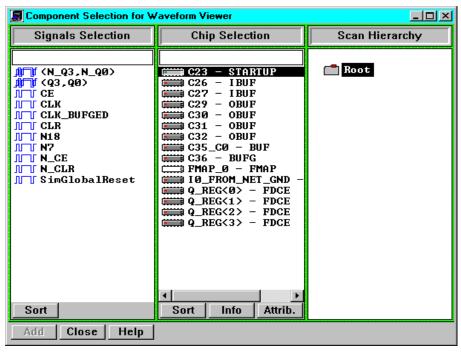

| Adding Signals                                      |      |

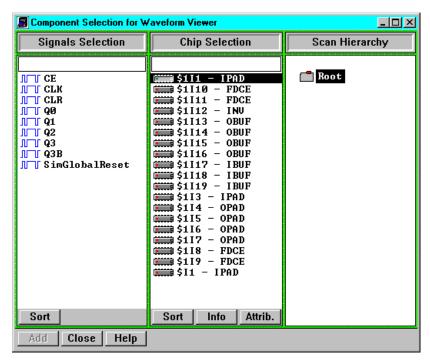

| Adding Signals Using the Component Selection Window |      |

| Deleting a Signal                                   |      |

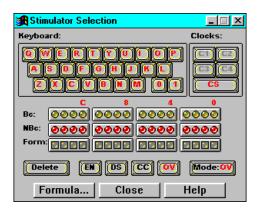

| Adding Stimulus                                     |      |

| Stimulating with the Internal Binary Counter        |      |

| Stimulating with Keyboard Stimulators               |      |

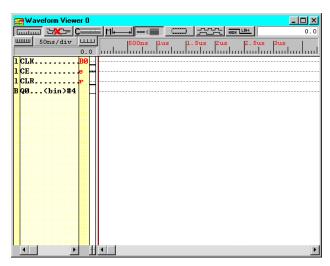

| Running the Simulation                              |      |

| Implementation                                      |      |

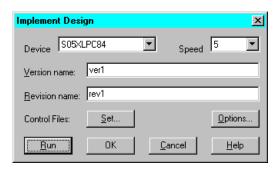

| Implementing the Schematic Design                   |      |

| Implementing the HDL Design                         |      |

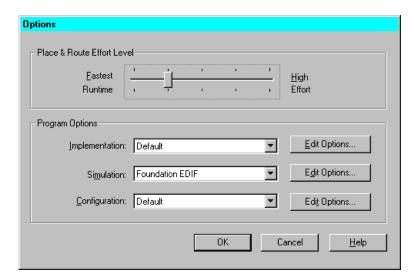

| Implementation Options                              |      |

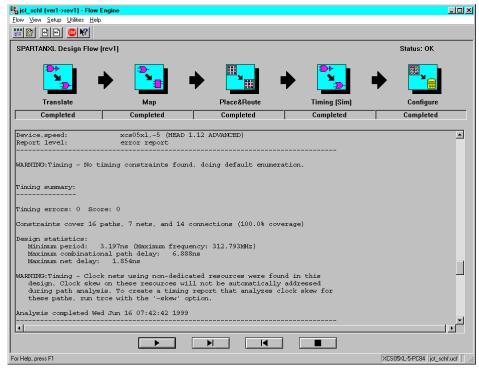

| Running Implementation — The Flow Engine            |      |

| Viewing Implementation Results                      |      |

| Timing Simulation                                   |      |

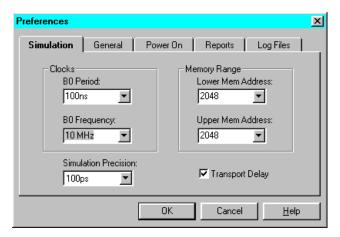

| Invoking Timing Simulation                          |      |

| Simulating with Script Files - Script Editor        |      |

| Running the Simulation from the Script Editor       |      |

| Closing the Simulator                               | 3-36 |

## **Appendix A Glossary**

# Chapter 1

# **Setting Up the Foundation Tools**

This chapter lists the system requirements for the Foundation Series 2.1i Xilinx design tools software and discusses the recommended machine types and memory requirements to comfortably run the software. Also included are general instructions for installing the software, contacting customer support, and obtaining and installing the necessary authorization codes and licenses.

For a detailed discussion, refer to the "System Requirements" chapter in the *Foundation Series 2.1i Installation Guide and Release Notes*.

This chapter contains the following sections:

- "Installation Notes"

- "Customer Service"

- "Technical Support"

#### **Installation Notes**

Ensure the optimum use and operation of your new design tools by installing Foundation Series 2.1i on the recommended hardware with sufficient memory (RAM and hard disk "swap" space). If you experience problems with either the installation, operation, or verification of your installation, contact the Xilinx Technical Support hotline. Refer to the "Technical Support" section of this chapter for specifics.

#### **Supported Platforms and Machine Requirements**

The Foundation Series 2.1i software is a PC-only release. Foundation runs on either Windows 95/98 or Windows NT. (Service Pack 3 or 4 required with NT.) The following list shows the minimum recommended type of PC you should have to perform designs for Xilinx FPGAs or CPLDs.

- Pentium Pro Processor®

- Windows 95<sup>®</sup>, Windows 98<sup>®</sup> or Windows NT 4.0<sup>®</sup>

(with Service Pack 3 or 4 installed)

- 120 MHz clock speed

- System Memory—32 MB to 64 MB (dependent on device)

- Swap Space—48 MB to128 MB (dependent on device)

- Required disk space, 2 GB recommended

- SVGA 17" monitor

- 4x CD-ROM drive

- Ports—Two ports (one for a pointing device and one parallel port for the parallel download cable, if needed). You can share the parallel port used for the parallel download cable.

- Keyboard

- Mouse—2-button or 3-button (Microsoft Windows compatible).

On a 3-button mouse, the middle button is not used.

**Note:** Due to the size and complexity of the XC4000 and Virtex devices, Xilinx recommends that these designs be compiled using a high-performance computer. 64 MB of RAM as well as 64 MB of swap space is required to compile XC4000EX designs, but Xilinx recommends that at least 128MB of both RAM and swap space be used. For Virtex designs, Xilinx recommends 256 MB of RAM.

Swap file size requirements also vary with the design and constraint set size. By default, Windows 95/98 manages its swap file size automatically, but for Windows NT, you may need to increase it. Typically, your Windows NT swap file size should be twice as large as your system RAM amount.

It is important to note that slower systems or systems with less than the recommended RAM and/or swap space may exhibit longer runtimes.

#### **Memory Requirements for Xilinx Architectures**

The various steps of designing Xilinx FPGAs or CPLDs require a substantial amount of memory, as shown in the following table.

**Table 1-1 Minimum Memory Requirements**

| Xilinx Packages                   | RAM   | Virtual Memory<br>(Swap Space) |

|-----------------------------------|-------|--------------------------------|

| Base or Base Express              | 48 MB | 64 MB                          |

| Standard or<br>Foundation Express | 64 MB | 128 MB                         |

**Note:** The values given in the above table are for typical designs and include the normal load created by the operating system. Additional memory may be required for certain "boundary-case" or "extremely large" designs, as well as for concurrent operation of other non-Xilinx applications.

### **Running Setup**

Please refer to the *Foundation Series 2.1i Installation Guide and Release Notes* for complete details on installation and prerequisites for installation.

1. To start the installation, insert the Design Environment CD into the CD-ROM drive.

If your system has the Auto Run feature enabled, the Foundation setup program will start automatically.

If you do not have the Auto Run enabled on your system, select Start  $\rightarrow$  Run. Type d:setup.exe in the Open field of the Run window and click OK. (If your CD-ROM drive is not the "d" drive, substitute the appropriate drive designation.)

You are required to enter your name, company, and CD key in the User Information screen before you can begin the installation. Your CD Key is the number printed on the CD Key label on the back of the CD case. The Product Information label, which is also located on the back of the CD case, contains the part number and serial number.

- 2. Follow the instructions on the screen to install the software. When complete, remove the CD.

- 3. (Optional) To install the Xilinx documentation CD, insert the CD and follow the instructions.

You may need to reboot your PC to allow the new/modified environment variables and path statement to take effect before you can run the design implementation tools. The Install program will inform you if you need to reboot.

There are optional CDs that you may have received in your package. Consult the *Foundation Series 2.1i Installation Guide and Release Notes* for information about these CDs.

### **Network Compatibility**

The Xilinx installation program supports only TCP-IP style networks. Novell is *not* a TCP-IP style network. You can run the Xilinx implementation tools from a network but not the Aldec design entry tools or Express. Also, ABEL cannot be run from the network.

#### **Obtaining and Setting Up Licenses**

A license is only required for the Base Express and Foundation Express products. New and existing customers installing the Foundation Series 2.1i Base or Standard products do *not* need Express licenses.

For complete details about licensing, refer to the "Express Software Licensing" chapter in the *Foundation Series 2.1i Installation Guide and Release Notes*.

If you are a new customer with no license.dat file installed and no LM\_LICENSE\_FILE variable set, a temporary license is automatically installed with Base Express and Foundation Express. With the Foundation Express temporary license, the Express constraints editor, timing analyzer, and Schematic Viewer GUIs are not available.

When you install the Foundation 2.1i software, this temporary license file (license.dat) is copied to %XILINX%\data on your system. In addition, the LM\_LICENSE\_FILE file variable is automatically set up to point to this license.dat file. When you receive a permanent license.dat file, Xilinx recommends that you put this permanent license outside the Xilinx software tree. A common location is c:\flexIm.

To obtain a permanent license, you need to be a registered user in the Customer Service database.

New Xilinx users should fill out their Xilinx registration card and *fax or mail* it to their Customer Service location. Customer Service will send your license and authorization codes. You can also register online within the software install program.

If you are an existing customer and you need a new license, you can obtain the new license by accessing online Web registration at http://support.xilinx.com. If you request your license by fax, please fill out the form that is enclosed in your package.

Upon receiving a permanent license from Xilinx, make sure your LM\_LICENSE\_FILE environment variable points to the new license file.

The following scenarios describe the requirements for licensing. For details about these scenarios and other licensing issues, see the

"Express Software Licensing" chapter in the Foundation Series 2.1i Installation Guide and Release Notes.

- If you are an existing customer upgrading from Base or Standard to Base Express or Foundation Express, you need to obtain a new license.dat file from Xilinx.

- If you are an existing customer with Base Express and are upgrading to 2.1i Base Express, you must modify the package definition in your license.dat file. Please see the "Upgrading an Existing License" section.

- If you are an existing customer with Foundation Express and are upgrading to 2.1i Foundation Express, you must modify the package definition in your license.dat file. Please see the "Upgrading an Existing License" section.

- If you are an existing customer with Base Express and are upgrading to Foundation Express, you must obtain a new license.dat file from Xilinx.

- If you are an existing customer with Base or Standard and are upgrading to the 2.1i Base or Standard, you do not need to obtain a license, that is, there are no licensing or registration requirements.

- If you are a new customer receiving Base or Standard, register with Xilinx. You do not need to obtain a license.

- If you are a new customer receiving Base Express or Foundation Express, you must register with Xilinx and obtain a permanent license.dat file.

#### **Upgrading an Existing License**

If you are upgrading Base Express or Foundation Express to 2.1i, you must manually update your existing license file. To update this file, perform the following steps:

Locate the existing permanent Foundation license file. This file is typically located at C:\flexlm\license.dat and will have FND BSX-PC or FND-EXP-PC increment lines similar to the following:

INCREMENT FND-BSX-PC xilinxd 1.000 01-JAN-0 0 CCD4DEC6B7D7723BB082\"XSJ\_davet" 00a024a9ea43

- 2. Open the license.dat file using a plain text editor.

- Replace the existing PACKAGE definitions with the following PACKAGE definitions.

The package definitions are available in electronic format in a file named "license\_update.txt". The license\_update.txt file is located both on the Foundation Series 2.1i CD and is copied to the Foundation Series 2.1i installation area in %XILINX%\data.

- Foundation Series 2.1i CD

Insert the CD in the CDROM drive (assume D:\). The package definitions are located in D:\license\_update.txt.

- Foundation Series 2.1i installation area

The peakers definitions are leasted in

The package definitions are located in C:\FNDTN\data\license\_update.txt

#### For FND-BSX-PC

```

PACKAGE FND-BSX-PC xilinxd 1.000 D07010C1B82E60A3A701 \

COMPONENTS="system-PC bit-PC \

xc3000D-PC xc4000E-PC xc5200E-PC \

ngd2vhdl-PC verilog-PC \

Foundation-PC X-VHDL-PC \

FPGA-Express:2000.05 \

FPGA-Express-VHDL-Base:2000.05 \

FPGA-Express-VLOG-Base:2000.05 \

FPGA-Express-XC3k-Optimizer:2000.05 \

FPGA-Express-XC4k-Optimizer:2000.05 \

FPGA-Express-XC5k-Optimizer:2000.05 \

FPGA-Express-XC9k-Optimizer:2000.05 "

For FND-EXP-PC

PACKAGE FND-EXP-PC xilinxd 1.000 2080B0F13916AA26C238 \

PACKAGE FND-EXP-PC xilinxd 1.000 20405041295F375FE6F6 \

COMPONENTS="system-PC bit-PC \

xc3000D-PC xc4000X-PC xc5200X-PC \

ngd2vhdl-PC verilog-PC \

Foundation-PC X-VHDL-PC \

FPGA-Express:2000.05 \

FPGA-Express-VHDL-Base:2000.05 \

FPGA-Express-VLOG-Base:2000.05 \

FPGA-Express-XC3k-Optimizer:2000.05 \

FPGA-Express-XC4k-Optimizer:2000.05 \

FPGA-Express-XC5k-Optimizer:2000.05 \

FPGA-Express-VIRTEX-Optimizer:2000.05 \

FPGA-Express-XC9k-Optimizer:2000.05 \

FPGA-Express-Constraint-Mgr:2000.05 \

FPGA-Express-GAT:2000.05 "

```

#### **Customer Service**

For software licensing information, warranty status, shipping, and order management issues, contact Xilinx Customer Service using the information in the following table.

| Country                               | Telephone        | Facsimile        |

|---------------------------------------|------------------|------------------|

| United States and Canada <sup>1</sup> | 1-800-624-4782   | 408-559-0115     |

| United Kingdom <sup>2</sup>           | 01932-333550     | 01932-828521     |

| Belgium <sup>2</sup>                  | 0800 73738       |                  |

| France <sup>2</sup>                   | 0800 918333      |                  |

| Germany <sup>2</sup>                  | 0130 816027      |                  |

| Italy <sup>2</sup>                    | 1677 90403       |                  |

| Netherlands <sup>2</sup>              | 0800 0221079     |                  |

| Other European Locations <sup>2</sup> | (44) 1932-333550 | (44) 1932-828521 |

| Japan                                 | 81 3 3297 9153   | 81 3 3297 9189   |

<sup>&</sup>lt;sup>1</sup>Mon-Fri, 8:00 am - 5:00 pm Pacific time

If you are an international customer, contact your local sales representative for customer service issues. Refer to the Xilinx web site at http://support.xilinx.com/company/sales/int\_reps.htm for contact information.

A complete list of Xilinx worldwide sales offices is at http://support.xilinx.com/company/sales/offices.htm.

$<sup>^2\</sup>mathrm{Monday-Friday},\,9:00$  a.m. to 5:30 p.m. United Kingdom time—English speaking only.

## **Technical Support**

The following section details how to reach the Xilinx Application Service centers for your area. If you experience problems with the installation or operation of your software, Xilinx suggests that you first go to our http://support.xilinx.com website.

You can also contact the Xilinx Technical Support hotline by phone, email, or fax. When e-mailing or faxing inquiries, provide your complete name, company name, and phone number. The following table gives Worldwide contact information for Xilinx Application Service centers.

| Location              | Telephone                        | Electronic Mail     | Facsimile (Fax)   |

|-----------------------|----------------------------------|---------------------|-------------------|

| North America         | 1-408-879-5199<br>1-800-255-7778 | hotline@xilinx.com  | 1-408-879-4442    |

| United Kingdom        | 44-1932-820821                   | ukhelp@xilinx.com   | 44-1932-828522    |

| France                | 33-1-3463-0100                   | frhelp@xilinx.com   | 33-1-3463-0959    |

| Germany               | 49-89-93088-130                  | dlhelp@xilinx.com   | 49-89-93088-188   |

| Japan                 | local distributor                | jhotline@xilinx.com | local distributor |

| Korea                 | local distributor                | korea@xilinx.com    | local distributor |

| Hong Kong             | local distributor                | hongkong@xilinx.com | local distributor |

| Taiwan                | local distributor                | taiwan@xilinx.com   | local distributor |

| Corporate Switchboard | 1-408-559-7778                   |                     |                   |

# Chapter 2

#### **Foundation Overview**

This overview explains the basic concepts and design flow of the Foundation Series 2.1i release as it spans the flow from netlist to final PROM file. The chapter describes the basic tools; for details on using the tools, refer to the "Basic Tutorial" chapter.

The Foundation Overview chapter contains the following sections:

- "New Features"

- · "Design Flows"

- "Using the Foundation Design Entry Tools"

- "Using the Design Implementation Tools"

- "Using Constraint Files"

- "Static Timing Analysis"

- "Creating Simulation Files"

- "Downloading a Design"

- "Re-Entrant Routing (FPGAs)"

The flow described in this chapter is generally applicable to all Xilinx families. However, many of the details apply only to the FPGA device families. For complete information on CPLD design flows, refer to the Foundation online help.

#### **New Features**

The major new features for the Foundation 2.1i release include the following:

- Integration of the CORE Generator tool within the Project Manager

- Enhanced project data archiving

- New 3.2 version of Foundation Express

- · Guide file functionality

- New conversion utilities, ABEL2HDL and AHDL2HDL

- Language Assistant support for the Core Generator tool

- Schematic support in HDL flows

- New device support

- Integration of the Xilinx Constraints Editor in the Project Manager

- Runtime improvement

- CPLD ChipViewer

- New HTML document viewer for all online documents

For a detailed description of these new features, refer to the What's New file by selecting  $\mathtt{Start} \to \mathtt{Programs} \to \mathtt{Xilinx}$  Foundation Series 2.1i  $\to \mathtt{What's}$  New.

For detailed information about Xilinx documentation, refer to the "Introduction" chapter of the *Foundation Series 2.1i User Guide*.

## **Design Flows**

The Foundation Series design tools interface supports two basic flows within the Project Manager: HDL and Schematic.

#### **HDL Flow**

An HDL Flow project can contain VHDL, Verilog, or schematic toplevel designs with underlying VHDL, Verilog, or schematic modules. HDL files can be created using the HDL Editor, Finite State Machine Editor, or other text editors. Design sources are analyzed and optimized by the Express Synthesis Engine.

LogiBLOX, CORE Generator, and ABEL modules as well as XNF files can be instantiated in the design source files using the "black box instantiation method". Black box modules are not elaborated and optimized during synthesis. State machine modules are synthesized as VHDL or Verilog.

For a detailed description of the design methodologies, refer to the "Design Methodologies - HDL Flow" chapter in the *Foundation Series* 2.1i User Guide.

#### Schematic Flow

The Schematic Flow supports the following design strategies.

- Top-level schematic design with the Xilinx Unified Libraries components, LogiBLOX symbols, CORE generated modules, and ABEL, HDL and/or state machine macros

- Top-level ABEL-based designs (not recommended for FPGA designs)

- Top-level State Machine designs—only as ABEL designs.

For a detailed description of the design methodologies, refer to the "Design Methodologies - Schematic Flow" chapter in the *Foundation Series 2.1i User Guide*.

Also refer to the "HDL Design Entry and Synthesis" chapter in the *Foundation Series 2.1i User Guide.*

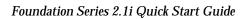

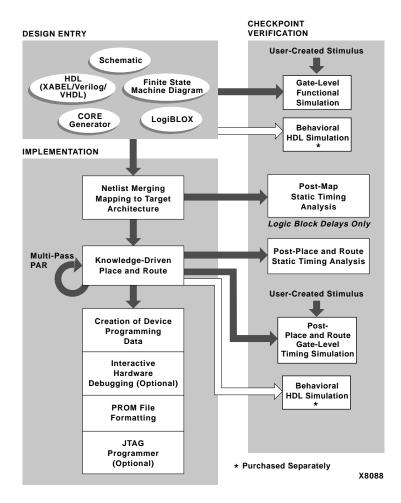

The following two figures illustrate the basic design flow for FPGAs and CPLDs. For detailed design flow illustrations, refer to the "File Processing Overview" appendix in the *Foundation 2.1i Series User Guide*.

Figure 2-1 Foundation Overall Design Flow for FPGAs

Figure 2-2 Foundation Overall Design Flow for CPLDs

## **Using the Foundation Design Entry Tools**

This section describes the basic procedure for using the design entry tools.

#### Starting the Foundation Project Manager

To start the Project Manager, double click the Project Manager icon in the Foundation Series program group. The icon to click is shown in the following figure.

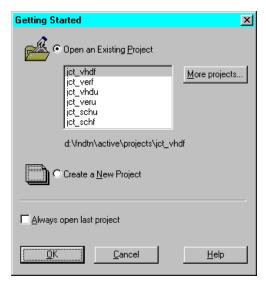

A Getting Started dialog box displays, allowing you to select a project to open or create a new project.

#### **Creating a New Project**

To create a new project, follow these steps:

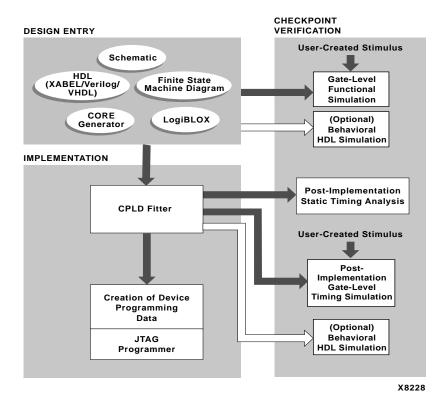

1. Select Create a New Project and click OK.

Figure 2-3 New Project Dialog Box

- 2. After the New Project dialog box displays, enter a name for the project. Change the directory for the project, if desired, by using the Browse button.

- 3. Choose the appropriate family, part, and speed grade and flow type. (schematic flow only)

- 4. Click OK. The new project displays in the Project Manager.

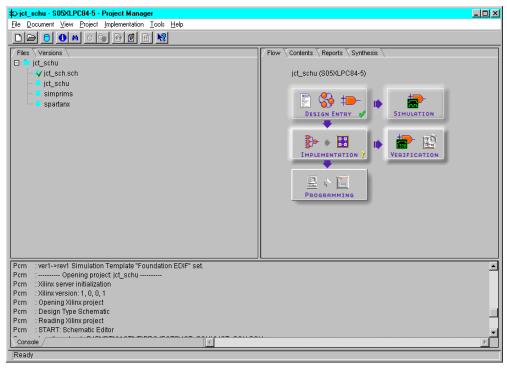

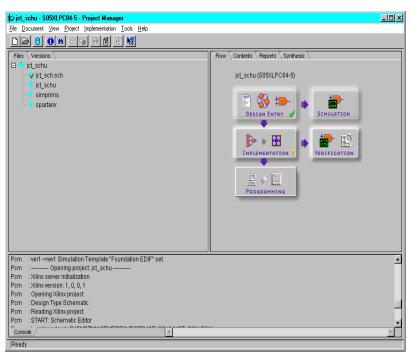

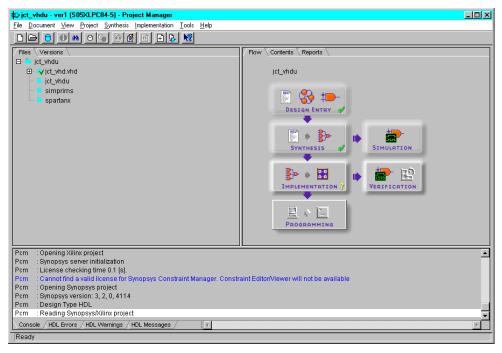

Figure 2-4 Foundation Project Manager

For more information about creating new projects in Foundation, refer to Foundation's online help system. For detailed information about the Project Manager, refer to the online help by selecting Help  $\rightarrow$  Foundation Help Contents  $\rightarrow$  Project Manager. Also see the "Project Manager" section of the "Project Toolset" chapter in the Foundation Series 2.1i User Guide.

#### Creating Top-level VHDL/Verilog Designs

You can create VHDL and Verilog designs if you purchased a version of Foundation that includes the Synopsys FPGA Express package. FPGA Express is included with these Foundation versions: 1) Base Express, and 2) Foundation Express.

You can create a variety of top-level schematic, VHDL or Verilog designs.

- All-HDL designs

- HDL designs with State Machine macros

- HDL designs with black box instantiations

- Schematic designs

Black boxes are not synthesized by Express; they are passed to the implementation tools for translation by the Flow Engine.

For a detailed description of the procedures for creating these types of designs, refer to the "Design Methodologies - HDL Flow" chapter in the *Foundation Series 2.1i User Guide*.

Also refer to the Foundation 2.1i Watch Tutorial located at http://support.xilinx.com/support/techsup/tutorials/index.htm.

For a discussion of HDL design issues, refer to the "HDL Design Entry and Synthesis" chapter in the *Foundation Series 2.1i User Guide*.

For information on how to use the VHDL and Verilog languages, refer to the online software documents, *VHDL Reference Guide* and *Verilog Reference Guide*.

Foundation 2.1i also includes utilities that convert ABEL and AHDL to HDL (ABEL2HDL and AHDL2HDL). To access these utilities from the Project Manager, select Tools  $\rightarrow$  Utilities. In order to use ABEL or AHDL designs as top-level HDL designs, you must convert the designs.

#### **Creating Top-Level Schematic Designs**

You can create a variety of top-level designs.

- All schematic designs

- Schematic designs with instantiated HDL macros, LogiBLOX and CORE Generator modules, and state machine macros

- Top-level ABEL-based designs

- State Machine designs—only as ABEL designs

For a detailed description of the procedures for creating these types of designs, refer to the "In-Depth Tutorial—Schematic-Based Designs" in the *Foundation 2.1i Watch Tutorial* located at http://support.xilinx.com/support/techsup/tutorials/index.htm.

Also refer to the "Design Methodologies - Schematic Flow" chapter in the *Foundation Series 2.1i User Guide*.

For a discussion of schematic design issues, refer to the "Schematic Design Entry" chapter in the *Foundation Series 2.1i User Guide*.

#### **Creating State Machine Designs**

State machine designs typically start with the translation of a concept into a "paper design," usually in the form of a state diagram or a bubble diagram. The paper design is converted to a state table and then, into the source code itself.

A State Machine design can be used in the following ways.

- Top-level design in a Schematic Flow—as an ABEL design only

- A module in a schematic

- A module in a VHDL or Verilog design (not ABEL)

For a detailed discussion of the design steps, refer to the "Design Methodologies - Schematic Flow" chapter and the "Design Methodologies - HDL Flow" chapter in the *Foundation Series 2.1i User Guide*.

For a description of a sample state machine, refer to the "State Machine Designs" chapter in the *Foundation Series 2.1i User Guide*.

# Instantiating LogiBLOX and CORE Generator Modules

LogiBLOX is a design tool for creating high-level modules such as counters, shift registers, and multiplexers for FPGA and CPLD designs. LogiBLOX includes both a library of generic modules and a set of tools for customizing these modules. LogiBLOX modules are pre-optimized to take advantage of Xilinx architectural features such as Fast Carry Logic for arithmetic functions and on-chip RAM for dual-port and synchronous RAM. With LogiBLOX, you can create high-level LogiBLOX modules that will fit into your schematic-based design or HDL-based design.

For information about instantiating LogiBLOX into designs, refer to the following sections in the *Foundation Series 2.1i User Guide*:

- "Schematic Designs With Instantiated LogiBLOX Modules" section of the "Design Methodologies - Schematic Flow" chapter

- "HDL Designs with Black Box Instantiation" section of the "Design Methodologies - HDL Flow" chapter.

The Xilinx CORE Generator tool is an easy-to-use design tool that delivers parameterizable cores, optimized for Xilinx FPGAs. The CORE Generator library includes cores as complex as DSP filters and multipliers and as simple as delay elements. You can use these cores as building blocks in order to complete your design more quickly. In Foundation 2.1i, the CORE Generator tools are integrated into the Project Manager, Schematic Editor, and HDL Editor. For details on how to instantiate cores in schematics, refer to the "Schematic Designs With Instantiated CORE Generator Cores" section of the "Design Methodologies - Schematic Flow" chapter. For details on how to instantiate cores in HDL designs, refer to the "CORE Generator COREs in a VHDL or Verilog Design" section of the "Design Methodologies - HDL Flow" chapter of the *Foundation Series 2.1i User Guide*.

For complete information about the CORE Generator tool, refer to the online manual, *CORE Generator System User Guide*.

### Accessing the Design Entry Tools

You can access all of the Design Entry tools from the Project Manager's Tools menu (Tools → Design Entry). The tools include the following:

- Schematic Editor

- State Editor

- HDL Editor

- Symbol Editor

- LogiBLOX module generator

- CORE Generator

You can also directly access the Schematic Editor, State Editor, and HDL Editor from the Design Entry phase button.

For a complete description on how to use these design entry tools, see the *Foundation Series 2.1i User Guide*.

After completing a design with design entry, the design is next implemented to a target Xilinx hardware part.

## **Using the Design Implementation Tools**

The implementation tools perform the translate map, place, route, (fit for CPLDs), and bitstream generation phases of the design flow

The Xilinx Flow Engine is the graphical interface that displays each of of these design phases. Results of these implementations are made available in reports and may be accessed through the Reports tab in the Project Manager.

The Foundation Project Manager provides menu and pushbutton access to other Xilinx tools such as the Timing Analyzer, PROM File Formatter, Floorplanner, FPGA Editor, Constraints Editor, and CPLD ChipViewer. You can access these tools through either the Tools menu or Implementation menu in the Project Manager or directly from the Project Flowchart pushbuttons.

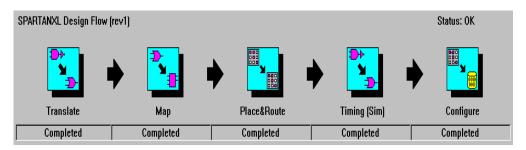

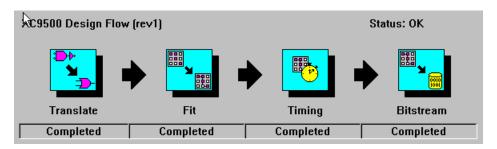

During design implemenation, the Flow Engine prominently displays the status of each phase of the design, as shown in the following figures.

Figure 2-5 Flow Engine Shows All Design Segments Completed (FPGAs)

Figure 2-6 Flow Engine Shows All Design Segments Completed (CPLDs)

#### **Translate**

The Flow Engine's first step, Translate, merges all of the input netlists. This is accomplished by running NGDBuild. For a complete description of NGDBuild, refer to the "NGDBuild" chapter of the *Development System Reference Guide*.

#### **MAP (FPGAs)**

The next step is the technology mapper. Map optimizes the gates and trims unused logic in the merged NGD netlist. This step also maps the design's logic resources; logic in the design is mapped to resources on the silicon, and a physical design rule check is performed. For more information about MAP, refer to the "MAP—The Technology Mapper" chapter in the online software manual, *Development System Reference Guide*.

#### Place and Route (FPGAs)

After the design is mapped, the Flow Engine places and routes the design. In the place stage, all logic blocks, including the configurable logic blocks (CLB) and input/output blocks (IOB) structures, are assigned to specific locations on the die.

If timing constraints have been placed on particular logic components, the placer tries to meet those constraints by moving the corresponding logic blocks closer together. In the routing stage, the logic blocks are assigned specific interconnect elements on the die. If timing constraints have been placed on particular logic components, the router tries to meet those constraints by choosing a faster interconnect. For more information about PAR, refer to the "PAR—Place and Route" chapter in the online software document, *Development System Reference Guide*.

#### **CPLD Fitter (CPLDs)**

The CPLD fitter implements designs for the XC9500 and XC9500XL devices. The fitter outputs several files: fitting report (design\_name.rpt), static timing report (design\_name.tim), guide file (design\_name.gyd, programming file (design\_name.jed), and timing simulation database (design\_name.nga).

For detailed information about implementing CPLD designs, refer to the Foundation online help.

#### Configure (FPGAs)

After place and route, the Flow Engine translates the physical implementation into a configuration file (bit) that is used to program the FPGA. The BitGen executable creates the configuration file. For more information about the BitGen executable, refer to the "BitGen" chapter in the online software document, *Development System Reference Guide*.

You can program an FPGA using the Hardware Debugger or JTAG Programmer to download a bitstream to configure a device. You can also use a bitstream as an input to the PROM File Formatter, which creates a specific configuration program for PROM use.

#### **Bitstream (CPLDs)**

At the end of a successful CPLD implementation, a .jed programming file is created. The JTAG Programmer uses this file to configure XC9500/XL CPLD devices.

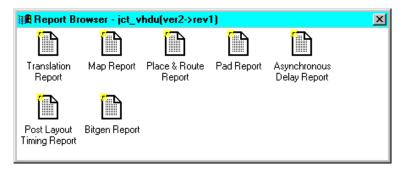

### **Interpreting the Reports**

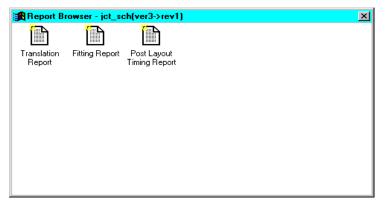

The reports generated by the implementation tools provide information on logic trimming, logic optimization, timing constraint performance, and I/O pin assignment. To access the reports, select the Reports tab from Project Manager. Double click the Implementation Report Files icon to open the Report Browser. To open a particular report, double click its icon, as shown in the "Report Browser (FPGAs)" figure.

Figure 2-7 Report Browser (FPGAs)

Figure 2-8 Report Browser (CPLDs)

#### **Translation Report**

The translation report (.bld) contains warning and error messages from the three translation processes: conversion of the EDIF or XNF style netlist to the Xilinx NGD netlist format, timing specification checks, and logical design rule checks. The report lists the following:

- Missing or untranslatable hierarchical blocks

- Invalid or incomplete timing constraints

- Output contention, loadless outputs, and sourceless inputs

#### Map Report (FPGAs)

The Map Report (.mrp) contains warning and error messages detailing logic optimization and problems in mapping logic to physical resources. The report lists the following information:

- Removed logic. Sourceless and loadless signals can cause a whole chain of logic to be removed. Each deleted element is listed with progressive indentation, so the origins of removed logic sections are easily identifiable; their deletion statements are not indented.

- Logic that has been added or expanded to optimize speed.

- The Design Summary section lists the number and percentage of used CLBs, IOBs, flip-flops, and latches. It also lists occurrences of architecturally-specific resources like global buffers and boundary scan logic.

**Note:** The Map Report can be very large. To find information, use key word searches. To quickly locate major sections, search for the string '---', because each section heading is underlined with dashes.

#### Place and Route Report (FPGAs)

The Place and Route Report (.par) contains the following information.

The overall placer score which measures the "goodness" of the

placement. Lower is better. The score is strongly dependent on

the nature of the design and the physical part that is being

targeted, so meaningful score comparisons can only be made

between iterations of the same design targeted for the same part.

- The Number of Signals Not Completely Routed should be zero for a completely implemented design. If non-zero, you may be able to improve results by using re-entrant routing or the multipass place and route flow.

- The timing summary at the end of the report details the design's delays. For information on timing constraint performance and synchronous delays, refer to the "Static Timing Analysis" section later in this chapter.

#### Pad Report (FPGAs)

The Pad Report lists the design's pinout in three ways.

- Signals are referenced according to pad numbers.

- Pad numbers are referenced according to signal names.

- PCF file constraints are listed.

#### Fitting Report (CPLDs)

The Fitting Report (*design\_name*.rpt) lists summary and detailed information about the logic and I/O pin resources used by the design, including the pinout, error and warning messages, and Boolean equations representing the implemented logic.

#### **Post Layout Timing Report**

A timing summary report shows the calculated worst-case timing for the logic paths in your design.

#### **Asynchronous Delay Report**

This report shows the 20 worst net delays within the design.

### **Selecting Options**

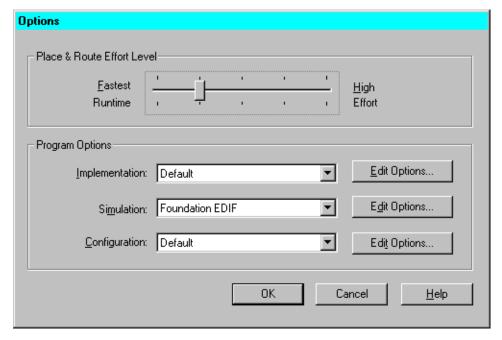

Options specify how a design is optimized, mapped, placed, routed, and configured. Options are grouped into objects called implementation, simulation, and configuration templates. Each template defines an implementation, simulation or configuration approach. For example, one implementation style could be Quick Evaluation, while another could be Timing Constraint Driven.

Figure 2-9 Flow Engine Options Dialog Box

You can have multiple templates in a project. To access the options and templates, perform the following steps.

- 1. Select the Options button in the Implement or Synthesis/Implementation dialog box.

- 2. In the Program Option portion of the Options dialog box, select the Edit Template button for Implementation, Simulation, or Configuration to access the associated template.

The default options settings provide sufficient performance for most design requirements. For information on the options, select  $\mathtt{Help} \rightarrow \mathtt{HelpTopics}$  from the Flow Engine menu.

### **Using Constraint Files**

With the design implementation tools, you can control the implementation of a design by entering constraints. There are two basic types of constraints that you can apply to a design: location constraints and timing constraints.

Location constraints are used to control the mapping and positioning of the logic elements in the target device. The most common location constraints are pad constraints. They are used to lock the pins of the design to specific I/O locations so that the pin placement is consistent from revision to revision.

Timing constraints tell the software which paths are critical, and therefore, need closer placement and faster routing. Conversely, timing constraints also tell the software which paths are not critical and, therefore, do not need closer placement or faster routing. Both the placer and the router can be timing constraint driven.

### Design, Netlist, and User Constraints

Constraints can be entered throughout the design entry and implementation processes. Constraints can be entered during the design entry phase by adding them to a schematic, specifying them through the use of a constraint entry GUI, or listing them in a user constraint file (.ucf). These three approaches differ in the following ways.

- Constraints entered directly in the input design are known simply as design constraints and are ultimately placed in the design netlist.

- If you want your constraints separated from the input design files, or if you want to modify your constraints without having to completely re-synthesize your design, you can use the Xilinx Constraints Editor or create a user constraints file design\_name.ucf.

### **Using the Xilinx Constraints Editor**

The Constraints Editor is a Graphical User Interface (GUI) that you can run after the Translate program to create new constraints in a UCF file. To access the Constraints Editor, select  $\mathtt{Tools} \rightarrow \mathtt{Implementation} \rightarrow \mathtt{Constraints}$  Editor from the Project Manager.

The Constraints Editor interface consists of a main window, three tab windows, and a number of dialog boxes. For more details, refer to the online software document, *Constraints Editor Guide*.

You can also directly enter constraints into a UCF file without using the Xilinx Constraints Editor. See the next section for details.

### **Creating a User Constraint File**

The user constraint file (.ucf) is a user-created ASCII file that holds timing and location constraints. It is read by NGDBuild during the translate process and is combined with an EDIF or XNF netlist into an NGD file. If a UCF file exists with the same name as the top-level netlist, then it will automatically be read. Otherwise, specify a file for User Constraints in the Implement Control Files Settings dialog box.

For Foundation 2.1i, if you already have an existing UCF file associated with a Revision, this UCF file is automatically copied and used as your UCF file within a new revision.

For an example of how to lock I/Os to pin locations and how to write Timespec and Timegroup constraints, refer to the "Foundation Constraints" appendix.

You can also lock pin locations within the Project Manager by selecting  $\mathtt{Tools} \to \mathtt{Implementation} \to \mathtt{Lock}$  Device Pins.

### **Static Timing Analysis**

You can perform timing analysis at several stages in the implementation flow to estimate delays. You create or generate the following.

- A post-synthesis pre-implementation display for HDL designs with the Express Time Tracker (Foundation Express only—not Base Express).

- A post-map timing report to evaluate the effects of logic delays on timing constraints.

- A post-place-and-route timing report that incorporates both block and routing delays as a final analysis of the design's timing constraints.

The Interactive Timing Analyzer tool produces detailed timing constraint, clock, and path analysis for post-map or post-place-and-route implementations.

**Note:** Static timing analysis may make the implementation processes run slower.

### Static Timing Analysis after Synthesis (HDL Only)

You can examine static timing results with the Express Time Tracker after synthesis and before implementation. You must be licensed to use Foundation Express to access the Time Tracker and the Express Constraints Editor.

- 1. After you synthesize your design, right click the optimized structure from the Versions tab.

- 2. Select View Synthesis Results.

- 3. Select the Paths tab from the Time Tracker to view estimated delays.

### Static Timing Analysis after Map (FPGAs Only)

Post-map timing reports can be very useful in evaluating timing performance. Although route delays are not accounted for, the logic delays can provide valuable information about the design.

If logic delays account for a significant portion (> 50%) of the total allowable delay of a path, the path may not be able to meet your timing requirements when routing delays are added.

Routing delays typically account for 40% to 60% of the total path delays. By identifying problem paths, you can mitigate potential problems before investing time in place and route. You can redesign the logic paths to use less levels of logic, tag the paths for specialized routing resources, move to a faster device, or allocate more time for the path.

If logic-only-delays account for much less (<35%) than the total allowable delay for a path or timing constraint, then the place-androute software can use very low placement effort levels. In these cases, reducing effort levels allow you to decrease runtimes while still meeting performance requirements.

# Static Timing Analysis after Place and Route (FPGAs Only)

Post-PAR timing reports incorporate all delays to provide a comprehensive timing summary. If a placed and routed design has met all of your timing constraints, then you can proceed by creating configuration data and downloading a device. On the other hand, if you identify problems in the timing reports, you can try fixing the problems by increasing the placer effort level, using re-entrant routing, or using multi-pass place and route. You can also redesign the logic paths to use fewer levels of logic, tag the paths for specialized routing resources, move to a faster device, or allocate more time for the paths.

For information on re-entrant routing or multi-pass place and route, see the "Re-Entrant Routing (FPGAs)" section at the end of this chapter.

### **Summary Timing Reports**

Summary reports show timing constraint performance and clock performance. Implementing a design in the Flow Engine can automatically generate summary timing reports. To create summary timing reports, perform the following steps:

- Open the Options dialog box (Implementation → Options) from the Project Manager and select Edit Options for the Implementation template.

- 2. Select the Timing Reports tab.

- 3. For a post-map report, select Produce Logic Level Timing Report. For a post-PAR report, select Produce Post Layout Timing Report.

- 4. To modify the reports to highlight path delays or paths that have failed timing constraints, select a report format.

- 5. After MAP or PAR has completed, the respective timing reports appear in the Report Browser.

### **Detailed Timing Analysis**

To perform detailed timing analysis, select Tools → Simulation/Verification → Interactive Timing Analyzer from the Project Manager menu. You can specify specific paths for analysis, discover paths not affected by timing constraints, and analyze the timing performance of the implementation based on another speed grade. For path analysis, perform the following:

- 1. Choose sources. From the Timing Analyzer menu, select Path Filters  $\rightarrow$  Custom Filters  $\rightarrow$  Select Sources.

- Choose destinations. From the Timing Analyzer menu, select

Path Filters → Custom Filters → Select

Destinations.

- To create a report, select one of the options under the Analyze menu.

To switch speed grades, select  $\mathtt{Options} \to \mathtt{Speed}$  Grade. After a new speed grade is selected, all new Timing Analyzer reports will be based on the design running with new speed grade delays. The design does not have to be re-implemented, because the new delays are read from a separate data file.

### **Creating Simulation Files**

After the design is implemented, you can perform a timing simulation to ascertain if the timing requirements and functionality of your design have been met. Timing simulation can save considerable time by reducing the time spent debugging test boards in the lab. Functional simulation can also potentially save time by uncovering design bugs before running PAR.

#### When Can Simulation Data be Created?

With the design implementation tools, you can create simulation data after each major processing step. This means that you can create functional simulation netlists after NGDBuild merges the design together in the Translate process and simulation netlists after PAR has placed and routed the design for FPGAs or the CPLD fitter has fit the design for CPLDs.

Additionally, for FPGAs, you can create simulation data after the design has been mapped. For a graphical representation of when you can conveniently simulate your design, refer to the "Foundation Overall Design Flow for FPGAs" figure and the "Foundation Overall Design Flow for CPLDs" figure.

For FPGAs, simulation data created after the design has been mapped contains timing data based on the CLB and IOB block delays, and all net (interconnect) delays are set to zero.

With post-map simulation, you can ensure that the design's current implementation will give the place and route software sufficient margin to route the design and still stay within your timing requirements.

Simulation data created after the design has been placed, but not routed, contains accurate block delays and estimates for the net delays.

You can use post-place simulation as an incremental simulation step between post-map simulation and a complete post-route timing simulation.

To simulate at any of these intermediate stages, select  $\mathtt{Tools} \rightarrow \mathtt{Simulation/Verification} \rightarrow \mathtt{Checkpoint\ Gate\ Simulation\ Control}$  from the Foundation Project Manager and choose the appropriate netlist to simulate.

### **Creating Functional Simulation Data**

For schematic and HDL designs, the functional simulation netlists are created in the Foundation design entry tools environment. Click the Simulation phase button in the Project Manager Flowchart area to invoke the Simulator and load the netlist. The Simulation phase button is shown in the following figure.

For designs that include macros whose underlying files are XNF or EDIF netlists, the design must first be "translated" in the Xilinx implementation tools in order to merge in these additional netlists. Follow these steps to translate the design and then invoke the simulator and load the functional netlist.

- Select Project → Create Version from the Project Manager.

- 2. Select  $Project \rightarrow Create Revision$  from the Project Manager.

- 3. Select Tools → Implementation → Flow Engine from the Project Manager while the new revision is selected in the Versions tab.

- 4. From within the Flow Engine, select Setup  $\rightarrow$  Stop After and then choose the Stop After Translate option.

- 5. Click OK, then select File  $\rightarrow$  Run in the Flow Engine.

- 6. After Translate is complete, go back to the Foundation Project Manager and select Tools → Simulation/Verification → Checkpoint Gate Simulation Control.

- 7. Choose the appropriate NGD file from the Revision which was just created and click OK. This invokes the simulator and loads the netlist.

For details about functional simulation, refer to the "Functional Simulation" chapter in the *Foundation Series 2.1i User Guide* and the "In-Depth Tutorial—Functional Simulation" chapter in the *Foundation 2.1i Watch Tutorial* located at http://support.xilinx.com/support/techsup/tutorials/index.htm.

For additional information about functional simulation, see the "Performing Functional Simulation" section of the "Design Methodologies - Schematic Flow" chapter in the *Foundation Series 2.1i User Guide.*

### **Creating Timing Simulation Data**

Before you perform timing simulation, ensure that you have generated a timing annotated simulation netlist. See the "Timing Simulation" section of the "Verification and Programming" chapter in the *Foundation Series 2.1i User Guide* for details and the "In-Depth Tutorial—Timing Simulation" chapter in the *Foundation 2.1i Watch Tutorial* located at http://support.xilinx.com/support/techsup/tutorials/index.htm.

- To create the timing simulation netlist, open the Options dialog box by selecting Implementation → Options, and verify that Foundation EDIF displays in the Simulation list box for Program Options.

- 2. Click ox.

- After the Implementation process is complete, return to the Foundation Project Manager, and click the timing simulation portion of the Verification phase button. This invokes the Simulator and loads the timing simulation netlist.

For additional information about timing simulation, refer to the "Verifying the Design" section of the "Design Methodologies - Schematic Flow" chapter in the *Foundation Series 2.1i User Guide*.

#### **HDL Simulation**

Foundation provides the option of adding HDL simulation capabilities to all Foundation design flows. Xilinx ships an evaluation version of an HDL simulator from MTI.

This product may be licensed for free evaluation for up to 30 days. Sale and support for this product is provided directly by the vendors.

All ModelSim product sales are handled directly by MTI and its authorized sales affiliates (email sales@model.com).

Customer support is also provided directly by MTI (email support@model.com or call the main number at (503) 641-1340)

Adding MTI's ModelSim product to the Foundation Series design environment enables simulation of VHDL, Verilog HDL or mixed-HDL designs (Verilog and VHDL). Source code debugging, functional simulation, and back-annotated timing simulation are all supported through this integrated solution. The availability of a mixed-language simulation environment offers maximum flexibility to HDL design methodologies which draw on design elements from both Verilog and VHDL.

### **Downloading a Design**

You can download an implemented FPGA design directly from your PC using the Hardware Debugger program with the XChecker cable, JTAG download cable, or MultiLINX cable. No cables are shipped with the Foundation product.

The Hardware Debugger can download a BIT file or a PROM file: MCS, EXO, or TEK file formats. A BIT file contains configuration information for an FPGA device. For more information on using the Hardware Debugger, see the *Hardware Debugger Guide*.

You can download an implemented CPLD design from your PC using the JTAG Programmer. The JTAG Programmer software is used to configure FPGAs and CPLDs and supports both the XChecker and the Parallel Cable III. This is a GUI based program. See the *JTAG Programmer Guide* for details. Also, see the *Hardware User Guide* for information about cable compatibility.

To download an implemented design, click the Programming icon in the Project Flow area.

### **Creating a PROM**

An FPGA or daisy chain of FPGAs can be configured from serial or parallel PROMs. The PROM File Formatter can create MCS, EXO, or TEK style files. The files are read by a PROM programmer that turns the image into a PROM.

A HEX file can also be used to configure an FPGA or a daisy chain of FPGAs through a microprocessor. The file is stored as a data structure in the microprocessor boot-up code.

### In-Circuit Debugging

Once a design has been downloaded to an FPGA, snapshots of internal signal states can be captured and read using the Hardware Debugger program with the XChecker cable, JTAG cable, or MultiLINX cable. You can display the signal states as waveforms in the Hardware Debugger.

This capability allows you to test and debug your design in a realtime environment as it interfaces with the other components on your board. You can also control the states of your state machines by controlling when clock edges are sent to your system clock input.

For more information on in-circuit debugging and the Hardware Debugger, see the *Hardware Debugger Guide*.

### Re-Entrant Routing (FPGAs)

The place and route software, PAR, has features that allow it to process complex designs that have tight timing requirements and/or are difficult to route. If your design is completely placed and routed but not meeting timing specifications, PAR can start from where it left off and continue re-routing the design to produce an implementation that meets your timing specifications.

As PAR is running, it continually updates the NCD file with its current placement and routing information. As long as an NCD file exists that is at least placed, PAR can used it for re-entrant routing. To initiate re-entrant routing, follow these steps.

- In the Project Manager, select Tools → Implementation → Flow Engine.

- In the Flow Engine, select the Setup → FPGA Re-entrant Route menu.

- In the Setup Re-entrant Route dialog box, select Allow Re-Entrant Route, which enables the re-entrant route options:

- Optional: If meeting timing specifications is a critical goal, then select Use Timespecs During Re-entrant Route. If meeting timing specifications is not critical, do not select this option, because timing-driven routing takes much longer to process than non-timing-driven routing.

- Optional: Select the number of re-entrant routing passes to perform. If left in "Auto," PAR will continue to perform routing iterations until either 1) it determines that it is no longer making significant progress, or 2) the design constraints have been fully met.

- Optional: Select the number of clean-up passes to run. Clean-up passes are run after the "main" routing passes are complete. Two types of clean-up routing passes can be invoked—cost-based and delay-based. The effectiveness of each type depends on the design, device, and constraints of the implementation.

- 4. Click **OK** (in the Setup Re-entrant Routing dialog box) to submit the options. This causes the Place and Route icon in the Flow Engine to show a loop back arrow and the Re-Entrant route label.

- If you are specifying timing or location constraints, you have the option to relax them to give PAR more flexibility. If you modify the UCF file, you must step backwards with the Flow Engine and re-run Translation in order to incorporate the changes.

### **Chapter 3**

### **Basic Tutorial**

This tutorial describes the features in the Foundation Series release 2.1i. The tutorial is provided in three separate types of projects:

- schematic

- Verilog

- VHDL

The chapter contains the following sections:

- "Getting Started"

- "Schematic Design Entry"

- "HDL-Based Design Entry"

- "Functional Simulation"

- "Implementation"

- "Timing Simulation"

### **Getting Started**

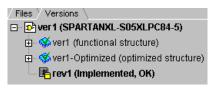

This section guides you through a typical FPGA-based design procedure using a design called "JCOUNT." The JCOUNT design targets a SpartanXL device—S05XLPC84-5; however, all of the principles and flows taught are applicable to any Xilinx device family, unless otherwise noted.

In the first part of the tutorial, you will use the Foundation design entry tools to complete the design. The design is composed of flipflops, buffers, and pads.

### **Design Description**

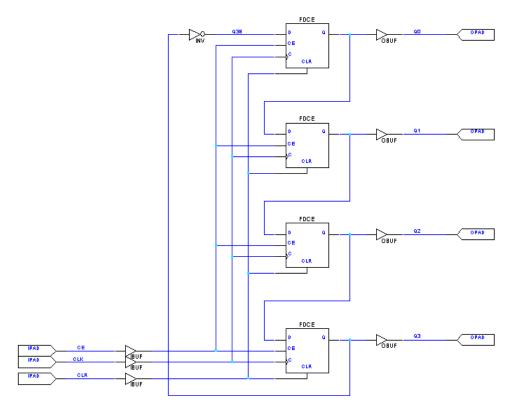

Throughout this tutorial, the design is referred to as JCOUNT.

The design begins as an unfinished design. After you complete the design, you will simulate it to verify the functionality.

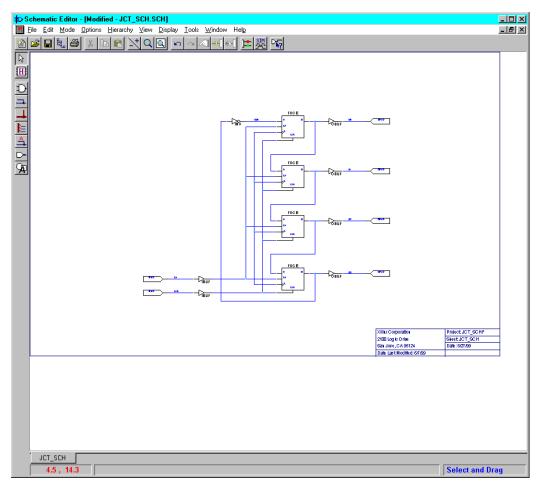

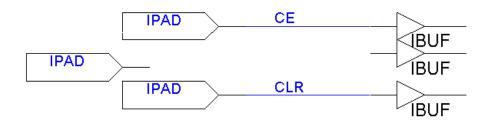

"JCOUNT" is a simple 4-bit Johnson counter. The completed schematic is shown in the following picture.

Figure 3-1 Completed JCOUNT Schematic

Controls:

CLK—input clock pulse

CE—clock enable (when set to 0, the counter freezes)

CLR—clear input (when set to 1, the counter is reset to all zeroes)

#### **Outputs:**

Q0-Q3—counter outputs

#### Operation:

The counter is triggered on the rising edge of the clock (CLK) when the clock enable signal (CE) is high. Following is the sequence of states during normal operation (that is, without clearing of the counter):

There are also two files external to the project that contain simulation results.

JCT\_F.TVE—prerouted design simulation results

JCT\_T.TVE—routed design timing simulation results

### **Starting the Project Manager**