# Synopsys Synthesis and Simulation Design Guide

**Getting Started**

**HDL Coding Hints**

Understanding High-Density Design Flow

Designing FPGAs with HDL

Simulating Your Design

Accelerate FPGA Macros with One-Hot Approach

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,777; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

# **About this Manual**

This manual provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with Hardware Description Languages (HDLs). It includes design hints for the novice HDL user, as well as for the experienced user who is designing FPGAs for the first time.

The design examples in this manual were created with Verilog and VHSIC Hardware Description Language (VHDL); compiled with the Synopsys FPGA Compiler; and targeted for XC4000, Spartan, and XC5200 devices. However, most of the design methodologies apply to other synthesis tools, as well as to other Xilinx FPGAs. Xilinx equally endorses both Verilog and VHDL. VHDL may be more difficult to learn than Verilog and usually requires more explanation.

This manual does not address certain topics that are important when creating HDL designs, such as the design environment; verification techniques; constraining in the synthesis tool; test considerations; and system verification. If you use Synopsys tools, refer to the Synopsys reference manuals and design methodology notes for additional information.

Before using this manual, you should be familiar with the operations that are common to all Xilinx software tools. These operations are covered in the *Quick Start Guide*.

## **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this

page. You can also directly access some of these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                     |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                               |  |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                            |  |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://www.support.xilinx.com/apps/appsweb.htm                                                                                                                                                  |  |  |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://www.support.xilinx.com/partinfo/databook.htm |  |  |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users<br>http://www.support.xilinx.com/xcell/xcell.htm                                                                                                                                                             |  |  |

| Tech Tips            | Latest news, design tips, and patch information on the Xilinx design environment http://www.support.xilinx.com/support/techsup/journals/index.htm                                                                                                                   |  |  |

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Getting Started," provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with HDLs. This chapter also includes installation requirements and instructions.

- Chapter 2, "HDL Coding Hints," includes HDL coding hints and design examples to help you develop an efficient coding style.

- Chapter 3, "Understanding High-Density Design Flow," provides synthesis and Xilinx implementation techniques to increase design performance and utilization.

- Chapter 4, "Designing FPGAs with HDL," includes coding techniques to help you improve synthesis results.

- Chapter 5, "Simulating Your Design," describes simulation methods for verifying the function and timing of your designs.

- Appendix A, "Accelerate FPGA Macros with One-Hot Approach," reprints an article describing one-hot encoding in detail.

## **Conventions**

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

# **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

\textbf{File} \rightarrow \textbf{Open}

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on | off}

```

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on | off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block name loc1 loc2 . . . locn;

```

## **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Contents**

| About this | Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|            | Additional Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |

| Conventio  | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

|            | TypographicalOnline Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Chapter 1  | Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |

|            | Introduction  Advantages of Using HDLs to Design FPGAs  Designing FPGAs with HDLs  Using Verilog  Using VHDL  Comparing ASICs and FPGAs  Using Synthesis Tools  Using FPGA System Features  Designing Hierarchy  Specifying Speed Requirements  Installing Design Examples and Tactical Software  Software Requirements  Workstation Requirements  Memory Requirements  Disk Space Requirements  Xilinx Internet Site  Retrieving Tactical Software and Design Examples  From Xilinx Internet FTP Site  Extracting the Files | 1-2 1-3 1-3 1-4 1-4 1-5 1-5 1-5 1-6 1-6 1-7 1-9 1-10 |

|            | Extracting .tar.Z File in UNIX Extracting .zip File in UNIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      |

|            | Extracting .zip File in MS-DOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |

|           | Directory Tree Structure  Synopsys Startup File and Library Setup  Technical Support  Xilinx World Wide Web Site  Technical and Applications Support Hotlines.  Xilinx FTP Site  XDOCS E-mail Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 1-15<br>. 1-15<br>. 1-15<br>. 1-15<br>. 1-16                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | HDL Coding Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

|           | Comparing Synthesis and Simulation Results Omit the Wait for XX ns Statement Omit theAfter XX ns or Delay Statement Use Case and If-Else Statements Order and Group Arithmetic Functions Omit Initial Values Selecting HDL Formatting Styles Selecting a Capitalization Style Verilog VHDL Using Xilinx Naming Conventions Matching File Names to Entity and Module Names Naming Identifiers, Types, and Packages Using Labels Labeling Flow Control Constructs Using Variables for Constants (VHDL Only) Using Constants to Specify Opcode Functions (VHDL) Using Parameters for Constants (Verilog Only) Using Parameters to Specify Opcode Functions (Verilog) Using Parameters to Specify Bus Size (Verilog) Using Named and Positional Association Managing Your Design Creating Readable Code Indenting Your Code Using Empty Lines Using Spaces Breaking Long Lines of Code Adding Comments Using Std_logic Data Type (VHDL only) Declaring Ports Minimizing the Use of Ports Declared as Buffers Comparing Signals and Variables (VHDL only) | 2-2<br>2-3<br>2-4<br>2-4<br>2-4<br>2-5<br>2-6<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-12<br>2-13<br>2-13<br>2-14 |

|           | Using Signals (VHDL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 2-15                                                                                                                            |

|           | Using Variables (VHDL)                                         | 2-16   |

|-----------|----------------------------------------------------------------|--------|

|           | Using Schematic Design Hints with HDL Designs                  |        |

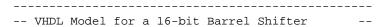

|           | Barrel Shifter Design                                          | 2-17   |

|           | 16-bit Barrel Shifter - VHDL                                   | 2-17   |

|           | 16-bit Barrel Shifter - Verilog                                | 2-20   |

|           | 16-bit Barrel Shifter with Two Levels of Multiplexers - VHDL   | 2-23   |

|           | 16-bit Barrel Shifter with Two Levels of Multiplexers - Verilo | g 2-24 |

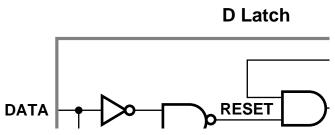

|           | Implementing Latches and Registers                             | 2-26   |

|           | D Latch Inference                                              | 2-27   |

|           | Converting a D Latch to a D Register                           | 2-28   |

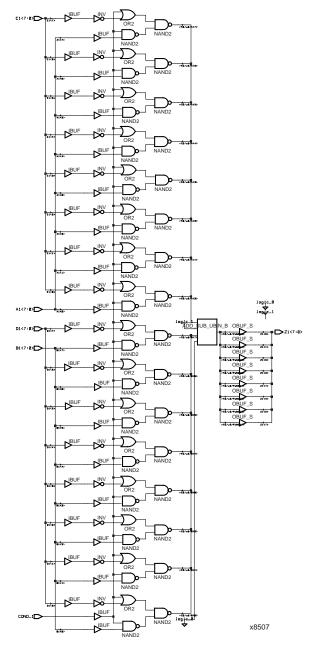

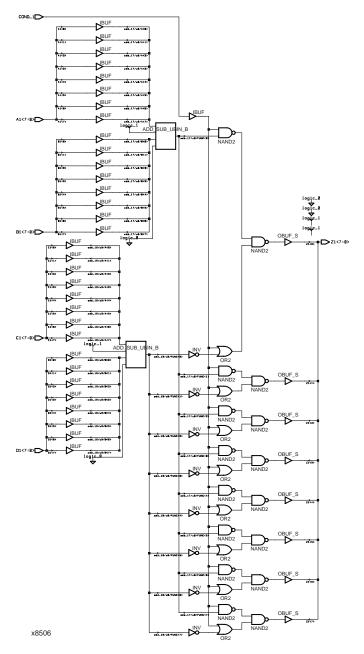

|           | Resource Sharing                                               | 2-31   |

|           | Gate Reduction                                                 | 2-38   |

|           | Preset Pin or Clear Pin                                        | 2-41   |

|           | Register Inference                                             | 2-43   |

|           | Using Clock Enable Pin                                         | 2-45   |

|           | Using If Statements                                            | 2-49   |

|           | Using Case Statements                                          |        |

|           | Using Nested If Statements                                     |        |

|           | Inefficient Use of Nested If Statement                         |        |

|           | Nested If Example Modified to Use If-Case                      |        |

|           | Comparing If Statement and Case Statement                      |        |

|           | 4-to-1 Multiplexer Design with If Construct                    |        |

|           | 4-to-1 Multiplexer Design with Case Construct                  | 2-61   |

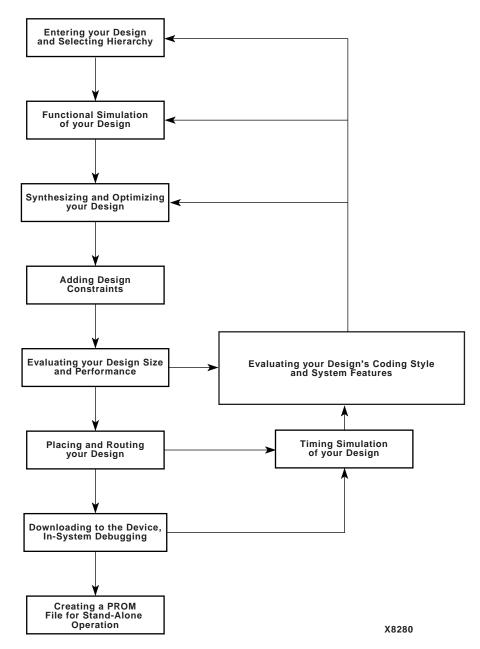

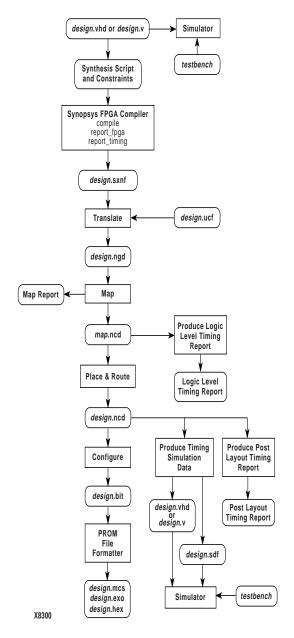

| Chapter 3 | Understanding High-Density Design Flow                         |        |

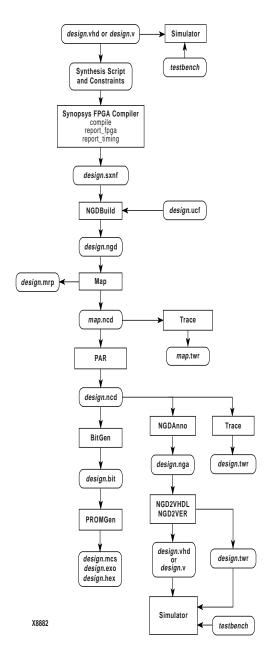

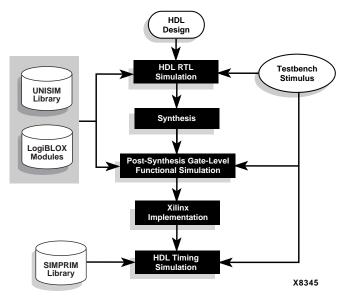

|           | Design Flow                                                    | 3-1    |

|           | Entering your Design and Selecting Hierarchy                   |        |

|           | Design Entry Recommendations                                   |        |

|           | Use RTL Code                                                   | 3-5    |

|           | Carefully Select Design Hierarchy                              | 3-5    |

|           | Functional Simulation of your Design                           | 3-5    |

|           | Synthesizing and Optimizing your Design                        | 3-6    |

|           | Creating a .synopsys_dc.setup File                             |        |

|           | Creating a Compile Run Script                                  | 3-7    |

|           | Compiling Your Design                                          | 3-7    |

|           | Modifying your Design                                          |        |

|           | Compiling Large Designs                                        |        |

|           | Saving your Compiled Design as an SXNF File                    |        |

|           | Setting Timing Constraints                                     |        |

|           | Naming and Grouping Signals Together                           |        |

|           | TNMs                                                           |        |

|           | TIMEGRPs                                                       | 3-0    |

|           | HIMEGRES                                                       | 3-3    |

|           | TPSYNC Specification                                              | 3-9     |

|-----------|-------------------------------------------------------------------|---------|

|           | Specifying Timing Constraints                                     |         |

|           | Period Constraint                                                 | 3-10    |

|           | FROM:TO Style Constraint                                          | 3-10    |

|           | Offset Constraint                                                 | 3-11    |

|           | Ignoring Timing Paths                                             | 3-11    |

|           | Controlling Signal Skew                                           | 3-12    |

|           | Timing Constraint Priority                                        | 3-12    |

|           | Evaluating Design Size and Performance                            | 3-14    |

|           | Using FPGA Compiler to Estimate Device Utilization and Perfo 3-14 | ormance |

|           | Using the Report_fpga Command                                     | 3-14    |

|           | Using the Report_timing Command                                   |         |

|           | Determining Actual Device Utilization and Pre-routed Performa     | ance 3- |

|           | Using the Design Manager to Map Your Design                       | 3-17    |

|           | Using the Command Line to Map Your Design                         |         |

|           | Evaluating your Design for Coding Style and System Features       |         |

|           | Tips for Improving Design Performance                             | 3-21    |

|           | Modifying Your Code                                               | 3-21    |

|           | Using FPGA System Features                                        | 3-21    |

|           | Placing and Routing Your Design                                   |         |

|           | Decreasing Implementation Time                                    | 3-22    |

|           | Improving Implementation Results                                  | 3-24    |

|           | Multi-Pass Place and Route Option                                 | 3-24    |

|           | Turns Engine Option (UNIX only)                                   | 3-24    |

|           | Re-entrant Routing Option                                         | 3-24    |

|           | Cost-Based Clean-up Option                                        | 3-26    |

|           | Delay-Based Clean-up Option                                       |         |

|           | Guide Option (not recommended)                                    |         |

|           | Timing Simulation of your Design                                  |         |

|           | Creating a Timing Simulation Netlist                              |         |

|           | From the Design Manager                                           |         |

|           | From the Command Line                                             |         |

|           | Downloading to the Device and In-system Debugging                 |         |

| _         | Creating a PROM File for Stand-Alone Operation                    | 3-28    |

| Chapter 4 | Designing FPGAs with HDL                                          |         |

|           | Introduction                                                      |         |

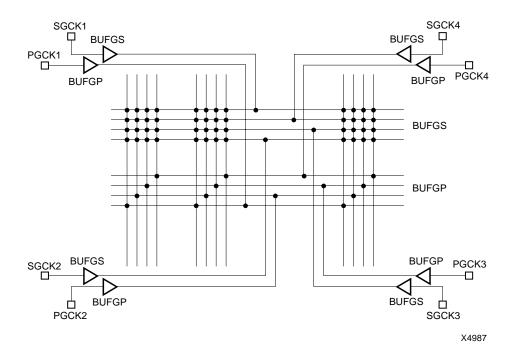

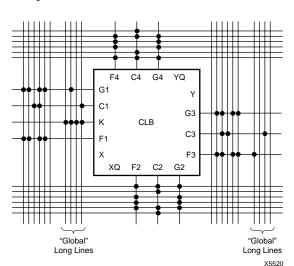

|           | Using Global Low-skew Clock Buffers                               |         |

|           | Inserting Clock BuffersInstantiating Global Clock Buffers         |         |

|           |                                                                   |         |

| Instantiating Buffers Driven from a Port            | 4-7       |

|-----------------------------------------------------|-----------|

| Instantiating Buffers Driven from Internal Logic    | 4-7       |

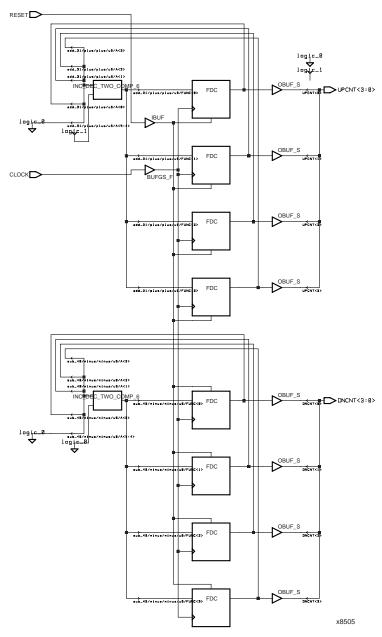

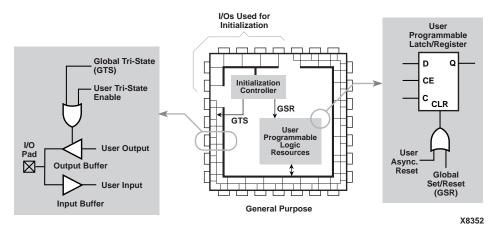

| Using Dedicated Global Set/Reset Resource           | 4-9       |

| Startup State                                       | 4-10      |

| Preset vs. Clear (XC4000, Spartan)                  | 4-11      |

| Increasing Performance with the GSR/GR Net          |           |

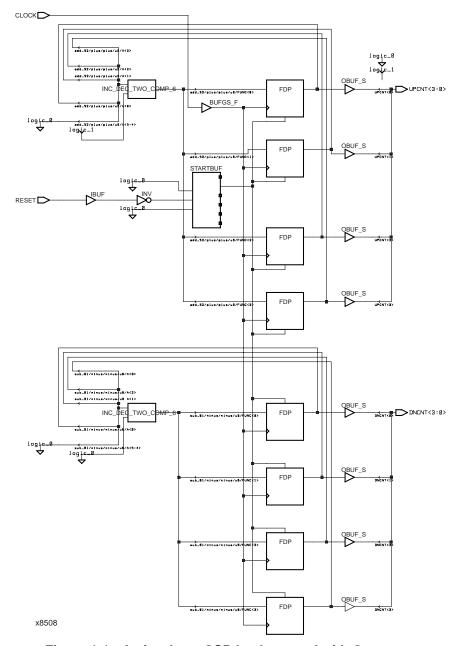

| Design Example without Dedicated GSR/GR Resource .  | 4-12      |

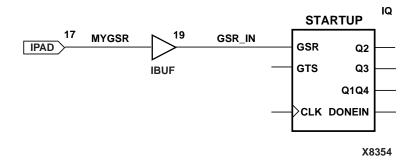

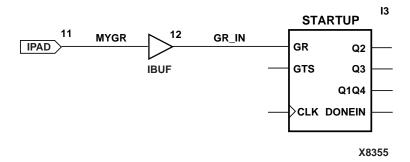

| Design Example with Dedicated GSR/GR Resource       | 4-17      |

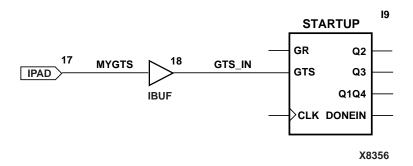

| Design Example with Active Low GSR/GR Signal        | 4-24      |

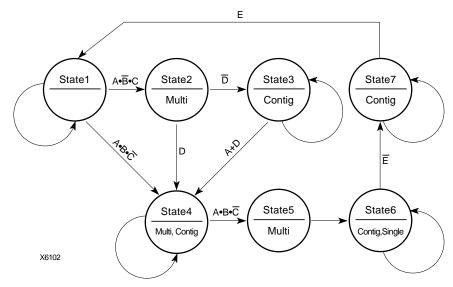

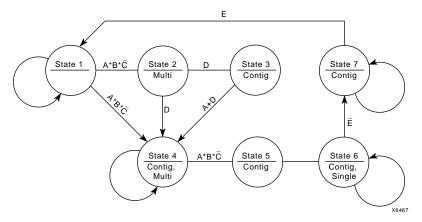

| Encoding State Machines                             | 4-26      |

| Using Binary Encoding                               | 4-27      |

| VHDL - Binary Encoded State Machine Example         | 4-28      |

| Verilog - Binary Encoded State Machine Example      | 4-30      |

| Using Enumerated Type Encoding                      |           |

| VHDL- Enumerated Type Encoded State Machine Exam    | ıple 4-34 |

| Verilog - Enumerated Type Encoded State Machine Exa | mple 4-35 |

| Using One-Hot Encoding                              |           |

| VHDL - One-hot Encoded State Machine Example        | 4-36      |

| Verilog - One-hot Encoded State Machine Example     | 4-37      |

| Summary of Encoding Styles                          | 4-39      |

| Comparing Synthesis Results for Encoding Styles     | 4-40      |

| Initializing the State Machine                      | 4-40      |

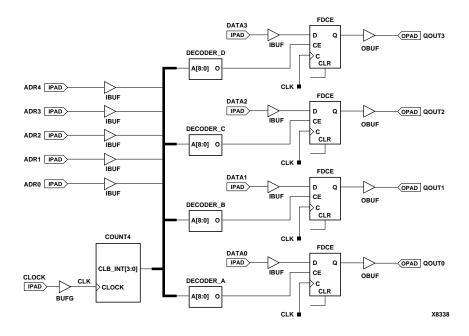

| Using Dedicated I/O Decoders                        | 4-41      |

| Instantiating LogiBLOX Modules                      | 4-46      |

| Using LogiBLOX in HDL Designs                       | 4-48      |

| Implementing Memory                                 |           |

| Implementing XC4000 and Spartan ROMs                |           |

| VHDL - RTL Description of a ROM                     |           |

| Verilog - RTL Description of a ROM                  |           |

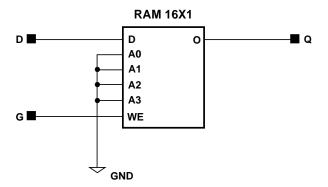

| Implementing XC4000 Family RAMs                     |           |

| VHDL - Instantiating RAM                            |           |

| Verilog - Instantiating RAM                         |           |

| Using LogiBLOX to Implement Memory                  |           |

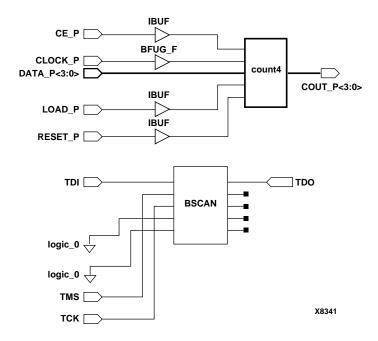

| Implementing Boundary Scan (JTAG 1149.1)            |           |

| Instantiating the Boundary Scan Symbol              |           |

| VHDL - Boundary Scan                                |           |

| Verilog - Boundary Scan                             |           |

| Implementing Logic with IOBs                        |           |

| XC4000E/EX/XLA/XL/XV and Spartan IOBs               |           |

| Inputs                                              |           |

| Outputs                                             | 4-66      |

| Slow Pate                                           | 4-67      |

|           | Pull-ups and Pull-downs                                    | . 4-67  |

|-----------|------------------------------------------------------------|---------|

|           | XC4000EX/XLA/XL/XV Output Multiplexer/2-Input Function     | า       |

|           | Generator                                                  | 4-68    |

|           | XC5200 IOBs                                                | 4-69    |

|           | Bi-directional I/O                                         | 4-70    |

|           | Inferring Bi-directional I/O                               | 4-70    |

|           | Instantiating Bi-directional I/O                           | . 4-72  |

|           | Using LogiBLOX to Create Bi-directional I/O                | . 4-75  |

|           | Specifying Pad Locations                                   | . 4-78  |

|           | Moving Registers into the IOB                              | 4-78    |

|           | Use -pr Option with Map                                    |         |

|           | Using Unbonded IOBs (XC4000E/EX/XLA/XL/XV and Spartar 4-80 | n Only) |

|           | VHDL - 4-bit Shift Register Using Unbonded I/O             | . 4-80  |

|           | Verilog - 4-bit Shift Register Using Unbonded I/O          |         |

|           | Implementing Multiplexers with Tristate Buffers            | . 4-83  |

|           | VHDL - Mux Implemented with Gates                          |         |

|           | Verilog - Mux Implemented with Gates                       |         |

|           | VHDL - Mux Implemented with BUFTs                          |         |

|           | Verilog - Mux Implemented with BUFTs                       |         |

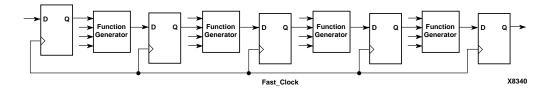

|           | Using Pipelining                                           |         |

|           | Before Pipelining                                          |         |

|           | After Pipelining                                           |         |

|           | Design Hierarchy                                           |         |

|           | Using Synopsys with Hierarchical Designs                   | . 4-90  |

| Chapter 5 | Simulating Your Design                                     |         |

|           | Introduction                                               | . 5-1   |

|           | Functional Simulation                                      | . 5-4   |

|           | Register Transfer Level (RTL)                              | . 5-4   |

|           | Post-Synthesis (Pre-NGDBuild) Gate-Level Simulation        | . 5-5   |

|           | Post-NGDBuild (Pre-Map) Gate-Level Simulation              |         |

|           | Post-Map Partial Timing (CLB and IOB Block Delays)         |         |

|           | Creating a Simulation Test Bench                           |         |

|           | XSI Pre-implementation Simulation                          |         |

|           | XSI Post-implementation Functional Simulation              |         |

|           | Post-NGDBuild Simulation                                   |         |

|           | Post-Map Simulation                                        |         |

|           | Post-PAR Simulation (timing simulation)                    |         |

|           | Timing Simulation                                          |         |

|           | Post-Route Full Timing (Block and Net Delays)              |         |

|           | Using VHDL/Verilog Libraries and Models                    | . 5-10  |

| Adhering to Industry Standards                                   | 5-11 |

|------------------------------------------------------------------|------|

| Locating Library Source Files                                    |      |

| Installing and Configuring XSI VHDL Libraries                    | 5-13 |

| Using the UniSim Library                                         | 5-15 |

| UniSim Library Structure                                         | 5-16 |

| Compiling the UniSim Library                                     | 5-17 |

| Instantiating UniSim Library Components                          | 5-18 |

| Using UniSim Libraries with XSI VHDL Designs                     |      |

| Using the LogiBLOX Library                                       |      |

| Compiling the LogiBLOX Library                                   | 5-19 |

| Instantiating LogiBLOX Modules                                   |      |

| Using the LogiCORE Library                                       |      |

| Simulating Global Signals                                        |      |

| Adapting Schematic Global Signal Methodology for VHDL            |      |

| Setting VHDL Global Set/Reset Emulation in Functional Simulation |      |

| Global Signal Considerations (VHDL)                              |      |

| GSR Network Design Cases                                         |      |

| Using VHDL Reset-On-Configuration (ROC) Cell (Case 1A            |      |

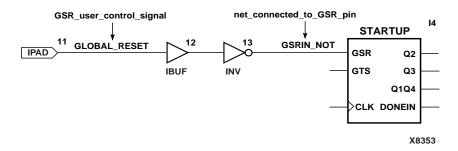

| Using ROC Cell Implementation Model (Case 1A)                    |      |

| ROC Test Bench (Case 1A)                                         | 5-29 |

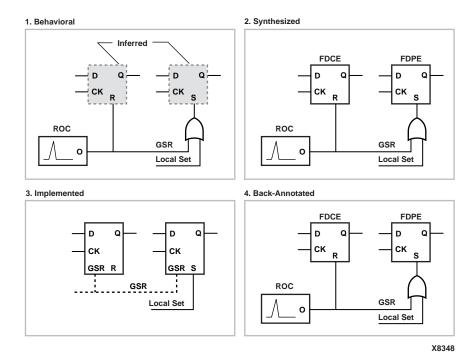

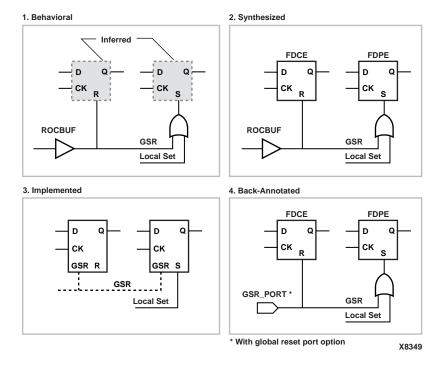

| ROC Model in Four Design Phases (Case 1A)                        | 5-30 |

| Using VHDL ROCBUF Cell (Case 1B)                                 |      |

| ROCBUF Model in Four Design Phases (Case 1B)                     |      |

| Using VHDL STARTBUF Block (Case 2A and 2B)                       |      |

| GTS Network Design Cases                                         |      |

| Using VHDL Tristate-On-Configuration (TOC)                       |      |

| VHDL TOC Cell (Case A1)                                          |      |

| TOC Cell Instantiation (Case A1)                                 |      |

| TOC Test Bench (Case A1)                                         |      |

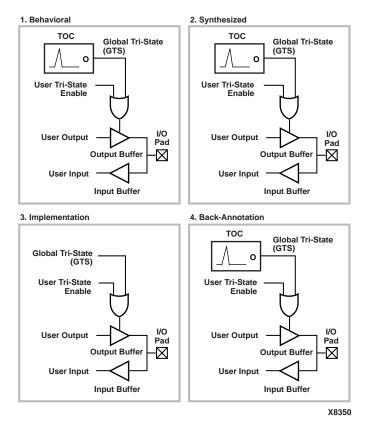

| TOC Model in Four Design Phases (Case A1)                        |      |

| Using VHDL TOCBUF (Case B1)                                      |      |

| TOCBUF Model Example (Case B1)                                   | 5-44 |

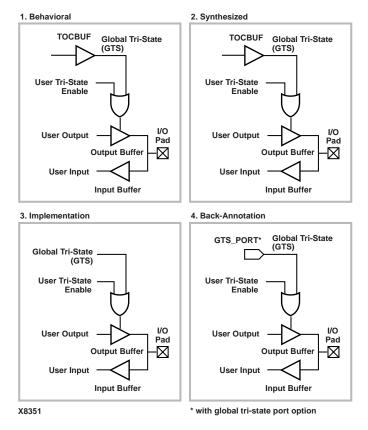

| TOCBUF Model in Four Design Phases (Case B1)                     |      |

| Using Oscillators (VHDL)                                         |      |

| VHDL Oscillator Example                                          |      |

| Oscillator Test Bench                                            |      |

| Compiling Verilog Libraries                                      |      |

| Compiling Libraries for ModelSim                                 |      |

| Setting Verilog Global Set/Reset                                 |      |

| Defining GSR in a Test Bench                                     |      |

| Designs without a STARTUP Block                                  | 5-55 |

| Example 1: XC4000E/L/X, Spartan/XL, or Virtex RTL Functional         |

|----------------------------------------------------------------------|

| Simulation (No STARTUP/STARTUP_VIRTEX Block) 5-55                    |

| Example 2: XC5200 RTL Functional Simulation (No STARTUP              |

| Block)5-58                                                           |

| Example 3: XC3000A/L, or XC3100A/L RTL Functional Simulatio          |

| (No STARTUP Block) 5-60                                              |

| Designs with a STARTUP Block 5-62                                    |

| Example 1: XC4000E/L/X and Spartan/XL Simulation with                |

| STARTUP, or Virtex with STARTUP_VIRTEX 5-64                          |

| Example 2: XC5200 Simulation with STARTUP 5-66                       |

| Example 3: XC3000A/L and XC3100A/L Designs 5-67                      |

| Setting Verilog Global Tristate (XC4000, Spartan, and XC5200 Outputs |

| Only) 5-67                                                           |

| Defining GTS in a Test Bench 5-67                                    |

| Designs without a STARTUP Block5-68                                  |

| XC4000E/L/X, Spartan/XL, Virtex and XC5200 RTL Functional            |

| Simulation (No STARTUP Block) 5-68                                   |

| Designs with a STARTUP Block 5-69                                    |

| Example 1: XC4000E/L/X, Spartan/XL, Virtex, and XC5200               |

| Simulation (With STARTUP/STARTUP_VIRTEX, GTS Pin                     |

| Connected) 5-69                                                      |

| Example 2: XC4000E/L/X, Spartan/XL, Virtex, and XC5200               |

| Simulation (With STARTUP/STARTUP_VIRTEX, GTS Pin not                 |

| connected) 5-70                                                      |

# Appendix A Accelerate FPGA Macros with One-Hot Approach

# Chapter 1

# **Getting Started**

This chapter provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with HDLs and also includes installation requirements and instructions. It includes the following.

- "Introduction"

- "Advantages of Using HDLs to Design FPGAs"

- "Designing FPGAs with HDLs"

- "Installing Design Examples and Tactical Software"

- "Synopsys Startup File and Library Setup"

- "Technical Support"

#### Introduction

Hardware Description Languages (HDLs) are used to describe the behavior and structure of system and circuit designs. This chapter includes a general overview of designing FPGAs with HDLs. System requirements and installation instructions are also provided.

To learn more about designing FPGAs with HDLs, Xilinx recommends that you enroll in the appropriate training classes offered by Xilinx and by the vendors of synthesis software. An understanding of FPGA architecture allows you to create HDL code that effectively uses FPGA system features.

Before you start to create your FPGA designs, refer to the current version of the Quick Start Guide for Xilinx Alliance Series for a description of the XSI flow; information on installing XSI; and general information on the Xilinx tools.

For the latest information on Xilinx parts and software, visit the Xilinx Web site at http://www.xilinx.com. On the Xilinx home page,

click on Service and Support, and Use the Customer Service and Support page to get answers to your technical questions. You can also use the File Download option to download the latest software patches, tutorials, design files, and documentation.

# Advantages of Using HDLs to Design FPGAs

Using HDLs to design high-density FPGAs is advantageous for the following reasons.

- Top-Down Approach for Large Projects—HDLs are used to create complex designs. The top-down approach to system design supported by HDLs is advantageous for large projects that require many designers working together. Once the overall design plan is determined, designers can work independently on separate sections of the code.

- Functional Simulation Early in the Design Flow—You can

verify the functionality of your design early in the design flow by

simulating the HDL description. Testing your design decisions

before the design is implemented at the RTL or gate level allows

you to make any necessary changes early in the design process.

- Synthesis of HDL Code to Gates—You can synthesize your hardware description to a design implemented with gates. This step decreases design time by eliminating the traditional gate-level bottleneck. Synthesis to gates also reduces the number of errors that can occur during a manual translation of a hardware description to a schematic design. Additionally, you can apply the techniques used by the synthesis tool (such as machine encoding styles or automatic I/O insertion) during the optimization of your design to the original HDL code, resulting in greater efficiency.

- Early Testing of Various Design Implementations—HDLs allow you to test different implementations of your design early in the design flow. You can then use the synthesis tool to perform the logic synthesis and optimization into gates. Additionally, Xilinx FPGAs allow you to implement your design at your computer. Since the synthesis time is short, you have more time to explore different architectural possibilities at the Register Transfer Level (RTL). You can reprogram Xilinx FPGAs to test several implementations of your design.

# **Designing FPGAs with HDLs**

If you are more familiar with schematic design entry, you may find it difficult at first to create HDL designs. You must make the transition from graphical concepts, such as block diagrams, state machines, flow diagrams and truth tables, to abstract representations of design components. You can ease this transition by not losing sight of your overall design plan as you code in HDL. To effectively use an HDL, you must understand the syntax of the language; the synthesis and simulator software; the architecture of your target device; and the implementation tools. This section gives you some design hints to help you create FPGAs with HDLs.

# **Using Verilog**

Verilog<sup>®</sup> is popular for synthesis designs because it is less verbose than traditional VHDL, and it is now being standardized by the IEEE 1364 Working Group. It was not originally intended as an input to synthesis, and many Verilog constructs are not supported by synthesis software. The Verilog examples in this manual were tested and synthesized with Synopsys<sup>®</sup> compilers. The coding strategies presented in the remaining chapters of this manual can help you create HDL descriptions that can be synthesized.

## **Using VHDL**

VHSIC Hardware Description Language (VHDL) is a hardware description language for designing Integrated Circuits (ICs). It was not originally intended as an input to synthesis, and many VHDL constructs are not supported by synthesis software. However, the high level of abstraction of VHDL makes it easy to describe the system-level components and test benches that are not synthesized. In addition, the various synthesis tools use different subsets of the VHDL language. The examples in this manual are written specifically for Synopsys compilers. The coding strategies presented in the remaining chapters of this manual can help you create HDL descriptions that can be synthesized.

# Comparing ASICs and FPGAs

Methods used to design ASICs do not always apply to FPGA designs. ASICs have more gate and routing resources than FPGAs. Since

ASICs have a large number of available resources, you can easily create inefficient code that results in a large number of gates. When designing FPGAs, you *must* create efficient code.

## **Using Synthesis Tools**

Synthesis tools, such as the Synopsys FPGA Compiler, have special optimization algorithms for Xilinx FPGAs. Constraints and compiling options perform differently depending on the target device. There are some commands and constraints that do not apply to FPGAs and, if used, may adversely impact your results. You should understand how your synthesis tool processes designs before creating FPGA designs.

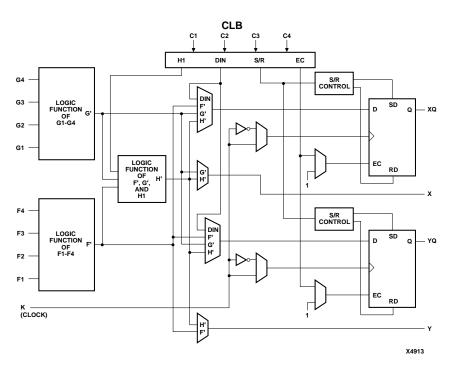

# **Using FPGA System Features**

You can improve device performance and area utilization by creating HDL code that uses FPGA system features, such as global reset, wide I/O decoders, and memory. FPGA system features are described in this manual.

# **Designing Hierarchy**

Current HDL design methods are specifically written for ASIC designs. You can use some of these ASIC design methods when designing FPGAs; however, certain techniques may unnecessarily increase the number of gates or CLB levels.

Design hierarchy is important in the implementation of an FPGA and also during incremental or interactive changes. Some synthesizers maintain the hierarchical boundaries unless you group modules together. Modules should have registered outputs so their boundaries are not an impediment to optimization. Otherwise, modules should be as large as possible within the limitations of your synthesis tool. The "5,000 gates per module" rule is no longer valid, and can interfere with optimization. Check with Synopsys for the current recommendations for preferred module size. As a last resort, use the grouping commands of your synthesizer. The size and content of the modules influence synthesis results and design implementation. This manual describes how to create effective design hierarchy.

# **Specifying Speed Requirements**

To meet timing requirements, you should understand how to set timing constraints in both the synthesis and placement/routing tools.

# **Installing Design Examples and Tactical Software**

The information in this section supplements information in the *Synopsys Interface Guide*. Also, read and follow the instructions in the latest version of the *Quick Start Guide for Xilinx Alliance Series*, as well as the current version of the *Alliance Series Install and Release Document*.

This manual includes numerous HDL design examples created with VHDL and Verilog. VHDL is more comprehensive than Verilog, and you many need to spend more time learning how to apply VHDL constructs to synthesis.

# **Software Requirements**

To synthesize, simulate, and implement the design examples in this manual, you should have the following versions of software (see the following table) installed on your system.

**Note:** The design examples in this manual were compiled with Synopsys 1997.08 and Xilinx M1 software; however, all programs, scripts, and design examples are compatible with the versions in the following table.

| Table ' | 1_1 | Software | Versions |

|---------|-----|----------|----------|

|         |     |          |          |

| Software                        | Version                      |  |

|---------------------------------|------------------------------|--|

| Xilinx Synopsys Interface (XSI) | Alliance Series 2.1 or later |  |

| Xilinx Development System       | Alliance Series 2.1 or later |  |

| Synopsys FPGA Compiler          | 1997.08 or later             |  |

# **Workstation Requirements**

The current release of the software supports the following workstation architectures and operating systems.

- Solaris<sup>®</sup> 2.5 and 2.51

- Ultra Sparc (or equivalent)

- HP-UX HP 10.2

- HP715 (or equivalent)

#### **Memory Requirements**

The values provided in the following table are for typical designs, and include loading the operating system. Additional memory may be required for certain "boundary-case" or unusual designs, as well as for the concurrent operation of other applications (for example, Design Compiler or Verilog XL). Xilinx recommends compiling XC4000EX/ XL designs on the Ultra Sparc, HP715, or equivalent workstations. Although 64 MB of RAM and 64 MB of swap space are required to compile XC4000EX designs, Xilinx recommends that you use 128 MB of RAM and 128 MB of swap space for more efficient processing of your XC4000EX designs.

Table 1-2 Memory Requirements for Workstations

| Xilinx Device                                                                                                                                      | RAM    | Swap Space      |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|

| XC3000A/L<br>XC3100A/L<br>XC4000E/L<br>XC4028EX through XC4036EX<br>XC4002XL through XC4028XL<br>XCS (Spartan)<br>XC5200<br>XC9500 (small devices) | 64 MB  | 64 MB – 128 MB  |

| XC4036XL through XC4062XL<br>XC9500 (large devices)                                                                                                | 128 MB | 128 MB – 256 MB |

| XC4085XL<br>XC40125XV                                                                                                                              | 256 MB | 256 MB – 512 MB |

## **Disk Space Requirements**

Before you install the programs and files, verify that your system meets the requirements listed in the following tables for the applicable options. The disk space requirements listed are approximations and may not exactly match the actual numbers. To significantly reduce the amount of disk space needed, install only the components and documentation that you will actually use.

**Note:** Refer to the *Alliance Series Install and Release Document* for more information on disk space requirements.

Table 1-3 Disk Space Requirements

| Software Component                                                                     | Data                               | Sol    | HP      |

|----------------------------------------------------------------------------------------|------------------------------------|--------|---------|

| Xilinx Core Technology                                                                 | ~12 MB                             | ~98 MB | ~108 MB |

| Xilinx Device Data Files (All devices) <sup>a</sup>                                    | ~195 MB                            | ~26 MB | ~26 MB  |

| Documentation: Online Help Documentation Browser Xilinx Tutorial Files Xilinx Userware | ~30 MB total  ~17 MB  ~1 MB  ~4 MB | ~10 MB | ~10 MB  |

a. The memory requirements specified are for the installation of all Xilinx devices. You can significantly reduce the amount of disk space required by installing only the files for the devices you want to target.

Table 1-4 XSI Interface Disk Space Requirements

| Software Component | Disk Space (MB) |

|--------------------|-----------------|

| XSI Interface      | ~105 MB         |

#### **Xilinx Internet Site**

To download the programs and files from the Xilinx Internet Site, you must meet the disk requirements listed in the following table.

Table 1-5 Internet Files

| Directory/Location             | Description                                                                                       | Compressed File                                                                      | Directory<br>Size |

|--------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------|

| M1_VHDL_source <sup>a</sup>    | All VHDL source code<br>only (no scripts, compila-<br>tion, or implementation<br>files)           | m1_vhdl_src.tar.Z<br>(size: 60 KB)<br>or<br>m1_vhdl_src.zip<br>(size: 68 KB)         | 271 KB            |

| M1_Verilog_source <sup>a</sup> | All Verilog source code<br>only (no scripts, compila-<br>tion, or implementation<br>files)        | m1_verilog_src.tar.Z<br>(size: 57 KB)<br>or<br>m1_verilog_src.zip<br>(size: 64 KB)   | 256 KB            |

| M1_HDL_source <sup>a</sup>     | All VHDL and Verilog<br>source code only (no<br>scripts, compilation, or<br>implementation files) | m1_hdl_src.tar.Z<br>(size: 110 KB)<br>or<br>m1_hdl_src.zip<br>(size: 129 KB)         | 497 KB            |

| M1_XSI_VHDL <sup>b</sup>       | All VHDL source code,<br>scripts, compilation, and<br>implementation files                        | m1_xsi_vhdl.tar.Z<br>(size: 6.3 MB)<br>or<br>m1_xsi_vhdl.zip<br>(size: 4.3 MB)       | 16.1 MB           |

| M1_XSI_Verilog <sup>b</sup>    | All Verilog source code,<br>scripts, compilation, and<br>implementation files                     | m1_xsi_verilog.tar.Z<br>(size: 5.3 MB)<br>or<br>m1_xsi_verilog.zip<br>(size: 3.6 MB) | 14.9 MB           |

| M1_XSI_HDL <sup>b</sup>        | All VHDL and Verilog<br>source code, scripts,<br>compilation, and imple-<br>mentation files       | m1_xsi_hdl.tar.Z<br>(size: 11.5 MB)<br>or<br>m1_xsi_hdl.zip<br>(size: 7.9 MB)        | 30.8 MB           |

a. These files are located at ftp://ftp.xilinx.com/pub/applications/3rd party

b. These files are located at ftp://ftp.xilinx.com/pub/swhelp/synopsys, as well as at ftp://ftp.xilinx.com/pub/applications/3rd party

The M1\_VHDL\_source and M1\_Verilog\_source directories are smaller than the M1\_XSI\_VHDL and M1\_XSI\_Verilog directories because they contain only the VHDL or Verilog source code, and not the compilation and implementation files. If you want to access both Verilog and VHDL examples from this book, you can download either the M1\_HDL\_source or M1\_HDL\_XSI directory.

# **Retrieving Tactical Software and Design Examples**

You can retrieve the HDL design examples from the Xilinx Internet Site. If you need assistance retrieving the files, use the information listed in the "Technical Support" section of this chapter to contact the Xilinx Hotline.

You must install the retrieved files on the same system as the Xilinx software and the Synopsys tools. However, do not install the files into the directory with the current release of the software since they may get overwritten during the installation of the next version of the software.

#### From Xilinx Internet FTP Site

You can retrieve the programs and files from the Xilinx Internet FTP (File Transfer Protocol) site. Alternatively, if you are not familiar with FTP, you can retrieve the files by going to the Xilinx Web site (http://www.xilinx.com), clicking on Service and Support, and using the File Download option. To access the Xilinx FTP Site, you must either have an internet-capable FTP utility available on your machine or a Web browser that has FTP. To use FTP, your machine must be connected to the Internet and you must have permission to use FTP on remote sites. If you need more information on this procedure, contact your system administrator.

To retrieve the programs and files from the Xilinx FTP site, use the following procedure.

- 1. Go to the directory on your local machine where you want to download the files, as follows.

- cd directory

- 2. Invoke the FTP utility or your Web browser that provides FTP.

- 3. Connect to the Xilinx FTP site, ftp.xilinx.com as follows.

ftp>open ftp.xilinx.com

or

Enter the following URL.

```

ftp://ftp.xilinx.com

```

4. Log into a guest account if the FTP utility or Web browser does not perform this automatically. This account gives you download privileges.

```

Name (machine:user-name): anonymous

Guest login ok, send your complete e-mail

address as the password.

Password: your_email_address

```

5. Go to the following directory.

```

ftp>cd pub/swhelp/synopsys

```

6. If you are using an FTP utility, make sure you are in binary mode.

```

ftp>bin

```

7. Retrieve the appropriate design files as follows.

```

ftp> get design_files.tar.Z

or

ftp> get design_files.zip

or

```

Select the appropriate file and select a destination directory on your local machine.

8. Extract the files as described in the next section.

# **Extracting the Files**

You must install the retrieved files on the same system as the current release of the Xilinx software and the Synopsys tools. However, do not install the files in the directory with the current software since they may get overwritten during the installation of the next version of the software. The files are stored in the UNIX $^{\text{TM}}$  standard tar and compress form, as well as in the PC $^{\text{TM}}$  standard zip form. To extract the files, use one of the following procedures.

**Note:** If the following procedures do not work on your system, consult your system administrator for help on extracting the files.

#### **Extracting .tar.Z File in UNIX**

- 1. Go to the directory where you downloaded the files:

- cd downloaded files

- 2. Uncompress the files:

```

uncompress design.tar.Z

```

3. Extract the files:

```

tar xvf design.tar

```

#### **Extracting .zip File in UNIX**

- 1. Go to the directory where you downloaded the files:

- cd downloaded files

- 2. Uncompress the files:

```

unzip design.zip

```

#### **Extracting .zip File in MS-DOS**

- 1. Go to the directory where you downloaded the files:

- cd downloaded files

- 2. Uncompress the files:

```

pkunzip -d design.zip

```

# **Directory Tree Structure**

After you have completed the installation, you should have the following directory tree structure:

```

/Barrel

/Barrel_Org

/Bidir_LogiBLOX

/VHDL

/Verilog

/Bidir_infer

/VHDL

/Verilog

/Bidir_instantiate

/VHDL

/Verilog

/Bnd_scan_4k

/VHDL

/Verilog

/Bnd_scan_5k

/VHDL

/Verilog

/Case_vs_if

/VHDL

/Case_ex

/If_ex

/Verilog

/Case_ex

/If_ex

/Clock_enable

/VHDL

/Verilog

/Clock_mux

/VHDL

/Verilog

/Constants

/VHDL

/Verilog

/Parameter1

/Parameter2

/D_latch

/VHDL

/Verilog

/D_register

/VHDL

/Verilog

/FF_example

/VHDL

/Verilog

/GR_5K

```

```

/VHDL

/Active_low_GR

/No_GR

/Use_GR

/Verilog

/Active_low_GR

/No_GR

/Use_GR

/GSR

/VHDL

/Active_low_GSR

/No_GSR

/Use_GSR

/Verilog

/Active_low_GSR

/No_GSR

/Use_GSR

/Gate_clock

/VHDL

/Gate_clock

/Gate_clock2

/Verilog

/Gate_clock

/Gate_clock2

/Gate_reduce

/VHDL

/Synopsys_dw

/Xilinx_dw

/Verilog

/Synopsys_dw

/Xilinx_dw

/IO_Decoder

/VHDL

/IO_Decoder

/Verilog

/LogiBLOX_DP_RAM

/VHDL

/Verilog

/LogiBLOX_SR

/VHDL

/Verilog

/Mux_vs_3state

/VHDL

/Mux_gate

/Mux_gate16

```

```

/Mux_tbuf

/Mux_tbuf16

/Verilog

/Mux_gate

/Mux_gate16

/Mux_tbuf

/Mux_tbuf16

/Nested_if

/VHDL

/If_case

/Nested_if

/Verilog

/If_case

/Nested_if

/OMUX_example

/VHDL

/Verilog

/RAM_primitive

/VHDL

/Verilog

/ROM_RTL

/VHDL

/Verilog

/Res_sharing

/VHDL

/Res_no_share

/Res_sharing

/Res_xdw_no_share

/Res_xdw_share

/Verilog

/Res_no_share

/Res_sharing

/Res_xdw_no_share

/Res_xdw_share1

/Set_and_Reset

/VHDL

/Verilog

/Sig_vs_Var

/VHDL

/Xor_Sig

/Xor_Var

/State_Machine

/VHDL

/Binary

/Enum

```

```

/One_Hot

/Verilog

/Binary

/Enum

/One_Hot

/Unbonded_IO

/VHDL

/Verilog

```

# Synopsys Startup File and Library Setup

Follow the procedures in the "Getting Started" chapter of the *Synopsys Interface Guide* for instructions on modifying the Synopsys startup file for the FPGA Compiler.

# **Technical Support**

You can contact Xilinx for additional information and assistance in the following ways.

#### Xilinx World Wide Web Site

http://www.xilinx.com

Click on the Service and Support option on the Xilinx Home Page. Use the Customer Service and Support page to get answers to your technical questions. You can use the Answers Search option to search the Answers database, file download area, application notes, XCELL journals, data sheets, and expert journals.

## **Technical and Applications Support Hotlines**

The telephone hotlines give you direct access to Xilinx Application Engineers worldwide. You can also e-mail or fax your technical questions to the same locations.

Table 1-6 Technical Support

| Location      | Telephone      | Electronic Mail     | Facsimile (Fax) |

|---------------|----------------|---------------------|-----------------|

| North America | 1-800-255-7778 | hotline@xilinx.com  | 1-408-879-4442  |

| Japan         | 81-3-3297-9163 | jhotline@xilinx.com | 81-3-3297-0067  |

| France        | 33-1-3463-0100 | frhelp@xilinx.com   | 33-1-3463-0959  |

**Table 1-6 Technical Support**

| Location                   | Telephone       | Electronic Mail   | Facsimile (Fax) |

|----------------------------|-----------------|-------------------|-----------------|

| Germany                    | 49-89-9915-4930 | dlhelp@xilinx.com | 49-89-904-4748  |

| United Kingdom             | 44-1932-820821  | ukhelp@xilinx.com | 44-1932-828522  |

| Corporate Switch-<br>board | 1-408-559-7778  |                   |                 |

**Note:** When e-mailing or faxing inquiries, provide your complete name, company name, and phone number. Also, provide a complete problem description including your design entry software and design stage.

#### Xilinx FTP Site

ftp.xilinx.com

The FTP site provides online access to automated tutorials, design examples, online documents, utilities, and published patches.

#### **XDOCS E-mail Server**

xdocs@xilinx.com

Include the word "help" in the subject header. This e-mail service provides access to the Customer Service and Support page from the Xilinx World Wide Web Site. On the Xilinx home page, click on Service and Support, and Use the Customer Service and Support page to get answers to your technical questions.

# **HDL Coding Hints**

This chapter contains HDL coding hints and design examples to help you develop an efficient coding style. It includes the following topics.

- "Comparing Synthesis and Simulation Results"

- "Selecting HDL Formatting Styles"

- "Using Schematic Design Hints with HDL Designs"

HDLs contain many complex constructs that are difficult to understand at first. Also, the methods and examples included in HDL manuals do not always apply to the design of FPGAs. If you currently use HDLs to design ASICs, your established coding style may unnecessarily increase the number of gates or CLB levels in FPGA designs.

HDL synthesis tools implement logic based on the coding style of your design. To learn how to efficiently code with HDLs, you can attend training classes, read reference and methodology notes, and refer to synthesis guidelines and templates available from Xilinx and the synthesis vendors. When coding your designs, remember that HDLs are mainly hardware description languages. You should try to find a balance between the quality of the end hardware results and the speed of simulation.

The coding hints and examples included in this chapter are not intended to teach you every aspect of VHDL or Verilog, but they should help you develop an efficient coding style.

# **Comparing Synthesis and Simulation Results**

VHDL and Verilog are hardware description and simulation languages that were not originally intended as input to synthesis. Therefore, many hardware description and simulation constructs are not supported by synthesis tools. In addition, the various synthesis tools use different subsets of VHDL and Verilog. VHDL and Verilog semantics are well defined for design simulation. The synthesis tools must adhere to these semantics to ensure that designs simulate the same way before and after synthesis. Follow the guidelines presented below to create code that simulates the same way before and after synthesis.

#### Omit the Wait for XX ns Statement

Do not use the Wait for XX ns statement in your code. XX specifies the number of nanoseconds that must pass before a condition is executed. This statement does not synthesize to a component. In designs that include this statement, the functionality of the simulated design does not match the functionality of the synthesized design. VHDL and Verilog examples of the Wait for XX ns statement are:

VHDL

```

wait for XX ns;

```

Verilog

#XX;

## Omit the ... After XX ns or Delay Statement

Do not use the ...After XX ns statement in your VHDL code or the Delay assignment in your Verilog code. Examples of these statements are:

VHDL

```

(O <=0 after XX ns)

```

Verilog

```

assign #XX Q=0;

```

XX specifies the number of nanoseconds that must pass before a condition is executed. This statement is usually ignored by the synthesis tool. In this case, the functionality of the simulated design does not match the functionality of the synthesized design.

### **Use Case and If-Else Statements**

You can use If-Else statements, Case statements, or other conditional code to create state machines or other conditional logic. These statements implement the functions differently, however, the simulated designs are identical. The If-Else statement specifies priority-encoded logic and the Case statement specifies parallel behavior. The If-Else statement can, in some cases, result in a slower circuit overall. Refer to the "Comparing If Statement and Case Statement" section of this chapter for more information.

# Order and Group Arithmetic Functions

The ordering and grouping of arithmetic functions can influence design performance. For example, the following two VHDL statements are not necessarily equivalent:

```

ADD <= A1 + A2 + A3 + A4;

ADD <= (A1 + A2) + (A3 + A4);

```

Additionally, for Verilog, the following two statements are not necessarily equivalent:

```

ADD = A1 + A2 + A3 + A4;

ADD = (A1 + A2) + (A3 + A4);

```

The first statement cascades three adders in series. The second statement creates two adders in parallel: A1 + A2 and A3 + A4. In the second statement, the two additions are evaluated in parallel and the results are combined with a third adder. RTL simulation results are the same for both statements, however, the second statement results in a faster circuit after synthesis (depending on the bit width of the input signals).

Although the second statement generally results in a faster circuit, in some cases, you may want to use the first statement. For example, if the A4 signal reaches the adder later than the other signals, the first statement produces a faster implementation because the cascaded structure creates fewer logic levels for A4. This structure allows A4 to catch up to the other signals. In this case, A1 is the fastest signal followed by A2 and A3; A4 is the slowest signal.

The FPGA Compiler can balance or restructure the arithmetic operator tree if timing constraints require it. However, Xilinx recommends that you code your design for your selected structure.

#### **Omit Initial Values**

Do not assign signals and variables initial values because initial values are ignored by most synthesis tools. The functionality of the simulated design may not match the functionality of the synthesized design.

For example, do not use initialization statements like the following VHDL and Verilog statements:

VHDL

```

variable SUM:INTEGER:=0;

```

Verilog

wire SUM=1'b0;

# **Selecting HDL Formatting Styles**

Because HDL designs are often created by design teams, Xilinx recommends that you agree on a style for your code at the beginning of your project. An established coding style allows you to read and understand code written by your fellow team members. Also, inefficient coding styles can adversely impact synthesis and simulation, which can result in slow circuits. Additionally, because portions of existing HDL designs are often used in new designs, you should follow coding standards that are understood by the majority of HDL designers. This section of the manual provides a list of suggested coding styles that you should establish before you begin your designs.

# **Selecting a Capitalization Style**

Select a capitalization style for your code. Xilinx recommends using a consistent style (lower or upper case) for entity or module names in FPGA designs.

### **Verilog**

For Verilog, the following style is recommended.

- Use lower case letters for entity or module names and reserved words

- Use upper case letters for the following.

- Keywords that are not entity names or reserved words

- Variable, signal, instance, and module names

- Labels

- · Libraries, packages, and data types

- Instantiated cells from the XSI Library

- For the names of standard or vendor packages, the style used by the vendor or uppercase letters are used, as shown for IEEE in the following example:

```

library IEEE;

use IEEE.std_logic_1164.all;

signal SIG: UNSIGNED (5 downto 0);

```

#### **VHDL**

For VHDL, use lower case for all language constructs from the IEEE-STD 1076. Any inputs defined by you should be upper case. For example, use upper case for the names of signals, instances, components, architectures, processes, entities, variables, configurations, libraries, functions, packages, data types, and sub-types.

# **Using Xilinx Naming Conventions**

Use the Xilinx naming conventions listed in this section for naming signals, variables, and instances that are translated into nets, buses, and symbols.

Note: Most synthesis tools convert illegal characters to legal ones.

- User-defined names can contain A-Z, a-z, \$, \_, -, <, and >. A "/" is also valid, however, it is not recommended since it is used as a hierarchy separator

- · Names must contain at least one non-numeric character

- Names cannot be more than 256 characters long

The following FPGA resource names are reserved and should not be used to name nets or components.

Components (Comps), Configurable Logic Blocks (CLBs), Input/ Output Blocks (IOBs), basic elements (bels), clock buffers (BUFGs), tristate buffers (BUFTs), oscillators (OSC), CCLK, DP, GND, VCC, and RST

- CLB names such as AA, AB, and R1C2

- Primitive names such as TD0, BSCAN, M0, M1, M2, or STARTUP

- Do not use pin names such as P1 and A4 for component names

- Do not use pad names such as PAD1 for component names

# **Matching File Names to Entity and Module Names**

The VHDL or Verilog source code file name should match the designated name of the entity (VHDL) or module (Verilog) specified in your design file. This is less confusing and generally makes it easier to create a script file for the compilation of your design. Xilinx also recommends that if your design contains more than one entity or module, it should be contained in a separate file with the appropriate file name. It is also a good idea to use the same name as your top-level design file for your Synopsys script file with either a .scr or .script file extension.

# Naming Identifiers, Types, and Packages

You can use long (256 characters maximum) identifier names with underscores and embedded punctuation in your code. Use meaningful names for signals and variables, such as CONTROL\_REGISTER. Use meaningful names when defining VHDL types and packages as shown in the following examples:

```

type LOCATION_TYPE is ...;

package STRING_IO_PKG is

```

## **Using Labels**

Use labels to group logic. Label all processes, functions, and procedures as shown in the following examples.

VHDL

```

ASYNC_FF: process (CLK,RST)

```

Verilog

```

always @ (posedge CLK or posedge RST) begin: ASYNC_FF

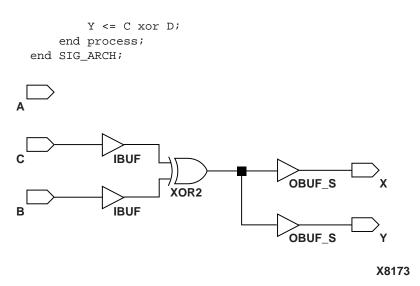

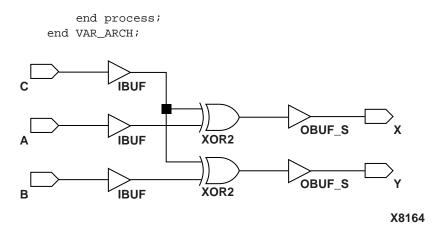

```