# *Floorplanner Guide*

Introduction

**Design Flow**

**Getting Started**

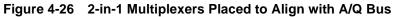

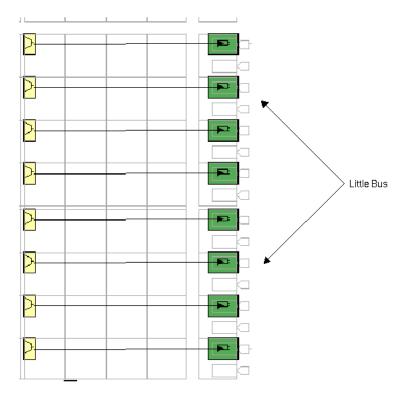

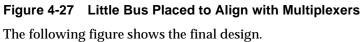

Using the Floorplanner

Menu Command Reference

Glossary

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479;

5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

Xilinx Development System

### **About This Manual**

This manual describes the Xilinx<sup>®</sup> Floorplanner, a graphically based tool that allows you to interactively and automatically place logic symbols from a hierarchical design into a Xilinx target FPGA.

Before using this manual, you should be familiar with the operations that are common to all Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Quick Start Guide*. Other publications you can consult for related information are the *Development System Reference Guide* and the *HDL Synthesis for FPGAs Design Guide*.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/index.htm              |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                           |

| Resource       | Description/URL                                                                                                                                                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Book      | Pages from <i>The Programmable Logic Data Book</i> , which describe device-<br>specific information on Xilinx device characteristics, including read-<br>back, boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                         |

| Tech Tips      | Latest news, design tips, and patch information on the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                         |

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," provides an overview of the Floorplanner interface, including basic operations, input and output files, and supported FPGA architectures.

- Chapter 2, "Design Flow," describes four distinct work flows in which you can use the Floorplanner.

- Chapter 3, "Getting Started," describes how to invoke the Floorplanner from the Design Manager or as a standalone tool, and provides more details about the interface.

- Chapter 4, "Using the Floorplanner," describes several important floorplanning procedures for implementing high-density designs in the XC4000 and Spartan FPGA families.

- Chapter 5, "Menu Command Reference," describes the Floorplanner menu commands and associated dialog boxes and toolbar buttons.

- Appendix A, "Glossary," defines the terms used in this manual.

### Conventions

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

### Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: -100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

Courier bold also indicates commands that you select from a menu.

$\texttt{File} \rightarrow \texttt{Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

edif2ngd [option\_name] design\_name

• Braces "{}" enclose a list of items from which you must choose one or more.

lowpwr ={on | off}

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on | off}

```

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2 . . . locn;

#### **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

### Contents

#### **About This Manual**

| Additional Resources | . i  |

|----------------------|------|

| Manual Contents      | . ii |

#### Conventions

| Typographical   | . iii |

|-----------------|-------|

| Online Document | . iv  |

#### Chapter 1 Introduction

| What is the Floorplanner?1    | -1 |

|-------------------------------|----|

| Floorplanner Icon 1           |    |

|                               | -3 |

| Floorplanning Prerequisites 1 | -3 |

| Features of the Floorplanner1 | -4 |

| Supported Architectures1      | -4 |

| New Files 1                   | -4 |

| nput Files 1                  | -5 |

| Dutput Files 1                | -6 |

#### Chapter 2 Design Flow

| Place and Route, then Floorplan 2        | 2-1 |

|------------------------------------------|-----|

| Floorplanning Prior to Place and Route 2 | 2-3 |

| Iterative Floorplanning                  | 2-4 |

| Incremental Design Changes 2             | 2-5 |

#### Chapter 3 Getting Started

| Running the Floorplanner | 3-1 |

|--------------------------|-----|

| Design Manager Interface | 3-2 |

| Command Line Interface   | 3-4 |

| Floorplanner Interface   | 3-5 |

| •                        |     |

| Status Bar                                        |

|---------------------------------------------------|

| Mouse 3-6                                         |

|                                                   |

| Keyboard                                          |

| Dialog Boxes                                      |

| The Floorplanner Windows                          |

| Primary Window                                    |

| Design Hierarchy Window 3-10                      |

| Hierarchy Display 3-11                            |

| Selecting Logic                                   |

| Expanding and Collapsing Hierarchical Groups 3-12 |

| Hierarchical Group Annotation                     |

| Symbol Annotation                                 |

| Design Nets Window 3-15                           |

| Floorplan Window 3-15                             |

| Resource Graphics 3-17                            |

| Placement Window 3-18                             |

| Closing the Current Design                        |

| Exiting the Floorplanner 3-19                     |

#### Chapter 4 Using the Floorplanner

| Opening a File                          | 4-3  |

|-----------------------------------------|------|

| Saving a File                           | 4-3  |

| Using Colors                            | 4-4  |

| In the Design Hierarchy Window          | 4-4  |

| In the Floorplan Window                 | 4-4  |

| Distinguishing Logic                    | 4-5  |

| Floorplanning Logic                     |      |

| Floorplanning Designs that Contain RPMs |      |

| Creating Groups                         | 4-9  |

| Manual Grouping                         |      |

| Automatic Grouping                      |      |

| Using Area Constraints                  |      |

| Flattening and Building the Hierarchy   | 4-12 |

| How to Flatten the Hierarchy            | 4-12 |

| How to Rebuild the Hierarchy            | 4-13 |

| Walking Through the Design              | 4-13 |

| Finding Logic                           |      |

| Finding Nets                            |      |

| Displaying the Ratsnest                 |      |

| Using the Ratsnest                      |      |

| Viewing Selected Nets in the Ratsnest   |      |

| Analyzing PAR Placement                           | 4-15 |

|---------------------------------------------------|------|

| Analyzing PAR Placement for Timing Constraints    | 4-18 |

| From the Design Manager                           | 4-18 |

| Using Find and Ratsnest to Find Critical Nets     | 4-19 |

| Finding Logic Connected to Nets                   | 4-22 |

| Displaying Resources and Logic                    | 4-22 |

| Performing Detailed Manual Placement              | 4-24 |

| Checking the Floorplan                            | 4-25 |

| Aligning Symbols                                  |      |

| Working with Patterns                             |      |

| Creating a Pattern                                | 4-30 |

| Using a Pattern                                   | 4-30 |

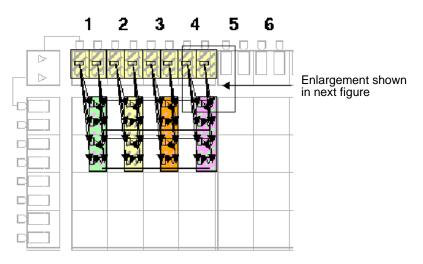

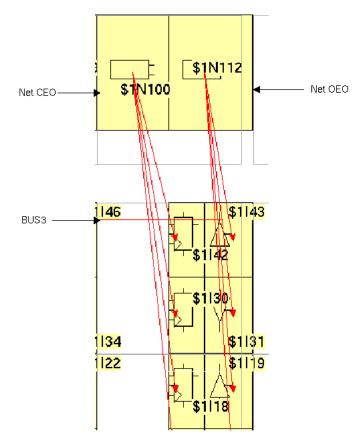

| How to Interleave Buses                           |      |

| Design Example                                    | 4-31 |

| Iterative Floorplanning                           | 4-40 |

| Floorplanning Incremental Schematic Changes       |      |

| Design Example                                    | 4-41 |

| Making Small Modifications to Automatic Placement | 4-45 |

| Lock Down I/Os from Automatically Placed Design   | 4-45 |

| Getting Started With an Unfamiliar Design         | 4-46 |

| Creating Hierarchy at a Higher Level              | 4-46 |

| Creating Subgroups                                | 4-47 |

| Floorplanning the New Hierarchy                   | 4-48 |

|                                                   |      |

#### Chapter 5 Menu Command Reference

| Menus 5                                  | j-1         |

|------------------------------------------|-------------|

| File Menu 5                              | j-2         |

| Edit Menu5                               | j-2         |

| View Menu5                               | j-3         |

| Hierarchy Menu5                          | -4          |

| Floorplan Menu                           | 5-5         |

| Window Menu 5                            | j-6         |

| Help Menu5                               | j-6         |

| Commands                                 | <b>5-</b> 6 |

| About Floorplanner (Help Menu)5          | j-6         |

| Allow (Floorplan Menu) 5                 | j-7         |

| Arrange Icons (Window Menu)5             | j-7         |

| Assign Area Constraint (Floorplan Menu)5 | j-7         |

| Bring Area To Front (Floorplan Menu)     | 5-7         |

| Capture Pattern (Floorplan Menu) 5       | j-7         |

| Cascade (Window Menu)5                   | 5-8         |

| Check Floorplan (Floorplan Menu) 5       | j-8         |

| Close (File Menu)                         | 5-9  |

|-------------------------------------------|------|

| Collapse (Hierarchy Menu)                 | 5-9  |

| Colors (Edit Menu)                        |      |

| Congestion (View Menu)                    | 5-11 |

| Constrain from Placement (Floorplan Menu) |      |

| Distribute Options (Floorplan Menu)       |      |

| Exit (File Menu)                          | 5-13 |

| Expand (Hierarchy Menu)                   |      |

| Find (Edit Menu)                          |      |

| Flatten Groups (Hierarchy Menu)           | 5-17 |

| Flip Horizontal (Floorplan Menu)          |      |

| Flip Vertical (Floorplan Menu)            | 5-17 |

| Floorplan (View Menu)                     |      |

| Goto Next (View Menu)                     | 5-18 |

| Goto Previous (View Menu)                 |      |

| Group (Hierarchy Menu)                    | 5-18 |

| Group By (Hierarchy Menu)                 | 5-19 |

| Help Topics (Help Menu)                   | 5-21 |

| Hierarchy (View Menu)                     |      |

| Impose Pattern (Floorplan Menu)           | 5-21 |

| Move (Hierarchy Menu)                     |      |

| Nets (View Menu)                          | 5-22 |

| New (File Menu)                           |      |

| New Window (Window Menu)                  | 5-24 |

| Open (File Menu)                          | 5-24 |

| Options (View Menu)                       |      |

| Resources                                 |      |

| Logic                                     | 5-27 |

| Ratsnest                                  | 5-28 |

| Congestion                                | 5-30 |

| Placement (View Menu)                     | 5-32 |

| Print (File Menu)                         | 5-32 |

| Print Preview (File Menu)                 | 5-32 |

| Print Setup (File Menu)                   | 5-33 |

| Prohibit (Floorplan Menu)                 | 5-33 |

| Properties (Edit Menu)                    |      |

| Push Area To Back (Floorplan Menu)        |      |

| Rebuild (Hierarchy Menu)                  | 5-34 |

| Refresh (View Menu)                       |      |

| Remove (Floorplan Menu)                   |      |

| Remove All (Floorplan Menu)               |      |

| Remove Groups (Hierarchy Menu)            | 5-35 |

| Poplace All with Discoment (Electrolan Manu) |   | E 2E |

|----------------------------------------------|---|------|

| Replace All with Placement (Floorplan Menu)  |   |      |

| Save (File Menu)                             |   |      |

| Save As (File Menu)                          |   |      |

| Select Loads (Edit Menu)                     |   |      |

| Select Sources (Edit Menu)                   |   |      |

| Sort (Hierarchy Menu)                        |   |      |

| Split (Window Menu)                          |   |      |

| Status Bar (View Menu)                       |   |      |

| Tile Compare (Window Menu)                   |   |      |

| Tile Normal (Window Menu)                    |   |      |

| Toolbar (View Menu)                          |   |      |

| Undo (Edit Menu)                             |   |      |

| Unselect All (Edit Menu)                     |   |      |

| Update (File Menu)                           |   |      |

| Zoom (View Menu)                             | է | 5-40 |

| Full View                                    | { | 5-41 |

| In                                           | { | 5-41 |

| Out                                          | { | 5-41 |

| То Вох                                       | { | 5-41 |

| To Selected                                  | { | 5-41 |

| Toolbar                                      | { | 5-41 |

| Assign Area Constraint                       | { | 5-41 |

| Distribution Direction                       |   |      |

| Distribute Up                                |   |      |

| Distribute Down                              |   |      |

| Distribute Left                              |   |      |

| Distribute Right                             |   |      |

| Distribute One at a Time                     |   |      |

| Capture Pattern                              |   |      |

| Impose Pattern                               |   |      |

| Flip Vertical                                |   |      |

| Flip Horizontal                              |   |      |

| Labels                                       |   |      |

| Ratsnest                                     |   |      |

| Resources                                    |   |      |

| Zoom In                                      |   |      |

| Zoom Out                                     |   |      |

| Zoom Full View                               |   |      |

| Zoom To Area                                 |   |      |

| Zoom To Selected                             |   |      |

|                                              |   | 5-40 |

#### Appendix A Glossary

| BEL                      | A-1 |

|--------------------------|-----|

| block                    | A-1 |

| BUFT                     | A-1 |

| CLB                      | A-1 |

| critical path            | A-1 |

| design hierarchy         | A-1 |

| DFF                      | A-2 |

| guide file               | A-2 |

| HDL                      | A-2 |

| IOB (input/output block) | A-2 |

| I/O blocks               |     |

| I/O pads                 | A-2 |

| logic icon               |     |

| logic icons in transit   | A-2 |

| longlines                | A-3 |

| map                      | A-3 |

| menu bar                 | A-3 |

| net                      | A-3 |

| optimize                 | A-3 |

| pad                      | A-3 |

| place                    | A-3 |

| ratsnest                 | A-4 |

| resource graphics        | A-4 |

| route                    | A-4 |

| router                   | A-4 |

| schematic                | A-4 |

| selecting logic          | A-4 |

| status bar               | A-4 |

| tristate buffer          |     |

| toolbar                  | A-5 |

# **Chapter 1**

### Introduction

This chapter describes the graphical interface and the important features and capabilities of the Xilinx Floorplanner. It contains the following sections.

- "What is the Floorplanner?" is a general introduction to the Floorplanner tool.

- "Floorplanner Icon" shows the icon that appears in the Design Manager window.

- "Why Floorplan?" explains how the Floorplanner can help you improve the performance and density of your design.

- "Floorplanning Prerequisites" explains the necessary requirements for successful floorplanning.

- "Features of the Floorplanner" lists the features provided by the Floorplanner.

- "Supported Architectures" lists the Xilinx device families that Floorplanner supports.

- "New Files" describes the two new file types that Floorplanner uses.

- "Input Files" lists the files that Floorplanner uses as input.

- "Output Files" lists the files that Floorplanner generates.

### What is the Floorplanner?

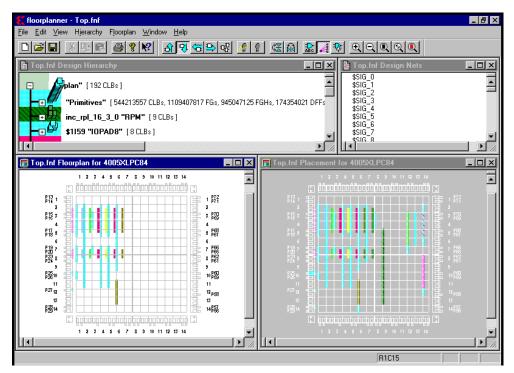

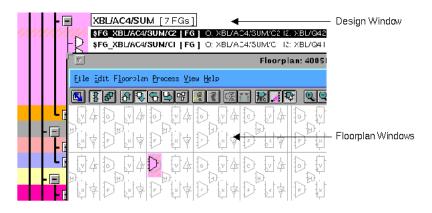

The Floorplanner is a graphical placement tool that gives you control over placing a design into a target FPGA using a "drag and drop" paradigm with the mouse pointer. The Floorplanner displays a hierarchical representation of the design in the Design Hierarchy window using hierarchy structure lines and colors to distinguish the different hierarchical levels. The Floorplan window displays the floorplan of the target device into which you place logic from the hierarchy. The following figure shows the windows on the PC version.

#### Figure 1-1 Floorplanner Window

Logic symbols represent each level of hierarchy in the Design Hierarchy window. You can modify that hierarchy in the Floorplanner without changing the original design.

You use the mouse to select the logic from the Design Hierarchy window and place it in the FPGA represented in the Floorplan window.

Alternatively, you can invoke the Floorplanner after running the automatic place and route tools to view and possibly improve the results of the automatic implementation.

#### **Floorplanner Icon**

The Floorplanner can be started by clicking the Floorplanner icon in the Design Manager screen. The following figure shows the icon.

### Why Floorplan?

Floorplanning is an optional methodology to help you improve performance and density of a fully, automatically placed and routed design. Floorplanning is particularly useful on structured designs and data path logic. With the Floorplanner, you see where to place logic in the floorplan for optimal results, placing data paths exactly at the desired location on the die.

With the Floorplanner, you can floorplan your design prior to or after running PAR. In an iterative design flow, you floorplan and place and route, interactively. You can modify the logic placement in the Floorplan window as often as necessary to achieve your design goals. You can save the iterations of your floorplanned design to use later as a constraints file for MAP.

### **Floorplanning Prerequisites**

The Floorplanner is specifically intended to assist those users who require some degree of handcrafting for their designs. You must understand both the details of the device architectures and how floorplanning can be used to refine a design. Successful floorplanning is very much an iterative process and it can take time to develop a floorplan that outperforms an "automatically" processed design.

Because of the nature of the Floorplanner's interaction with the automatic MAP and PAR tools, several prerequisites are necessary in order to floorplan your design successfully.

- Detailed knowledge of the specifics of the target architecture and part

- Detailed knowledge of the specifics of the design being implemented

- A design that lends itself to floorplanning

- A willingness to iterate a floorplan to achieve the desired results

- Realistic performance and density goals

### Features of the Floorplanner

The Floorplanner provides an easy-to-use graphical interface that offers the following features.

- Interacts at a high level of the design hierarchy, as well as with low-level elements such as I/Os, function generators, tristate buffers, flip-flops, and RAM/ROM

- Captures and imposes complex patterns, which is useful for repetitive logic structures such as interleaved buses

- Automatically distributes logic into columns or rows

- Uses dynamic rubberbanding to show the ratsnest connections

- Finds logic or nets by name or connectivity

- Permits design hierarchy rearrangement to simplify floorplanning

- Groups logic by connectivity or function

- Identifies placement problems in the Floorplan window

- Provides online help

### **Supported Architectures**

The Floorplanner supports all Xilinx architectures in the Spartan<sup>TM</sup>, Spartan<sup>2TM</sup>, Virtex<sup>TM</sup>, and XC4000<sup>TM</sup> device families.

### **New Files**

There are two new file types that Floorplanner uses that you need to be aware of.

• FNF

The Floorplanner Netlist File (FNF) is the floorplanner's database. Its core function is to retain a record of all the (physical) constraints entered in the Floorplan window. If the FNF is generated using a placed NCD file, the placement information is also recorded in the FNF for use by the placement window. Additionally, the FNF file retains user-created groups from the Design Hierarchy window. When design modifications are made (modified source files (.ngd) or new placement (.ncd)), the existing FNF file can be updated with the new information using the File  $\rightarrow$ Update command. This allows for design iterations without the loss of your previous work. Any design archive should include the FNF file to allow subsequent design or constraint modifications.

• MFP

The Mapper Floorplan (MFP) file links the Floorplanner to the M1 flow by directing MAP behavior. It is the intervention into the map phase of the flow that permits you to floorplan at the BEL (Basic Element) level. The MFP is a subset (physical constraints only) of the FNF file. The FNF2MFP utility is automatically invoked when saving a floorplan, which produces an MFP file from the relevant information in the FNF file. The MFP file name always has the same root name as the FNF file, for example, design.fnf and design.mfp.

**Note:** The Floorplanner cannot read MFP files. You must save the FNF file in order to archive floorplan information.

#### **Input Files**

The Floorplanner can read in the following input files.

• NCD

This file is generated by either MAP or PAR. It is used by the Floorplanner during the File  $\rightarrow$  New command to generate the physical design for the FNF file.

• NGD

This file is generated by NGDBuild. It is used by the Floorplanner during the **File**  $\rightarrow$  **New** command to correlate the physical design to the logical design when creating the FNF file.

• FNF

A previous version of this file, which was generated by a File  $\rightarrow$  **Save** in the Floorplanner, can optionally be used in the creation of a new FNF file. If used, it helps retain design constraints between floorplanning iterations.

### **Output Files**

The Floorplanner generates the following output files.

• FNF

The FNF file is the Floorplanner's database. It can be saved by using the File  $\rightarrow$  Save command.

• MFP

This file is generated when the FNF file is saved in the Floorplanner. It is used as an input to MAP to transfer physical constraints from the Floorplanner back to the automatic implementation tools.

## **Chapter 2**

### **Design Flow**

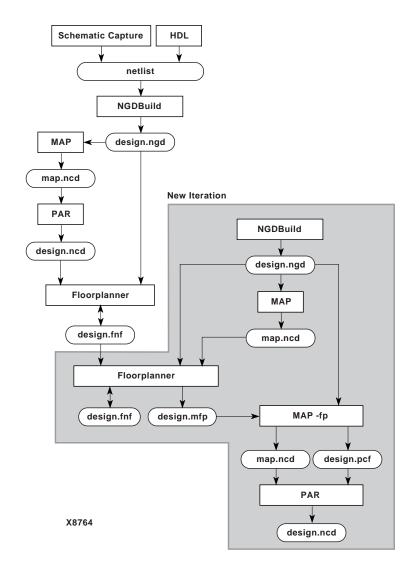

This chapter describes the four different design flows that you can use with the Floorplanner to implement your design in a Xilinx FPGA. Accompanying each design flow is a comprehensive flow chart that indicates the programs you use, the input files required, and output files that are generated. The four design flows are described in the following sections.

- "Place and Route, then Floorplan"

- "Floorplanning Prior to Place and Route"

- "Iterative Floorplanning"

- "Incremental Design Changes"

Xilinx strongly recommends that you read the *HDL Synthesis and Simulation Design Guide* before attempting to floorplan your HDL designs. This document explains HDL-specific design issues and understanding them will make floorplanning your HDL designs easier and more effective.

The design flows in this chapter present a general picture of where the Floorplanner fits in the Xilinx design flow; in some instances the descriptions of the design flows are more relevant to designers using schematic capture tools than to designers using HDL.

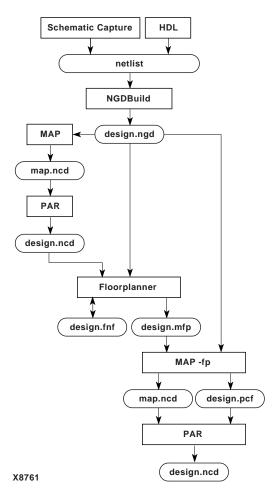

#### Place and Route, then Floorplan

The first design flow describes how to Floorplan your design after placing and routing your design. This is the preferred methodology because it allows you to view both the physical constraints for the design and the results of the automatic placement.

You enter your design using either a schematic capture tool or HDL. Next, run MAP and PAR to place and route the design in a target FPGA device. To view and improve performance of the automatic implementation, create a new Floorplan Netlist File within the Floorplanner from the placed and routed NCD file. Next, use the Floorplanner to constrain critical paths or adjust the automatic placement. Finally, run MAP and PAR with the newly generated MFP file to obtain the results of the floorplanned design. Refer to the design flow in the following figure.

Figure 2-1 PAR Before Floorplanning Design Flow

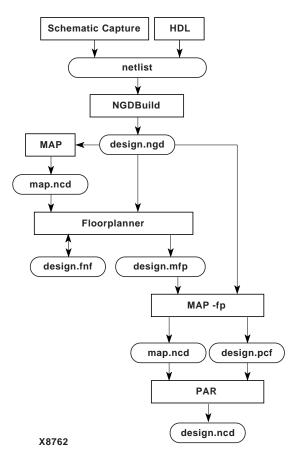

### **Floorplanning Prior to Place and Route**

The second design flow is to floorplan your design before using PAR to place and route it. In this flow, you enter your design using either a schematic capture tool or HDL. Run MAP on the design to create a physical design file (NCD). Use the Floorplanner to define placement constraints by manually placing selected logic into the resources of the target device. Next, run MAP and PAR to fit the design into the target FPGA using the Floorplan constraints. Refer to the design flow in the following figure.

Figure 2-2 Floorplan First Design Flow

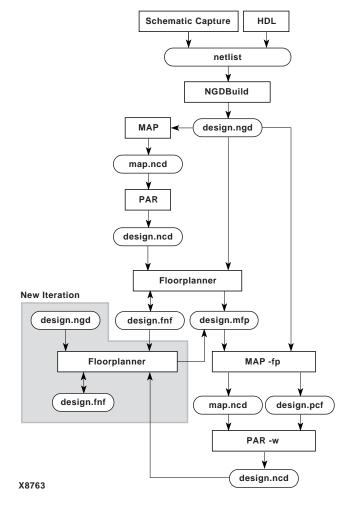

### **Iterative Floorplanning**

In the third design flow, iterative floorplanning, you enter the design using a schematic capture tool or HDL. Next, use the Floorplanner to constrain portions of the design. Then, run MAP and PAR to map, place, and route the design into the target FPGA.

Based on the results of the automatic place and route tools, you can modify the currently floorplanned logic or select another portion of the design to constrain. Run MAP and PAR again with the new floorplanner constraints.

In addition, you can make small modifications to the placement done by PAR. After copying the placement over to the Floorplan window, you can make small changes to the Floorplan and save the new fullyconstrained FNF file. The Floorplan  $\rightarrow$  Constrain All From Placement command fully constrains the placement of the design and can be used to fix small performance problems, such as a few design elements that are not optimally placed.

Repeat this Floorplanner-to-MAP and PAR loop until you have achieved your performance goals for the design. Refer to the design flow in the following figure.

Note that the same NGD file is used throughout the design flow.

Figure 2-3 Iterative Floorplanning Design Flow

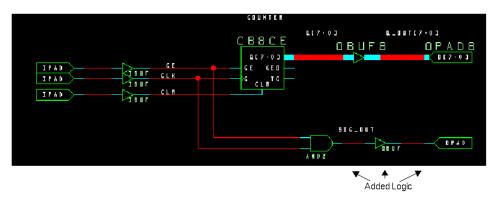

### **Incremental Design Changes**

In the fourth design flow, you make changes to the schematic of a design that has been previously implemented in an FPGA, with or without floorplanning. You must re-implement the design into the target device while making only minimal changes to the previous implementation. These changes could be one or more of the following.

- Adding logic

- Removing logic

- Changing existing logic

If you used the Floorplanner to floorplan the original design, use the Floorplanner now to correlate the logic in that design with the new changes, and adjust the constraints information accordingly. Next, use the Floorplanner's output MFP file to constrain the design during the mapping and placement phases of the implementation.

For HDL users, incremental design change is more complex with HDL designs because the synthesis tools change symbol names whenever the compilation method changes. When applying a previous revision of your Floorplan to the newly synthesized revision, it may be necessary to constrain some or all of the previously floorplanned elements.

Figure 2-4 Incremental Design Change Design Flow

# **Chapter 3**

### **Getting Started**

This chapter describes how to start and exit the Floorplanner. It also explains the basic elements and operations of the Floorplanner graphical user interface (GUI).

This chapter contains the following sections.

- "Running the Floorplanner" describes how to start the Floorplanner.

- "Design Manager Interface" explains how to use the Design Manager to run the Floorplanner.

- "Command Line Interface" shows the syntax to use when running NGDBuild, MAP, and PAR in a command window as part of the floorplanning process.

- "Floorplanner Interface" describes the GUI.

- "Closing the Current Design" describes how to close the current design without exiting the Floorplanner.

- "Exiting the Floorplanner" explains how to save your current design and exit the Floorplanner.

#### **Running the Floorplanner**

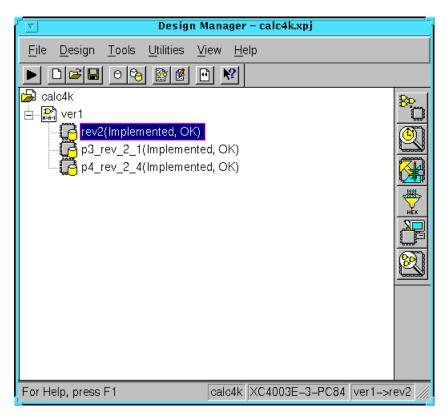

You can run the Floorplanner on a PC running Windows NT<sup>®</sup> or on an HP-based or Solaris<sup>®</sup>-based workstation under Design Manager. You can input either an HDL-based design or a schematic-based design.

The following figure shows the Design Manager screen from which you can launch the Floorplanner.

Figure 3-1 Design Manager Window

You can invoke the Floorplanner from the Design Manager in either of two ways.

- Select the  $Tools \rightarrow Floorplanner$  command.

- Click the Floorplanner toolbox button. In the above figure, this is the third button from the top in the toolbar on the right.

Refer to the *Design Manager/Flow Engine Guide* for more details about invoking the Floorplanner from the Design Manager.

### **Design Manager Interface**

When you use the Floorplanner, an MFP file is generated that contains mapping information. You can instruct the Design Manager to use this file as a guide for mapping an implementation revision. To guide a design with Floorplan files, do the following steps. For more information, refer to the *Design Manager/Flow Engine Guide*.

- 1. In the Design Manager project view, select an implementation revision that has been mapped and modified using the Floor-planner.

- 2. Select  $\texttt{Design} \rightarrow \texttt{Set Floorplan File(s)}$  from the Design Manager.

The Set Floorplan File(s) dialog box appears, as shown below.

| Set Floorplan File(s)     |        |              |  |

|---------------------------|--------|--------------|--|

| <u>F</u> loorplan Design: | None   | 4            |  |

| ОК                        | Cancel | <u>H</u> elp |  |

Figure 3-2 Set Floorplan File(s) Dialog Box

- 3. Select a Floorplan guide design from the Floorplan Design dropdown list.

- Select an existing implementation revision.

- Select None if you do not want to guide the design.

- Select **Project Clipboard** to guide from the implementation revision copied to your project clipboard. If no data exists in the clipboard or if you want to copy new data to the clipboard, use the **Copy floorplan data to project clipboard** option in the Implement dialog box. This dialog box is described in the "Menu Commands" chapter of the *Design Manager/Flow Engine Guide*.

- Select Custom to guide from any mapped file in your file system, including designs not generated from within the Design Manager. This option invokes the Custom dialog box, shown in the following figure. You can specify an FNF file for the Floorplanning File field and an MFP file for the Floorplanned Guide File field.

|                                  | Custom    |        |

|----------------------------------|-----------|--------|

| <u>F</u> loorplanning File:      | []        | Browse |

| Floorplanned <u>G</u> uide File: |           | Browse |

|                                  | OK Cancel | Help   |

Figure 3-3 Custom Dialog Box (Floorplan Files)

4. The Flow Engine uses the selected file to guide the implementation.

#### **Command Line Interface**

As shown in the "PAR Before Floorplanning Design Flow" figure of the "Design Flow" chapter, the Floorplanner interacts with the core flow by first reading in an NCD file generated by MAP or PAR and an NGD file generated by NGDBuild. Next, it writes out a *design*.fnf file, which stores all the Floorplanning information, and a *design*.mfp file, which is used during MAP to apply the floorplanning constraints. Following is a sample of the command lines that would be used in a typical floorplanning session.

ngdbuild -p part\_name design\_name

map -p part\_name -o map.ncd design\_name.ngd design\_name.pcf

par map.ncd design\_name.ncd design\_name.pcf

Use File  $\rightarrow$  New in the Floorplanner to create a floorplan and File  $\rightarrow$  Save to create *design\_name*.fnf and *design\_name*.mfp.

map -fp design\_name.mfp -p part\_name -o map.ncd

design\_name.ngd design\_name.pcf

**Note:** The **-fp** option above tells MAP to use the Floorplanner constraints in the MFP file.

par map.ncd design\_name.ncd design\_name.pcf

#### **Floorplanner Interface**

The Floorplanner GUI consists of the primary Floorplanner window and four sub-windows labelled Floorplan, Placement, Design Hierarchy, and Design Nets. The primary window also contains pulldown menus, dialog boxes, a toolbar, and a status bar.

The Floorplanner GUI uses pull-down menus that contain all of the necessary commands to floorplan your design. The menus contain many commands that open dialog boxes, from which you can select various options and parameters for that command. Other commands act immediately on the selected logic.

Window operations, such as opening, closing, sizing, and moving are consistent with the window environment of your particular platform.

#### Toolbar

The toolbar is a feature on the Floorplanner that gives you pushbutton access to many tasks. You can zoom in and out of the Floorplan window and enable the display of resource graphics, labels, and ratsnest lines. It also gives you pushbutton access to changing the distribution direction for placing logic symbols.

You can use the toolbar buttons shown in the following figure instead of the pull-down menus to perform some of the basic operations in the Floorplan window. For a complete description of the toolbar buttons, refer to the "Toolbar" section of the "Menu Command Reference" chapter.

**Note:** The toolbar also contains buttons for a number of standard system functions, such as opening a file and printing. These buttons are not shown below.

#### Figure 3-4 Floorplanner Toolbar

#### **Status Bar**

The status bar is at the bottom of the primary window. In this area, the Floorplanner displays various resource information. To the far

right it displays current row and column coordinates when the mouse pointer is in the Floorplan window.

The status bar also provides information about the toolbar buttons. When the toolbar is enabled and you move the mouse pointer over a toolbar button, the Floorplanner displays the name of that button and its function.

#### Mouse

The mouse is integral to many operations. Use it to select and place logic, access commands from the menus, and perform various window operations. Selecting logic in the Floorplanner windows is a "drag-and-drop" operation using the mouse pointer. You select logic from the hierarchical design in the Design Hierarchy window by placing the pointer over the symbol icon or hierarchical group name and clicking the left mouse button. Then you drag the pointer to the Floorplan window (a ghost image of the selected logic moves with the pointer) and release the mouse button to drop the logic at the pointer's location in the window.

To make multiple logic selections in the Floorplanner, use the standard windows procedures.

- To make multiple consecutive selections, click the left mouse button when the pointer is over the first selection. Then move the pointer to the last item, press and hold down the Shift key, and click the left mouse button.

- To make multiple nonconsecutive selections, click the left mouse button when the pointer is over the first selection. Then hold down the Control (Ctrl) key and click the left mouse button over each additional selection. Clicking on a selection that is already highlighted deselects that choice.

#### Keyboard

The Floorplanner uses the keyboard function keys that are mapped to specific menu commands and Floorplanner functions for ease of use. The following table lists the keyboard shortcuts for the Floorplanner and shows the related toolbar button, if any. You should exercise care when using the keyboard shortcuts.

| Function Key | Menu Command/Function                                | Toolbar Button |

|--------------|------------------------------------------------------|----------------|

| F1           | $\mathtt{Help}  ightarrow \mathtt{Help}$ Topics      | None           |

| F2           | View  ightarrow Options                              | None           |

| F3           | Hierarchy $\rightarrow$ Group                        | None           |

| F4           | Edit  ightarrow Colors                               | None           |

| F5           | $\mathtt{View}  ightarrow \mathtt{Refresh}$          | None           |

| F6           | $\mathtt{View}  ightarrow \mathtt{Zoom}$ to Selected | <b>Q</b>       |

| F7           | View $\rightarrow$ Zoom In                           | <b>€</b>       |

| F8           | View  ightarrow Zoom Out                             | Q              |

| F9           | View $ ightarrow$ Zoom to Box                        | ۹              |

| F10          | Change focus to the menu bar                         | None           |

| F11          | $View  ightarrow 	extsf{Zoom Full View}$             | Q              |

| Del          | $\texttt{Floorplan} \rightarrow \texttt{Remove}$     | None           |

| Esc          | Cancel current operation                             | None           |

#### **Dialog Boxes**

The Floorplanner has many commands that, when invoked, open dialog boxes that contain default settings for command execution. These types of commands have an ellipsis (...) after the command name in the menu.

The dialog boxes are composed of the following elements.

- Edit boxes, in which you can type information such as a different path name

- List boxes, which list design information such as net names

- Buttons, which allow you browse information and easily change the way a command functions

The "Using the Floorplanner" chapter provides a detailed description of the Floorplanner dialog boxes in the command descriptions.

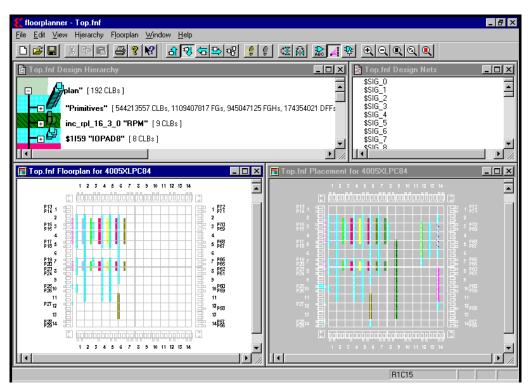

### **The Floorplanner Windows**

The primary Floorplanner window contains four sub-windows: Design Hierarchy, Design Nets, Floorplan, and Placement. Descriptions of these windows follow.

#### **Primary Window**

When you invoke the Floorplanner, the primary window, shown in the following figure, is the first window to display on your monitor.

| K floorplanner                                    |      |

|---------------------------------------------------|------|

| Eile ⊻iew Help<br>DIEFE X BEL SYN SYCE>R ST KA 22 |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

|                                                   |      |

| For Help, press F1                                | ROCO |

Figure 3-5 Floorplanner Primary Window

To begin floorplanning, select  $\texttt{File} \rightarrow \texttt{New}$  to create a Floorplan file.

When you load a Floorplan file using the  $\texttt{File} \rightarrow \texttt{New}$  or  $\texttt{File} \rightarrow \texttt{Open}$  command, the Design Hierarchy, Design Nets, Floorplan, and Placement windows are opened, as shown in the following figure.

**Note:** The Placement window only appears if PAR was run on the NCD file used to create the Floorplan file (FNF).

Figure 3-6 Floorplanner Windows

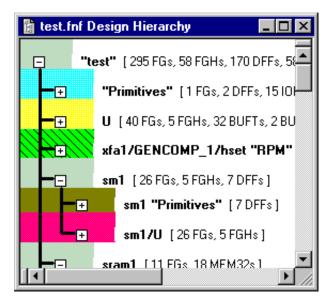

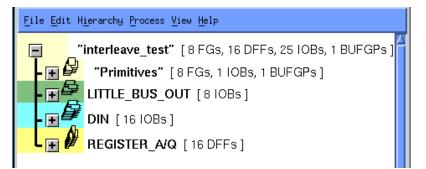

### **Design Hierarchy Window**

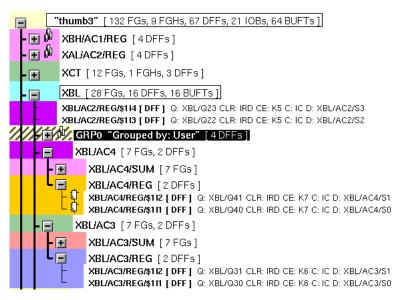

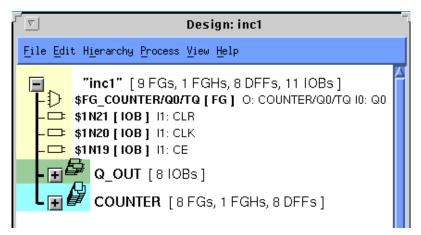

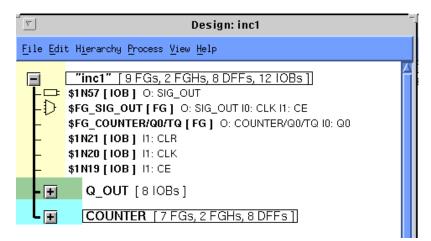

The Floorplanner generates a hierarchical representation from the NGD and NCD input files. The Design Hierarchy window, shown in the following figure, displays a fully expandable and annotated hierarchy. The header line indicates the name of the design that is currently loaded.

Figure 3-7 Design Hierarchy Window

#### **Hierarchy Display**

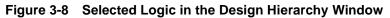

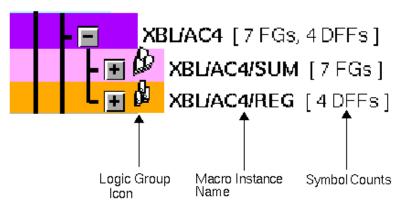

The Floorplanner uses colors in the hierarchy display to distinguish the levels in the hierarchy, which are annotated with the instance name from the design file. Hierarchy structure lines are black lines that traverse the colored areas and show the hierarchy of each hierarchical group. Each hierarchical group has a gray box with a minus sign, "–", or a plus sign, "+". The "–" indicates that the hierarchical group is expanded to show the next lower level of hierarchy. The "+" indicates that the hierarchical group is collapsed, and that lower levels of hierarchy exist for that hierarchical group.

### **Selecting Logic**

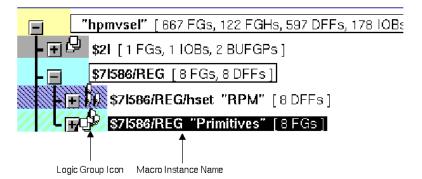

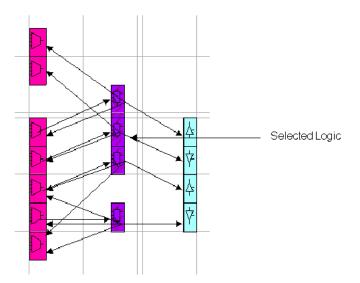

When you place the mouse pointer over a hierarchical group instance name or its logic symbol icon (in the Design Hierarchy window) and click the left mouse button, you select that logic. The Floorplanner displays selected logic in the Design Hierarchy window in reverse video. (If Flashing is enabled, the selected logic in the Floorplan window flashes.) When you select a hierarchical group, you also select all the sub-hierarchy in that hierarchical group. When you select logic at some lower level, the Floorplanner draws a rectangular box around all associated higher levels of hierarchy. The following figure shows an example. The \$71586/REG hierarchical group is the selected logic, as indicated by the reverse video. The hierarchical groups hpmvsel and \$71586/REG are the higher-level associated logic, as indicated by the box around those hierarchical group names.

#### **Expanding and Collapsing Hierarchical Groups**

Click the left mouse button on the Expand/Collapse button when it displays the "+" sign to expand a hierarchical group and display the next level of hierarchy. The logic elements that comprise each hierarchical group appear as an icon between the Expand/Collapse button and the instance name. The following figure shows a sample hierarchy.

Figure 3-9 Hierarchical Group Display in the Design Hierarchy Window

#### **Hierarchical Group Annotation**

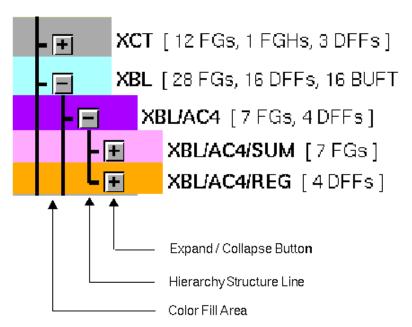

Each hierarchical group in the design hierarchy contains the instance name and symbol counts and, optionally, the group or source name. The symbol count is the number of FPGA resources required to accommodate that hierarchical group in the floorplan. Groups that you create with either the Group or Group By commands contain a non-hierarchical name and symbol count.

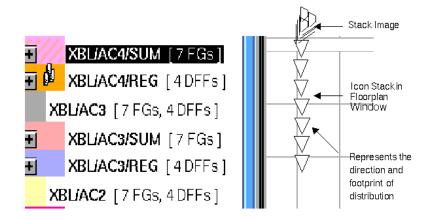

In the case of the XC4000 family, the FPGA resources are categorized by type, such as FG (function generator), BUFTs (tristate buffers), DFFs (registers), IOBs (input/output pads), RAM/ROM, and related logic. The following figure shows the important parts of a hierarchical group.

Figure 3-10 Hierarchical Group Annotation

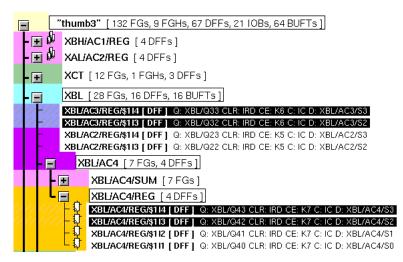

#### **Symbol Annotation**

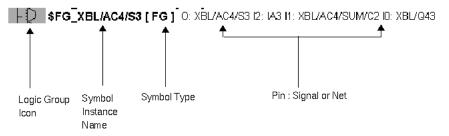

The symbol line represents the lowest hierarchy of any hierarchical group. It represents a single resource requirement of the design. The symbol line contains a logic icon, the symbol name, symbol type, and the list of pin:net pairs. The following figure shows one of the symbol instances of the expanded hierarchical group, XBL/AC4/SUM (shown in the above figure). It labels the important parts of the symbol line.

#### Figure 3-11 Symbol Annotation

In this figure, the logic icon that is shown represents a single 4-input function generator (FG) named \$FG\_XBL/AC4/S3; its output connects to net XBL/AC4/S3; its inputs connect to the nets IA3, XBL/AC4/SUM/C2, and XBL/Q43.

The symbol instance name is the corresponding symbol in the source netlist. For function generators or CLBs, it is a name that the mapping

software (MAP) provides. For other symbols, it is the name in the schematic that either you or the schematic entry tool chooses.

The symbol type refers to the type of resource that the symbol requires. Examples of symbol types are DFF (D-type flip-flop), IOB (Input/Output buffer), CLB (configurable logic block), FG (function generator), and BUFT (tristate buffer).

#### **Design Nets Window**

The Design Nets window lists the nets that connect the logic in the design. This window is shown in the following figure.

| 🖹 test.fnf Design Nets | - 🗆 × |

|------------------------|-------|

| ADRBUS<0>              |       |

| ADRBUS<1>              |       |

| ADRBUS<2>              |       |

| ADRBUS<3>              |       |

| ADRBUS<4>              |       |

| ag1/n128<0>            |       |

| ag1/n375               |       |

| ag1/n395               |       |

| ag1/n396               |       |

| ag1/n397               |       |

| ag1/n398               |       |

| ag1/n415               |       |

|                        | Ľ     |

| •                      |       |

Figure 3-12 Design Nets Window

You can list either all nets in the design or just the nets that are currently displayed in the Floorplan window. To switch from one list to the other, click the right mouse button to bring up a menu and then click the List Visible Nets or List All Nets command in that menu.

When only the visible nets are listed in the window, the heading of the window changes to Visible Nets.

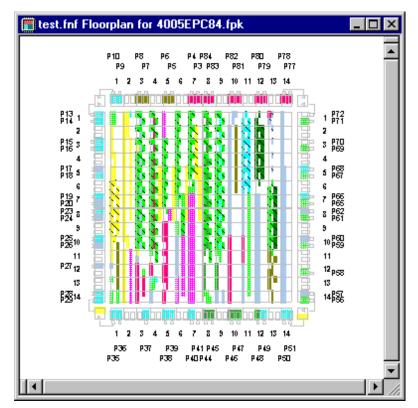

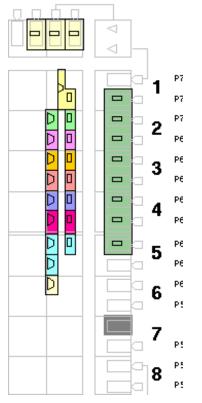

### **Floorplan Window**

The Floorplan window displays the die for a selected part type, such as XC4005EPC84. This window, shown in the following figure, is a

scrollable, scalable view of a resource map of the device that is specified in the design.

#### Figure 3-13 Floorplan Window

You floorplan by dragging selected logic from the Design Hierarchy window and dropping it into this window.

When a new Floorplan file (FNF) is created for a design and a previous FNF does not exist, the Floorplan window displays any physical design constraints that are in the initial design netlist, the UCF file, or the NCF file. If a previous Floorplan file does exist and is specified in the creation of the FNF file, the initial Floorplan constraints are generated from the previous FNF file. All netlist, UCF, and NCF constraints are ignored, unless they exist in the previous FNF.

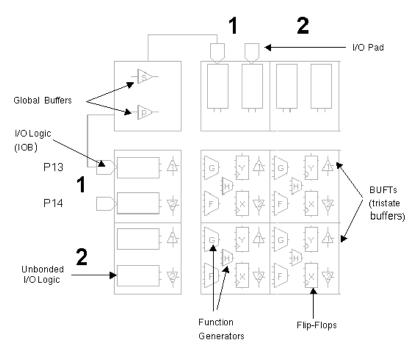

#### **Resource Graphics**

Each device family architecture has specific resources on the die. You can display these resources using the Resources panel of the  $view \rightarrow Options$  command. For example the resource graphics for the XC4000 family include I/O pads, function generators, registers, RAM/ROM, and BUFTs in the CLBs. With this feature, you control the view of the logic and available device resources. The fewer resources you display in the window, the faster the screen refreshes.

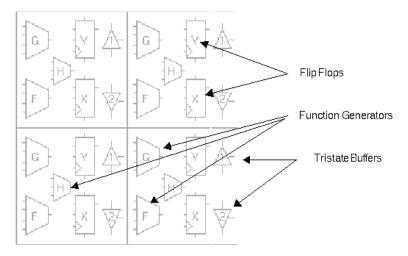

In the XC4000 family devices, flip-flops display as rectangles, function generators as trapezoids, and BUFTs as triangles. The following figure shows an example of the resource graphics available in a quadrant of the Floorplan window.

**Note:** The global buffers have a pair of dedicated I/O pads that can also connect to other logic. The lines in the floorplan die show which I/O pad is dedicated to that buffer.

Figure 3-14 Resource Graphics for an XC4000 Device

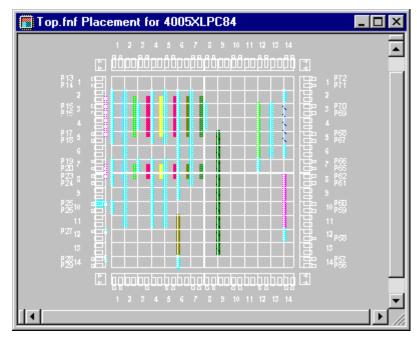

#### **Placement Window**

The Placement window displays the design after it has been placed and routed. This window is shown in the following figure. This is a very useful function to help evaluate the properties of an automatically generated placement.

#### Figure 3-15 Placement Window

The elements in the Placement Window cannot be moved or modified without loading in new placement information from a placed NCD file using the File  $\rightarrow$  New or File  $\rightarrow$  Update commands. To translate placement information into Floorplan constraints, use the Floorplan  $\rightarrow$  Constrain From Placement or Floorplan  $\rightarrow$  Replace All With Placement commands.

### **Closing the Current Design**

To close the current design without exiting the Floorplanner, select the  $\texttt{File} \rightarrow \texttt{Close}$  command. If you have not made any changes to the current design, the windows that contain the design close while the Floorplanner window remains open.

If you have made any changes to the design in the Floorplanner, a dialog box prompts you to save those changes. Click the appropriate button.

- If you click **Yes**, the Floorplanner writes out an FNF file that is a snapshot of the floorplanned logic and the Floorplanner environment. In addition, the Floorplanner runs a utility to create an MFP file containing all physically constrained elements in the FNF file. The current design then closes.

- If you click **No**, the current design closes without saving the changes to the design.

- If you click Cancel, the dialog box closes and you can continue with the current floorplanning session.

# **Exiting the Floorplanner**

To exit from the current floorplanning session, select File  $\rightarrow$  Exit. If you have not made any changes to the design, the Floorplanner window closes.

If you have floorplanned any logic, a dialog box displays and prompts you to save the changes to the current floorplan. Click the appropriate button.

- If you click **Yes**, the Floorplanner writes out an FNF file that is a snapshot of the floorplanned logic and the Floorplanner environment. In addition, the Floorplanner runs a utility to create an MFP file containing all physically constrained elements in the FNF file. The Floorplanner window closes.

- If you click **No**, the Floorplanner window closes without saving the changes to the current design.

- If you click Cancel, the dialog box closes and you can continue with the current floorplanning session.

# **Chapter 4**

# Using the Floorplanner

This chapter provides step-by-step instructions for performing the important floorplanning tasks.

These procedures are presented in sequential order; however, not every task that can be performed is documented in this chapter. Floorplanning a design may require you to repeat some procedures several times. Consult the design flows in the "Design Flow" chapter to aid your floorplanning efforts.

For information on starting and exiting the Floorplanner, see the "Getting Started" chapter.

This chapter contains the following sections.

- "Opening a File" describes how to load a design file into the Floorplanner.

- "Saving a File" explains how to save your floorplanned design.

- "Using Colors" explains how to assign different colors to the hierarchical groups display.

- "Floorplanning Logic" describes how to move logic symbols from the Design Hierarchy window to the Floorplan window.

- "Floorplanning Designs that Contain RPMs" explains how to floorplan designs that contain Relationally Placed Macros (RPMs).

- "Creating Groups" explains how to rearrange and regroup the design hierarchy.

- "Using Area Constraints" describes how to create area constraints.

- "Flattening and Building the Hierarchy" describes how to flatten and rebuild the design hierarchy.

- "Walking Through the Design" describes how to select successive logic by connectivity rather than by name.

- "Analyzing PAR Placement" describes how to analyze the placement results that PAR generates.

- "Analyzing PAR Placement for Timing Constraints" describes how to analyze the placement of floorplanned logic by PAR with respect to Timing Constraints.

- "Finding Logic Connected to Nets" explains how to find logic that is connected to nets in the floorplanned design.

- "Displaying Resources and Logic" describes how to display the logic resources that are available on the FPGA.

- "Performing Detailed Manual Placement" explains how to manually place logic into the Floorplanner window.

- "Checking the Floorplan" describes how to check the floorplanned logic for placement problems.

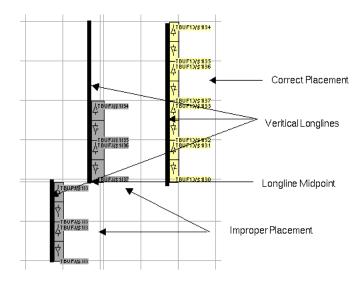

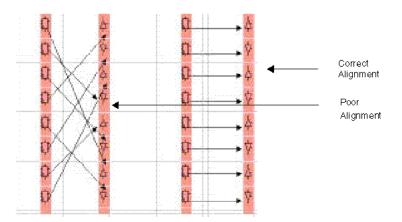

- "Aligning Symbols" describes how to align symbols in the Floorplan window to reduce unnecessary routing.

- "Working with Patterns" describes how to work with patterns when you place selected logic in the Floorplan window.

- "How to Interleave Buses" describes how to interleave buses in the Floorplan design.

- "Iterative Floorplanning" explains how to floorplan your design iteratively.

- "Floorplanning Incremental Schematic Changes" describes how to make incremental changes to a design that has been previously implemented in an FPGA.

- "Making Small Modifications to Automatic Placement" describes how to make small changes to an automatically placed design in order to fix packing or placement problems.

- "Lock Down I/Os from Automatically Placed Design" describes how to select the I/Os from an automatically placed and routed design and lock them down in the Floorplan window.

- "Getting Started With an Unfamiliar Design" describes how to familiarize yourself with the connectivity of someone else's design.

# **Opening a File**

To load a design file in the Floorplanner, follow these steps.

1. Select File  $\rightarrow$  Open.

This command opens the Open File dialog box where you specify which FNF file to load. In this dialog box, you can also change directories if the desired FNF file is in a directory other than the current directory.

- 2. Scroll the files list box until you find the desired design file in the list.

- 3. Double-click on the design file name or select the file name and then click Open to open the Floorplanner windows.

When you load in an FNF file, the Floorplanner reads the file, loads the correct device (part type), opens the Design Hierarchy window with a hierarchical design, and opens the Floorplan window with the correct FPGA die.

**Note:** If an FNF file exists in the current directory and it is newer than the NCD and NGD files, the Floorplanner reads in the FNF file. Otherwise, it opens a dialog box that asks if you want to update the FNF file from the newer NCD or NGD files.

# Saving a File

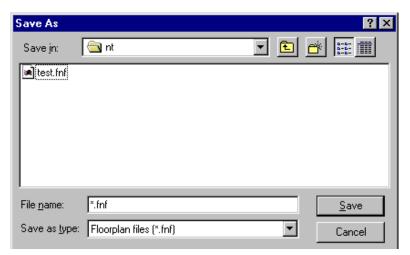

To save your floorplanned design, select  $\texttt{File} \rightarrow \texttt{Save}.$

The Save command creates a file with the same name as the current design and the extension .fnf. The information stored in this file includes the design's hierarchy organization, floorplanned logic, and net, logic, and color assignments.

This file represents a snapshot of the current state of the floorplan that you can use later.

In addition, whenever the FNF file is saved, the floorplanner automatically creates an MFP file. The MFP file contains all the physical constraints for the design that appear in the Floorplan window, and is used as an input to MAP.

# Using Colors

The Floorplanner automatically assigns unique colors to hierarchical groups when it reads a new design. Hierarchical nodes that have one lower level of hierarchy are set to the color of that lower level node. Hierarchical groups with more than one lower level of hierarchy, as well as individual symbols, are not assigned colors. Individual symbols without assigned colors inherit the color of the lowest level of associated hierarchy.

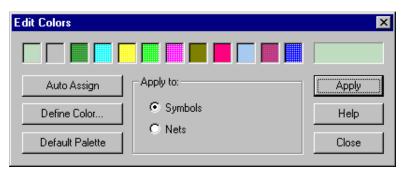

You can change the colors of any hierarchical group using the Edit  $\rightarrow$  Colors command. If you assign a color to a symbol, that symbol is always shown in that color in both windows. If you assign a color to a hierarchical group, the colorless symbols under that node will appear in that group's color.

**Note:** You can remove color assignments using the Auto Assign button in the Colors dialog box.

The following sections describe using colors in the Design Hierarchy window and in the Floorplan window. The last section describes how to use colors to distinguish between floorplanned logic and place and routed logic.

#### In the Design Hierarchy Window

- 1. Select the hierarchical groups and symbols for which you want to change colors.

- 2. Select  $\texttt{Edit} \rightarrow \texttt{Colors}$ .

This command opens the Edit Colors dialog box.

- 3. Click the button that displays the color you want to use.

- 4. Click Apply to change to the new color.

#### In the Floorplan Window

- 1. Select the logic by dragging out an area around the desired logic for which you want to change colors, or click the left mouse button on an individual symbol.

- 2. Select  $\texttt{Edit} \rightarrow \texttt{Colors}$ .

This command opens the Edit Colors dialog box.

- 3. Click the button that displays the color you want to use.

- 4. Make sure the Apply to Symbols radio button is selected.

- 5. Click Apply to change to the new color.

# **Distinguishing Logic**

You can use the **Edit**  $\rightarrow$  **Colors** command to distinguish placed and routed logic and floorplanned logic. You can change the color of the floorplanned logic to a color not used in the hierarchy. Then, when you view the placement window, the unique color distinguishes the placed and routed logic from floorplanned logic in the design.

- 1. Select all the logic in the design.

- 2. Select  $\texttt{Edit} \rightarrow \texttt{Colors}$ .

- 3. Choose a new color for the selected logic from the palette in the Edit Colors dialog box.

**Note:** When colors are automatically assigned, the first two and the last two colors are not included. You can use one of those colors to make the logic distinguishable from the rest of the design.

- 4. Click Apply.

- 5. Select the floorplanned logic by dragging the mouse pointer over the entire Floorplan window.

- 6. Choose a different color from the palette in the Edit Colors dialog box for the selected floorplanned logic.

- 7. Click Apply.

- If the NCD file that was used to create the Floorplanner file contained placement information, selecting View → Placement will show the entire placed design, with the Floorplanned logic in a different color than the non-floorplanned logic.

**Note:** You can use the Auto Assign button in the Edit Colors dialog box to return to a normal display.

# **Floorplanning Logic**

This procedure explains how to select, move, and manipulate logic symbols from the Design Hierarchy window to the Floorplan window.

- 1. Select the desired logic from the Design Hierarchy window. There are two ways to do this.

- Using the mouse, place the pointer on the logic group icon of the desired hierarchical group and click the left mouse button.

# Figure 4-1 Select an Icon Stack from the Design Hierarchy Window

• Select Edit → Find to find and select the desired logic. In the Find dialog box, you can type in the instance name, choose a specific type of logic, such as I/O Pads for IOBs, Flip-Flops for DFF, or type of connection.

Click Find.

If the search criteria that you applied is correct, an arrow will point to the applicable instance or hierarchical group in the Design Hierarchy window.

- 2. Use the mouse and click on the found logic or hierarchical group icon.

- 3. If you want to move an individual piece of logic, expand the hierarchical group and click on the desired logic icon.

The logic icons change to a ghost image as you move the mouse pointer.

When moving more than one icon at a time, you must use one of the four directional arrow toolbar buttons to determine the distribution direction. The default direction is from top to bottom.

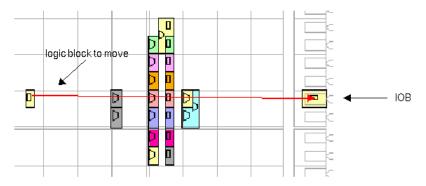

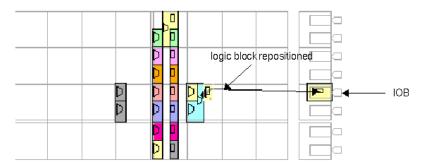

4. Move the mouse pointer from the Design Hierarchy window to the desired location on the FPGA in the Floorplan window.

A ghost image of the selected logic icons showing the allocation direction moves with the pointer.

# Figure 4-2 Icons in Transit from the Design Hierarchy Window to the Floorplan Window

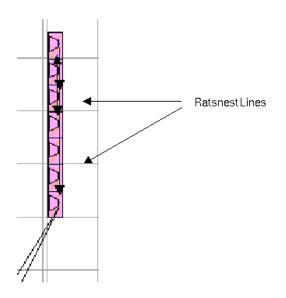

5. At the desired location in the Floorplanner window, click the left mouse button to place the logic. The Floorplanner places the logic according to the distribution direction you have chosen.

If you have Ratsnest turned on, you will see black lines indicating logic connectivity to the group you have just selected and placed.

# **Floorplanning Designs that Contain RPMs**

This procedure explains how to floorplan designs that contain Relationally Placed Macros (RPMs). RPMs are optimized macros that have the relative positions of the logic locked down. For this reason, you can only place RPMs as a whole unit into the Floorplan window.

You must have enough resources in the Floorplan window to accommodate the entire RPM, because it must be placed in its entirety. For example, if an RPM is four CLBs in height and the largest vacancy in the die is 3 CLBs high, the RPM will not fit.

Perform the following steps to place an RPM in the Floorplan window.

- 1. Select the desired RPM from the Design Hierarchy window.

- 2. Place the selected RPM into the Floorplan window in an area that can accommodate the entire RPM.

**Note:** A good floorplanning practice is to floorplan both the RPM and the logic it is driving in a specific set of locations.

# **Creating Groups**

The hierarchical representation of your design is a result of mapping your original design; it might not be optimized for your floorplanning preferences. To make floorplanning easier, you can rearrange and regroup the design hierarchy.

**Note:** The function or connectivity of logic elements may be a reason for you to place them together as a group.

### **Manual Grouping**

- 1. In the Design Hierarchy window, select the logic that you want to group.

- 2. Select the first piece of logic with the left mouse button and subsequent logic with the middle mouse button. Or, select subsequent logic by holding down the control key and pressing the left mouse button.

- 3. Select Hierarchy  $\rightarrow$  Group, or press the F3 key.

The Floorplanner creates a new group and assigns an arbitrary name to the group "GRP0". The text line looks as follows.

GRP0 "Grouped by: User" [symbol count]

[symbol count] is the number of logic elements

The Floorplanner labels subsequent new user-created groups "GRP1", "GRP2", and so on.

4. Use the  $\texttt{Edit} \to \texttt{Properties}$  command to give the new group a better name.

The newly created group occupies a position in the lowest level of hierarchy that is common to all logic that comprises the group.

The following figures illustrate how to create a new group in the design hierarchy.

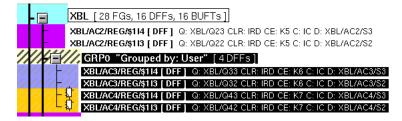

The first figure shows the four D-type flip-flops that appear in reverse video. These are the logic symbols that have been selected to form a new group.

Figure 4-4 Select Logic for Grouping

The next figure shows the new group. The new group is named GRP0 (highlighted in reverse video). It is the first new group to be created in the design. Note that the four flip-flops are no longer part of XBL and AC4, respectively, as indicated by the new symbol counts.

Figure 4-5 The Floorplanner Creates New Group

The Floorplanner places the new group in the hierarchy near the group XBL, the lowest level of hierarchy that is common to the four flip-flops chosen for the group. When you expand the new group, you see that the four flip-flops are now in the new group.

The following figure shows the new group expanded. You can place this new group as a unit on the floorplan die.

Figure 4-6 GRP0 Expanded to Show Logic Elements

#### **Automatic Grouping**

It is often more convenient to group logic by common type or signal names. Creating such groups can make it easier to floorplan.

For example, you might want to make a group of all the BUFTs that have a common output enable. In this case, do the following steps.

1. Select  $\texttt{Edit} \rightarrow \texttt{Find}$ .

This command opens the Find dialog box.

- 2. Select a BUFT in the Design Hierarchy window that contains the enable signal of interest by clicking the mouse on the appropriate line (on the BUFT's instance name).

- 3. In the Connections list box, select Common Enable (BUFTs, DFFs, IO).

- 4. Click Find.

- 5. Click Select Found.

The Floorplanner searches throughout the design hierarchy and highlights each BUFT that meets the criteria you selected.

**Note:** The Floorplanner automatically expands groups that have sub-hierarchy that meet the find criteria.

6. Select Hierarchy  $\rightarrow$  Group, or press the F3 key.

The Floorplanner creates a new group and assigns an arbitrary name to the group "GRP0" (if this is the first user-created group). The text line looks as follows.

GRP0 "Grouped by: User" [symbol count]

[symbol count] is the number of logic elements

**Note:** You can also use the Hierarchy  $\rightarrow$  Group By command to create these types of groups.

# **Using Area Constraints**

Area constraints are a way of restricting where PAR can place a particular piece of logic. By reducing PAR's search area for placing logic, PAR's performance may be improved.

To create an area constraint, do the following steps.

- 1. Select a hierarchical group in the Design Hierarchy window.

- 2. Select  $Floorplan \rightarrow Assign Area Constraint or click on the toolbar button.$

- 3. In the Floorplan window, use the mouse to drag out a rectangular box where you want the area constraint to be located. The area constraint will cover all the tiles that are inside the drag box.

Area constraints may overlap each other. Select Floorplan  $\rightarrow$  Bring Area To Front or Floorplan  $\rightarrow$  Push Area To Back to move a selected area constraint in front of or behind another.

# Flattening and Building the Hierarchy

You may have floorplanned the design and saved it. Then you realize that you must make a change to the design at the schematic level that deletes some logic. When you read in the FNF file, the Floorplanner reads in the old hierarchy. Due to the changes made at the schematic level, the old hierarchy may represent divisions that are no longer valid.

#### How to Flatten the Hierarchy

You must select a hierarchical node to enable the Flatten Groups command.

This procedure explains how to flatten the hierarchy in the Design Hierarchy window.

1. Select the part of the design hierarchy that you want to flatten. You can select just the level of hierarchy that contains the logic that was changed in the schematic.

To flatten the entire hierarchy, select the top-level hierarchy.

2. Select Hierarchy  $\rightarrow$  Flatten Groups.

The Floorplanner removes all lower level hierarchy from the selected hierarchical node and moves all of the associated symbols up in the hierarchy.

#### How to Rebuild the Hierarchy

To rebuild the hierarchy using symbol instance names, select Hierarchy  $\rightarrow$  Rebuild. The Floorplanner builds a hierarchy tree and places the selected logic symbols in their proper positions in that tree.

**Note:** The Rebuild command works on all logic, not just selected logic.

# Walking Through the Design

This procedure explains how to select successive logic by connectivity rather than by name. This process helps you see which floorplanned logic elements drive other logic in the design.

# **Finding Logic**

- 1. Determine the logic that is of interest.

- 2. Select  $\texttt{Edit} \rightarrow \texttt{Find}$ .

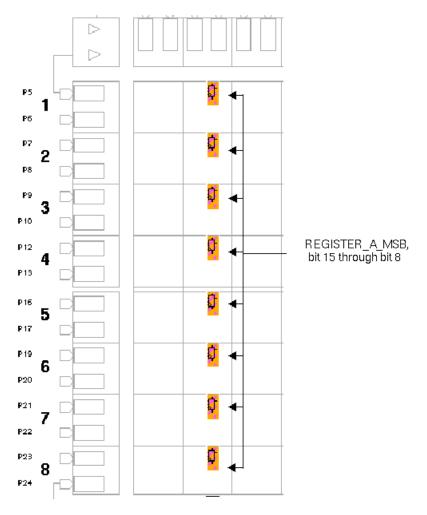

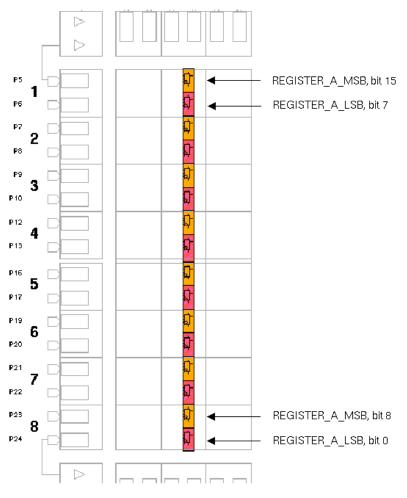

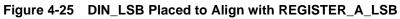

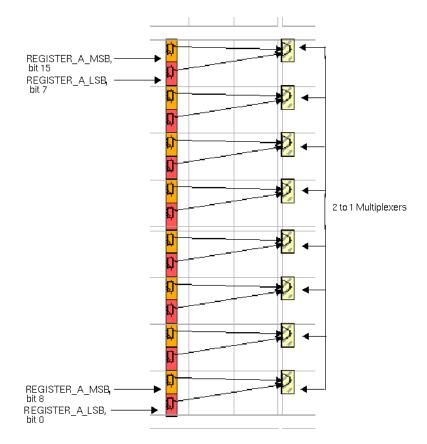

This command opens the Find dialog box.