#### X2443 X2443I

## 256 Bit Serial Nonvolatile Static RAM

# 16x16 Bit Serial NOVRAM\*

- Ideal for use with Single Chip Microcomputers

- Static Timing

- Minimum I/O Interface

- Minimum Support Circuits

- Software and Hardware Control of Nonvolatile Functions

- Maximum Store Protection

- TTL Compatible

- 16x16 Organization

- Reliable N-Channel Floating Gate Technology

- Single 5V Supply

- Low Power Dissipation

- Active Current: 15mA Typ.

- Store Current: 8mA Typ.

- Standby Current: 6mA Typ.

- Sleep Current: 5mA Typ.

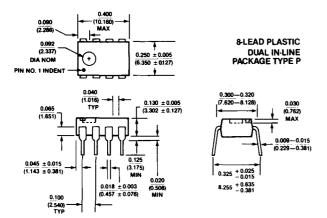

- 8-Pin Mini-Dip

- Low Cost

- Compact

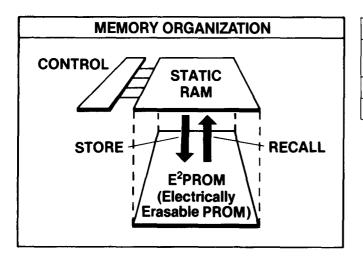

The X2443 is a 256-bit Xicor NOVRAM memory fabricated in Xicor's proven NMOS technology. The device is organized as 16 words of 16 bits each. Serial access allows the use of a cost-effective 8-pin package, making the X2443 ideal for cost sensitive and compact design applications. Each bit of the static RAM is overlayed with a bit of nonvolatile electrically erasable PROM (E<sup>2</sup>PROM). Data can be transferred back and forth between the two memories either by instructions sent from the processor over the serial interface, or by toggling the external STORE and RECALL inputs. Nonvolatile data is retained in the E<sup>2</sup>PROM, while independent data can be accessed and updated in the RAM.

High voltage pulses and supplies are not required. A single 5V supply is the only power source needed, and all signals are TTL compatible.

The X2443 offers many modes of operation in order to minimize the power consumption of the chip. The chip is placed in the STANDBY mode whenever it is deselected, and is placed in the SLEEP mode whenever the sleep instruction is executed. The chip will automatically return active from STANDBY when selected by CE, and will exit the SLEEP mode when the next RECALL operation is performed, either by the RCL instruction or by taking the RECALL input low.

XICOR, Inc., 851 BuckeyeCourt, Milpitas, California 95035

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias X2443 | -10° C to +85° C  |

|------------------------------|-------------------|

| X2443I                       | -65°C to +125°C   |

| Storage Temperature          | - 65°C to + 150°C |

| Voltage on any Pin with      |                   |

| Respect to V <sub>SS</sub>   | – 1.0V to + 6V    |

| D.C. Output Current          | 5mA               |

## DC OPERATING CHARACTERISTICS

#### \*COMMENT:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| X2443 $T_A = 0^{\circ}$ C to +70° C, X24431 $T_A = -40^{\circ}$ C to +85° C.                      |

|---------------------------------------------------------------------------------------------------|

| $V_{CC} = +5V \pm 5\%$ unless otherwise specified. All voltages with respect to V <sub>SS</sub> . |

| Symbol          | Parameter              |       | Limits              |                    |       | Conditions                      |

|-----------------|------------------------|-------|---------------------|--------------------|-------|---------------------------------|

| Symbol          | Faiametei              | Min.  | Typ. <sup>(1)</sup> | Max.               | Units | Conditions                      |

| V <sub>CC</sub> | Operating Voltage      | 4.75  | 5                   | 5.25               | V     |                                 |

| Icc             | Power Supply Current   |       | 15                  |                    | mA    | Inputs = 5V, $I_{I/O}$ = 0mA    |

| I <sub>SL</sub> | Sleep Current          |       | 5                   |                    | mA    |                                 |

| I <sub>SB</sub> | Standby Current        |       | 6                   |                    | mA    | CE = 0.4V                       |

| ISTO            | Store Current          |       | 8                   |                    | mA    |                                 |

| ILI             | Input Load Current     |       | .1                  | 10                 | μA    | $V_{IN} = 0V$ to 5.5V           |

| ILO             | Output Leakage Current |       | .1                  | 10                 | μΑ    | $V_{OUT} = 0V \text{ to } 5.5V$ |

| VIL             | Input Low Voltage      | - 1.0 |                     | .8                 | V     |                                 |

| VIH             | Input High Voltage     | 2.0   |                     | $V_{\rm CC} + 0.5$ | V     |                                 |

| V <sub>OL</sub> | Output Low Voltage     |       |                     | .4                 | V     | I <sub>OL</sub> = 2.4mA         |

| V <sub>OH</sub> | Output Low Voltage     | 2.4   |                     |                    | V     | l <sub>OH</sub> =8mA            |

## CAPACITANCE (2)

$T_A = 25^{\circ}C$ , f = 1.0 MHz,  $V_{CC} = 5V$

| Symbol          | Test               | Max. | Unit | Conditions      |

|-----------------|--------------------|------|------|-----------------|

| Co              | Output Capacitance | 8    | pF   | $V_{I/O} = 0 V$ |

| C <sub>IN</sub> | Input Capacitance  | 6    | pF   | $V_{IN} = 0 V$  |

## A.C. CONDITIONS OF TEST

| Input Pulse Levels             | 0 Volt to 3.0 Volt                    |

|--------------------------------|---------------------------------------|

| Input Rise and Fall Times      | 10 nsec                               |

| Input and Output Timing Levels | 1.5 Volts                             |

| Output Load                    | 1 TTL Gate and $C_L = 100 \text{ pF}$ |

### NONVOLATILE OPERATIONS<sup>(3)</sup>

| Operation       | STORE | RECALL | INST | WRITE<br>ENABLE<br>LATCH | Previous<br>RECALL |

|-----------------|-------|--------|------|--------------------------|--------------------|

| Hardware Recall | 1     | 0      | NOP  | X                        | X                  |

| Software Recall | 1     | 1      | RCL  | X                        | X                  |

| Hardware Store  | 0     | 1      | NOP  | SET                      | True               |

| Software Store  | 1     | 1      | STO  | SET                      | True               |

Notes:

(1) Typical values for  $T_A = 25^{\circ}C$  and nominal voltage

(2) This parameter is periodically sampled and not 100% tested.

<sup>(3)</sup> Positive logic is used, i.e., a low voltage represents a logic "0". A high voltage represents a logic "1". NOP designates when the X2443 is not currently executing an instruction.

## **AC CHARACTERISTICS**

X2443  $T_A = 0^{\circ}$  C to +70° C, X24431  $T_A = -40^{\circ}$  C to +85° C. V<sub>CC</sub> = +5V ± 5% unless otherwise specified.

| <u> </u>         |                              |      |                                                                                                             |      |       |

|------------------|------------------------------|------|-------------------------------------------------------------------------------------------------------------|------|-------|

| Symbol           | Parameter                    | Min. | Typ.(1)                                                                                                     | Max. | Units |

| F <sub>SK</sub>  | SK Frequency                 | 0.0  |                                                                                                             | 1.0  | MHz   |

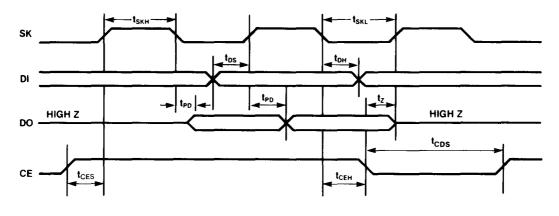

| t <sub>sкн</sub> | SK Positive Pulse Width      | 0.4  |                                                                                                             |      | μs    |

| t <sub>SKL</sub> | SK Negative Pulse Width      | 0.4  |                                                                                                             |      | μs    |

| t <sub>DS</sub>  | Data Setup Time              | 0.4  |                                                                                                             |      | μS    |

| t <sub>DH</sub>  | Data Hold Time               | 0.2  |                                                                                                             |      | μs    |

| t <sub>PD</sub>  | SK to Data Valid             |      | · · _ · _ · _ · _ · _ · _ · _ · / · · _ · / · · _ · / · · _ · / · · / · · / · · / · · / · · / · · / · · / · | 0.75 | μS    |

| tz               | Chip Enable to Output High Z |      |                                                                                                             | 1.0  | μS    |

| t <sub>CES</sub> | Chip Enable Setup            | 0.8  |                                                                                                             |      | μS    |

| t <sub>CEH</sub> | Chip Enable Hold             | 0.4  |                                                                                                             |      | μS    |

| t <sub>CDS</sub> | Chip De-select               | 0.8  |                                                                                                             |      | μs    |

## **CONTROL/DATA TIMING**

**Diagram 1**

-CE must be taken low between instructions.

- Once the chip has been selected with CE, the first logic "1" clocked by the rising edge of SK into the DI input marks the beginning of an instruction. All previous logic '0's are ignored.

| INSTRUCTION SET   |                                                      |                                                       |  |  |  |

|-------------------|------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Instruction       | Format, I <sub>2</sub> I <sub>1</sub> I <sub>0</sub> | Operation                                             |  |  |  |

| WRDS (Diagram 5)  | 1XXXX000                                             | Reset Write Enable Latch (Disables writes and stores) |  |  |  |

| STO (Diagram 5)   | 1XXXX001                                             | Store RAM data in E <sup>2</sup> PROM                 |  |  |  |

| SLEEP (Diagram 5) | 1XXXX010                                             | Enter SLEEP Mode                                      |  |  |  |

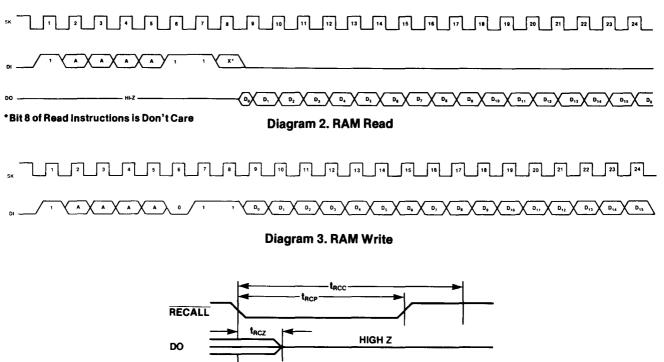

| WRITE (Diagram 3) | 1AAAA011                                             | Write Data into RAM Address AAAA                      |  |  |  |

| WREN (Diagram 5)  | 1XXXX100                                             | Set Write Enable Latch (Enables writes and stores)    |  |  |  |

| RCL (Diagram 5)   | 1XXXX101                                             | Recall E <sup>2</sup> PROM Data into RAM              |  |  |  |

| READ (Diagram 2)  | 1AAAA11X                                             | Read Data from RAM Address AAAA                       |  |  |  |

# DATA OPERATIONS

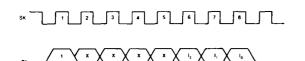

**Diagram 4. Hardware Recall**

## **ARRAY RECALL CYCLE**

|                  |                         | Limits |      |      |       |

|------------------|-------------------------|--------|------|------|-------|

| Symbol           | Parameter               | Min.   | Тур. | Max. | Units |

| t <sub>RCC</sub> | Recall Cycle Time       | 2.5    |      |      | μS    |

| t <sub>RCP</sub> | Recall Pulse Width      | 1.0    |      |      | μS    |

| t <sub>RCZ</sub> | Recall to Output High Z |        |      | 0.5  | μS    |

### NUMBER OF RECALL CYCLES:

After data has been stored properly in the nonvolatile memory (E<sup>2</sup>PROM), the NOVRAM is expected to recall this data an unlimited number of times during the lifetime of the device.

Diagram 5. Non-Data Operations

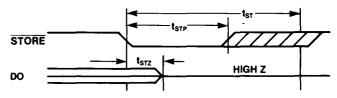

## **STORE CYCLE**

| Symbol Parameter |                        | Limits |      |      |       |

|------------------|------------------------|--------|------|------|-------|

|                  | Parameter              | Min.   | Тур. | Max. | Units |

| t <sub>ST</sub>  | Store Time             |        |      | 10   | ms    |

| t <sub>STD</sub> | Store Pulse Width      | 0.1    |      |      | μS    |

| t <sub>STZ</sub> | Store to Output High Z |        |      | 0.5  | μS    |

## NUMBER OF STORE CYCLES:

NOVRAMs are specified to perform a minimum of 10,000 store cycles. Each cell is specified to complete 1000 data changes per bit.

## **RECALL OPERATION**

The RECALL operation transfers the data currently in the nonvolatile E<sup>2</sup>PROM into the RAM section of the X2443. The RECALL operation can be initiated either from the RECALL input being driven low, or the execution of the RCL instruction. Once initiated, all other operations are inhibited, and the previous data in the RAM is overwritten. If the chip had been previously placed in SLEEP mode, the RECALL operation will leave the chip in Active mode. The first RECALL after power-on also sets an internal latch, which must be set in order to do subsequent STORE operations.

#### STORE OPERATION

The STORE operation transfers the data currently in the X2443 RAM into the E<sup>2</sup>PROM. The data currently in the E<sup>2</sup>PROM is overwritten. The STORE operation can be initiated from either the STORE input being driven low, or the execution of a STO instruction. In order to protect against inadvertent stores which might destroy important information in the E<sup>2</sup>PROM, several conditions must be true in order to perform the STORE operation.

- 1. STO Command issued or STORE driven low

- 2. Write Enable Latch must be set

- 3. Previous Recall Latch must be set

The STORE operation inhibits all other operations, and any attempt to read the part during a STORE operation will result in the DO output remaining in the high impedance state. The STORE operation clears the Write Enable latch. If the X2443 is performing a WRITE operation, the STORE input is ignored until CE is taken low.

#### WRITE/STORE PROTECTION

WRITE and STORE protection is provided by the X2443 internal Write Enable Latch. This latch must be set in order to do either a WRITE or STORE operation. This latch can be set with the WREN instruction and reset with the WRDS instruction. The Write Enable latch is automatically reset after a STORE operation is performed.

### **READ/WRITE MEMORY**

The RAM in the chip is accessed by the READ and WRITE instructions. These instructions include a 4-bit address, which selects which word is to be written or read. After the instruction and address have been sent, serial data (16-bits) will be either output on the DO pin in the case of a read, or input through the DI pin in the case of a write. The X2443 design allows the connection of the DI and DO lines together to form a bi-directional serial interface.

The least significant bit of the READ instruction is a don't care to enhance the use of the shared I/O capability of the DI and DO lines.

### SLEEP MODE

The SLEEP mode places the X2443 into a low power quiescent mode. Internal RAM is turned off, and any data currently in RAM becomes invalid. Data is maintained in E<sup>2</sup>PROM, as it was saved in the last STORE operation. The SLEEP mode can only be exited by a hardware or software initiated RECALL operation.

| ORDERING INFORMATION                           |                |       |  |  |

|------------------------------------------------|----------------|-------|--|--|

| Part Number Temperature Range Memo<br>Organiza |                |       |  |  |

| X2443P                                         | 0°C to 70°C    | 16x16 |  |  |

| X2443PI                                        | - 40°C to 85°C | 16x16 |  |  |

### **PACKAGING INFORMATION**

#### LIMITED WARRANTY

Xicor, Inc. warrants that the products sold hereunder are free from any defects in material and/or workmanship and that the products meet the nominal specifications contained in the Xicor data sheet in effect at date of manufacture of such products. No other warranty is intended or should be implied by the purchaser, and Xicor specifically disclaims any incidental or consequential damages which may result from the use of the purchased products. Purchaser's sole remedy under this warranty shall be the replacement, without charge, of any Xicor products which do not comply with this warranty and which are returned to Xicor products which do not comply with this warranty and which are returned to Xicor product sufficient to the specification that the product can be returned to Xicor, purchaser must notify Xicor, in writing, of noncompliance of Xicor product with this warranty. This notice should include proof of purchase, all details of the use of the product since purchase, and certification that the product has been operated in compliance with the specified operating conditions and specified absolute maximum ratings. Further, no product will be returned to Xicor under the terms of this warranty without the express written consent of Xicor, which consent shall not be unreasonably withheld. Xicor reserves the sole rights to determine compliance under the terms of this warranty.

Purchaser is solely responsible to determining whether any Xicor product is suitable for use in purchaser's application. Xicor therefore assumes no responsibility for purchaser's circuits and systems operation. The foregoing is in lieu of any other warranty, express, implied or statutory, including the implied warranties of merchantability and fitness for a particular

The foregoing is in lieu of any other warranty, express, implied or statutory, including the implied warranties of merchantability and fitness for a particular purpose, and any implied warranty arising from course or performance, course of dealing or usage of trade, all of which other warranties are hereby expressly disclaimed.

Nothing herein shall be construed as passing or intending to pass Seller's warranty to Purchaser directly on to any customer(s) of Purchaser. In no event shall Seller be liable to Purchaser for loss of profits, loss of use, or damages of any kind based upon a claim for breach of warranty.

#### LIFE SUPPORT POLICY

Xicor's products are not authorized for use as critical components in life support devices or systems.

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform,

when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.