## **AB 301**

# **APPLICATIONS BOOK**

#### TABLE OF CONTENTS

| APPLICATION NOTES                                        |     |

|----------------------------------------------------------|-----|

| AN101 Xicor NOVRAM Family, Easier Than Ever To Use       | 1   |

| AN102 Storing Data in Xicor NOVRAMs During Power Failure | 9   |

| AN103 Xicor Replaces DIP Switches and Trimmers with      | -   |

| NOVRAM Memories                                          | 15  |

| AN104 The World's Easiest-To-Use EEPROMs Are Here        | 23  |

|                                                          | 23  |

| APPLICATION BRIEFS                                       |     |

| Nonvolatile Data Integrity: Inadvertent Write/Store      |     |

| Elimination                                              | 31  |

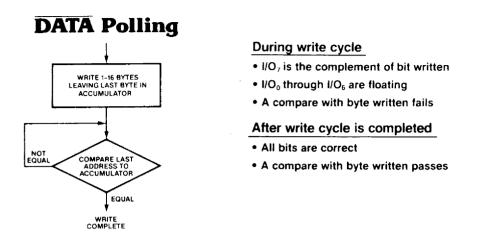

| Automatic Page Write *** DATA Polling                    | 35  |

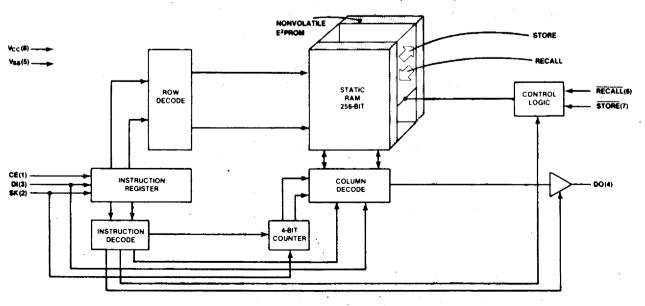

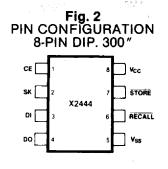

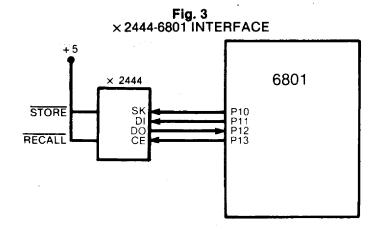

| X2443/X2444 Nonvolatile RAMs                             | 39  |

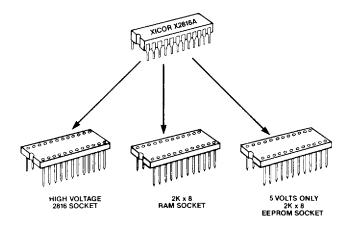

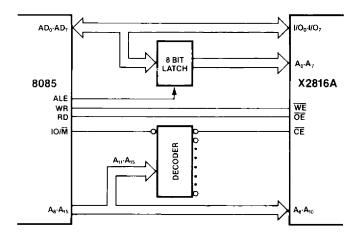

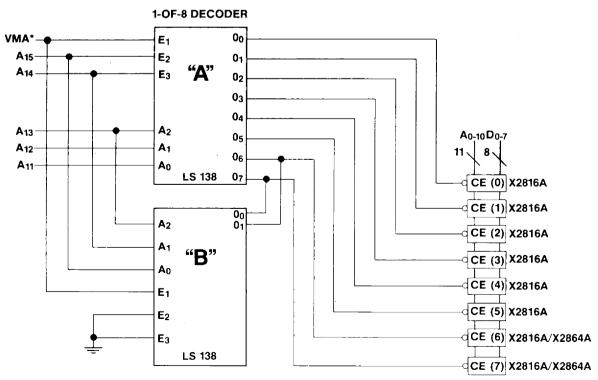

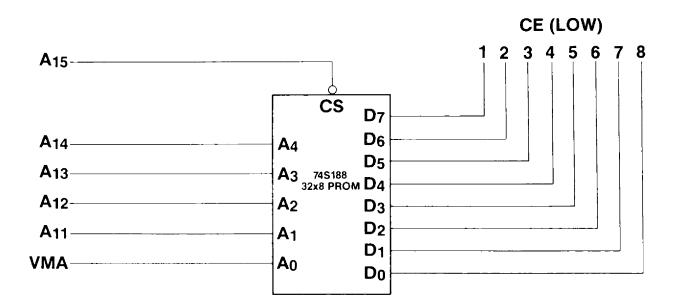

| X2816A Design Allows Upgrade To X2864A and Beyond        | 43  |

|                                                          | 43  |

| Replacing DIP Switches with Nonvolatile Technology       |     |

| Ready/BUSY: A Solution Or A Limitation?                  | 51  |

| Using DATA Polling In An Interrupt Driven Environment    | 53  |

| ARTICLE REPRINTS                                         |     |

| 5-volt-only EE-PROM Mimics Static-RAM Timing             |     |

| <i>Electronics</i> , June 30, 1982                       | 57  |

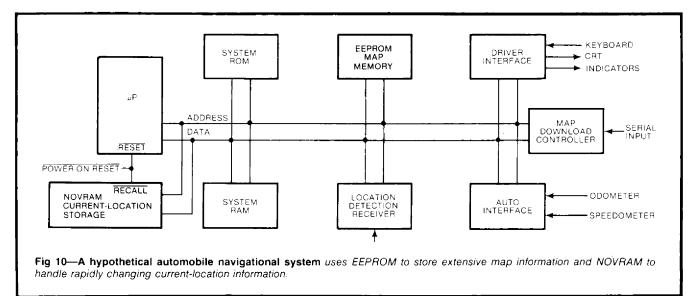

| Understand Your Application In Choosing NOVRAM, EEPROM   | 0,  |

| EDN, May 12, 1983                                        | 63  |

|                                                          | 03  |

| Non-volatile Memories Keep Appliances Out Of The Dark    | 75  |

| Design News, October 1983                                | 75  |

| RELIABILITY REPORTS                                      |     |

| RR502 NOVRAM Reliability Report                          | 81  |

| RR503 X2816A/04A Preliminary Reliability Summary         | 97  |

|                                                          | 51  |

| SALES OFFICES                                            |     |

| Distributors                                             | 111 |

| U.S. and Canadian                                        | 112 |

| International                                            | 113 |

|                                                          |     |

For data sheet specifications on Xicor products see Data Book (DB201).

·

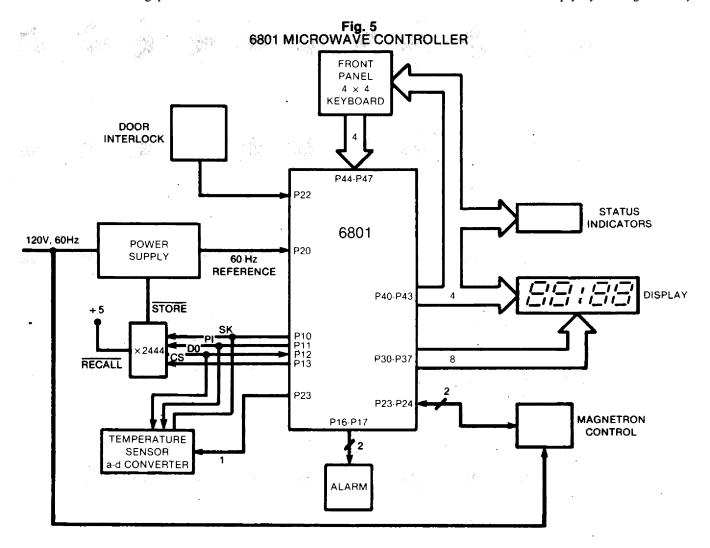

#### XICOR NOVRAM FAMILY, EASIER THAN EVER TO USE BY GEORGE LANDERS

1

#### Introduction

The purpose of this application note is to take the user through the internal operation of NOVRAMs as well as their external operation. These devices are finding their way into many diverse applications due to their ease of use. The major features of the XICOR family of NOVRAMs are 1) only 5 volts is required for all operations including programming, 2) only TTL signals are required and 3) all pulse widths are short (< 450 ns).

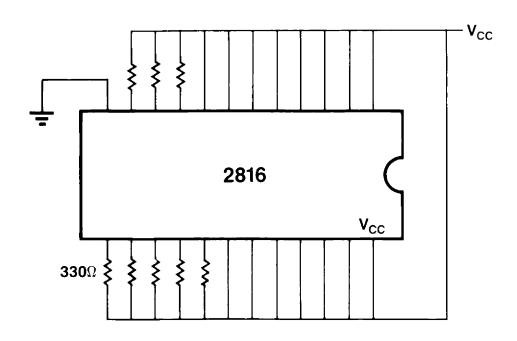

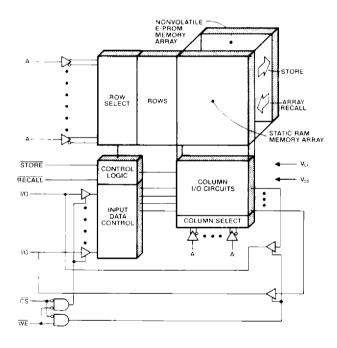

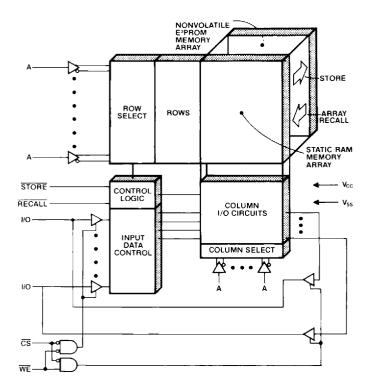

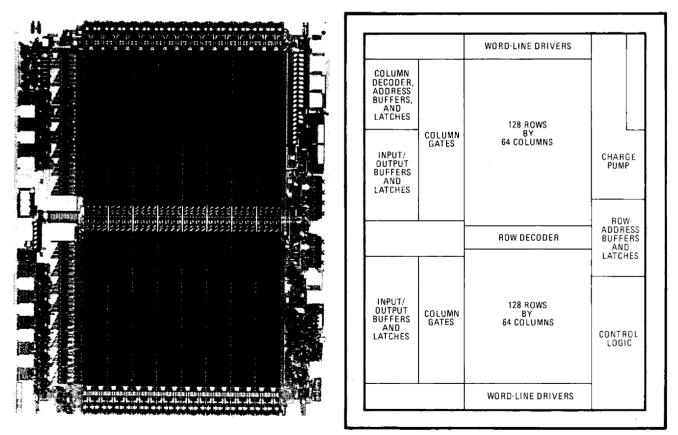

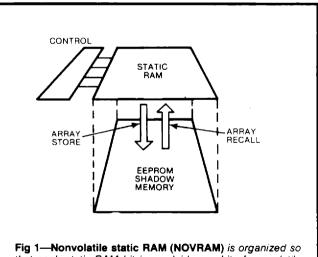

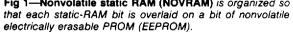

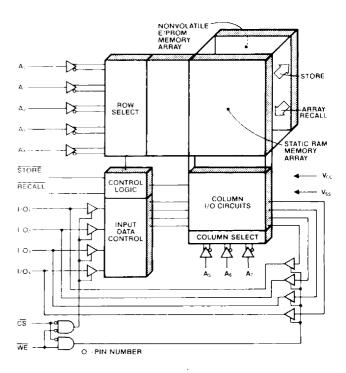

Basically a NOVRAM is a memory device that has a static RAM overlaid with an EEPROM (Electrically Erasable Programmable ROM). The operation of the RAM is identical with other popular static RAMs such as the 2102A and the 2114. Figure 1 shows the block diagram of the XICOR NOVRAM family. NOVRAMs have CS and WE pins in common with their standard static RAM cousins but also have two additional control pins: STORE and RECALL. The STORE and RECALL pins control movement of data between the RAM and the EEPROM.

Figure 1) Block diagram of the XICOR NOVRAM family.

The STORE pin is used to transfer the contents of the RAM to the EEPROM in a single operation. The entire contents of the RAM are transferred with one STORE operation. After a STORE operation is completed the original data is still in the RAM as well as the EEPROM.

The RECALL pin is used to transfer the contents of the EEPROM back to the RAM. When this is done, whatever data were in the RAM prior to the RECALL operation are totally replaced by the contents of the EEPROM. The STORE and RECALL operations function on the entire contents of the memory and not on a word by word basis. After either operation the contents of both the RAM and the EEPROM will be the same.

This may seem too good to be true; however, with XICOR's family of NOVRAMs the life of the systems designer is made even easier. Only a single five volt power supply is required for all operations including the STORE and RECALL operations. All addresses, data lines and control pins are TTL compatible and all pulse widths are short enough that most microprocessors do not require wait states. There are no high voltages or long pulse widths required which will inhibit the designer from designing a system with clean operation.

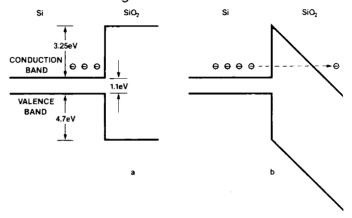

#### Technology

The XICOR NOVRAM stores its nonvolatile data during periods of power off by the absence or presence of charges on floating polysilicon gates. This is the same structure that is widely used in UV-EPROMS. The floating gate is an island of polysilicon surrounded by oxides with thicknesses of about 800 A°. Charge can be injected or removed from the floating gate by applying electric fields of sufficient strength to cause electron tunneling through the oxides. At normal field strengths the charges are permanently trapped on the floating gate even when power is removed.

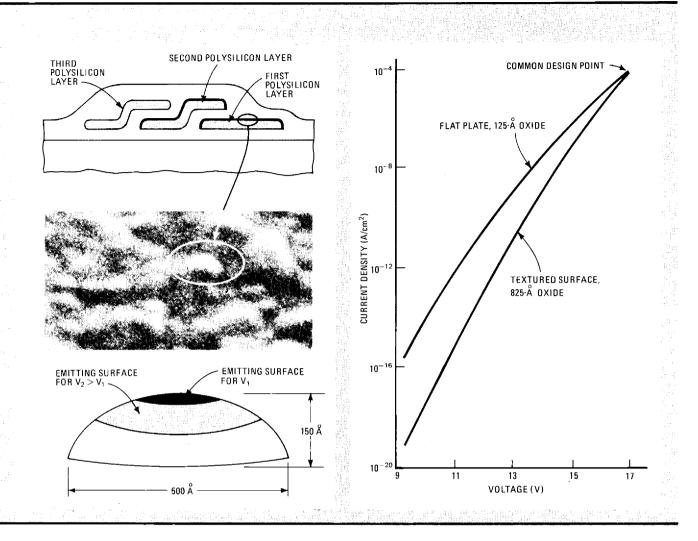

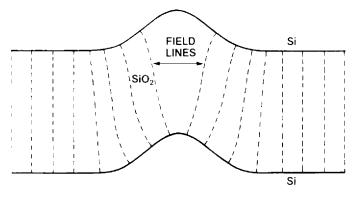

The XICOR family of NOVRAMs uses three layers of polysilicon; the second layer is the floating gate. This structure employs a phenomenon known as Fowler-Nordheim tunneling. This form of tunneling is described in Vol. 40 No. 1 (Jan. 1969, pg. 278) of the Journal of Applied Physics and Vol. 27 No. 9 (Nov. 1975, pg. 505) of the Applied Physics Letters. In XICOR NOVRAMs this tunneling is enhanced by the use of textured polysilicon surfaces to generate higher field strengths at the surface to enhance electron injection into the oxide. The alternative to field enhancement by textured surfaces is to use ultrathin oxide layers in order to conduct the charge. The use by XICOR of standard oxide thickness gives XICOR a very manufacturable product, thus ensuring its low cost and volume delivery.

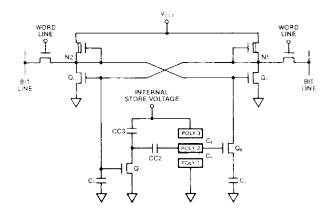

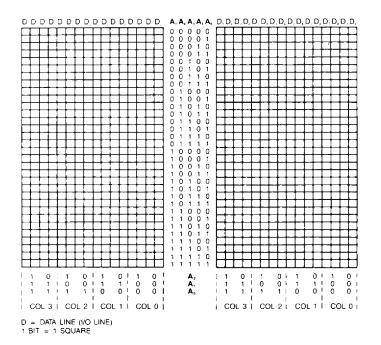

Figure 2. shows the circuit of the NOVRAM cell containing a conventional 6 transistor static RAM cell and a floating gate EEPROM cell with 2 additional transistors to control the action of data transfer. The floating gate (POLY 2) is connected to the rest of the circuit only through capacitance. Electrons are moved to the floating gate by tunneling from POLY 1 to POLY 2 and removed by tunneling from POLY 2 to POLY 3.

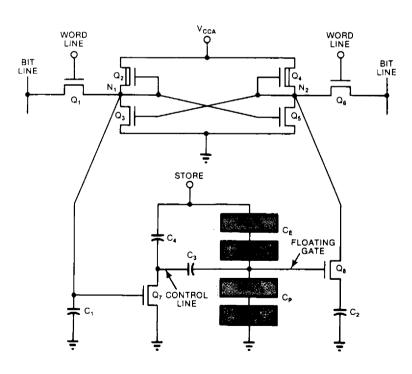

The capacitance ratios are the key to the operation of the transfer of data from RAM to EEPROM. If node

pplication Notes

N1 is LOW, transistor Q7 is turned OFF. This allows the junction between CC2 and CC3 to float. Since the combined capacitance of CC2 and CC3 are larger than CP the floating gate follows the Internal Store Voltage node. When the voltage on the floating gate is high enough electrons are tunneled from POLY 1 to POLY 2 and the floating gate is negatively charged.

Figure 2) Circuit diagram of a NOVRAM cell.

If node N1 is HIGH, transistor Q7 is turned ON which grounds the junction between CC2 and CC3. Since CC2 is larger than CE, CC2 holds the floating gate near ground when the Internal Store Voltage node is pulled HIGH. This creates a sufficient field between POLY 2 and POLY 3 to tunnel electrons away from the floating gate leaving it with a positive charge.

The RECALL operation also takes advantage of capacitance ratios. The value of C2 in Figure 2 is larger than that of C1. When the external RECALL command is received, the internal power supply, VCCA, is first pulled LOW to equalize the voltage on N1 and N2. When the internal power node is allowed to rise, the node which has the lighter loading will rise more rapidly and the gain of the flip-flop will cause it to latch HIGH and the opposite node to latch LOW. If the floating gate has a positive charge C2, is connected to N2 through Q8 and N2 will latch LOW. If the floating gate has a negative charge Q8, is turned OFF and N1 will have the heavier loading.

#### The Xicor NOVRAM Family

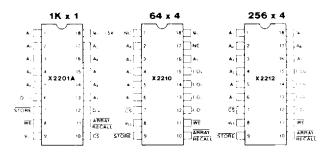

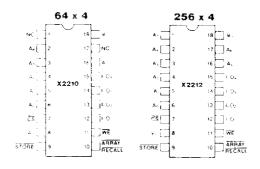

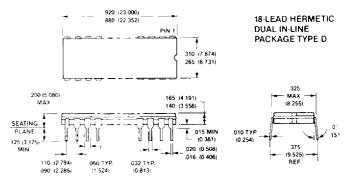

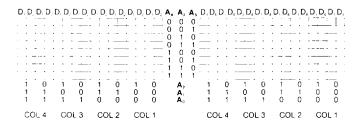

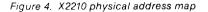

XICOR's family of NOVRAMs contains three members with identical operating characteristics. The three parts offer the designer a choice of memory organization. The X2201A, X2210 andX2212 are organized 1024 x 1, 64 x 4 and 256 x 4 respectively. All three devices are packaged in 18 pin DIPs with 300 mil centers. Figure 3 shows the pin configuration of the three different NOVRAMs.

Figure 3) Pin configuration of the XICOR NOVRAM family.

The only functional difference between the three devices is that the X2201A has separate Data I/O lines while the two 4 bit wide parts have common I/O. Additionally, the X2210 and the X2212 are pin compatible. The two unused pins on the X2210 are used for the two higher order addresses on the X2212. The control pins STORE, RECALL, CS and WE operate identically on all three parts.

#### Write Operation

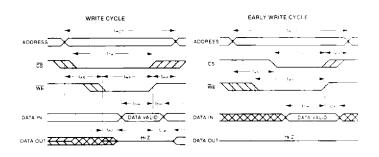

The WRITE operation is initiated by applying valid addresses followed by both CS and WE going LOW. On the 300ns version access time version, at least one of these two signals must remain HIGH until the addresses are valid. CS and WE must remain LOW simultaneously for 100ns.

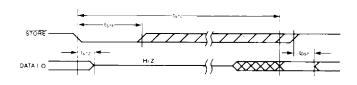

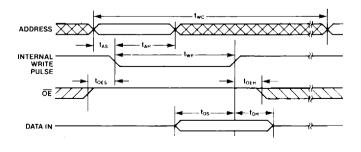

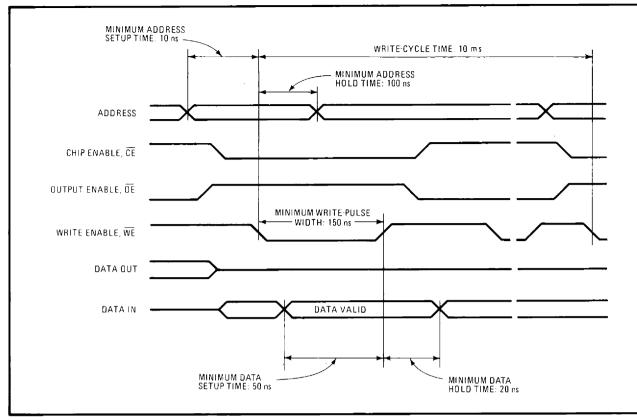

An easy way to look at this is to consider the internal write command as the simultaneous LOW of  $\overline{CS}$  and  $\overline{WE}$ . The internal write command is started by the last edge down and terminated by the first edge up. Valid addresses must overlap this internal write command. Data must be referenced to the first positive edge of  $\overline{CS}$  or  $\overline{WE}$ . The timing required for writing to the RAM is shown in Figure 4.

Figure 4) Timing diagram for Writing to the RAM.

#### **Read Operation**

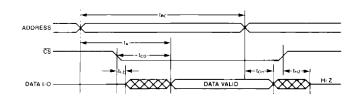

The READ operation is the easiest of the four operations performed by the NOVRAM. In the case of the 300ns access time version, data will be valid at the outputs 300ns after valid addresses or 200ns after CS goes LOW, whichever is later.

Figure 5) Timing diagram for Reading from the RAM.

#### **Store Operation**

The STORE operation is initiated by the application of an active LOW TTL pulse of 100ns or greater on the STORE pin. As long as the power supply remains within its specification for 10ms after the beginning of the STORE pulse the contents of the RAM will have been transferred to the EEPROM in total. The STORE operation cannot be terminated once initiated except by removing the power supply. This can not be counted upon to rapidly terminate the STORE operation since the user cannot determine how far the STORE operation the device has progressed. Additionally, if the power supply drops below the specification during the 10ms the integrity of the STORE operation is not assured. Figure 6 shows the timing diagram for transferring data from the RAM to the EEPROM.

Figure 6) Timing diagram for the STORE operation where data is transferred from the RAM to the EEPROM.

The STORE operation takes precedence over all other operations except the RECALL operation. If the RECALL operation has begun, any STORE command is ignored as long as the RECALL pin remains LOW. Once the STORE operation has started, taking the RECALL pin LOW has no effect and the STORE operation will be completed. If a READ or WRITE cycle is in progress when a STORE command is received, that cycle is terminated. The data in the selected RAM address during an interrupted WRITE cycle would be indeterminate.

During the 10ms of the STORE operation the NOVRAM should not be accessed for any other operation as it would not be known if the internal STORE operation was completed or not. If the internal STORE operation was completed before the 10ms and another operation command was entered, that command would be executed. However, if the internal STORE operation was not completed and another operation command was received, the later command would be ignored. During the STORE operation the outputs of the NOVRAM are in the floating state.

#### **Recall Operation**

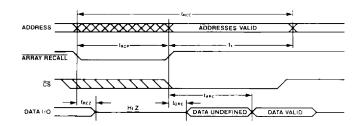

The RECALL operation is initiated by the application of an active LOW TTL pulse of 450ns or greater on the RECALL pin. The positive going edge of this pulse determines when it is possible to read data from the RAM. Valid data from the RAM can be viewed on the outputs of the NOVRAM 750ns after the rising edge of RECALL or 300ns after application of valid addresses, whichever comes latest. FIGURE 7 shows the timing requirements for transferring data from the EEPROM to the RAM.

Figure 7) Timing diagram for the RECALL operation.

The RECALL operation takes precedence over all other operations. RECALL will terminate a READ or WRITE cycle if applied in the middle of either cycle. The RECALL operation can take precedence over the STORE operation only if the RECALL command was received prior to the STORE command.

#### Hooking up the NOVRAM

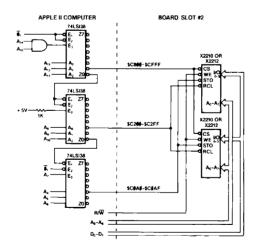

Now that the basics of the four NOVRAM operations have been described, we may discuss using these unique parts in a system. Let's first discuss a system in in which we connect the NOVRAMs to a 6502. We'll assume that the system powers up and down cleanly. The problem of systems where this does not occur will be dealt with later. The 6502 microprocessor uses memory space for I/O functions. The design uses one set of addresses for the READ and WRITE operations and other blocks of addresses to initiate the STORE and RECALL operations. An APPLE II\* computer was used as the 6502 computer because it has address space already decoded for I/O functions and convenient card slots to communicate with these decoder outputs.

The RAM was placed in the address space starting at HEX address \$C800 by connecting pin 20 on the APPLE II peripheral connector to the CS on the NOVRAM. This pin is activated when any of the 2048 bytes starting at \$C800 are accessed. Peripheral slot 2 was selected for the NOVRAM design. On slot 2 pin 41 is activated whenever the 16 bytes located at HEX address \$C0A0 are accessed. This address space is sent only to slot 2 and was tied to the STORE pin on the NOVRAM. PIN 1 also has a unique address space for slot 2 and was tied to the RECALL pin. This space is the 256 bytes starting at HEX address \$C200.

Figure 8 shows the connections of the card to be plugged into peripheral card slot 2. Reading and writing are accomplished from the BASIC programming language by PEEK and POKE instructions to HEX addresses starting at \$C800. The STORE operation is called by either a PEEK or a POKE instruction to any of the 16 addresses starting at \$C0A0. RECALL is initiated by accessing any of the 256 bytes starting at \$C200.

Figure 8) Connections for operating the NOVRAM on the I/O Bus of an APPLE II computer.

The APPLESOFT\* program in Table 1 demonstrates how a NOVRAM can be accessed easily. The statement 210 is a Write operation to HEX address \$C200 while statement 310 is a Write to HEX address \$C0A0. The  $\overline{\text{CS}}$  pin is activated with statement 430 and statement 580 respectively. This program was written for the X2210 but it could be easily modified for the X2212 or even eight X2201s.

| S TEXT : HOME<br>10 A0 = "01 WELCOME TO THE WORLD"                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S EASIEST TO USENONVOLATILE<br>STATIC RAM''"<br>O'B'S "%2 ONLY A SINGLE 5 VOLT<br>FOWER SUFFLY IS REQUIRED FOR<br>OPERATIONS"<br>SO CS = "%3 ALL INPUTS AND OUTPUT<br>E BEDUIDE ONLY TIL INFESEO                                                                                                              |

|                                                                                                                                                                                                                                                                                                               |

| E SIGNALS!!!"<br>40 F\$ = "#4 ALL TIMING SIGNALS AR<br>E MICROPROCESSORCOMPATIBLE-N                                                                                                                                                                                                                           |

| D STRECHING'"<br>50 G# = "#5 3 SIZES AVAILABLE:(X2<br>201)1024X1, (X2212)256X4                                                                                                                                                                                                                                |

| 201)1024X1, (X2212)256X4<br>.(X2210)64X4"<br>60 VTAB 5: HTAB 11: PRINT "XICOR                                                                                                                                                                                                                                 |

| 'S X2210 DEMO"<br>75 PRINT : PRINT : HTAB 51 PRINT<br>"1=RECALL":: HTAB 25: PRINT                                                                                                                                                                                                                             |

| "3=READ"<br>80 PRINT : HTAB 5: PRINT "2=STOR<br>E":: HTAB 25: PRINT "4=WRITE                                                                                                                                                                                                                                  |

| "<br>85 FRINT : HTAB 17: PRINT "5≖EX1<br>T"                                                                                                                                                                                                                                                                   |

| 90 VIAR 15, HTAR 12, INDUT FOR F                                                                                                                                                                                                                                                                              |

| CT DNC?.":A<br>100 IF A < 1 DR A 5 THEN HOME<br>I VTAB 51 HTAB 51 PRINT "ONL<br>Y 1-5 ALLOWEDTRY AGAIN"; GOTO<br>75                                                                                                                                                                                           |

| 110 ON A SOTO 200.300.400.500.60                                                                                                                                                                                                                                                                              |

| 0<br>200 REM ###########################<br>201 REM # RECALL SUBROUTINE #<br>202 REM ###################################                                                                                                                                                                                      |

| 202 REM ###################################                                                                                                                                                                                                                                                                   |

| 215 HONE ; VTAB 5; HTAB 14<br>216 PRINT "RECALL COMPLETE"<br>219 FOR I = 1 TO 1000; NEXT I<br>220 HONE ; GOTO 60<br>300 REM \$\$TORE SUBROUTINE *<br>301 REM \$\$TORE SUBROUTINE *<br>302 REM \$\$TORE SUBROUTINE *<br>302 REM \$\$TORE SUBROUTINE *<br>303 HONE ; VTAB 5; HTAB 14; PRINT<br>"STORE COMPLETE" |

| 210 FDR 1 = 1 70 1000; NEXT 1<br>220 HOME : GOTO 60                                                                                                                                                                                                                                                           |

| 300 REM ###################################                                                                                                                                                                                                                                                                   |

| 301 REM # STORE SUBROUTINE #<br>302 REM #########################                                                                                                                                                                                                                                             |

| 310 PUNE - 16224,9                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                               |

| 325 HOME : GOTO 60                                                                                                                                                                                                                                                                                            |

| 400 REM \$\$\$\$\$\$\$\$\$\$\$\$                                                                                                                                                                                                                                                                              |

| 400 REM \$\$\$\$*************<br>401 REM \$ READ SUBROUTINE \$<br>402 REM \$\$\$\$********                                                                                                                                                                                                                    |

| 422 HOME<br>423 VTAB 5: HTAB 12: PRINT "RESU                                                                                                                                                                                                                                                                  |

| LTS FROM RAM": PRINT : PRINT                                                                                                                                                                                                                                                                                  |

| 425 FOR I ≈ 1 TO 64<br>430 PRINT CHR\$ (PEEE: ( - 14336<br>+ I});<br>435 NEXT I                                                                                                                                                                                                                               |

| 435 NEXT I<br>440 FOR I = 1 TO 5000: NEXT I<br>445 Houme : 60TO 60<br>500 REM ***************                                                                                                                                                                                                                 |

| 500 REM **********                                                                                                                                                                                                                                                                                            |

| 501 REM # WRITE SUBROUTINE #<br>502 REM ####################                                                                                                                                                                                                                                                  |

| 505 HOME : VTAB 5: HTAB 6: PRINT<br>"PRESELECTED MESSAGES (1-5)"                                                                                                                                                                                                                                              |

| 1 PRINT : PRINT                                                                                                                                                                                                                                                                                               |

| "ENTER MESSAGE FROM KEYBOARD                                                                                                                                                                                                                                                                                  |

| SZO PRINT : PRINT : HTAB 11: INPUT<br>"SELECT ONE (1~6)?<";A                                                                                                                                                                                                                                                  |

| 525 DN A GOTO 531,532,533,534,53<br>5,540                                                                                                                                                                                                                                                                     |

| 531 Q\$ - A\$; GDTO 548<br>532 Q\$ - B\$; GDTO 548                                                                                                                                                                                                                                                            |

| 533 Q\$ = C\$: GOTO 548                                                                                                                                                                                                                                                                                       |

| 534 Q# = F#: 6010 548<br>535 Q# = G#: 6010 548                                                                                                                                                                                                                                                                |

| 540 PRINT : PRINT : HTAB 5: PRINT<br>"INPUT MESSAGE-64CHARACTERS                                                                                                                                                                                                                                              |

| MAX": INPUT Q\$<br>545 Q\$ = Q\$ + "                                                                                                                                                                                                                                                                          |

| "<br>548 HOME : VTAB 5: HTAB 12: PRINT<br>"WRITTEN INTO RAM": PRINT : PRINT                                                                                                                                                                                                                                   |

| 550 (76 = LEFTS (08.64)<br>570 For I = 1 TO 64<br>575 Z8 = MID\$ (0\$.I,1):Z = ASC                                                                                                                                                                                                                            |

| (20)<br>580 POKE - 14336 + 1,2<br>582 PRINT Z0;                                                                                                                                                                                                                                                               |

| 585 NEXT I                                                                                                                                                                                                                                                                                                    |

| 590 FOR I = 1 TO 5000: NEXT I<br>595 HOME : GOTO 60<br>600 END                                                                                                                                                                                                                                                |

| 600 END                                                                                                                                                                                                                                                                                                       |

\* APPLE II and APPLESOFT are trademarks of Apple Computers.

Table 1) An APPLESOFT BASIC program for demonstrating the four operations of NOVRAMs.

#### Protection Against Inadvertent Store

The circuit described in the previous section assumes that the system is powered up and down in an orderly manner. This would mean that the microprocessor would never generate addresses unless they were part of the program. Unfortunately real systems do not operate in this ideal manner. Although the circuit described above has not produced a fault during extensive testing, the possibility exists that the hex addresses \$COA0-\$COAF could come up during power up, or during a brown out when the supply dropped below the operating specification, or during a power failure.

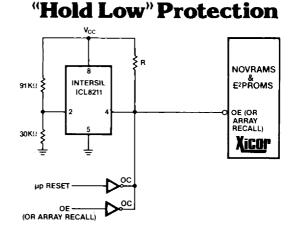

Several methods can be used to insure that the NOVRAM does not react to errors produced by the system when it is out of its operating specification. Setting the RECALL pin LOW to block a STORE operation is the easiest. Holding the STORE pin between VIH MIN and the falling power supply is another.

Most microprocessors are not totally under control for the first few cycles after power up. Their early addresses depend on what is in the registers after the System Reset pulse terminates. There is a possibility that these registers can cause one of the early addresses to be the same selected for a STORE operation. In this case the circuit shown in Figure 8 could cause the EEPROM to be written with false data during the power up operation. Figure 8 allows the STORE operation to be initiated if any of 16 addresses is selected for either a read or a write.

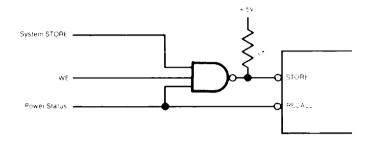

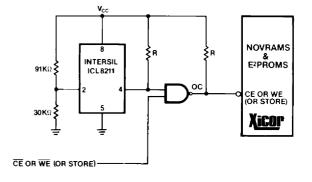

Although microprocessors can put out uncontrolled addresses they do not put out uncontrolled write commands. By ANDing the System Write line with the System STORE command, the NOVRAM would recognize a STORE operation only on a machine write cycle.

A potential danger in the use of the above schemes is the fact that three state TTL gates are not under total control while the power supply is coming up. This could produce glitches on the STORE pin even though no Write command was received at the input of the date. A more positive way to insure that the STORE pin follows the power supply as the voltage increases is to use an open collector NAND gate with one of the inputs provided by a signal that determines power supply status (Circuitry for power supply status will be covered later in this application note). If one input of an open collector NAND gate is held LOW the output transistor is turned OFF since it can not receive base current. Pulling the output of this gate to the power supply of the NOVRAM through a pullup resistor will then insure that the output follows the power supply with no alitches.

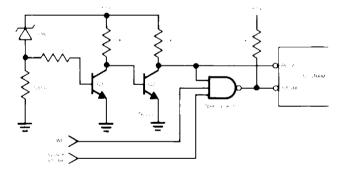

Carrying the use of a power supply status signal one step further, would be to use it to hold the RECALL pin LOW in addition to holding the STORE pin HIGH. A direct connection of this status signal to the RECALL pin is all that is necessary as shown in Figure 9. This circuit has a more positive control of the NOVRAM since it takes two actions to prevent an inadvertent STORE operation.

Figure 9) A power supply status line held LOW can insure that both the RECALL pin is held LOW and the STORE pin is held HIGH.

An example of a basic circuit to monitor the power supply status is shown in Figure 10. The output of this two-stage circuit is held LOW whenever the power supply is below 4.5 Volts. This same technique can be used with a Zener diode and an operational amplifier. The designer is cautioned to consider temperature effects.

Figure 10) The Zener power supply detector is used in combination with the open collector on the STORE pin to provide protection against an inadvertent STORE operation during power up and power down.

Another method of power supply status is to assume that the only power supply fault which requires insuring that wrong data is not stored is the loss of the AC line voltage. Many commercially available AC line fault monitors are on the market. Two of these line fault monitors are the MID 400 Power Line Monitor from General Instrument and the SG1547 from Silicon General. Additionally, many commercially available power supplies have a power fail signal either as a standard feature or as an option.

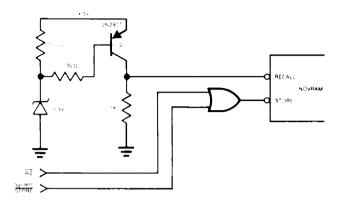

The circuit shown in Figure 11 shows another type of power supply status detector. This circuit is a low cost solution but it should be used only to take the RECALL

pin LOW because it does not provide adequate drive for a TTL gate.

Figure 11) Another form of power supply status detector to drive the RECALL pin LOW when the supply drops below 4.5Volts.

Some other schemes to protect against inadvertent STORE operations are the use of jumpers, cables and/or switches. The STORE signal is transmitted through the jumper or switch which is normally open unless it is desired to change the data in the EEPROM. During normal operation the only component attached to the STORE pin is a resistor to the power supply.

A more comprehensive discussion of power supply status circuitry can be found in XICOR's Ap Note #102. This note covers those requirements that STORE data at power failure.

#### Applications

Most microprocessor systems have need for some form of nonvolatile memory to store important data such as:

- 1) Calibration constants

- 2) Set-up configuration information

- 3) User system ID

- 4) Changeable programs/firmware

- 5) System status

- 6) Accounting information

- 7) Error conditions

The types of equipment that are today being designed to include NOVRAMs vary through the complete line of electronic equipment. Some of these systems are:

- 1) Computer peripherals/terminals etc.

- 2) Automatic tellers/transaction terminals

- 3) Point-of-sale terminals

- 4) Smart scales

- 5) Vending machines and games (i.e. arcade games, slot machines)

- 6) Meters (i.e. utilities, taxi, gas pumps)

- 7) Process control

- 8) Robots

- 9) Instruments (musical, medical, test, avionics)

- 10) Communications

- 11) Transducers/load cells

- 12) Automotive: odometers, engine control

- 13) Office equipment: copiers, word processors

- 14) Military products

Some of the competitive products being replaced by NOVRAMs in systems are:

- 1) DIP switches

- 2) Thumbwheel switches

- 3) CMOS with batteries

- 4) EAROM

- 5) EEPROM

- 6) Potentiometers

One should let his imagination soar when thinking applications for these unique NOVRAMs. XICOR is always interested in application ideas that represent both normal and off-beat uses of these NOVRAMs. Any ideas sent to XICOR will be greatly appreciated.

#### STORING DATA IN XICOR NOVRAMS DURING POWER FAILURE BY GEORGE LANDERS AND JÜRG RUDIN

Xicor

#### Introduction

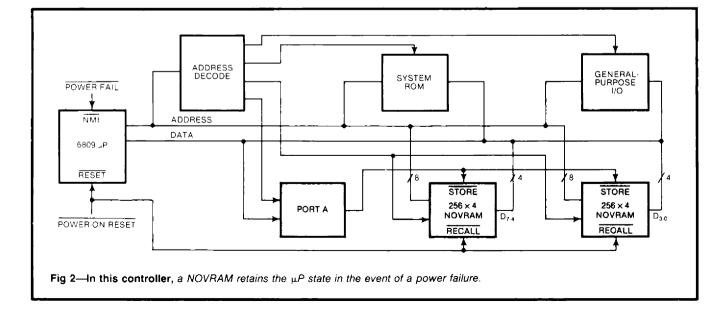

Many systems require that some data be saved at the time of a power failure. This can be a wide variety of data such as accounting information, system status, program counter or register contents, or security information. The XICOR NOVRAM family is ideal for applications of this type as a NOVRAM\* memory can save the entire contents of its RAM into an on-chip EEPROM in only 10ms and with a single 5V power supply.

This application note addresses several methods of detecting a power failure and insuring that the regulated + 5 Volts supply remains within specification for at least the 10ms required to complete the STORE operation. Various schemes of detecting the absence of ac and the decline of unregulated dc are discussed. The use of either hardware or software control is also covered. Since each system and power supply has individual requirements, it will be up to the system designer to select the circuit approach best suited to the application. None of the circuits shown are necessarily better in all cases and indeed the ideal circuit for a particular situation may not even be shown.

#### **Store Requirements**

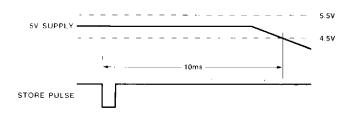

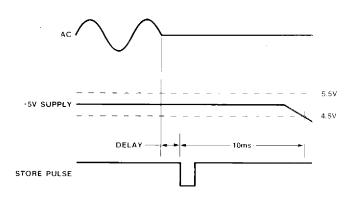

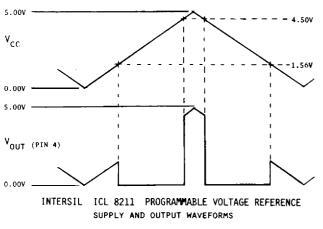

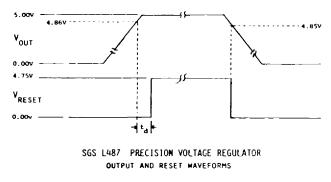

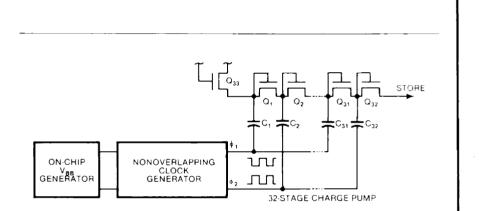

The requirements to save data in the NOVRAM memory are very straightforward. It is only required that a low level TTL pulse, 100ns or greater duration, be applied to the STORE pin and the power supply remain above 4.5 Volts for 10ms after the beginning of the STORE pulse. Figure 1 shows the relationship between the STORE pulse and the +5 Volt power supply. Once the STORE operation has started it can not be terminated unless the supply drops below + 4.5V.

Figure 1) The  $\pm$  5 Volt power supply must remain above  $\pm$  4.5 Volts for 10ms after the STORE pulse starts.

During the STORE operation, the NOVRAM memory is not on the bus allowing the microprocessor to complete other tasks that may be required by the system for an orderly shutdown. The STORE operation is determined by the falling edge of the STORE pulse. If the STORE pin is held LOW, another STORE cycle will not be started. The STORE pin must be brought HIGH before another STORE operation can occur.

Since the regulated +5 Volt power supply must remain above +4.5 Volts for 10ms, some other point must be monitored for power failure. The detection of regulated dc dropping is already too late to provide an assured 10ms of at least +4.5 Volts. Two possible points to monitor for an early indication of declining power are the ac to the power supply and/or the raw or unregulated dc to the regulator itself.

Detecting the absence of ac can be performed either before or after the transformer. If it is done in front of the transformer, it is necessary that the signal be electrically decoupled from the dc portions of the system. This can be accomplished by using optoelectronic components which transmit light signals between two points with differing electrical references.

If detection is accomplished after the transformer, it needs to be isolated from the heavily filtered unregulated dc of the main power supply as the response time there is very slow. This is done by using either a separate transformer tap or two extra diodes to isolate the signal from the bridge. Figure 2 shows the relationship necessary between the ac, the +5 Volt supply and the STORE pulse.

Figure 2) Missing ac must trigger a STORE pulse at least 10ms prior to the regulated dc dropping below specification.

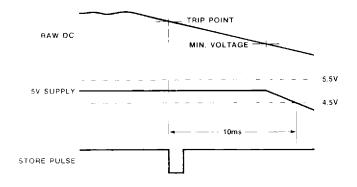

The other technique for early detection of failing power is to sense the unregulated or raw dc in front of the regulator. The regulator has a range of input voltage for which it will maintain the output within fixed limits. If a trip point is set up below the normal input voltage, a STORE signal can be sent to the NOVRAM memory with enough time to insure that the +5 Volts stays within specification for at least 10ms as shown in Figure 3.

\*NOVRAM is Xicor's nonvolatile static RAM'device

Figure 3) Falling dc is detected to trigger a STORE pulse at least 10ms before the  $\pm$  5 Volt supply drops below 4.5 Volts.

#### AC Power Failure Detect Circuits

It is possible to detect the loss of ac power with some very simple circuits. Four differing approaches are discussed in this section. These include a simple transistor zero crossing detector, two optoelectronic detectors and a CMOS Schmitt trigger method.

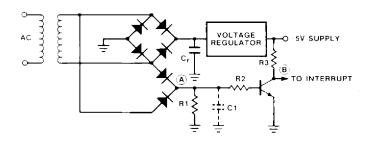

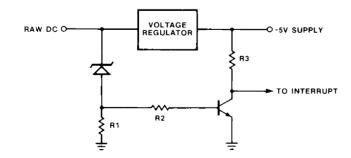

The circuit shown in Figure 4 is a low cost technique for detecting the loss of ac. It uses two diodes to isolate the circuit from the filter capacitor in front of the regulator. The resistor R2 is selected to limit the base current of Q1 and is dependent on the value of the ac signal.

Figure 4) A circuit to detect the absence of ac.

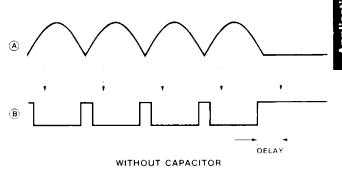

When the full wave rectified ac drops toward zero, the transistor Q1 loses base current and the output goes HIGH. If the capacitor is not used, the circuit produces a short HIGH pulse every 8.3ms. This signal is then used to interupt the microprocessor. Since the ac has probably not been lost, the microprocessor starts a subroutine to determine if this is a true power loss event. This subroutine produces a short delay (2ms) and looks at the detector again. If the output of the detector is still HIGH the power loss is real and the microprocessor issues to the NOVRAM memory a STORE pulse. The waveform produced by the circuit without the capacitor is shown in Figure 5.

Figure 5) Waveforms in the circuit of Figure 4 without the capacitor. The microprocessor is interupted every 8.3ms and must check 2ms later to determine if the power loss is real.

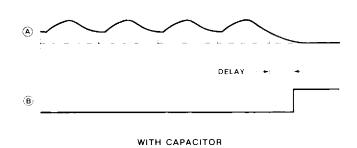

The disadvantage of using an interupt every half cycle is that the available processing time is reduced by nearly 25%. In many applications this is undesirable. A capacitor in the circuit of Figure 4 eliminates the pulses every half cycle. The value of that capacitor depends on many factors. Among these are the holdup time of the power supply, the desired delay of missing ac before triggering STORE and the values of R1 and R2. Figure 6 shows the signals under these conditions. In the lab circuit the values were R1 = 33K Ohms, R2 = 10K Ohms, C1 = .1 microfarad and a full wave rectified ac of 20 volts peak. This combination produced a delay of 2ms from the time that a half cycle was missing.

Figure 6) A capacitor in the circuit of Figure 4 fills in the valley in the rectified ac to produce a pulse only when ac disappears.

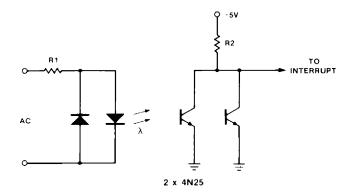

Care should be taken to insure that the timerise of the output of any detector circuit is fast enough for the microprocessor. Extra logic gates can be used to improve the timerise. An approach that allows direct connection to the ac power line is shown in Figure 7. In this circuit the ac line is connected through a resistor to two optoelectronic isolators connected with their diodes back to back.

Figure 7) Two optoelectronic isolators are connected with their diodes back to back to provide an interupt signal.

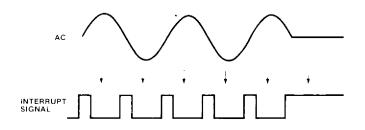

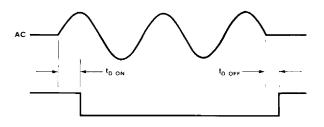

This circuit produces a positive pulse each time that ac line has a zero crossing as shown in Figure 8.

Figure 8) The circuit of Figure 7 produces positive pulses every 8.3ms until ac power failure and then remains HIGH until the dc decays.

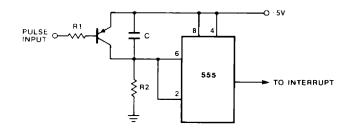

This circuit is similar to the one in Figure 4 in that it produces an interupt every 8.3 ms. This ties up the microprocessor during the delay time when the output of the detector must be resampled. In addition to the method of adding a capacitor to the circuit in Figure 4, a missing pulse detector similar to that shown in Figure 9 can be used.

Figure 9) A 555 timer connected as a missing pulse detector.

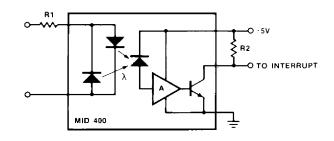

Another circuit for connecting directly to the ac power line is shown in Figure 10. This circuit uses the MID400 from General Instruments. It requires only two resistors to provide a clean interupt signal.

Figure 10) The MID400 requires only two resistors to connect directly to the ac power line.

The waveforms are shown in Figure 11. The turn on and turn off delays can be adjusted with a capacitor. (see the G.I. data sheet for details)

Figure 11) Waveforms for the MID400.

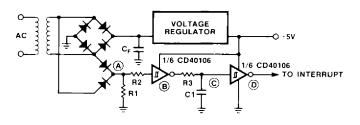

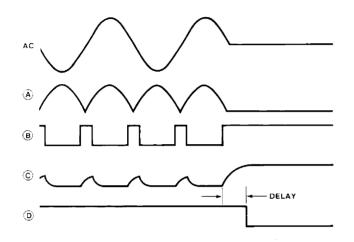

The last ac detect circuit to be discussed uses a CMOS Schmitt Trigger as both a full wave ac low voltage detector and a missing pulse detector. This circuit is shown in Figure 12.

Figure 12) Two CMOS Schmitt Triggers are used to detect the absence of ac.

Care should be taken to insure that the input voltage of the CMOS Schmitt Triggers does not exceed the 5 Volt power supply. If this occurs, the possibility of latchup exists which can be destructive to the CMOS cir-

Application Notes

cuits. A resistor in series between the bridge and R1 will limit the input voltage.

The ac input voltage should be as high as possible to provide narrow pulsewidths out of the first gate. The values of R3 and C1 determine the delay from the output. The waveforms can be seen in Figure 13.

Figure 13) The delay established by R3 and C1 must be longer than the pulsewidth out of the first gate.

#### DC Power Failure Detect Circuits

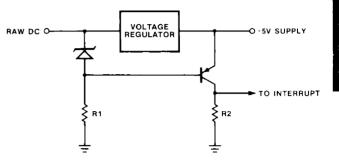

Detecting the decline of the raw dc does not involve missing pulses or capacitor delays. The first circuit shown in Figure 14 uses a Zener diode to set a trigger point. This trigger point should be as high as possible without being high enough for the normal range of unregulated dc to trip it. The value of the diode should be selected to be equal to the trip point desired minus .7 volts for the base-emitter drop.

Figure 14) A Zener diode in series with a base-emitter diode establishes the trip point of this dc detector.

A PNP transistor can be used as shown in Figure 15. In this circuit the value of the Zener diode is the

desired trip point minus 5 Volts plus .7 Volts for the base-emitter drop.

Figure 15) A dropping unregulated dc turns on the PNP transistor.

Care should be used with these last two circuits to insure that all tolerances and temperature coefficients have been considered.

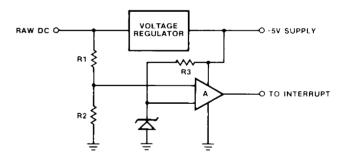

The last circuit that will be discussed in this application note uses an operational amplifier and a Zener diode with some resistors as shown in Figure 16. The circuit trips when the raw dc drops the junction of R1 and R2 to the value of the Zener diode. This circuit can provide either a positive or negative interupt signal depending on the connection of the two amplifier inputs.

Figure 16) R1 and R2 with the Zener diode determine the trip point of this circuit.

#### **Notes On Filter Capacitors**

The value of the filter capacitor on the unregulated dc to ground should be high enough to ensure that the regulator remains in regulation for at least 10ms after the STORE pulse has been sent. This is dependent on the value of the trip point, the lowest input voltage to the regulator and the load. For an example consider a system with a 300mA load, a 15 Volt trip point and a 7 Volt lowest regulation voltage. Using the I = CdV/dT equation we have:  $C = 300 \times (10/8) \times 10^{-6} = 375$ microfarads.

#### **Notes On Software**

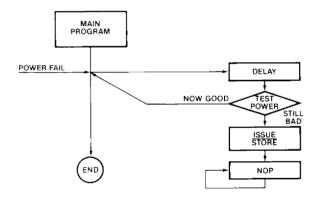

When using a microprocessor interupt to issue the STORE command, the program should branch to a STORE subroutine. This subroutine contains a short delay followed by a test of the power supply detector to insure that the power failure is valid. This can be seen in Figure 17.

Figure 17: The program branches to a STORE subroutine when a power failure is detected.

**Note:** The exact values of components in the preceding drawings depend on system conditions such as secondary AC voltage and power supply hold-up time.

Some lab values for the drawings to use as starting points are as follows:

Figure 7.  $R_1 = 12k\Omega$ ,  $R_2 = 2k\Omega$ , AC = 120V

Figure 9.  $R_1 = 5k\Omega$ ,  $R_2 = 3.3k\Omega$ ,  $C = 1\mu$ F, Time delay = 2msec Figure 10.  $R_1 = 22k\Omega$ ,  $R_2 = 2k\Omega$ , AC = 120V

*Figure 12.*  $R_1 = 20k\Omega$ ,  $R_2 = 20k\Omega$ ,  $R_3 = 10k\Omega$ ,  $C_1 = .2\mu F$ .

Rectified AC = 20V, Time Delay = 2msec

Figure 14. Zener = 10V,  $R_1 = 1k\Omega$ ,  $R_2 = 2k\Omega$ ,  $R_3 = 2k\Omega$ . Trip Point = 10.7V

Figure 15. Zener = 10V,  $R_1 = 2k\Omega$ ,  $R_2 = 2k\Omega$ , Trip Point = 14.3V Figure 16. Zener = 3.3V,  $R_1 = 20k\Omega$ ,  $R_2 = 6k\Omega$ ,  $R_3 = 2k\Omega$ , Trip Point = 14.3V

#### XICOR REPLACES DIP SWITCHES AND TRIMMERS WITH NOVRAM MEMORIES BY GEORGE LANDERS

#### Introduction

The desire to replace mechanical components in electronic systems for purposes of increased reliability, lower costs and ease of maintainability has spread to DIP switches and trimming potentiometers or trimmers. The component that makes this replacement possible is the NOVRAM memory from Xicor. The NOVRAM memory is a device that has two memories in parallel, a standard static RAM and a nonvolatile electrically erasable programmable read only memory (EEPROM). The EEPROM portion of the NOVRAM memory holds data that is equivalent to the settings of the now obsolete DIP switches and trimmers.

## What Is A NOVRAM Memory?

A NOVRAM memory, as stated previously, is two memories in a single unit. The standard static RAM has a nonvolatile EEPROM cell associated with each RAM cell. Figure 1 shows a block diagram of a typical NOVRAM memory.

Figure 1) NOVRAM memory block diagram.

There are two additional pins on a NOVRAM memory device that do not appear on an ordinary static RAM. These two pins are called STORE and

RECALL. The STORE pin is used to transfer the entire contents of the RAM to the EEPROM as a single block. This operation is performed in parallel. The RECALL pin is used to transfer the entire contents of the EEPROM back to the RAM. At the end of either operation, the contents of the two memories are identical.

Access to the EEPROM data is through the RAM portion. To alter the contents of the EEPROM, the data must first be written into the RAM and then transferred to the EEPROM with a Store operation. To use the contents of the EEPROM in the system, perform a Recall operation and then the contents of the RAM may be read. Once data is stored in the EEPROM, the RAM can be used as an entirely separate and independent memory. Some users put configuration data into the EEPROM and then use the RAM as a separate scratchpad.

Besides these operational features, the NOVRAM memory has some unique electrical features. These devices are the world's easiest-to-use nonvolatile components in that they operate with only a single 5-volt power supply, simple TTL level pulses and short pulse widths (<450 ns). Even for operations such as the Store operation, which takes 10 ms to complete, it only requires a low level TTL pulse of 100 ns or greater to initiate. During the remaining time, the NOVRAM memory is not on the bus, which frees the microprocessor and the bus for other tasks. Complete details of the operation of NOVRAM memories can be found in the individual data sheets and application note AN101.

#### Replacing DIP Switches With NOVRAM Memories

DIP switches and thumbwheel switches have been used in systems to provide alterable, nonvolatile data. Some uses of this data are to set up configuration parameters and to provide calibration constants. The apparent low cost of these components is one of their attractive features. The drawback is that costs of these components do not end with installation.

The biggest cost of these mechanical, nonvolatile components is in post-installation service. A simple change of a DIP switch setting can require a technician to visit the equipment, disassemble the unit, throw the switch and reassemble the equipment. This could easily run the total use costs to well over 10 times the installed cost. A solution to the problems presented by DIP switches is to use a NOVRAM memory to hold valuable configuration or calibration data. In addition to a lower-cost, easier, and more secure method of changing data, NOVRAM memories cost less at the installed level.

The disadvantages of using DIP switches in modern electronic systems accumulate through each step of the manufacturing process. The first stage of NOVRAM memory advantages starts right at system concept and design. Since the density of NOVRAM memories is significantly greater (up to 1024 switches in a single low-cost DIP package), more functional options can be added to enhance the total value of the system. Features such as electronic unit type signature can be added for a small software cost, with no extra components. No special access needs to be provided to change the NOVRAM memory, as all changes can be made from a keyboard or over phone lines. This can not be said for DIP switches, which require disassembly or special doors or hatches to provide access.

At incoming inspection it is difficult to completely test a package of DIP switches for all possible combinations, or even as individual switches. The NOVRAM memory, on the other hand is tested by automatic test equipment both quickly and thoroughly. The NOVRAM memories are 100% tested by Xicor and can be further tested at whatever levels the user desires, including the quick testing of all the options that were designed into the equipment. In the case of the DIP switch, this would require manually setting each option, rather than have the final system test equipment take care of the task.

The assembly operation is made more difficult when trying to wave solder or clean a board containing DIP switches. These operations can cause contamination in the degreasing step. This is true, even on the components that have tape or other cover for protection, as these are extra items to handle or become lost. Again, the NOVRAM memory exhibits none of these problems in that they are in sealed packages like the rest of the semiconductor components that make up the bulk of the system.

Once the system is in the field, the advantages of the NOVRAM memory are further enhanced. The basic reliability improvement of semiconductors over mechanical components is well known. Equipment warranties can be enforced since there is no need for a customer to open the equipment. The greatest advantage of all comes in service. No longer is it necessary for a technician to travel to the users site to change the setting on DIP switches as this can be accomplished over a phone hookup.

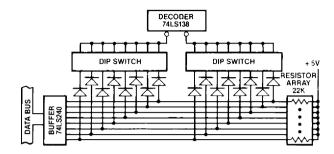

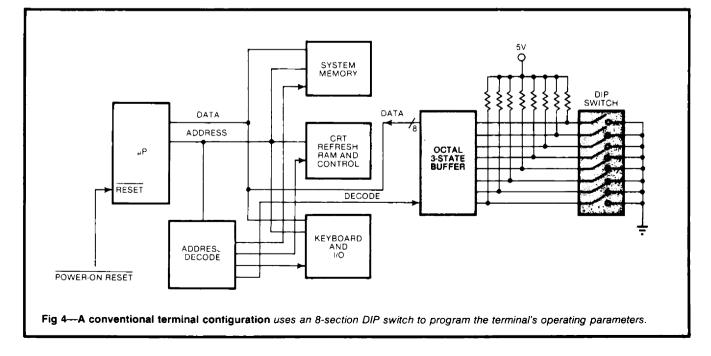

In addition to all of the above cost savings and system benefits in using NOVRAM memories, the basic component cost is also very low. Figure 2 shows a typical interface for DIP switches in a microprocessor system. Each package of 8 switches requires a decoder port and 8 diodes to provide isolation from other switches.

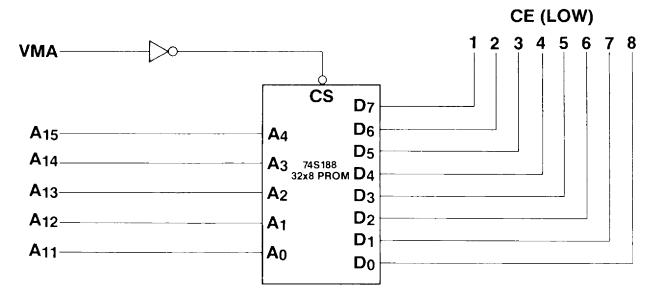

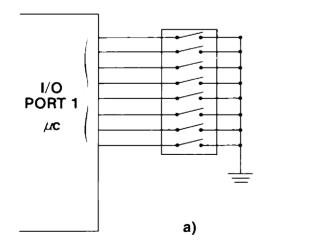

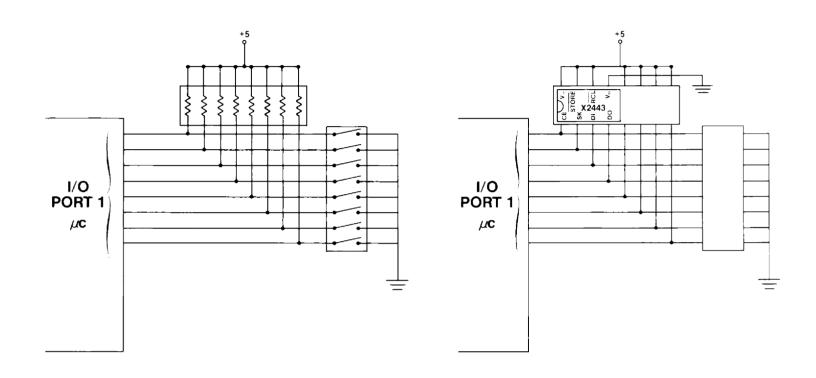

Figure 2) Typical DIP switch interface for multiple packages.

An octal buffer and 8 pull up resistors are required for any quantity of switch packages in a given system. Matrix schemes could be applied to reduce the decoder ports at the cost of more buffers but, by then, the costs will be much greater than those of using NOVRAM memories.

The assembly costs include incoming inspection, handling, inventory, board real estate, and final inspection. These costs are variable depending on volume and other factors.

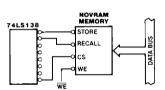

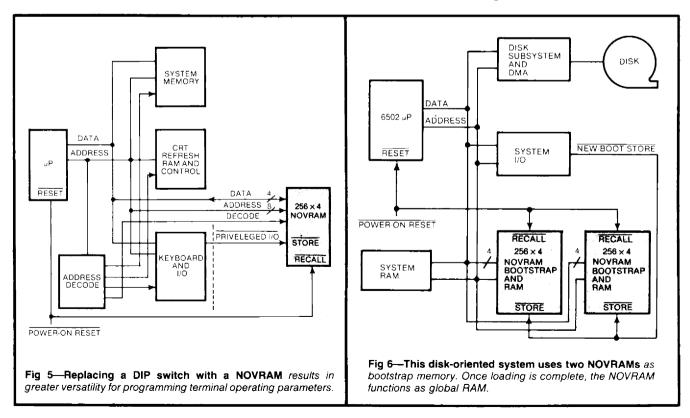

The interface of a NOVRAM memory to a microprocessor is shown in Figure 3.

Figure 3) The typical NOVRAM memory interface requires only 3 decoder ports for any number of switches up to 1024.

This setup requires 3 decoder ports for any number of switches up to 1024 and then starts adding a single port for each additional package of 256 or 1024 switches.

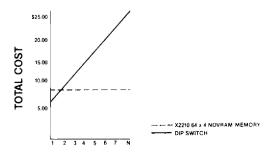

The plot in Figure 4 shows that system costs using NOVRAM memories remain constant as the equivalent packages of DIP switches required are increased. These costs include the costs of all associated components, assembly and testing.

Figure 4) Relative costs of using NOVRAM memories as opposed to DIP switches as a function of packages of 8 switches required.

The plot shows that whenever the required number of DIP switch packages of 8 switches exceeds 1, the NOVRAM approach is lower in cost at the systems level.

The cost of using DIP switches rises constantly as the number of required packages increases. An actual cost crossover occurs between 1 and 2 packages of 8 switches. Designers can derive their actual costs by calculating the two approaches based on the costs at their firm. These costs should include, in addition to the component costs, all costs associated with incoming inspection, warehousing, assembly and system tests. One will find that the crossover between 1 and 2 packages of 8 switches is consistent and favors the NOVRAM memory approach.

#### Where And Why Trimmers Are Used

The trimming potentiometer or trimmer is a 3terminal device that can be connected in many different configurations. The purpose of the trimmer in the analog circuit is to make a fine adjustment of a current or a voltage. This current or voltage is then used in analog circuits to compensate for component variations in frequency, gain, offset, voltage or current.

Like the DIP switch, the trimmer appears quite inexpensive when one considers only the purchased price. In actuality it can be one of the most expensive components on the card when the costs of field calibration are taken into consideration. It takes only one service call (considered by some to cost approximately \$200) due to a changed setting caused by vibration, humidity or even well-intentioned user tampering, to run the cost of using the trimmer to high levels. In addition, the trimmer requires equipment disassembly and the skilled use of a screwdriver. This skill adds to the cost of owning the equipment.

Taking an 'all costs considered' approach is one way manufacturers are reducing the cost of equipment ownership as a function of performance. Although the end customer wants equipment that is low in purchase price and service costs while delivering a high level of performance, they will purchase a more expensive piece of equipment if they believe that the service costs and possible downtime will be reduced.

The functions of the trimmer can be duplicated quite well by a NOVRAM memory combined with a Digitalto-Analog Converter (DAC). A DAC is a device that delivers a voltage at the output that is a function of a digital signal at the input. In a microprocessor system, this is a variable voltage source that is under the control of the program. While the DAC cannot exactly duplicate the 3 terminals of the trimmer, the circuit can be modified to provide equivalent results.

The NOVRAM memory provides settings for the DAC that are free from problems of humidity and vibration, as well as holding onto those settings during times of no power. Once the NOVRAM memory/DAC combination is in the circuit, the calibration can be made automatic by closing the loop since all mechanical adjustments are eliminated. A self-calibrating system can eliminate all expensive service calls for recalibration.

#### **Duplicating The Function** Of The Trimmer

This section will demonstrate a few simple concepts for using a NOVRAM memory and a DAC in combination to modify important circuit parameters. As previously mentioned, a trimmer adjusts small variations of frequency, gain, offset, voltage or current. By properly interfacing the output voltage of a DAC in the analog circuit, these functions can be easily duplicated.

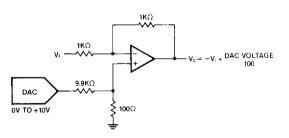

The first example shown will demonstrate how to effect a small adjustment in voltage that can be used as a reference or for some other need. Figure 5 shows an operational amplifier connected to provide a small amount of trim to the output. The 9.9k and 100 ohm resistors provide a division by 100 of the DAC output.

Figure 5) The DAC output provides up to 100 millivolts of trim for the operational amplifier output voltage.

If the DAC can be adjusted from 0 to 10 volts, this voltage divider provides an offset of up to 100 millivolts. The operational amplifier offset adds this amount to the output, providing up to 100 millivolts of reference voltage trim.

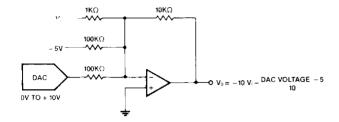

The next example will show how to provide a small offset for a fixed gain amplifier. Figure 6 shows the operational amplifier connected as an inverting amplifier with a gain of 10.

Figure 6) The DAC output provides an offset of 0.5 volt for a fixed gain amplifier.

The fixed gain is established by the 1K and 10K resistors. As the DAC output is varied from 0 through 10 volts, this voltage, combined with the -5 volts, reduces the amplifier output by 1/10 of the difference. This gives a fixed offset of up to 0.5 volt in either direction.

The third example will show a different use of a DAC to change the operational amplifier gain. This example uses a CMOS DAC with the ladder network in the amplifier feedback loop.

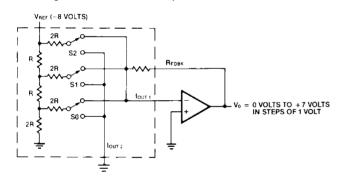

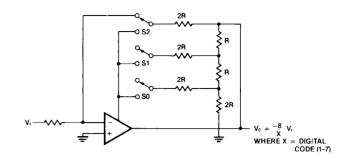

A short course in CMOS DACs is in order at this time. Figure 7 shows a simple 3-switch CMOS DAC.

Figure 7) A simplified 3-switch CMOS DAC.

The outputs of a CMOS DAC are in the form of current. The sum of the two output currents is always a constant. In the case of Figure 7, this sum is 7/8 x V<sub>REE</sub>/R. Both current outputs must look into a ground potential. In Figure 7 the lour1 pin is tied to the summing junction of an operational amplifier while the loute pin is tied to system ground. The internally provided feedback resistor should be used with an amplifier since its temperature coefficient is identical to the other resistors on the DAC chip. The DAC switches are operated by standard 5 volt logic levels. The amplifier output in Figure 7 will vary from 0 to 7 volts in 1 volt increments depending on the setting of switches S0, S1 and S2. These switches in the 'up' position add 1. 2 and 4 volts, respectively, to the amplifier output. In the positions shown, the amplifier output is 7 volts.

Figure 8 shows the CMOS DAC of Figure 7 in a slightly different configuration.

Figure 8) A CMOS DAC used in the amplifier feedback loop to adjust the amplifier gain.

The ladder network provides the feedback to the amplifier while the internal feedback resistor is used as the input resistor. If one goes through the equations, the result for Figure 8 is VO = VI x 8/×, where × is the digital code for the switch settings from 1 to 7. The circuit gain runs from a low of  $^{8}/_{7}$  for the switches in the indicated position, to a gain of 8 when S0 is high and the other switches are low. Table 1 shows a listing of the gains obtainable.

| Ē | S2   | S1 | S0 | GAIN         |

|---|------|----|----|--------------|

|   | L    | L  | Н  | 8            |

|   | L    | н  | L  | 4            |

|   | L    | н  | н  | 2²/3         |

|   | н    | L  | L  | 2            |

|   | н    | L  | 'н | 13/5<br>11/3 |

|   | н    | н  | L  | 11/3         |

| _ | . н_ | н  | Н  | 11/2         |

Table 1) Gains of the circuit in Figure 5 as a function of the switch settings.

#### **Analog Circuit Examples**

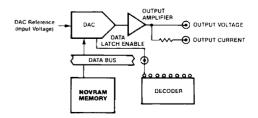

This section will present some actual circuit examples for using a NOVRAM memory combined with a DAC. The circuits that appear in this section have been built and tested. The concepts presented may be useful to stimulate ideas which will help to solve the reader's system problems and may even be of immediate use. Figure 9 shows how the NOVRAM memory/ DAC combination provides a voltage or a current for the application.

Figure 9) A NOVRAM memory DAC combination provides a voltage or a current to correct analog circuits.

It is, of course, possible for a single NOVRAM memory to provide the address setting for multiple DACs. The DAC size used is selected for the user's application, depending on the accuracy and resolution required. There are even multiple DACs available in a single package such as the SAB 3013 from Philips for more cost sensitive applications.

#### **Tuneable Crystal Oscillator**

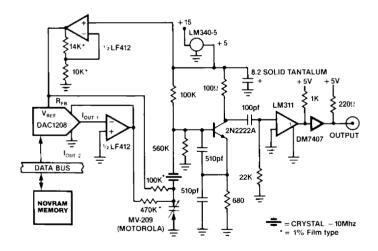

The first application example of a NOVRAM memory used in combination with a DAC is that of a quartz crystal oscillator. These circuits find application in many areas, including aviation and nautical navigation, as well as time measuring due to high stability. The oscillator is normally trimmed with a small padding capacitor in shunt or series with the crystal. This trim is used to 'pull' the resonance point of the crystal by a few parts per million (PPM) to set the operating frequency of the circuit. The capacitor may have to be adjusted in the field to retrim for the aging effects of the crystal and its associated circuitry.

The circuit in Figure 10 uses a NOVRAM memory/ DAC combination to provide the trim voltage for a varactor.

Figure 10) Tuneable crystal oscillator.

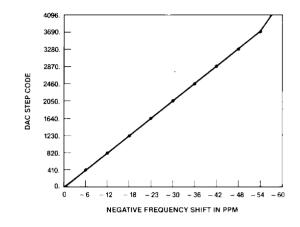

A varactor is a diode whose capacitance is a function of the applied voltage. This varactor in series with the crystal provides the actual trim function. The fixed operating point for the varactor is supplied through the 100K resistor. Variable bias for the diode is supplied by the DAC through the 470K resistor. Figure 11 shows that a 50 PPM frequency trim range is achievable with the 12-bit DAC used.

Figure 11) Tuning range of the tuneable crystal oscillator of Figure 10.

The frequency shift is down so it is recommended to specify the crystal approximately 25 PPM higher than the desired frequency. Initial trimming and re-trimming is easily accomplished by changing the DAC address settings as stored in the NOVRAM memory.

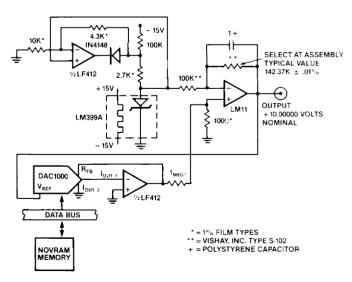

### Software Programmable Voltage Reference

Many systems (such as DVMs, test equipment. data acquisition systems and most forms of measurement and control apparatus) require a voltage reference that places a limit on total system performance. Figure 12 shows how a NOVRAM memory/DAC combination can provide a means of adjusting the ouput of a precision 10 volt reference.

Figure 12) Software programmable voltage reference.

An LM399A 6.95 volt reference is used in a bootstrap configuration to supply bias to the LF412 amplifier which in turn drives the LM399A. The 100K resistor insures start-up. The reference supplies bias to the LM11 amplifier, which supplies the circuit's output.

The NOVRAM memory/DAC-1000 combination supplies an offset voltage for the LM11 of 1 millivolt full scale in 1 microvolt increments. The 0.1  $\mu$ F capacitor insures dynamic stability and low noise at the LM11 output. To calibrate the output to within 1 microvolt, one sets the DAC to half scale and selects the feedback resistor of the LM11 until the output is within a few hundred microvolts of the desired value. Then the RAM portion of the NOVRAM memory is exercised, providing new inputs for the DAC until the desired value is achieved. This setting is then stored in the EEPROM portion of the NOVRAM memory. If a wider trim range is desired, the 1 megohm resistor can be reduced, but this degrades the setpoint resolution appropriately.

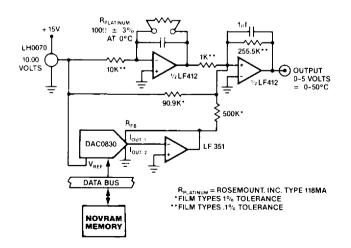

#### Self-Calibrating, Interchangeable Probe Thermometer

A standard industrial temperature sensor with high linearity and long term stability is obtained using platinum resistance temperature detectors (RTDs). The RTD is specified in terms of its resistance at 0° centigrade (as this is a function of the manufacturing process), while the gain slope is relatively constant from unit to unit. A constant gain amplifier with an offset to compensate for the changing impedance at 0° centigrade is shown in Figure 13.

The NOVRAM memory/DAC combination is used to modify the offset voltage of the amplifier to allow full interchangeability of probes in the field.

The plantinum RTD shown has a  $\pm 3\%$  tolerance at 0°C ( $\pm 7.5$ °C) and is driven with a 1 milliampere constant current source by placing it in the feedback loop of the LF412 amplifier. The constant current is provided by the 10 volt reference IC. The amplifier output will be a linear function of the sensed temperature at the RTD. The 1 µF capacitor limits noise pickup and also insures that the RTD, a wirewound device with parasitic inductance, does not cause amplifier oscillations. The second half of the LF412 provides a fixed gain to the signal.

The 90.9K resistor provides a current to the summing junction of the amplifier to move beyond the correction for the worst case sensor. The NOVRAM memory/DAC pair then pull enough current from the summing junction to correct for the inserted RTD. Over a 0°C to 55°C range, this circuit is accurate to within  $\pm 0.25$ °C while allowing the use of probes with a  $\pm 7.5$ °C tolerance specification.

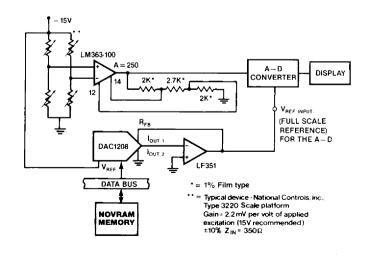

#### **Automatic Scale Calibration**

The scale normally does not worry about a zerolevel reading from its sensor, since it may have a wide variety of items on the platform such as wrapping paper or containers. An algorithm is usually required to automatically zero the scale before loading the material into the container. The transducer used in scale applications has a large variation in gain slope which must be corrected before shipping the scale or when changing the load cell. Figure 14 shows a circuit for providing these necessary corrections for the gain slope of the sensor.

Figure 13) Self-calibrating, interchangeable probe thermometer.

Figure 14) Automatic scale calibration.

The transducer shown, combined with the fixed gain amplifier, can produce outputs of 7.424 volts to 9.075 volts for full load depending on the transducer selected. To bring this result to the required value, the NOVRAM memory/DAC combination is used to vary the reference of an analog-to-digital converter. Since the DAC and the platform bridge are driven from the same supply, the measurement is ratiometric and no stable voltages are necessary. As the -15 volt supply changes, the readout on the display will not vary. To calibrate a new platform, the scale is first zeroed out using the internal algorithm and then a fixed known weight is added to the platform. Then the NOVRAM memory/DAC unit is exercised until the correct readout is obtained. This calibration can be called from the scale's keyboard. Security for this adjustment can be in a software access code which is also stored in the NOVRAM memory.

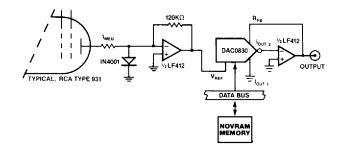

#### Gain Trimming For Photomultiplier Tube

The last example handles gain variations in a slightly different manner. The gain of a photomultiplier tube varies over time, temperature and power supply for a given input level. The output is a current from a high impedance source. A circuit to trim the changing gain is shown in Figure 15. fine resolution is to use an 8-bit DAC connected as shown in Figure 8 in place of the DAC arrangement of Figure 15. If the feedback resistor of the left-hand amplifier is changed to 50K, very fine tuning (around a voltage gain of 2) is possible. This gain of 2 is established when the DAC is set for midrange of the digital value which gives a fine tuning range.

#### Conclusion

This application note has shown how the NOVRAM memory can be used to replace commonly used mechanical components such as trimmers and DIP switches. This replacement improves reliability and reduces service costs for recalibration and resetting. In addition, actual equipment costs can be reduced.

Once a single NOVRAM memory is in the system, it is easy to include additional features in the unused portions. For example, a system designer could use a NOVRAM memory to replace DIP switches used for configuration data and then place calibration data for DACs in the unused memory. If even more unused space exists, storage of other desired data such as ID numbers or a service log would be possible.

The possible uses of NOVRAM memories are limitless. The designer is encouraged to build upon the ideas presented by this application note.

NOVRAM is a trademark of Xicor, Inc., for its nonvolatile RAM devices.

Figure 15) Gain trimming for photomultiplier tubes.

This current is converted to a voltage by the amplifier on the left side of the figure. For a full scale current of 100  $\mu$ A, the output voltage of this amplifier is 12 volts. This voltage output is used as the reference input for a NOVRAM memory/8-bit DAC combination which amplifies the reference from 1/256 through 1 depending on DAC setting. This gain can be varied in steps of 1/256. The currents out of the photomultiplier tube are normally accurate to only 1% once the calibration is complete. Some applications, however, may require smaller steps in resolution. If this is the case, one could use a 10-bit DAC. Another method of obtaining

stes

lic

P

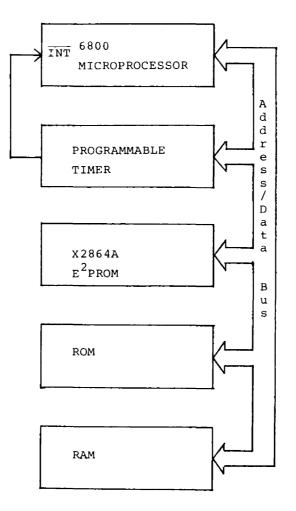

#### HE WORL **'**S D **EASIEST-**1 Ş Ε Γ **EEPROMS** A Ξ Ē **BY GEORGE LANDERS**

#### Introduction

The EEPROM has been available for several years and performs the very useful function of storing data or programs on a nonvolatile basis, while still allowing alteration of that information in the system. Many designers have wanted to use EEPROMs, but have been limited by the support circuitry needed by currently available products. With the announcement of 'The World's Easiest-To-Use EEPROM', Xicor has removed these limitations. This new product family operates with the simplicity of a standard static RAM.

Much has been said about the ease-of-use of EEPROMs. Most EEPROMs are indeed very easy to use during the read operation but, when it comes to the write operation, the term 'easy-to-use' applies only loosely. All EEPROMs introduced prior to the Xicor components described in this application note require one or more of the following during the write operation:

- 1. One or more high voltage power supplies may be required in addition to the +5 volt power supply.

- 2. A specially shaped high voltage pulse may be needed.

- 3. Addresses and data may be required for the entire write time.

- It may be necessary for data stored in an address location to be preconditioned before writing new information.

- 5. Additional timing components such as capacitors may be necessary.

The Xicor EEPROMs require none of these for operation, and exhibit the following features:

- 1. Only a single + 5 volt power supply is required for any operation including the write operation.

- 2. Only TTL level signals are required to control the part.

- 3. The write operation requires that addresses and data be stable for less than 200nsec to initiate the self controlled 10msec internal write cycle.

- The write operation accepts random data to be changed to random data with no preconditioning.

- An optional mode is available that allows the Xicor parts to plug into an existing socket for some of the older EEPROMs requiring shaped high voltage pulses.

#### The Xicor EEPROM Family

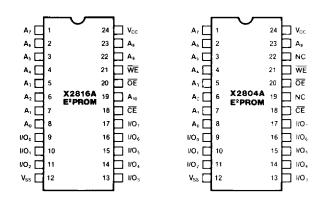

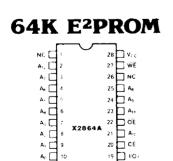

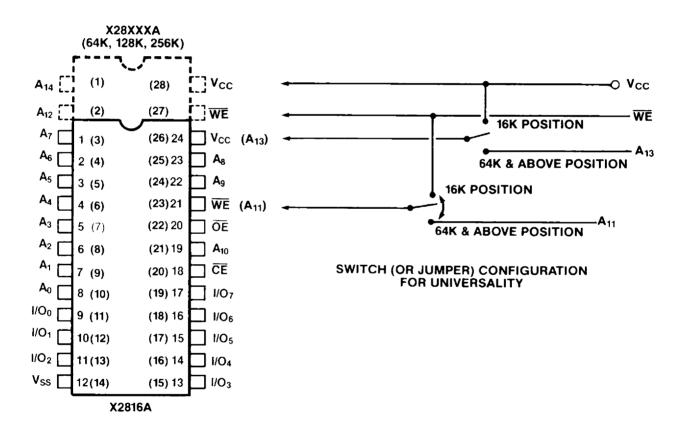

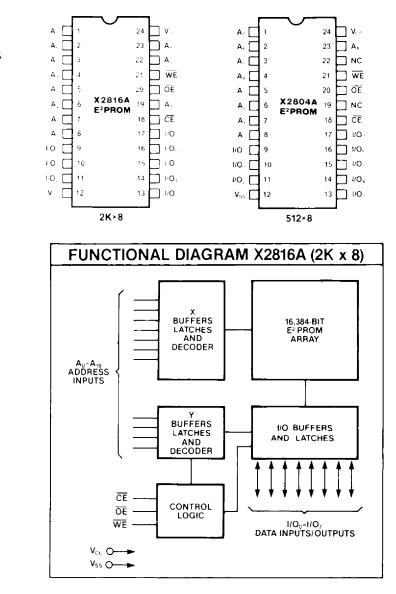

The Xicor family of EEPROMs presently consists of two pin-compatible members: the X2816A, which is organized 2048 x 8 and the X2804A, which is organized 512 x 8. Figure 1 shows the pinouts of these two components.

Figure 1) Pinouts of the Xicor family of EEPROMs.

Parts conform to the JEDEC standard pinouts for byte-wide memories. These two different chips use the same design rules. The smaller chip was designed in response to many requests for a smaller, more cost effective part for those applications requiring fewer bytes of storage.

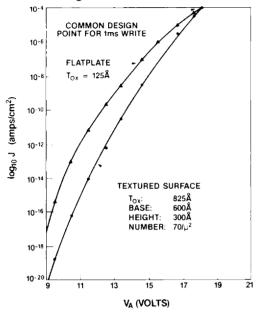

The X2816A and the X2804A are manufactured using the same proven process used in Xicor's popular 5 volt programmable NOVRAM<sup>™</sup> memories. The process is a reliable n-channel floating gate MOS technology using triple polysilicon. The method of data storage utilizes charge trapped on a floating gate, similar to the popular 2716 UV-EPROM. The charge is added and removed from the floating gate utilizing Fowler-Nordheim tunneling, enhanced by textured polysilicon surfaces. This enhancement allows fabrication with thicker oxides than other EEPROMs which don't employ textured emission surfaces. A more thorough treatment of positive reliability and data retention implications of textured surfaces is available in Xicor Reliability Report RR501.

## Operation of the Xicor EEPROMs

The X2816A will be used to demonstrate the use and features of the Xicor EEPROM family. The X2804A works identically to the X2816A and fits all those applications that require smaller segments of memory. The X2816A uses a three line control structure to ease interface requirements. These three lines are:

- CE: Chip Enable is activated (LOW) whenever it is desired to access the part for a read or a write operation. When CE is HIGH the power is reduced to a standby level.

- WE: Write Enable is activated (LOW) whenever it is desired to write new data into a byte. OE must be HIGH to allow a write to start.

OE: Output Enable is activated (LOW) whenever it is desired to read data from a byte. This eliminates all chances of data bus contention.

The mode selection chart in Figure 2 shows the required setting of the control signals to select the various modes of operation.

| CE | ŌĒ | WE | MODE                      | I/O    | POWER   |

|----|----|----|---------------------------|--------|---------|

| н  | Х  | Х  | Standby                   | High Z | Standby |

| L  | L  | н  | Read                      | Dout   | Active  |

| L  | н  | L  | Byte Write                | DIN    | Active  |

| L  | н  | н  | Read and Write<br>Inhibit | High Z | Active  |

Figure 2) Mode selection chart for the Xicor EEPROM family.

The one possible state of the inputs not shown (all three control lines LOW) is also an inhibit mode.

#### **Read Cycle**

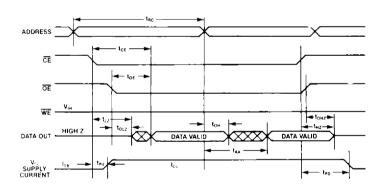

The read cycle for the X2816A is shown in Figure 3.

Figure 3) Timing diagram for the Xicor EEPROM read cycle.

This cycle is totally static. It is level sensitive and requires no clocking. Addresses must be stable for the entire read cycle. If CE and OE are both LOW, a change of address produces new data on the output buffers. The CE pin also controls the power level. When CE is HIGH, the power dissipation is at a standby level increasing to operating level only during the time that the CE pin is LOW. Most EEPROMs on the market operate in a similar manner.

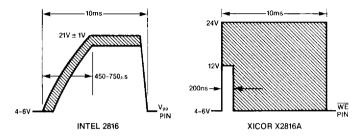

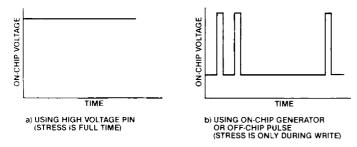

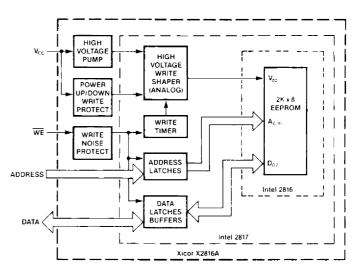

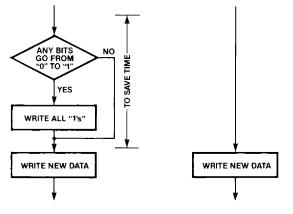

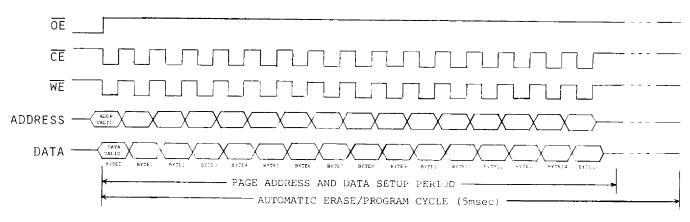

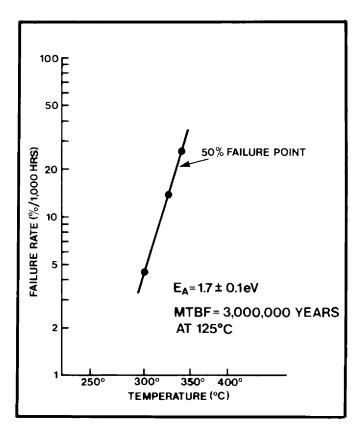

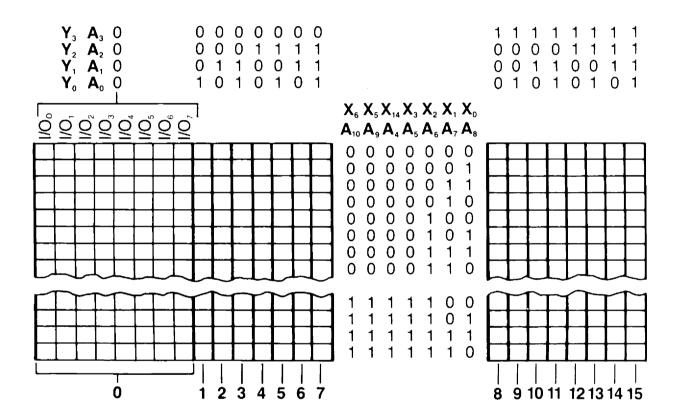

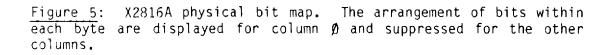

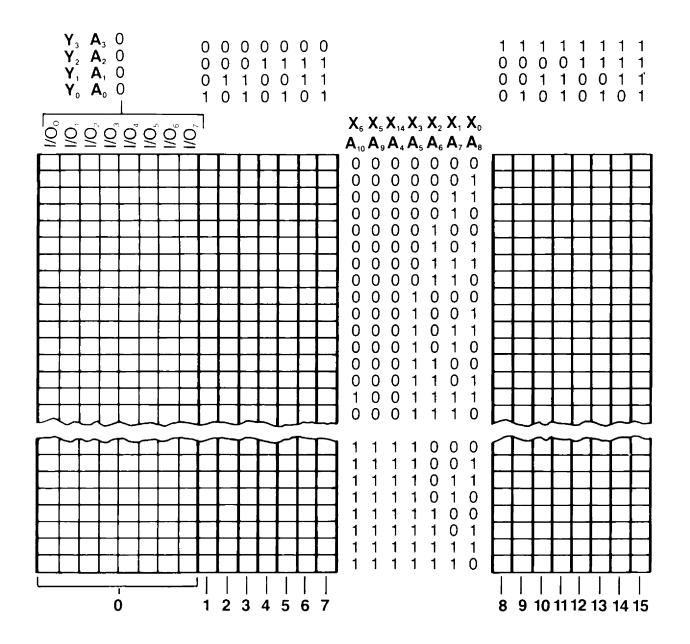

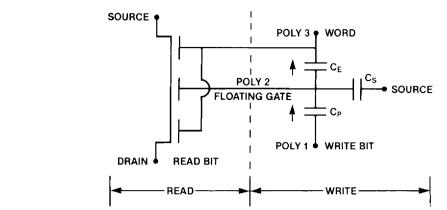

#### Write Cycle