9718228 0015082 238 WWW

WD90C56

T.52-33-49

Video Local Bus Interface

(VLBI) Device

20-0

20

| T-52- | 33-49 |

|-------|-------|

|       |       |

|         |       | TABLE OF CONTENTS                              | 1-52-55 11 |             |         |         |

|---------|-------|------------------------------------------------|------------|-------------|---------|---------|

| Section | Title | WESTERN DIG                                    | ITAL       | CORP        |         | Page    |

| 1.0     | INTR  |                                                |            |             |         | . 20-1  |

| A       | 1.1   | Document Scope                                 |            |             |         | . 20-1  |

|         | 1.2   | Reference Documents                            | ·          |             | • • •   | . 20-1  |

|         | 1.3   | Features                                       |            |             |         | . 20-1  |

| 18 M    | 1.4   | General Description                            | • • •      | • • • • • • | · · ·   | . 20-1  |

| 2.0     | ARCH  | HITECTURE                                      |            |             |         | . 20-2  |

|         | 2.1   | Functional Description                         |            |             |         | . 20-2  |

|         | 2.2   | VGA RAMDAC Color Palette Shadowing             |            |             |         |         |

|         | 2.3   | VGA Write Buffer                               |            |             |         | . 20-4  |

|         | 2.4   | VLBI Data Transfer Mode                        |            |             |         | . 20-4  |

|         |       | 2.4.1 Direct Transfer Mode                     |            |             | ·       | . 20-4  |

| · · · · | 2.5   | Laptop Support                                 |            |             |         |         |

| •       |       | 2.5.1 Suspend                                  |            |             |         |         |

|         |       | 2.5.2 Processor Power-Down and Clock St        | top        |             |         | . 20-4  |

| .*      | 2.6   | VLBI Dual Display Mode                         |            |             | • • • • | . 20-5  |

|         | 2.7   | Configuring the VLBI                           |            |             |         | . 20-6  |

|         |       | 2.7.1 Hardware Configuration                   |            |             |         | . 20-8  |

|         |       | 2.7.2 Software Configuration                   |            |             | • • •   | . 20-9  |

|         | 2.8   | Programming the VLBI Chip                      | • • • •    |             | • • • • | . 20-10 |

| 3.0     | INTE  | RFACES                                         |            |             |         | . 20-13 |

|         | 3.1   | VLBI Interface for Integrated Cache Controller | Based S    | system .    |         | . 20-13 |

|         | 3.2   | VLBI Interface with Stand-Alone Cache Contro   |            |             |         |         |

|         | 3.3   | Processor Interface                            |            | •           |         |         |

|         | 3.4   | Clock Scheme                                   |            |             |         | . 20-13 |

| 4.0     | SIGN  | AL DESCRIPTION                                 |            |             | • • •   | . 20-14 |

| 5.0     | REGI  | STER DESCRIPTION                               |            |             |         | . 20-19 |

| 6.0     | DC E  | LECTRICAL SPECIFICATIONS                       |            |             |         | . 20-21 |

|         | 6.1   | Maximum Ratings                                |            |             |         | 20-21   |

|         | 6.2   | Standard Test Conditions                       |            |             |         | . 20-21 |

|         | 6.3   | DC Characteristics                             |            |             |         |         |

| 7.0     | AC O  | PERATING CHARACTERISTICS                       |            |             |         | . 20-23 |

|         | 7.1   | Timing for 33 MHz Clock                        |            |             | • • •   | . 20-23 |

|         | 7.2   | Timing for 66 MHz Clock                        |            |             |         | . 20-25 |

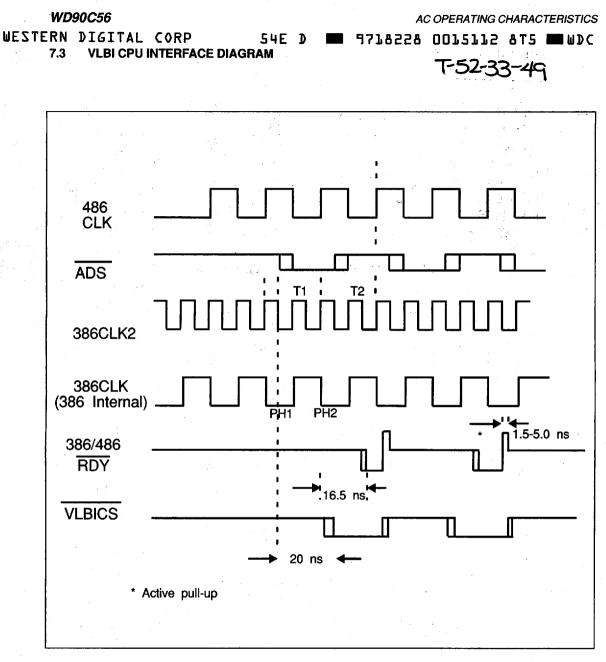

|         | 7.3   | VLBI CPU Interface Diagram                     |            |             |         | . 20-26 |

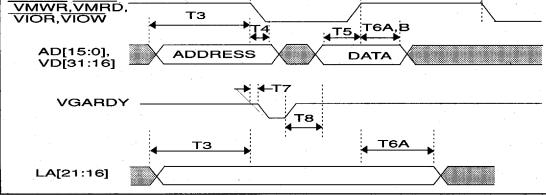

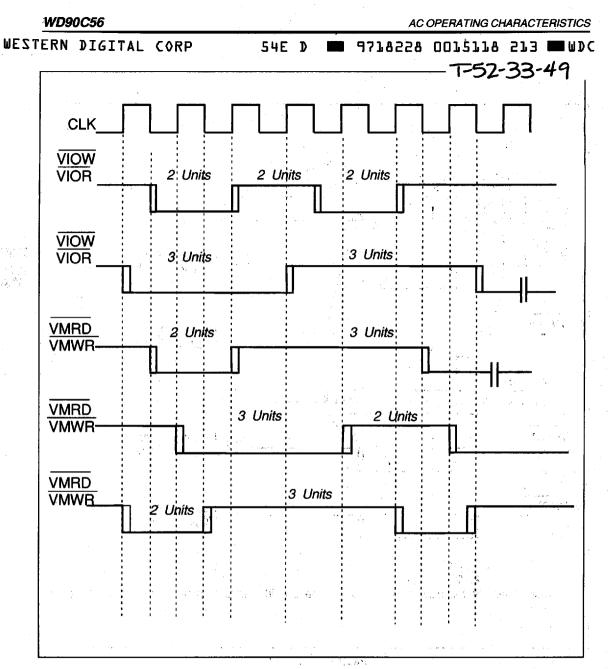

|         | 7.4   | VLBI Timing Diagrams                           | <b></b> .  |             |         | . 20-27 |

20-i

| Section     | Title |         | WESI            | TERN DIGITAL CORP T-52-33-49                                                                                                                                | Page    |

|-------------|-------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

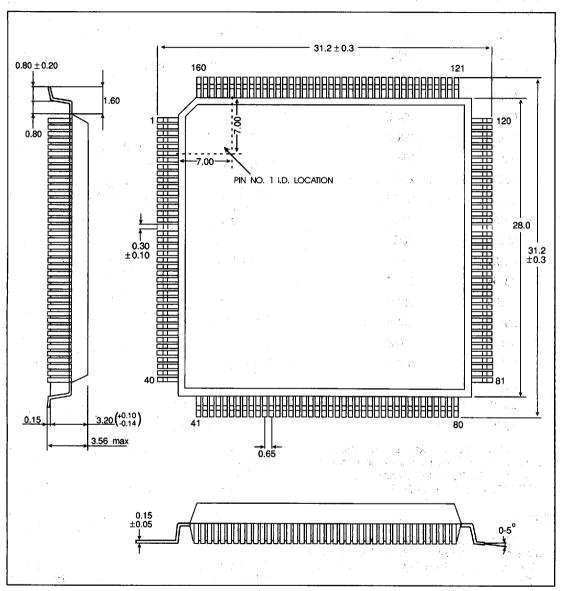

| 8.0         | PACH  |         | MENSION         | 3                                                                                                                                                           | 20-33   |

| <b>A</b> .0 | VGA   | I/O AND | MEMORY          |                                                                                                                                                             | . 20-34 |

|             | A.1   | VGA I/  | O Decoding      | ) <u>.</u>                                                                                                                                                  |         |

|             | A.2   | Sixteer | -<br>Bit I/O Re | ad or Memory Access                                                                                                                                         | . 20-34 |

|             | A.3   |         | emory Dec       | oding                                                                                                                                                       |         |

|             |       | A.3.1   | CPU Add         | Iress A19-A0 Decoding                                                                                                                                       | . 20-35 |

|             |       |         | A.3.1.1         | Case1: 3CF.0B Bits 5,4 = 01                                                                                                                                 | . 20-35 |

|             |       |         | A.3.1.2         | Case2: 3CF.0B Bits 5,4 = 10                                                                                                                                 | . 20-35 |

|             |       |         | A.3.1.3         | Case3: 3CF.0B Bits 5,4 = 11                                                                                                                                 | . 20-35 |

|             |       |         | A.3.1.4         | Case4: Decoding CPU Address A31-A20                                                                                                                         | . 20-35 |

|             | A.4   | CMD F   | ulse Width      | Programming                                                                                                                                                 | . 20-35 |

|             | ۰.    | A.4.1   | VIOW Pu         | Ilse Width Control for RAMDAC Operation                                                                                                                     | . 20-35 |

|             |       | A.4.2   | VGA Inte        | rface Timing for WD90C31 Only                                                                                                                               | . 20-36 |

|             |       | A.4.3   |                 | te Shadow VGA Registers                                                                                                                                     | . 20-36 |

|             |       | A.4.4   | VLBI and        | VGA Interface Control Registers                                                                                                                             | . 20-36 |

|             |       |         | A.4.4.1         | Register 2DF0                                                                                                                                               | . 20-36 |

| · .         |       |         | A.4.4.2         | Register 2DF1                                                                                                                                               | . 20-36 |

|             |       |         | A.4.4.3         | CPU Address A31-A20 Mapping Register                                                                                                                        | . 20-37 |

|             |       | . •     | A.4.4.4         | Memory Access Decoding Control                                                                                                                              | . 20-37 |

|             |       |         | A.4.4.5         | VIOW/VMWR Start/Finish Edge Control Register 2DF6                                                                                                           | 20-37   |

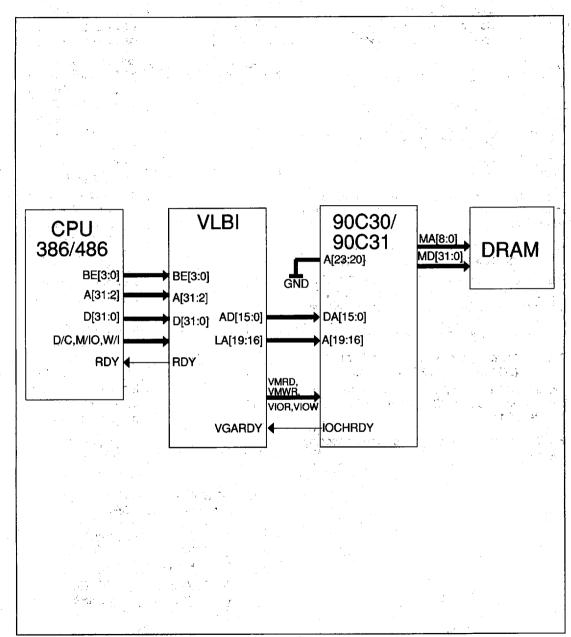

| B.0         | VLBI  | INTERF  | ACE IMPLE       | EMENTATION TO WD90C30/WD90C31                                                                                                                               | . 20-38 |

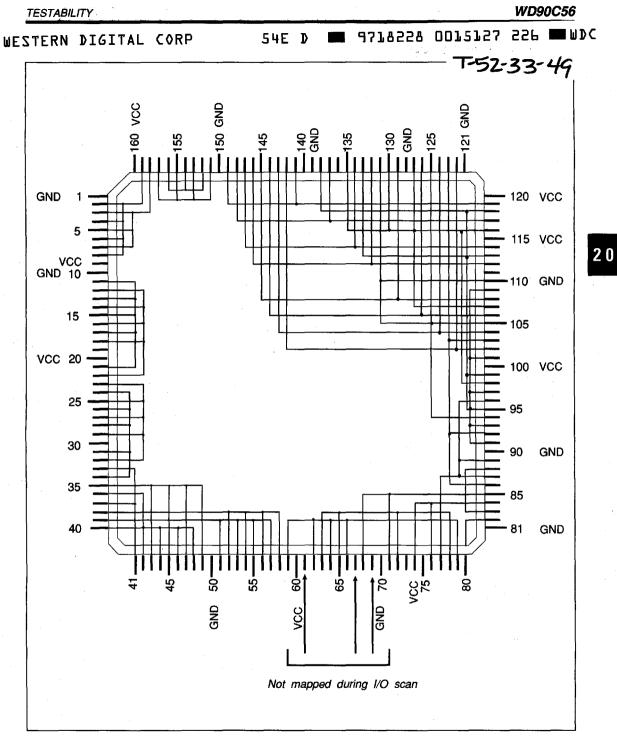

| C.0         | TEST  | ABILITY | · · · · ·       |                                                                                                                                                             | . 20-39 |

| D.0         | DEVI  |         | STORY           | n an an an Anna an Anna<br>Anna an | . 20-42 |

٩.

# T-52-33-49

| Figure | Title WESTERN                 | DIGITAL CORP                          | Page  |

|--------|-------------------------------|---------------------------------------|-------|

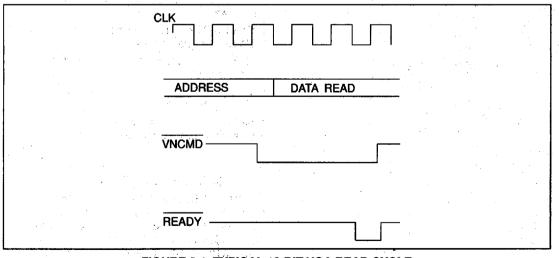

| 2-1    | Typical 16-Bit VGA Read Cycle |                                       |       |

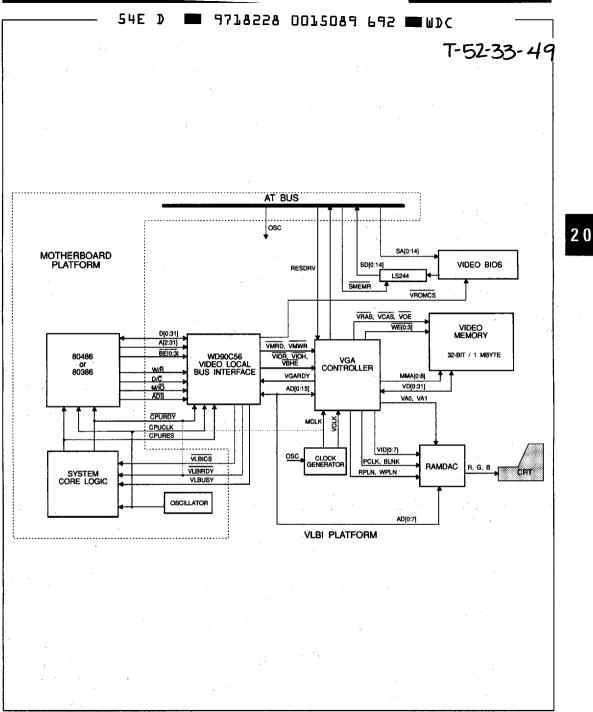

| 2-2    | VLBI System Block Diagram     |                                       | 20-3  |

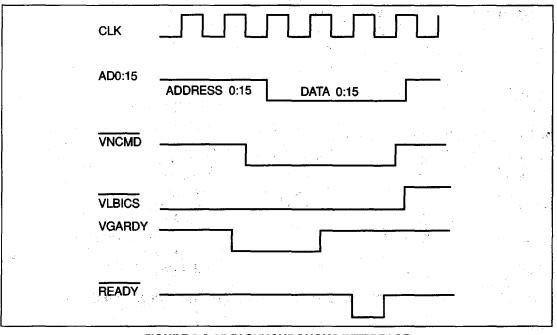

| 2-3    | VLBI Synchronous Interface    | · · · · · · · · · · · · · · · · · · · |       |

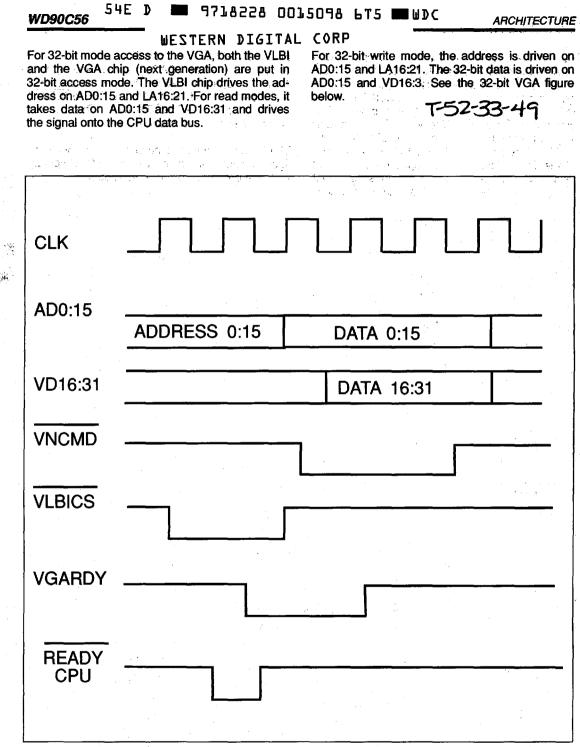

| 2-4    | 32-Bit Access to VGA          |                                       | 20-12 |

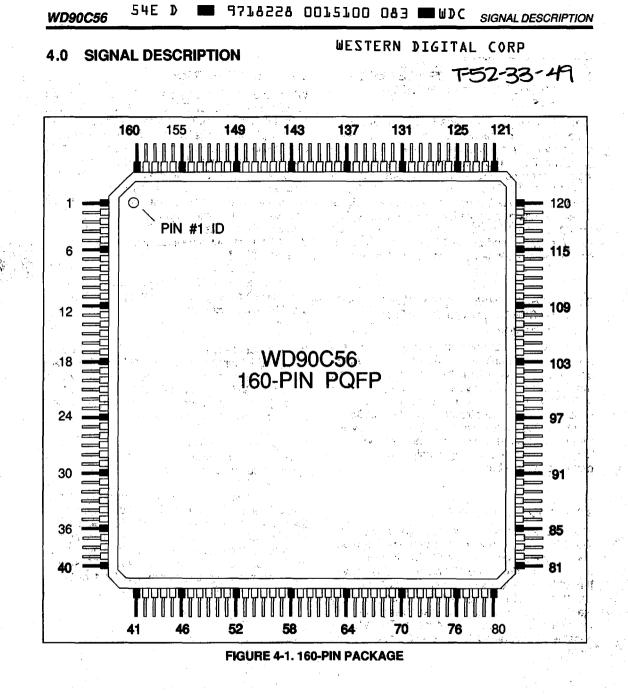

| 4-1    | 160-Pin Package               |                                       |       |

| 7-1    | VLBI CPU Interface            |                                       | 20-26 |

| 7-2    | 33 MHz Command Timing         |                                       |       |

| 7-3    | 45 MHz Command Timing         | · · · · · · · · · · · · · ·           |       |

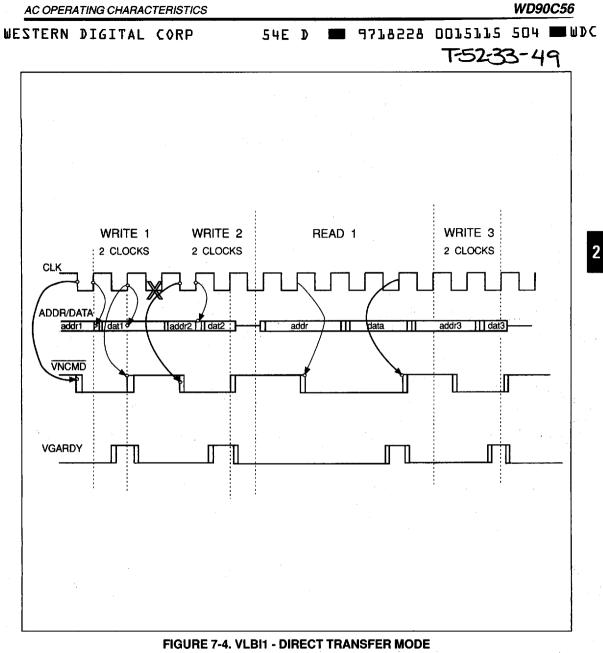

| 7-4    | VLBI1-Direct Transfer Mode    |                                       | 20-29 |

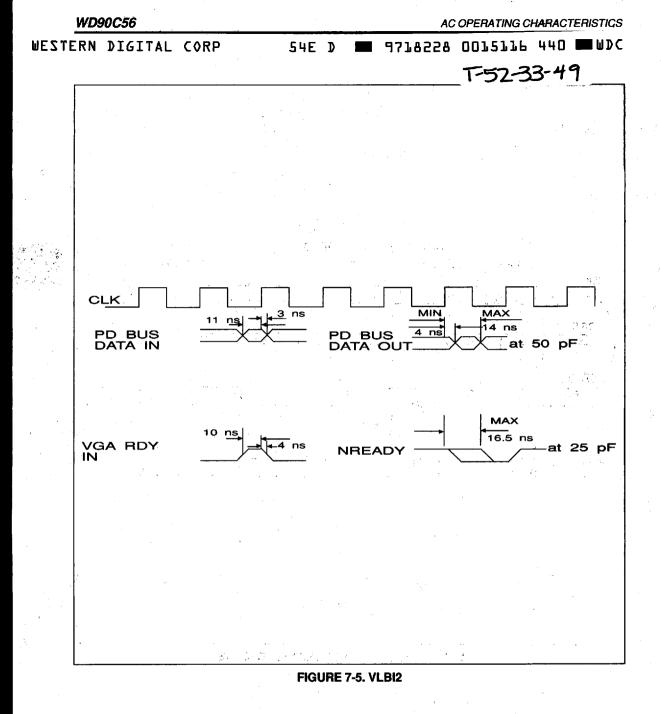

| 7-5    | VLBI2                         |                                       |       |

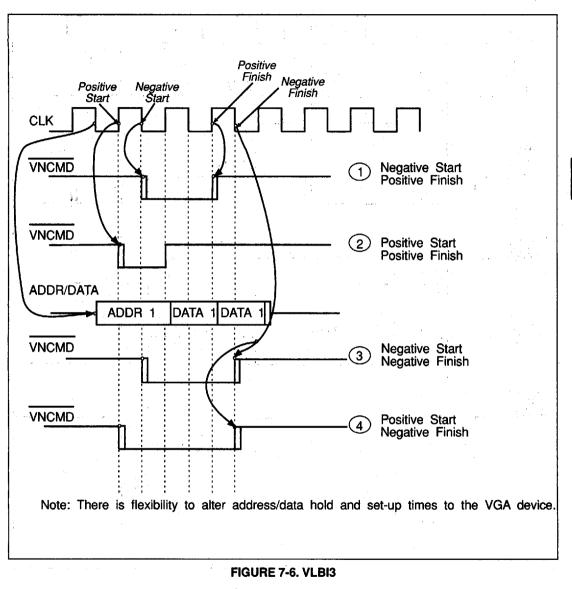

| 7-6    | VLBI3                         |                                       |       |

| 7-7    |                               |                                       |       |

| 8-1    | Package Dimensions            |                                       | 20-33 |

| B-1    | VLBI Interfaced to WD90C30/WD | DC31                                  |       |

| C-1    | WD90C56 PinScan I/O Map       | ••••••                                | 20-41 |

LIST OF ILLUSTRATIONS

# **LIST OF TABLES**

# T-52-33-49

1/2

|                       | Table | Title WESTERN DIGITAL CORP Page            |  |

|-----------------------|-------|--------------------------------------------|--|

|                       | 2-1   | Hardware Registers                         |  |

|                       | 2-2   | Configure Using Software Registers         |  |

|                       | 2-3   | Additional Software Registers to Configure |  |

| •                     | 4-1   | WD90C56 Pin Assignments                    |  |

|                       | 4-2   | Signal Description                         |  |

| ·                     | 5-1   | Register Summary                           |  |

|                       | 6-1   | DC Characteristics                         |  |

|                       | 7-1   | 33 MHz CLK                                 |  |

|                       | 7-2   | 33 MHz CLK486 Specification                |  |

|                       | 7-3   | 33 MHz VMCLK Input (CMOS)                  |  |

| $\otimes_{i=1}^{N-1}$ | 7-4   | 66 MHz CLK Specification                   |  |

|                       | 7-5   | 33 MHz Command                             |  |

|                       | 7-6   | 45 MHz Command                             |  |

|                       | C-1   | VLBI PinScan Table                         |  |

|                       |       |                                            |  |

# INTRODUCTION

# WESTERN DIGITAL CORP

#### 9718228 OO15087 81T ПЛС

# WD90C56

T-52-33

#### 54E D INTRODUCTION 1.0

#### 1:1 DOCUMENT SCOPE

This document describes the WD90C56, a single chip VLBI, Video Local Bus Interface.

In this document, the term VLBI (Video Local Bus Interface) is used as a term when referring to the WD90C56.

#### 1.2 REFERENCE DOCUMENTS

The following reference documents may be of help:

- WD90C30 Data Sheet

- WD90C31 Data Sheet

- WD90C56 Product Bulletin

#### 1.3 FEATURES

- 160 pin PQFP

- High speed local bus interface to VGA controllers

- Minimal local bus capacitive loading typically > 10 pF

- Designed to work with current integrated cache controllers (ISA, MC, and EISA bus controllers)

- · Designed to work with stand-alone cache controllers

- Supports 386SX, 386DX, and 486 microprocessors

- Supports 20, 25 and 33 MHz 486 CPU operation

- Supports 20, 25, and 33 MHz 386SX/DX operation

- · Supports WD90C30, WD90C31 and future 32-bit data bus VGA chips

- One level 32-bit write buffer

- Laptop Mode supports future Western Digital laptop VGAs

- Supports Dual RAMDACs (one on the local bus and one on the AT bus)

- Supports dual display modes (VGA and Monochrome AT card)

- VGA MEMCLK can be synchronous or asynchronous to the CPU for optimized bandwidth

- RAMDAC low and high time for IOWs 9 and 18 clocks - programmable

- RAMDAC high time for IORs 9 and 18 clocks programmable

- VIOWs, VIORs have two to five programmable clocks (low and high time)

- VMWR, VMRD have two to five clocks separately programmable low and high

#### **GENERAL DESCRIPTION** 1.4

The WD90C56 is a 160-pin device that can significantly improve VGA performance in high end PC systems. The VGA chip is directly interfaced to the 486/386 or 386SX local bus through the VLBI interface chip to achieve high-performance VGA subsystems.

WESTERN DIGITAL CORP

9718228 0015088 756 **6** WD¢ 🗧

# WD90C56 54E D

# 2.0 ARCHITECTURE

# 2.1 FUNCTIONAL DESCRIPTION

The VLBI chip monitors the CPU ADS for detecting CPU accesses to the VGA chip. If the chip detects a VGA cycle, it generates a VLBICS signal to block the core logic from generating any cycles on the system bus (AT, MC, EISA, or other bus). The VGA chip, WD90C31, uses a 16-bit multiplexed AD0:15 data address bus. The VLBI chip drives the address on AD0:15, for a read cycle and turns the AD0:15 into input mode. For IO cycles the number of wait states can be programmed into the VLBI chip. The VGA does not assert VGARDY for I/O cycles. For memory cycles to the VGA, it looks at VGARDY and extends the cycles until VGARDY is sampled high. A typical cycles on the VGA side is shown at the bottom of the page.

For a Read cycle, the VLBI stops driving the address on AD0:15 after meeting a hold time to the read command (VIOR/VMRD). For a Write cycle, the write data is driven onto AD0:15 after negation of the address. Similar to the read commands, the data is transferred on AD0:15 and sampled into the VGA chip at the rising edge of either VMWR or VIOW. For different speeds the wait states can be programmed into the VLBI chip.

The VLBI chip can interface with CPU speeds from 16 MHz 386SX to 33 MHz 386 and 486

processors. The wait states for IO access can be programmed while memory access to the VGA depends on VGARDY from the VGA as well as the chosen (programmable) parameters for command high and low durations. For 16-bit access to IO ports in VGA, the VLBI knows which ports are 8-bits and which are 16-bits and handles the byte swapping function for 8-bit ports. The VLBI chip can tell the difference between a Laptop and Desktop bus and places the data/address on the appropriate VD or AD bus.

ARCHITECTURE

T-52-33-49

#### 2.2 VGA RAMDAC COLOR PALETTE SHADOWING

The RAMDAC is also interfaced to the Local Bus through the VLBI, via lines [AD7:0] and [LA18:16]. For compatibility with 8514/A, XGA, and others, the Dual RAMDAC mode can be invoked by setting Bit 7 of 2DF7. The write cycles to the RAM-DAC registers generate both local VLBI cycles and system cycles by NOT generating VLBICS and the VLBI chip does not generate READY but waits for the core logic to run a write cycle on the system bus and then completes the cycle when a ready from the core logic is received. For read cycles, VLBICS is always generated and data is read through the VLBI interface. This guarantees that any plug-in card in the system bus can still

# FIGURE 2-1. TYPICAL 16-BIT VGA READ CYCLE

Note: The VGA commands: VIOR, VIOW, VMRD, and VMWR are collectively called VNCMD.

# WESTERN DIGITAL CORP

FIGURE 2-2. VLBI SYSTEM BLOCK DIAGRAM

ARCHITECTURE F52-33-49

see all writes to the RAMDAC and capture the data for emulation modes.

In systems where the AT bus contains write buffers the VLBUSY signal from the VLBI is used to delay the system READY signal being returned to the CPU by the write buffer logic. The READY is gated by the VLBUSY to avoid coherency problems.

# WESTERN DIGITAL CORP

# 2.3 VGA WRITE BUFFER

There is one level of 32-bit write buffer. This is the default. For 486 applications with multiple Bus Masters, there may be overruns due to insufficient time. This can be caused by a read from a CPU to the VGA when the write buffer is full. This is avoided by asserting the BOFF signal if there is a Hold request to the 486 thus making the 486 retract its last cycle. This option is disabled by setting bit 2 of 2DF6. The default is the BOFF signal asserted when the buffer is full and there is a Hold request.

#### 2.4 VLBI DATA TRANSFER MODE

#### 2.4.1 Direct Transfer Mode

The Direct Transfer mode can be invoked on either 16-bit (default) or 32-bit VGA interfaces. The 16-bit transfers are exactly like the normal 16-bit transfers on an AT bus.

In 32-bit Direct Transfer mode, there are four byte enables provided to the VGA. They are in the form of AD0/BB0, VBHE/BBE1, AD1/BBE2 and VBE3/BBE3.

In either case the protocol is the same. The VNCMD signal is asserted after the address and then the VLBI waits for the VGA RDY signal from the VGA to terminate the current cycle. The procedure is repeated again for a new cycle.

The VLBI is designed to work with 16-bit and 32bit VGAs. At power up the default is a 16-bit interface. The software changes modes by writing to registers. See Register Summary Table.

\$2.00 A.C.A.

# 2.5 LAPTOP SUPPORT

The VLBI in conjunction with the WD7710/7910 fully supports Laptop features. It also supports the full range Laptop features when interfaced to the WD86C10.

There are three special features that are supported in the WD7600/7700 family. These are as follows:

- Suspend

- Processor Power-Down

- Stop clock

#### 2.5.1 Suspend

In Suspend, the DC power is removed to all devices except the WD7600 core chip set. In this mode the VLBI's power is also removed. Prior to removal of power, the CPU interrogates the VLBI BUSY flag to ensure that the VLBI is idle before invoking suspend.

On resume, the power is restored to the VLBI along with the rest of the system. This routine is identical to the power up routine from a cold start.

For Laptop VGAs, like the WD90C26, the Data (SD 15:0) will be on the AD bus and the address (SA 15:0) will be on the VD bus. This is determined at power up on interrogation of the LA20 pin.

#### 2.5.2 Processor Power-Down and Clock Stop

In Processor Power-Down, the DC power is removed from only the processor and co-processor. The rest of the system is in quiescent mode, expending very little power. In this mode, the CPU interrogates a BUSY flag (Bit 0: @ address 2DF7). provided by the VLBI. If active, this means that the VLBI is still involved in a transfer with the VGA and that it is not ready to be put to sleep or suspended. If the BUSY flag is inactive, the VLBI is ready to be put to sleep and the CPU can do so by setting the Sleep flag in the VLBI. Once the sleep flag is set, the VLBI disables all processor interface inputs including the incoming clocks. At this stage, the VLBI awaits the assertion of the PROC PWRDN signal from the external logic. On receipt of the PROC PWRDN signal, the VLBI

20

drives the PD bus low to prevent it from floating during sleep.

On coming out of sleep, the VLBI is awakened by the negation of the PROC PWRDN signal followed by the processor interface input clocks and ultimately by the CPURES signal. At the end of this sequence, the VLBI is once again ready for more VGA transfers.

On Clock Stop, the procedure is similar except there is no assertion of the Sleep Flag or the PROC PWRDN signal. Instead, the CPU interface clock from either the WD76C10A or the WD7710 is reduced in frequency or stopped completely.

The reversal into the operating mode is completely transparent to the VLBI.

#### 2.6 VLBI DUAL DISPLAY MODE

The VLBI supports a second display adapter card, which can be either a Monochrome card (MDA), a Color Graphic Card (CGA), or another Video Graphics Array card (VGA), while residing on the local bus.

There are two read/write bits (5,6) assigned at address 2DF4 which indicate whether there is a secondary display in the system. Since, the local VLBI/VGA and secondary card share the same addresses for several I/O writes, these accesses are passed to the VLBI/VGA as well as to the system bus. The VLBUSY signal is generated in all these accesses. The system designer is responsible for assigning two independent memory areas to the VLBI/VGA and the secondary display adapter, so that the individual display memories can be independently read and written.

The following table defines the various configurations:

| WESTERN DIGITAL CORPT-52-33 |                                       |              |  |  |  |  |

|-----------------------------|---------------------------------------|--------------|--|--|--|--|

| I/O PORT                    | VLBICS-                               | VLBUSY       |  |  |  |  |

| 03D0-03DF                   | No, if bits                           | Yes, if bits |  |  |  |  |

|                             | 6,5=11.                               | 5,6=11 for   |  |  |  |  |

|                             | (System Bus                           | IOWs.        |  |  |  |  |

|                             | CGA is                                |              |  |  |  |  |

|                             | enabled)                              |              |  |  |  |  |

|                             | Else, Yes                             | Else,No.     |  |  |  |  |

| 03B0-03BF                   | No, if bits                           | Yes, if bits |  |  |  |  |

|                             | 6,5=10                                | 6,5=10 for   |  |  |  |  |

| 4 ° .                       |                                       | IOWs         |  |  |  |  |

|                             |                                       |              |  |  |  |  |

| 20 E                        | Else, Yes.                            | Else, No     |  |  |  |  |

|                             | System bus                            |              |  |  |  |  |

|                             | MDA enabled                           |              |  |  |  |  |

| 03C0-03C2                   | Yes,always                            | No           |  |  |  |  |

| 03C4-03C5                   |                                       |              |  |  |  |  |

| 23C0-23C7                   |                                       |              |  |  |  |  |

| 03CA-03CF                   |                                       |              |  |  |  |  |

| 46E8,56E8,                  | Yes for IOWs                          | No for IOWs. |  |  |  |  |

| 66E8, 76E8,                 | Yes for IORs                          | No for IORs. |  |  |  |  |

| 03C3, 0102                  | · · · · · · · · · · · · · · · · · · · |              |  |  |  |  |

| 03C6-03C9                   | No for IOWs                           | Yes for all  |  |  |  |  |

| (for dual                   | Yes for IORs                          | IOW's.       |  |  |  |  |

| RAMDAC)                     |                                       | No for IORs  |  |  |  |  |

Notes:

1. I/O decode control register; R/W, @ I/O port: 2DF4 bits 5.6.

| BIT5 | BIT6 | CGA | MDA | VLBI |

|------|------|-----|-----|------|

| 0    | 0    | Dis | Dis | En   |

| 0    | 1    | Dis | En  | En   |

| 1    | 0    | Dis | Dis | En   |

| 1    | 1    | En  | Dis | En   |

#### Dis=disable En=enable

VLBUSY signal should be used to disqualify the RDY signal from the core logic to prevent these write cycles from finishing prior to the VLBI finishing.

3. When VLBICS is not generated for the VGA I/O operation, the cycles are passed to the core logic. However, the VLBI still responds and lets the core logic terminate these cycles. Under no circumstances does the VLBI generate read cycles when the VLBICS signal is not generated.

1/2

WD90C56 54E D M 9718228 0015092 187 WDC ARCHITECTURE

#### 2.7 CONFIGURING THE VLBI

At power up, the latched upper two bit address lines LA19:18 are used as inputs. By lightly pulling up or down with resistors, the user is able to configure the VLBI to one of the following modes.

Alternatively, the user can configure the VLBI by making the BIOS setup these parameters and writing to the appropriate registers. See the Register Summary Table.

| LA19 | LA18 | MODE     |

|------|------|----------|

| 1 1  | 1    | AT style |

| 1    | 0    | Reserved |

| 0    | 1    | Reserved |

| 0    | 0    | Reserved |

The LA19 and LA18 lines are internally latched by RESET going high and the mode is configured and preserved. Shortly after RESET going high the LA19:18 lines are turned into permanent outputs.

Similarly, LA17 is used to either use the VMCLK or internal CPU CLK for the VGA interface logic.

T-52

-33-49

| LA7 |                        | VGA I/F CLK |  |

|-----|------------------------|-------------|--|

| 1 . | 1994 - 1 <sup>96</sup> | VMCLK       |  |

| 0   | 11.7                   | CPU CLK     |  |

Similarly, LA16 is used to configure the pin RDYIN as input for terminating cycles by the VLBI or to ignore that input when terminating cycles.

| LA16 | NRDYIN                 |  |  |

|------|------------------------|--|--|

| 1    | Default - ignore       |  |  |

| 0    | Terminate on valid low |  |  |

|      |                        |  |  |

| LA20 | LAPTOP                 |  |  |

| 1    | Laptop mode            |  |  |

| 0    | Desktop mode           |  |  |

The initial condition of the LA20 to LA16 line is reflected in a register which is readable by the CPU at the I/O port address 2DF5.

### WESTERN DIGITAL CORP

18228 0015093 013

WESTERN DIGITAL CORP

WD90C5

| REG<br>ADDR<br>PORT | BIT | DESCRIPTION |

|---------------------|-----|-------------|

| 2DF5                | 7   | LA21        |

| 2DF5                | 6   | LA20        |

| 2DF5                | 5   | LA19        |

| 2DF5                | 4   | LA18        |

| 2DF5                | 3_  | LA17        |

| 2DF5                | 2   | LA16        |

| 2DF5                | 1   | VD22*       |

| 2DF5                | 0   | Reserved    |

54E

| CLK ARRANGEMENT<br>(AFTER INITIALIZATION): |    |    |    |       |  |  |  |

|--------------------------------------------|----|----|----|-------|--|--|--|

| CASE CLK CLK VMCLK MODE<br>2386 486        |    |    |    |       |  |  |  |

| 1                                          | IN | NC | NC | 386   |  |  |  |

| 2                                          | IN | *  | IN | 386** |  |  |  |

| 3                                          | NC | IN | NC | 486   |  |  |  |

| 4                                          | NC | IN | IN | 486** |  |  |  |

h DC

\*Either input or no connect (NC)

\*\*Asynchronous

Notes:

Case 1: CLK2386 is divided by 2 and is used internally.

Case 2: This is asynchronous mode. VMCLK is a different frequency and the CLK486 can be either input or a no connect (NC).

Case 3: The 486 clock is the input to the CLK486 pin and is used internally.

Case 4: This is asynchronous mode. VMCLK is a different frequency and the CLK486 is an input.

Cases 1 and 3 can also function with a different clock (high frequency greater than or equal to 50 MHz) on the VGA MEMCLK. In these cases, the pin VD22 should either be pulled up at power up or Bit 1 of register 2DF5 should be set to a 1 by the software. Also Bit 1 of 2DF4 should be set to 1. See the Clock Scheme section.

\* Async RDY, hardware configurable -VD22

On power up, the VLBI interrogates the CPU config pin, to tell if it is in 386 or 486 mode. If the CPU config pin is low, the VLBI assumes 386 mode. If the CPU config is high, the VLBI assumes 486 mode. The CPU config pin has an internal pull up resistor.

Similarly the VMCLK config pin is interrogated at power up to determine whether an external source is driving it. In the absence of an external clock, the VLBI should be set up in synchronous mode.

To distinguish between 386SX and 386DX, the byte enable BE3 is inspected. If BE3 is high, then the CPU is assumed to be a 386SX.

$\mathscr{D}$

WESTERN DIGITAL CORP T-52-33-49

718228 0015094 TST

#### 2.7.1 Hardware Configuration

WD90C56

54E D

Most timing parameters are made programmable; however, their default values are preset by either pulling up or down VD bus pins with resistors. This arrangement eliminates using different BIOS PROMs for different CPU speeds, etc. These presettings can be overridden by writing software to the appropriate registers.

MDC

See Register Summary Table in the "Register Description" section.

| PIN  | REG  | BITS                   | FUNCTION                        |

|------|------|------------------------|---------------------------------|

| VD16 | 2DF0 | 0                      | VIOW- H/L 2-5 clocks            |

| VD17 | 2DF0 | 1                      | VIOW- H/L 5 clocks if pulled up |

| VD18 | 2DF0 | 2 / 3                  | VIOR- H/L 2-5 clocks            |

| VD19 | 2DF0 | 3                      | VIOR- H/L 5 clocks if pulled up |

| VD20 | 2DF0 | 5                      | VLBI EN/DIS EN if pulled up     |

| VD24 | 2DF1 | 0                      | VMRD-L                          |

| VD25 | 2DF1 | 1                      | VMRD- L 2-5 clocks              |

| VD26 | 2DF1 | 2                      | VMRD-H 5 clocks if pulled up    |

| VD27 | 2DF1 | 3                      | VMRD- H                         |

| VD28 | 2DF1 | <sup>a.</sup> <b>4</b> | VMWR- L                         |

| VD29 | 2DF1 | 5                      | VMWR- L 2-5 clocks              |

| VD30 | 2DF1 | 6                      | VMWR-H 5 clocks if pulled up    |

| VD31 | 2DF1 | 7                      | VMWR- H                         |

TABLE 2-1. HARDWARE REGISTERS

Note: It is preferred that the VLBI is disabled at power-up and later is enabled by the software. In this case, Pin VD20 should be pulled low with a resistor.

20-8

■ 9718228 0015095 996 ■■₩♪C

WD90C56

1.454E

WESTERN DIGITAL CORP

## 2.7.2 Software Configuration

In addition to configuring the VLBI by means of pull/down down resistors, there are several modes and parameters that can be invoked by software at power up. See Register Summary section for complete details.

54E D

| MODE                     | REG  | BITS | FUNCTION                                |

|--------------------------|------|------|-----------------------------------------|

| 16/32<br>Direct transfer | 2DF4 | 0    | L - 16 bit, H - 32 bit<br>VGA Interface |

| Sync                     | 2DF4 |      | L - Async Mode Default                  |

| Future1                  | 2DF4 | 2    | L -Disabled Default                     |

| Future2                  | 2DF4 | 3_   | L - Disabled Default                    |

| Laptop<br>Sleep Mode     |      | 4    | L - Disabled Default                    |

| *                        | 2DF4 | 5:6  | See below                               |

| End Pos/Neg              | 2DF0 | 6    | 0 Pos default                           |

| Start Pos/Neg            | 2DF0 | 7    | 0 Neg default                           |

## TABLE 2-2. CONFIGURE USING SOFTWARE REGISTERS

\* 2DF4, Bits 5 and 6 are used as follows:

| BIT6 | BIT5 | CGA | MDA | VLBI |

|------|------|-----|-----|------|

| 0    | 0    | Dis | Dis | En   |

| 0    | 1    | Dis | Dis | En   |

| 1    | 0    | Dis | En  | En   |

| 1    | 1    | En  | Dis | En   |

Dis=disable En=enable

At power-up all register bits are reset to zero.

| MODE      | REG      | BITS   | FUNCTION                        |

|-----------|----------|--------|---------------------------------|

| READY     | 2DF6     | 1:0=00 | 2 wait states                   |

|           | a mara a | 01     | 1 wait states                   |

| Assertion | 1        | 10     | 0 wait states                   |

|           |          | 11     | Reserved                        |

| BOFF#     | 2DF6     | 2      | 0 - Default BOFF asserted       |

|           |          | 1      | 1 - No assertion of BOFF        |

| BUSY      | 2DF7     | 0      | VLBI BUSY - default 0 not busy. |

#### TABLE 2-3. ADDITIONAL SOFTWARE REGISTERS TO CONFIGURE

WD90C56

54E D 🔲 9718228 0015096 822 페 WDC

WESTERN DIGITAL CORP

### 2.8 PROGRAMMING THE VLBI CHIP

The VLBI chip shadows all necessary configuration programmable registers for the Western Digital VGA chip, so that the VLBI knows about all IO address space and all memory space occupied by the VGA chip. All writes to programmable configuration registers of the VGA chip are captured by the VLBI chip and are transparent to the software. These configurations include the start address of the VGA RAM and the size of the RAM, the type of CPU (16- or 32-bit), and other parameters.

The VLBI chip interprets the CPU Bus cycles for the VGA chip and converts the CPU address and Data Bus to a multiplexed 16-bit AD0:15 bus for the VGA chip. For the highest possible performance while accessing the VGA, the interface between the VGA chip and the CPU can be configured in synchronous or asynchronous mode. The asynchronous mode is suitable when the CPU is running at a low frequency. In this case the VLBI's VMCLK can be connected to the VGA's MEMCLK (at 45 MHz). This will increase the rate of data transfer between the VGA and the VLBI. However, the interface can be configured to synchronous mode as well, to increase performance at higher frequencies. In this case the VMCLK is left unconnected.

T-52-33-49

All three devices (CPU, VLBI, and VGA) must operate on one clock. This mode is known as the synchronous mode. See figure below.

For this mode, CLK486 **must** be connected to the VGA chip MEMCLK pin. It is necessary to use the same clock to the VGA interface in the VLBI and to MEMCLK in the VGA device. This assures that the VGA and VLBI are always synchronous. Similarly the CPU interface in the VLBI and the CPU use the same clock to maintain synchronous operation.

In synchronous mode, yet another configuration is possible, for this mode, CLK486 can be asynchronous to the VGA MEMCLK, although the VLBI is configured in synchronous mode. This is possible because the WD90C30 and WD90C31 sample the VGA commands from the VLBI with the VGA MEMCLK.

### FIGURE 2-3. VLBI SYNCHRONOUS INTERFACE

9718228 0015097 769 🛲 WDC

WESTERN DIGITAL CORP

For a Read cycle, the <u>VLBI</u> chip stops driving AD0:15 after generating <u>VNCMD</u> so that the VGA chip can drive the read data. The <u>VNCMD</u> is generated from the falling edge of CLK (programmable positive/negative start, and others. See timing diagram VLBI3). The <u>VLBICS</u> is valid after T1 but before the middle of T2 of CPUCLK. The VLBI chip stops driving the AD0:15 bus at the end of the CLK edge. If at the beginning of the next rising edge of the CLK and on every subsequent rising edge of the CLK, if the VGARDY is low.

54E

D

CORP T-52-33-44 then the VNCMD is extended (for normal memory cycles only). When VGARDY is sampled high on the rising edge, the next CPUCLK is the last clock of the cycle. Therefore, the VLBI will drive READY low to complete the CPU Bus cycle. This mode is known as synchronous mode.

The VLBI is designed to accomodate various configurations brought upon by different CPU speeds and different VGA memory bandwidths.

WD90C56

1

#### FIGURE 2-4. 32-BIT ACCESS TO VGA (WRITE CYCLE)

WESTERN DIGITAL CORP

WD90C56

T-52-33-49

# 3.0 INTERFACES

#### 3.1 VLBI INTERFACE FOR INTEGRATED CACHE CONTROLLER BASED SYSTEM

The VLBI chip is designed to interface with various CPU and cache and core logic chip sets to improve VGA performance in Intel 80x86 based high end PCs. The VLBI and the system core logic monitor the ADS, PA2:31 and bus status information (M/IO, D/C, W/R) from the CPU in the T1 cycle. The VLBI generates the VLBICS signal for all address references it is going to satisfy. The timing of the VLBICS is such that it can be sampled by the end of the T2 cycle. The VLBICS can be directly connected to the core chip sets.

#### 3.2 VLBI INTERFACE WITH STAND-ALONE CACHE CONTROLLER BASED SYSTEMS

For a system which has a stand-alone cache controller, the VLBI chip is connected to  $\overline{ADS}$  A2:31 and  $M/\overline{O}$ ,  $D/\overline{C}$ ,  $W/\overline{R}$  from the CPU. The VLBI chip monitors the CPU cycle and generates the VLBICS signal for access to its address space. The Cache controller generates  $\overline{SADS}$  for non-cachable cycles which is suppressed by external PAL logic before going to the core logic chip set, so that the core logic chip set does not generate system bus cycles.

### 3.3 PROCESSOR INTERFACE

The VLBI supports both 386 and 486 processors. The 386 is only supported in non-pipeline mode and the same is true for the 386SX. In 486 mode, the clock that drives the 486 processor also drives the VLBI. In 386 mode, since the 386 runs on CLK2, the VLBI is required to run on CLK2 as well. The CPURES signal is taken in by the VLBI for synchronizing the CPU access. The VLBI is capable of supporting 386 and 486 designs up to 33 MHz.

## 3.4 CLOCK SCHEME

When the CPU, VLBI, and VGA are operated synchronously the CPU, VLBI, and VGA must run from the same clock source, that is the same frequency/phase. In the case of a 486 design, the clock used by all three can be the same (CLK486) and the VLBI's VMCLK is left unconnected. The CLK486 in the VLBI is an input. The CLK2386 is also an input and should be left unconnected in 486 mode. The CLK486 is sourced by an external source, by discrete logic, or in the case of Western Digital's AT design it is sourced by the WD76C10A family of devices. **Bit 1 of 2DF4 must be set to 1.**

In the case of a 386 design, CLK2386 comes from the same source that provides the CLK2 to the 386 CPU. However, CLK486 is left unconnected.

In other applications, the VLBI VMCLK will be an input and is connected to the VGA MEMCLK. An external clock source drives both VGA MEMCLK and VLBI VMCLK and this clock is treated as completely asynchronous to the CPU interface clock both in 386 as well as 486 modes.

On power up the VLBI assumes the asynchronous mode and can be changed to synchronous mode by software.

The VLBI VMCLK can be left unconnected and the VGA MEMCLK can have a higher frequency than the CPU. For example, CPUCLK=33 MHz; VGA MEMCLK=50 MHz. For maximum performance, set the internal VLBI logic to synchronous mode, i.e., Bit 1 of 2DF4=1. Also VD22 should either be pulled up at power-up or Bit 1 of 2DF5 should be set to 1.

.

■ 9718228 0015101 TLT ■ WDC \_\_WD90C56

WESTERN DIGITAL CORP

T-52-33-49

20

| PIN-NAME  | PIN-NAME            | PIN-NAME      | PIN-NAME        |

|-----------|---------------------|---------------|-----------------|

| 1-GND     | 41-A14              | 81-GND        | 121-GND         |

| 2-CLK486  | 42-ADS              | 82-VMCLK      | 122-AD14        |

| 3-A28     | 43-BE0              | 83-VGARDY     | 123-AD13        |

| 4-A21     | 44-BE1              | 84-VIOR       | 124-AD12        |

| 5-A20     | 45-BE2              | 85-VIOW       | 125-AD11        |

| 6-BOFF    | 46-BE3              | 86-CPU config | 126-AD10        |

| 7-A19     | 47-W/R              | 87-VBHE       | 127-AD9         |

| 8-A18     | 48-D/C              | 88-RESRV9     | 128-GND         |

| 9-VCC     | 49-M/ <del>IO</del> | 89-LA16/VA0   | 129-AD8         |

| 10-GND    | 50-GND              | 90-GND        | 130-RESRV4      |

| 11-PD6    | 51-A15              | 91-LA17/VA1   | 131-AD7         |

| 12-PD7    | 52-A16              | 92-LA18/VA2   | 132-AD6         |

| 13-PD8    | 53-A17              | 93-LA19       | 133-AD5         |

| 14-PD9    | 54-A7               | 94-RESRV7     | 134-AD4         |

| 15-PD10   | 55-A8               | 95-RESRV8     | 135-AD3         |

| 16-PD11   | 56-A9               | 96-VMWR       | 136-VCC         |

| 17-PD12   | 57-A10              | 97-VMRD       | 137-AD2         |

| 18-PD13   | 58-A11              | 98-LA20       | 138-AD1         |

| 19-GND    | 59-A12              | 99-LA21       | 139-GND         |

| 20-VCC    | 60-VCC              | 100-VCC       | 140-TEST        |

| 21-PD14   | 61-VLBICS           | 101-VD31      | 141-AD0         |

| 22-PD15   | 62-A13              | 102-VD30      | 142-PD31        |

| 23-PD0    | 63-A6               | 103-VD29      | 143-PD30        |

| 24-PD1    | 64-A5               | 104-VD28      | 144-PD29        |

| 25-PD2    | 65-A4               | 105-VD27      | 145-PD28        |

| 26-PD3    | 66-A3               | 106-VD26      | 146-PD27        |

| 27-PD4    | 67-VLBUSY           | 107-VD25      | 147-PD26        |

| 28-PD5    | 68-A2               | 108-VD24      | 148-PD25        |

| 29-HREQ   | 69-READY            | 109-AD15      | 149-PD24        |

| 30-GND    | 70-GND              | 110-GND       | 150-GND         |

| 31-PD16   | 71-A30              | 111-VD23      | 151-PD23        |

| 32-PD17   | 72-A31              | 112-VD22      | 152-PD22        |

| 33-PD18   | 73-CPURES           | 113-VD21      | 153-A23         |

| 34-PD19   | 74-VCC              | 114-VD20      | 1 <b>54-A24</b> |

| 35-PD20   | 75-RESET            | 115-VCC       | 155-A25         |

| 36-PD21   | 76-RDYIN            | 116-VD19      | 156-A26         |

| 37-RESRV1 | 77-PWRDWN           | 117-VD18      | 157-A27         |

| 38-RESRV5 | 78-VBE3             | 118-VD17      | 158-RESRV2      |

| 39-RESRV6 | 79-VBROM            | 119-VD16      | 159-CLK2386     |

| 40-A22    | 80-A29              | 120-VCC       | 160-VCC         |

TABLE 4-1. WD90C56 PIN ASSIGNMENTS

**%**

20-15

WD90C56 54E D . 9718228 0015102 956 . UDC SIGNAL DESCRIPTION

|                                                                                               |                                       | STE | RN DIGITAL CORP                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                                                                                           | MNEMONIC                              | 1/0 | DESCRIPTION T-52-33-49                                                                                                                                                                                                                                        |

| - · · · · · · · · · · · · · · · · · · ·                                                       | · · · · · · · · · · · · · · · · · · · |     | VLBI INTERFACE                                                                                                                                                                                                                                                |

| 68,<br>66-63,<br>59-54,<br>62,41<br>53-51,<br>8-7, 5-4,<br>40,<br>157-153,<br>3, 80,<br>72-71 | A2:31                                 |     | <b>CPU Address Bus</b><br>CPU Address Bus Input for decoding VGA address map decodes.<br>Use only A2:23 for 386SX.                                                                                                                                            |

| 43-46                                                                                         | BE0-BE3                               |     | Byte Enable 0 thru 3<br>Active low byte enable from the CPU or BLE, BHE, and A1 for the 386SX CPU.<br>If the trailing edge of $\overrightarrow{\text{RESET}}$ BE3 is low, then a 16-bit SX CPU mode is assumed. If high, a 32-bit 386 or 486 mode is assumed. |

| 42                                                                                            | ADS                                   | 1   | CPU Address Strobe<br>From 386/486.                                                                                                                                                                                                                           |

|                                                                                               | PD0:31                                | 1/0 | CPU Data Bus<br>CPU DATA BUS 32-bits. Uses only 16-bits in the case of 80386SX.                                                                                                                                                                               |

| 69                                                                                            | READY                                 | 0   | <b>Ready</b><br>The Ready signal of the CPU. The pin is driven high for 5 ns, then<br>is left tristated and is driven low by the VLBI only if it is responding<br>to a CPU cycle.                                                                             |

| 141,<br>138, 137,<br>135-131,<br>129,<br>127-122,<br>109                                      | AD0:15<br>[AD0/BBE0]                  | I/O | Address and Data Bus<br>The 16-bit Multiplexed Address and Data Bus to the VGA chip<br>WD90C30, and others.<br>In 32-bit mode, AD0 and AD1 are the [AD1/BBE2] output byte<br>enable 0 and 2 to the VGA.                                                       |

| 78                                                                                            | VBE3                                  | 1/0 | Valid Byte Enable<br>Indicates to a 32-bit VGA a valid high byte in a 32-bit word. Active<br>low.                                                                                                                                                             |

**TABLE 4-2. SIGNAL DESCRIPTION**

SIGNAL DESCRIPTION

54E D 🔳 9718228

# 9718228 0015103 892 **WD**0C **WD90C56**

WESTERN DIGITAL CORP

T-52-33-49 PIN **MNEMONIC** i/O DESCRIPTION 119-116. VD16:31 I/O High Data 114-111. The upper 16-bits of the data bus to the VGA. For VGA chips 108-101 which have a 32-bit data interface, these pins carry the upper word and AD0:15 carry the lower word. They can carry either light pulldowns or pullups to configure various parameters at power on. 83 VGARDY 1 VGA Readv Active high ready signal from the VGA chip. For access to the VGA 87 VBHE 0 VGA Byte High Enable [BBE1] Output during CPU access to the VGA. In 32-bit modes, this pin plays a double role because it indicates to the VGA a high byte for a low word. VMRD Active low commands to the VGA chip. Their definitions are similar 97 0 VMWR to the AT bus signals. The commands can be made to start and 96 VIOR finish at rising or falling edges of the clock. These commands are 84 VIOW collectively referred to as VNCMD. 85 140 TEST ł Test In conjunction with PD0, PD1, and NRESET, a positive edge on this input will pull the VLBI into various modes; i.e. tristate, I/O map, and others. VLBICS VLBI Chip Select 61 0 Active low signal indicating that the current CPU cycle will be satisfied by the VLBI and the system logic chip set should ignore the cvcle. This line is connected to the bidirectional signal AF32 of the Chips and Technology Peak chip set. Or it can be connected to the NLDS32 signal for WD86C10 based Western Digital designs. This line is driven only if the current cycle is to be serviced by the VLBI. Otherwise the line is tristated. **Hold Request** HLDREQ L 29 The output from the core logic chip set to the processor to indicate that the system bus request is received by either REFRESH, DMA, or a MASTER signal. The processor acknowledges by asserting HOLD ACKNOWLEDGE after relinguishing the bus. 2 Clock486 CLK486 I. The input interface for the 486 CPU clock with a 486 CPU. In 386 this is a no connect (NC). 159 CLK2386 Ł Clock2386 The input interface for the 386DX or 386SX Mode. A clock on this pin assumes 386 mode (386 CPU clock).

**TABLE 4-2. SIGNAL DESCRIPTION (CONTINUED)**

54E

D

■ 9718228 0015104 729 **■ W**D: signal description

| · ·                    | _ WESTERN  | DI         | GITAL CORP T-52-33-41                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                    | MNEMONIC   | 1/0        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |

| 82                     | VMCLK      | 1          | VLBI VGA Clock or left unconnected<br>This is normally connected to VGA MEMCLK. If VGA MEMCLK is<br>different from the 486CLK, the VLBI functions in asynchronous<br>mode.                                                                                                                                                                                                   |

| 73                     | CPURES     |            | <b>CPU Reset</b><br>The synchronous reset to the CPU used to generate internal CLK<br>for maintaining phase of CLK2 in sync with 386DX, 386SX CPU.                                                                                                                                                                                                                           |

| 75                     | RESET      | -          | Reset<br>Active low system reset (power on). Various parameters as well as<br>the mode the VLBI assumes is preset on its trailing edge.                                                                                                                                                                                                                                      |

| 89,<br>91-93,<br>98-99 | LA16:21    | I/O        | Upper 6-bits of the 22-bit address to the VGA chip. At power-up<br>these bits are used as inputs to tell which mode (AT, etc.) should<br>be selected.<br>Pins LA18:16 contain the low order address A2:0 for the RAMDAC<br>I/O cycles - these perform the same function as the AT bus SA2:0.                                                                                 |

| 6                      | BOFF       | 0          | <b>BOFF</b><br>Connects directly to the 486 BOFF# pin. When active, it makes<br>the 486 CPU retract its last cycle and enables the other masters to<br>intervene and obtain the local bus, generated by a read cycle for<br>the VGA when the write buffers are full and HLDREQ is active.                                                                                    |

| 67                     | VLBUSY     | 0          | VLBI Busy<br>Output during RAMDAC or dual display I/O cycles, this signal is<br>the result of the RAMDAC or dual display I/O decode. Once as-<br>serted it remains asserted until the cycle is captured by the VLBI.<br>The VLBUSY signal is also generated for cycles that are common<br>yet meant for CGAs or MDAs that reside on the system bus. Ac-<br>tive high signal. |

| 77                     | PWRDWN     | <b>I</b> . | <b>Power Down</b><br>This signal is active low. When active it drives the PD bus low thus<br>preventing the PD bus from floating during sleep.                                                                                                                                                                                                                               |

| 79                     | VBROM      |            | Video BIOS ROM<br>This pin provides the decode of the CPU address C0000-CFFFF<br>to enable the video BIOS ROMs to be used with the VLBI. Active<br>low.                                                                                                                                                                                                                      |

| 76                     | RDYIN      | 1          | This pin is used for synchronizing with CPU cycles.                                                                                                                                                                                                                                                                                                                          |

| 86                     | CPU config |            | Processor select pin. High=486, low=386.                                                                                                                                                                                                                                                                                                                                     |

## TABLE 4-2. SIGNAL DESCRIPTION (CONTINUED)

#### Note:

1. All clock inputs have internal pullups.

2. Address inputs PA2 to PA31 are not pulled up internally therefore, unused Address inputs in a 16-bit CPU environment should be externally terminated. This minimizes power dissipation in Laptop environment.

# 5.0 REGISTER DESCRIPTION

Some of the programmable register descriptions are included in Section 2, "Architecture." Additional register information is in Appendix A.

54E D

The VLBI has a lock mechanism to protect its registers from being accidentially tampered with by third party programs.

The address to unlock these is A875hex and the data is AChex. Once unlocked, the 2DF0hex series address can be accessed.

# WESTERN DIGITAL CORP T-52-33-49

To lock data other than AChex is written to the address A875hex.

VLBICS is generated for all such accesses, exclusive of the address A875hex.

Once locked, any access requests to the 2DF0 series registers do not produce VLBICS. Therefore, these access requests go to the AT bus.

The following table is a summary of the VLBI registers.

| ADDRESS            | DEFAULT<br>VALUES | PROGRAM<br>SIGNAL | DESCRIPTION                                                                                                                          |

|--------------------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                    | · · · ·           | LOC               | KED                                                                                                                                  |

| 2DF0[0]<br>2DF0[1] | 1                 | VD[16]<br>VD[17]  | Determines VIOW high/low duration (2 to 5 clk)                                                                                       |

| 2DF0[2]<br>2DF0[3] | 1                 | VD[18]<br>VD[19]  | Determines VIOR high/low duration (2 to 5 clk)                                                                                       |

| 2DF0[4]            | 1                 | BIOS              | Determines pulse width of RAMDAC VIOW<br>command (0=9 clk; 1=18 clk)<br>Also high time for VIOR during RAMDAC (0=9<br>clk; 1=18 clk) |

| 2DF0[5]            | 1                 | VD[20]            | VLBI enable control (0= disable)                                                                                                     |

| 2DF0[6]<br>2DF0[7] | 1                 | BIOS<br>BIOS      | End VGA read cycle on pos/neg edge (1=pos)<br>Start VGA read cycle on pos/neg edge (1=neg)                                           |

| 2DF1[0]<br>2DF1[1] | 1                 | VD[24]<br>VD[25]  | Determines VMRD low duration (2 to 5 clk)                                                                                            |

| 2DF1[2]<br>2DF1[3] | 1                 | VD[26]<br>VD[27]  | Determines VMRD high duration (2 to 5 clk)                                                                                           |

| 2DF1[4]<br>2DF1[5] | 1                 | VD[28]<br>VD[29]  | Determines VMWR low duration (2 to 5 clk)                                                                                            |

| 2DF1[6]<br>2DF1[7] | 1                 | VD[30]<br>VD[31]  | Determines VMWR high duration (2 to 5 clk)                                                                                           |

| 2DF2[7:0]          | 0x00              | BIOS              | Compares with A[31:24] to decode video memory                                                                                        |

| 2DF3[7:4]          | 0x0               | BIOS              | Compares with A[23:20] to decode video memory                                                                                        |

| 2DF3[3:0]          | 0xF               | BIOS              | Video memory decode enable<br>0000=decode A[31:24]<br>1000=decode A[31:23]                                                           |

|                    |                   |                   | 1100=decode A[31:22]<br>1110=decode A[31:22]<br>1110=decode A[31:21]<br>1111=decode A[31:20]                                         |

| 2DF4[0]            | 0                 | BIOS              | VGA interface data width (0=16 bit)                                                                                                  |

TABLE 5-1. REGISTER SUMMARY

| 541<br>WD90C56     | E D 🖿 97                              | 19559 0018        | BLOL STI MUDC REGISTER DESCRIPTION                                                   |

|--------------------|---------------------------------------|-------------------|--------------------------------------------------------------------------------------|

| <b>.</b>           | WESTE                                 | RN DIGITAL        | CORP                                                                                 |

| ADDRESS            | DEFAULT<br>VALUES                     | PROGRAM<br>SIGNAL | DESCRIPTION T-52-33-49                                                               |

| 2DF4[1]            | 0                                     | BIOS              | CPU/VGA are async/sync clk (0=async)                                                 |

| 2DF4[2]            | 0                                     | BIOS              | Reserved                                                                             |

| 2DF4[3]            | 0                                     | BIOS              | Reserved                                                                             |

| 2DF4[4]            | 0                                     | BIOS              | VLBI enters Sleep Mode (0=disable)                                                   |

| 2DF4[6:5]          | 00                                    | BIOS              | Enable Dual Display<br>CGA MDA                                                       |

|                    | · .                                   |                   | 00≐ dis dis                                                                          |

|                    |                                       |                   | 10= dis en<br>01= dis dis<br>11= en dis                                              |

| 2DF4[7]            | 0                                     | BIOS              | Dual RAMDAC (0=disable=default)                                                      |

| 2DF5[0]            | 0                                     |                   | Reserved                                                                             |

| 2DF5[1]            | 1                                     | VD[22]            | Async/sync VGARDY (1=async)                                                          |

| 2DF5[2]            | 1                                     | LA[16]            | Terminate VLBI cycle when RDYIN low<br>(1=terminate regardless of RDYIN)             |

| 2DF5[3]            | 1                                     | LA[17]            | Use CPUCLK or VMCLK for VGA interface<br>(1=use VMCLK)                               |

| 2DF5[4]<br>2DF5[5] | 1                                     | LA[18]<br>LA[19]  | System interface selection<br>11=AT bus<br>10=reserved<br>01=reserved<br>00=reserved |

| 2DF5[6]            | 1                                     | LA[20]            | Laptop/desktop mode select (1=laptop)                                                |

| 2DF5[7]            | 1                                     | LA[21]            | Reserved                                                                             |

| 2DF6[1:0]          | 00                                    | BIOS              | Number of wait states<br>00=2 wait states<br>01=1 wait state<br>10=0 wait state      |

|                    | 0                                     | BIOS              | 11=invalid code<br>Use BOFF (0=assert BOFF)                                          |

| 2DF6[2]<br>2DF6[3] | 0                                     | BIOS              | Reserved                                                                             |

| 2DF6[3]            | 0                                     | BIOS              | End VGA write cycle on pos/neg edge (0=pos)                                          |

| 2DF6[4]<br>2DF6[5] | 0                                     | BIOS              | Start VGA write cycle on pos/neg edge (0=pos)                                        |

| 2DF7[0]            | 0                                     | BIOS              | VLBI ready to sleep (0=ready); Read only                                             |

|                    | · · · · · · · · · · · · · · · · · · · | VGA M             |                                                                                      |

| 03C4[4:0]          | 0x00                                  | BIOS              | Index to 03C5                                                                        |

| 03C5.11[1:0]       | 00                                    | BIOS              | 8- or 16-bit I/O control                                                             |

| 03CE[3:0]          | 0x0                                   | BIOS              | Index to 03CF                                                                        |

| 03CF.06[3:2]       | 00                                    | BIOS              | IBM VGA memory mapping                                                               |

| 03CF.0A[2]         | 0                                     | BIOS              | 16-bit memory cycle                                                                  |

| 03CF.0B[5:4]       | 00                                    | BIOS              | Control a [A19:0] decoding                                                           |

TABLE 5-1. REGISTER SUMMARY (CONTINUED)

1/2

DC ELECTRICAL SPECIFICATIONS

WESTERN DIGITAL CORP

6.0 DC ELECTRICAL SPECIFICATIONS

# 6.1 MAXIMUM RATINGS

Maximum ratings; all voltages referenced to Vss.

| Storage Temperature | 0°C to 85°C         |  |

|---------------------|---------------------|--|

| Vcc                 | 5 volts <u>+</u> 5% |  |

# NOTE:

Stress above those listed under Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of the specification is not implied. Exposure to maximum rating conditions for extended periods may effect product reliability. T-52-33-49

54E D

# WD90C56

# 📕 9718228 0015107 438 🌉 WDC

#### 6.2 STANDARD TEST CONDITIONS

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to  $V_{SS}$  (0V Ground). Positive current flows to the referenced pin.

| Storage Temperature | 0°C to 85°C |

|---------------------|-------------|

| Vcc                 | 5 volts ±5% |

# **DC ELECTRICAL SPECIFICATIONS**

■ W D C

# WESTERN DIGITAL CORP

6.3 DC CHARACTERISTICS

÷

54E D 🔳

2. F52-33-49

9718228 0015108 374 1

فشوشق الأرجج

| SYMBOL          | PARAMETER              | MIN  | MAX     | UNITS | CONDITIONS                            |

|-----------------|------------------------|------|---------|-------|---------------------------------------|

| Vil             | Input Low Voltage      | -0.3 | 0.8     | V     | All inputs except CLK2386,<br>VMCLK   |

| ViH             | Input High Voltage     | 2.2  | Vcc+0.3 |       | All inputs except CLK2386, VMCLK      |

| VIL             | Input Low Voltage      | -0.3 |         | V     | CLK2386, VMCLK                        |

| ViH             | Input High Voltage     | 3.7  | Vcc+0.3 | V.,   | CLK2386, VMCLK                        |

| lu              | Input Leakage Current  |      | ±10     | μA    |                                       |

| VOL             | Output Low Voltage     |      | 0.45    | V     |                                       |

| lol.            | Output Low Current     |      | 2.00    | mA    | LA(20:21), VD Bus                     |

| <b>IOL</b>      | Output Low Current     |      | 8.00    | mA    | PD Bus, AD Bus                        |

| lol 🛛           | Output Low Current     |      | 24.00   | mA    | VLBUSY, READY, VLBICS*                |

| lol             | Output Low Current     |      | 8.00    | mA    | All other outputs                     |

| V <sub>OH</sub> | Output High Voltage    |      | 2.4     | V     |                                       |

| ЮН              | Output High Current    |      | 2.0     | mA    | All outputs                           |

| ILO             | Output Leakage Current |      | ±10     | μA    |                                       |

| lcc             | Supply Current         |      | 100     | mA    | @ 25MHz                               |

| lcc             | Supply Current         |      | 130     | mA    | @ 33MHz                               |

| CIN             | Input Capacitance      |      | 15      | ρF    |                                       |

| COUT            | Output Capacitance     |      | 15      | pF    |                                       |

| CIN             | Clk Input Capacitance  |      | 15      | pF    | · · · · · · · · · · · · · · · · · · · |

| COUT            | Clk Output Capacitance |      | 15      | рF    |                                       |

| CI/O            | I/O Pin Capacitance    |      | 20      | pF    | · · · · · · · · · · · · · · · · · · · |

# TABLE 6-1. DC CHARACTERISTICS

\* VLBICS may require a strong pull-up resistor (470 ohm)

# WESTERN DIGITAL CORP 54E D 7.0 AC OPERATING CHARACTERISTICS

The following notes apply to all of the parameters presented in this section:

1. All units are in nanoseconds.

2. Temperature =  $0^{\circ}$ C to  $70^{\circ}$ C.

3. All timings are specified with the rising edge of CLK unless otherwise noted.

4. All timings are measured between 0.8 volts logic low and 2.2 volts logic high, unless otherwise noted.

#### 7.1 TIMING FOR 33 MHZ CLOCK

|               |                                            | <u> </u> |      | · ·   |                                       |

|---------------|--------------------------------------------|----------|------|-------|---------------------------------------|

| SIGNAL        | INPUT/OUTPUT                               | MIN      | MAX  | UNITS | CONDITIONS                            |

| AD Bus        | AD Bus I/O at 30 pF                        | NA       | ŇA   |       | See Tables 7-6                        |

| LA Bus        | LA Bus Output at 30 pF                     | NA       | NA   |       | and 7-7                               |

| VD Bus        | VD Bus I/O at 30 pF                        | NA       | NA   |       | · · · · · ·                           |

| PD Bus        | PD Bus I/O at 50 pF                        | 4        | 14   | ns    |                                       |

| VLBICS        | Output from NADS at 30 pF                  |          | 20   | ns    | · · · · · · · · · · · · · · · · · · · |

| *             | Output at 30 pF                            | 4        | 24   | ns    | · · · · · · · · · · · · · · · · · · · |

| READY         | Output at 25 pF                            | 13       | 16.5 | ns    |                                       |

| VLBUSY (low)  | Output at 30 pF                            |          | 25   | ns    | from ADS                              |

| VLBUSY (high) | Output at 30 pF                            |          | 15   | ns 🐳  | from CLK                              |

| CLK_486       | Input Frequency                            |          | 33   | MHz   |                                       |

| CLK2386       | Input Frequency                            |          | 66   | MHz   |                                       |

| CLK2386       | Rise/fall times                            |          | 4    | ns    | CMOS                                  |

| CLK486        | Rise/fall times                            |          | 3    | ns    |                                       |

| CPURES        | Setup time to CLK2386<br>@33MHz and @50 pF | 7        |      | ns    |                                       |

| CPURES        | Hold time to CLK2386<br>@33MHz and @50 pF  | 2        |      | ns    |                                       |

| **            | Input setup time to CLK                    | 11       |      | ns    | 486/ref 486 clk                       |

| **            | Input setup time to CLK                    | 11       |      | ns    | 386/ref 486 clk †                     |

| **            | Input hold time to CLK                     | 4        |      | ns    | 486/ref 486 clk                       |

| **            | Input hold time to CLK                     | 4        |      | ns    | 386/ref 486 clk †                     |

TABLE 7-1. 33 MHZ CLOCK

\* All other outputs: VBHE, VMRD, VMWR, VIOR, VIOW, and VBE3

† Referenced to 486 clock or internal clock divided by two of clock2386, phase two

\*\* CPU inputs: PA2:31, PD BUS, BE0-BE3/BLE,BHE,ADS,M/IO,D/C and W/R

WD90C56

20

1-52-33-49

9718228 0015109 200 **...**WDC

AC OPERATING CHARACTERISTICS

# WESTERN DIGITAL CORP

■ 9718228 0015110 T22 ■ WDC

| _   | T-52-33-49      |     |          |       |            |  |

|-----|-----------------|-----|----------|-------|------------|--|

| No. | PARAMETER       | MIN | MAX      | UNITS | CONDITIONS |  |

| 1   | Frequency       |     | 33       | MHz   |            |  |

| 2   | Clock period    | 30  |          | ns    | 1          |  |

| 3   | Clock high time | 11  |          | ns    | 0.8V       |  |

| 4   | Clock low time  | 11  | <u> </u> | ns    | 0.8V       |  |

| 5   | Clock fall time |     | 3        | ns    | 2V-0.8V    |  |

| 6   | Clock rise time |     | 3        | ns    | 0.8V-2V    |  |

54E D

TABLE 7-2. 33 MHZ CLK486 SPECIFICATION

| No. | PARAMETER       | MIN  | MAX                                                                          | UNITS | CONDITIONS                            |

|-----|-----------------|------|------------------------------------------------------------------------------|-------|---------------------------------------|

| 1   | Frequency       |      | 45                                                                           | MHz   | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| 2   | Clock period    | 22.0 |                                                                              | ns    |                                       |

| 3   | Clock high time | 8.0  | $= \frac{1}{1 + 1} = \frac{1}{2} \left( \frac{1}{2} + \frac{1}{2} \right)^2$ | ns    | 2V                                    |

| 4   | Clock low time  | 8.0  |                                                                              | ns    | 0.8V                                  |

| 5   | Clock fall time |      | 3                                                                            | ns    | 2V-0.8V                               |

| 6   | Clock rise time |      | 3                                                                            | ns    | 0.8V-2V                               |

TABLE 7-3. 33 MHZ VMCLK INPUT (CMOS)

VMCLK ports is fabricated with CMOS buffers.

AC OPERATING CHARACTERISTICS

WD90C56

WESTERN DIGITAL CORP 7.2 TIMING FOR 66 MHZ CLOCK

54E D 🔳 9718228 0015111 969 🖿 WDC

T-52-33-49

| No. | PARAMETER       | MIN  | MAX  | UNITS | CONDITIONS |

|-----|-----------------|------|------|-------|------------|

| 1   | Frequency       | 16   | 66   | MHz   |            |

| 2   | Clock period    | 15   | 62.5 | ns    |            |

| 3   | Clock high time | 6.25 |      | ns    | 2V         |

| 4   | Clock low time  | 6.25 |      | ns    | 2V         |

| 5   | Clock high time | 4.5  |      | ns    | 3.7V       |

| 6   | Clock low time  | 4.5  |      | ns    | 0.8V       |

| 5   | Clock fall time |      | 4.0  | ns    | 3.7V-0.8V  |

| 6   | Clock rise time |      | 4.0  | ns    | 0.8V-3.7V  |

TABLE 7-4. 66 MHZ CLK2386 SPECIFICATION

FIGURE 7-1. VLBI/CPU INTERFACE

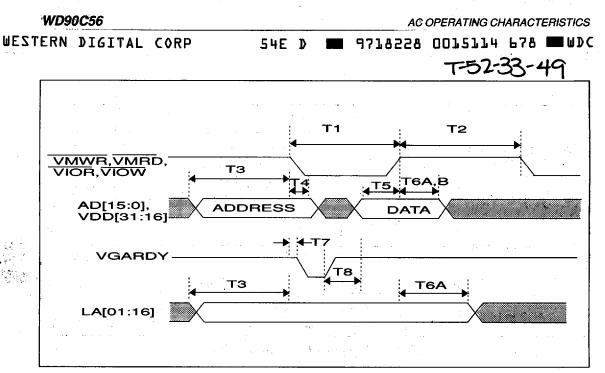

AC OPERATING CHARACTERISTICS WESTERN DIGITAL CORP 7.4 **VLBI TIMING DIAGRAMS**

54E D ■ 9718228 0015113 731 | ∎W⊅C

WD90C56

20

| No. | PARAMETER                                         | MIN     | MAX  | UNITS  |

|-----|---------------------------------------------------|---------|------|--------|