# WD57C65 Floppy Disk Subsystem Controller

### FEATURES

- IBM\* PS/2\* and IBM PC XT\* Compatible

- 100% Software Compatible with WD37C65B

Integrated High Performance DPLL Data

- Separator

- —<10E-9 industry standard error rates</p>

- Data rates of 125, 250, 300, 500

Kbits/second

- · Automatic Write Precompensation

- Defeat option

- -Programmable values of 62,125,187, and

- 250 nanoseconds for standard data rates. • On Chip Clock Generation

- —Two TTL clock inputs (44 pin PLCC)

- -One XTAL oscillator circuit for standard data rates.

- Enhanced Host Interface

- Read/write accesses compatible with an 8 or 12 MHz 286 microprocessor with 0 wait states

- -Twenty LSTTL output drive capability

- TTL Schmitt trigger inputs (except Data Bus)

- Direct Floppy Disk Drive Interface No Buffers Needed

- —48mA sink output drivers

- Schmitt trigger input line receivers

- -Supports three drives

- Complete Application Support for Systems Compatible with the IBM PS/2 and IBM PC XT. —Register file on chip.

- PC XT mode provides required signal qualification to DMA channel

- -BIOS compatible

### DESCRIPTION

The WD57C65 Floppy Disk Subsystem Controller is an LSI device which incorporates all the functional blocks that typically make up a floppy disk subsystem controller, such as the formatter/controller, data separation, write precompensation, data rate selection, clock generation, and floppy drive interface drivers and receivers. Traditionally, data rate selection, drive selection, and motor control have been output ports of the host processor's architecture. The WD57C65 provides all the necessary status and control registers necessary to integrate all the functions of the floppy disk subsystem on a single chip.

The WD57C65 is designed for systems compatible with the IBM PS/2 and IBM PC XT and interfaces with three 5.25 or 3.5-inch floppy disk drives. It is available in a 40-pin, totally encapsulated plastic DIP or a 44-pin PLCC package.

The WD57C65 retains the core of the WD37C65B floppy disk controller so that the Micro-Sequencer is functionally equivalent and all commands will execute identically to ensure software compatibility. The Control State Machine is also functionally equivalent. The Micro-Sequencer and the Control State Machine operate at eight times the selected bit data rate in MFM and sixteen times the bit data rate in FM.

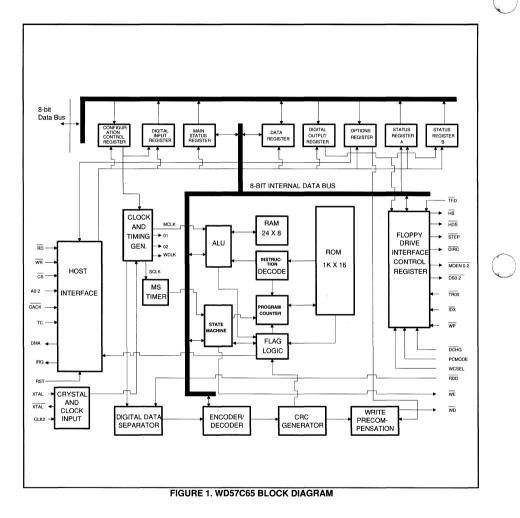

Figure 1 shows a block diagram of the WD57C65 "superchip".

### **Host Interface**

The host interface provides the standard host access signals (eight control signals and eight data signals), but with enhanced timing. A detailed interface description appears in the Interface section of this document.

### **Floppy Drive Interface**

The floppy drive interface provides data separation that has been designed to address high-performance error rates on floppy disk drives. It contains all the necessary logic to achieve 2nd order, type 2, phase-locked loop performance. Write precompensation is included along with the usual formatting, encoding/decoding, stepper motor control, and status sensing functions. A detailed interface description appears in the Interface section of this document.

### **Clock and Timing Generator**

This logical block provides all the clocks needed by the WD57C65: Master Clock, Write Clock and Sampling Clock. Sampling Clock (SCLK) is the clock which drives the digital phase lock loop data separator that is used during data recovery. This clock frequency is always 32 times the selected data rate. The encoder logic uses the Write Clock (WCLK) to place MFM or FM on the serial Write Data stream to the disk. WCLK always has a frequency two times the selected data rate. Master clock (MCLK) is used by the microsequencer. MCLK and MCLK/ clock all latches in a two-phase scheme. One microinstruction cycle is four MCLK cycles. MCLK has a frequency equal to eight times the selected MFM data rate or 16 times the

\* IBM and PS/2 are registered trademarks; and XT is a trademark of International Business Machines Corporation.

WESTERN DIGITAL

| DATA RATE | CODE | SCLK     | MCLK    | WCLK    |

|-----------|------|----------|---------|---------|

| 500 kb/s  | MFM  | 16.0 MHz | 4.0 MHz | 1.0 MHz |

| 250 kb/s  | FM   | 8.0 MHz  | 4.0 MHz | 500 KHz |

| 250 kb/s  | MFM  | 8.0 MHz  | 2.0 MHz | 500 KHz |

| 125 kb/s  | FM   | 4.0 MHz  | 2.0 MHz | 250 KHz |

| 300 kb/s  | MFM  | 9.6 MHz  | 2.4 MHz | 600 KHz |

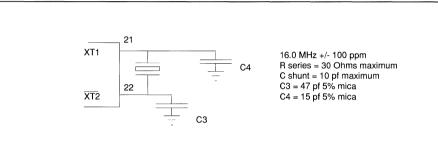

#### FIGURE 2. XTAL OSCILLATOR CIRCUITS FOR THE 44-PIN PLCC

FM data rate. Table 1 presents the Clock Data Rates. Figure 2 illustrates the XTAL oscillator circuits for the 44-pin PLCC configuration.

#### **Crystal and Clock Input**

An XTAL oscillator circuit (Figure 2) provides the necessary signal for internal timing when using the 44-pin PLCC package. There is one 16 Mhz oscillator on the WD57C65 which handles all standard data rates (500, 250, 125 Kbits/sec) and one TTL level clock input used for non-standard data rates; e.g. 300 Kbits/second used in PC AT\* designs. Note, however, that the WD57C65 does not support the IBM PC AT due to register address mapping conflicts.

When using the 40-pin DIP, one TTL level clock input handles the standard data rates. The 40-pin DIP does not support non-standard rates.

\* AT is a registered trademark of International Business Machines Corporation.

#### Write Precompensation

The WD57C65 maintains the standard first level algorithm to determine when write precompensation should be applied. These EARLY and LATE signals are used internally to select the appropriate delay in the Write Data pulse stream. The encoded write data signal is synchronized to the 16 MHz clock, if this is the frequency on pin XTAL, and clocked through a shift register. Signals EARLY, NOM, and LATE determine the amount of delay through the shift register before a multiplexer gates the chosen bit to the output. The output data pulse width has 25% duty cycle, i.e. one-fourth of the bit cell period, also equal to half of the WCLK period.

The Write Precompensation value is micro programmable. The precompensation values are

defined by two bits in the Options Register (bit 2 and 3). After reset the default value for Precompensation is +/- two clocks and is valid for all tracks. There is no write precompensation value for FM. Precompensation can be disabled by the use of bit 2 in the Configuration Control Register for models compatible with the IBM PS/2 Model 30. For models compatible with the IBM PS/2 Models 50,60 and 80, bit 4 in the Options Register disables Write precompensation. The precompensation value is independent of track.

#### **Data Separator**

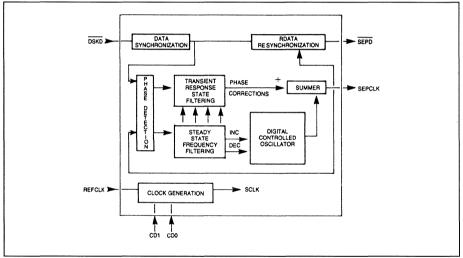

The Data Separator is a WD92C32 Digital Phase Lock Loop Floppy Disk Data Separator (DPLL). It

was designed to address high performance error rates on floppy disk drives, and to provide superior performance in terms of available bit jitter tolerance. It contains the necessary logic to achieve classical 2nd order, type 2, phase-locked loop performance. Figure 3 is a simplified block diagaram of the WD92C32. The bit jitter tolerance for the data separator is 60%, which guarantees an error rate of <10E-9.

### WD57C65 Registers

The WD57C65 provides nine registers for status, control, option selection and buffering functions. These registers are described in detail in the Interface Description.

FIGURE 3. WD92C32 SIMPLIFIED BLOCK DIAGRAM

### INTERFACE DESCRIPTION

$\bigcap$

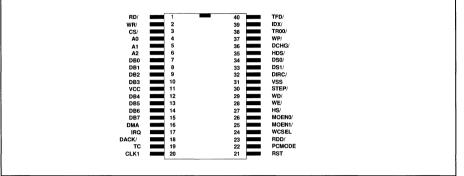

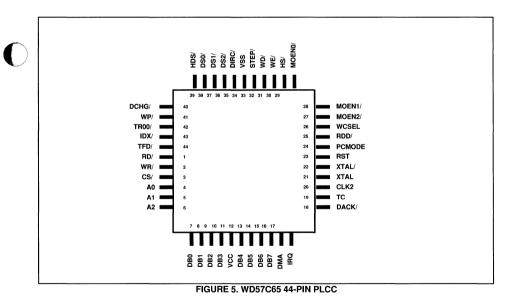

Figures 4 and 5 show the pinouts of the floppy subsystem controllers for systems compatible with the IBM PS/2. Table 2 provides a pinout signal description of the WD57C65.

FIGURE 4. WD57C65 40-PIN DIP

Table 2 below lists the DIP/PLCC pin numbers and the corresponding signal and signal function description. Note: For pin numbers separated by a "/", the first number is a DIP pin number. The number following the slash is the PLCC pin number.

| D/P PIN    | MNEMONIC | SIGNAL NAME              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------|--------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RD/      | Read                     | I   | Control signal for transfer of data or status onto the data bus by WD57C65.                                                                                                                                                                                                                                                                                                                                                           |

| 2          | WR/      | Write                    | I   | Control signal for latching data from the bus into WD57C65 buffer register. Also other registers of Write - only type.                                                                                                                                                                                                                                                                                                                |

| 3          | CS/      | Chip Select              | ł   | Enables RD/ or WR/ operation from the host.                                                                                                                                                                                                                                                                                                                                                                                           |

| 4-6        | A0-2     | Address                  | Ι   | Address lines selecting data.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7-10,12-15 | DB0-7    | Data Bus                 | I/O | 8 bit bi-directional tri-state data bus.                                                                                                                                                                                                                                                                                                                                                                                              |

| 11         | vcc      |                          |     | +5V Supply                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16         | DMA      | Direct Memory-<br>Access | 0   | DMA request for byte transfers of data. In a mode compatible with the IBM PC XT and IBM PS/2 Model 30, this pin is tri-stated, enabled by DMAEN signal from the Digital Output register. In modes compatible with the IBM PS/2 Models 50, 60 and 80, this internal signal, DMAEN, is always forced valid.                                                                                                                             |

| 17         | IRQ      | Interrupt Request        | 0   | Interrupt request indicating completion IRQ/ of com-<br>mand execution or data transfer requests (in non-<br>DMA mode). In modes compatible with the IBM PC<br>XT and PS/2 model 30, this pin is tri-stated, enabled<br>by DMAEN signal from the Digital Output register<br>and is active high. It is open drain for modes com-<br>patible with the IBM PS/2 Models 50, 60 and 80, re-<br>quires external pull-up, and is active low. |

| 18         | DACK/    | DMA Acknowledge          | I   | Used by DMA controller to transfer data from WD57C65 onto the bus. Logical equivalent to CS/ and Addr=101. In a mode compatible with the IBM PC XT and IBM PS/2 Model 30, this signal is qualified by DMAEN from the Digital Output register. In modes compatible with the IBM PS/2 Model 50, 60 and 80, this signal is not qualified.                                                                                                |

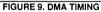

| 19         | тс       | Terminal Count           | I   | This signal indicates to WD57C65 that TC/ data transfer is complete. TC is always qualified by DACK/. In the IBM PC XT and IBM PS/2 Model 30, qualification by DACK/ requires Digital Output Register signal DMAEN to be logically true. In the IBM PS/2 models 50, 60 and 80, TC is active low, and the internal signal DMAEN is always forced valid.                                                                                |

| 20/NA      | CLK1     | Clock 1                  | I   | 16 MHz TTL level clock input used to generate all in-<br>ternal timings for standard data rates. Non-standard<br>data rates (300 Kbits/second) are not supported by<br>the 40-pin dip package.                                                                                                                                                                                                                                        |

### TABLE 2. PINOUT DESCRIPTION

| D/P PIN | MNEMONIC | SIGNAL NAME                  | I/O | DESCRIPTION                                                                                                                                                                                                                                                          |

|---------|----------|------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NA/20   | CLK2     | Clock 2                      | I   | TTL level clock input used for non-standard da<br>rates, such as 300 Kbits/second in an IBM PC /<br>application. Must be 32 times MFM data rate; i.e. 5<br>MHz for 300 Kbits/second, and can only be select<br>from the Control Register. It has an internal pull-up |

| NA/21   | XTAL     | XTAL                         | I   | Oscillator input requiring 16MHz crystal. This os lator is used for all standard data rates. It may driven with a TTL level signal.                                                                                                                                  |

| NA/22   | XTAL/    | XTAL                         | 0   | XTAL oscillator drive output fro 44-pin PLCC.                                                                                                                                                                                                                        |

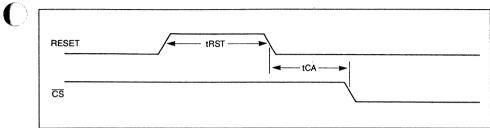

| 21/23   | RST      | Reset                        | I   | Resets controller, placing micro-sequencer in ic Resets device outputs.                                                                                                                                                                                              |

| 22/24   | PCMODE   | PC MODE                      | I   | PC application mode select. Selects a mode co<br>patible with the IBM's PC XT and IBM PS/2 Mod<br>30, or a mode compatible with the IBM PS/2 Mod<br>50, 60 and 80.                                                                                                   |

| 23/25   | RDD/     | Read Disk Data               | Ι   | This Schmitt Trigger (ST) input senses the serial stream from the disk drive. The falling edge of expulse represents a flux transition of the encod data.                                                                                                            |

| 24/26   | WCSEL    | Write Control<br>Select      | I   | Allows direct interface to both 5.25 and 3.5-inch fl<br>py disk drives. For logical function see Table 3.                                                                                                                                                            |

| NA/27   | MOEN2/   | Floppy Drive<br>Motor Enable | 0   | This high current driver (HCD) output, when ac<br>low, enables disk drive #2. This signal comes fr<br>Digital Output Register.                                                                                                                                       |

| 25/28   | MOEN1/   | Floppy Drive<br>Motor Enable | 0   | This HCD output, when active low, enables of<br>drive #1. This signal comes from Digital Out<br>Register.                                                                                                                                                            |

| 26/29   | MOEN0/   | Floppy Drive<br>Motor Enable | 0   | This HCD output, when active low, enables or<br>drive #0. This signal comes from Digital Out<br>Register                                                                                                                                                             |

| 27/30   | HS/      | Head Select                  | 0   | This HCD output selects the head, or side of the f py disk that is being read or written. Logic $1 = side \log c 0 = side 1$ .                                                                                                                                       |

| 28/31   | WE/      | Write Enable                 | 0   | This HCD output goes active low just prior to wri<br>on the diskette. This allows current to flow thro<br>the write head.                                                                                                                                            |

| 29/32   | WD/      | Write Data                   | 0   | This HCD output is write data. Each falling edge<br>the encoded data pulse stream causes a flux tra<br>tion on the media.                                                                                                                                            |

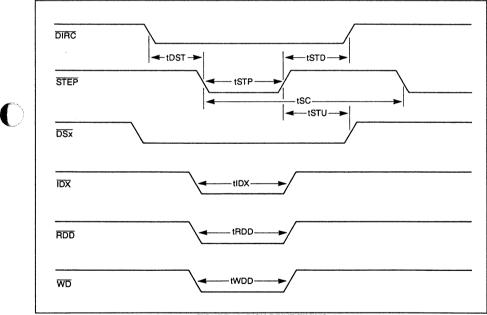

| 30/33   | STEP/    | Step                         | 0   | This HCD output issues an active low pulse for e<br>track-to-track movement of the head. The state<br>the Direction signal at the trailing edge of the ST<br>pulse determines the direction of the head motion                                                       |

|         |          |                              |     |                                                                                                                                                                                                                                                                      |

| )/P PIN | MNEMONIC | SIGNAL NAME            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                     |

|---------|----------|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31/34   | VSS      |                        |     | Ground                                                                                                                                                                                                                                                                          |

| 32/35   | DIRC/    | Direction Control      | 0   | This HCD output determines the direction of the head stepper motor. Logic 1 = outward motion, logic 0 = inward motion.                                                                                                                                                          |

| 35/39   | HDS/     | High Density<br>Select | 0   | This HCD output indicates to the drive the ap-<br>propriate write current level to use for the data rate<br>and media density currently being used. The active<br>logic level used to select between High Density vs<br>Double Density is determined by the WCSEL input<br>pin. |

| 34/38   | DS0/     | Drive Select 0         | 0   | This HCD output, when active low, enables Drive O's interface. This signal comes from the Digital Output register. This signal is qualified by MOEN0/ active low.                                                                                                               |

| 33/37   | DS1/     | Drive Select 1         | 0   | This HCD output, when active low, enables Drive 1's interface. This signal comes from the Digital Input register. This signal is qualified by MOEN1/ active low.                                                                                                                |

| NA/36   | DS2/     | Drive Select 2         | 0   | This HCD output, when active low, enables Drive 2's interface. This signal comes from the Digital input Digital Input register. This signal is qualified by MOEN2/ active low.                                                                                                  |

| 36/40   | DCHG/    | Diskette Change        | I   | This is a Schmitt Trigger input which is an active low signal when the disk drive door is open or if the diskette has possibly changed since last drive selection. This status is reflected in the Digital Input Register.                                                      |

| 37/41   | WP/      | Write Protected        | 1   | This Schmitt Trigger input indicates status from the disk drive, going active low when a diskette is Write Protected.                                                                                                                                                           |

| 38/42   | TR00/    | Track 00               | I   | This Schmitt Trigger input indicates status from the drive, going active low when the head is positioned over the outermost track, track 00.                                                                                                                                    |

| 39/43   | IDX/     | Index                  | I   | This Schmitt Trigger input indicates status from the drive, going active low when the head is positioned over the beginning of a track marked by an index hole.                                                                                                                 |

| 40/44   | TFD/     | Twp Floppy Drive       | I   | This Schmitt Trigger input indicates status from the drive, going active low when a second drive is in-<br>stalled.                                                                                                                                                             |

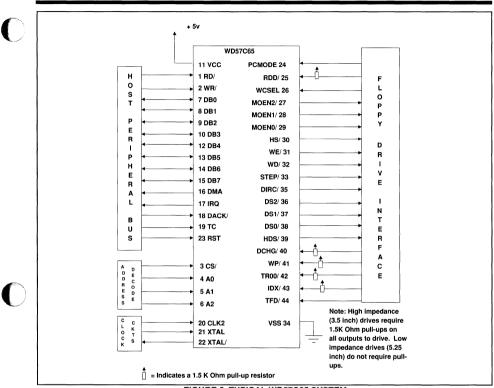

FIGURE 6. TYPICAL WD57C65 SYSTEM

Figure 6 illustrates a typical interface system for the WD57C65.

### Floppy Drive Interface

The WD57C65 Floppy Drive Interface provides different options than its predecessor, the WD37C65B. Most notably, it supports three drives rather than just two. A new input signal, Write Control Select (WCSEL) allows interfacing with 5.25 and 3.5 inch floppy drives. WCSEL and the selected data rate determine the correct logical level on the High Density Select (HDS/) output pin. If WCSEL = 0, HDS/ = CR0. If WCSEL =1, HDS/ = CR1. Refer to Table 3, HDS Truth Table.

PCMODE input signal selects either IBM PC XT-PS/2 30 mode or the PS/2 50, 60, and 80 mode. WD57C65 does not support IBM AT systems.

Since PS/2 compatible systems require a Two Floppy Drive (TFD/) pin, the WD57C65 provides TFD/ and has dropped the PCVAL pin used for precompensation in the WD37C65B predecessor. Write precompensation values are determined by bits 2 and 3 in the Options Register. The reset default value for write precompensation is +/- 2 clocks.

| DATA RATE AND CODE | WCSEL      | HDS | DESCRIPTION                                              |

|--------------------|------------|-----|----------------------------------------------------------|

| 500 K MFM or       | 0          | 1   | 5.25" High Density / 1.2 MByte FDD                       |

| 250 K FM           | . <b>1</b> | o   | 3.5" High Density / 1.44 MByte FDD                       |

| 300 K MFM          | 0          | 0   | 5.25" Double Density / 1.2 MByte FDD                     |

|                    | 1          | 0   | Not Defined                                              |

| 250 K MFM or       | 0          | 1   | 5.25" Double Density / 360 KByte FDD                     |

| 125 K FM           | 1          | 1   | 3.5" Double Density / 720 KByte FDD<br>or 1.44 MByte FDD |

| 125 K FM           | 0          | 0   | 5.25" Single Density / 360 KByte FDD                     |

|                    | 1          | 1   | 3.5" Single Density / 720 KByte FDD                      |

#### TABLE 3. HDS TRUTH TABLE

#### **Host Interface**

Host Microprocessor Peripheral Bus provides eight control signals and eight data signals. In the XT and PS2 30 mode, IRQ and DMA Request are tri-stated and enabled by DMAEN, which is internally provided by the Digital Output Register. In PS/2 50, 60 and 80 mode, IRQ is open drain, active low, requires external pull-up, and DMAEN is always forced valid. The data bus, DMA, and IRQ outputs are designed to handle 20 LSTTL loading. Inputs, except the data bus, are Schmitt trigger receivers and can be hooked up to a bus or backplane without any additional buffering.

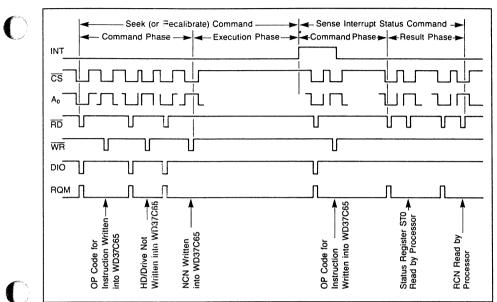

During the command or result phases, the Main Status Register must be read by the processor before each byte of information is written into or read from the Data Register. After each byte of data is read from or written into the Data Register, the CPU should wait for 12 microseconds before reading the Main Status Register. Bits D6 and D7 in the Main Status Register must be in a "0" and "1" state, respectively, before each byte of the command word may be written into the WD57C65. Many of the commands require multiple bytes. As a result, the Main Status Register must be read prior to each byte transfer to the WD57C65. During the result phase, Bits D6 and D7 in the Main Status Register must both be "1's" before reading each byte from the Data Register. Note that this reading of the Main Status Register before each byte transfer to the WD57C65 is required only in the command and result phases, and not during the execution phase. Note also that DB6 and DB7 in the MSR can be polled instead of waiting 12 microseconds.

During the execution phase, the Main Status Register need not be read. If the WD57C65 is in the non-DMA mode, then receipt of each data byte (WD57C65 is reading data from the FDD) is indicated by an interrupt signal on pin 17 (IRQ=1). The generation of a Read signal (RD=0) will clear the interrupt as well as output the data onto the data bus. If the processor cannot handle interrupts fast enough (every 13 microseconds for the MFM mode), then it may poll the Main Status Register and bit D7 (RQM) functions as the interrupt signal. If a Write command is in process, then the WR signal performs the reset to the Interrupt signal.

#### All timing mentioned above is double for minifloppy (5.25-inch) data rates.

Note that in the non-DMA mode it is necessary to examine the Main Status Register to determine the cause of the interrupt since it could be a data interrupt or a command termination interrupt, either normal or abnormal. If the WD57C65 is in the DMA mode, no interrupt signals are generated during the execution phase. The WD57C65

### TABLE 4. ADDRESS REGISTER MAP

| ADDRESS MAP                    | CS/ | A2 | A1 | A0 | R/W/RW      |

|--------------------------------|-----|----|----|----|-------------|

| Status Register A              | 0   | 0  | 0  | 0  | Read only   |

| Status Register B              | 0   | 0  | 0  | 1  | Read only   |

| Digital Output Register        | 0   | 0  | 1  | 0  | Write only  |

| Not Defined                    | 0   | 0  | 1  | 1  | Not defined |

| Main Status Register           | 0   | 1  | 0  | 0  | Read only   |

| Main Data Register             | 0   | 1  | 0  | 1  | Read/Write  |

| Options Register               | 0   | 1  | 1  | 0  | Write only  |

| Digital Input Register         | 0   | 1  | 1  | 1  | Read only   |

| Configuration Control Register | 0   | 1  | 1  | 1  | Write only  |

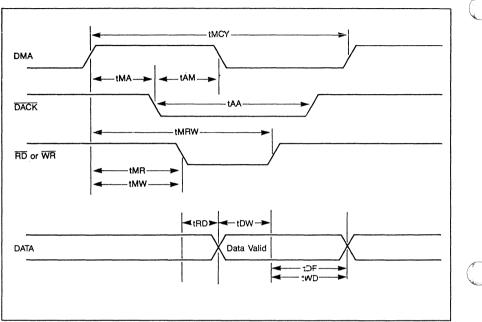

generates DMA requests when each byte of data is available. The DMA controller responds to this request with both DACK/ = 0 (DMA Acknowledge) and a RD/ =0 (Read signal). When the DMA Acknowledge signal goes low (DACK/ = 0), then the DMA Request is cleared (DMA = 0). If a Write Command has been issued, then a WR signal will appear instead of RD. After the execution phase has been completed (Terminal Count has occurred or the EOT sector is read or written), then an interrupt occurs (IRQ = 1). This signifies the beginning of the Result phase. When the first byte of data is read during the result phase, the Interrupt automatically clears (IRQ = 0).

The RD/ or WR/ signals should be asserted while DACK/ is true. The CS/ signal is used in conjunction with RD/ and WR/ as a gating function during programmed I/O operations. CS has no effect during DMA operations. If the non-DMA mode is chosen, the DACK/ signal should be pulled up to VCC. During the result phase all bytes shown in the Command Table must be read. The Read Data Command, for example, has several bytes of data in the result phase. All seven bytes must be read in order to successfully complete the Read Data command. The WD57C65 will not accept a new command until all seven bytes have been read. Other commands may require fewer bytes to be read during the result phase. The WD57C65 contains an address decoder for the register file on the host interface side. The ad-dress mapping is shown in Table 4. The Main Status Register mentioned may be read by the processor at any time. The other four Status Registers (ST0, ST1, ST2, and ST3) are available only during the result phase and may be read only after completing a command. The particular command that has been executed determines how many of the status registers will be read.

The bytes of data which are sent to the WD57C65 during the command phase, and are read out of the WD57C65 in the result phase, must occur in the order shown in the Command Table. The command code must be sent first and the other bytes sent in the prescribed sequence. No foreshortening of the command or result phases is allowed. After the last byte of data in the command phase is sent to the WD57C65, the execution phase automatically starts. In a similar fashion, when the last byte of data is read out in the result phase, the command is automatically ended and the WD57C65 is ready for a new command.

### **Configuration Control Register**

The Configuration Control Register provides support logic that latches the three least significant bits of the data bus upon receiving CS/ Address = 111 and WR/. These bits select the desired data rate, which in turn controls the internal clock generation. Clock switchover is internally "deglitched," allowing continuous operation after changing data rates. If the Configuration Control Register is not used, the data rate is governed by the supplied clock or crystal. The frequency must be 32 times the desired MFM data rate up to a maximum frequency of 16 MHz. This implies a maximum data rate of 500 kbits/second, unless the Configuration Control Register is used.

Switching this clock must be "glitchless" or the device will need to be reset. Tables 5 and 6 show the Configuration Control Register.

### TABLE 5. CONFIGURATION CONTROL REGISTER FOR SYSTEMS COMPATIBLE WITH IBM PS/2 50, 60 & 80

| BIT | SIGNAL NAME / FUNCTION | STORAGE<br>ELEMENT | RESET<br>CONDITION | CLOCK<br>QUALIFIER |

|-----|------------------------|--------------------|--------------------|--------------------|

| 0   | Data Rate              | F/F                | 0                  | None (1)           |

| 1   | Data Rate              | F/F                | 0                  | None (1)           |

| 2   | Reserved               | None               | N/A                | None               |

| 3   | Reserved               | None               | N/A                | None               |

| 4   | Reserved               | None               | N/A                | None               |

| 5   | Reserved               | None               | N/A                | None               |

| 6   | Reserved               | None               | N/A                | None               |

| 7   | Reserved               | None               | N/A                | None               |

|     |                        |                    |                    |                    |

|     |                        | 1                  | 1                  |                    |

Note 1: 250K data rate is selected if bits 0 and 1 are anything but "0,0" in models compatible with the IBM PS/2 50, 60 and 80.

### TABLE 6. CONFIGURATION CONTROL REGISTER FOR SYSTEMS COMPATIBLE WITH IBM PC XT & PS/2 30.

| BIT                                  | SIGNAL NAME / FUNCTION                                                                                         | STORAGE<br>ELEMENT                                 | RESET<br>CONDITION                        | CLOCK<br>QUALIFIER                                       |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|----------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Data Rate<br>Data Rate<br>No Write Precompensation<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved | F/F<br>F/F<br>None<br>None<br>None<br>None<br>None | 0<br>0<br>N/A<br>N/A<br>N/A<br>N/A<br>N/A | None (3)<br>None<br>None<br>None<br>None<br>None<br>None |

Note 3: Undefined in applications compatible with IBM PS/2 30, but supported by the 57C65.

### TABLE 7. DATA RATE SELECTION

| CR1 | CR0 | DATA RATE | COMMENTS                                                |

|-----|-----|-----------|---------------------------------------------------------|

| 0   | 0   | 500 K     | MFM, RST default (Defined in both modes)                |

| 0   | 0   | 250 K     | FM (Undefined in PC applications)                       |

| 0   | 1   | 300 K     | MFM (Defined in applications compatible with IBM PC/AT) |

| 1   | 0   | 250 K     | MFM (Defined in modes compatible with PC XT and PS/2)   |

| 1   | 0   | 125 K     | FM (Undefined in PC applications)                       |

| 1   | 1   | 125 K     | FM (Undefined in PC applications)                       |

Bit 2 (CR2) is undefined in the IBM PS/2 50, 60 and 80 modes, and is set to a "1".

Bit 4 (CR4) enables (0) or disables (1) write precompensation in the IBM PS/2 50, 60 and 80 mode.

In the IBM PC XT and PS/2 30 mode, CR2 enables (0) or disables (1) write precompensation

#### **Main Status Register**

The Main Status Register is an eight-bit register that contains the status information of the FDC, and may be accessed at any time. Only the Main Status Register may be read and used to facilitate the transfer of data between the processor and WD57C65. The DIO and RQM bits in the Main Status Register indicate when data is ready and in which direction data will be transferred on the data bus. The maximum time between the last RD or WR during a command or result phase and DIO and RQM getting set is 12 microseconds if 500 kbits/second MFM data rate is selected. (If 250 kbits/second MFM is selected the delay is 24 microseconds.) For this reason, every time the Main Status Register is read, the CPU should wait 12 microseconds. The maximum time from the trailing edge of the last RD/ in the result phase to when DB4 (FDC busy) goes low is 12 microseconds. Tables 8 through 12 show the bits in the Master Status Register and Status Registers 0 through 3.

### TABLE 8. MAIN STATUS REGISTER BITS

|     | BIT                   |        | DESCRIPTION                                                                                                                                                                                                        |

|-----|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                  | SYMBOL | DESCRIPTION                                                                                                                                                                                                        |

| DB0 | FDD 0 BUSY            | D0B    | FDD number is 0 in the Seek Mode. If any of the bits is set, FDC will not accept READ or WRITE commands.                                                                                                           |

| DB1 | FDD 1 BUSY            | D1B    | FDD number 1 is in the Seek Mode. If any of the bits is set,<br>FDC will not accept READ or WRITE commands.                                                                                                        |

| DB2 | FDD 2 BUSY            | D2B    | FDD number 2 is in the Seek Mode. If any of the bits is set,<br>FDC will not accept READ or WRITE commands.                                                                                                        |

| DB3 | FDD 3 BUSY            | D3B    | FDD number 3 is in the Seek Mode. If any of the bits is set,<br>FDC will not accept READ or WRITE commands.                                                                                                        |

| DB4 | FDC BUSY              | СВ     | A READ or WRITE command is in progress. FDC will not accept any other command.                                                                                                                                     |

| DB5 | EXECUTION MODE        | EXM    | This bit is set only during Execution phase in non-DMA mode.<br>When DB5 goes low Execution phase has ended and Results<br>Phase has started. It operates only during non-DMA mode<br>of operation.                |

| DB6 | DATA INPUT            | DIO    | Indicates direction of data transfer between FDC and Data<br>Register. If DIO-1, then transfer is from Data Register to the<br>processor. If DIO-0, then transfer is from the processor to<br>Data Register.       |

| DB7 | REQUEST FOR<br>MASTER | RQM    | Indicates Data Register is ready to send or receive data to<br>or from the processor. Both bits DIO and RQM should be<br>used to perform the handshaking functions of "ready" and<br>"direction" to the processor. |

### TABLE 9. STATUS REGISTER 0 BITS

|     | BIT             |        | DESCRIPTION                                                                                                                                                                                                              |

|-----|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME            | SYMBOL | DESCRIPTION                                                                                                                                                                                                              |

| D7  | INTERRUPT CODE  | IC     | D7=0 and D6=0. Normal termination of command was<br>completed and properly executed.<br>D7=0 and D6=1. Abnormal termination of command, (AT).<br>Execution of command was started but was not successfully<br>completed. |

| D6  |                 |        | D7=1 and D6=0.<br>Invalid command issue, (IC). Command which was issued<br>was never started.                                                                                                                            |

| D5  | SEEK END        | SE     | When the FDC completes the SEEK command, this flag is set to 1 (high).                                                                                                                                                   |

| †D4 | EQUIPMENT CHECK | EC     | If the Track 0 signal fails to occur after 255 step pulses (Recalibrate Command), then this flag is set.                                                                                                                 |

| +D3 | NOT READY       | NR     | Since drive Ready is always presumed true, this will always be a logic 0.                                                                                                                                                |

| D2  | HEAD SELECT     | HS     | This flag is used to indicate the state of the head at interrupt.                                                                                                                                                        |

| D1  | UNIT SELECT 1   | US1    | This flag is used to indicate a Drive Unit Number at interrupt.                                                                                                                                                          |

| D0  | UNIT SELECT 0   | US0    | This flag is used to indicate a Drive Unit Number at interrupt.                                                                                                                                                          |

## TABLE 10. STATUS REGISTER 1 BITS

O

|     | BIT                     |        | DESCRIPTION                                                                                                                                                                                                                                                                                       |  |

|-----|-------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME                    | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                       |  |

| D7  | END OF CYLINDER         | EN     | When the FDC tries to access a sector beyond the final sector<br>of a cylinder, this flag is set.                                                                                                                                                                                                 |  |

| D6  |                         |        | Not used. This bit is always 0 (low).                                                                                                                                                                                                                                                             |  |

| D5  | DATA ERROR              | DE     | When the FDC detects a *CRC error in either the ID field<br>or the data field, this flag is set.                                                                                                                                                                                                  |  |

| D4  | OVERRUN                 | OR     | If the FDC is not serviced by the host system during data transfers within a certain time interval, this flag is set.                                                                                                                                                                             |  |

| D3  |                         | 1      | Not used. This bit is always 0 (low).                                                                                                                                                                                                                                                             |  |

| D2  | NO DATA                 | ND     | During execution of READ DATA, WRITE DELETED DATA,<br>or SCAN command, if the FDC cannot find the sector<br>specified in the <b>*</b> IDR Register, this flag is set. During<br>execution of the READ ID command, if the FDC cannot read<br>the ID field without an error, then this flag is set. |  |

|     |                         |        | During execution of the READ A TRACK command, if the starting sector cannot be found, then this flag is set.                                                                                                                                                                                      |  |

| D1  | NOT WRITEABLE           | NW     | During execution of WRITE DATA, WRITE DELETED DATA<br>or FORMAT A TRACK commands, if the FDC detects a WP<br>signal from the FDD, then this flag is set.                                                                                                                                          |  |

| D0  | MISSING ADDRESS<br>MARK | MA     | If the FDC cannot detect the ID Address Mark after<br>encountering the index hole twice, then this flag is set.                                                                                                                                                                                   |  |

|     |                         |        | If the FDC cannot detect the Data Address Mark or Deleted<br>Data Address Mark, this flag is set. At the same time the<br>MD (Missing Address Mark in data field) of Status Register<br>2 is set.                                                                                                 |  |

### TABLE 11. STATUS REGISTER 2 BITS

|     | BIT                                   |        | DESCRIPTION                                                                                                                                                                    |

|-----|---------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                                  | SYMBOL | DESCRIPTION                                                                                                                                                                    |

| D7  |                                       |        | Not Used. This bit is always 0 (low).                                                                                                                                          |

| D6  | CONTROL MARK                          | СМ     | During execution of the READ DATA or SCAN Command,<br>if the FDC encounters a sector which contains a Deleted Data<br>Address Mark, this flag is set.                          |

| D5  | DATA ERROR                            | DD     | If the FDC detects a CRC error in the data field, then this flag is set.                                                                                                       |

| D4  | WRONG CYLINDER                        | WC     | This bit is related to the ND bit, and when the contents of $* * * C$ on the medium is different from that stored in the IDR, this flag is set.                                |

| D3  | SCAN EQUAL                            | SH     | During execution of the SCAN command, if the condition of "equal" is satisfied, this flag is set.                                                                              |

| D2  | SCAN NOT                              | SN     | During execution of the SCAN command, if the FDC cannot<br>find a sector on the cylinder which meets the condition, then<br>this flag is set.                                  |

| D1  | BAD CYLINDER                          | BC     | This bit is related to the ND bit, and when the contents of<br>C on the medium is different from that stored in the IDR and<br>the contents of C is FF, then this flag is set. |

| D0  | MISSING ADDRESS<br>MARK IN DATA FIELD | MD     | When data is read from the medium, if the FDC cannot find<br>a Data Address Mark or Deleted Data Address Mark, then<br>this flag is set.                                       |

# TABLE 12. STATUS REGISTER 3 BITS

| BIT |                 |        | DESCRIPTION                                                                        |  |

|-----|-----------------|--------|------------------------------------------------------------------------------------|--|

| NO. | NAME            | SYMBOL | DESCRIPTION                                                                        |  |

| †D7 | -               |        | Not used. Will always be logic 0.                                                  |  |

| D6  | WRITE PROTECTED | WP     | This bit is used to indicate the status of the WRIT PROTECTED signal from the FDD. |  |

| †D5 | READY           | RY     | This bit will always be a logic 1.                                                 |  |

|     |                 |        | Drive is presumed to be ready.                                                     |  |

| D4  | TRACK 0         | то     | This bit is used to indicate the status of the Track 0 sign from the FDD.          |  |

| †D3 | WRITE PROTECTED | WP     | This bit is used to indicate the status of the WRIT PROTECTED signal from the FDD. |  |

| D2  | HEAD SELECT     | HS     | This bit is used to indicate the status of the Side Select sign to the FDD.        |  |

| D1  | UNIT SELECT 1   | US1    | This bit is used to indicate the status of the Unit Select signal to the FDD.      |  |

| D0  | UNIT SELECT 2   | USO    | This bit is used to indicate the status of the Unit Select signal to the FDD.      |  |

### Status Register A (CS/ = 0 and Address = 000 - Read Only)

### TABLE 13. STATUS REGISTER A FOR SYSTEMS COMPATIBLE WITH IBM PS/2 50, 60 AND 80

| 0+ DirectionTSBN/ANone1- Write ProtectionTSBN/ANone2- IndexTSBN/ANone3+ Head 1 SelectTSBN/ANone4- Track 0TSBN/ANone5+ StepTSBN/ANone6- 2nd Drive InstalledTSBN/ANone7InterruptTSBN/ANone | BIT                        | SIGNAL NAME / FUNCTION                                                                                    | STORAGE<br>ELEMENT                     | RESET<br>CONDITION              | CLOCK<br>QUALIFIER                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|--------------------------------------|

|                                                                                                                                                                                          | 1<br>2<br>3<br>4<br>5<br>6 | <ul> <li>Write Protection</li> <li>Index</li> <li>Head 1 Select</li> <li>Track 0</li> <li>Step</li> </ul> | TSB<br>TSB<br>TSB<br>TSB<br>TSB<br>TSB | N/A<br>N/A<br>N/A<br>N/A<br>N/A | None<br>None<br>None<br>None<br>None |

### TABLE 14. STATUS REGISTER A FOR SYSTEMS COMPATIBLE WITH THE IBM PC XT AND IBM PS/2 30

| BIT                                  | SIGNAL NAME / FUNCTION                                                                                                                                    | STORAGE<br>ELEMENT                               | RESET<br>CONDITION                          | CLOCK<br>QUALIFIER                                       |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------|----------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | <ul> <li>Direction</li> <li>Write Protect</li> <li>Index</li> <li>Head 1 Select</li> <li>Track 0</li> <li>Step</li> <li>DRQ</li> <li>Interrupt</li> </ul> | TSB<br>TSB<br>TSB<br>TSB<br>SR F/F<br>TSB<br>TSB | N/A<br>N/A<br>N/A<br>N/A<br>0<br>N/A<br>N/A | None<br>None<br>None<br>None<br>STEP (1)<br>None<br>None |

Note 1: Not synchronized to unknown PAL clocks in systems compatible with the IBM PS2. Reset is forced to logic "0" for test purposes. Also resets to logic "0" when address 3F7 is read and STEP causes a set condition.

TSB = Tri-state buffer

SR F/F = Set Reset Flip Flop

If Storage Element is "none", Reset Condition reflects fixed logic state.

### Status Register B (CS/ = 0 and Address = 001 - Read Only)

### TABLE 15. STATUS REGISTER B FOR SYSTEMS COMPATIBLE WITH THE IBM PS/2 50, 60, AND 80.

| BIT                                  | SIGNAL NAME / FUNCTION                                                                                              | STORAGE<br>ELEMENT                                                               | RESET<br>CONDITION                    | CLOCK<br>QUALIFIER                                              |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Motor Enable 0<br>Motor Enable 1<br>Write Enable<br>Read Data<br>Write Data<br>Drive Select<br>Reserved<br>Reserved | TSB<br>TSB<br>TSB<br>Toggle F/F<br>Toggle F/F<br>TSB<br>Unused TSB<br>Unused TSB | N/A<br>N/A<br>0<br>0<br>N/A<br>1<br>1 | None<br>None<br>RDD/ (1)<br>WD/ (2)<br>None (3)<br>None<br>None |

Note 1: Not synchronized to unknown PAL clocks in systems compatible with the IBM PS/2 50, 60 and 80. Reset is forced to logic "0" for test purposes.

Note 2: Not synchronized to unknown PAL clocks in systems compatible with the IBM PS/2 50, 60 and 80. Reset is forced to logic "0" for test purposes. This "WD" clock is an internal signal not qualified by WE/ signal.

Note 3: This status reflects Digital Output Register bit 0 only.

### TABLE 16. STATUS REGISTER B FOR SYSTEMS COMPATIBLE WITH IBM PC XT AND IBM PS/2 MODEL 30

| BIT | SIGNAL NAME / FUNCTION                                                                                                                                                                    | STORAGE<br>ELEMENT | RESET<br>CONDITION | CLOCK<br>QUALIFIER |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| 0   | <ul> <li>Drive Select 2</li> <li>Drive Select 3</li> <li>Write Enable</li> <li>Read Data</li> <li>Write Data</li> <li>Drive Select 0</li> <li>Drive Select 1</li> <li>Reserved</li> </ul> | TSB                | N/A                | None (5)           |

| 1   |                                                                                                                                                                                           | TSB                | N/A                | None (5)           |

| 2   |                                                                                                                                                                                           | SR F/F             | 0                  | WE/ (4)            |

| 3   |                                                                                                                                                                                           | SR F/F             | 0                  | RDD/ (4)           |

| 4   |                                                                                                                                                                                           | SR F/F             | 0                  | WD/ (4)            |

| 5   |                                                                                                                                                                                           | TSB                | N/A                | None (5)           |

| 6   |                                                                                                                                                                                           | TSB                | N/A                | None (5)           |

| 7   |                                                                                                                                                                                           | Unused TSB         | 0                  | None               |

Note 4: Not synchronized to unknown PAL clocks in systems compatible with IBM PS/2 30. Reset is forced to logic "0" for test purposes and when reading address 357. WE/, RDD/ and WD/ are internal signals and cause a set condition.

Note 5: Drive select signals (0-3) are qualified by Motor Enable signals (0-3)

TSB = Tri-state Buffer

SR F/F = Set Reset Flip Flop.

If Storage Element is none, Reset Condition reflects fixed logic state.

### Data Register

The eight-bit Data Register stores data, commands, parameters, and FDD status information. Data bytes are read out of, or written into, the Data Register in order to program or obtain the results after a particular command. The relationship between the Master Status Register and the Data Register and the signals RD/, WR/, CS/ and A0-A2 are shown in Table 17.

### TABLE 17. MASTER STATUS AND DATA REGISTERS RELATIONSHIP

| A0 | A1 | A2 | CS | RD | WR | FUNCTION                  |

|----|----|----|----|----|----|---------------------------|

| 1  | 0  | 0  | 0  | 0  | 1  | Read Main Status Register |

| 1  | 0  | 1  | 0  | 0  | 1  | Read from Data Register   |

| 1  | 0  | 1  | 0  | 1  | 0  | Write into Data Register  |

### Digital Output Register (CS/=0 and Address = 010 - Write Only)

The Digital Output Register (DOR) provides support logic that latches the data bus upon receiving CS/, Address = 010 and WR/. This register replaces the typical latched port seen in floppy subsystems used to control disk drive spindle motors and select drives. Table 18 illustrates the bit decode (bits 0 and 1 of the DOR) used to select drives 0 through 2. Table 19 provides a bit description of the contents of the DOR.

### TABLE 18. BIT DECODE FOR DRIVE SELECT

| DSEL1 | DSEL0 | DRIVE         |

|-------|-------|---------------|

| 0     | 0     | Drive 0       |

| 0     | 1     | Drive 1       |

| 1     | 0     | Drive 2       |

| 1     | 1     | Not Supported |

### TABLE 19. DIGITAL OUTPUT REGISTER

| BIT  | SIGNAL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOR0 | DSEL0  | Drive Select. If decode select is "0" and MOEN0/<br>is active low, then DS0/ is selected. If decode<br>select is "1" and MOEN1/ is active low, then DS1/<br>is selected. If decode select is "2" and MOEN2/ is<br>active low, then DS2/ is selected if in a mode<br>compatible with the IBM PC XT and IBM PS/2<br>Model 30. Although DS2/ is undefined in applica-<br>tions compatible with the IBM PS/2 50, 60 and 80,<br>the WD57C65 supports DS2/ in both modes. |

| DOR1 | DSEL1  | Drive Select                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DOR2 | SRST/  | Soft Reset, active low                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DOR3 | DMAEN  | DMA Enable. Active in a mode compatible with<br>the IBM PC XT and IBM PS/2 Model 30, qualifies<br>DMA and IRQ outputs and also DACK/input. In<br>modes compatible with the IBM PS/2 models 50,<br>60 and 80 this internal signal is always valid.                                                                                                                                                                                                                   |

| BIT   | SIGNAL | COMMENTS                                                                                                                                                               |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOR 4 | MOEN0  | Motor enable (Inverted output is MOEN0/)                                                                                                                               |

| DOR 5 | MOEN1  | Motor enable (Inverted output is MOEN1/)                                                                                                                               |

| DOR6  | MOEN2  | Motor enable (Inverted output is MOEN2/) Un-<br>defined in applications compatible with the IBM<br>PS/2 50, 60 and 80, but supported by the<br>WD57C65 in both modes.) |

| DOR7  |        | Reserved                                                                                                                                                               |

### TABLE 20. DIGITAL OUTPUT REGISTER FOR SYSTEMS COMPATIBLE WITH IBM PS/2 50,60, AND 80

| BIT | SIGNAL NAME / FUNCTION | STORAGE<br>ELEMENT | RESET<br>CONDITION | CLOCK<br>QUALIFIER |

|-----|------------------------|--------------------|--------------------|--------------------|

| 0   | Drive Select           | F/F                | 0                  | None (1)           |

| 1   | Drive Select           | F/F                | 0                  | None (1)           |

| 2   | - Reset                | F/F                | 0                  | None               |

| 3   | Reserved               | Unused F/F         | N/A                | None               |

| 4   | Motor 0                | F/F                | 0                  | None               |

| 5   | Motor 1                | F/F                | 0                  | None               |

| 6   | Motor 2                | F/F                | 0                  | None (1)           |

| 7   | Reserved               | Unused F/F         | N/A                | None               |

|     |                        |                    |                    |                    |

Note 1: Although undefined in applications compatible with the IBM PS/2 50, 60 and 80, this signal is supported by the WD57C65.

### TABLE 21. DIGITAL OUTPUT REGISTER FOR SYSTEMS COMPATIBLE WITH IBM PC XT AND IBM PS/2 30.

| BIT | SIGNAL NAME / FUNCTION   | STORAGE<br>ELEMENT | RESET<br>CONDITION | CLOCK<br>QUALIFIER |

|-----|--------------------------|--------------------|--------------------|--------------------|

| 0   | Drive Select             | F/F                | 0                  | None               |

| 1   | Drive Select             | F/F                | 0                  | None               |

| 2   | - Reset                  | F/F                | 0                  | None               |

| 3   | DMA and Interrupt Enable | F/F                | 0                  | None               |

| 4   | Motor 0                  | F/F                | 0                  | None               |

| 5   | Motor 1                  | F/F                | 0                  | None               |

| 6   | Motor 2                  | F/F                | 0                  | None               |

| 7   | Reserved                 | Unused F/F         | N/A                | None (2)           |

|     |                          |                    |                    |                    |

Note 2: This bit is defined as Motor Enable 3 in models compatible with the IBM PS/2 30, but WD57C65 does not support it.

TSB = Tri-state Buffer F/F = Flip Flop

If Storage Element is "none", Reset condition reflects fixed logic state.

### Digital Input Register (CS/=0 and Address = 111 - Read only)

### TABLE 22. DIGITAL INPUT REGISTER FOR SYSTEMS COMPATIBLE WITH THE IBM PS/2 50, 60 AND 80

| BIT | SIGNAL NAME / FUNCTION | STORAGE<br>ELEMENT | RESET<br>CONDITION | CLOCK<br>QUALIFIER |

|-----|------------------------|--------------------|--------------------|--------------------|

| 0   | - High Density Select  | TSB                | N/A                | None               |

| 1   | Reserved               | Unused TSB         | 1                  | None               |

| 2   | Reserved               | Unused TSB         | 1                  | None               |

| 3   | Reserved               | Unused TSB         | 1                  | None               |

| 4   | Reserved               | Unused TSB         | 1                  | None               |

| 5   | Reserved               | Unused TSB         | 1                  | None               |

| 6   | Reserved               | Unused TSB         | 1                  | None               |

| 7   | Disk Change            | TSB                | N/A                | None               |

|     | -                      |                    |                    |                    |

### TABLE 23. DIGITAL INPUT REGISTER FOR SYSTEMS COMPATIBLE WITH THE IBM PC XT AND IBM PS/2 30

| BIT                                  | SIGNAL NAME / FUNCTION                                                                                                                 | STORAGE<br>ELEMENT                                                        | RESET<br>CONDITION                    | CLOCK<br>QUALIFIER                                   |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Reserved<br>250K Rate Select<br>No Write Precompensation<br>DMA, Interrupt Enable<br>Reserved<br>Reserved<br>Reserved<br>- Disk Change | Unused TSB<br>TSB<br>TSB<br>Unused TSB<br>Unused TSB<br>Unused TSB<br>TSB | 0<br>N/A<br>N/A<br>0<br>0<br>0<br>N/A | None<br>None<br>None<br>None<br>None<br>None<br>None |

|                                      |                                                                                                                                        |                                                                           |                                       |                                                      |

TSB = Tri-state Buffer

F/F = Flip Flop

If Storage Element is "none" or "unused", Reset Condition reflects fixed logic state.

### **Options Register**

### TABLE 24. OPTIONS REGISTER

| BIT | SIGNAL           | FUNCTION                                                                                                                                                                                                                                        |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Boot Disk Select | If "0", causes DS1/ and MOEN/1 to be swapped in<br>H/W with DS0/ and MOEN0/. Therefore, if DOR<br>selects Drive 0, then actually Drive #1 will be<br>selected and enabled, allowing a S/W operating<br>system to be booted from the disk drive. |

| 1   | SWTC             | Software Terminal Count allows a TC to be issued to the core controller under BIOS driver control.                                                                                                                                              |

| 2-3 | PCV              | These two bits define the precompensation values, as shown in the truth table below.                                                                                                                                                            |

| 4   | NWP              | This bit disables write precompensation in modes compatible with IBM PS/2 50, 60 and 80 only.                                                                                                                                                   |

### **TABLE 25. TRUTH TABLE**

| BIT 3         | BIT 2 | PRECOMP VALUE  |  |  |  |  |  |  |  |

|---------------|-------|----------------|--|--|--|--|--|--|--|

| 0             | 0     | +/- 1 Clocks   |  |  |  |  |  |  |  |

| 0             | 1     | +/- 2 Clocks * |  |  |  |  |  |  |  |

| 1             | 0     | +/- 3 Clocks   |  |  |  |  |  |  |  |

| 1             | 1     | +/- 4 Clocks   |  |  |  |  |  |  |  |

| * RST Default |       |                |  |  |  |  |  |  |  |

Note: Clk = Clk 1 for all data rates, except when 300 Kb/s is selected which requires Clk 2. In PS/2 model 30 precompensation can be disabled by using bit 2 in the Configuration Control Register. In PS/2 50, 60 and 80, bit 4 of the Options Register disables precompensation.

### TABLE 26. OPTIONS REGISTER

| BIT        | SIGNAL NAME / FUNCTION                       | STORAGE<br>ELEMENT | RESET<br>CONDITION | CLOCK<br>QUALIFIER |  |  |  |  |  |  |  |

|------------|----------------------------------------------|--------------------|--------------------|--------------------|--|--|--|--|--|--|--|

| 0          | Boot Disk Select                             | F/F                | 0                  | None               |  |  |  |  |  |  |  |

| 1          | SWTC                                         | F/F                | 0                  | None               |  |  |  |  |  |  |  |

| 2          | PCV                                          | F/F                | 0                  | None               |  |  |  |  |  |  |  |

| 3          | PCV                                          | SR F/F             | 1                  | None               |  |  |  |  |  |  |  |

| 4          | No Write Precompensation                     | F/F                | 0                  | None               |  |  |  |  |  |  |  |

| 5          | Reserved                                     | Unused F/F         | 0                  | None               |  |  |  |  |  |  |  |

| 6          | Reserved                                     | Unused F/F         | 0                  | None               |  |  |  |  |  |  |  |

| 7          | Reserved                                     | Unused F/F         | 0                  | None               |  |  |  |  |  |  |  |

|            |                                              |                    |                    |                    |  |  |  |  |  |  |  |

| F/F = Flip | F/F = Flip Flop SR F/F = Set Reset Flip Flop |                    |                    |                    |  |  |  |  |  |  |  |

## SPECIFICATIONS

C

### ABSOLUTE MAXIMUM RATINGS - all voltages referenced to VSS

| VCC                   | 7.0 Volts                            |

|-----------------------|--------------------------------------|

| Voltage at any pin    | -0.3 to VCC +0.3 Volts               |

| Storage Temperature   | -55° to +150° C                      |

| Operating Temperature | 0 <sup>o</sup> to +70 <sup>o</sup> C |

|   | DC CHARACTERISTICS<br>PARAMETER               | SYMBOL     | MIN  | МАХ  | UNIT |

|---|-----------------------------------------------|------------|------|------|------|

|   | +5V Supply                                    | VCC        | 4.5  | 5.5  | V    |

|   | Input Low Voltage - Data Bus & XTOSC          | VIL        |      | 0.8  | V    |

|   | Input High Volt - Data Bus & XTOSC            | VIH        | 2.0  |      | V    |

|   | Input Low Threshold-Schmitt Trigger           | VILT       | 0.8  |      | V    |

|   | Input High Threshold-Schmitt Trigger          | VIHT       |      | 2.0  | V    |

|   | Schmitt Trigger Input Hysteresis              | VIHYS      | 0.45 |      | V    |

|   | Output Low - DBx,IRQ,DMA ; lo=12.0mA          | VOL        |      | 0.4  | V    |

|   | Output High - DBx,IRQ,DMA; Io=-5.0mA          | VOH        | 2.8  |      | V    |

|   | Output Low - High Current; Io=48mA            | VOLHC      |      | 0.4  | V    |

|   | PQR trip threshold                            | VPQR       | 2.75 | 4.35 | V    |

| 1 | Latch Up Current Low                          | ILUL       | 40   |      | mA   |

| ) | Latch Up Current High                         | ILUH       | -40  |      | mA   |

|   | Leakage Current Low                           | ILL        |      | 10   | μA   |

|   | Leakage Current High                          | ILH        |      | -10  | μA   |

|   | Supply Current - 100µA source loads           | ICC        |      | 40   | mA   |

|   | Supply Current - 5mA source loads             | ICCHL      |      | 90   | mA   |

|   | Power Dissipation - ICC max *                 | PD         |      | 400  | mW   |

|   | Power Dissipation - ICCHL max *               | PDHL       |      | 550  | mW   |

|   | * Includes open drain high current drivers at | Vol = 0.4V |      |      |      |

| TIMING CHARACTERISTICS (CL=100pf):<br>PARAMETER | SYMBOL | MIN | МАХ | UNIT |

|-------------------------------------------------|--------|-----|-----|------|

|                                                 |        |     | WAA |      |

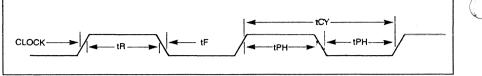

| Clock Period                                    | tCY    | 60  |     | nS   |

| Clock Active (High or Low)                      | tPH    | 25  |     | nS   |

| Clock Rise Time (Vin 0.8 to 2.0)                | tR     |     | 5   | nS   |

| Clock Fall Time (Vin 2.0 to 0.8)                | tF     |     | 5   | nS   |

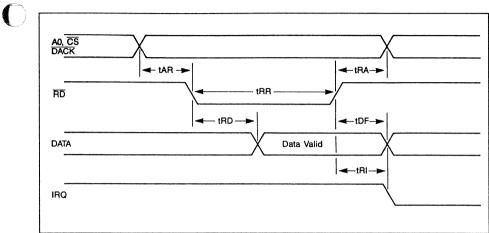

| A0-2 Set Up Time to RD- low                     | tAR    | 10  |     | nS   |

| A0-2, Hold Time to RD- high                     | tRA    | 0   |     | nS   |

| CS-, DACK Set Up Time to RD- low                | tCDR   | 0   |     | nS   |

| CS-, DACK Hold Time to RD- high                 | tRCD   | 0   |     | nS   |

| RD- Width                                       | tRR    | 80  |     | nS   |