# WESTERN DIGITAL IMAGING PERSONAL WORKSTATION GRAPHICS ARRAY-1 (PWGA-1)

DATA BOOK

|                                                                                          |                                                                  | N DIGITAL                                    |          |

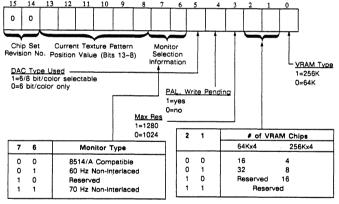

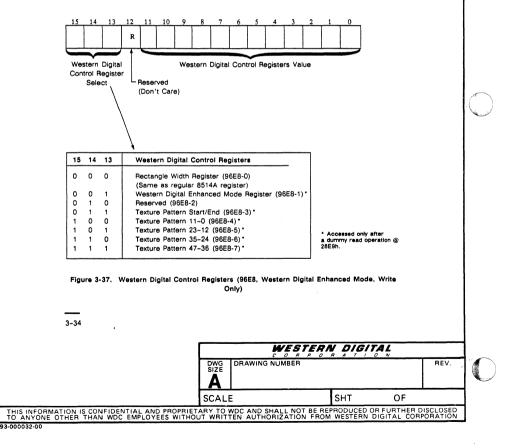

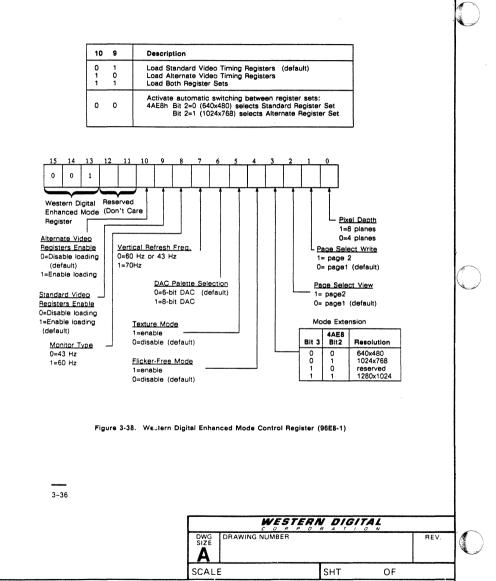

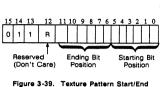

|------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|----------|

|                                                                                          | DWG DRAWING NUMBER                                               |                                              | REV.     |

|                                                                                          | SCALE                                                            | SHT OF                                       |          |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIE<br>TO ANYONE OTHER THAN WDC EMPLOYEES WITHO | TARY TO WDC AND SHALL NOT BE RE<br>UT WRITTEN AUTHORIZATION FROM | PRODUCED OR FURTHER D<br>WESTERN DIGITAL COR | PORATION |

93-000032-00

#### Contents

# COPYRIGHT

Copyright  $hinspace{0}$  1988 Western Digital Imaging. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of Western Digital Imaging.

Western Digital Imaging reserves the right to make changes or improvements to the equipment, software, hardware, and documentation described herein at any time and without notice.

IBM and P/S2 are registered trademarks and Micro Channel is a trademark of International Business Machine Corporation.

| Rev. 1 March 1989 |  | Rev. | 1 | March | 1989 |

|-------------------|--|------|---|-------|------|

|-------------------|--|------|---|-------|------|

| DWG DRAWING NUMBER           |                               |                    | REV.                                                                            | C                  |

|------------------------------|-------------------------------|--------------------|---------------------------------------------------------------------------------|--------------------|

| SCALE                        | SHT                           | OF                 |                                                                                 |                    |

| TARY TO WDC AND SHALL NOT BE | REPRODUCED OF<br>OM WESTERN D | R FURTHER          | DISCLOSED                                                                       | ]                  |

|                              | DWG DRAWING NUMBER            | DWG DRAWING NUMBER | DWG<br>SIZE<br>A<br>SCALE<br>TARY TO WDC AND SHALL NOT BE REPRODUCED OR FURTHER | DWG DRAWING NUMBER |

# Contents

| 1. GENERAL INFORMATION                                                                                                                                                          | 1-1              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Introduction                                                                                                                                                                    | 1-1<br>1-1       |

| How to Use This Document                                                                                                                                                        |                  |

| Board Operation Overview                                                                                                                                                        |                  |

| Architecture                                                                                                                                                                    |                  |

| External Architecture                                                                                                                                                           | 1-4              |

| PWGA-1 Functional Organization                                                                                                                                                  |                  |

|                                                                                                                                                                                 |                  |

| 2. BOARD DESIGN GUIDE                                                                                                                                                           | 2-1              |

| CPU Interface                                                                                                                                                                   | 2-1              |

| VRAM Design and Interface                                                                                                                                                       |                  |

| Video DAC and Interface Subsystem                                                                                                                                               |                  |

| Other Board Design Elements                                                                                                                                                     |                  |

| EPROM<br>PAM-PDM Interface                                                                                                                                                      |                  |

| Configuration Strapping                                                                                                                                                         | -25              |

| Clock Considerations                                                                                                                                                            | -26              |

| 3. SOFTWARE INTERFACE                                                                                                                                                           | 3-1              |

| IBM® 8514/A Compatible Registers                                                                                                                                                |                  |

| DAC Interface                                                                                                                                                                   |                  |

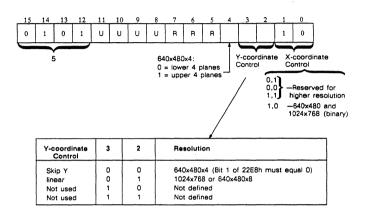

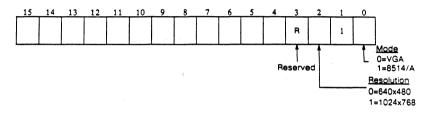

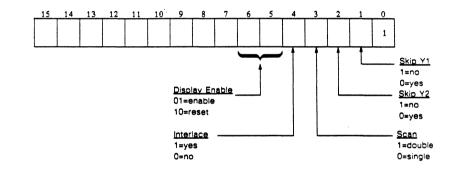

| Graphics Mode Control Register                                                                                                                                                  |                  |

| Display Control Register                                                                                                                                                        |                  |

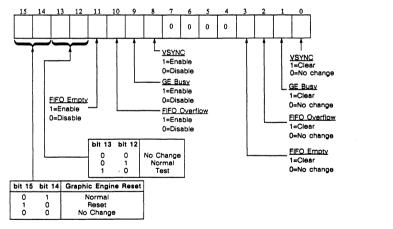

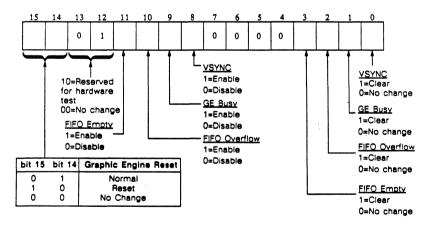

| Interrupt Control Register                                                                                                                                                      | 3-7              |

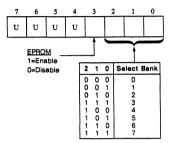

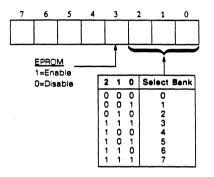

| EPROM Selection Register                                                                                                                                                        |                  |

| BIOS EPROM Memory Location                                                                                                                                                      |                  |

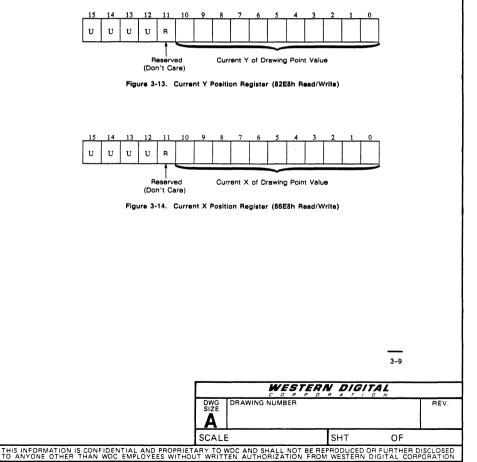

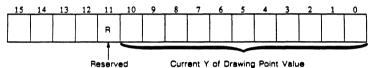

| Current Y Position (CYP) Register                                                                                                                                               |                  |

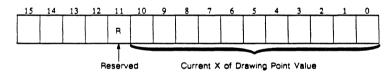

| Current X Position (CXP) Register                                                                                                                                               | 3-9              |

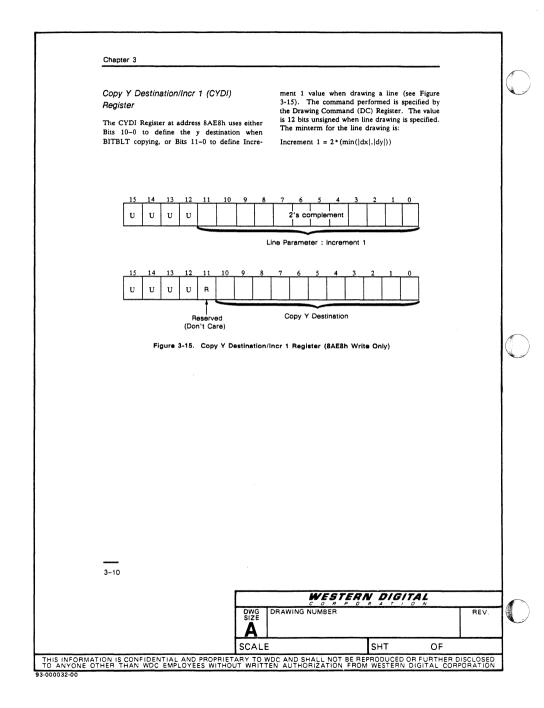

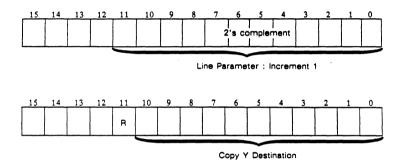

| Copy Y Destination/Incr 1 (CYDI) Register                                                                                                                                       |                  |

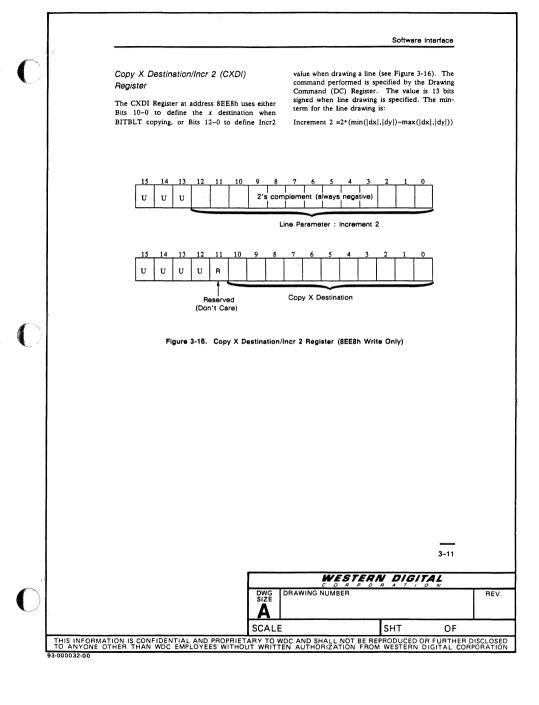

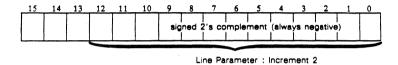

| Copy X Destination/Incr 2 (CXDI) Register                                                                                                                                       |                  |

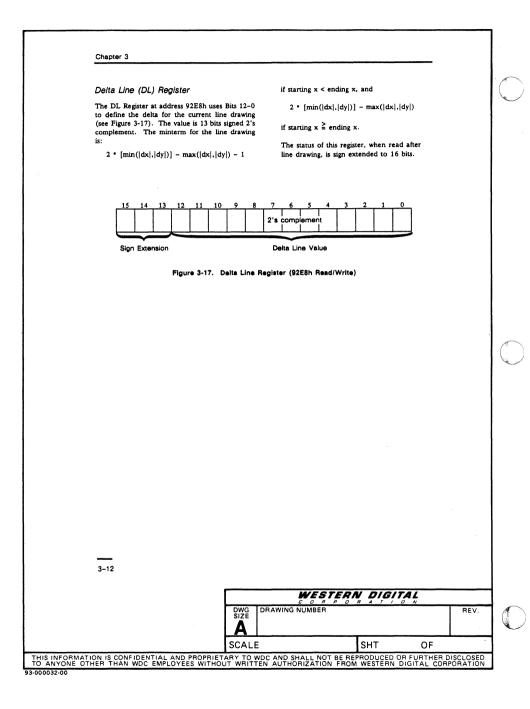

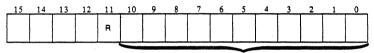

| Rectangle Width/Max (RWM) Register                                                                                                                                              |                  |

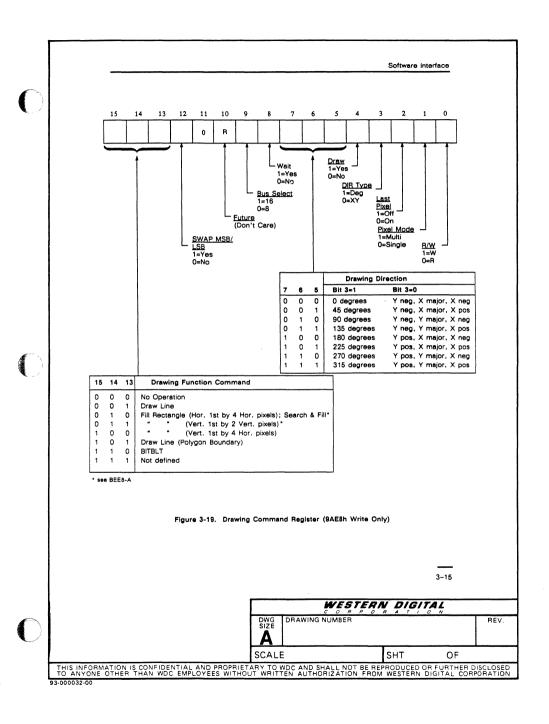

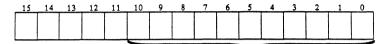

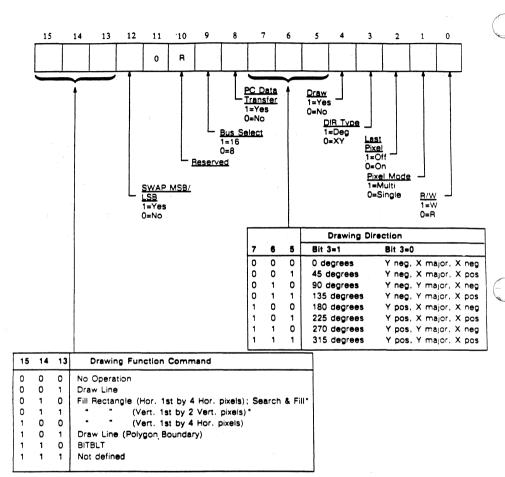

| Drawing Command (DC) Register                                                                                                                                                   |                  |

| -                                                                                                                                                                               |                  |

|                                                                                                                                                                                 | ш                |

| WESTERN DIGITAL                                                                                                                                                                 | <u>,</u>         |

| DWG DRAWING NUMBER                                                                                                                                                              | REV.             |

| SIZE A                                                                                                                                                                          |                  |

| SCALE SHT                                                                                                                                                                       | OF               |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIETARY TO WDC AND SHALL NOT BE REPRODUCED OR FU<br>TO ANYONE OTHER THAN WDC EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DIGI | IRTHER DISCLOSED |

| TO ANYONE OTHER THAN WOO EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DICH                                                                                              | TAL COPPORATION  |

(

C

### Contents

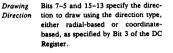

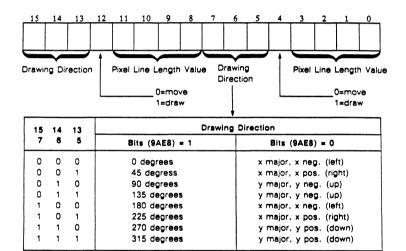

|    | Short-Stroke Vector Control (SSVC) Register |

|----|---------------------------------------------|

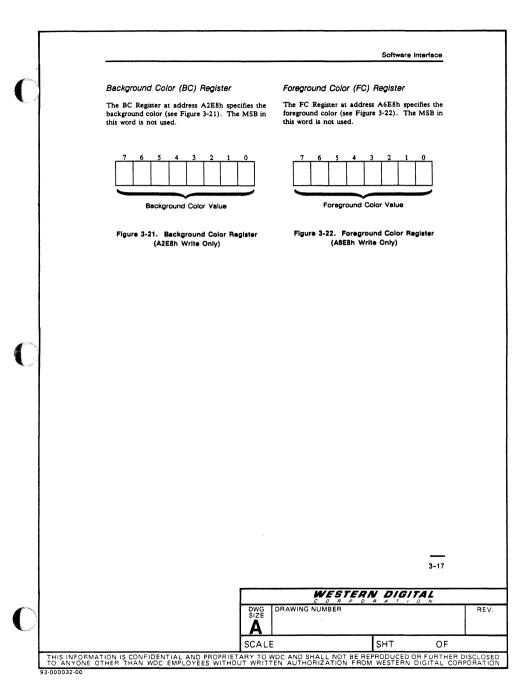

|    | Background Color (BC) Register              |

|    | Foreground Color (FC) Register              |

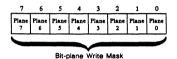

|    | Bit-plane Write Mask (BWM) Register         |

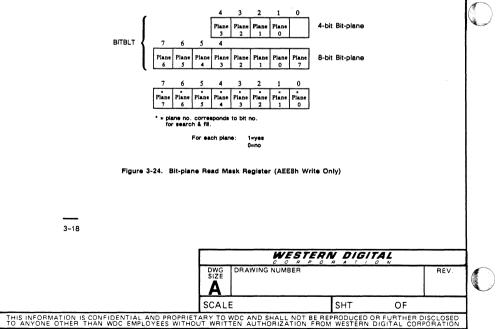

|    | Bit-plane Read Mask (BRM) Register          |

|    | Comparison Color (CC) Register              |

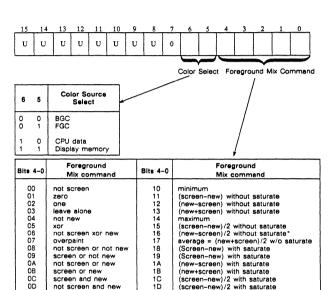

|    | Background Mix (BM) Register                |

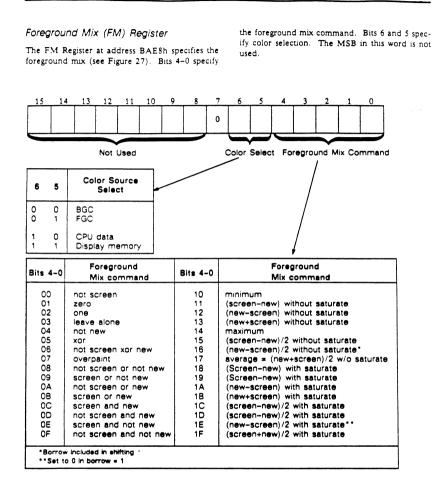

|    | Foreground Mix (FM) Register                |

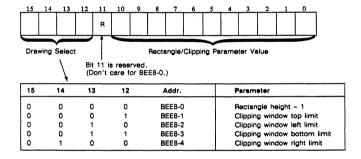

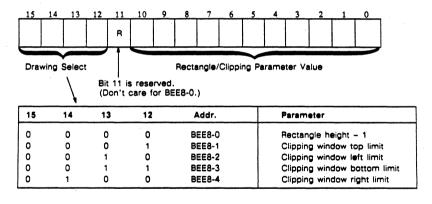

|    | Multifunction Control (MC) Register         |

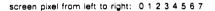

|    | Image Read/Write (IRW) Register             |

|    |                                             |

|    | Status                                      |

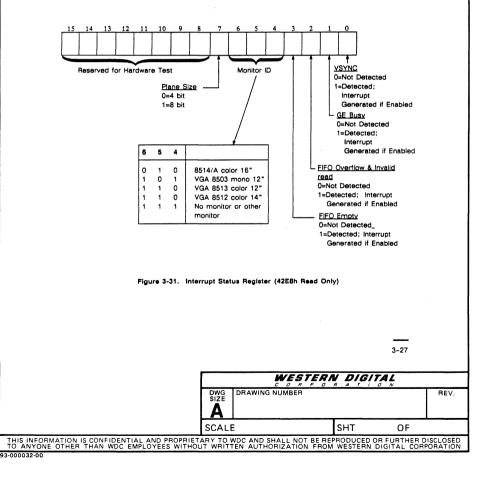

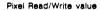

|    | Interrupt Status (IS) Register 3-27         |

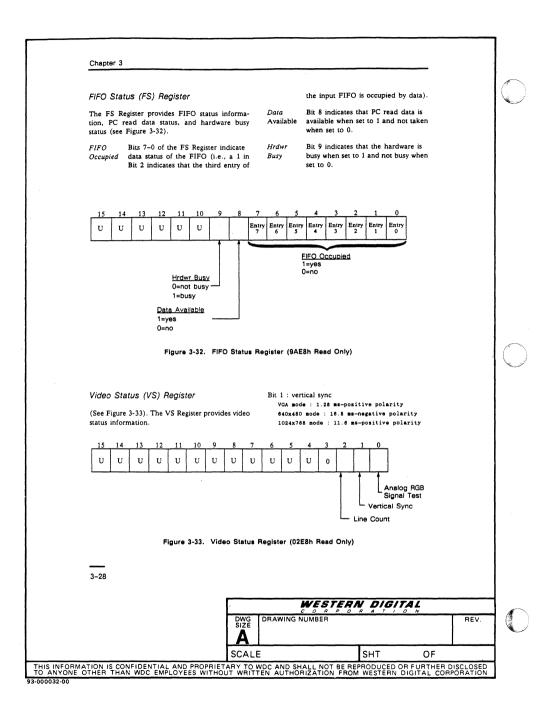

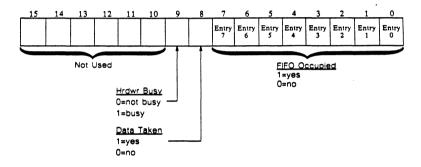

|    | FIFO Status (FS) Register 3-28              |

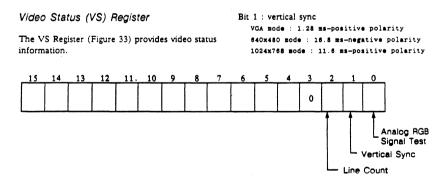

|    | Video Status (VS) Register 3-28             |

|    | Software Interface Extensions               |

|    | Extended Register Operation                 |

|    | Enhanced Solid-Line Drawing                 |

|    | Textured-Line Drawing                       |

|    | Flicker-Free Palette Loading                |

|    |                                             |

| Α. | PIN DESCRIPTION                             |

|    |                                             |

| В. | ELECTRICAL SPECIFICATIONS B-1               |

|    |                                             |

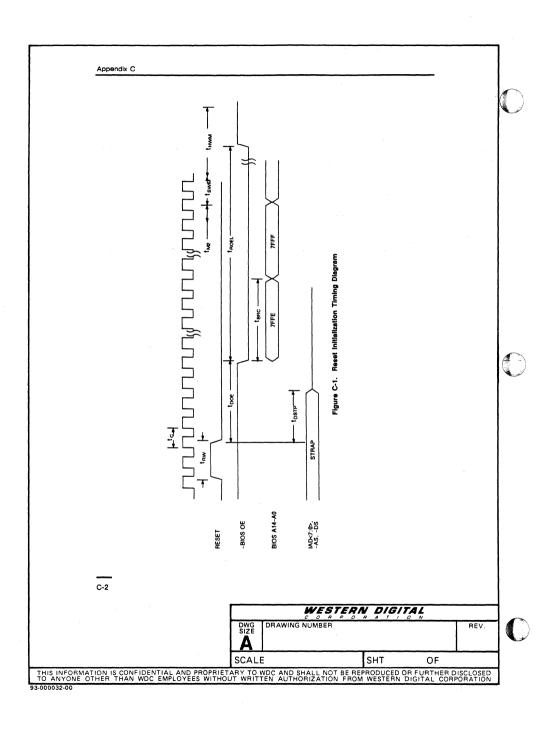

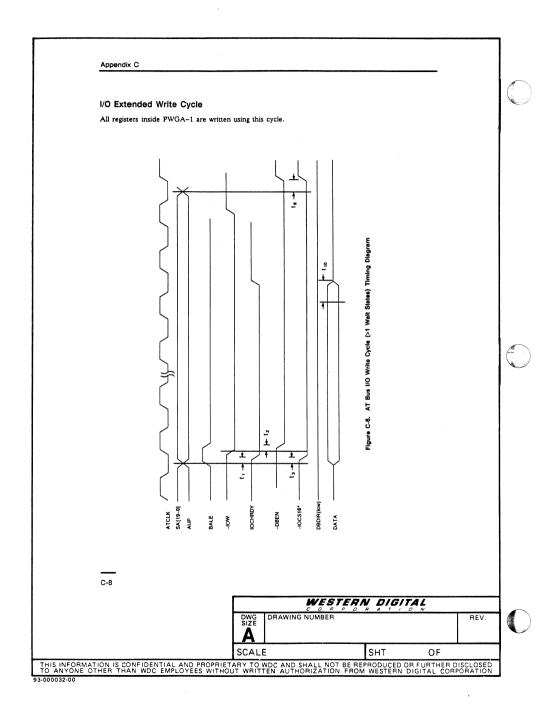

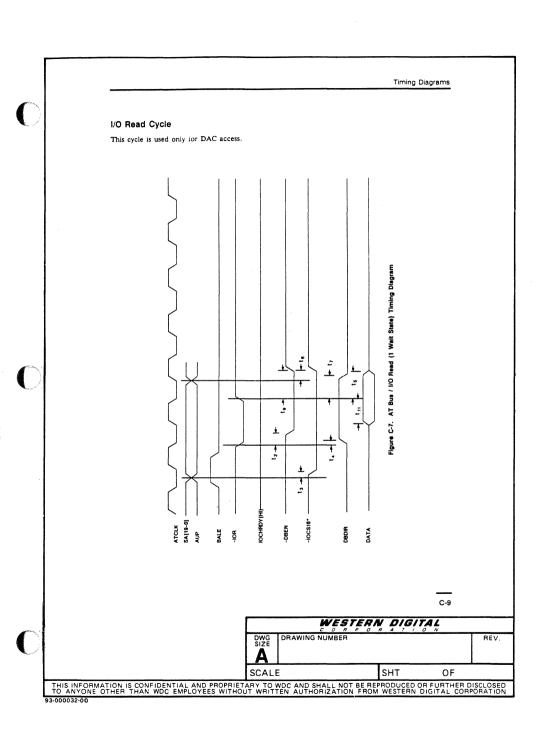

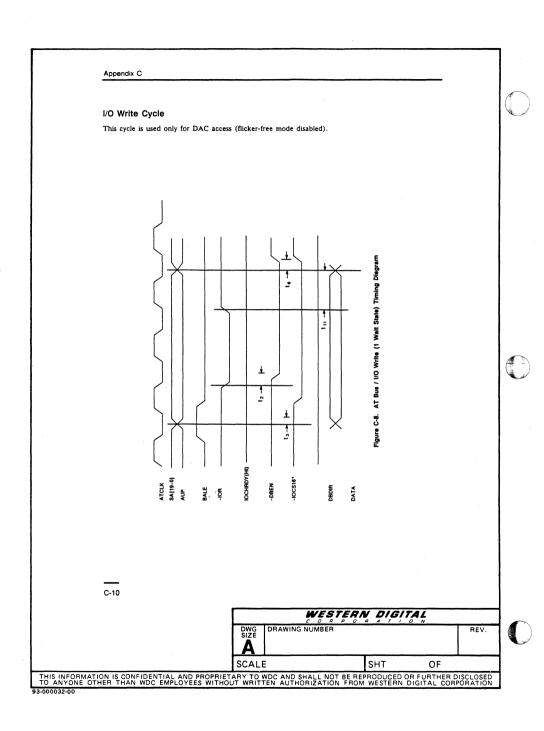

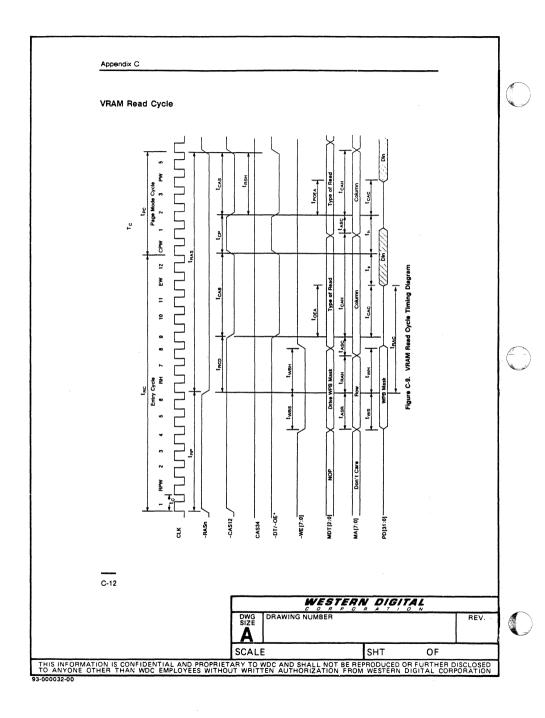

| C. | TIMING DIAGRAMS                             |

| υ. | TIMINO DIAGRAMO                             |

| D  | PIN DIAGRAMS                                |

| υ. | PIN DIAGRAMS                                |

|                                                                                           |             | WESTERI                                           | DIGI    |             |          |   |

|-------------------------------------------------------------------------------------------|-------------|---------------------------------------------------|---------|-------------|----------|---|

|                                                                                           | DWG<br>SIZE | DRAWING NUMBER                                    |         |             | REV.     | L |

|                                                                                           | SCAL        | E                                                 | SHT     | OF          |          |   |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIET<br>TO ANYONE OTHER THAN WDC EMPLOYEES WITHO | TARY TO     | WDC AND SHALL NOT BE RE<br>TEN AUTHORIZATION FROM | WESTERN | R FURTHER D | PORATION |   |

93-000032-00

# General Information

## INTRODUCTION

#### **Product Summary**

The Western Digital Imaging Personal Workstation Graphics Array-1 (PWGA-1) is a set of two proprietary VLSI chips designed to serve as the primary components of intelligent high-resolution color graphics add-in boards for the IBM PS/2 and PC-AT computer systems and compatibles. When the remaining board-level components and software are properly selected and integrated, the PWGA-1 will provide for complete emulation of the IBM Display Adapter 8514/A with superior performance plus functional enhancements (Western Digital extensions). Western Digital Imaging supplies register definitions, Adapter Interface (AI) software and BIOS extension firmware for the on-board EPROM in order to take full advantage of all features, including the unique extensions.

### Feature Notes

- Full functional emulation of the IBM Display Adapter 8514/A, including 100% register-level compatibility.

- Western Digital extension: can be used with PC-AT bus as well as PS/2 Micro Channel with no loss of functionality.

- Performance is 30% to 100% faster than 8514/A in all graphic operations.

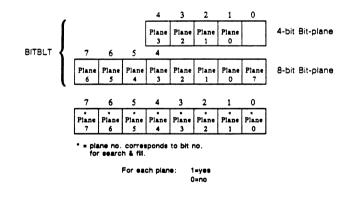

- BITBLT performance four times that of IBM 8514/A in Turbo 4-bit mode using either sixteen 64Kx4 VRAM chips or eight 256Kx4 VRAM chips; Turbo 4-bit mode is two times faster than regular 4-bit or 8-bit mode in BITBLT.

- Western Digital extension: Locked-in feature for a double set of video timing registers to ensure software compatibility when interfacing with different monitors.

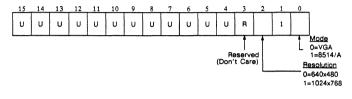

- Pixel resolution supported:

IBM 8514/A emulation: one screen page of 1024x768 pixels or two screen pages of 640x480 pixels, with 16/256 colors simultaneously displayable in both cases (1024x768x4/8 or 2@ 640x480x4/8).

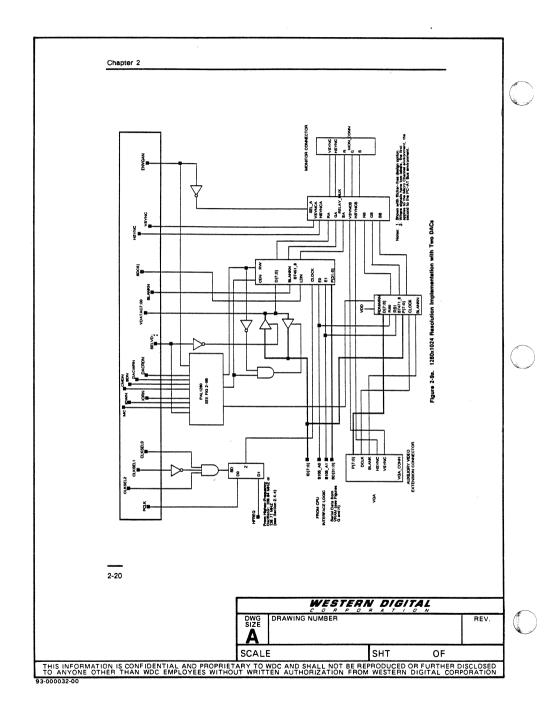

Western Digital extension: Enhanced resolution of one page of 1280x1024 pixels or two pages of 1024x768 pixels, also with 256 displayable colors in both cases (1280x1024x8 or 2@ 1024x768x8).

- Western Digital extension: High-speed hardware generation of textured lines and enhanced solid lines.

- Western Digital extension: Flicker-free video DAC programming option.

- All features, including most extensions, are supported by AI driver software and EPROM BIOS available from Western Digital.

- Supports both 64Kx4 and 256Kx4 video RAM (VRAM) in different speed grade; minimum configuration is four 256Kx4 chips or sixteen 64Kx4 chips. PWGA-1 can optimize performance by selecting different memory cycle timing for different speed grade VRAMs.

- Supports both INMOS and Brooktree video DACs and compatibles, with back-end integration to minimize external glue logic.

- Supports both interlaced and non-interlaced video monitors at up to 70Hz vertical refresh

1-1

|                                                 |             | WESTERN                  | DIGI    | TAL                          |                     |

|-------------------------------------------------|-------------|--------------------------|---------|------------------------------|---------------------|

|                                                 | DWG<br>SIZE | DRAWING NUMBER           |         |                              | REV.                |

|                                                 | SCALE       | 2                        | SHT     | OF                           |                     |

| FIDENTIAL AND PROPRIET,<br>WDC EMPLOYEES WITHOU | ARY TO W    | NDC AND SHALL NOT BE REP | WESTERN | OR FURTHER D<br>DIGITAL CORP | ISCLOSED<br>ORATION |

93-000032-00

THIS INFORMATION IS CON TO ANYONE OTHER THAN

rate. Software written for 8514A interlaced monitors needs no modification for non-interlaced monitors.

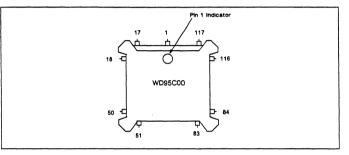

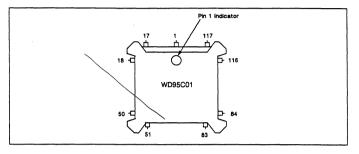

Packaged as two 132-pin Plastic Quad Fine Pitch Packs (PQFPs), fabricated with 1.25 micron CMOS technology.

#### **Options and Advantages**

In addition to full emulation of the IBM 8514/A, which provides intelligent graphics functions such as polyline drawing, pattern fill for rectangles, "areas" (polygons), and "scissoring" (clipping), the PWGA-1 provides several functional enhancements and options as well as superior performance.

A major enhancement is the support of higher screen resolution, 1280x1024 pixels with 256 simultaneously displayable colors, as opposed to the 1024x768 maximum for the IBM 8514/A. Alternatively, the PWGA-1 can support a second screen page at the highest 8514/A resolution.

The PWGA-1 will give end users dramatic speed improvement in almost all graphics operations; in regular 4-bit mode, the PWGA-1 performs Bit Block Transfers (BITBLTs) twice as fast as the IBM 8514/A. In Turbo 4-bit mode, it is four times as fast. In particular, enhanced performance will be obvious when moving large images on the screen (e.g., scrolling). Under turbo mode all horizontal data movement will be twice as fast. This includes BITBLT, rectangle fill, horizontal line, and polygon search and fill.

Users will also notice considerable performance improvement with the PWGA-1 in all new linedrawing operations, because it directly performs several functions that the IBM 8514/A must perform in much slower CPU software. One such improvement is the direct generation of textured lines; another is the automatic, high-speed calculation of line parameters by the PWGA-1, replacing the tedious CPU software procedures with simple specifications of only the beginning and ending points of any line.

Whereas the IBM Display Adapter 8514/A is designed only for use in the PS/2 computer models that use the Micro Channel bus, the PWGA-1 provides an alternate interface to allow full 8514/A functionality (with extensions) for the Micro Channel, and more importantly, for all PC-AT computers and compatibles. The interface selection is made with a single device pin that is "strapped" at board design time.

Many graphics applications result in noticeable screen flickering, when the software steals refresh cycles to modify the color palette in the video DAC. A unique low-cost board design option will provide flicker-free display operation by allowing the PWGA-1 to buffer the new palette values and apply them during the monitor's horizontal retrace (flyback).

PWGA-1-based boards can accommodate both interfaced display monitors, such as the IBM 8514, and non-interfaced monitors; the PWGA-1 will drive either, automatically configuring itself at reset time based on the signals in the monitor interface cable (for IBM-compatible interfaced monitors) or on users' selection through AUTOEXEC.BAT wility. End users can thus exploit cost/performance trade-offs that are not available with the IBM 8514/A board.

Software written directly to 8514/A registers programs the video registers to IBM 8514/A display interlaced timing for 1024x768 resolution. To achieve maximum flexibility for driving different monitors, two sets of video registers are provided: one for 1024x768 resolution and one for 640x480 resolution. These registers can be preprogrammed by the BIOS EPROM at power up and their values locked in so that direct access by software later will not affect the preset video timine.

For the board designer, the PWGA-1 provides several further cost/function/performance tradeoff opportunities, and also saves design time, board space, and component costs by integrating much of the peripheral logic into its design. The designer can choose among several video memory (VRAM) architectures, using either 64Kx4 or 256Kx4 VRAM chips, with back-end logic integrated into the PWGA-1 for 8514/A emulation and extension to two pages of 1024x768x8 (1280x1024 extended resolution requires off-chip logic support). The designer may also exploit the use of different clock rates for the drawing process and the screen refresh process; and bypass design of video data multiplexing and serializing, as these functions are integrated into the PWGA-1 chips.

| 1-2                                                                                         |             |                                                    |            |           |                      |   |

|---------------------------------------------------------------------------------------------|-------------|----------------------------------------------------|------------|-----------|----------------------|---|

|                                                                                             |             | WESTERN                                            | DIGIT      |           |                      |   |

|                                                                                             | DWG<br>SIZE | DRAWING NUMBER                                     |            |           | REV.                 | C |

|                                                                                             | SCALI       | E                                                  | SHT        | OF        |                      |   |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIETA<br>TO ANYONE OTHER THAN WDC EMPLOYEES WITHOU | ARY TO N    | WDC AND SHALL NOT BE REP<br>TEN AUTHORIZATION FROM | WESTERN DI | FURTHER D | ISCLOSED<br>PORATION |   |

| 3-000032-00                                                                                 |             |                                                    |            |           |                      | - |

# HOW TO USE THIS DOCUMENT

This data book is modularized for use in two ways. Chapters 1, 2, and 3 (General Information, Board Design Guide, Software Interface) plus the four appendices (specifications, including summary pin-out, and timing diagrams) contain the information required to use the PWGA-1 chip set in a board design and then use the resulting board in a computer system. In particular, Chapter 2 contains a detailed presentation of pin interfaces as well as guidelines for the selection and configuration of other necessary board-level components.

Note that much of the material in these three chapters is presented in a quasi-tutorial style, for the benefit of readers who may not be expert in advanced graphics hardware.

The following IBM publication may be useful for the board designer: *IBM Personal System* 12 Display Adapter 8514/A Technical Reference, publication no. 68X2248/S68X-2248-0, April 1987.

## BOARD OPERATION OVERVIEW

The functions of any PWGA-1-based board, as well as those of the IBM 8514/A, can be summarized as follows:

A. Screen refresh: A key function is driving the display monitor. The board reads data from its VRAM-stored representation of the screen image, and then converts the data, pixel by pixel, into RGB signals for the display monitor, in synchronization with the sweeping of the monitor's RGB guns across its screen.

B. Drawing: The other major board function, less time-critical than screen refresh, is the generation of new lines and areas within VRAM in response to commands from the system CPU. In this context, "drawing" includes filling polygonal shapes with patterns, establishing boundaries for "scissoring" (clipping), and similar operations. Drawing operations can involve complex algorithms, and they require correspondingly sophisticated processing by the PWGA-1.

C. Image transfer: In most graphics work, it is common to save board-drawn images (e.g., popup menu) elsewhere in main system memory and/ or on disk for later restoration to on-board video memory and thence to the display screen.

D. VGA input: The host CPU may request that the monitor be driven by the VGA (Video Graphics Array), a similar but less sophisticated graphics facility located elsewhere in the system: in this case the PWGA-1-based board (or the 8514/A) essentially becomes a passive pass-through channel, taking video data and sync signals from the "auxiliary video extension" bus connector. Note that another monitor can be attached directly to the VGA; if the PWGA-1-based board (or 8514/A) is not in pass-through mode, then the two monitors can simultaneously display different images.

E. Palette loading: Pixel color interpretation is mediated by a small "palette" memory in the video DAC on the board. The CPU can very rapidly effect changes on the screen by changing the contents of this memory, as distinct from issuing drawing commands. The palette is further discussed in the next section.

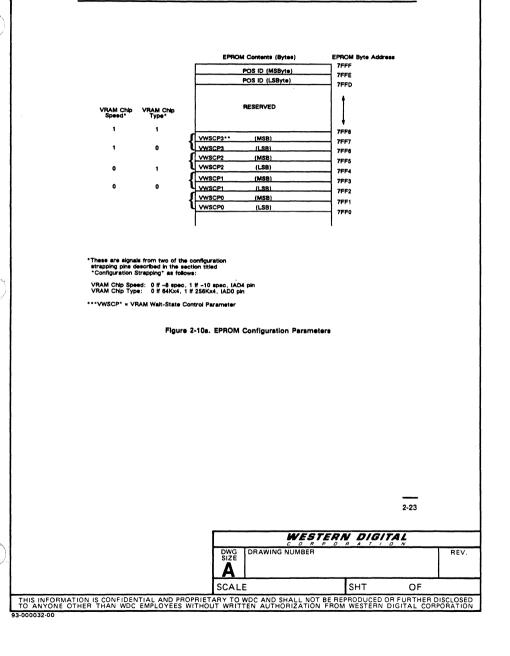

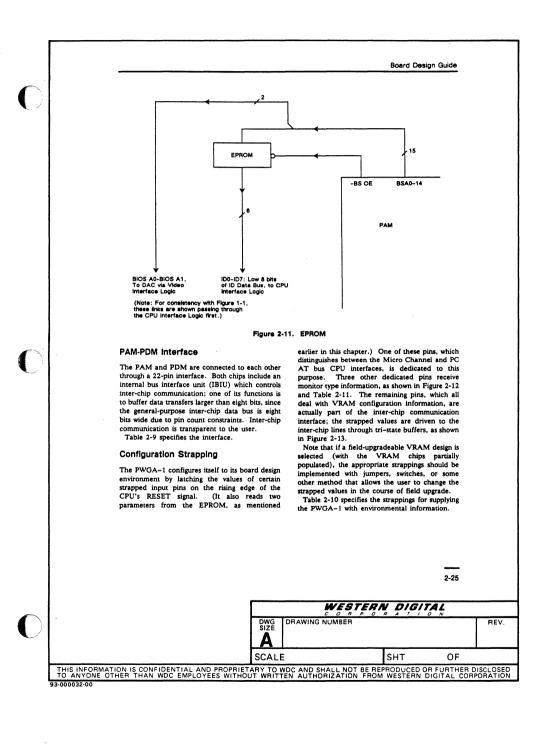

F. EPROM access: The board includes a small EPROM containing a BIOS extension available to the CPU. The EPROM is mainly for initialization and diagnostic testing during power up. (Note that a portion of EPROM contains certain board configuration information read by the PWGA-1 upon power up.)

G. Other: Finally, the board design must provide for customary CPU handshaking, interrupts, and miscellaneous bus interface signals.

1-3

|                        |          | WESTERA                                           | DIGITA     | 4 <u>/</u> |                      |

|------------------------|----------|---------------------------------------------------|------------|------------|----------------------|

|                        |          | DRAWING NUMBER                                    |            |            | REV.                 |

|                        | SCALE    |                                                   | SHT        | OF         |                      |

| FIDENTIAL AND PROPRIET | ARY TO W | VDC AND SHALL NOT BE REP<br>EN AUTHORIZATION FROM | WESTERN DI | FURTHER D  | ISCLOSED<br>PORATION |

93-000032-00

THIS INFORMATION IS CON TO ANYONE OTHER THAN

# ARCHITECTURE

#### **External Architecture**

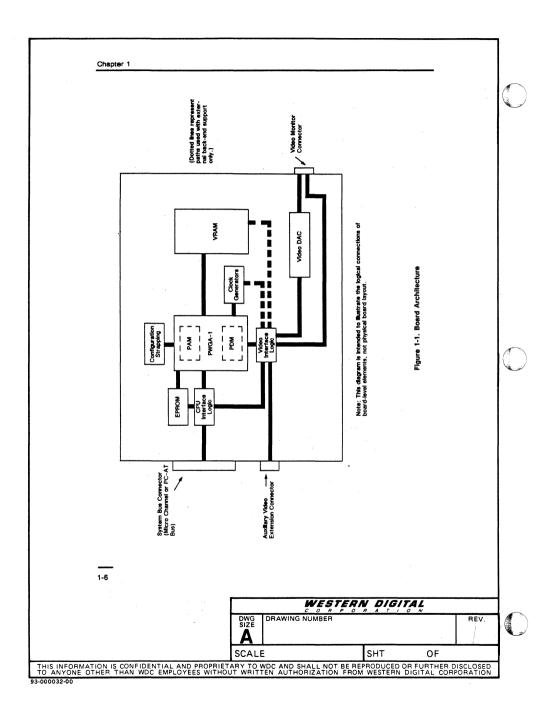

Figure 1-1 illustrates the logical architecture of a PWGA-1-based board in block-diagram style. Each of its major elements, which for now are presented as functional "black boxes," is discussed below.

The PWGA-1 (Western Digital Personal Workstation Graphics Array-1) consists of two 132-pin chips: the PAM (Pixel Address Manager) and the PDM (Pixel Data Manager). The next sections provide a brief explanation of the internal components of the PAM and PDM; their detailed architecture and operation are discussed in the proprietary portion of this document, in Chapters 4 and 5, respectively.

The VRAM block in Figure 1-1 represents the video memory subsystem, used to store screen images generated in the PWGA-1 (as a result of CPU drawing instructions) or sent from the CPU (typically for the purpose of restoring previously drawn images that had been stored elsewhere in the system). The PWGA-1 then accesses these images for automatic display-screen refresh. Drawing operations take place within a pixel coordinate space of 2K by 2K; similar to the 8514/A, remaining VRAM storage is available to the PWGA-1 and the CPU for "off-screen" use, including storage of fill patterns and scratchpad data. Chapter 2 describes VRAM operation, presents a selection of configuration choices, and defines the detailed interface of the VRAM subsystem to the PWGA-1 chip set.

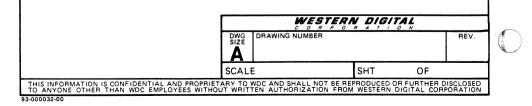

In the standard board configuration, the PWGA-1 is responsible for serializing and multiplexing data extracted from VRAM for screen refresh, and then forwarding the data to the DAC via the video interface logic block. In VRAM archliectures using external back-end support, which is necessary to achieve 1280x1024 pixel resolution, serializing and multiplexing is done within the VRAM block, and the resultant screen refresh data bypasses the PWGA-1, as shown in Figure 1-1.

The video DAC (Digital-to-Analog Converter) has the primary function of generating analog intensity signals for the red, blue, and green guns of the display monitor, varying these values in synchronization with pixel coordinates as the guns sweep across the screen. The source of these values is the "pixel data" that the PWGA-1 reads out of VRAM in its screen refresh operation. With external back-end support, extra intelligence is required in the DAC to assist in the data formatting begun in the serializing and multiplexing logic within the VRAM block.

The DAC contains the color palette, a small memory that maps a given pixel data value into a specific combination of RGB intensities, according to the contents of each of the cells in palette memory. For example, in a 256-color arrangement, an eight-bit pixel data value selects one of 256 palette memory cells. Each of the latter have been loaded with an 18-bit datum partitioned into three 6-bit fields whose values are in turn converted into red, blue, and green signal intensities when that cell is selected. Palette values may be loaded directly from the CPU, or, with the Western Digital flicker-free option, indirectly through the PWGA-1.

The video DAC and its interfaces, the auxiliary video extension (used to drive the monitor from an off-board source, normally the system VGA), the monitor interface, and other related logic and interfaces together comprise the "video DAC and interfaces together comprise the "video DAC and interfaces together comprise the "video DAC and interface subsystem," described in detail in Chapter 2. Note that the small block in Figure 1-1 labelled "Video Interface Logic" represents only a modest amount of logic and, in fact, consits largely of pass-through routing of signals; the block is drawn chiefly for convenience in explanation.

The CPU Interface Logic block contains the bus transceivers and TTL glue logic necessary to interface the PWGA-1 chips to the system bus (either the IBM PS/2 Micro Channel or the IBM PC-AT bus, or compatible buses). This block also provides a data path to the DAC, used by the CPU to directly access palette values, and to the EPROM. The CPU interface logic is described in detail in Chapter 2.

The remaining board elements are the EPROM (containing Western Digital-supplied BIOS extension firmware), the clock generators, and a grouping of minor components (pull-up/down logic and DIP switches) used by the PWGA-1 to sense its environmental configuration: whether Micro Channel or AT bus, VRAM organization, etc. These elements are described in Chapter 2, together with the inter-chip (PAM-PDM) connections.

| 1-4                                                                                       |                                                                 |                                               |                    |   |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------|--------------------|---|

|                                                                                           | WESTERA                                                         | DIGITAL                                       |                    |   |

|                                                                                           | DWG DRAWING NUMBER                                              |                                               | REV.               | C |

|                                                                                           | SCALE                                                           | SHT OF                                        |                    |   |

| HIS INFORMATION IS CONFIDENTIAL AND PROPRIETA<br>O ANYONE OTHER THAN WDC EMPLOYEES WITHOU | ARY TO WDC AND SHALL NOT BE REP<br>T WRITTEN AUTHORIZATION FROM | RODUCED OR FURTHER DI<br>WESTERN DIGITAL CORP | SCLOSED<br>ORATION |   |

| 000032-00                                                                                 |                                                                 |                                               |                    |   |

#### General Information

Finally, the PWGA-1 contains a set of user-accessible internal registers that are compatible with those on the IBM 8514/A board, plus certain extra registers to support Western Digital extensions. From the user's point of view, the registers exist chiefly as destinations for software commands ('orders,' in IBM terminology) and their parameters. User programming considerations required to exploit the Western Digital extensions are discussed in Chapter 3.

#### **PWGA-1 Functional Organization**

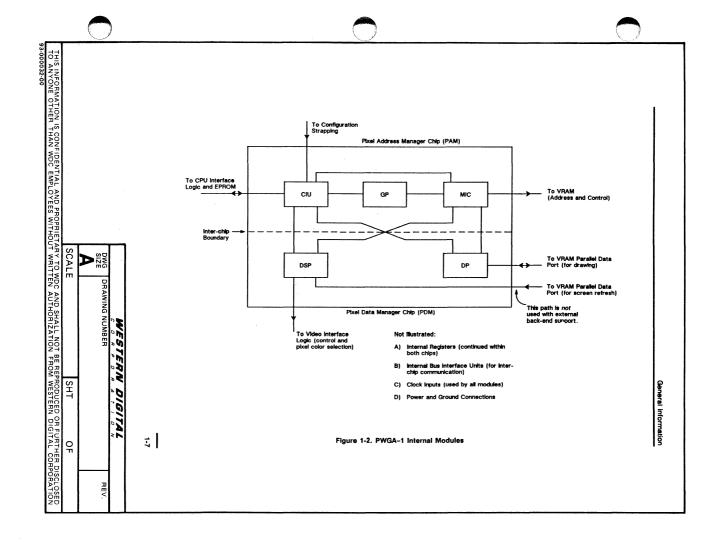

Figure 1-2 introduces the internal functional blocks of the PAM and PDM chips. Communication between the two chips is mediated by two Internal Bus Interface Units (IBIUs); they are transparent to user operations, and are not shown in the diagram.

In addition to the internal registers and the IBIUs, the functional modules within the PWGA-1 are as follows:

Within the PAM: CIU: CPU Interface Unit GP: Graphics Processor MIC: Memory Interface Controller

Within the PDM: DP: Data Processor DSP: Display Processor

The CIU controls communication with the system bus (via the CPU interface logic block external to the chip set), and passes data to and from all the other units on the chip set. It also performs certain miscellaneous functions, such as forwarding addresses from the system bus to the EPROM.

The GP performs the actual drawing computations; it supports all 8514/A graphics modes, plus Western Digital extensions. The modes include line drawing, fill area outline drawing (arbitrary polygons), rectangle drawing, image transfer from the CPU, BITBLT copying (Bit Block Transfer within VRAM), and scissoring. The GP receives its drawing instructions from the CIU and sends the resulting pixel coordinates to the MIC. The MIC controls VRAM addressing and access. In a typical drawing operation, it will convert the GP-supplied pixel coordinates into VRAM addresses, cause the VRAM to send the addressed data (pixel color values) to the DP for modification, and then rewrite back into VRAM. When not involved in a drawing or special-purpose access, the MIC manages the VRAM addressing portion of the constantly on-going screen refresh process. The MIC gives screen refresh the highest priority for VRAM access; next is timerbased VRAM chip refresh, with GP-requested drawing access given the lowest priority.

The DP is responsible for updating VRAM in support of drawing and data transfer operations and altering pixel data (color values) according to masks and parameters, including "mix" specifications supplied in shared internal registers by the DP and GP. The DP receives pixel data on a bidirectional bus from VRAM, modifies it, and then writes it back on the same bus.

The DSP manages the DAC and monitor, coordinating its role in the screen refresh process with the MIC. With an integrated back-end support VRAM design, the DSP serializes and multiplexes pixel data, "pumped" out of VRAM by the MIC, to the DAC, in synchronization with the timing of the monitor's sweep across the display screen. (With external back-end support, this DSP function is assumed by extra logic within the VRAM block and the DAC.)

#### **Test Considerations**

To facilitate board testing, all output pins of both PAM and PDM can be disabled during Reset through the test strap pin (Bit 6 of IAD bus).

If the test strap pin is low, all output signals except SLD are tri-stated. SLD is tri-stated if TSEL2-TSEL0 are also high.

For PC board in-circuit test, the test strap pin should be low and TSEL2-TSEL0 should be high. All bi-directional pins are forced to be input. All input and bi-directional pads have internal pull-up resistors, therefore they are high if not actively driven low.

1-5

WESTERN DIGITAL

DWG

DRAWING NUMBER

DIG

DRAWING NUMBER

SIZE

DRAWING NUMBER

REV.

SCALE

SCALE

SHT

THIS INFORMATION IS CONFIDENTIAL AND PROPRIETARY TO WDC AND SHALL NOT BE REPRODUCED OR FURTHER DISCLOSED

TO ANYONE OTHER THAN WDC EMPLOYEES WITHOUT WRITTEN AUTHORIZATION FROM WESTERN DIGITAL CORPORATION

S000032-00

| 1-8                                                                                         |             |                                                    |            |           |                      |  |

|---------------------------------------------------------------------------------------------|-------------|----------------------------------------------------|------------|-----------|----------------------|--|

|                                                                                             |             |                                                    |            |           |                      |  |

|                                                                                             |             | WESTERN<br>C                                       | DIGITA     |           |                      |  |

|                                                                                             | DWG<br>SIZE | DRAWING NUMBER                                     |            |           | REV.                 |  |

|                                                                                             | Α           |                                                    |            |           |                      |  |

|                                                                                             | SCAL        | E                                                  | SHT        | OF        |                      |  |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIETA<br>TO ANYONE OTHER THAN WDC EMPLOYEES WITHOU | ARY TO      | WDC AND SHALL NOT BE REP<br>TEN AUTHORIZATION FROM | WESTERN DI | FURTHER D | ISCLOSED<br>PORATION |  |

| 93-000032-00                                                                                |             |                                                    |            |           |                      |  |

# **2** Board Design Guide

# **CPU INTERFACE**

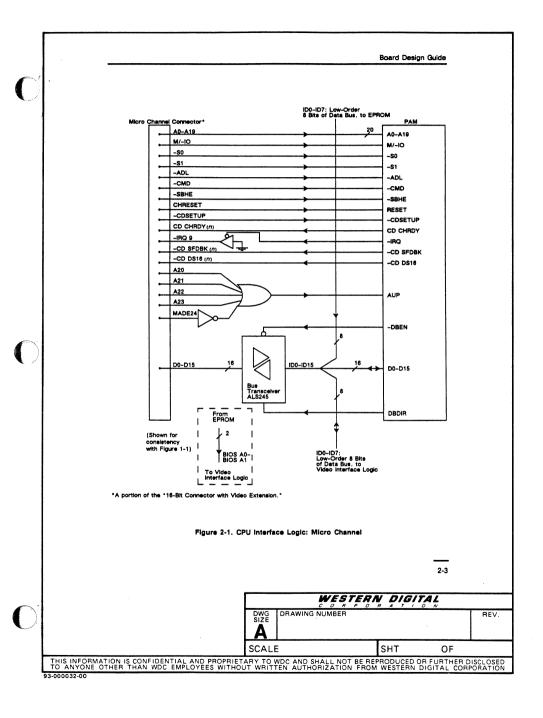

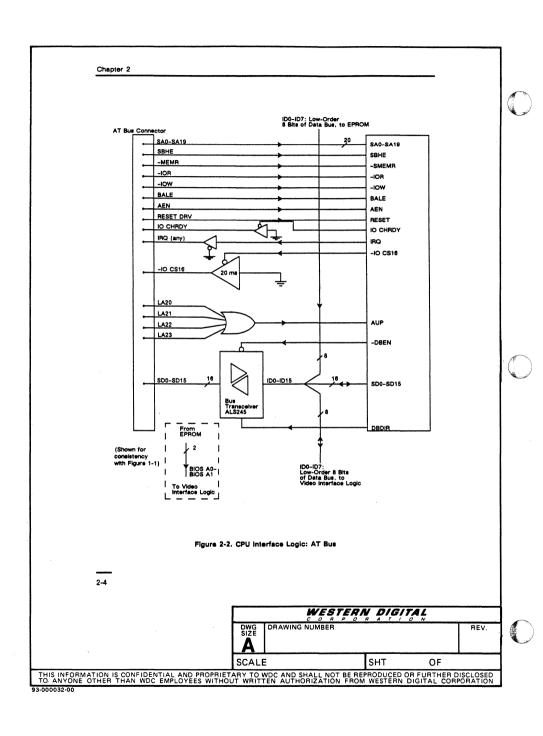

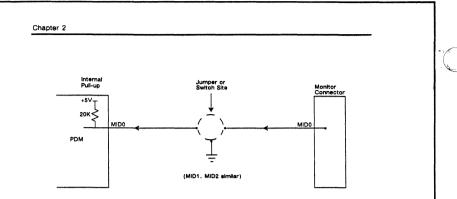

The PAM provides interface pins to connect to either the IBM PS/2 Micro Channel or the AT bus via a small amount of external logic, illustrated in Figures 2-1 and 2-2. The CIU configures itself for one of the two different interfaces according to the value of a configuration strapping pin, described later in this chapter (Table 2-10). Because of the two possible external environments, most of these CPU interface pins have two alternate interpretations, as shown in the following tables. In both cases, however, the names and uses of most of these pins correspond precisely to the IBM specifications for the Micro Channel or AT bus, and so do not need special explanation.

Table 2-1. CPU Interface Pins (PAM) for Micro Channel Interface (see Figure 2-1)

| Name      | PAM Pin #      | I/O | Description                                                                                                                                                                    |

|-----------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A19    | 62-69, 71-82   | I   | CPU address Bits 0 through 19                                                                                                                                                  |

| AUP       | 85             | I   | Decoding of upper CPU address Bits<br>23-20, plus MADE24; all these should be<br>0 if the lower 20 bits of address are to be<br>considered valid for the PWGA-1-based<br>board |

| M/-IO     | 57             | I   | Distinguishes memory access from I/O access                                                                                                                                    |

| -S0       | 59             | I   | -Status Bit 0                                                                                                                                                                  |

| -S1       | 58             | I   | -Status Bit 1                                                                                                                                                                  |

| -ADL      | 61             | I   | -Address Latch                                                                                                                                                                 |

| -CMD      | 60             | I   | -Command                                                                                                                                                                       |

| -SBHE     | 56             | I   | -System Byte High Enable                                                                                                                                                       |

| RESET     | 52             | I   | Channel Reset                                                                                                                                                                  |

| -CDSETUP  | 86             | I   | -Card Setup                                                                                                                                                                    |

| CD CHRDY  | 90             | 0   | Channel Ready                                                                                                                                                                  |

| -IRQ      | 88             | ο   | -Interrupt Request; tied to Micro Channe<br>-IRQ 9                                                                                                                             |

| -CD SFDBK | 89             | ο   | -Card Selected Feedback                                                                                                                                                        |

| -CD DS16  | 55             | ο   | -Card Data Size 16                                                                                                                                                             |

| -DBEN     | 91             | 0   | -Data Bus Enable                                                                                                                                                               |

| D0-D15    | 94-98, 100-110 | I/O | CPU Data Bits 0 through 16                                                                                                                                                     |

| DBDIR     | 92             | ο   | Data Bus Direction (high for CPU read,<br>low for CPU write)                                                                                                                   |

2-1

93-000032-00

| Table 2-2. CPU Interface Pins (PAM) for AT Bus Interface (see Figure 2-2) |                |     |                                                                                                                                                                |  |

|---------------------------------------------------------------------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                                                      | PAM Pin #      | I/O | Description                                                                                                                                                    |  |

| SA0-SA19                                                                  | 62-69, 71-82   | I   | CPU address Bits 0 through 19                                                                                                                                  |  |

| AUP                                                                       | 85             | I   | Decoding of upper CPU address Bits<br>23-20; all these should be 0 if the lower<br>20 bits of address are to be considered<br>valid for the PWGA-1-based board |  |

| -SBHE                                                                     | 56             | I   | -System Bus High Enable                                                                                                                                        |  |

| -MEMR                                                                     | 57             | I   | -Memory Read                                                                                                                                                   |  |

| -MEMW                                                                     | 59             | I   | -Memory Write                                                                                                                                                  |  |

| -IOR                                                                      | 58             | I   | -I/O Read                                                                                                                                                      |  |

| -IOW                                                                      | 60             | I   | -I/O Write                                                                                                                                                     |  |

| BALE                                                                      | 61             | I   | Buffered Address Latch Enable                                                                                                                                  |  |

| AEN                                                                       | 86             | I   | Address Enable                                                                                                                                                 |  |

| RESET                                                                     | 52             | I   | System Reset                                                                                                                                                   |  |

| I/O CHRDY                                                                 | 90             | ο   | I/O Channel Ready                                                                                                                                              |  |

| IRQ                                                                       | 88             | 0   | Interrupt Request; tied to any AT bus interrupt line                                                                                                           |  |

| -I/O CS16                                                                 | 55             | 0   | -I/O 16-bit Chip Select                                                                                                                                        |  |

| -DBEN                                                                     | 91             | 0   | –Data Bus Enable                                                                                                                                               |  |

| SD0-SD15                                                                  | 94-98, 100-110 | I/O | CPU Data Bits 0 through 16                                                                                                                                     |  |

| DBDIR                                                                     | 92             | ο   | Data Bus Direction (high for CPU read,<br>low for CPU write)                                                                                                   |  |

| ATCLK                                                                     | 84             | I   | AT Bus Clock                                                                                                                                                   |  |

# VRAM DESIGN AND INTERFACE

The PWGA-1 supports four VRAM designs. Each of these in turn can be implemented with two or three levels of chip population, for a total of ten implementations. The design choice depends on the desired combination of the following criteria (with only certain combinations possible):

- pixel resolution: 640x480, 1024x768, or 1280x1024

- pixel depth: 4 or 8 bits per pixel

- number of screen pages: one or two

- size of VRAM chips to be used: 64Kx4 or 256Kx4

- number of VRAM chips (and hence board size)

- field upgradeability

- type of design: with back-end support (serializing and multiplexing of pixel data for screen refresh) integrated within the PWGA-1, or with external back-end support

External back-end support-which includes use of a more sophisticated DAC-is required to achieve 1280x1024 resolution.

| 2-2                                                                                         |                                                                |                                             |          |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------|----------|

| ]                                                                                           | WESTERN                                                        | DIGITAL                                     |          |

|                                                                                             | DWG DRAWING NUMBER                                             |                                             | REV.     |

|                                                                                             | SCALE                                                          | SHT OF                                      |          |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIETA<br>TO ANYONE OTHER THAN WDC EMPLOYEES WITHOU | RY TO WDC AND SHALL NOT BE REP<br>T WRITTEN AUTHORIZATION FROM | RODUCED OR FURTHER D<br>WESTERN DIGITAL COR | PORATION |

| 93-000032-00                                                                                | 4                                                              |                                             | ÷,       |

Board Design Guide

| I/E* | Chip<br>Size | No. of<br>Chips | Pixel<br>Resolution | Pixel<br>Depth | # of Screen<br>Pages | S/W** |

|------|--------------|-----------------|---------------------|----------------|----------------------|-------|

| I    | 64Kx4        | 16              | 1024x768            | 4              | 1                    | S     |

|      |              |                 | 640x480             | 4              | 2                    | S     |

|      |              | 32              | 1024x768            | 8              | 1                    | S     |

|      |              |                 | 1024x768            | 4              | 2                    | w     |

|      |              |                 | 640x480             | 8              | 1                    | S     |

| I    | 256Kx4       | 4               | 1024x768            | 4              | 1                    | s     |

|      |              |                 | 640x480             | 4              | 2                    | S     |

|      |              | 8               | 1024x768            | 8              | 1                    | S     |

|      |              |                 | 1024x768            | 4              | 2                    | w     |

|      |              |                 | 640x480             | 8              | 1                    | S     |

|      |              | 16              | 1024x768            | 8              | 2                    | w     |

|      |              |                 | 1024x768            | 4              | 2                    | w     |

|      |              |                 | 640x480             | 8              | 2                    | w     |

| Е    | 256Kx4       | 8               | 1280x1024           | 4              | 1                    | w     |

|      |              |                 | 1024x768            | 8              | 1                    | S     |

|      |              |                 | 1024x768            | 4              | 2                    | w     |

|      |              |                 | 640x480             | 8              | 1                    | S     |

|      |              | 16              | 1280x1024           | 8              | 1                    | w     |

|      |              |                 | 1024x768            | 8              | 2                    | w     |

|      |              |                 | 1024x768            | 4              | 2                    | w     |

|      |              |                 | 640x480             | 8              | 2                    | w     |

Table 2-3. VRAM Parameters

W = Western Digital extension to 8514/A capability

The capabilities of the various VRAM designs, with their several levels of chip population, are shown in Table 2-3. Note: Although not shown, each level of chip loading for a given design includes the capabilities of the smaller chip population(s).

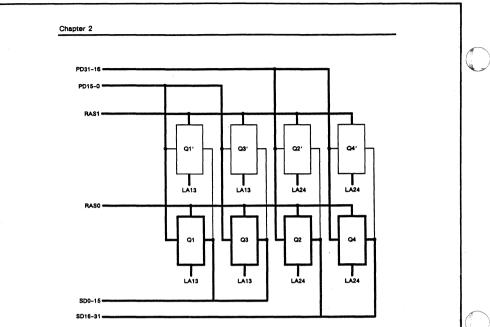

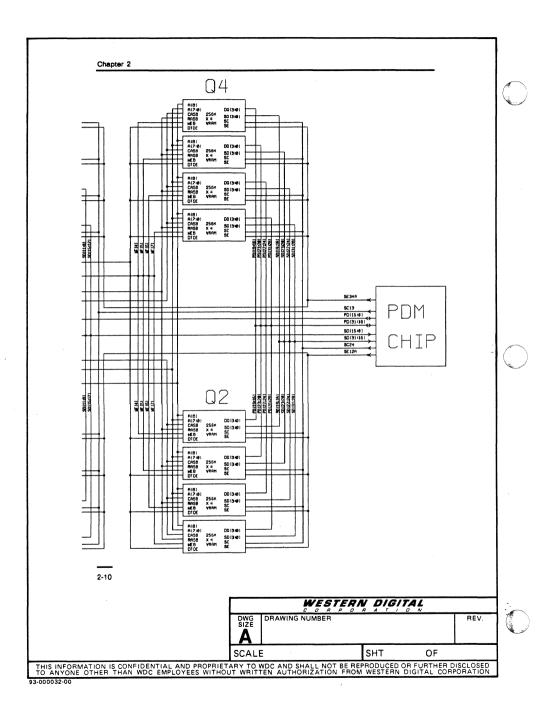

Since the 16-chip implementation of 64Kx4 of this design cannot support maximum IBM 8514/A resolution, the 32-chip version, shown in Figure 2-3, will typically form the basis for board design except for special applications. Figure 2-3 does, however, illustrate which chip positions should be left unpopulated if a 16-chip field-upgradeable version is to be produced.

If maximum IBM 8514/A resolution is desired, this design should be implemented to at least the

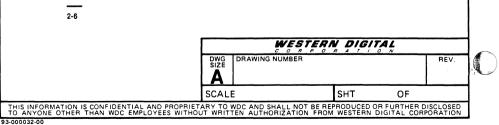

8-chip 256Kx4 level; implementation at the 16-chip level provides for the extended capability of doubling the number of screen pages supported by the 8-chip version. Figure 2-4 illustrates the 16-chip version with indications of which chips should be left unpopulated if field upgradeable 4-chip and/ or 16-chip versions are to be produced. The same diagram can also serve as the basis for an 8-chip design, with half of those chips omitted for future field upgrade if desired.

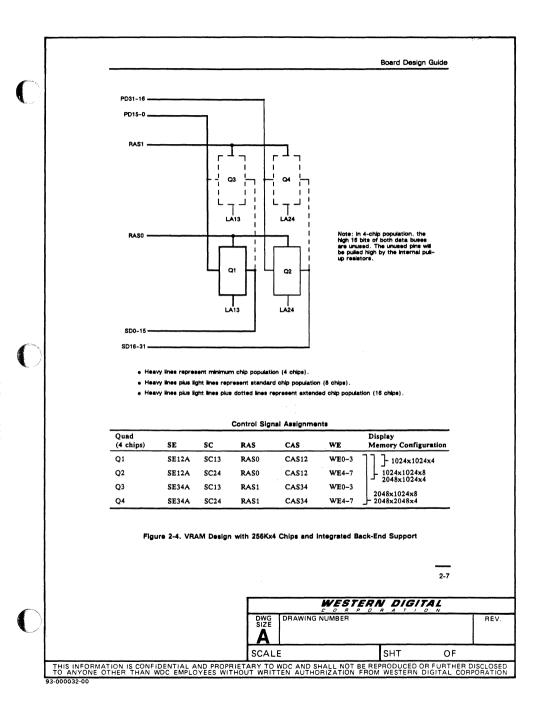

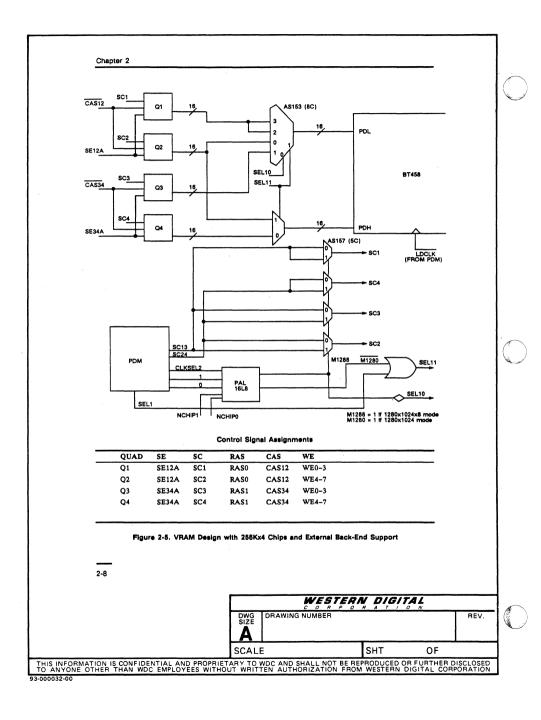

Figure 2-5 illustrates the 16-chip version with 256Kx4 VRAMS and external backend support. A Brooktree 8-bit video DAC BT458 is used. Figure 2-6 shows the detail connections for 256Kx4 VRAMs to PAM and PDM.

• Heavy lines represent minimum chip population (16 chips). · Heavy lines plus light lines represent standard chip population (32 chips).

Control Signal Assignments

| Quad<br>(4 chips) | SE    | SC   | RAS  | CAS   | WE    | Display<br>Memory Configuration |

|-------------------|-------|------|------|-------|-------|---------------------------------|

| Q1                | SE12A | SC13 | RAS0 | CAS12 | WE0-3 | 77                              |

| Q2                | SE12A | SC24 | RAS0 | CAS12 | WE4-7 | - 1024x1024x4                   |

| Q3                | SE34A | SC13 | RAS0 | CAS34 | WE0-3 | 10242102424                     |

| Q4                | SE34A | SC24 | RAS0 | CAS34 | WE4-7 |                                 |

| Q1'               | SE12B | SC13 | RAS1 | CAS12 | WE0-3 | 1024x1024x8                     |

| Q2'               | SE12B | SC24 | RAS1 | CAS12 | WE4-7 | - 2048x1024x4                   |

| Q3'               | SE34B | SC13 | RAS1 | CAS34 | WE0-3 |                                 |

| Q4'               | SE34B | SC24 | RAS1 | CAS34 | WE4-7 |                                 |

Board Design Guide

| Pin Name | PAM Pin # | Description                                                                                                                                                                                      |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA7-MA0  | 19, 16-10 | Low-order address lines, into all quads. For 64Kx4<br>designs, MA7 is not used; for 256Kx4 chips, all eight<br>lines are used.                                                                   |

| LA13     | 34        | Used as high-order address bit (MA8) for quads Q1, Q3, and their "" counterparts, in all designs.                                                                                                |

| LA24     | 35        | Used as high-order address bit (MA8) for quads Q2, Q4, and their "" counterparts, in all designs.                                                                                                |

| -RAS0    | 22        | Row Address Strobe 0                                                                                                                                                                             |

| -RAS1    | 23        | Row Address Strobe 1                                                                                                                                                                             |

| -CAS12   | 20        | Column Address Strobe 1                                                                                                                                                                          |

| -CAS34   | 21        | Column Address Strobe 2                                                                                                                                                                          |

| WE7-WE0  | 31-24     | Pixel data Write Enable lines to enable writing into<br>VRAM on the PD bus (bidirectional Parallel Data bus,<br>between VRAM and DP; see below). A given quad<br>receives either WE0-3 or WE4-7. |

| -DT/-OE  | 32        | Transfer-cycle control and serial data output enable, used by all quads.                                                                                                                         |

Table 2-4. PAM Pin Interface to VRAM

Certain interfacing information is common to all VRAM designs. For example, all designs use the concept of "quadding" the VRAM chips into groups of four, with each of the four chips in a "quad" receiving the same control signals. (The write enable lines are an exception; the signal assignment tables show a given quad receiving WE0-3 or WE4-7, but the four lines are distributed individually to each of the four chips within the quad.) The diagrams (Figures 2-3 to 2-5) label quads as Q1, Q2, Q3, and Q4 for minimum chip population, with a "" symbol added for the second population level.

Tables 2-4 and 2-5 show the PAM and PDM pins used to form the VRAM interface. The four

VRAM design diagrams (Figures 2-7a, b, c, d) that follow include tables that specify which quads receive which control signals. Not all signals are used in a given VRAM design and chip population.

All the pins in Table 2-4 drive control signals generated by the MIC.

The PD Pixel Data bus is managed by the Data Processor module (DP); all other pins in Table 2-5 are managed by the Display Processor (DSP).

WE0-3 are for pixel positions 0-3, respectively. In turbo mode, WE4-7 are for positions 4-7. For x8 mode, WE4-7 are the same as WE0-3.

2-11

|                                                                                           | WESTERN                                                          | DIGITAL                                      |         |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|---------|

|                                                                                           | DWG<br>SIZE                                                      |                                              | REV.    |

|                                                                                           | SCALE                                                            | SHT OF                                       |         |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIET, TO ANYONE OTHER THAN WDC EMPLOYEES WITHOUT | ARY TO WDC AND SHALL NOT BE REP<br>IT WRITTEN AUTHORIZATION FROM | RODUCED OR FURTHER D<br>WESTERN DIGITAL CORP | SCLOSED |

93-000032-00

Table 2-5. PDM Pin interface to VRAM

| Pin Name                     | PDM Pin #                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD31-PD0                     | 90-93, 95-98,<br>100-114, 117-125 | Parallel Data bus, connecting the DP module to the<br>VRAM block; data is bidirectional. (This is the path<br>through which the DP first reads, then rewrites pixels<br>in support of drawing operations.)                                                                                                                                                                                                                                                                                                                                                                              |

| SD31-SD0                     | 46-49, 52-67,<br>71-82            | Serial Data bus; in VRAM designs with integrated<br>back-end support, this is the path by which screen re-<br>fresh data is extracted (by a transfer cycle) from the<br>serial ports of the VRAM chips and then moved to the<br>DSP module for serializing and multiplexing before be-<br>ing sent to the DAC. In VRAM designs with external<br>back-end support, the serial data bus to the DSP is no<br>used; instead, the DSP reconfigures itself to use some<br>of these pins (replacing SD5,SD6) as output drivers<br>for additional control signals to VRAM, as shown be-<br>low. |

| SE12A, SE34A<br>SE12B, SE34B | 87, 85,<br>86, 84                 | Serial data output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SC13                         | 88                                | Serial data clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SC24                         | 89                                | Serial data clock 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| The following pins           | are changed for external          | back-end support:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SEL1 (SD5)                   | 77                                | Mux select 1 (External back-end support. See Fig 2-5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LDCLK (SD6)                  | 76                                | (With external back-end support, this pin is recon-<br>figured from SD6 to the LDCLK signal to the DAC, as<br>discussed in the next section. See Fig 2-5)                                                                                                                                                                                                                                                                                                                                                                                                                               |

In the following VRAM design diagrams, the PD lines connect to the parallel data ports of the VRAM chips, while the SD lines connect to their serial data ports.

The different resolution modes require different memory addressing schemes to configure the display memory properly for screen pixel position. Figures 2-7a, 2-7b, 2-7c and 2-7d show how the PAM generated addresses connect to the row and column addresses of the 256Kx4 VRAMS (see Figure 2-6). X2 to X9 indicates the horizontal position of each "4 pixel" group from left to right on the screen. X0 and X1 are not shown because of the "4 pixel" group organization. Y0 to Y9 indicates the vertical position of each pixel from top to bottom on the screen. Each figure also has a small map for the top left-hand corner of the screen showing the X,Y position and the rowcolumn address of the VRAM.

| 2-12                                           |          |                          |                          |           |         |  |

|------------------------------------------------|----------|--------------------------|--------------------------|-----------|---------|--|

|                                                |          |                          |                          |           |         |  |

|                                                |          |                          |                          |           |         |  |

|                                                |          | WESTERN                  | <b>V DIGIT</b>           |           |         |  |

|                                                | DWG      | DRAWING NUMBER           |                          | I         | REV.    |  |

|                                                | SIZE     |                          |                          |           |         |  |

|                                                | Α        |                          |                          |           |         |  |

|                                                | SCALE    |                          | SHT                      | OF        |         |  |

| THIS INFORMATION IS CONFIDENTIAL AND PROPRIETA | ARY TO N | NDC AND SHALL NOT BE REP | PRODUCED OF<br>WESTERN D | FURTHER D | SCLOSED |  |

| 000032-00                                      |          |                          |                          |           |         |  |

| Memory Config    | : 1024x768x4             | Four 256Kx4 Ch               | ps              |

|------------------|--------------------------|------------------------------|-----------------|

| PAM<br>Memory    |                          | VRAM                         |                 |

| Address 1        | Line Row Add             | ress Column Address          | Comments        |

| LA13             | ¥9                       | YO                           | A8 for Q1 chips |

| LA24             | D.C.                     | D.C.                         | Unused Pin      |

| MA7              | Y8                       | X9                           |                 |

| MA6              | ¥7                       | X8                           |                 |

| MA5<br>MA4       | ¥6<br>¥5                 | X7<br>X6                     |                 |

| MA3              | Y4                       | X5                           |                 |

| MA2              | ¥3                       | X4                           |                 |

| MA1<br>MA0       | Y2<br>Y1                 | X3<br>X2                     |                 |

|                  |                          |                              |                 |

| RAS Decoding     | : RAS0 and RAS1          | active regardless of address |                 |

| CAS Decoding     | : CAS12 active, CA       | S34 inactive regardless of a | ddress          |

| WE Decoding      | : Pixel Write Mask 1     | not nibble swapped           |                 |

| Display Memo     | ry Map :                 |                              |                 |

| X4               | 0000 0000 1              | 0000   0000                  |                 |

| X3               | 0000 0000                | 1111   1111                  |                 |

| X2               |                          | 0000   1111                  |                 |

| YYY X1<br>210 X0 |                          | 0011   0011  <br>0101   0101 |                 |

|                  | -++                      | +                            |                 |

| 000              | Q1 Q1 Q1 0, 0* 0, 1      | Q1   Q1  <br>0, 2   0, 3     |                 |

| 001              | Q1 Q1                    | Q1   Q1                      |                 |

|                  | -+++                     | 0,102  0,103                 |                 |

| 010              | Q1 Q1   Q1   1, 0   1, 1 | Q1   Q1  <br>1, 2   1, 3     |                 |

| 011              | Q1 Q1   Q1   1,101       | Q1 Q1  <br>1 102   1 103     |                 |

|                  | Column Address respecti  | play Memory Addressing t     | or 1024x768x4   |

|                  |                          | W                            | 2-13            |

|                  |                          |                              | BER             |

|                  |                          | DWG DRAWING NUN<br>SIZE A    | SHT OF          |

THIS INFOR TO ANYON 93-000032-00

(

C

O

| Memory Config : | 640x480x4(x 2 page) | Four 256Kx4 Chips |                 |

|-----------------|---------------------|-------------------|-----------------|

| PAM<br>Memory   | VRA                 | м                 |                 |

| Address Line    | Row Address         | Column Address    | Comments        |

| LA13            | ¥9                  | X9                | A8 for Q1 chips |

| LA24            | D.C.                | D.C.              | Unused Pin      |

| MA7             | Y8                  | X8                |                 |

| MA6             | ¥7                  | X7                |                 |

| MA5             | ¥6                  | X6                |                 |

| MA4             | ¥5                  | X5                |                 |

| MA3             | ¥4                  | X4                |                 |

| MA2             | ¥3                  | X3                |                 |

| MA1             | ¥2                  | X2                |                 |

| MAO             | YO                  | Y1                |                 |

RAS Decoding : RAS0 and RAS1 active regardless of address

CAS Decoding : CAS12 active, CAS34 inactive regardless of address

WE Decoding : Pixel Write Mask not nibble swapped

Display Memory Map :

2-14

| X4       | 0000  | 0000 | 0000 | 0000 |

|----------|-------|------|------|------|

| X3       | 0000  | 0000 | 1111 | 1111 |

| X2       | 0000  | 1111 | 0000 | 1111 |

| Y Y Y X1 | 0011  | 0011 | 0011 | 0011 |

| 2 1 0 X0 | 0101  | 0101 | 0101 | 0101 |

| 000      | Q1    | Q1   | Q1   | Q1   |

|          | 0, 0* | 0, 2 | 0,4  | 0, 6 |

| 001      | Q1    | Q1   | Q1   | Q1   |

|          | 1, 0  | 1, 2 | 1, 4 | 1, 6 |

| 010      | Q1    | Q1   | Q1   | Q1   |

|          | 0, 1  | 0, 3 | 0, 5 | 0, 7 |

| 011      | Q1    | Q1   | Q1   | Q1   |

|          | 1, 1  | 1, 3 | 1, 5 | 1, 7 |

\*Row Address, Column Address respectively in HEX

Figure 2-7b. Display Memory Addressing for 640x480x4 (2 page)

| Memory Config :              | 1024x768x8                             | Eight 256Kx4 Chips               |                  |

|------------------------------|----------------------------------------|----------------------------------|------------------|

| PAM<br>Memory<br>Address Lir |                                        | VRAM<br>Column Address           | Comments         |

| LA13                         | ¥9                                     | YO                               | A8 for Q1 chips  |

| LA24<br>MA7                  | Y9<br>Y8                               | ¥0<br>X9                         | A8 for Q2 chips  |

| MA6                          | ¥7                                     | X8                               |                  |

| MA5                          | ¥6                                     | X7                               |                  |

| MA4<br>MA3                   | Y5<br>Y4                               | X6<br>X5                         |                  |

| MA2                          | Y3                                     | X4                               |                  |

| MA1<br>MA0                   | Y2<br>Y1                               | X3<br>X2                         |                  |

| RAS Decoding :               | RAS0 and RAS1 activ                    | ve regardless of address         |                  |

| CAS Decoding :               | CAS12 active, CAS34                    | inactive regardless of address   | 5                |

| -                            |                                        | mask is generated by replication | ng lower nibble. |

| Display Memory               | -                                      |                                  |                  |

| X4<br>X3                     |                                        | 00 0000                          |                  |