# **FE6010 DMA and Arbitration Control Device**

- Completely compatible with the IBM\* Personal 1 System/2\* Models 70 and 80

- Configurable for systems based on the 80386 u – (FE6500) or the 80386SX

- 16, 20, and 25 MHz Clock Speeds to Maximize <u>ا</u> Flexibility and Performance

- Half-speed 80387/80387SX Operation Ľ

- 4-Gigabyte Enhanced Addressing 1

- Micro Channel\* Arbitration Control Logic

- Functionality equivalent to two 8237 DMA con- $\square$ trollers with Extended Mode Support

- Clock, Resets, and Parity Latch Control Extended Setup Facility<sup>TM</sup> (ESF)<sup>TM</sup>

- Low Power 1.25 Micron CMOS Technology

- 132-Lead JEDEC Plastic Quad Flat Pack

The FE6010 integrated circuit forms part of the Western Digital® innovative FE6500 chip set, facilitating the design and implementation of boards equivalent to the Model 70 and 80 system boards. It decreases design complexity and saves space by combining the functions of many discrete arrays and components, while reducing system cost and increasing system reliability.

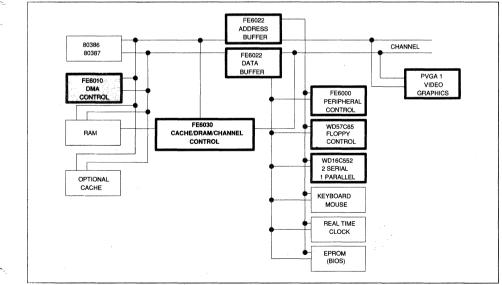

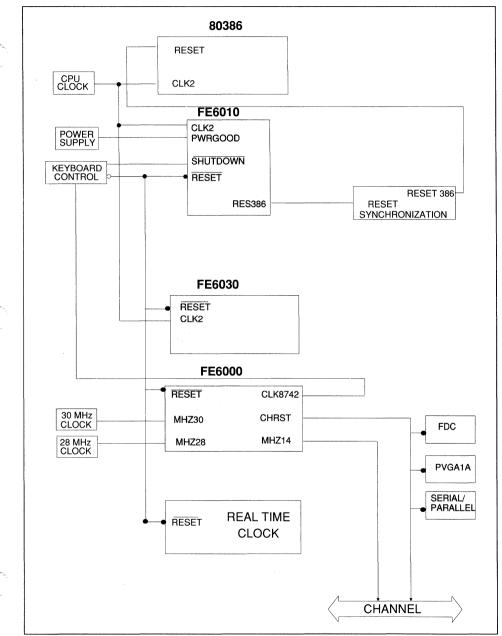

The Extended Setup Facility is a Western Digital enhancement, designed to allow more functionality such as a Winchester Controller, LAN Adapter or additional serial port to be added on to the system board. It provides product differentiation at the system level and helps hold down costs. The general block diagram in Figure 1 illustrates a typical system using the FE6500 chip set. Devices with bold outlines are available from Western Digital Corporation.

Figure 1. System Block Diagram

(\*) IBM is a registered trademark and Personal System/2, PS/2, Micro Channel, and Micro Channel Architecture are trademarks of International Business Machines Corporation Western Digital is a registered trademark and Extended Setup Facility and ESF are trademarks of Western Digital Corporation.

# WESTERN DIGITAL

Additional References IBM AT Technical Reference Manual Intel\* Microprocessor and Peripheral Handbook

#### Disclaimer

Western Digital Corporation makes no representation or warranty of any kind with regard to the hardware and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Western Digital Corporation reserves the right to revise this hardware and associated documentation and to make changes from time to time in the content without obligation of Western Digital Corporation to notify any person of such revisions or changes.

#### Copyright

Copyright © 1988, 1989 Western Digital Corporation. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of Western Digital Corporation, 2445 McCabe Way, Irvine, CA 92714.

Western Digital Corporation reserves the right to make changes or improvements to the equipment, software, hardware, and documentation described herein at any time and without notice.

\* Intel is a registered trademark of Intel Corporation.

ſ

# **Table of Contents**

| 1.0 PIN DESCRIPTION                                                                | <br> | 3  |

|------------------------------------------------------------------------------------|------|----|

| 2.0 DMA CONTROLLER                                                                 | <br> | 14 |

| 2.1 DMA INTERFACE                                                                  | <br> | 14 |

| 2.2 INTERNAL ARCHITECTURE                                                          | <br> | 14 |

| 2.2.1 Address Translator                                                           | <br> | 14 |

| 2.2.2 RAM Registers                                                                |      |    |

| 2.2.3 DMA Registers                                                                |      |    |

| 2.2.4 Transfer Control                                                             |      |    |

| 2.2.5 Register Control                                                             | <br> | 17 |

| 2.2.6 Work Registers                                                               | <br> | 17 |

| 2.3 SYSTEM CPU ACCESS MODES                                                        | <br> | 17 |

| 2.3.1 Compatibility Mode                                                           | <br> | 17 |

| 2.3.2 Extended Mode                                                                | <br> | 19 |

| 2.3.3 Enhanced Mode                                                                | <br> | 20 |

| 2.4 DMA OPERATION                                                                  |      |    |

| 2.4.1 Single Transfer Mode                                                         | <br> | 20 |

| 2.4.2 Demand Transfer Mode                                                         |      |    |

| 2.4.3 Verify Mode                                                                  |      |    |

| 2.4.4 Submodes                                                                     | <br> | 23 |

| 2.4.5 Boundary And End Conditions                                                  | <br> | 24 |

| 2.4.6 Direct Commands                                                              | <br> | 26 |

| 2.4.7 Enhanced Mode                                                                | <br> | 26 |

| 3.0 RESET CONTROL                                                                  | <br> | 26 |

| 4.0 ARBITRATION CONTROL (AC)                                                       |      |    |

| 4.1 ARBITRATION REGISTER                                                           |      |    |

| 4.2 ARBITRATION CONTROL FUNCTIONS                                                  |      |    |

| 4.2.1 Execute Arbitration Cycles                                                   |      |    |

| 4.2.2 Arbitrate the Local CPU Bus                                                  |      |    |

| 4.2.3 Regulate Arbitration Cycle Duration                                          |      |    |

| 4.2.4 Arbitration Monitor                                                          |      |    |

| 4.2.5 Floppy Disk Controller DMA Interface                                         | <br> | 20 |

| 4.3 PREEMPT GENERATOR                                                              | <br> | 20 |

| 4.3.1 Floppy Controller DMA Request                                                | <br> | 20 |

| 4.3.2 Refresh Request                                                              |      |    |

| 4.3.3 Arbitration Register Bit 6 Set                                               |      |    |

| 4.3.4 Interrupt Request                                                            |      |    |

| 5.0 SYSTEM FUNCTIONS                                                               |      |    |

| 6.0 HALF-SPEED INTERFACE                                                           |      |    |

|                                                                                    | <br> |    |

| 7.0 DIAGNOSTICS                                                                    |      |    |

| 7.1 DIAGNOSTIC REGISTER 1                                                          | <br> |    |

| 7.2 DIAGNOSTIC REGISTER 2                                                          |      |    |

| 7.3 DIAGNOSTIC REGISTER 3                                                          |      |    |

| 7.4 DIAGNOSTIC REGISTER 4                                                          |      |    |

| 7.5 DIAGNOSTIC REGISTER 5                                                          |      |    |

| 7.6 DIAGNOSTIC REGISTER 6                                                          |      |    |

| 8.0 EXTENDED SETUP FACILITY (ESF)                                                  | <br> | 33 |

| 8.1 ESF ACCESS                                                                     | <br> | 33 |

| 8.2 ESF ADDRESS MAPS                                                               | <br> | 34 |

| 9.0 THE FE6010 IN 80386 AND 80386SX ENVIRONMENTS                                   | <br> | 35 |

| 10.0 TECHNICAL SPECIFICATIONS                                                      |      |    |

| 10.1 ABSOLUTE MAXIMUM RATINGS                                                      |      |    |

| 10.1 ABSOLUTE MAXIMUM RATINGS                                                      |      |    |

| 10.3 DC CHARACTERISTICS (UNDER NORMAL OPERATING CONDITIONS)                        |      |    |

| 10.3 DC CHARACTERISTICS (UNDER NORMAL OPERATING CONDITIONS)<br>10.4 A.C TEST LOADS |      |    |

|                                                                                    |      |    |

| 11.0 TIMING                                                                        | <br> | 37 |

# List of Illustrations

| Figure 1. System Block Diagram                                                           |    |

|------------------------------------------------------------------------------------------|----|

| Figure 2. FE6010 Block Diagram                                                           | 1  |

| Figure 3. Pin Diagram                                                                    | 2  |

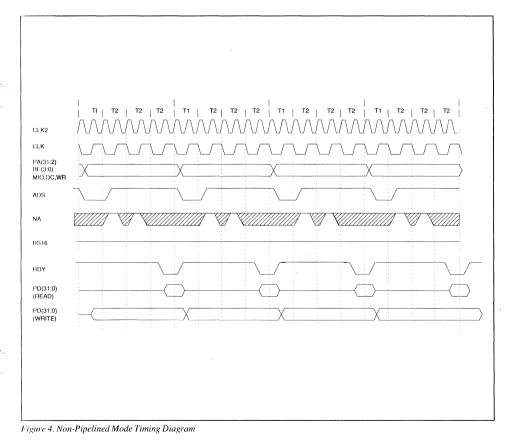

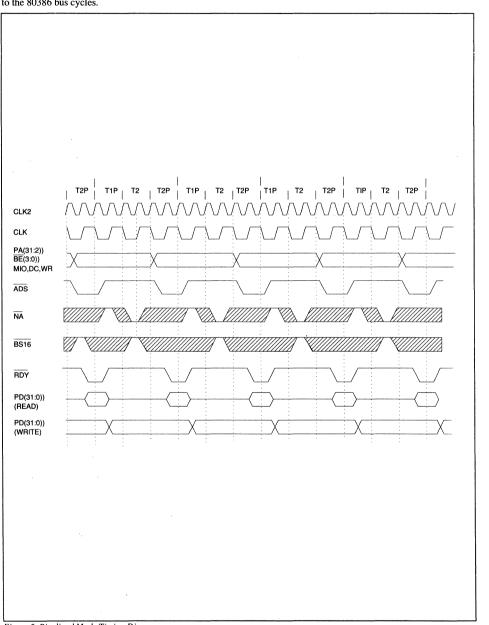

| Figure 4. Non-Pipelined Mode Timing Diagram                                              | 11 |

| Figure 5. Pipelined Mode Timing Diagram                                                  | 12 |

| Figure 6. Read Cycle With Auto-Initialize                                                | 15 |

| Figure 7. Mask Register Format                                                           | 16 |

| Figure 8. Mode Register Format                                                           | 16 |

| Figure 9. Arbus Register Format                                                          | 17 |

| Figure 10. Status Register Format                                                        | 17 |

| Figure 11. Extended Function Register (EFR)(0018H)                                       | 19 |

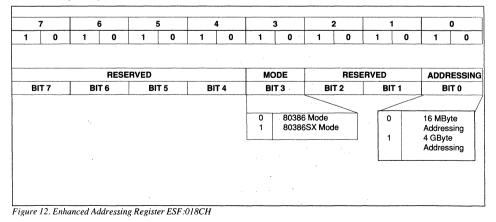

| Figure 12. Enhanced Addressing Register ESF:018CH                                        | 20 |

| Figure 13. 16-Bit Read Transfer With Transfer Count Expiration                           | 21 |

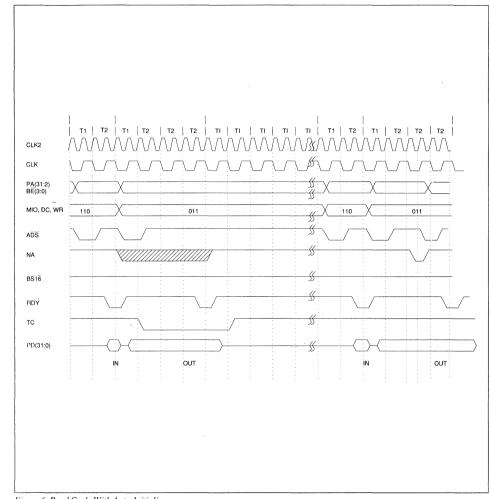

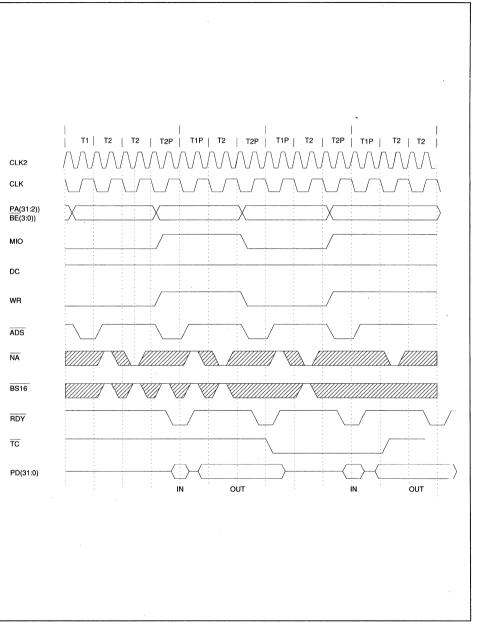

| Figure 14. 16-Bit Write Transfer With Transfer Count Expiration                          | 22 |

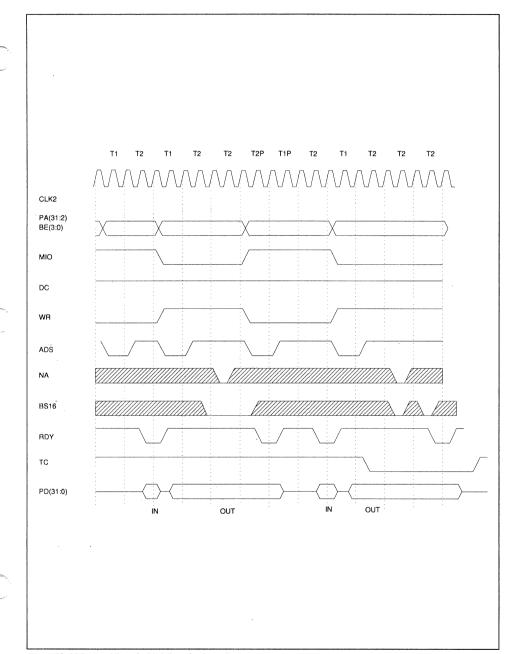

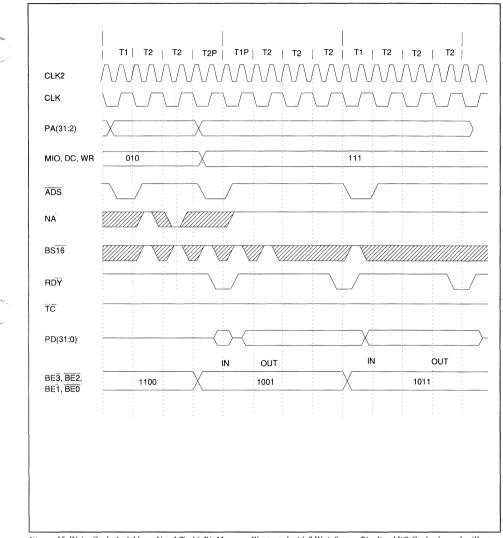

| Figure 15. Write Cycle At Address N + 1 To 16-Bit Memory, Illustrated With 2 Wait States | 23 |

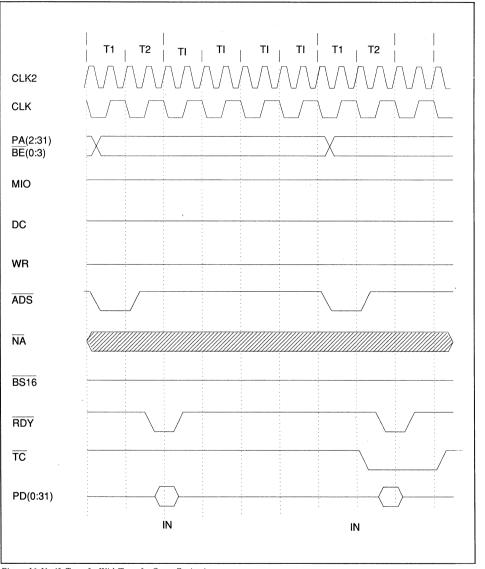

| Figure 16. Verify Transfer With Transfer Count Expiration                                | 24 |

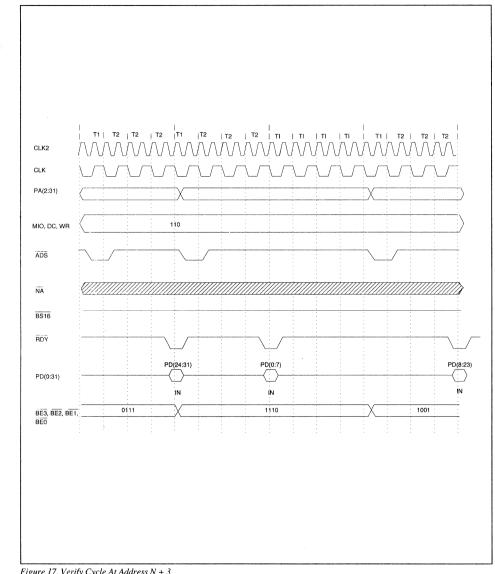

| Figure 17. Verify Cycle At Address N + 3                                                 | 25 |

| Figure 18. Arbitration Register Format (0090H)                                           | 26 |

| Figure 19. System Clock and Reset Control                                                | 27 |

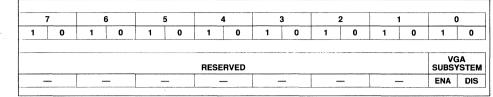

| Figure 20. PVGA Register Format                                                          | 29 |

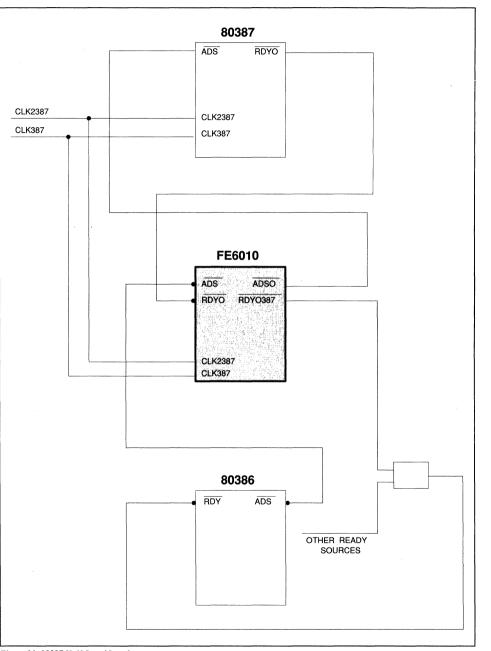

| Figure 21. 80387 Half-Speed Interface                                                    | 30 |

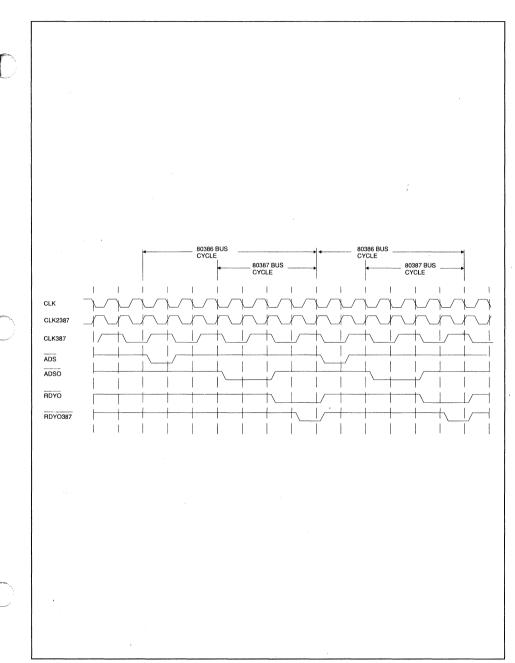

| Figure 22. 80387 Half-Speed Interface Timing Diagram                                     | 31 |

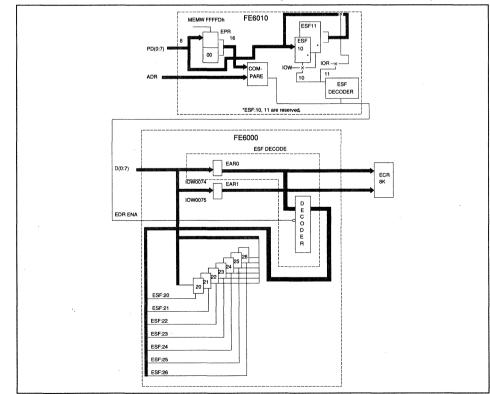

| Figure 23. ECR and ESF Block Diagram                                                     | 33 |

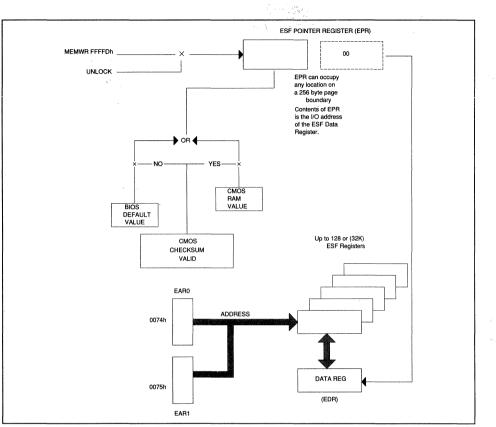

| Figure 24. Extended Setup Facility Overview                                              | 34 |

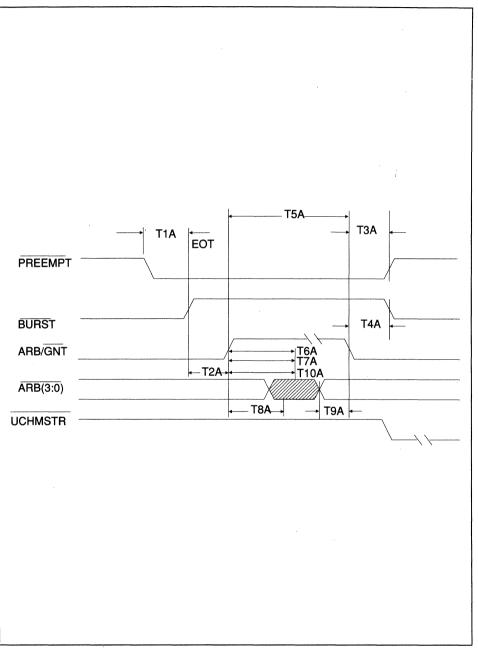

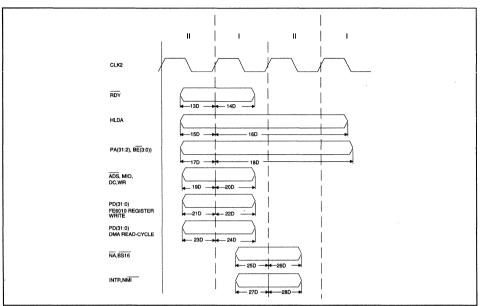

| Figure 25. Arbitration Timing                                                            | 38 |

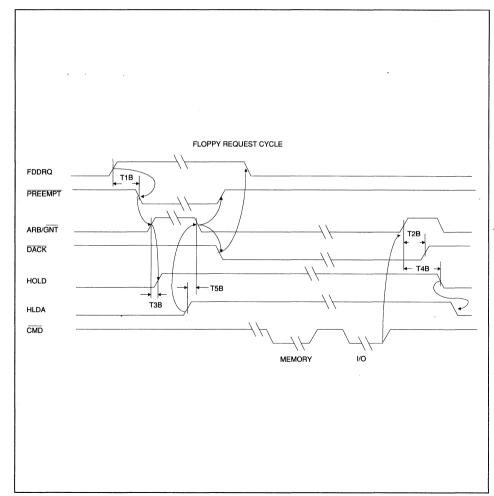

| Figure 26. Floppy Request Cycle                                                          | 39 |

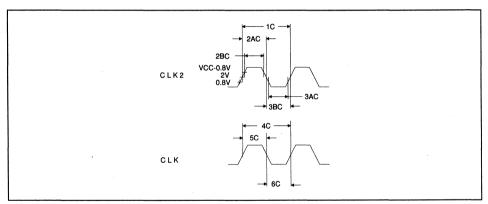

| Figure 27. Input Clock Specifications                                                    | 40 |

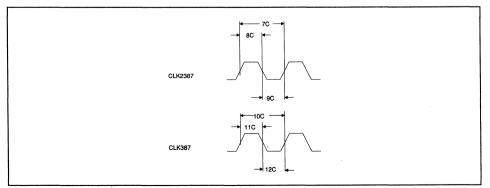

| Figure 28. Input Clock Specifications II                                                 | 40 |

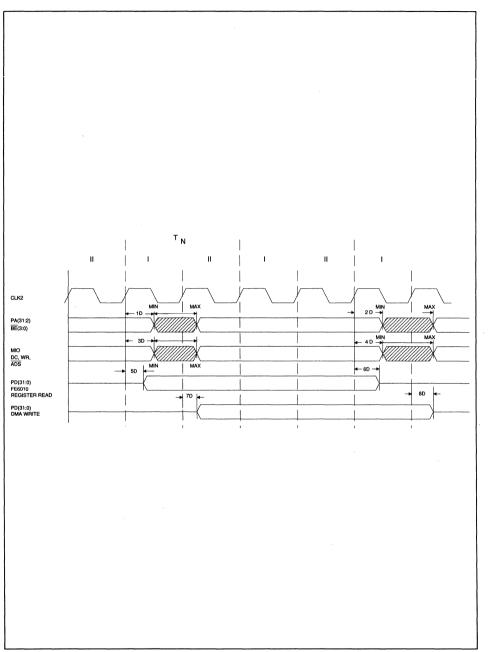

| Figure 29. FE6010 Output Valid Delay Timing                                              | 42 |

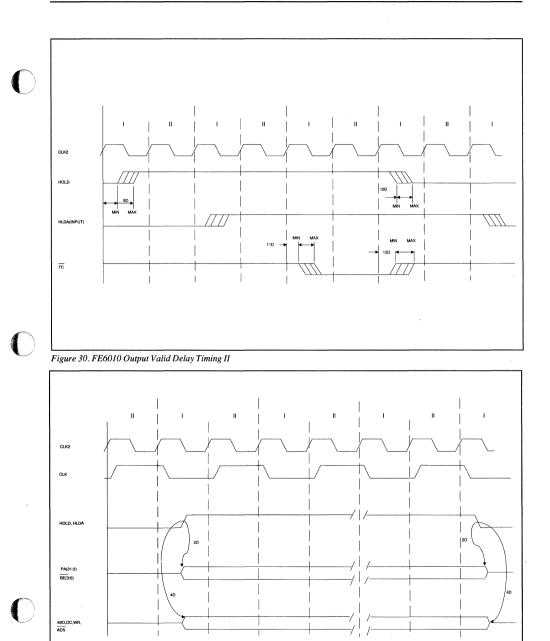

| Figure 30. FE6010 Output Valide Delay Timing II                                          | 43 |

| Figure 31. Bus Tristate Timings                                                          | 43 |

| Figure 32. Input Setup and Hold Timings                                                  | 44 |

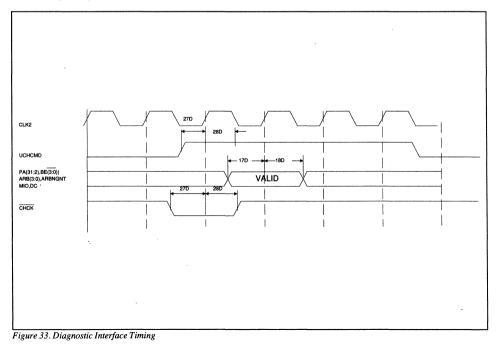

| Figure 33. Diagnostic Interface Timing                                                   | 44 |

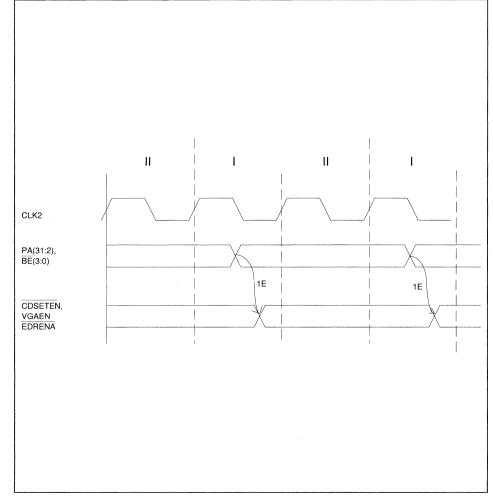

| Figure 34. Device Enable Timings                                                         | 45 |

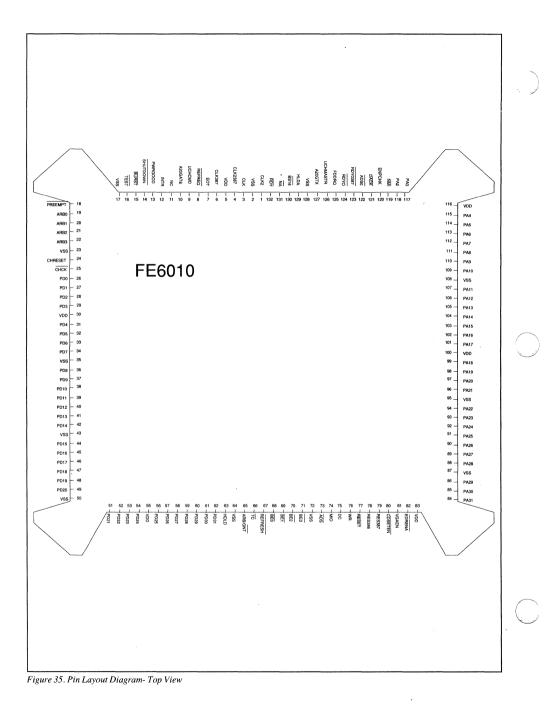

| Figure 35. Pin Layout Diagram - Top View                                                 | 46 |

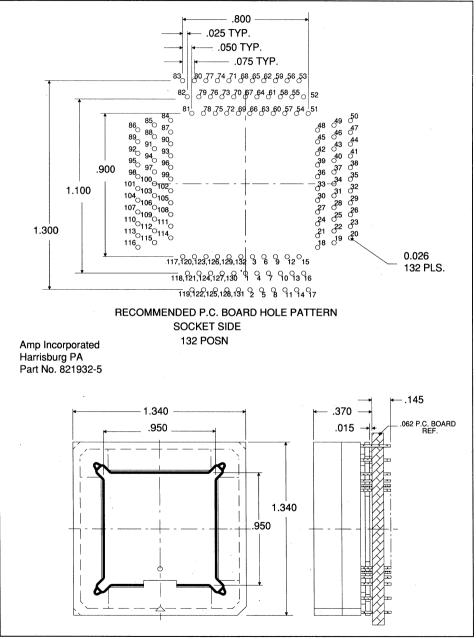

| Figure 36. 132-Pin JEDEC Flat Pack Packaging Diagram                                     | 47 |

| Figure 37. Socket Diagram                                                                | 48 |

|                                                                                          |    |

# List of Tables

| Table 1. Pin Signals                             |    | • • | <br> |     | <br> |      |  |  | <br> |  |  | <br>. 1 | 1  |

|--------------------------------------------------|----|-----|------|-----|------|------|--|--|------|--|--|---------|----|

| Table 2. System Level I/O Map                    |    |     |      |     |      |      |  |  |      |  |  |         |    |

| Table 3. DMA Register Allocation                 |    |     | <br> |     | <br> |      |  |  | <br> |  |  | <br>. 1 | 6  |

| Table 4. Compatibility Mode I/O Map              |    |     | <br> |     | <br> |      |  |  | <br> |  |  | <br>1   | 8  |

| Table 5. Extended Mode I/O Addresses             |    |     | <br> |     | <br> | <br> |  |  | <br> |  |  | <br>. 1 | 9  |

| Table 6. Clock Rate Definitions                  |    |     |      |     |      |      |  |  |      |  |  |         |    |

| Table 7. Extending the Default Arbitration Cycle |    |     |      |     |      |      |  |  |      |  |  |         |    |

| Table 8. ESF Registers for an FE6500 System .    |    |     |      |     |      |      |  |  |      |  |  |         |    |

| Table 9. Arbitration Cycles (In ns)              |    |     |      |     |      |      |  |  |      |  |  |         |    |

| Table 10. Floppy Request Cycles                  | •• |     | <br> | • • | <br> |      |  |  |      |  |  | <br>. 3 | 39 |

FE6010

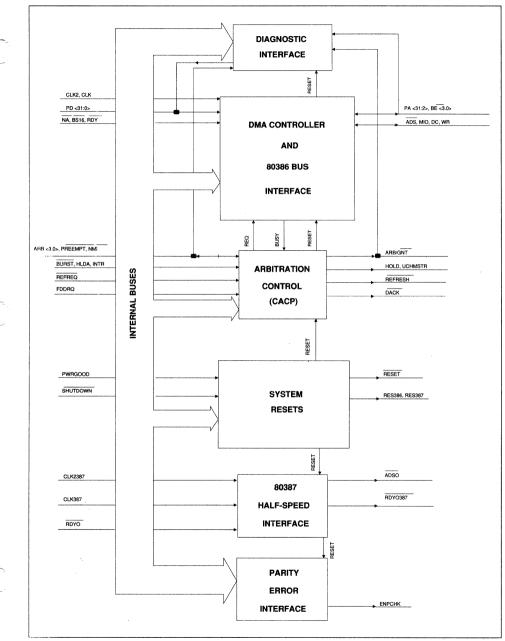

Figure 2. FE6010 Block Diagram

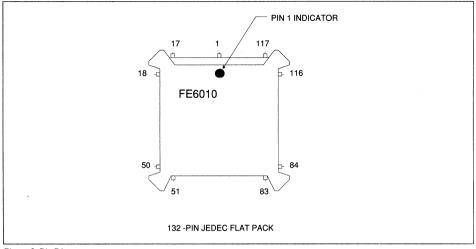

# Figure 3. Pin Diagram

| PIN | - | NAME            | PIN - | - | NAME    | PIN | _ | NAME            | PIN | _ | NAME            |

|-----|---|-----------------|-------|---|---------|-----|---|-----------------|-----|---|-----------------|

| 1   |   | CLK2            | 34 -  | - | PD7     | 67  | - | REFRESH         | 100 | - | VDD             |

| 2   |   | Vss             | 35 -  | - | Vss     | 68  | - | BE0             | 101 | - | PA17            |

| 3   | - | CLK             | 36 -  | - | PD8     | 69  |   | BE1             | 102 |   | PA16            |

| 4   | - | CLK2387         | 37 -  | - | PD9     | 70  | - | BE2             | 103 | - | PA15            |

| 5   |   | V <sub>DD</sub> | 38 -  | - | PD10    | 71  |   | BE3             | 104 | - | PA14            |

| 6   | - | CLK387          | 39 ·  | - | PD11    | 72  | - | Vss             | 105 | - | PA13            |

| 7   |   | EOT             | 40 ·  | - | PD12    | 73  |   | ADS             | 106 | - | PA12            |

| 8   | - | REFREQ          | 41 ·  | - | PD13    | 74  | - | MIO             | 107 | - | PA11            |

| 9   |   | UCHCMD          | 42 ·  | - | PD14    | 75  | - | DC              | 108 | - | Vss             |

| 10  | - | A20GATE         | 43 -  | - | Vss     | 76  |   | WR              | 109 | - | PA10            |

| 11  | - | No Connect      | 44 ·  | - | PD15    | 77  | - | RESET           | 110 | - | PA9             |

| 12  | - | INTR            | 45 ·  | - | PD16    | 78  | - | RES386          | 111 | - | PA8             |

| 13  | - | PWRGOOD         | 46 ·  | - | PD17    | 79  | - | RES387          | 112 | - | PA7             |

| 14  | - | SHUTDOWN        |       | - | PD18    | 80  | - | CDSETEN         | 113 | - | PA6             |

| 15  | - | BURST           | 48 ·  | - | PD19    | 81  | - | VGAEN           | 114 | - | PA5             |

| 16  |   | TEST            | 49 ·  | - | PD20    | 82  | - | EDRENA          | 115 | - | PA4             |

| 17  | - | Vss             |       | - | Vss     | 83  | - | V <sub>DD</sub> | 116 | - | V <sub>DD</sub> |

| 18  | - | PREEMPT         |       | - | PD21    | 84  |   | PA31            | 117 | - | PA3             |

| 19  |   | ARB0            |       | - | PD22    | 85  | - | PA30            | 118 | - | PA2             |

| 20  | - | ARB1            | 53 ·  | - | PD23    | 86  | - | PA29            | 119 |   | NMI             |

| 21  |   | ARB2            | •     | - | PD24    | 87  | - | Vss             | 120 | - | ENPCHK          |

| 22  |   | ARB3            | 55 ·  | - | VDD     | 88  | - | PA28            | 121 | - | DACK            |

| 23  |   | Vss             | ••    | - | PD25    | 89  |   | PA27            | 122 | - | ADSO            |

| 24  | - | CHRESET         | 0,    | - | PD26    | 90  |   | PA26            | 123 | - | RDYO387         |

| 25  | - | CHCK            | ••    | - | PD27    | 91  | - | PA25            | 124 | - | RDYO            |

| 26  | - | PD0             | 59    | - | PD28    | 92  | - | PA24            | 125 | - | FDDRQ           |

| 27  | - | PD1             |       | - | PD29    | 93  | - | PA23            | 126 |   | UCHMSTR         |

| 28  | - | PD2             |       | - | PD30    | 94  |   | PA22            | 127 |   | A20GTX          |

| 29  | - | PD3             | 62    | - | PD31    | 95  | - | Vss             | 128 | - | Vss             |

| 30  | - | VDD             | 63    | - | HOLD    | 96  | - | PA21            | 129 |   | HLDA            |

| 31  |   | PD4             | • •   | - | Vss     | 97  | - | PA20            | 130 | - | BS16            |

| 32  | - | PD5             |       | - | ARB/GNT | 98  | - | PA19            | 131 | - | NA              |

| 33  | - | PD6             | 66    | - | TC      | 99  | - | PA18            | 132 | - | RDY             |

# **1.0 PIN DESCRIPTION**

The signals assigned to the different pins are grouped according to their function, and discussed individually in Table 1.

#### RESET CONTROLS

The Reset Control block in the FE6010 generates three levels of resets, compatible with the Model 70/80.

- A system reset, RESET, which resets all the devices in the system.

- An 80386 reset, RES386, which only resets the 80386/80386SX microprocessor. The synchronization of this signal to the 80386 clock, CLK2, must be done externally.

- An 80387 reset, RES387, which only resets the 80387 numeric coprocessor. Synchronizing this signal to the 80387 clock, CLK2387, must be executed externally.

### NOTE

The FE6010 is compatible with both the 80386 and the 80386SX microprocessors. In the following description, any references to the system microprocessor refer to both the 80386 and the 80386SX, unless specifically stated otherwise. Similarly, any references to the NPX (Numeric coprocessor extension) refer to the both the 80387 and the 80387SX, unless explicitly stated otherwise. Section 9.0 describes the differences in implementation on an 80386 system versus an 80386SX system.

#### ARBITRATION CONTROL

The Arbitration Control block in the FE6010 arbitrates between different masters requesting use of the bus at the same time. The Central Arbitration Control Point (CACP) controls the arbitration timing in accordance with Channel specifications.

#### DMA CONTROLLER SIGNALS

The DMA Controller on the FE6010 is fully compatible with the Model 70/80 in the basic mode. In addition, the Faraday FE6010 provides an enhanced addressing mode, the 4Gig Mode, to enhance the DMA addressing capability.

#### NOTE

The registers implemented on the FE6010 can only be accessed by the system microprocessor.

#### NUMERIC COPROCESSOR EXTENSION (NPX) HALF-SPEED INTERFACE

The NPX half-speed interface allows the NPX to be operated at half the speed of the CPU. A half-speed NPX interface is useful in systems where the costperformance requirements dictate an inexpensive coprocessor. In an 80386 system, the coprocessor used is an 80387; on an 80386SX system it is an 80387SX.

#### DECODES

This interface is used to diagnose errors in the system. This block implements the decodes for system-wide functions.

#### DIAGNOSTICS

The diagnostic signals recover the state of the bus after an error condition. For more details, see Section 7.6.

#### PARITY LATCH CONTROL

This signal interfaces with external parity latches and provides the capability to latch parity errors.

#### MISCELLANEOUS

The  $V_{DD}$  signals indicate the +5V power supply, and the V<sub>SS</sub> signals indicate the 0V ground.

| PIN NO. | NAME     | TYPE | FUNCTION                                                                                                                                                                                                                   |                                                                                     |                                                                     |                                                                     |                                                    |

|---------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|

|         |          |      | CLOCK RESET CO                                                                                                                                                                                                             | NTROL                                                                               |                                                                     |                                                                     |                                                    |

| 14      | SHUTDOWN | 1    | SHUT DOWN - This signal in keyboard controller, as comma                                                                                                                                                                   | -                                                                                   |                                                                     | d is generated                                                      | d by the 8X42                                      |

| 13      | PWRGOOD  | 1    | POWER SUPPLY VOLTAGE S<br>indicates the state of the power<br>the state of this line.                                                                                                                                      | STATUS - This                                                                       | signal original                                                     |                                                                     |                                                    |

| 77      | RESET    | 0    | SYSTEM RESET – This syste<br>with CLK2, resets all the compo-<br>refreshes take place.                                                                                                                                     | 0,0                                                                                 |                                                                     |                                                                     | ,                                                  |

| 78      | RES386   | 0    | 80386 RESET - This signal is<br>board Shutdown, or Processor<br>processor. It must be externall<br>sent to the processor.                                                                                                  | Shutdown cycles                                                                     | s, and is an ur                                                     | nsynchronized                                                       | reset for the                                      |

|         |          |      | On an Alternate Hot Reset or F<br>valid for at least sixteen CLK2<br>the 8X42 when a keyboard shu<br>system reset.                                                                                                         | periods. The pul                                                                    | se width of the                                                     | e signal is det                                                     | ermined by                                         |

| 79      | RES387   | 0    | 80387 RESET – This reset sig<br>and is an unsynchronized reset<br>being sent to the NPX.<br>On a system reset, the pulse w<br>On an NPX soft reset (an I/O w<br>256 CLK2s. When the NPX is<br>width is 128 CLK2387 periods | t for the NPX. It<br>ridth of the signal<br>rrite to Port 00F1<br>operating at half | must be exter<br>is determined<br>), this signal h<br>the frequency | nally synchron<br>d by the powe<br>las a pulse wi<br>v of the 80386 | nized before<br>r supply logic.<br>dth of at least |

|         |          |      | The table that follows shows th<br>in response to the sources in a                                                                                                                                                         |                                                                                     |                                                                     | •                                                                   |                                                    |

|         |          |      | RESET SOURCE                                                                                                                                                                                                               | RESET                                                                               | RES386                                                              | RES387                                                              | CHRESET                                            |

|         |          |      | Power-On                                                                                                                                                                                                                   | x                                                                                   | x                                                                   | x                                                                   | x                                                  |

|         |          |      | Alternate Hot Reset                                                                                                                                                                                                        |                                                                                     | x                                                                   | _                                                                   |                                                    |

|         |          |      | (Port 92, Bit 0)                                                                                                                                                                                                           |                                                                                     |                                                                     |                                                                     |                                                    |

|         |          |      | Soft Channel Reset                                                                                                                                                                                                         | _                                                                                   |                                                                     |                                                                     | x                                                  |

|         |          |      | Keyboard Shutdown                                                                                                                                                                                                          |                                                                                     | x                                                                   |                                                                     |                                                    |

|         |          |      | Processor Shutdown                                                                                                                                                                                                         |                                                                                     | x                                                                   |                                                                     |                                                    |

|         |          |      | NPX Soft Reset (Port F1)                                                                                                                                                                                                   |                                                                                     |                                                                     | х                                                                   |                                                    |

|         |          |      | ARBITRATION CO                                                                                                                                                                                                             | NTROL                                                                               |                                                                     |                                                                     |                                                    |

| 22      | ARB3     | I/O  | ARBITRATION BUS - These                                                                                                                                                                                                    | four open collec                                                                    | ctor lines conta                                                    | ain the state c                                                     | of all the Chan-                                   |

| 21      | ARB2     |      | nel local arbiters after an arbitr                                                                                                                                                                                         |                                                                                     |                                                                     |                                                                     |                                                    |

| 20      | ARB1     |      | state, the master or the slave a                                                                                                                                                                                           | dapter owning th                                                                    | nat arbitration                                                     | level is given                                                      | ownership of                                       |

| 19      | ARB0     |      | the Channel bus. When the flo                                                                                                                                                                                              | ppy controller re                                                                   | quests the bu                                                       | s through FDI                                                       | DRQ, these                                         |

|         | •        |      | lines are driven by the FE6010                                                                                                                                                                                             |                                                                                     |                                                                     |                                                                     |                                                    |

| 12      | INTR     | 1    | INTERRUPT – If Bit 4 of the<br>than the system CPU is using the<br>cycle. This allows the system C                                                                                                                         | the bus, this inter                                                                 | rupt signal is                                                      | used to initiat                                                     | e an arbitratior                                   |

0 = Output, I = Input, I/O = Bi-directional

Γ

| PIN NO. | NAME    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | PREEMPT | I/O  | PREEMPT – This open collector line signals that a Channel adapter wants to use the<br>bus, and the CACP initiates an arbitration cycle when the line is asserted. A floppy con-<br>troller request, a refresh cycle request, or receipt of an NMI causes the line to be driven<br>by the CACP.                                                                                                                                                                                                                      |

| 15      | BURST   | 1    | BURST – This signals that the current Channel bus owner will continue to hold the bus<br>for more than one transfer. For DMA transfers, BURST is removed during the last I/O<br>bus cycle of the transfer or during TC if the terminal count is reached. To prevent more<br>transfers from taking place, BURST must be de-asserted in accordance with Channel<br>timings.                                                                                                                                           |

| 7       | EOT     | I    | END-OF-TRANSFER SIGNAL – This signal from the FE6022 (Address Buffer Mode) in dicates an End-of-Transfer condition. It is activated when both CMD and S(1:0) are inactive on the Channel. Internally, it is ORed with BURST to show an End of Cycle condition. This information is used by the CACP.                                                                                                                                                                                                                |

| 8       | REFREQ  | 1    | REFRESH REQUEST – This signal is generated by the FE6000 to request a refresh cycle. The FE6010 responds by driving the PREEMPT signal. The CACP enters the ARB state and requests the local CPU bus. The refresh cycle is executed and the bus returned to the GNT state. If the CACP is already in the ARB state, the refresh request extends the period by one bus cycle.                                                                                                                                        |

|         |         |      | Depending on the FREF bit in the Memory Control Register, the FE6000 generates Fast Refreshes (every 0.8 $\mu$ s, FREF = 0) or normal refreshes (every 15.1 $\mu$ s, FREF = 0).                                                                                                                                                                                                                                                                                                                                     |

| 125     | FDDRQ   | I    | FLOPPY DISK REQUEST – This signal indicates that the floppy disk controller requires<br>the DMA transfer services. The CACP translates this request into Arbitration Level 2 and<br>competes on the Channel.                                                                                                                                                                                                                                                                                                        |

| 121     | DACK    | I/O  | $\overline{\text{DMA REQUEST ACKNOWLEDGE}} - \text{This pin has two functions. Normally it is an output signal to the floppy controller, which, when active, initiates a single I/O read or write transfer. Multiple transfers are only initiated if \overline{\text{BURST}} is also active.$                                                                                                                                                                                                                       |

|         |         |      | At power-on, it is an input signal. The state of this pin is sampled on the trailing edge of $\overrightarrow{RESET}$ and is used to determine whether the FE6010 will operate in an 80386-compatible or 80386SX-compatible mode.                                                                                                                                                                                                                                                                                   |

| 65      | ARB/GNT | 0    | ARBITRATION/GRANT – This signal indicates the state of the system arbiter. In the<br>ARB state (high), all local arbiters and adapters must remove their drivers from the bus.<br>Local arbiters may compete for Channel ownership by comparing their arbitration levels<br>on a bit-for-bit basis. At the end of the ARB time (a minimum of 300 ns), the Channel is<br>given to the owner of the winning arbitration level, and the change is signified by the<br>change in the polarity of the line to GNT (low). |

| 129     | HLDA    | I    | HOLD ACKNOWLEDGE - The CPU assesses HLDA in response to a HOLD signal an<br>indicates that it has relinquished the local bus.                                                                                                                                                                                                                                                                                                                                                                                       |

| 63      | HOLD    | 0    | HOLD – This signal is synchronous with CLK2. When asserted, it requests the 80386 to relinquish the local bus for a Refresh, DMA, or Channel master transfer.                                                                                                                                                                                                                                                                                                                                                       |

| 119     | NMI     | I/O  | NON-MASKABLE INTERRUPT – When driven by the FE6010 to the system CPU, NM<br>indicates that the CACP has reached a bus time-out condition while monitoring the Char<br>nel bus. When the signal is received from the FE6000, it tells the CACP to initiate an ar-<br>bitration cycle to remove any bus masters so that the system CPU can service the NMI.                                                                                                                                                           |

O - Output, I = Input, I/O = Bi-directional

| PIN NO.                                | NAME                                                 | TYPE |                                                                                                                                                                               | FUNCTION                                                                                                                                                                                                     |                                                                                                                                                                                            |                                                                                  |

|----------------------------------------|------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 67                                     | REFRESH                                              | 0    | is a refresh cycle.                                                                                                                                                           | is Channel signal indicates<br>The PA address lines (10:<br>n the DMA controller. The i                                                                                                                      | 2) and $\overline{BE}$ (3:0) hold the st                                                                                                                                                   | tate of the refresh                                                              |

|                                        |                                                      |      | only refresh for th                                                                                                                                                           | E6030 performs a memory<br>e motherboard DRAM. On<br>de-asserting CHRDY.                                                                                                                                     |                                                                                                                                                                                            |                                                                                  |

| 126                                    | UCHMSTR                                              | 1/0  |                                                                                                                                                                               | ER – The Channel Master<br>han the 80386 or the mothe                                                                                                                                                        | -                                                                                                                                                                                          |                                                                                  |

|                                        |                                                      |      |                                                                                                                                                                               | pin functions differently. Thand is used in conjunction w<br>m will operate.                                                                                                                                 | - ,                                                                                                                                                                                        | -                                                                                |

|                                        |                                                      |      | FREQUENCY                                                                                                                                                                     | UCHMSTR (F1)                                                                                                                                                                                                 | A20GTX (F0)                                                                                                                                                                                |                                                                                  |

|                                        |                                                      |      | 16 MHz                                                                                                                                                                        | 0                                                                                                                                                                                                            | 0                                                                                                                                                                                          |                                                                                  |

|                                        |                                                      |      | 20 MHz                                                                                                                                                                        | 0                                                                                                                                                                                                            | 1                                                                                                                                                                                          |                                                                                  |

|                                        |                                                      |      | 25 MHz                                                                                                                                                                        | 1                                                                                                                                                                                                            | 1                                                                                                                                                                                          |                                                                                  |

|                                        |                                                      |      | Reserved                                                                                                                                                                      | 1                                                                                                                                                                                                            | 0                                                                                                                                                                                          |                                                                                  |

|                                        |                                                      | -ll  |                                                                                                                                                                               | MA CONTROL                                                                                                                                                                                                   |                                                                                                                                                                                            | ·····                                                                            |

| 3                                      | CLK                                                  | 1    |                                                                                                                                                                               | 6 - Both signals are CMO                                                                                                                                                                                     | S-level clock signals. CLK                                                                                                                                                                 | 2 has a frequenc                                                                 |

| 1                                      | CLK2                                                 |      |                                                                                                                                                                               | rocessor clock frequency, a                                                                                                                                                                                  | •                                                                                                                                                                                          |                                                                                  |

|                                        | 0 Li iL                                              |      |                                                                                                                                                                               | e same frequency as the p                                                                                                                                                                                    |                                                                                                                                                                                            | -                                                                                |

|                                        |                                                      |      |                                                                                                                                                                               | with CLK2 as the internal                                                                                                                                                                                    |                                                                                                                                                                                            | in has the same                                                                  |

| 71                                     | BE3                                                  | 1/0  |                                                                                                                                                                               | These byte enable signals                                                                                                                                                                                    |                                                                                                                                                                                            | the data is trans                                                                |

| 70                                     | BE2                                                  | 1/0  |                                                                                                                                                                               | MA operation they are outp                                                                                                                                                                                   |                                                                                                                                                                                            |                                                                                  |

| 69                                     | BE1                                                  |      | •                                                                                                                                                                             | egisters, they are input sign                                                                                                                                                                                | • •                                                                                                                                                                                        |                                                                                  |

| 68                                     | BEO                                                  |      |                                                                                                                                                                               | of microprocessor (80386 c                                                                                                                                                                                   |                                                                                                                                                                                            | -                                                                                |

|                                        |                                                      |      | ponor up.                                                                                                                                                                     |                                                                                                                                                                                                              |                                                                                                                                                                                            |                                                                                  |

|                                        |                                                      |      | SIGNAL                                                                                                                                                                        | 80386 SYSTEM                                                                                                                                                                                                 | 80386SX SYSTEM                                                                                                                                                                             |                                                                                  |

|                                        |                                                      |      | SIGNAL                                                                                                                                                                        |                                                                                                                                                                                                              |                                                                                                                                                                                            |                                                                                  |

|                                        |                                                      |      | SIGNAL<br>BE3                                                                                                                                                                 | BE3                                                                                                                                                                                                          | Not connected                                                                                                                                                                              | -                                                                                |

|                                        |                                                      |      | SIGNAL<br>BE3<br>BE2                                                                                                                                                          | BE3<br>BE2                                                                                                                                                                                                   | Not connected<br>PA1_                                                                                                                                                                      |                                                                                  |

|                                        |                                                      |      | SIGNAL<br>BE3                                                                                                                                                                 | BE3                                                                                                                                                                                                          | Not connected                                                                                                                                                                              | -                                                                                |

| 84                                     | PA31                                                 | 1/0  | BE3<br>BE2<br>BE1<br>BE0                                                                                                                                                      | BE3<br>BE2<br>BE1<br>BE0                                                                                                                                                                                     | Not connected<br>PA1<br>BEH<br>BEL                                                                                                                                                         |                                                                                  |

| 84<br>85                               | PA31<br>PA30                                         | 1/0  | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E                                                                                                                           | BE3<br>BE2<br>BE1<br>BE0<br>BUS - This is a bi-direction                                                                                                                                                     | Not connected<br>PA1<br>BEH<br>BEL<br>nal address bus between th                                                                                                                           | •                                                                                |

| 84<br>85<br>86                         |                                                      | 1/0  | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During                                                                                                        | BE3<br>BE2<br>BE1<br>BE0<br>BUS – This is a bi-direction<br>CPU accesses to FE6010 i                                                                                                                         | Not connected<br>PA1<br>BEH<br>BEL<br>nal address bus between th                                                                                                                           | •                                                                                |

| 85                                     | PA30                                                 | 1/0  | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During                                                                                                        | BE3<br>BE2<br>BE1<br>BE0<br>BUS - This is a bi-direction                                                                                                                                                     | Not connected<br>PA1<br>BEH<br>BEL<br>nal address bus between th                                                                                                                           | •                                                                                |

| 85<br>86                               | PA30<br>PA29                                         | I/Ο  | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During<br>DMA transfers the                                                                                   | BE3<br>BE2<br>BE1<br>BE0<br>BUS – This is a bi-direction<br>CPU accesses to FE6010 i                                                                                                                         | Not connected<br>PA1<br>BEH<br>BEL<br>mal address bus between the<br>registers, these are input s                                                                                          | ignals, and during                                                               |

| 85<br>86<br>88                         | PA30<br>PA29<br>PA28                                 | ΙΟ   | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During<br>DMA transfers the<br>During DMA trans                                                               | BE3<br>BE2<br>BE1<br>BE0<br>BUS - This is a bi-direction<br>CPU accesses to FE6010 of<br>ay are output signals.                                                                                              | Not connected<br>PA1<br>BEH<br>BEL<br>nal address bus between th<br>registers, these are input s                                                                                           | ignals, and during<br>r-on default, the                                          |

| 85<br>86<br>88<br>89                   | PA30<br>PA29<br>PA28<br>PA27                         | 1/0  | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During<br>DMA transfers the<br>During DMA trans<br>FE6010 drives PA                                           | BE3<br>BE2<br>BE1<br>BE0<br>BUS – This is a bi-direction<br>CPU accesses to FE6010 of<br>an eoutput signals.                                                                                                 | Not connected<br>PA1<br>BEH<br>BEL<br>hal address bus between th<br>registers, these are input s<br>y mode, which is the powe<br>ogrammed addresses. Bits                                  | ignals, and during<br>r-on default, the<br>s (31:24) are al-                     |

| 85<br>86<br>88<br>89<br>90             | PA30<br>PA29<br>PA28<br>PA27<br>PA26                 | 1/0  | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During<br>DMA transfers the<br>During DMA trans<br>FE6010 drives PA<br>ways driven to zet                     | BE3<br>BE2<br>BE1<br>BE0<br>3US - This is a bi-directior<br>CPU accesses to FE6010 r<br>ey are output signals.<br>ders in the IBM compatibility<br>(23:2) according to the pro-<br>ro. In Enhanced Addressin | Not connected<br>PA1<br>BEH<br>BEL<br>hal address bus between th<br>registers, these are input s<br>y mode, which is the powe<br>ogrammed addresses. Bits                                  | ignals, and during<br>r-on default, the<br>s (31:24) are al-                     |

| 85<br>86<br>88<br>89<br>90<br>91       | PA30<br>PA29<br>PA28<br>PA27<br>PA26<br>PA25         | νo   | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During<br>DMA transfers the<br>During DMA trans<br>FE6010 drives PA                                           | BE3<br>BE2<br>BE1<br>BE0<br>3US - This is a bi-directior<br>CPU accesses to FE6010 r<br>ey are output signals.<br>ders in the IBM compatibility<br>(23:2) according to the pro-<br>ro. In Enhanced Addressin | Not connected<br>PA1<br>BEH<br>BEL<br>hal address bus between th<br>registers, these are input s<br>y mode, which is the powe<br>ogrammed addresses. Bits                                  | ignals, and during<br>r-on default, the<br>s (31:24) are al-                     |

| 85<br>86<br>88<br>89<br>90<br>91<br>92 | PA30<br>PA29<br>PA28<br>PA27<br>PA26<br>PA25<br>PA24 | ΙΟ   | SIGNAL<br>BE3<br>BE2<br>BE1<br>BE0<br>CPU ADDRESS E<br>the DMA. During<br>DMA transfers the<br>During DMA trans<br>FE6010 drives PA<br>ways driven to zet<br>the programmed a | BE3<br>BE2<br>BE1<br>BE0<br>3US - This is a bi-directior<br>CPU accesses to FE6010 r<br>ey are output signals.<br>ders in the IBM compatibility<br>(23:2) according to the pro-<br>ro. In Enhanced Addressin | Not connected<br>PA1<br>BEH<br>BEL<br>nal address bus between the<br>registers, these are input s<br>y mode, which is the powe<br>ogrammed addresses. Bits<br>g Mode all the bits are driv | ignals, and during<br>r-on default, the<br>s (31:24) are al-<br>ren according to |

O = Output, I = Input, I/O = Bi-directional

l

| PIN NO.                                                                                                                                                                                                                                                         | NAME                                                                                                                                                                                      | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                             |                                                                                                                                                                                |                                                                                                                                                                     |                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 97                                                                                                                                                                                                                                                              | PA20                                                                                                                                                                                      | 1/O  | CPU ADDRESS BUS                                                                                                                                                                                                                                                                                                                                                                               | S – (Continue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ed)                                                                                                                                                                                                                         |                                                                                                                                                                                |                                                                                                                                                                     |                                                                                                                                                                                                                      |

| 98                                                                                                                                                                                                                                                              | PA19                                                                                                                                                                                      |      |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                             |                                                                                                                                                                                |                                                                                                                                                                     |                                                                                                                                                                                                                      |