WD60C40A

Peripheral Cache

Manager Device

# **TABLE OF CONTENTS**

| Section | Title |                                                                                                          | Page  |

|---------|-------|----------------------------------------------------------------------------------------------------------|-------|

| 1.0     | INTE  |                                                                                                          | 29-1  |

|         | 1.1   | Architectural Description                                                                                | 29-1  |

|         | 1.2   | Features                                                                                                 |       |

|         |       | 1.2.1 Longitudinal Redundancy Checking                                                                   | 29-3  |

|         |       | 1.2.2 Through Parity                                                                                     | 29-3  |

|         |       | 1.2.3 Western Digital Bus Mode                                                                           | 29-3  |

| 2.0     | PIN I | DESCRIPTION                                                                                              | 29-6  |

| 3.0     | NON   | J-CHANNEL REGISTERS                                                                                      | 29-8  |

|         | 3.1   | Option Register                                                                                          |       |

|         |       | 3.1.1 RRC3 thru RRC0 Refresh Rate Count Field                                                            |       |

|         |       | 3.1.2 SRAM Static RAM Mode (Bit 4)                                                                       |       |

|         |       | 3.1.3 CAW1, CAW0 Column Address Width Field (Bits 6,5)                                                   |       |

|         |       | 3.1.4 MPAR Memory Parity Enable (Bit 7)                                                                  | 29-9  |

|         | 3.2   | Option Register 2                                                                                        |       |

|         |       | 3.2.1 AINTE A Channel Interrupt Enable                                                                   | 29-10 |

|         |       | 3.2.2 BINTE B Channel Interrupt Enable                                                                   | 29-10 |

|         |       | 3.2.3 WAITE Wait Enable                                                                                  | 29-10 |

|         |       | 3.2.4 NOWAIT Non-Waitable Microprocessor Interface (Bit 5)                                               | 29-10 |

|         | 3.3   | Master Status Register                                                                                   | 29-11 |

|         |       | 3.3.1 AINTR Channel A Interrupt Request Read Only Bit<br>BINTR Channel B Interrupt Request Read Only Bit | 20-11 |

|         |       | 3.3.2 PPE Processor Parity Error                                                                         |       |

|         |       | 3.3.3 BANR Buffer Access Not Ready Read Only Bit                                                         |       |

|         |       | 3.3.4 PRNR Power Reset Not Ready (Bit 4) Read Only Bit                                                   |       |

|         |       | 3.3.5 DNR Device Not Ready (Bit 7) Read Only Bit                                                         |       |

|         | 3.4   | Buffer Data Latch                                                                                        |       |

|         | 3.5   | Microprocessor Address Pointer                                                                           |       |

|         | 3.6   | Test Address & Status Register                                                                           |       |

|         | 3.7   | Reset and Test Register                                                                                  |       |

|         | •     | 3.7.1 MTPAF Microprocessor to Port A FIFO Test (Bit 0)                                                   |       |

|         |       | 3.7.2 MTPBF Microprocessor to Port B FIFO Test (Bit 1)                                                   |       |

|         |       | 3.7.3 CNTRT Counter Test Mode (Bit 2)                                                                    |       |

|         |       | 3.7.4 TSMEM - Tri-State Memory Interface (Bit 3)                                                         |       |

|         |       | 3.7.5 ARST A Channel Reset (Bit 4)                                                                       |       |

|         |       | 3.7.6 BRST B Channel Reset (Bit 5)                                                                       |       |

|         |       | 3.7.7 SWRST Software Reset (Bit 7)                                                                       |       |

|         | 3.8   | Buffer Access Register                                                                                   |       |

|         | 3.9   | Autoincrement Access Register                                                                            |       |

| Section | Title |         |                                                      | Page    |

|---------|-------|---------|------------------------------------------------------|---------|

| 4.0     | DEVI  | CE CHAN |                                                      |         |

|         | 4.1   | Channel | Timing Register                                      |         |

|         |       | 4.1.1   | SC0(1)A (SC0(1)B) Channel Strobe Control Field       | . 29-17 |

|         |       | 4.1.2   | DLYA (DLYB) Delay Strobe Bit                         | . 29-17 |

|         |       | 4.1.3   | SDTCA (SDTCB) Strobe Deasserted Time Control Bit     | . 29-17 |

|         |       | 4.1.4   | RQPLA (RQPLB) DMA Request Polarity Bit               | . 29-17 |

|         |       | 4.1.5   | DKPLA (DKPLB) DMA Acknowledge Polarity Bit           | . 29-17 |

|         |       | 4.1.6   | PPEA (PPEB) Port Parity Enable Bit                   | . 29-17 |

|         |       | 4.1.7   | LPBMA (LPBMB) Loop Back Mode Enable                  | . 29-17 |

|         | 4.2   | Channel | Control Register                                     | . 29-19 |

|         |       | 4.2.1   | IBEA (IBEB) Interrupt on Busy Bit                    | . 29-19 |

|         |       | 4.2.2   | DIRA (DIRB) Channel Transfer Direction Bit           | . 29-19 |

|         |       | 4.2.3   | PAUSA (PAUSB) Channel Pause Control Bit (Bit 3)      | . 29-20 |

|         |       | 4.2.4   | EDACA (EDACB) EDAC Idle Enable (Bit 4)               | . 29-20 |

|         |       | 4.2.5   | DISKA (DISKB) Disk Type Device (Bit 5)               | . 29-20 |

|         |       |         | BRSTA (BRSTB) Burst Transfer Device (Bit 6)          | . 29-20 |

|         |       |         | SLAVA (SLAVB) Slave Mode Interface (Bit 7)           | . 29-20 |

|         |       | 4.2.6   | 000 DMA Single Cycle Master                          |         |

|         |       | 4.2.7   | 002 DMA Single Cycle Disk                            |         |

|         |       | 4.2.8   | 010 DMA Burst Cycle Master                           | . 29-21 |

|         |       | 4.2.9   | 011 Programmed I/O Mode                              | . 29-22 |

|         |       | 4.2.10  | 100 Single Cycle Slave Mode                          | . 29-22 |

|         |       | 4.2.11  | Unused & Reserved Mode                               | . 29-22 |

|         |       | 4.2.12  | 110 Burst Cycle Slave Mode                           |         |

|         |       | 4.2.13  | 111 Slave Burst Mode Disk                            | . 29-22 |

|         | 4.3   | Channel | Status Register                                      | . 29-23 |

|         |       | 4.3.1   | BSYA (BSYB) Channel Busy Status                      |         |

|         |       | 4.3.2   | VBSYA (VBSYB) Channel Very Busy Status               |         |

|         |       | 4.3.3   | FMTA (FMTB) Channel FIFO Empty Status (Bit 2)        |         |

|         |       | 4.3.4   | PNRA (PNRB) Port Not Ready Status (Bit 3)            |         |

|         |       | 4.3.5   | RQSTA (RQSTB) Channel DRQ Pin Status (Bit 4)         | . 29-23 |

|         |       | 4.3.6   | DKSTA (DKSTB) Channel DACK Pin Status (Bit 5)        |         |

|         | 4.4   | Channel | Interrupt Status Register                            | . 29-24 |

|         |       | 4.4.1   | BSYIA (BSYIB) Interrupt From Busy                    |         |

|         |       | 4.4.2   | VBIA (VBIB) Interrupt From Very Busy                 |         |

|         |       | 4.4.3   | PERRA (PERRB) Channel Parity Error Bit               |         |

|         |       | 4.4.4   | LATEA (LATEB) Channel Data Late Error Bit (Bit 3)    |         |

|         |       | 4.4.5   | REJA (REJB) Channel Command Reject Error Bit (Bit 4) |         |

|         |       | 4.4.6   | IOEA (IOEB) I/O Error Bit (Bit 5)                    |         |

|         |       | 4.4.7   | IOPEA (IOPEB) Programmed I/O Parity Error (Bit 6)    |         |

|         |       |         |                                                      |         |

| Section | Title P                                                                                                                                                                                                                                                                                                                        | age                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Section | 4.4.8   AERRA (AERRB) Any Error Bit (Bit 7)   29     4.5   Channel Data Latch   29     4.6   Channel Buffer Pointer   29     4.7   Channel Transfer Counter   29     4.8   Channel Start Register   29     4.9   Channel Stop Register   29     4.10   Channel Pointer Capture Register   29     4.11   EDAC Idle Counter   29 | 9-25<br>9-26<br>9-27<br>9-28<br>9-29<br>9-30<br>9-30 |

|         | 4.12 Longitudinal Reduncy Checking Register                                                                                                                                                                                                                                                                                    | Э-31                                                 |

| 5.0     | MICROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                       | <del>)</del> -32                                     |

| 6.0     | I/O MEMORY MAP                                                                                                                                                                                                                                                                                                                 | э-зз                                                 |

| 7.0     | INTERRUPTS                                                                                                                                                                                                                                                                                                                     | 9-33                                                 |

| 8.0     | RESET SEQUENCES                                                                                                                                                                                                                                                                                                                | 9-33                                                 |

| 9.0     | READY SEQUENCES AND LATENCIES                                                                                                                                                                                                                                                                                                  | э-34                                                 |

| 10.0    | NON-CHANNEL REGISTERS MAP                                                                                                                                                                                                                                                                                                      | э-35                                                 |

| 11.0    | CHANNEL REGISTERS MAP                                                                                                                                                                                                                                                                                                          | 9-36                                                 |

| 12.0    | ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                     | 9-37                                                 |

| 13.0    | MISCELLANEOUS CHARACTERISTICS                                                                                                                                                                                                                                                                                                  | <del>9</del> -38                                     |

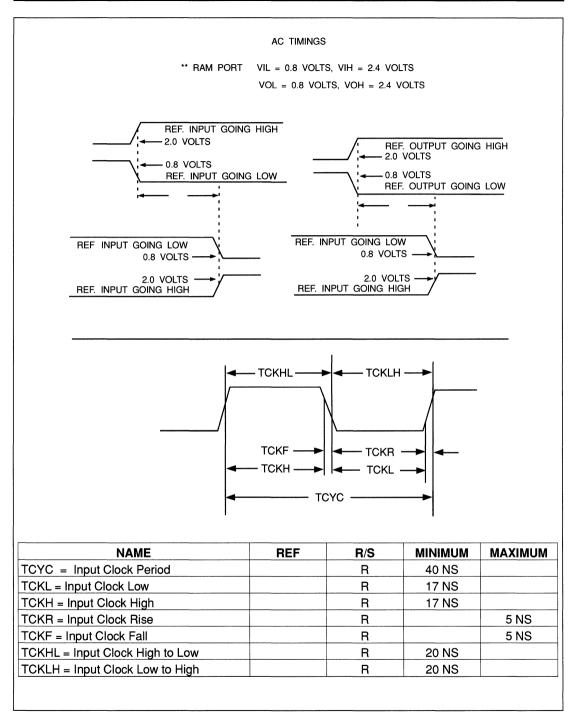

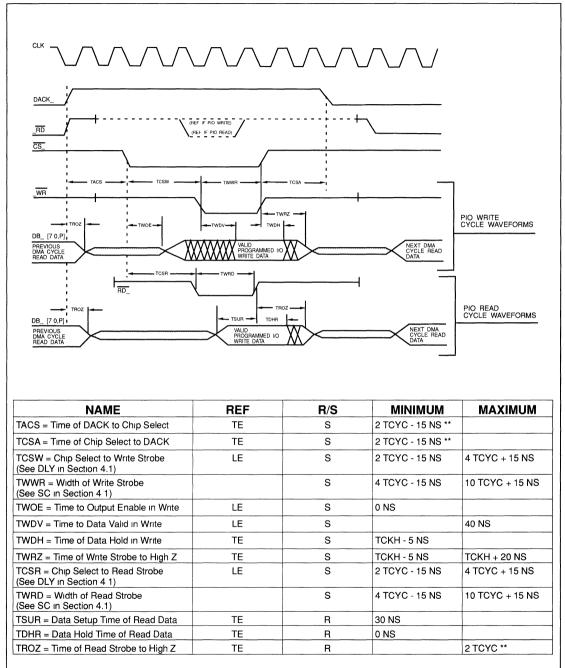

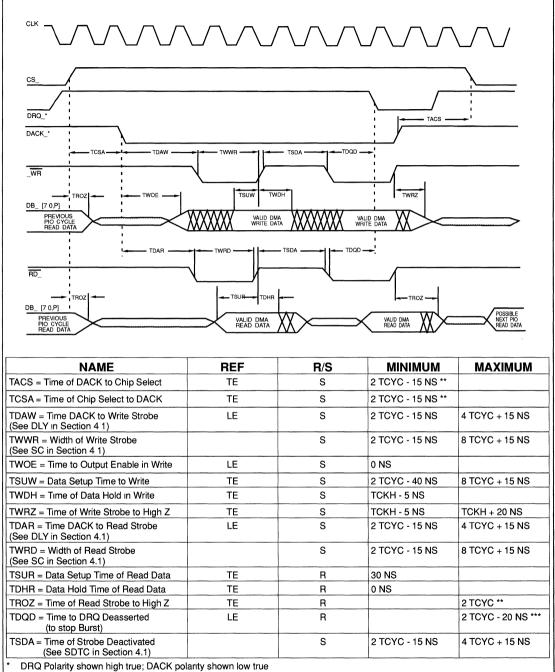

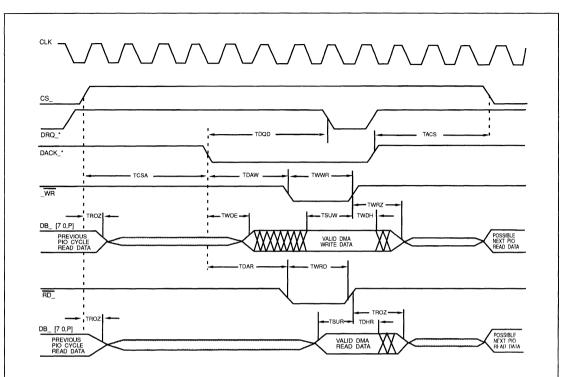

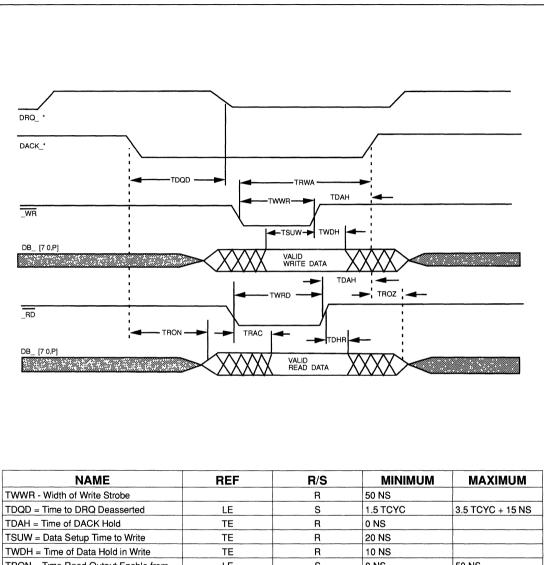

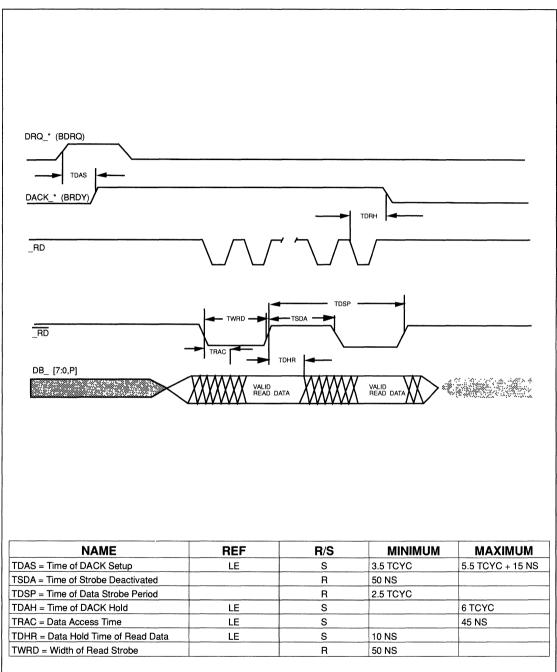

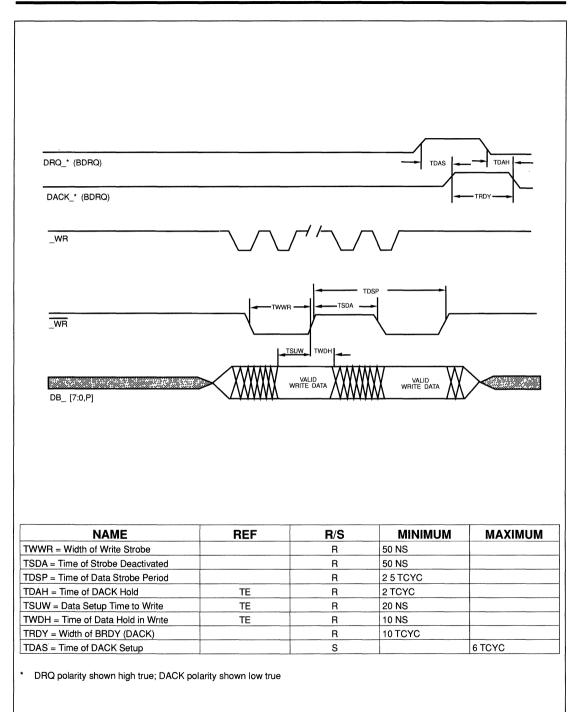

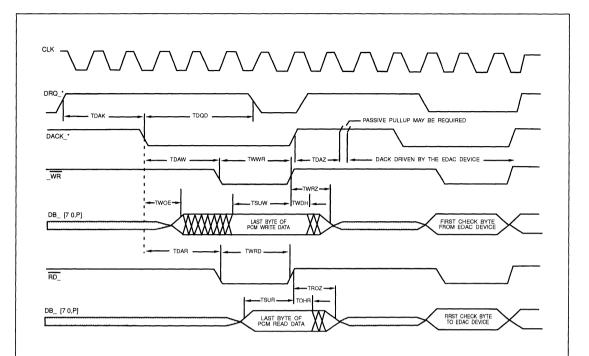

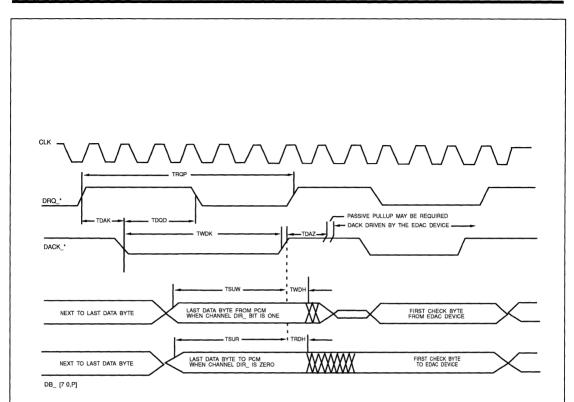

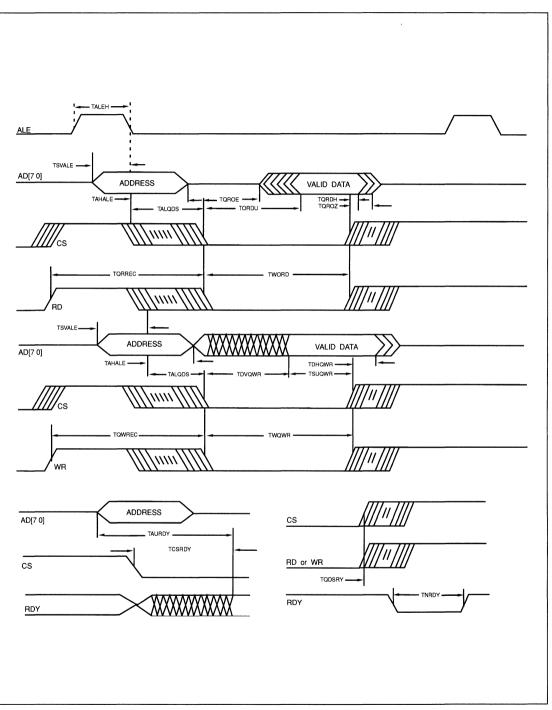

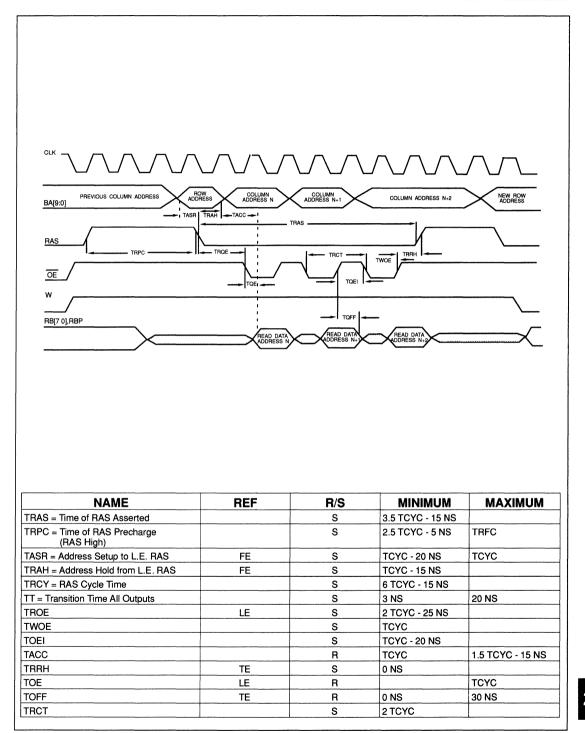

| 14.0    | TIMING SPECIFICATION                                                                                                                                                                                                                                                                                                           | 9-38                                                 |

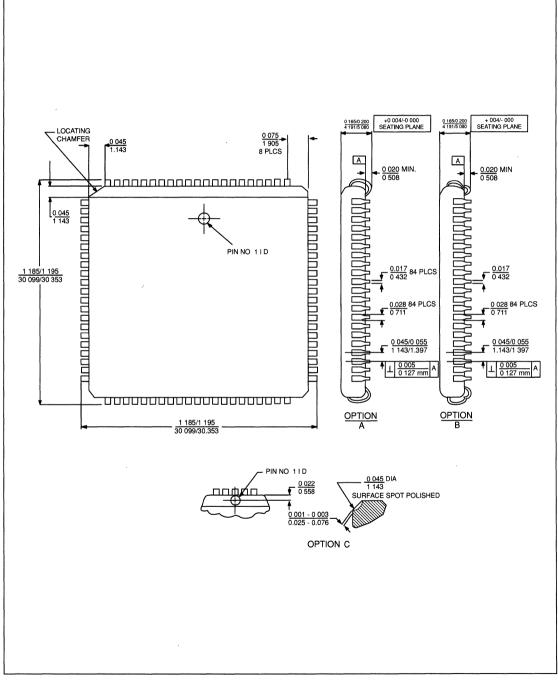

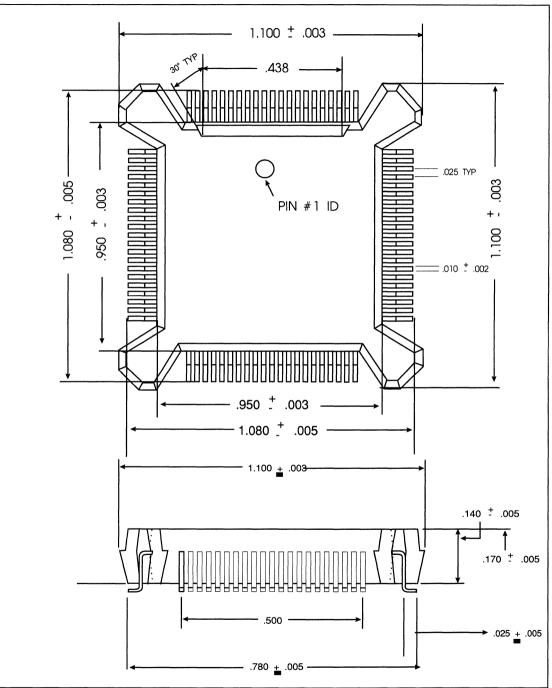

| 15.0    | PACKAGE DIAGRAMS                                                                                                                                                                                                                                                                                                               | 9-58                                                 |

# LIST OF ILLUSTRATIONS

| Figure | Title                               | Page |

|--------|-------------------------------------|------|

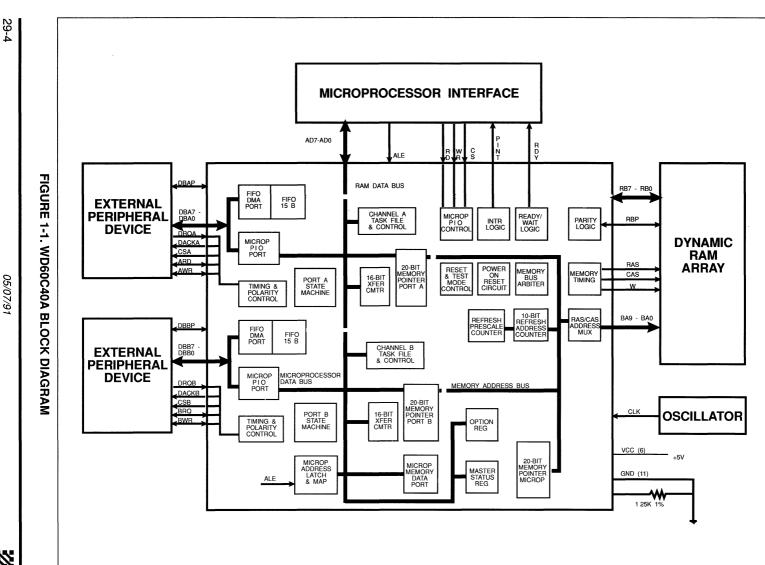

| 1-1    | WD60C40 Block Diagram               |      |

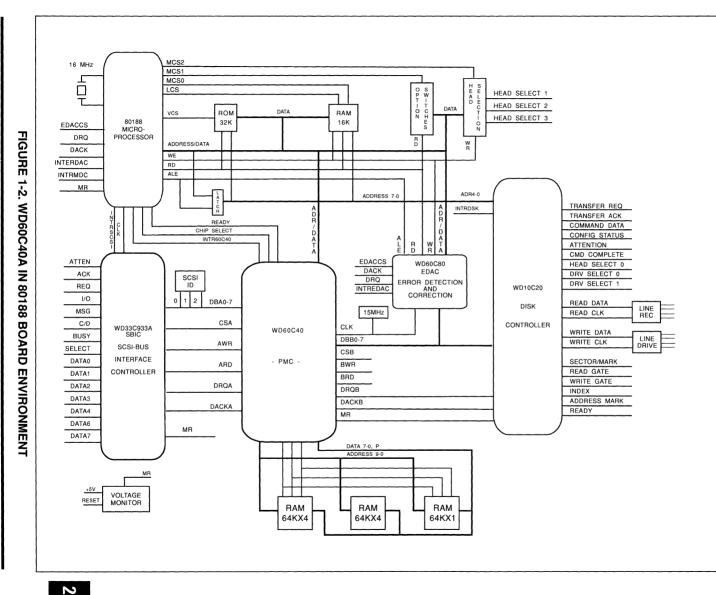

| 1-2    | WD60C40 in 80188 Board Environment  |      |

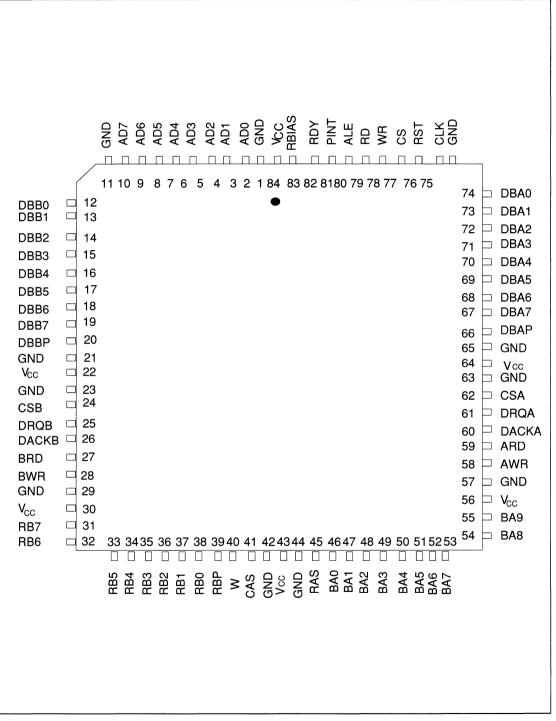

| 2-1    | 84-Pin PLCC or PQFP Pin Assignments |      |

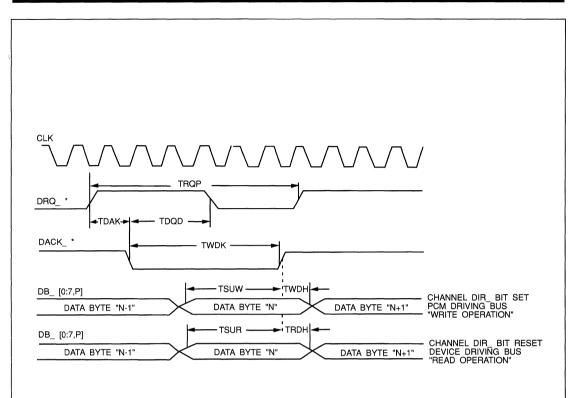

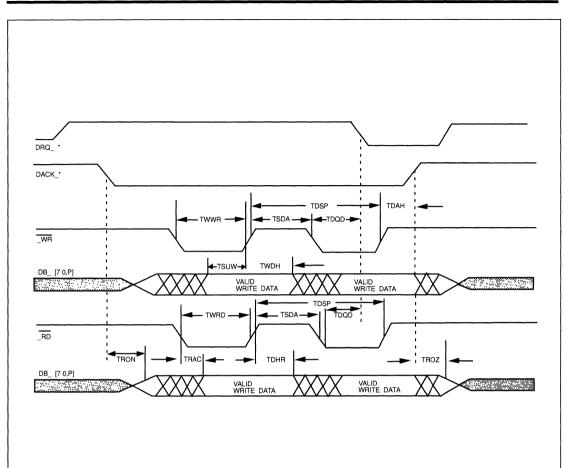

| 14-1   | Rise/Fall and Miscellaneous Timing  |      |

| 14-2   | PIO Read/Write of External Devices  |      |

| 14-3   | DMA Burst Mode Transfers            |      |

| 14-4   | DMA Single Cycle Mode               |      |

| 14-5   | Bus Master Disk Mode                |      |

| 14-6   | Slave Burst Mode Transfers          |      |

| 14-7   | Slave Single Cycle Transfer         |      |

| 14-8   | Slave Burst Disk Mode (Read)        |      |

| 14-9   | Slave Burst Disk Mode (Write)       |      |

| 14-10  | EDAC Mode (DMA Single Cycle)        |      |

| 14-11  | EDAC Mode (DMA Disk)                |      |

| 14-12  | Miicroprocessor Bus Timing          |      |

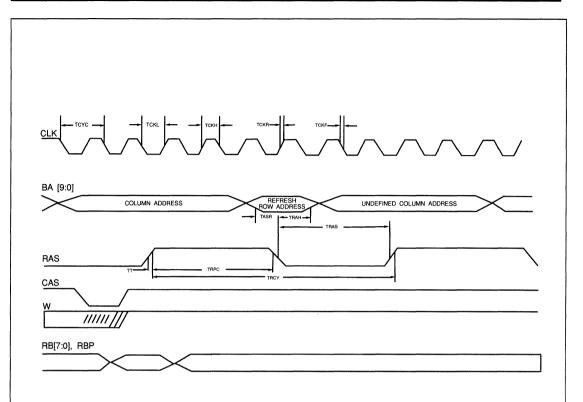

| 14-13  | RAS Only Refresh Timing             |      |

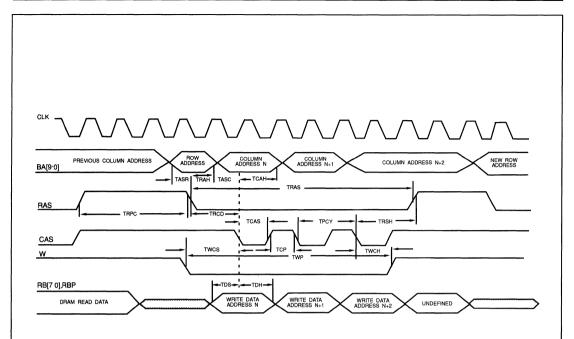

| 14-14  | Page Mode Write Timing              |      |

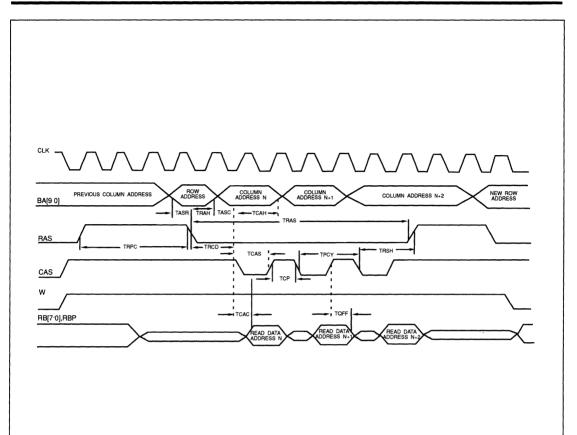

| 14-15  | Page Mode Read Timing               |      |

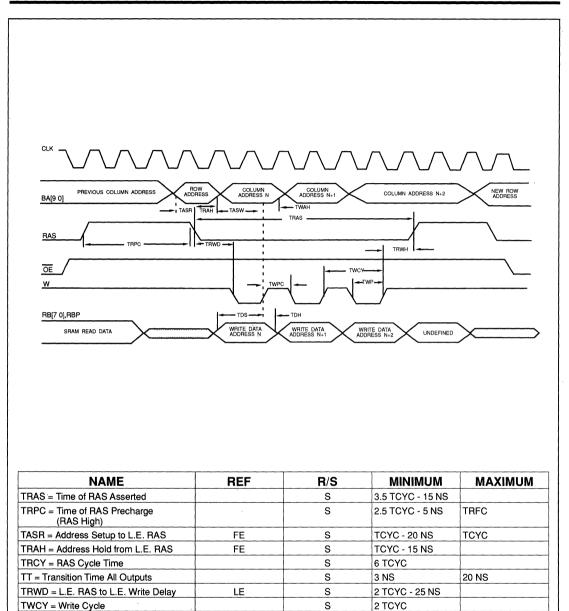

| 14-16  | Static RAM Write Timing             |      |

| 14-17  | Static RAM Read Timing              |      |

| 15-1   | 84-Pin PLCC Package Dimensions      |      |

| 15-2   | 84-Pin PQFP Package Dimensions      |      |

# LIST OF TABLES

| Table | Title                     | Page    |

|-------|---------------------------|---------|

| 2-1   | Pin Descriptions          | . 29-6  |

| 14-1  | Microprocessor Bus Timing | . 29-52 |

# 1.0 INTRODUCTION

## 1.1 ARCHITECTURAL DESCRIPTION

The WD60C40A peripheral cache manager (PCM) is a custom enhancement of the WD60C40, and is intended to be a drop-in replacement for the latter device. The WD60C40A is fully compatible with the WD60C40 as far as functional and timing requirements are concerned. In addition, the WD60C40A provides three new features: longitudinal redundancy checking (LRC), through parity, and an improved slave burst mode protocol (WD Bus Mode).

The WD60C40A peripheral cache manager (PCM) can control 1 Mbyte of dynamic RAM and the buffering required to allow seemingly simultaneous access of this buffer by three requestors. The three requestors are assumed to be two block-oriented devices and a microprocessor.

The two device interfaces to the dynamic RAM are designed to support block-oriented peripheral formatter chips, such as the WD10C00 Hard Disk Formatter, or block-oriented bus interface chips, such as the WD33C93A SCSI Bus Interface Chip. The implication of block-oriented devices is that the devices do not have the capability of randomly accessing data within the memory array. This restriction allows for the removal of the addressing pins that are normally associated with an interface. The 20-bit address counters that are required to select a byte within the array are now incorporated into the WD60C40A.

The buffer control logic interfaces with an external dynamic RAM array and arbitrates the access into this array from the three external sources. The internal arbitrator in the PCM also includes the refresh logic that is internal to the PCM into its arbitration mechanism.

The dynamic RAM memories do not have the random access bandwidth to sustain multiple highspeed devices. The dynamic RAM memories do incorporate a feature known as "page mode" that increases their bandwidth to the point that they can sustain multiple high-speed devices. The dynamic RAMs have a multiplexed address bus width the address into the array being divided into two parts, a row address and a column address. The dynamic RAMs allow a feature that if the next access into the array is in the same row (same page), then only the column address must be updated from the addressing logic. This scheme carries the penalty that a FIFO must be available to hold the data to/from the pcrt to ensure that it can transfer data in a continuous block when a port gains access to the RAM. The PCM incorporates 16 bytes of FIFO into each of the peripheral ports to support the page mode memory architecture. This scheme has the advantage that the memory bandwidth is increased by a factor of about 75% over the random access bandwidth, allowing a large buffer memory to be mechanized by inexpensive dynamic RAMs, but having the performance characteristics of a static RAM buffer.

The external dynamic RAM buffer may be eight bits or nine bits wide. The depth of the array and the organization of the devices that make up the array are as follows:

| SIZE   | OR | GANIZATION | J                    |

|--------|----|------------|----------------------|

| 16 KB  | 2  | 16Kb x 4   | (+ 64Kb x 1 parity)  |

| 64 KB  | 2  | 64Kb x 4   | (+ 64Kb x 1 parity)  |

| 64 KB  | 8  | 64Kb x 1   | (+ 64Kb x 1 parity)  |

| 256 KB | 2  | 256Kb x 4  | (+ 256Kb x 1 parity) |

| 256 KB | 8  | 256Kb x 1  | (+ 256Kb x 1 parity) |

| 1 MB   | 2  | 1Mb x 4    | (+ 1Mb x 1 parity)   |

| 1 MB   | 8  | 1Mb x 1    | (+ 1Mb x 1 parity)   |

Note: The use of static RAM is possible with additional logic.

In the following description, refer to Figure 1, the block diagram of the WD60C40A, and to the example board environment in Figure 2. A typical situation to use as an example of the actions within the part is that of a disk controller. In this example, port 'B' of the device is connected to a bus interface controller (ex. WD33C93A), and port 'A' of the device is connected to a disk interface controller (ex. WD10C00).

The example begins with the assumption that all devices are currently active, the refresh time has arrived, and the microprocessor is requesting a data item. The PCM is currently servicing the FIFO that is attached to the device port 'A'. The microprocessor is currently at a wait bus cycle because of the RDY signal from the PCM being inactive. The PCM moves data to/from the memory and the port 'A' FIFO until the FIFO is full/empty, or the transfer counter of port 'A' is exhausted. If during this sequence, the PCM detects that a dynamic RAM page boundary is

being crossed, the PCM will update the row address, and continue the page mode transfer. While this action is occuring, any byte transfers to/from the other device port are stored in that device port's FIFO. When port 'A' has finished its data transfers, the PCM first services the host data request, then the refresh request(s), both of which have priority over block transfers. The PCM then initiates transfer between the port 'B' FIFO, and the dynamic RAMs.

The PCMs priority system when arbitrating is:

- microprocessor requests

- refresh requests

- the higher priority peripheral channel

- the lower priority peripheral channel

The control of the peripheral channel priority is under firmware control if the channels are peers in their capability of sustaining a pause in their transfers. If a channel is programmed as 'nonpausible', and the other channel is 'pausible' then this channel is given priority in the arbitration mechanism, regardless of the other firmware priority controls. If the channels are peers, such as both being 'pausible' or both being 'nonpausible', then the priority of the channels is controlled by firmware selecting one of the channels as higher priority through option register 2. See also the descriptions of the AHI bit in option register 2, and PAUS bits in the channel control register.

Note that arbitration does not occur until the requestor currently being serviced has completed its entire burst. This means that page mode bursts between the channels and memory are not interrupted by requests from higher priority requestors. There are two exceptions to this general rule. The first exception is a non-pausible device that is selected by firmware as having higher arbiter priority. This channel is then allowed an "urgent request", when its FIFO is almost exhausted. This "urgent request" will send a false end of transfer signal through the other port and cause arbitration to occur, and this channel will then win arbitration if the single cycle devices are not requesting. This is done to minimize the occurence of over/underrun errors in high priority non-pausible devices. The second exception that causes a burst to be halted is for a refresh burst. The refresh request occurs at regular intervals (see option register section for specific details), but if it is not serviced because of a channel burst, then the request is

queued into a counter. When four refresh cycles have been queued (about 60  $\mu$ sec.), then the "urgent request" mechanism will force arbitration, and a burst of four refresh cycles will be performed. This is done to maintain memory data integrity.

The programmable features of the internal logic allow the controller firmware to control and "tune" the actions of the PCM. The PCM needs know if the devices are capable of being throttled. Most devices that attach to peripherals have minimum data buffering, so the port logic must be programmed to look for overrun/underrun situations when the FIFO is full/empty. Some devices that attach to busses or other peripherals that have variable data rates, are capable of being 'stalled' when the FIFO is full/empty, and the port logic is capable of holding the port until the FIFO is ready.

The PCM also implements a "pipelined" pointer mechanism that allows the programmer to set the pointer (buffer address) of the current device transfer, and if required, set the pointer of the next transfer, while the current transfer is taking place. This address is held in the address pointer holding register to be automatically transferred to the address pointer at the end of the current transfer. If the next transfer's buffer is contiguous with the current transfer's buffer, then the address pointer "pipeline" need not be loaded, and when the next transfer begins the address pointer will continue from its current position. This address is therefore only necessary if the next transfer is at a memory address that is not contiguous with the end of the current transfer. The transfer counter is always loaded from the transfer counter holding register at the start of a new block transfer, but the transfer counter holding register need only be reloaded if the block size of a transfer needs to be changed. When the current transfer finishes, the firmware can be interrupted, while the hardware continues directly into the next transfer. With this mechanism, the firmware now has a block time to determine what is to be done when this transfer finishes, rather than doing this during the interblock gap times. If pipelined (ie. continuous) transfers are required, then microprocessor action is required whenever the pipeline becomes empty. If the next transfer is the same size as the current, and contiguous in address, then the firmware need only issue a new channel start command. Alternatively, the firmware can load new values into the "pipeline" registers before issuing the

start, and dynamically control the transfer size and buffer location. The firmware can poll the status or wait for an interrupt (if enabled) to indicate that the holding registers are available.

The device channels are mechanized with eight or nine data lines, and five control/handshake lines. Four control signals are programmable to allow interfaceing to multiple types of device controller chips. Features such as the master/slave relationships between the PCM and the external peripheral controller, the polarity and timing of the signals that do the handshake, input/output control direction, and the mode that the control lines emulate are all programmable.

## 1.2 FEATURES

- 5 Volt only operational power.

- 1.25 micron CMOS for low power consumption.

- 84 pin PLCC or 84-pin PQFP packages.

- Supports dynamic memory configurations from 16 KB to 1 MB.

- · Supports static memory configurations.

- Supports parity on the memory array.

- · Supports parity on peripheral ports.

- Supports parity pass-through (parity is passed through a device with the data and not regenerated at the device's outputs).

- Supports longitudinal redundancy checking (LRC) on peripheral ports and FIFOs.

- Aggregate memory bandwidth of greater than 9.0 Mbytes/sec, using industry standard 100 ns. dynamic RAMs.

- · Supports two peripheral channels.

- High Speed Channels support peripheral data rates of:

- 6.25 Mbytes/sec as bus master with 25 MHz input clock, the maximum data rate is input clock divided by 4.

- 10.0 Mbytes/sec as bus slave, with 25 MHZ input clock, the maximum data rate is input clock divided by 2.5.

- Programmable configuration of device channel interface.

- Internal FIFOs on peripheral channels.

- Supports independant transfers on both peripheral ports and microprocessor simultaneously.

- Large memory allows peripheral controllers to be implemented that "decouple" the host and disk transfer rates, maintaining 1:1 disk interleave regardless of host transfer rate.

- Provides "minimum chip count" solution for mechanizing a peripheral cache controller.

- Supports high-speed microprocessor bus cycles, such as Intel\* 80186 or 80188 processors running at 12.5 MHz (no wait state required when accessing the PCM registers).

#### 1.2.1 Longitudinal Redundancy Checking

Both channels must operate as the bus master when using the LRC feature. LRC generation and checking takes place between the channel data bus input and output buffers and the channel FIFO. The LRC calculations do not include the parity bit. Refer to Section 4.12 for more information.

#### 1.2.2 Through Parity

Parity is passed through the chip with the data and not regenerated at the chip's output. This makes it possible to chain "send status" in the WD33C93A.

#### 1.2.3 Western Digital Bus Mode

The slave burst DMA protocol is modified in order to use the pipelining capability of the WD60C40A with the SBIC. As the WD60C40A nears the end of a burst, it switches to a single-byte transfer protocol to avoid over/under-flowing the FIFO. In the old implementation, the WD60C40 waits to deassert DRQ when both DACK and the \_RD or \_WR strobe is asserted. This may result in the SBIC sending two bytes instead of just one. The WD60C40 will be confused if the SBIC sends two bytes on the last request. The new implementation fixes this by having the WD60C40A deassert DRQ upon the assertion of DACK, thus guaranteeing that the SBIC sends only one byte.

INTRODUCTION

$\otimes$

INTRODUCTION

WD60C40A

$\otimes$

05/07/91

29-5

9

## 2.0 PIN DESCRIPTION

| PIN NUMBER                              | MNEMONIC                  | SIGNAL NAME                     | I/O              |

|-----------------------------------------|---------------------------|---------------------------------|------------------|

| 1,22,30,43,<br>56,64                    | Vcc                       | +5 Volt power supply connection | I                |

| 2,11,21,23,<br>29,42,44,57,<br>63,65,75 | GND                       | Ground power supply connection  | Ι                |

| 3 thru 10                               | AD0 thru AD7              | μP ADDRESS/DATA BUS             | I/O              |

| 12 thru 19                              | DBB0 thru<br>DBB7         | DEVICE BUS B DATA               | I/O              |

| 20                                      | DBBP                      | DEVICE BUS B PARITY BIT         | I/O              |

| 24                                      | CSB                       | CHANNEL SELECT B                | 0                |

| 25                                      | DRQB                      | DEVICE PORT B CYCLE REQUEST     | I/O <sup>1</sup> |

| 26                                      | DACKB                     | DEVICE PORT B CYCLE ACKNOWLEDGE | I/O <sup>2</sup> |

| 27                                      | BRD                       | DEVICE PORT B READ STROBE       | I/O              |

| 28                                      | BWR                       | DEVICE PORT B WRITE STROBE      | I/O              |

| 31 thru 38                              | RB7 thru RB0              | DYNAMIC RAM DATA BUS            | I/O              |

| 39                                      | RBP                       | DYNAMIC RAM PARITY BIT          | I/O              |

| 40                                      | W/WE                      | DYNAMIC RAM WRITE/STATIC RAM WE | 0                |

| 41                                      | CAS/OE                    | DYNAMIC RAM CAS/STATUS RAM OE   | 0                |

| 45                                      | RAS                       | RAM ROW ADDRESS STROBE          | 0                |

| 46 thru 55                              | BA0 <sup>3</sup> thru BA9 | RAM ADDRESS BUS <sup>3</sup>    | 0                |

| 58                                      | AWR                       | DEVICE PORT A WRITE STROBE      | I/O              |

| 59                                      | ARD                       | DEVICE PORT A READ STROBE       | I/O              |

| 60                                      | DACKA                     | DEVICE PORT A CYCLE ACKNOWLEGE  | I/O <sup>2</sup> |

| 61                                      | DRQA                      | DEVICE PORT A CYCLE REQUEST     | I/O <sup>1</sup> |

| 62                                      | CSA                       | CHANNEL SELECT A                | 0                |

| 66                                      | DBAP                      | DEVICE BUS A PARITY BIT         | I/O              |

| 67 thru 74                              | DBA7 thru<br>DBA0         | DEVICE BUS A DATA BUS           | I/O              |

| 76                                      | CLK                       | CLOCK                           | I                |

| 77                                      | RST                       | RESET                           | 1                |

| 78                                      | CS                        | up BUS CHIP SELECT              | I                |

| 79                                      | WR                        | μP BUS WRITE CYCLE STROBE       | <u> </u>         |

| 80                                      | RD                        | μΡ BUS READ CYCLE STROBE        | I                |

| 81                                      | ALE                       | μP ADDRESS STROBE               | I                |

| 82                                      | PINT                      | μP INTERRUPT REQUEST            | O <sup>4</sup>   |

| 83                                      | RDY                       | μΡ WAIT CONTROL                 | O <sup>4</sup>   |

| 84                                      | RBIAS <sup>5</sup>        | RESISTOR BIAS <sup>5</sup>      |                  |

#### NOTES:

1 I = WD60C40A bus master mode. O = WD60C40A bus slave mode

2 I = WD60C40A bus slave mode. O = WD60C40A bus master mode.

3 BA0 is the LSB.

4 Open drain output

## **TABLE 2-1. PIN DESCRIPTIONS**

FIGURE 2-1. 84-PIN PLCC OR PQFP PIN ASSIGNMENTS

29

## 3.0 NON-CHANNEL REGISTERS

The PCM was intended for use with the Intel 80186 processor and as such has been designed to interface easily with the 16-bit data bus of that processor. This is not to say that it cannot easily attach to other 8-bit or 16-bit microprocessors like Intel 8085, 8051, or 8096. The main requirement is that it be supplied with a multiplexed address/data bus with A7 to A0 multiplexed with D7 to D0 in that order.

As the PCM has only an eight bit data bus and it was decided not to handle the BHE signal, there are certain characteristics of the PCM that need explaining. First, all internal registers appear on even and the following odd byte address. This is because address signal A0 is not used inside of the PCM. The order of the registers was also arranged so that they appear in the order that they would normally be programmed. This allows the PCM to be attached to the 80186 and string move operations used to allow the fastest possible handling of loading the PCM.

Finally, the registers associated with the operation of the PCM itself do not decode the signal A7 so that they appear in both halves of the register map, facilitating an easier modulization of the driving firmware. Only the even addresses of the registers will be shown. Refer to pages 10 through 35 for a summary of all the non-channel registers.

#### 3.1.1 RRC3 Through RRC0 Refresh Rate Count Field

The refresh rate count field indicates to the PCM the prescale count to use for determing the refresh rate of the dynamic RAMs. The value of the refresh rate count field is effectively multiplied by 32, then subtracted from 512 to determine the number of clocks that will occur between refresh cycles. The value of this field is dependent upon the frequency of the PCMs clock. The following table shows the relationship of clock frequency, and refresh rate count field values, to produce 15.6 microsecond refresh cycles (for standard 128 cycle 2 ms. dynamic RAMs).

| Field<br>Value | Cycle<br>Count | Freq. Range <sup>1</sup><br>Low High |      | Refresh li<br>Low I | ntrvl <sup>2</sup><br>High |

|----------------|----------------|--------------------------------------|------|---------------------|----------------------------|

| 12             | 128            | 8.2                                  | 10.2 | 15.6                | 12.5                       |

| 11             | 160            | 10.4                                 | 12.2 | 15.4                | 13.1                       |

| 10             | 192            | 12.4                                 | 14.2 | 15.5                | 13.5                       |

| 9              | 224            | 14.4                                 | 16.4 | 15.6                | 13.7                       |

| 8              | 256            | 16.6                                 | 18.4 | 15.4                | 13.9                       |

| 7              | 288            | 18.6                                 | 20.4 | 15.5                | 14.1                       |

| 6              | 320            | 20.6                                 | 22.4 | 15.5                | 14.3                       |

| 5              | 352            | 22.6                                 | 24.4 | 15.6                | 14.4                       |

<sup>2</sup> Refresh intervals are in µs.

NOTE:

The other field values are valid but are unlikely to be useful to the customer

## 3.1 OPTION REGISTER

| ddress = 6<br>Read/write r |      |      |      |      |      |      |      |

|----------------------------|------|------|------|------|------|------|------|

| 7                          | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| MPAR                       | CAW1 | CAW0 | SRAM | RRC3 | RRC2 | RRC1 | RRC0 |

The option register is a read/write only register to the firmware. The bits represent settings of options that must be selected to match the board design. There is the facility to read option switches and allow the firmware to ascertain the hardware configuration in user 'adjustable' implementations. This register should be the first written after a reset sequence, and should not be written to thereafter unless another reset sequence has occurred.

## 3.1.2 SRAM Static Ram Mode (bit 4)

The Static Ram Mode bit informs the PCM that the memory array is composed of static RAMs. When the bit is set, the PCM is in static RAM mode. This changes the signals that the PCM uses to access the memory array. Because of the multiplexed address bus of dynamic RAMs, it will be necessary for an external latch to be added to demultiplex the address lines. In addition, external address decoding will be necessary to expand the

RAM to the full addressable capability. To assist in this, two of the RAM control signals change when the static RAM bit is set. First, the RAS signal is used to control the external latch that is to demultiplex the address, when a valid row address is available on BA8 to BA0. RAS is intended to drive the clock input of a 74F373 type octal D-type latch, there is a direct analogy to the operation of dynamic RAMs at this point, with the exception that the row address latch is external to the memory devices. Secondly, static RAMs also have different read and write characteristics to dynamic RAMs. In dynamic mode, the W signal, signals the RAMs that a write cycle is about to occur, with the actual write action being generated by the falling edge of the CAS signal. This is known as early write mode. A read would occur if the CAS signal went active (low) with the W signal inactive (high). In static mode, the W and CAS signals change to support the separate WE and OE signals of static RAMs. In static mode, the CAS becomes the OE signal, still being active low but it will only occur on RAM read cycles, having the same shape and timing as for dynamic RAM cycles. The W signal becomes the WE signal, still being active low and only occuring in write cycles, but of a shape and timing similar to the CAS/OE signal. Finally, the arbitration logic no longer receives refresh requests as the static RAMs require no refresh, of course. At this stage it should be noted that the static RAM configuration is still liable to the row change overhead, when a row boundary is crossed during a burst of data cycles between the peripheral port FIFO and the memorv.

The PCM is initialized to a special state at power up to ensure that there is no activity on the RAM control pins. This feature is used in the "power start" of the dynamic RAMs, which need to be left for a minimum time after power up. Please refer to the "Reset Sequences" section of this document for a description.

## 3.1.3 CAW1, CAW0 Column Address Width Field (bits 6,5)

The column address width field informs the PCM the type of RAM array that it is dealing with. The PCM uses the field to control the address multiplexer to the RAMs, and to determine the page mode boundaries of the RAMs. When a new page is detected, then the PCM executes a new RAS cycle, RAS goes inactive to precharge the RAS signal and then RAS goes active to latch the new row address and establish access in the new RAM page.

This field has no affect if the SRAM bit (bit 4) is set. When the SRAM mode is in effect, the PCM is forced to the ten bit column address mode.

00 = 10-bit column address (1meg DRAM). Bits 19 - 10 are the output on BA9 - BA0 during RAS time. Bits 9 - 0 are the output on BA9 - BA0 during CAS time.

01 = 9-bit column address (256K DRAM). Bits 18 - 9 are the output on BA9 - BA0 during RAS time. Bits 8 - 0 are the output on BA8 - BA0 during CAS time.

10 = 8-bit column address (64K DRAM). Bits 17 - 8 are the output on BA9 - BA0 during RAS time. Bits 7 - 0 are the output on BA7 - BA0 during CAS time.

11 = 6-bit column address (16K DRAM). Bits 15 - 6 are the output on BA9 - BA0 during RAS time. Bits 5 - 0 are the output on BA5 - BA0 during CAS time.

## 3.1.4 MPAR = Memory Parity Enable (bit 7)

The parity enable bit informs the PCM that the memory array has a parity bit attached. When the bit is set, the PCM generates odd parity (the sum of all one bits including the parity bit will be an odd number) on memory writes, and checks parity on memory reads. If there is even parity on a memory read, the PCM will cause a parity error interrupt in the appropriate status register. When the bit is reset, the PCM will not generate parity on a write, or check parity on a read. The microprocessor firmware can use this bit to test the parity logic of the PCM, when there is parity memory. When the parity enable bit is reset, the RBP pin of the PCM will be at a logic one level during a write cycle.

## 3.2 OPTION REGISTER 2

| ead/write re<br>he option re |   | initialized to zer | ro by the PCN | l reset sequ | ence |       |       |

|------------------------------|---|--------------------|---------------|--------------|------|-------|-------|

| 7                            | 6 | 5                  | 4             | 3            | 2    | 1     | 0     |

| •                            | 0 | NOWAIT             | WAITE         | AHI          | INTE | BINTE | AINTE |

#### 3.2.1 AINTE A Channel Interrupt Enable

The A channel interrupt enable bit allows interrupts from the "A" peripheral channel to exit the PCM by way of the PINT pin. This allows the programmer the capability to selectively disable interrupts from this channel while still allowing PCM interrupts from the other PCM resources. This bit only affects the transmission of the channels interrupt to the PINT pin, and does not affect the operation of any of the channels interrupt enables, or interrupt status flags.

| 'A' CHANNEL  | 'B' CHANNEL  |                  | AHI<br>PRIORITY |

|--------------|--------------|------------------|-----------------|

| Non-pausible | Pausible     | $\mathbf{X}^{j}$ | A Channel       |

| Pausible     | Non-pausible | х                | B Channel       |

| Non-pausible | Non-pausible | 1                | A Channel       |

| Non-pausible | Non-pausible | 0                | B Channel       |

| Pausible     | Pausible     | 1                | A Channel       |

#### 3.2.2 BINTE B Channel Interrupt Enable

This bit performs the same function as AINTE, but for the "B" channel.

## 3.2.3 WAITE Wait Enable

This bit is the master enable for any PCM wait condition to exit the PCM by the RDY pin. This allows the programmer the capability to selectively disable the RDY pin from the PCM. This bit only affects the transmission of the wait to the RDY pin, and does not affect the operation of any of the PCM wait sequences, or status.

#### 3.2.4 NOWAT Non-waitable Microprocessor Interface (bit 5)

The "non-waitable" bit is used to distinguish to the PCM that the microprocessor or board design does not support the RDY function to extend bus cycles. This bit controls how the PCM performs accesses to the data buffer and programmed I/O to the peripheral ports. This bit is reset by the PCM reset sequence.

When this bit is a zero, the PCM is to be used in a board with multiple devices sharing the microprocessor ready signal. The internal "ready" status of the PCM is gated with the CS signal, so only when the PCM is selected does it drive RDY. When the microprocessor accesses the data buffer or the peripherals for programmed I/O, the PCM asserts RDY low to halt the bus cycle until it can perform the access. The PCM uses the leading edge of the data strobe to trigger the access, and if the firmware is writing data, then there is a specified time from the leading edge of the strobe that write data must become available within. When the access is complete, the PCM deasserts the RDY signal and allows the bus cycle to finish.

When this bit is a one, the PCM is used in a configuration with a microprocessor that does not support wait states, and the RDY signal is normally used as a status signal to a microprocessor's PIO input pin and polled by the firmware, or the internal status of the RDY pin is polled through the PCM task file register. In this configuration, the PCM does not gate the CS signal with the internal RDY status, so the RDY status is available continuously. The PCM uses the trailing edge of the strobe to trigger the access, and as such there is no timing requirement on the write data from leading edge of strobe.

## 3.3 MASTER STATUS REGISTER

| Address = 64<br>Read/write re |   |   |      |      |     |       |       |

|-------------------------------|---|---|------|------|-----|-------|-------|

| 7                             | 6 | 5 | 4    | 3    | 2   | 1     | 0     |

| DNR                           | 0 | 0 | PRNR | BANR | PPE | BINTR | AINTR |

#### 3.3.1 AINTR Channel A Interrupt Request Read Only Bit BINTR Channel B Interrupt Request Read Only Bit

Setting AINTR (BINTR) indicates that the channel detected a situation requiring microprocessor action. The normal use of the interrupt is that the channel has completed an operation. The interrupt bit does not indicate if the operation was completed successfully, or if it terminated because of an error. The channel interrupt bit for each channel resets when the microprocessor clears all the interrupting states in the particular channel status register. This bit represents the 'or' function of all the interrupt conditions in the channel.

## 3.3.2 **PPE Processor Parity Error**

The processor parity error bit is set when a buffer read operation from the microprocessor interface resulted in a parity error. The bit is reset by the writing a one to the PPE bit. Writing a zero to PPE does not affect this bit.

#### 3.3.3 BANR Buffer Access Not Ready Read Only Bit

The PCM "buffer access not ready" status bit is used to signal the microprocessor that the PCM is currently performing an access of the buffer and the registers that are associated with the buffer are not available. When the access is complete, this bit will be reset. See also the "DNR" bit in the master status register.

#### 3.3.4 PRNR Power Reset Not Ready (bit 4) Read Only Bit

The PCM "power reset not ready" status bit is used to signal the microprocessor that the PCM is currently performing a power on reset sequence, or a programmed reset sequence, and all registers in the PCM except this register are not available. When the reset sequence is complete, this bit will be reset. See also the "DNR" bit in the master status register.

#### 3.3.5 DNR Device Not Ready (Bit 7) Read Only Bit

The PCM "device not ready" status bit is used to signal the microprocessor that the PCM is currently performing a task that does not allow access to some resource in the PCM. The bit is essentially a logical 'or' of four conditions in the device that require multiple clock times to resolve themselves. The conditions are:

- the buffer manager reset sequence

- the microprocessor access of the buffer memory

- the microprocessor access of either of the peripheral ports for programmed I/O.

When the power is applied to the PCM, or firmware issues a soft reset, the bit sets indicating that all internal registers except this registerare inaccessable. This bit will then reset when the PCM has completed its reset sequence. The "PRNR" bit in the master status register will also reflect this condition.

When the microprocessor accesses either of the peripheral ports for programmed I/O, or the microprocessor accesses the data buffer, the "device not ready" will reflect the status of the RDY pin of the PCM. This feature allows the firmware to 'poll' the PCM during these accesses when the board design or the microprocessor does not support the RDY function in hardware. The three accesses that cause this bit go to true are all independent, and can be occuring simultaneously. Because of the 'or' mechanism the bit will be false only when all accesses have completed.

When the microprocessor interface does support the RDY function, then there is no need to check this bit after the PCM has completed its reset sequence. When this bit is set because of RDY, the microprocessor is still in a wait state while the specific access is performed, and when the microprocessor is released from the wait state, then this bit is known to be reset.

## 3.4 BUFFER DATA LATCH

| Address = 68<br>Read/write re |      |      |      |      |      |      |      |

|-------------------------------|------|------|------|------|------|------|------|

| 7                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| BDL7                          | BDL6 | BDL5 | BDL4 | BDL3 | BDL2 | BDL1 | BDL0 |

| BUL/                          | BDLO | BDL5 | BDL4 | BDL3 | BULZ |      |      |

The buffer data latch register holds the data last transferred between the microprocessor and buffer. The register is in the task file address space, so access of the register does not cause RDY to go false (no wait states). Access of the buffer data latch not cause the triggering of a buffer access. The register is used when the board or microprocessor does not support the RDY function in hardware. Refer to the buffer access register description for specific details of the interaction of this register and the Buffer Access Register. The register is also useful for diagnostic purposes to test the PCM internal data path between the microprocessor and the internal task file.

## 3.5 MICROPROCESSOR ADDRESS POINTER

|           |      | r    |       |      |      |         | [    |

|-----------|------|------|-------|------|------|---------|------|

| 7         | 6    | 5    | 4     | 3    | 2    | 1       | 0    |

| _         | 0    | 0    | 0     | MP19 | MP18 | MP17    | MP16 |

| 0         | 0    | 0    | 0     |      |      | 1411 17 |      |

| 0<br>MP15 | MP14 | MP13 | MPM12 | MP11 | MP10 | MP09    | MP08 |

#### MP19 through MP00 Microprocessor Address Pointer

The Microprocessor Address Pointer is a 20-bit register/counter that supplies the address lines to the buffer memory when the microprocessor is requesting a buffer data access. These registers

may be read or written when the "BANR" bit in the master status register is reset, to show or set the current RAM window. If the microprocessor accesses the buffer through the Autoincrement Access Register, then this pointer will increment after the access has been performed.

## 3.6 TEST ADDRESS AND STATUS REGISTER

| ad/write r | 8H or F8H<br>egister |      |      |      |      |      |      |

|------------|----------------------|------|------|------|------|------|------|

| 7          | 6                    | 5    | 4    | 3    | 2    | 1    | 0    |

| TAS7       | TAS6                 | TAS5 | TAS4 | TAS3 | TAS2 | TAS1 | TAS0 |

The Test Address and Status register is a window into the internal logic of the PCM to allow greater visibility of the internal functioning of the device, and therefor greater test comprehensiveness.

The PMC contains an address register that can be loaded when a microprocessor write to the Test Address and Status Register occurs. This allows the selection of several internal registers and counters, and state machine registers, and the subsequent display of their content by reading this location.

This location also interacts with the Reset and Test register to invoke the test functions. Specifically there is an interlock so that test mode is more difficult to invoke, and less prone to be enabled accidently. The sequence to enable test mode is to write 80H to this register when all the test bits in the Reset and Test register are zero. This must be followed with a write to the Reset and Test register with the selected test mode (the soft reset bit must be zero). Then write F0H to this register. Once this procedure has been executed, then write the test address to this location, and read this location to view the desired internal status. When test mode is invoked, the only way to restore normal operation is to issue a soft reset, or assert the RST pin.

## 3.7 RESET AND TEST REGISTER

| Address = 7AI<br>Write only reg |   |      |      |       |       |       |       |

|---------------------------------|---|------|------|-------|-------|-------|-------|

| 7                               | 6 | 5    | 4    | 3     | 2     | 1     | 0     |

| SWRST                           | 0 | BRST | ARST | TSMEM | CNTRT | MTPBF | MTPAF |

The Reset and test register allows a software reset of the PCM device. It is important that, during the normal operation, the value written to this register is 80H. This register is also used for setting test modes and a value in this register other than 80H causes the PCM to behave unpredictably to the user. The actions that occur when the register is written with 80H are identical to those that occur during power up, and the reset sequences that are described in the reset sequences section. This register is register is initialized to 00H when either the reset input pin (RST) is asserted, or the software reset function is invoked.

#### 3.7.1 MTPAF Microprocessor to Port A FIFO Test (bit 0)

The microprocessor to port A FIFO test is used to verify the integrity of the internal data paths from/to the port FIFO, and to allow testing of the FIFO data cells. When this bit is set, the memory controller sets the data path from the memory side of the port FIFO to the buffer access register in the microprocessor section. The port should be in loopback mode, and when the microprocessor writes or reads the buffer access register the data will be transferred from/to the port FIFO instead of the external memory. Specifically, if the port has the DIR bit set so that data is to go from memory to the peripheral, then the microprocessor would write to the buffer access register, and the data would be read back from the FIFO through the channel data latch in loop back mode. The reverse direction has the microprocessor writing to the channel data latch, and reading the resultant data in the buffer access register.

#### 3.7.2 MTPBF Microprocessor to Port B FIFO Test (bit 1)

This is identical to bit 0 but uses the B channel.

## 3.7.3 CNTRT Counter Test Mode (bit 2)

When this bit is set, the 16 and 20 bit counters will be divided along 4 bit boundaries, and the carry input to these boundaries will be forced true. The example is of the Buffer Address Pointer, if it is initially set to 12345H, when an access through the autoincrement access register is made, the counter will contain as its next value 23456H. The counters affected by this bit are:

- port A address pointer

- port A transfer counter

- port A EDAC idle counter

- port B address pointer

- · port B transfer counter

- port B EDAC idle counter

- buffer address pointer

- refresh address counter.

# 3.7.4 TSMEM Tristate Memory Interface (bit 3)

When this bit is set the control signals to the memory interface are forced to a tristate mode, to allow testing of the memory devices by an external test machine.

## 3.7.5 ARST A Channel Reset (bit 4)

When written with a one causes the 'A' Channel to receive a reset. This reset does not affect the memory controller, or the other peripheral channel. The reset is removed when a zero is written into the bit, or a PCM reset sequence is initiated. When a channel is receiving a reset it will have its PNRA bit in its Channel Status Register set.

## 3.7.6 BRST B Channel Reset (bit 5)

This is identical to bit 4 but resets the 'B' Channel.

## 3.7.7 SWRST Software Reset (bit 7)

When written with a one causes initiation of the PCM reset sequence. This bit is self resetting when the PCM completes the reset sequence (denoted by the PRNR bit in the master status register being cleared), and initiates the PCM reset sequence on the trailing edge of the write strobe of this register.

#### 3.8 BUFFER ACCESS REGISTER

| ead/write r | egister |      |      |      |      |      |      |

|-------------|---------|------|------|------|------|------|------|

| 7           | 6       | 5    | 4    | 3    | 2    | 1    | 0    |

| BAR7        | BAR6    | BAR5 | BAR4 | BAR3 | BAR2 | BAR1 | BAR0 |

The Buffer Access Register is the window that the microprocessor uses to load/store data to/from the buffer memory. The microprocessor address pointer supplies the address to/from which the RAM transfer will be made.

When the microprocessor and board design support the RDY function in hardware, (the NOWAT bit is zero), then this register passes the data through to/from the microprocessor and buffer. The leading edge of the microprocessors read or write strobe causes a "not ready" signal to the microprocessor, holding this state until memory arbitration and the actual data transfer has been accomplished. When the transfer is complete by RDY going true, then the cycle will end and the task is complete. There is no need of the buffer data latch when using the PCM in this mode.

In the case where the RDY function is not supported in the hardware, (the NOWAT bit is one), then the firmware must perform a program sequence to complete a transfer. If the microprocessor is writing data to the buffer, then it will write to this register and data will be latched along with the fact it is a write. The trailing edge of the strobe will cause the PCM to request arbitration for the buffer. The firmware is free at this time to perform other tasks, or poll the "DNR" status bit or the "BANR" in the Master Status Register, or poll the PCM RDY pin. When the access is complete then "not ready" will go false, and the firmware is again allowed to access the buffer.

If the microprocessor desires to read the buffer, then it must first read this register and discard the data. This action is only used to initiate the arbiter request, and latch the fact it is a read access. The trailing edge of the strobe will cause the buffer access to initiate. When the "not ready" condition goes false, then the data that was fetched is available in this register, and also in the Buffer Data Latch. Note that reading the Buffer Data Latch does not cause a "not ready" condition, or perform another access of the buffer, where if data is read from this register then another access will be initiated.

#### 3.9 AUTOINCREMENT ACCESS REGISTER

| ad/write r | egister |      |      |      |      |      |      |

|------------|---------|------|------|------|------|------|------|

| 7          | 6       | 5    | 4    | 3    | 2    | 1    | 0    |

| BAR7       | BAR6    | BAR5 | BAR4 | BAR3 | BAR2 | BAR1 | BAR0 |

The autoincrement data register performs the identical function of the buffer access register with the added feature that at the end of the data transaction, the microprocessor address pointer increments to the next address.

If the firmware desires to read or write a small block of data in the buffer, then access through this register will simplify the programming sequence. When the PCM is in the "waitable" microprocessor mode, then firmware need only continuously read or write data through this register. The transfer of data to/from the buffer occurs while the microprocessor is in a wait state. and the incrementing of the Microprocessor Address Pointer occurs in the intervening time between consecutive microprocessor bus cycles. If the PCM is in the "non-waitable" microprocessor mode, then firmware must poll the "not ready" status between accesses of this register. In this mode when reading a string of bytes from the buffer, if the last byte is accessed from this register, then another buffer access will occur, and the address pointer will be incremented. If this is not desired, then the last byte read from the buffer should be read from the buffer data latch instead of from this register.

The autoincrement access register is intended for use when small blocks of data are to be moved to/from the buffer while both ports are transferring data. If a large amount of data is to be moved to/from the microprocessor it is suggested that one of the ports be used in loopback mode, to achieve the maximum data transfer rate.

# 4.0 DEVICE CHANNELS

|      | ddress = C0l<br>egister - not p |      |      |      |     |     |     |

|------|---------------------------------|------|------|------|-----|-----|-----|

| 7    | 6                               | 5    | 4    | 3    | 2   | 1   | 0   |

| LPBM | PPE                             | DKPI | ROPL | SDTC | DLY | SC1 | SC0 |

**NOTE** There is an A or B appended to each bit name corresponding to the appropriate channel.

There are two device channels that the PCM controls. The channel registers are independent and identical across the two channels. Within the PCM the channels appear as 64-byte memory spaces in the chips total address space of 256 bytes. The channels are referred to as A, and B, with channel A being the 64 bytes of address space from 00H to 3FH, channel B being the 64 bytes of address space from 80H to BFH. Because the devices attached to the channels get their address lines (if necessary) directly from the microprocessor bus the even only address characteristic of the internal registers does not apply.

The registers that control the channels, are in the 32 bytes of address space that immediately follow the respective channels address space. The registers for channel A are in the address space of 40H to 5FH. The registers for channel B are in the address space of C0H to DFH. As these registers are internal, the odd addresses in the channel's respective address blocks are just a ghost image of the registers at the even addresses.

When the controller firmware accesses a register that controls a channel, the microprocessor will not have to wait for access, because these registers are all within the PCM chip, and are always available for immediate access. When the controller firmware accesses a register in a device on a channel, the PCM must evaluate the state and mode of the channel to determine if access of the register is possible. If the PCM is the bus master, then it will arbitrate the access of the channel, and will insert wait states for the microprocessor. The number of wait states for this access is dependent upon both the strobe timing of the channel, and the arbitration time of the channel. If the PCM is in slave mode it will not attempt the access but cause an I/O error interrupt and status to occur.

The channels function is to allow access between a peripheral device and the data buffer. The characteristics of any transfer have both fixed and variable components. The fixed components are associated with the peripheral device and the hardware that will perform the transfer. These components are set at the beginning of the total transfer, and do not vary for the duration of the transfer. The variable components of the transfer are associated with the data buffer itself, and the arrangement of data, and the firmware control of the data. The fixed components are not 'pipelined', and are set by firmware at the start of a (group of) transfer(s).

The channel 'pipeline' mechanism allows firmware to control the data buffer on the fly. In applications where the firmware is attempting to either control a ring buffer or a cache, the mechanism allows the firmware to 'look ahead' to its next operation.

The registers have been organized in the order in which they would normally be programmed. It is especially important to ensure that the timing register is set up before the control register.

## 4.1 CHANNEL TIMING REGISTER

The channel timing register is used to control hardware actions that occur during a transfer to the external device. The action the register performs is that of controlling the pulse timing on the channel when the PCM is the bus master. This allows peripheral devices of various timing characteristics to be interfaced to the PCM. The register also defines to the channel logic specific characteristics of the external peripheral device, such as its handshake signal polarities, and parity capability. The firmware is only allowed to write to the channel timing register when the channel is idle. The channel state machine will set the I/O error bit in the channel interrupt status register if the channel timing register is written while the channel is busy.

All bits in the register are cleared by the reset sequence.

#### 4.1.1 SC0(1)A (SC0(1)B) Channel Strobe Control Field

The channel strobe control field is a two bit field that is used to control the width of the read and write strobes to the peripheral devices when the channel is in modes where the PCM is the bus master (DMA), or when doing PIO operations. The width of the strobes is programmable by setting the field. When the PCM is doing DMA cycles, for values of 0,1,2,3 the strobes will be 2,4,6,8 clocks wide respectively. When the PCM is doing PIO cycles, for values of 0,1,2,3 the strobes will be 4,6,8,10 clocks wide respectively.

## 4.1.2 DLYA (DLYB) Delay Strobe Bit

Normally, the  $\overline{CS}$  and  $\underline{DACK}$  signals go active two PCM clock before the RD or WR signals. When this bit is set, this period is extended by 2 PCM clocks. The primary use of this feature is for external decoding logic if multiple peripheral devices exist on the channel.

#### 4.1.3 SDTCA (SDTCB) Strobe Deasserted Time Control Bit

This bit is relevant when the PCM is the bus master and in burst data transfer mode, then this bit is used to control the time that the RD and WR signals are deasserted. When this bit is zero, the RD and WR strobes will be deasserted for two PCM clocks during a data burst. When this bit is one, the RD and WR signals will be deasserted for 4 PCM clocks during a data burst.

#### 4.1.4 RQPLA (RQPLB) DMA Request Polarity Bit

This bit controls the polarity of the PCM port DRQ pin. When this bit is set the PCM will consider the DRQ pin as active high. This is true whether this pin is receiving the request when the PCM is bus master or transmitting the request when the PCM is bus slave.

#### 4.1.5 DKPLA (DKPLB) DMA Acknowledge Polarity Bit

This bit controls the polarity of the PCM port DACK pin. When this bit is set, the PCM will consider the DACK pin as active high. This is true whether this pin is transmitting the acknowledge when the PCM is bus master or receiving the acknowledge when the PCM is bus slave. Note that both the above situations occur when EDAC redundancy byte counting is enabled.

## 4.1.6 PPEA (PPEB) Port Parity Enable Bit

The device port can be optionally set to check the parity on transfers to the PCM from the peripheral device. Odd parity is supported and is generated when this bit is set. When this bit is set, all reads (data going into PCM) of the device channel by the PCM (either as master or slave) will result in parity checking being done, and interrupts being generated if even parity is detected. It should be noted that **ALL** transfers, including programmed I/O, are checked if this bit is set. When the PPE bit is reset, the port parity bit will be at a logic one level when data is transferring from the PCM to the peripheral device.

#### 4.1.7 LPBMA (LPBMB) Loop Back Mode Enable

The purpose of this bit is to enable the microprocessor to use the FIFO to speed block transfers between the microprocessor and the buffer RAM. When set, this bit paths the channel data latch to the FIFO. It inactivates the outputs of the channel (CS, DACK, DRQ, WR, RD, and data bus). The microprocessor will appear to the channel as an external device and the channel will appear as if in slave mode. More explicitly the loopback mode sets the channel to a state of a non-pausible slave mode. In this state the microprocessor can transfer data to/from the FIFO at its maximum speed with the channel monitoring the FIFO for overrun/underrun conditions. The channel mode bits in the Channel Control Register need not be changed, but the Direction, and Interrupt Enable bits need to be programmed as if programming for an external transfer. In all other channel registers programming is as if for a normal external transfer, with the normal pipeline mechanisms in operation. Note the Direction bit in the Channel Control Register still needs to reflect the direction of transfer to/from an external device. As such the direction bit is SET for a transfer from the buffer to microprocessor (similar to a peripheral write command), though the microprocessor issues READ cycles to access the FIFO data.

## 4.2 CHANNEL CONTROL REGISTER

|   | Address = C2H<br>register - not p |   |   |   |   |   |   |

|---|-----------------------------------|---|---|---|---|---|---|

|   |                                   |   |   | • |   |   |   |

| 7 | 6                                 | 5 | 4 | 3 | 2 | 1 | 0 |

NOTE. There is an A or B appended to to each bit name corresponding to the appropriate channel

Where the Timing Control Register sets the physical environment of the interface with the external device, the Channel Control Register sets the logical environment of the interface. The register contains two types of parameters about the transfer being programmed. The high order five bits are used to identify the logical protocol that the PCM is going to use to interface to the external device. The low three bits are used to set a firmware environment to control the manbagement of the transfer direction and interrupts desired.

The firmware is only allowed to write to the channel control register when the channel is idle. The channel state machine will set the I/O error bit in the channel interrupt status register if the channel control register is written while the channel is busy.

Whenever the firmware writes to the channel control register, the PCM will take 10 PCM clocks to synchronize the action to the PCM clock, and advance the channels status. During this time the firmware can only access non-channel registers.

The register is initalized to A8H by the rest sequence.

## 4.2.1 IBEA (IBEB) Interrupt on Busy Bit

The busy interrupt bit indicates to the channel that the microprocessor desires an interrupt when the channel very busy status bit transitions from a one to a zero.

#### 4.2.2 DIRA (DIRB) Channel Transfer Direction Bit

The channel transfer direction bit is used to inform the PCM the direction of the transfer of this channel. The PCM uses this information to determine the read/write control of the buffer. When the transfer direction bit is a zero, the device is transferring data to the buffer (device read mode, buffer write mode). When the transfer direction bit is a one, the device is transferring data from the buffer (device write mode, buffer read mode).

The transfer direction bit is used by the channel logic to position the transfer counter, and the input of the FIFO to the source of the data. When the direction bit is a zero, (data transfer from the peripheral to the buffer), the transfer counter is monitoring the device handshake signals, and the count reflects the number of bytes that remain to be transferred from the peripheral device, to the input of the FIFO. When the transfer count exhausts and the FIFO goes empty, the logic will signal the end of this transfer if EDAC mode is not in effect. If EDAC mode is in effect, the channel will monitor the DACK pin to count EDAC trans fers, and when the EDAC idle counter exhausts and the FIFO is empty, it will signal the end of this transfer.

When the direction bit is a one, (data transfer from the buffer to the peripheral), the transfer counter is monitoring the buffer signals, and the count reflects the number of bytes that remain to be transferred from the buffer to the input of the

FIFO. When the transfer count exhausts and the FIFO goes empty, the logic will signal the end of this transfer if EDAC mode is not in effect. If EDAC mode is in effect when the FIFO goes empty, the channel will monitor the DACK pin to count EDAC transfers, and when the EDAC idle counter exhausts it will signal the end of this transfer.

#### 4.2.3 PAUSA (PAUSB) Channel Pause Control Bit (bit 3)

The bit is used by the memory arbiter. When this port is pausible (this bit set), and the other port is non-pausible (this bit reset), then the other port will have higher priority in the memory arbiter. If this bit is set the same in both channel control registers, then priority is determined by the "AHI" bit in the option 2 register.

This bit enables the "urgent request" logic. Because it controls priority, if the highest priority port's FIFO is near to overrun/underrun condition, then an "urgent request" is sent to the arbiter to stop the other port's burst and force arbitration.

# 4.2.4 EDACA (EDACB) EDAC Idle Enable (bit 4)

The EDAC Idle Enable bit is used to allow the port interface to share control of the peripheral bus with the WD60C80 EDAC device. The EDAC (Error Detection And Correction) is used in disk applications to append redundancy information to data blocks to allow error correction. The bit when set will allow the PCM to strip this information and not transfer it to the buffer on reads, and to allow the EDAC to append the information to the device data on writes. The EDAC bit is only relevant when the channel is programmed to be a bus master. The Channel EDAC Idle Counter contains a count of the number of redundancy bytes to ignore between data transfers. When this bit is set the transfer counter must be programmed for a single block size. When the transfer count exhausts the channel will tristate the DACK pin and begin to count DACK pulses until the EDAC idle counter exhausts. While the EDAC idle counter is enabled, no transfers are allowed between the port and the FIFO (the redundancy bytes transfer between peripheral and the EDAC device). When the EDAC idle count exhausts the channel will then continue normal pipeline operations if the firmware has programmed them.

#### 4.2.5 DISKA (DISKB) Disk Type Device (bit 5); BRSTA (BRSTB) Burst Transfer Device (bit 6); SLAVA (SLAVB) Slave Mode Interface (bit 7)

These three bits are used collectively to define to the port logic the type of peripheral device it will interface with, and the protocol to use with the interface signals. The signals will be described as per their individual significance, and then their collective significance. The names are derived from relationships they assume when the bit is set.

The SLAVE bit is used to instruct the channel that the external device is the bus master, and as such will control the WR and RD interface signals. When the bit is zero, the PCM is the bus master and controls the  $\overline{WR}$  and  $\overline{RD}$  signals. The master/slave relationship controls whether the PCM has the capability of performing programmed I/O on the external bus. When the microprocessor attempts to do programmed I/O and the channel is in a master and non-disk mode, the channel will arbitrate the external bus and interleave the programmed I/O with the DMA transfers the external device is requesting. When the channel is in slave mode, programmed I/O is rejected. If the microprocessor attempts programmed I/O an I/O error interrupt and status are asserted.