2 4

WD33C93B

Enhanced SCSI Bus

Interface Controller

# 24

# **TABLE OF CONTENTS**

| 1.0 IN<br>1<br>1<br>1 | 2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 P                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.0 W                 | D33C93B REGISTERS       24-6         1 Register Descriptions       24-7         3.1.1 Auxiliary Status Register       24-7         3.1.2 Address Register       24-7         3.1.3 Own ID/CDB Size Register       24-8         3.1.4 Control Register       24-8         3.1.5 Timeout Period Register       24-10         3.1.6 Command Descriptor Block Registers       24-10         3.1.7 Total Sectors Register       24-11         3.1.8 Total Heads Register       24-11         3.1.10 Logical Address Register       24-11         3.1.11 Sector Number Register       24-11         3.1.12 Head Number Register       24-11         3.1.13 Cylinder Number Register       24-11         3.1.14 Target LUN Register       24-11         3.1.15 Command Phase Register       24-12         3.1.16 Synchronous Transfer Register       24-12         3.1.17 Transfer Count Register       24-12         3.1.18 Destination ID Register       24-13         3.1.19 Source ID Register       24-14         3.1.20 SCSI Status Register       24-15         3.1.21 Command Register       24-19 |

| 3.                    | 3.1.22       Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.0     | COM    | MANDS     |                                           | 4-22         |

|---------|--------|-----------|-------------------------------------------|--------------|

|         | 4.1    | Commar    | nd List                                   | 4-22         |

|         | 4.2    | 33C93B    | Command Types                             | 4-23         |

|         | 4.3    | 33C93B    | Specific Features                         | 4-23         |

|         |        | 4.3.1     | Advanced Mode Features                    | 4-23         |

|         | 4.4    | Level I C | Commands                                  | 4-24         |

|         |        | 4.4.1     | Reset (00 hex)                            | 4-24         |

|         |        | 4.4.2     | Abort (01 hex)                            | 4-25         |

|         |        | 4.4.3     | Disconnect (04 hex)                       | 4-25         |

|         |        | 4.4.4     | Assert ATN (02 hex)                       | 4-25         |

|         |        | 4.4.5     | Negate ACK (03 hex)                       |              |

|         |        | 4.4.6     | Set IDI (0F hex)                          |              |

|         | 4.5    | Simple L  | evel II Commands                          |              |

|         |        | 4.5.1     | Select-with-ATN (06 hex)                  |              |

|         |        | 4.5.2     | Select-without-ATN (07 hex)               |              |

|         |        | 4.5.3     | Reselect (05 hex)                         |              |

|         |        | 4.5.4     | Receive (10-13 hex)                       |              |

|         |        | 4.5.5     | Send (14-17 hex)                          |              |

|         |        | 4.5.6     | Transfer Info (20 hex)                    |              |

|         |        | 4.5.7     | Translate Address (18 hex)                |              |

|         | 4.6    | Combina   | ation Level II Commands                   |              |

|         |        | 4.6.1     | Select-and-Transfer (08 and 09 hex)       |              |

|         |        | 4.6.2     | Reselect-and-Transfer (0A and 0B hex)     |              |

|         |        | 4.6.3     | Wait-for-Select-and-Receive (0C hex)      |              |

|         |        | 4.6.4     | Send-Status-and-Command-Complete (0D hex) |              |

|         |        | 4.6.5     | Send-Disconnect-Message (0E hex)          |              |

| <b></b> | EL E0: | TDICAL (  | ·                                         |              |

| 5.0     | ELEC   | IRICAL    | CHARACTERISTICS                           | +-4 I        |

| 6.0     | TIMIN  |           | ACTERISTICS                               |              |

|         | 6.1    | Processo  | or/DMA Interface                          | <b>1-44</b>  |

|         |        | 6.1.1     | CLK                                       | 1-44         |

|         |        | 6.1.2     | MR                                        | 1-44         |

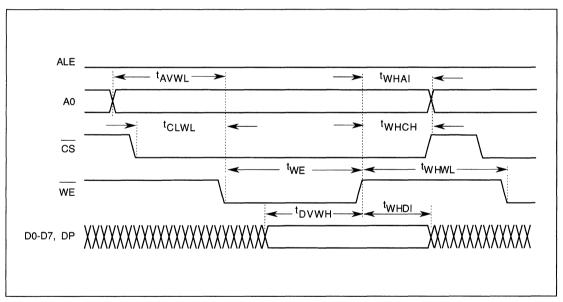

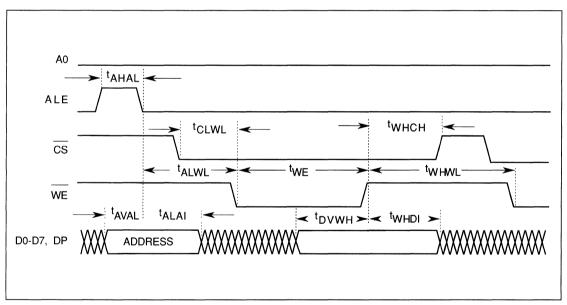

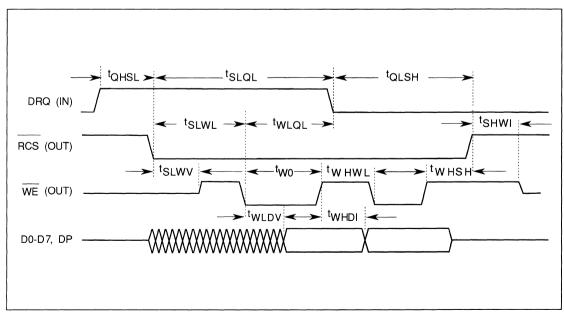

|         |        | 6.1.3     | Processor Write (Indirect Addressing)     | 4-45         |

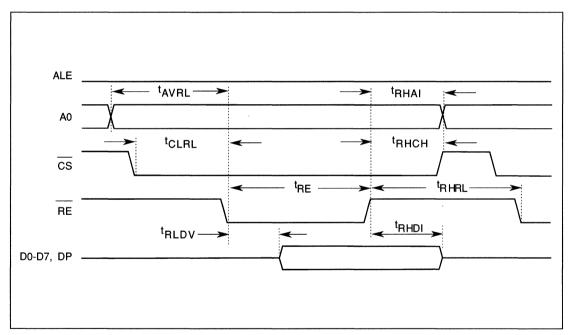

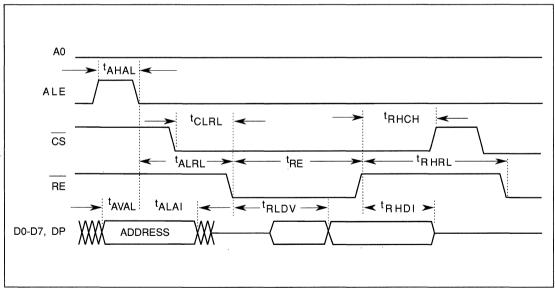

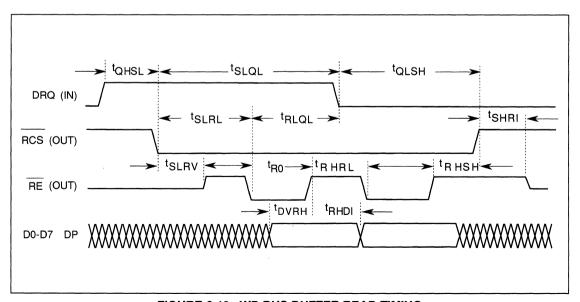

|         |        | 6.1.4     | Processor Read (Indirect Addressing)      | <b>4-46</b>  |

|         |        | 6.1.5     | Processor Write (Direct Addressing)       | <b>1-4</b> 7 |

|         |        | 6.1.6     | Processor Read (Direct Addressing)        | <b>4-48</b>  |

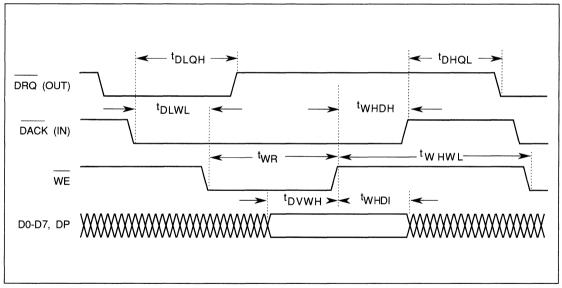

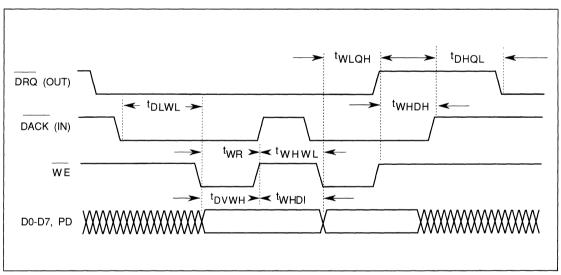

|         |        | 6.1.7     | DMA Write                                 | 4-49         |

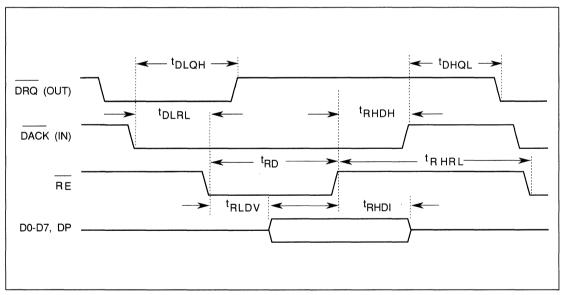

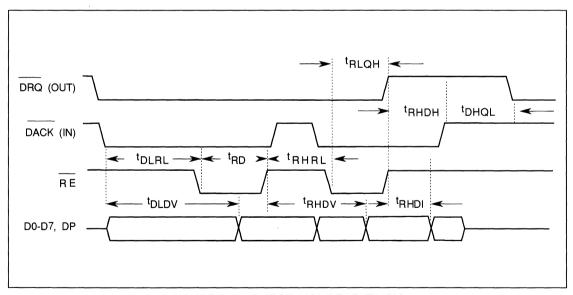

|         |        | 6.1.8     | DMA Read                                  | 4-50         |

|         |        | 6.1.9     | WD-BUS Buffer Write                       | 4-51         |

|         |        | 6.1.10    | WD-BUS Buffer Read                        | 4-52         |

|         |        | 6.1.11    | Burst DMA Write                           | 4-53         |

|         |        | 6.1.12    | Burst DMA Read                            |              |

|         |        | 6.1.13    | INTRQ                                     | 4-55         |

**//**

| 6.2 | SCSI In | nterface                                                                 |

|-----|---------|--------------------------------------------------------------------------|

|     | 6.2.1   | Arbitration                                                              |

|     | 6.2.2   | Selecting A Target (As An Initiator)                                     |

|     | 6.2.3   | Response To Selection (As A Target)                                      |

|     | 6.2.4   | Reselecting An Initiator (As A Target)                                   |

|     | 6.2.5   | Response To Reselection (As An Initiator)                                |

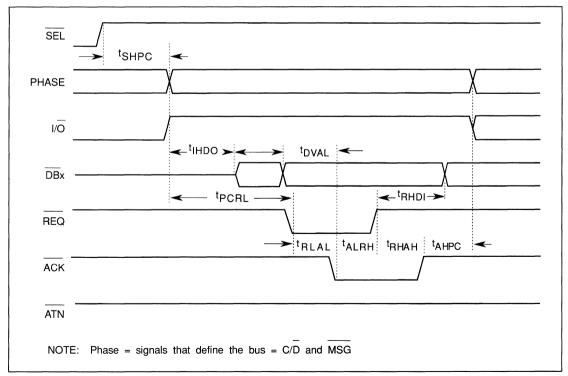

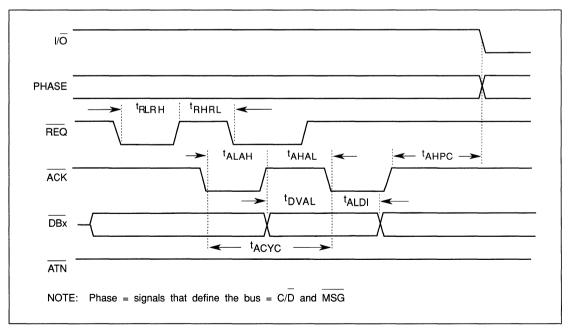

|     | 6.2.6   | Receive Asynchronous Information Transfer In                             |

|     |         | (Acting As An Initiator)                                                 |

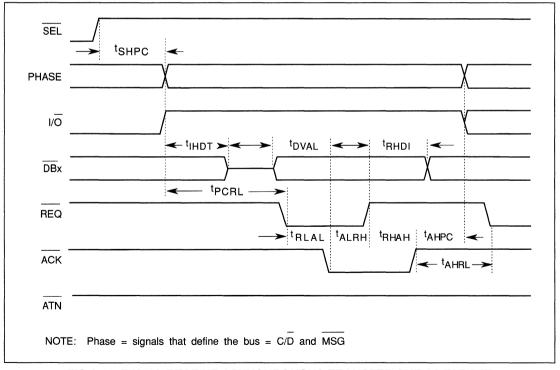

|     | 6.2.7   | Send Asynchronous Information Transfer In (Acting As A Target) . 24-62   |

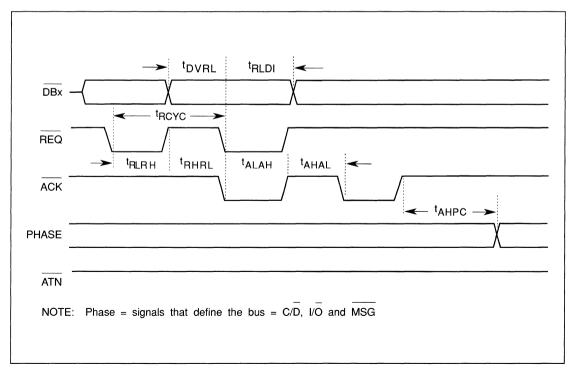

|     | 6.2.8   | Send Asynchronous Information Transfer Out                               |

|     |         | (Acting As An Initiator)                                                 |

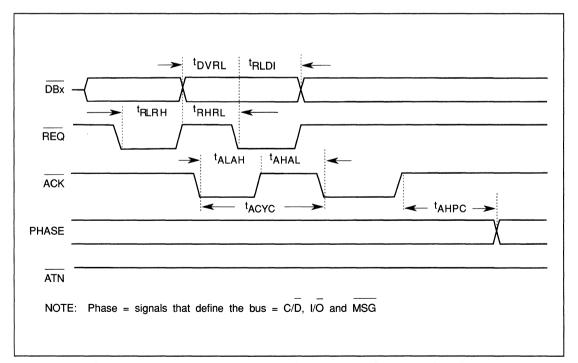

|     | 6.2.9   | Receive Asynchronous Information Transfer Out (Acting As A Target) 24-64 |

|     | 6.2.10  | Receive Synchronous Information Transfer In (5 and 10 Mb/s)              |

|     |         | (Acting As An Initiator)                                                 |

|     | 6.2.11  | Send Synchronous Information Transfer In (5 Mb/s)                        |

|     |         | (Acting As A Target)                                                     |

|     | 6.2.12  | Send Synchronous Information Transfer In (10 Mb/s)                       |

|     |         | (Acting As A Target)                                                     |

|     | 6.2.13  | Send Synchronous Information Transfer Out (5 Mb/s)                       |

|     |         | (Acting As An Initiator)                                                 |

|     | 6.2.14  | Send Synchronous Information Transfer Out (10 Mb/s)                      |

|     |         | (Acting As An Initiator)                                                 |

|     | 6.2.15  | Receive Synchronous Information Transfer Out (5 and 10 Mb/s)             |

|     |         | (Acting As A Target)                                                     |

|     | 6.2.16  | Arbitration To Bus Free                                                  |

|     | 6.2.17  | Selection (As An Initiator) Or Reselection (As A Target)                 |

|     |         | To Bus Free (Selection Timeout)                                          |

|     | 6.2.18  | Connected-As-An-Initiator To Bus Free                                    |

|     | 6219    | Connected-As-A-Target To Bus Free 24-74                                  |

# **LIST OF TABLES**

| Table | Title                                     | Page   |

|-------|-------------------------------------------|--------|

| 2-1   | Signal Descriptions                       | . 24-3 |

| 3-1   | Register Map                              | . 24-6 |

| 3-2   | Reset State Interrupts                    | 24-16  |

| 3-3   | Successful Completion Interrupts          | 24-16  |

| 3-4   | Paused or Aborted Interrupts              | 24-17  |

| 3-5   | Terminated Interrupts                     | 24-18  |

| 3-6   | Service Required Interrupts               | 24-19  |

| 4-1   | Command List                              | 24-22  |

| 4-2   | Select-and-Transfer Commands              | 24-32  |

| 4-3   | Select-and-Transfer Commands              | 24-33  |

| 4-4   | Reselect-and-Transfer Commands            | 24-35  |

| 4-5   | Reselect-and-Transfer Commands            | 24-35  |

| 4-6   | Wait-For-Select-and-Receive Commands      | 24-37  |

| 4-7   | Wait-For-Select-and-Receive Commands      | 24-38  |

| 4-8   | Send-Status-and-Command-Complete Commands | 24-39  |

| 4-9   | Send-Status-and-Command-Complete Commands | 24-39  |

| 4-10  | Send-to-Disconnect-Message Commands       | 24-40  |

# LIST OF ILLUSTRATIONS

| Figure | Title                                               | Page  |

|--------|-----------------------------------------------------|-------|

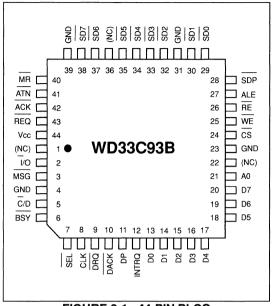

| 2-1    | 44-Pin PLCC                                         | 24-3  |

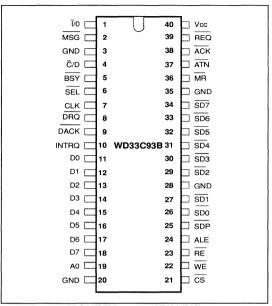

| 2-2    | 40-Pin DIP                                          | 24-3  |

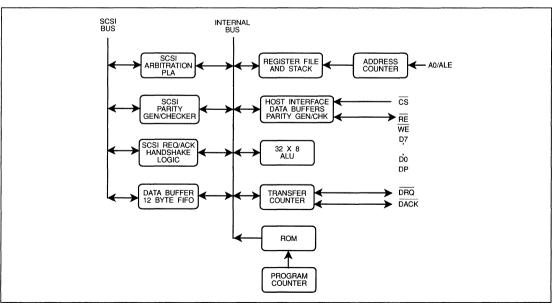

| 2-3    | WD33C93B Block Diagram                              | 24-5  |

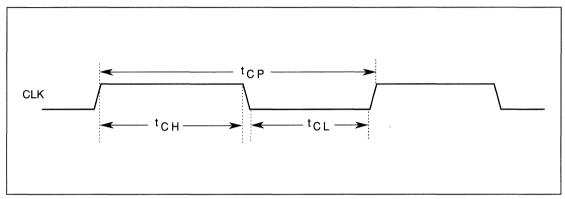

| 6-1    | Clock Timing                                        | 24-44 |

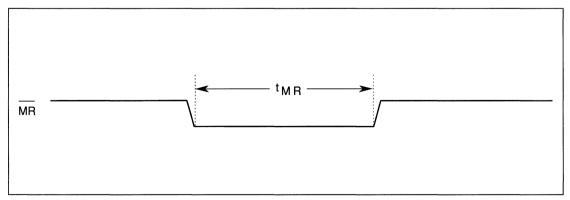

| 6-2    | MR Timing                                           | 24-44 |

| 6-3    | Processor Write Timing                              | 24-45 |

| 6-4    | Processor Read Timing                               | 24-46 |

| 6-5    | Processor Write (Direct) Timing                     | 24-47 |

| 6-6    | Processor Read (Direct) Timing                      | 24-48 |

| 6-7    | DMA Write Timing                                    | 24-49 |

| 6-8    | DMA Read Timing                                     | 24-50 |

| 6-9    | WD Bus Buffer Write Timing                          | 24-51 |

| 6-10   | WD Bus Buffer Read Timing                           | 24-52 |

| 6-11   | Burst DMA Write Timing                              | 24-53 |

| 6-12   | Burst DMA Read Timing                               | 24-54 |

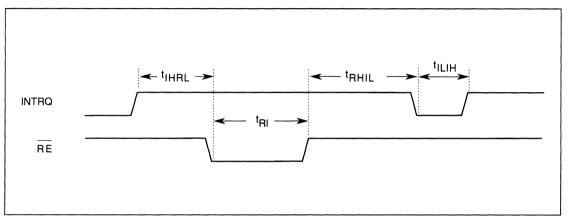

| 6-13   | INTRQ Timing                                        | 24-55 |

| 6-14   | Arbitration Timing                                  | 24-56 |

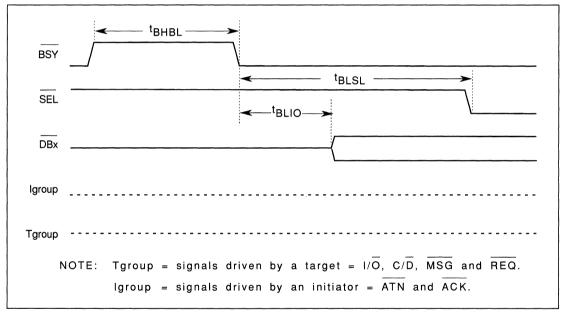

| 6-15   | Timing-Initiator Selecting a Target                 | 24-57 |

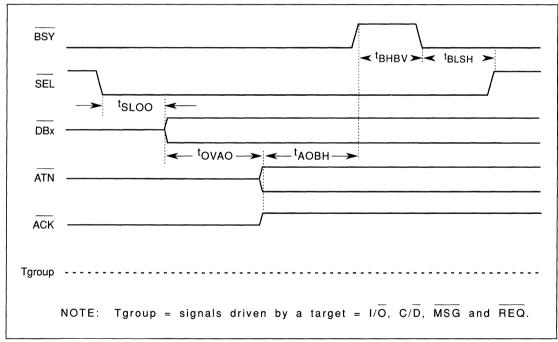

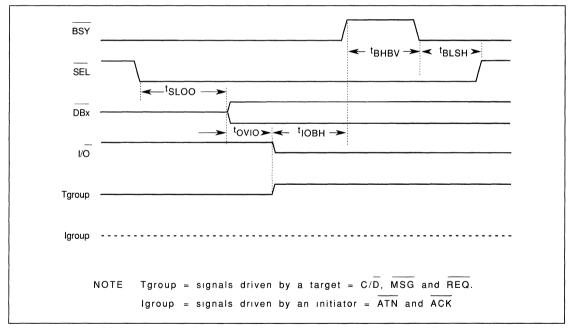

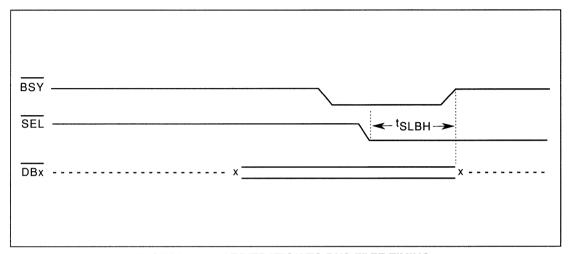

| 6-16   | Timing Target Response                              | 24-58 |

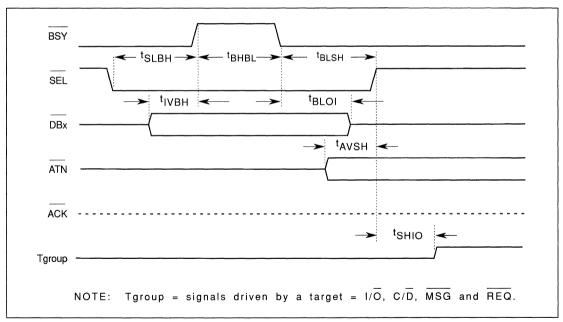

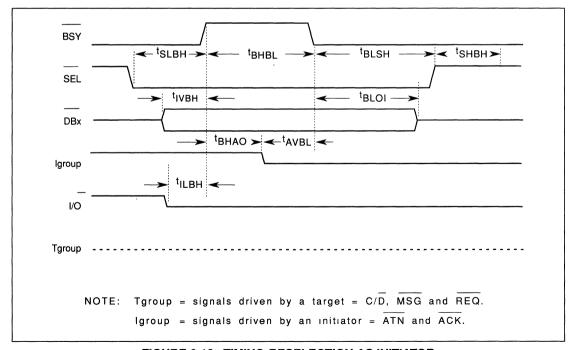

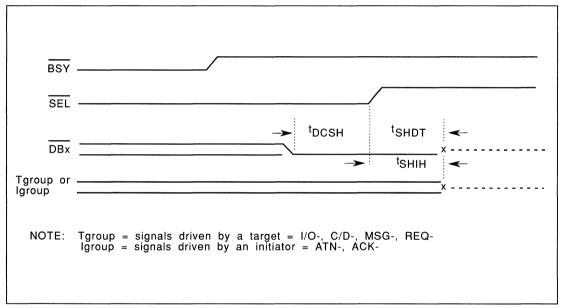

| 6-17   | Timing Reselecting a Target                         | 24-59 |

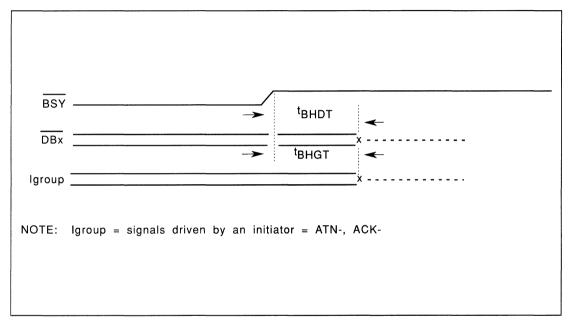

| 6-18   | Timing Reselection as Initiator                     | 24-60 |

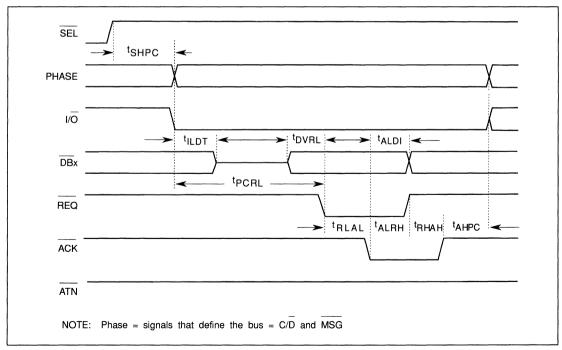

| 6-19   | Timing-Asynchronous Transfer In An Initiator        | 24-61 |

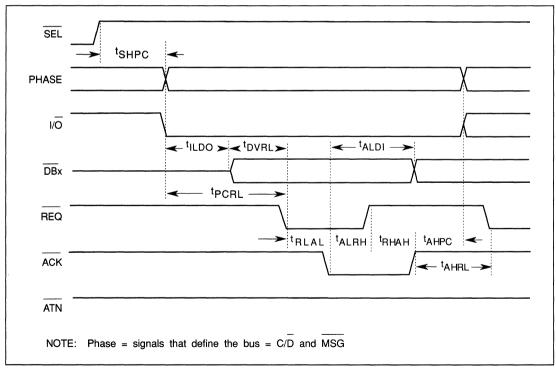

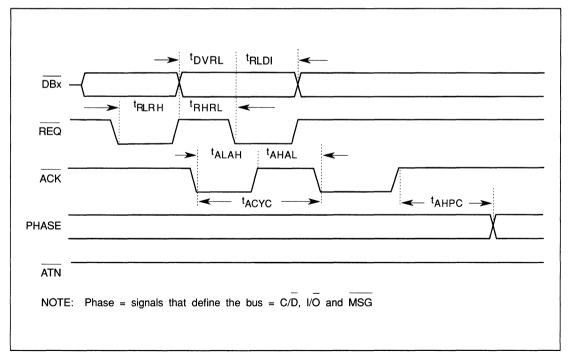

| 6-20   | Timing-Asynchronous Transfer In As Target           | 24-62 |

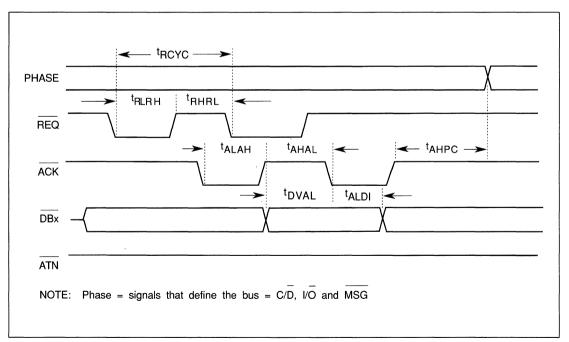

| 6-21   | Timing-Asynchronous Transfer Out As Initiator       | 24-63 |

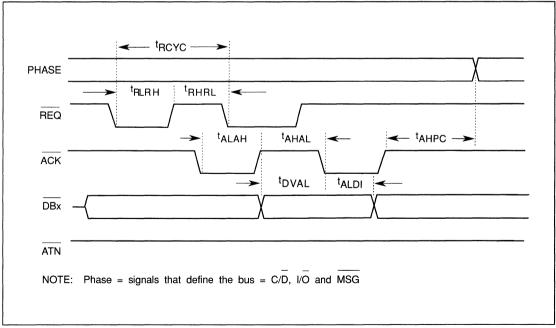

| 6-22   | Timing-Receive Asynchronous Transfer Out As Target  | 24-64 |

| 6-23   | Timing-Receive Synchronous Transfer In As Initiator | 24-65 |

| 6-24   | Timing-Send Synchronous Transfer In As Target       | 24-66 |

| 6-25   | Timing-Send Synchronous Transfer In As Target       | 24-67 |

| 6-26   | Timing-Send Synchronous Transfer Out As Initiator   | 24-68 |

| 6-27   | Timing-Send Synchronous Transfer Out As Initiator   | 24-69 |

| 6-28   | Timing-Receive Synchronous Transfer Out As Target   | 24-70 |

| 6-29   | Arbitration to Bus Free Timing                      | 24-71 |

| 6-30   | Timing-Selection to Bus Free                        | 24-72 |

| 6-31   | Timing-Initiator to Bus Free                        | 24-73 |

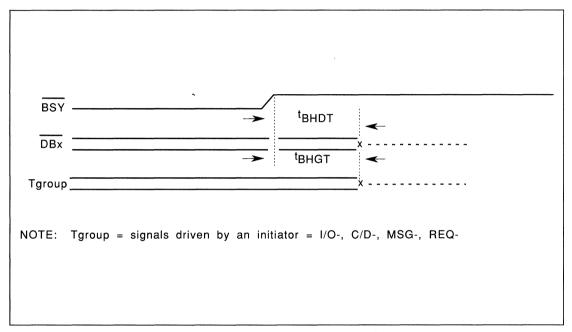

| 6-32   | Timing-Target to Bus Free                           | 24-74 |

## 1.0 INTRODUCTION

## 1.1 DESCRIPTION

The 33C93B, a MOS/VLSI device implemented in Western Digital's CMOS process, operates from a single 5 volt supply and is available in either a 44-pin PLCC or a 40-pin dual-in-line (DIP) package. All inputs and outputs are TTL compatible.

The 33C93B is intended for use in systems which interface to the Small Computer System Interface (SCSI) Bus. The 33C93B can operate in both the initiator (typically, a host computer system) and the target (typically, a peripheral device) SCSI bus roles.

When used in the host system, the 33C93B interfaces to both the host bus and the SCSI bus. To perform a SCSI operation, the host processor issues a command to the 33C93B to select the desired target. The 33C93B then arbitrates for the SCSI bus and selects the peripheral unit. If it fails to get the bus because of a device with higher priority, it continues trying and notifies the host when it has succeeded by generating an interrupt. At this point, the 33C93B is operating in the initiator role. When the peripheral requests a SCSI command from the host, the 33C93B receives the request and generates another interrupt to the host. The host responds to this interrupt by issuing a "Transfer Info" command and supplying SCSI command bytes to the 33C93B. The 33C93B transfers the SCSI command to the peripheral and then waits for the next bus phase request. This process continues until all SCSI information including data. status, and messages have been transferred.

The 33C93B also offers high-level Select-and-Transfer commands which eliminate the interrupt handling otherwise required between each SCSI bus phase.

When the 33C93B is used in a peripheral system, the 33C93B operates primarily in a target role. It interfaces with a local processor and the SCSI bus in this environment just as it does when used in a host adapter. The target-role command set enables the 33C93B to request each SCSI bus phase individually or to sequence the SCSI bus phases automatically through the use of combination commands.

The 33C93B has an internal microcontroller, a register task file, and SCSI interface logic. This architecture supports both tight control of the

protocol for non-standard SCSI implementations, as well as a hands-free mode for standard SCSI applications.

#### 1.2 FEATURES

- Implements full SCSI bus features: arbitration, disconnect, reconnect, parity generation and checking on both data ports, soft reset, and synchronous data transfers.

- Includes 48 mA drivers for direct connection to the SCSI bus.

- Operates in both initiator and target roles.

- Synchronous offset selectable from one to twelve bytes.

- Programmable timeout for selection and reselection.

- Support for SCSI-2 features:

- Synchronous transfer rates up to 10 Mbytes/s for Fast SCSI transfers; up to 5 Mbyte/s for standard SCSI transfers.

- Select-and-Transfer, Reselect-and-Transfer, and Wait-for-Select-and-Receive commands provide support for queue tag messages and target routine identify messages.

- Special "Translate Address" command performs the Logical-to-Physical address mapping.

- "Combination" commands greatly reduce interrupt-handling responsibilities.

- Compatible with most microprocessors through an 8-bit data bus; supports both multiplexed and non-multiplexed address/data bus systems. Host bus data parity checking and generation is an optional feature.

- Burst data transfers up to 4096 bytes.

- Data transfer options include programmed I/O, single-byte DMA, burst (multibyte) DMA, or direct bus access (WD bus) transfers.

- Single +5 V supply.

- Available in 44-pin PLCC or 40-pin DIP.

- Low-power CMOS design.

## 1.3 DIFFERENCES BETWEEN THE 33C93A AND 33C93B

The 33C93B delivers the same functionality as the 33C93A as well as additional features to support SCSI-2 and improve system performance. Unless the device is configured with the RAF bit in the OWN ID register set, the 33C93B is completely backward compatible to the 33C93A; consequently, in most applications, it may replace the 33C93A with no modification to the hardware or the firmware.

The 33C93B has grouped several recently added features of the 33C93A with two 33C93B-only enhancements into a mode enabled by configuring the device with the RAF bit set. Section 4.3.1 describes this new mode. The first two features---the loading of the microcode revision on a soft reset condition and the aborting of a target Receive command upon the detection of the SCSI Attention condition or of a parity error---existed in the 33C93A design. The 33C93B design has added to this mode the ability to detect possible data corruption and unexpected disconnects from the SCSI bus when operating as a target.

To support SCSI-2, the combination commands Select-and-Transfer, Reselect-and-Transfer, and Wait-for-Select-and-Receive optionally send or receive Queue-tag messages at appropriate points in the SCSI bus sequence. The host via two bits in the Destination ID Register and the newly added Queue Tag Register provides information which the first two commands use to generate and check these messages. Wait-for-Select-and-Receive, through the same locations, relays information to the host regarding the type of Queue-tag message received, including whether the initiator sent a message or not, and the actual queue tag.

These commands also support the LUNTAR bit in the Identify message. By setting the corresponding bit in the Target LUN Register, the host enables the Select-and-Transfer and Reselect-and-Transfer commands to send an Identify message for a target routine. In the case of Select-and-Transfer, setting this bit also enables the 33C93B to accept automatically an Identify message with the LUNTAR bit set. The host also has the option to let the Wait-for-Select-and-Receive command receive a target routine Identify message and proceed to the next phase or to interrupt the host so that it may reject the message when the application does not support target routines.

The last new feature pertaining to SCSI-2 relates to Fast SCSI. When the 33C93B has an input clock between 16 MHz and 20 MHz, by controlling the Fast SCSI Select (FSS) bit in the Synchronous Transfer Register, the host can select between normal synchronous transfers which reach a maximum transfer rate of 5 MB/s and Fast synchronous transfers with a peak rate of 10 MB/s on both the SCSI and host DMA interfaces.

The final addition to the 33C93B is the FIFO Full/Empty (FFE) bit in the Auxiliary Status Register to be used primarily during polled I/O transfers. As its name suggests, this bit reflects the full or empty state of the FIFO depending on the direction of the transfer. If the host is writing data to the FIFO, the 33C93B sets this bit when the FIFO is empty, indicating that the host may write up to twelve bytes to the FIFO without having to poll the DBR bit before writing each byte. Similarly, when the host is reading data from the FIFO, the 33C93B sets this bit when the FIFO is full, indicating that the host may read the Data Register twelve times without polling DBR before each read. Some restrictions do apply when using this bit, and they are described in Section 3.1.22.

# 2.0 PIN DESCRIPTIONS

FIGURE 2-1. 44-PIN PLCC

FIGURE 2-2. 40-PIN DIP

## 2.1 PROCESSOR/DMA INTERFACE

| NAME  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK   | ı   | 8-20 MHz square wave clock                                                                                                                                                                                                                                                                 |

| MR    | I   | Reset is an active-low input which forces the 33C93B into an idle state and forces all SCSI signals to the negated state.                                                                                                                                                                  |

| INTRQ | 0   | Interrupt Request to the external microprocessor indicates a command completion/termination or a need to service the SCSI interface. Reading the SCSI Status Register clears this bit.                                                                                                     |

| RE    | I/O | Read Enable is an active-low input used with $\overline{CS}$ to read a register or with DACK to access the DATA register in DMA mode. In WD Bus mode, it is used as an output to read data from a sector buffer. (Tri-state).                                                              |

| WE-   | I/O | Write Enable is an active-low input used with $\overline{\text{CS}}$ to write a register or with DACK to access the Data Register in DMA mode. In WD Bus mode, it is used as an output to write data to a sector buffer. (Tri-state)                                                       |

| CS    | I   | Chip Select is an active-low input which qualified $\overline{RE}$ and $\overline{WE}$ when accessign a register. This signal must be inactive during a DMA cycle (DACK active in DMA and Burst DMA mode or DRQ active in WD Bus mode).                                                    |

| A0    | ı   | Address Pin A0 is used to access the internal registers for non-multiplexed address/data busses (i.e.; the ALE pin is grounded). The address of the desired register is loaded into the address register during a write cycle with A0=0. The selected register is then accessed when A0=1. |

**TABLE 2-1. SIGNAL DESCRIPTIONS**

| NAME          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE           |     | Address Latch Enable is used for multiplexed address/data busses to load the address of the desired 33C93B register from the data bus. For indirect addressing, the ALE pin should be grounded. See the description of the Address Register for a complete discussion of direct and indirect addressing.                                                                                                                                                                                                                                                                                                                                                                          |

| DACK<br>(RCS) | I/O | DMA Acknowledge is an active-low input used for interfacing to an external DMA controller (e.g. 8237). When DACK is low, all bus transfers are to or from the DATA register regardless of the contents of the Address Register. In WD Bus mode this pin, an open-drain output, functions as a RAM Chip Select to the sector buffer. RE and WE are outputs when RCS is active. Regardless of the host DMA mode selected, this pin should be pulled via external circuitry (e.g. a pullup resistor) to an inactive state and should not be left floating.                                                                                                                           |

| DRQ           | I/O | Data Request is an active-low output when used for interfacing to an external DMA controller and an active-high input when in WD Bus mode. In the first application, DRQ and DACK form the handshake for the DMA data transfers. In Burst mode, DRQ remains low so long as there is data to transfer; in Single-byte DMA mode, DRQ toggles for each byte. Since this pin is an open drain output, a pullup resistor may be required when operating in these modes. In WD Bus mode, this pin becomes the DRQ input. A high level on this pin enables the 33C93B to perform burst transfers; a low level inhibits transfers by deasserting RCS and disabling the RE and WE outputs. |

| D7 - D0       | I/O | Processor data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DP            | I/O | Data Parity is used only for checking and generating parity during data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

TABLE 2-1. SIGNAL DESCRIPTIONS (Continued)

## 2.2 SCSI INTERFACE

| NAME | I/O | DESCRIPTION                                                                                                                                                           |  |  |  |

|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ATN  | I/O | ATN is an output in the initiator role and an input in the target role. Its assertion indicates the ATTENTION condition.                                              |  |  |  |

| REQ  | I/O | REQ is an input in the initiator role and an output in the target role. It indicates a request for a data transfer.                                                   |  |  |  |

| ACK  | I/O | ACK is an output in the initiator role and an input in the target role. It indicates an acknowledgement of a data transfer.                                           |  |  |  |

| MSG  | I/O | MSG is an input in the initiator role and an output in the target role.  The target asserts this signal when requesting message information.                          |  |  |  |

| C/D  | I/O | C/D is an input in the initiator role and an output in the target role. It specifies whether control or data information is on the SCSI data bus.                     |  |  |  |

| Ī/O  | I/O | I/O is an input in the initiator role and an output in the target role. It controls the direction of data movement on the SCSI data bus with respect to an initiator. |  |  |  |

| SD7  | I/O | SCSI data bus.                                                                                                                                                        |  |  |  |

| SD0  | I/O | SCSI data bus.                                                                                                                                                        |  |  |  |

| SDP  | I/O | SCSI data bus parity signal.                                                                                                                                          |  |  |  |

| BSY  | I/O | BSY is asserted when the 33C93B is attempting to arbitrate for the SCSI bus or when connected as a target.                                                            |  |  |  |

| SEL  | I/O | SEL is asserted when the 33C93B is attempting to select or reselect another SCSI device.                                                                              |  |  |  |

NOTE: All pins have open-drain output drivers.

**TABLE 2-1. SIGNAL DESCRIPTIONS (Continued)**

FIGURE 2-3. WD33C93B BLOCK DIAGRAM

WD33C93B WD33C93B REGISTERS

## 3.0 WD33C93B REGISTERS

| Α0 | R/W | REGISTER ACCESSI                   | ADDRESS<br>(HEX) |    |  |  |

|----|-----|------------------------------------|------------------|----|--|--|

| 0  | R   | Auxiliary Status Register          |                  | XX |  |  |

| 0  | W   | Address Register                   |                  | XX |  |  |

| 1  | R/W | Own ID Register                    | /CDB Size        | 00 |  |  |

| 1  | R/W | Control Register                   |                  | 01 |  |  |

| 1  | R/W | Timeout Period Register            |                  | 02 |  |  |

| 1  | R/W | Total Sectors Register             | /CDB 1st         | 03 |  |  |

| 1  | R/W | Total Heads Register               | /CDB 2nd         | 04 |  |  |

| 1  | R/W | Total Cylinders Register (MSB)     | /CDB 3rd         | 05 |  |  |

| 1  | R/W | Total Cylinders Register (LSB)     | /CDB 4th         | 06 |  |  |

| 1  | R/W | Logical Address (MSB)              | /CDB 5th         | 07 |  |  |

| 1  | R/W | Logical Address (2nd)              | /CDB 6th         | 08 |  |  |

| 1  | R/W | Logical Address (3rd)              | /CDB 7th         | 09 |  |  |

| 1  | R/W | Logical Address (LSB)              | /CDB 8th         | 0A |  |  |

| 1  | R/W | Sector Number Register             | /CDB 9th         | 0B |  |  |

| 1  | R/W | Head Number Register               | /CDB 10th        | 0C |  |  |

| 1  | R/W | Cylinder Number (MSB) Register     | /CDB 11th        | 0D |  |  |

| 1  | R/W | Cylinder Number (MSB) Register     | 0E               |    |  |  |

| 1  | R/W | Target LUN Register                |                  |    |  |  |

| 1  | R/W | Command Phase Register             |                  | 10 |  |  |

| 1  | R/W | Synchronous Transfer Register      |                  | 11 |  |  |

| 1  | R/W | Transfer Count Register (MSB)      |                  | 12 |  |  |

| 1  | R/W | Transfer Count Register (2nd Byte) |                  | 13 |  |  |

| 1  | R/W | Transfer Count Register (LSB)      |                  |    |  |  |

| 1  | R/W | Destination ID Register            | 15               |    |  |  |

| 1  | R/W | Source ID Register                 | 16               |    |  |  |

| 1  | R   | SCSI Status Register               | 17               |    |  |  |

| 1  | R/W | Command Register                   |                  |    |  |  |

| 1  | R/W | Data Register                      |                  |    |  |  |

| 1  | R/W | Queue Tag Register                 |                  | 1A |  |  |

NOTE: 1. All unused bits of a defined register are reserved and must be zero.

- 2. Reading an undefined or unavailable register results in an all-ones data bus output.

- 3. Register addresses are determined by the Address Register bits AR7 through AR0.

- 4. When using a multiplexed address/data bus with ALE, the A0 pin is ignored, and the Address Register is loaded with ALE. In this mode, the Auxiliary Status Register is mapped at 1F hex.

- 5. See Section 3.2 for a description of how reset affects the internal registers.

**TABLE 3-1. REGISTER MAP**

#### 3.1 REGISTER DESCRIPTIONS

#### 3.1.1 Auxiliary Status Register

The Auxiliary Status Register, a read-only register, contains general status information not directly associated with the interrupt condition. The host may access the Auxiliary Status Register at any time except during DMA accesses. (DACK asserted in DMA/Burst mode or RCS asserted in WD bus mode).

| 7   | 6   | 5   | 4   | 3 | 2   | 1  | 0   |

|-----|-----|-----|-----|---|-----|----|-----|

| INT | LCI | BSY | CIP | 0 | FFE | PE | DBR |

#### **Bit ODBR-DATA BUFFER READY**

Data Buffer Ready indicates to the processor whether or not the Data Register is available for reading or writing. During a Send command or a Transfer Info command which transmits data over the SCSI bus, the 33C93B sets this bit when ready to take a byte from the host; it resets this bit when the processor writes the byte to the DATA register. During a Receive command or a Transfer Info command which receives data over the SCSI bus, the 33C93B sets DBR when it receives a byte and resets DBR when the processor reads the byte from the DATA register.

## **Bit 1PE-PARITY ERROR**

Parity Error status indicates that the 33C93B received a byte with even parity during a transfer. SCSI parity checking is always enabled; host parity checking is enabled via the EHP bit in the OWN ID register Detection of a parity error will set the PE status bit regardless of the state of the HHP or HSP bits in the CONTRO register. Issuing a command clears the PE bit.

#### Bit 2FFE -FIFO FULL/EMPTY

FIFO Full/Empty indicates when the FIFO is full or empty depending on the direction of the transfer. (see Section 3.1.22)

## **Bit 4CIP - COMMAND IN PROGRESS**

Command In Progress indicates that the 33C93B is interpreting the last command entered into the Command Register which is therefore unavailable.

3/12//91

#### Bit 5BSY-BUSY

Busy indicates that a Level II command is currently executing, so the host may only access the Command Register (when CIP = 0),the Data Register, and the Auxiliary Status Register. When this bit is set, the host should not issue a Level II command.

## Bit 6 LCI -LAST COMMAND IGNORED

Last Command Ignored indicates that the 33C93B ignored a command because the host issued it just prior to or concurrent with a pending interrupt.

#### **Bit 7 INT-INTERRUPT PENDING**

Interrupt Pending reflects the state of the INTRQ pin. When set, the host should read the SCSI Status Register to clear INTRQ prior to issuing any commands.

#### 3.1.2 Address Register

The Address Register, a write-only register, holds the address of the register to be accessed. Registers in the 33C93B may be accessed in one of two ways:

- Direct addressing (multiplexed address/data busses). In this mode, the falling edge of the ALE signal latches the contents of the host data bus into the ADDRESS register. The CS and WE or RE signals typically follow to access the selected register. When using direct addressing, the A0 pin should be connected to ground, and the Auxiliary Status Register is located at address 1F hex.

- Indirect addressing (separate address/data busses). This method, enabled by tying ALE to ground, requires two separate cycles for a register access. The first cycle loads the desired address into the Address Register by writing (CS and WE asserted) to the 33C93B with A0=0.The second cycle, with A0=1, then reads (CS and RE asserted) or writes (CS and WE asserted) the selected register. Every cycle with A0=1 increments the ADDRESS register except when accessing the Data or Command Registers. In indirect addressing, the Auxiliary Status Register is accessed by performing a read (CS and RE asserted) with A0=0.

#### 3.1.3 Own ID/CDB Size Register

The Own ID/CDB Size Register, in its first mode, contains information which the Soft Reset command uses to configure the device. Following a hardware reset, the host, before issuing any other command, must initialize this register and issue the Reset command to set the clock divisor and the SCSI bus ID of the device and to enable various sets of features and host bus parity checking.

In the second mode, bits 3-0 of this register specify the SCSI CDB size if the command group is unknown (i.e. not a group 0, group 1, or group 5 SCSI command) to the 33C93B during the Select-and-Transfer and Wait-for-Select commands. This mode is enabled only when advanced features (see Section 4.3.1) have been selected.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| FS1 | FS0 | RAF | EHP | EAF | ID2 | ID1 | ID0 |

#### Bit 0-2IDn-SCSI ID BITS

SCSI ID Bits 0-2 set the SCSI bus ID that the 33C93B uses during arbitration and selection.

#### Bit 3EAF-ENABLE ADVANCED FEATURES

Enable Advanced Features, when set, enables functions described in section 4.3.1.

#### **Bit 4 EHP-ENABLE HOST PARITY**

Enable Host Parity enables odd parity checking on the host bus. The PE bit in the Auxiliary Status Register will then also indicate parity errors detected on the host bus, and the HHP bit in the Control Register will have effect during transfers. When host parity is disabled, the PE bit is not set when a parity error occurs on the host bus, and the HHP bit must be set to zero. Note: Parity is always generated on the host data parity bit (DP), regardless of the state of this bit.

#### Bit 5 RAF-REALLY ADVANCED FEATURES

Really Advanced Features, when set, enables features described in section 4.3.1.

## Bit 6-7 FSn-FREQUENCY SELECT

Frequency Select 0-1 select the divisor that is applied to the input clock. The divided clock is used for data transfer timing

and for SCSI bus arbitration timing. The table below shows input clock frequency ranges and their corresponding divisors. An incorrect divisor for the input clock may result in violation of SCSI bus timing specifications.

| INPUT CLOCK<br>FREQUENCY<br>(MHz) | FS1 | FS0 | RESULTING<br>DIVISOR |

|-----------------------------------|-----|-----|----------------------|

| 8-10                              | 0   | 0   | 2                    |

| 12-15                             | 0   | 1   | 3                    |

| 16-20                             | 1   | 0   | 4                    |

| XX                                | 1   | 1   | Undefined            |

Note that a clock rate between 10 MHz and 12 MHz should not be used, as the resulting SCSI bus clear delay may violate SCSI specifications. The formula for computing the maximum SCSI data transfer rate is given in Section 6.

#### 3.1.4 Control Register

The Control Register consists of option bits which affect response to parity errors and to the SCSI attention condition, suppress interrupts, allow command chaining, and select the mode of DMA transfer.

| 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0   |

|-----|-----|-----|-----|-----|-----|----|-----|

| DM2 | DM1 | DM0 | HHP | EDI | IDI | НА | HSP |

#### Bit 0 HSP-HALT on SCSI PARITY ERROR

The Halt on SCSI Parity Error bit enables the 33C93B to terminate a Receive or Transfer Info command if a parity error occurs on an incoming SCSI data byte. Asynchronous transfers check parity on every byte: synchronous data transfers check parity on 4096-byte boundaries in most cases. In the initiator role, the 33C93B responds to a SCSI parity error by leaving the ACK pin asserted to inhibit any additional data transfers (REQs) by the target and to facilitate error handling with the target. If Immediate Halts are enabled, a SCSI parity error during a synchronous Receive or Reselect-and-Receive command will abort the transfer before the 4096-byte boundary.

# 24

#### Bit 1 HA-HALT on ATTENTION

The Halt on Attention bit (target mode only) enables the 33C93B to terminate a Send or Receive command if the initiator asserts ATN. The 33C93B normally tests for the ATN condition before the start of a data transfer, on 4096 byte boundaries, and after the end of the transfer. If the Immediate Halt feature is enabled, an Abort command will be issued upon recognition of the ATN condition. These rules apply to both synchronous and asynchronous transfers.

# Bit 2 IDI-INTERMEDIATE DISCONNECT INTERRUPT

The Intermediate Disconnect Interrupt bit, when set in the initiator role, causes the 33C93B to terminate a Select-and-Transfer command and generate an 85 hex interrupt upon a proper target disconnect. When this bit is reset, a valid disconnect will not cause the 33C93B to generate an interrupt, and command execution proceeds. This feature, when used with the Resume SAT command, provides support for overlapped SCSI operations. In the target role, the IDI bit selects combination command execution options. Refer to Section 4 for more details.

#### Bit 3EDI-ENDING DISCONNECT INTERRUPT

The Ending Disconnect Interrupt bit, when set, delays the 16 hex interrupt which normally follows receipt of the Command-Complete message during a Select-and-Transfer command until after the target disconnects, replacing the 85 hex interrupt. This bit also enables chaining between certain target-role combination commands to reduce host system overhead. Refer to Section 4 for more details.

## **Bit 4HHP-HALT on HOST PARITY ERROR**

The Halt on Host Parity Error bit allows the 33C93B to terminate a Send or Transfer command if a parity error occurs on an incoming host data byte. The 33C93B checks for host parity errors according to the sames rules it uses when checking for SCSI parity errors. However, a host parity error will not leave the ACK signal asserted.

#### Bit 5-7 DMx-DMA MODE SELECT

The DMA Mode Select bits 2-0 select the host bus transfer mode to be used during a Data phase. The following table describes the different DMA modes and specifies the state of these bits to select each mode:

| DM2 | DM1 | DMO | DMA MODE SELECTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | Polled I/O Mode or no DMA enabled. The host must poll for DBR in the Auxiliary Status Register and then, depending on the direction of the transfer, read or write the DATA register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | 0   | 1   | Burst Mode or demand-mode DMA. In this mode, the $\overline{DRQ}$ signal will remain active so long as data or space exists in the internal FIFO to allow the transfer to continue. The DMA controller responds by asserting DACK and pulsing RE or WE to transfer the data.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0   | 1   | 0   | WD-Bus Mode or Direct Buffer Access (DBA) mode. In this mode, the 33C93B acts as a bus master, and all data access signals reverse their directions. The DRQ pin becomes the DRQ input, which when high, enables the 33C93B to drive the buffer control signals. The DACK pin becomes the RCS output and serves as a chip select for the buffer. The RE and WE pins become outputs which drive the read and write functions of the RAM buffer. Transfers will continue in a burst manner until the transfer is complete or until the external buffer logic pauses the transfer by negating the DRQ signal. One transfer may occur after DRQ drops and then the DACK, RE, and WE signals will tri-state. |

| 1   | 0   | 0   | DMA MODE or Single-byte DMA. In this mode,a DRQ/DACK handshake occurs for each byte. The DMA controller transfers the byte by asserting WE or RE while asserting DACK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### 3.1.5 Timeout Period Register

The Timeout Period Register stores a user-selected, 8-bit value which determines the timeout period for selection and reselection attempts. The timeout period specifies how long the 33C93B will wait for a response (i.e. assertion of the BSY signal) after it has begun the Selection phase (asserted SEL and negated BSY) before terminating the command. Loading this register with zero disables the timeout feature. For a desired timeout period, the register value depends upon the input clock frequency, as shown in the following equation:

where Tper = the desired timeout period in milliseconds; Ficlk = the input clock frequency at the MCK pin in megahertz (with no divisor applied).

The constant '80' scales the units of the equation, as it is based on the internal timeout cycle time. The user should round the resulting 'register value' up to the next integral value to ensure that the minimum timeout requirement is met.

#### 3.1.6 Command Descriptor Block Registers

The Command Descriptor Block Registers hold the SCSI command bytes to be sent during Command phase of a Select-and-Transfer command and the command bytes received during the Command phase of a Wait-for-Select-and-Receive command.

The Send-Status-and-Command-Complete command uses the contents of the CDB11 register as the returned status and determines the type of the Command-Complete message to send from the contents of the CDB12 register. Bit 0 of CDB12 selects whether the command sends a simple Command-Complete message bit 0=0) or a Linked-Command-Complete message (bit 0=1). In the latter case, bit 1 of CDB12, the FLAG bit, specifies whether a 0A hex (FLAG=0) or a 0B hex (FLAG=1) message is sent.

## 3.1.7 Total Sectors Register

The Total Sectors Register stores an 8-bit value specifying the total number of sectors per track for the Translate Address command.

## 3.1.8 Total Heads Register

The Total Heads Register stores an 8-bit value specifying the total number of heads for the Translate Address command.

## 3.1.9 Total Cylinders Register

The Total Cylinders Register stores a 16-bit value specifying the total number of cylinders for the Translate Address command.

## 3.1.10 Logical Address Register

The Logical Address Register stores the 32-bit logical address to be translated by the Translate Address command.

## 3.1.11 Sector Number Register

The Sector Number Register will contain the resulting physical sector number following a Translate Address command.

#### 3.1.12 Head Number Register

The Head Number Register contains the resulting head number following a Translate Address command.

If the host desires the 33C93B to compensate for spare sectors on the disk, this register should contain the number of spare sectors per cylinder prior to issuing the Translate Address command. A value of zero indicates no compensation. With compensation, the maximum number of cylinders allowed is 4096, and the maximum number of heads is 15.

#### 3.1.13 Cylinder Number Register

The Cylinder Number Register contains a 16-bit value specifying the resulting cylinder number following a Translate Address command.

If the host desires the 33C93B to compensate for spare sectors on the disk, the Translate Address

command expects this register to contain the number of sectors per cylinder after allowing for the spares, i.e. (sectors/track \* heads - spares/cylinders).

#### 3.1.14 Target LUN Register

The Target LUN Register holds the Logical Unit Number (LUN) and other target status information during various 33C93B commands and sequences.

The Select-and-Transfer commands use the contents of this register and the Source ID Register to generate and check Identify messages. In addition, these commands also store the returned status byte from the target in this register. For proper operation of the Select-and-Transfer commands, the host should not set the TLV bit in this register.

In advanced mode, the Select-and-Transfer commands, in the event of an unexpected reselection, place the logical unit number (TRN=0) or the target routine number (TRN=1) of a reselecting target in this register. The TLV and DOK bits will be zero.

The Wait-for-Select-and-Receive command places a copy of a received Identify message in this register. If the TLV bit is zero, the initiator did not send a valid Identify message. If the TLV bit is one, the initiator sent a valid Identify message, and the DOK bit will then indicate whether or not the initiator has enabled disconnects. The Wait-for-Select-and-Receive command will accept an Identify message with the TRN bit set only if the host issues the command with the SBT bit in the Command Register set.

The Reselect-and-Transfer commands use only the LUN portion and the TRN bit of this register to generate the Identify message. The TLV and DOK bits are not used.

| 7   | 6   | 5   | 4 | 3 | 2   | 1   | 0   |

|-----|-----|-----|---|---|-----|-----|-----|

| TLV | DOK | TRN | 0 | 0 | TL2 | TL1 | TL0 |

## 3.1.15 Command Phase Register

The Command Phase Register indicates which phases of a combination command have completed. Thus, if the command has terminated abnormally, the processor can read this register to determine the cause of the termination and decide how to respond to it.

When resuming a combination command, the contents of this register specify from which point to restart the command. Refer to the description of the specific commands for details regarding the various command phases and resume values.

| 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|

| 0 | CP6 | CP5 | CP4 | CP3 | CP2 | CP1 | CP0 |

## 3.1.16 Synchronous Transfer Register

The contents of the Synchronous Transfer Register specify the maximum transfer rate and the transfer mode for a SCSI data phase.

For information phases other than a Data phase or when the selected offset is zero (OF3= OF2=OF1=OF0=0), the 33C93B performs asynchronous transfers. A non-zero offset value, which should be twelve or less, selects synchronous data transfers and determines the effective FIFO depth. This value is typically determined through negotiation (as defined in the SCSI standard) with the other SCSI device.

The Transfer Period control bits select the minimum transfer period for both synchronous and asynchronous SCSI data transfers and, in WD-Bus mode, the transfer period and the width of the RE/WE strobes for host transfers; for non-data transfers, the transfer period defaults to six periods. The period is defined in terms of the internal clock cycle time, which depends upon the input clock, the divisor selected in the Own ID Register, and the setting of the FSS bit.

The FSS bit has effect only when operating with an input clock frequency of 16-20 MHz, i.e. the divisor

set to 4. Setting this bit enables Fast SCSI transfers, doubling the maximum transfer rate for synchronous transfers. For example, with a 20 MHz input clock and a transfer period of 2, the normal maximum transfer rate (FSS=0) would be 5 MB/s; the Fast SCSI transfer rate (FSS=1) would be twice this value or 10 MB/s. The FSS bit does not affect the rate of asynchronous transfers.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| FSS | TP2 | TP1 | TP0 | OF3 | OF2 | OF1 | OF0 |

#### Bit 0-3 OFx - OFFSET

The OFFSET bits specifies the desired offset according to the following table:

| 3 | 2 | 1 | 0 | SELECTED OFFSET |

|---|---|---|---|-----------------|

| 0 | 0 | 0 | 0 | 0 *             |

| 0 | 0 | 0 | 1 | 11              |

| 0 | 0 | 1 | 0 | 2               |

| 0 | 0 | 1 | 1 | 3               |

| 0 | 1 | 0 | 0 | 4               |

| 0 | 1 | 0 | 1 | 5               |

| 0 | 1 | 1 | 0 | 6               |

| 0 | 1 | 1 | 1 | 7               |

| 1 | 0 | 0 | 0 | 8               |

| 1 | 0 | 0 | 1 | 9               |

| 1 | 0 | 1 | 0 | 10              |

| 1 | 0 | 1 | 1 | 11              |

| 1 | 1 | 0 | 0 | 12              |

| 1 | 1 | 0 | 1 | Undefined       |

| 1 | 1 | 1 | Χ | Undefined       |

<sup>\*</sup> Asynchronous data phase transfers.

| 6 | 5 | 4 | SCSI/WD-BUS<br>TRANSFER PERIOD | (SCSI REQ/ACK Synchronous Pulse Width and WD-BUS RE/WE Pulse Width |

|---|---|---|--------------------------------|--------------------------------------------------------------------|

| 0 | 0 | Х | 8 cycles                       | (4 cycles)                                                         |

| 0 | 1 | 0 | 2 cycles                       | (1 cycle)                                                          |

| 0 | 1 | 1 | 3 cycles                       | (1 cycle)                                                          |

| 1 | 0 | 0 | 4 cycles                       | (2 cycles)                                                         |

| 1 | 0 | 1 | 5 cycles                       | (3 cycles)                                                         |

| 1 | 1 | 0 | 6 cycles                       | (4 cycles)                                                         |

| 1 | 1 | 1 | 7 cycles                       | (4 cycles)                                                         |

The 'cycle' referred to above is the period of the internal data transfer clock. For asynchronous transfers or for synchronous transfer when the input clock frequency is less than 16 MHz, it is calculated as follows:

CYCLE (

$$\mu$$

s) =

$$\frac{\text{DIVISOR (from OWN ID)}}{2 * \text{INPUT CLOCK FREQUENCY (MHz)}}$$

For synchronous transfers when the input clock frequency is 16 MHz or greater, the cycle time is calculated as follows:

#### Bit 4-6TPx - TRANSFER PERIOD

The Transfer Period bits select the desired desired transfer period according to the following table:

## Bit 7 FSS - FAST SCSI SELECT

The Fast SCSI Select bit under the conditions mentioned above enables the doubling of the internal clock frequency resulting in a synchronous transfer rate up to 10 MB/s.

#### 3.1.17 Transfer Count Register

The Transfer Count Register, a 24-bit register, stores a preset value for the internal transfer counter. A Send, Receive, or Transfer Info command causes the 33C93B to load this preset value into the internal transfer counter, which then decrements as each data byte is transferred over the

SCSI bus and causes a "successful completion" interrupt when it reaches zero.

Loading the Transfer Count Register with zeros prior to issuing these command or issuing the command with the Single-byte Transfer bit set in the Command Register disables the counter function. If the counter is disabled, the Send, Receive, or Transfer Info command will complete when a single byte has been transferred.

In combination commands, this register specifies the number of bytes to be transferred during a Data phase. A zero value indicates the lack of a Data phase.

After the completion of any successful transfer, including commands issued in Single Byte Transfer mode, the Transfer Count Register will be zero.

When a transfer halts because of an error condition, a SCSI bus phase change, or an abort, the Transfer Count Register will contain the number of bytes NOT successfully transferred over the SCSI bus, including any bytes present in the FIFO at the time of the interruption. The FIFO clearing process may cause the Transfer Count Register to differ with the host DMA controller count, because some bytes may have been transferred into the FIFO but not to the SCSI bus.

#### 3.1.18 Destination ID Register

The Destination ID Register stores the encoded SCSI bus ID of the device to be selected or reselected when a Select or Reselect command is issued. This register also contains control bits that affect the operation of certain combination commands.

| 7   | 6   | 5  | 4   | 3   | 2   | 1   | 0   |

|-----|-----|----|-----|-----|-----|-----|-----|

| SCC | DPD | DF | TG1 | TG0 | DI2 | DI1 | DI0 |

#### **Bit 2-0DIx - DESTINATION ID**

Destination ID bits 2-0 specify which SCSI device to select or reselect.

#### Bit 3-4TGx - TAG MESSAGE

The Tag Message bits select which tag message code to send during Select-and-Transfer and identify which tag message code was received by the Wait-for-Select-and-Receive command. In addition, the Reselect-and-Transfer commands send a Simple-Queue Tag message following the Identify message if either of these bits are set.

| 4 | 3 | MESSAGE RECEIVED OR SENT |

|---|---|--------------------------|

| 0 | 0 | No Message               |

| 0 | 1 | Simple Queue Tag (20H)   |

| 1 | 0 | Head Of Queue Tag (21H)  |

| 1 | 1 | Ordered Queue Tag (22H)  |

## Bit 5DF -DISABLE FEATURE

Disable Feature, when set, disables Data phase direction checking in advanced mode and inhibits the normally automatic link from Send-Status-and-Command-Complete to the command fetch portion of Wait-for-

Select-and-Receive when a Linked-Command-Complete message is sent.

#### Bit 6 DPD - DATA PHASE DIRECTION

Data Phase Direction, when advanced features are enabled (see Section 4.3.1), specifies the expected direction of the SCSI Data phase of a Select-and-Transfer command. When this bit is zero, the expected direction is out (to the target), and when this bit is one, the expected direction is in (from the target). An unexpected data phase error will occur if the actual direction does not match the setting of this bit.

#### Bit 7 SCC - SELECT COMMAND CHAIN

Select Command Chain selects which command will follow a Reselect-and-Transfer command when chaining is enabled (EDI=1). When this bit is zero, a Send-Status-and-Command-Complete command will follow; when this bit is one, a Send-Disconnect-Message command follows.

## 3.1.19 Source ID Register

The SOURCE ID register is used to report the SCSI bus ID of the device that has selected or reselected the 33C93B. It also contains bits that enable and control response to selection and reselection.

| 7  | 6  | 5   | 4 | 3   | 2   | 1   | 0   |

|----|----|-----|---|-----|-----|-----|-----|

| ER | ES | DSP | 0 | SIV | SI2 | SI1 | SI0 |

#### Bit 2-0SIx - SOURCE ID

Source ID Bits 2-0, valid only if the SIV bit is set, indicate the SCSI bus ID of the device that selected or reselected the 33C93B.

#### Bit 3SIV - SOURCE ID VALID

Source ID Valid is set to one when the 33C93B is selected or reselected and the other SCSI bus device asserted its own bus ID bit during the Selection/Reselection phase. This bit is zero if only the bus ID bit of the 33C93B was asserted.

#### Bit 5DSP DISABLE SELECT PARITY

Disable Select Parity, when set, causes the 33C93B to ignore the bus parity when responding to selection or reselection.

#### Bit 6 FS - FNABLE SELECTION

Enable Selection, when set, allows the 33C93B to respond to selection by another device on the SCSI bus.

#### Bit 7ER - ENABLE RESELECTION

Enable Reselection, when set, allows the 33C93B to respond to re-selection by another device on the SCSI bus.

## 3.1.20 SCSI Status Register

The SCSI Status Register, a read-only register, holds a value which indicates the cause of the most recent INTRQ assertion. The 33C93B asserts INTRQ whenever a condition occurs that requires intervention by the host. For example,

- the 33C93B has been reset;

- the command completed successfully;

- the bus phase changed;

- an error occurred.

After assertion of INTRQ, the contents of this register will not change until the host reads the register or until the 33C93B has been reset.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| SS7 | SS6 | SS5 | SS4 | SS3 | SS2 | SS1 | SS0 |

## Bit 0-3SSx - SCSI STATUS

SCSI Status bits 0-3 are status qualifiers with meanings that depend upon the upper (4-7) status bits.

## Bit 4-7SSx - SCSI STATUS

SCSI Status bits 4-7 define the type of interrupt that occurred. The following table describes the various types:

| STATUS | CODE | GROUP MEANING                                                                                   |

|--------|------|-------------------------------------------------------------------------------------------------|

| 0000   | xxxx | The 33C93B is in a reset state.                                                                 |

| 0001   | xxxx | A 33C93B command has completed successfully.                                                    |

| 0010   | xxxx | A 33C93B command has paused or was aborted.                                                     |

| 0100   | xxxx | A 33C93B command has been terminated prematurely due to an error or other unexpected condition. |

| 1000   | xxxx | An event on the SCSI bus requires service.                                                      |

All other Status Code groups are currently not used and are reserved for future use.

WD33C93B WD33C93B REGISTERS

In the following tables, the 'STATE' column indicates the state---Disconnected, Target, or Initiator---from which the Status Code can occur. The MCI field refers to the signals that define a SCSI bus information transfer phase: MSG, C/D, and I/O. A bit set to one indicates that the signal is asserted on the SCSI bus; a zero indicates negation. Whenever one of these Status Codes occurs, the REQ signal is asserted on the SCSI bus. The table on the right summarizes the meaning of the MCI field:

| MCI CODE | MEANING                    |

|----------|----------------------------|

| 000      | Data Out phase             |

| 001      | Data In phase              |

| 010      | Command phase              |

| 011      | Status phase               |

| 100      | Unspecified Info Out phase |

| 101      | Unspecified Info In phase  |

| 110      | Message Out phase          |

| 111      | Message In phase           |

| STATUS | CODE | STATE | SPECIFIC MEANING                                                                                                                                                          |

|--------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000   | 0000 | DTI   | 33C93 Reset. The device has been hard reset, or a Reset command has executed successfully with no advanced features enabled. The new state of the 33C93B is disconnected. |

| 0000   | 0001 | DTI   | 33C93B Reset. The device has successfully completed a Reset command with advanced features enabled. The new state of the 33C93B is disconnected.                          |

**TABLE 3-2. RESET STATE INTERRUPTS**

| STATUS | CODE | STATE | SPECIFIC MEANING                                                                                                                                                                         |  |

|--------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0001   | 0000 | D     | A Reselect command completed successfully. The new state of the 33C93B is connected as a target.                                                                                         |  |

| 0001   | 0001 | D     | A Select command completed successfully. The new state of the 33C93B is connected as an initiator.                                                                                       |  |

| 0001   | 0010 | -     | Reserved for future use.                                                                                                                                                                 |  |

| 0001   | 0011 | Т     | A Receive, Send, Reselect-and-Transfer, Wait- for-Select and-Receive, Send-Status-and-Command-Complete, or Send-Disconnect-Message command completed successfully (ATN is not asserted). |  |

| 0001   | 0100 | Т     | A Receive, Send, Reselect-and-Transfer, Wait-for-Select and-Receive, or Send-Status-and-Command-Complete command completed successfully (ATN is asserted).                               |  |

| 0001   | 0101 | DT    | A Translate Address command completed successfully.                                                                                                                                      |  |

| 0001   | 0110 | ı     | A Select-and-Transfer command completed successfully.                                                                                                                                    |  |

| 0001   | 0111 | -     | Reserved for future use.                                                                                                                                                                 |  |

| 0001   | 1MCI | İ     | A Transfer Info (non-Message-In phase) command completed successfully. MCI defines the new information type (SCSI bus phase) requested.                                                  |  |

TABLE 3-3. SUCCESSFUL COMPLETION INTERRUPTS

| STATUS | CODE | STATE | SPECIFIC MEANING                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0010   | 0000 | ı     | A Transfer Info (Message In phase) command has paused with ACK asserted, giving the host the opportunity to reject the message.                                                                                                                                                                                                                                                                                                               |  |  |

| 0010   | 0001 | I     | A Save-Data-Pointer message was received during a Select-and-Transfer command. The host should save its current data buffer pointer.                                                                                                                                                                                                                                                                                                          |  |  |

| 0010   | 0010 | D     | A Select, Reselect, or Wait-for-Select-and-Receive command aborted.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 0010   | 0011 | Т     | A Receive or Send command aborted, or a Wait-for-Select- <u>and-Receive</u> detected an error in the Identify message. (ATN is not asserted).                                                                                                                                                                                                                                                                                                 |  |  |

| 0010   | 0100 | Т     | A command aborted or halted due to assertion of ATN, or a Wait-for-Select-and-Receive detected an error in the Identify message. (ATN is asserted).                                                                                                                                                                                                                                                                                           |  |  |

| 0010   | 0101 | Т     | A transfer has aborted because of a violation of the data transfer protocol, possibly corrupting the data.                                                                                                                                                                                                                                                                                                                                    |  |  |

| 0010   | 0110 | I     | An I/O process with a queue tag which does not match the value in the Queue Tag Register reselected the 33C93B. ACK has been left asserted.                                                                                                                                                                                                                                                                                                   |  |  |

| 0010   | 0111 | I     | A target whose SCSI bus ID does not match the ID in the Destination ID Register reselected the 33C93B or the following Identify message did not match the LUN in the Target LUN Register. ACK has been left asserted following the Identify message, and the bus ID and LUN of the reselecting target are available in the Source ID and Target LUN Registers. This status only occurs when executing a Select-and-Transfer in advanced mode. |  |  |

| 0010   | 1MCI | -     | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

**TABLE 3-4. PAUSED OR ABORTED INTERRUPTS**