## WD90C24

Windows Accelerated High Resolution VGA LCD Controller for Low Power Applications

## TABLE OF CONTENTS

| Section | Title |          |                                 | Page  |

|---------|-------|----------|---------------------------------|-------|

| 1.0     | INTRO | DUCTION  |                                 | 13-1  |

|         | 1.1   | FEATUF   | RES                             | 13-1  |

|         | 1.2   | GENER    | AL DESCRIPTION                  |       |

| 2.0     | ARCH  | ITECTURE |                                 | 13-2  |

|         | 2. 1  | INTROD   | UCTION                          | 13-2  |

|         | 2. 2  | CRT CO   | NTROLLER MODULE                 | 13-4  |

|         | 2.3   | SEQUE    | NCER                            | 13-4  |

|         | 2.4   | GRAPHI   | CS CONTROLLER                   | 13-4  |

|         | 2.5   |          | UTE CONTROLLER                  |       |

|         | 2.6   | FLAT PA  | NEL CONTROLLER AND INTERFACE    | 13-4  |

|         | 2. 7  | WEIGH1   | AND MAPPING LOGIC               | 13-5  |

|         | 2. 8  | DITHER   | ING ENGINE                      | 13-5  |

|         | 2. 9  | HARDW    | ARE WINDOW ACCELERATOR (BITBLT) | 13-5  |

|         | 2. 10 |          | ARE CURSOR CONTROLLER           |       |

|         | 2. 11 | RAMDA    | С                               | 13-6  |

|         | 2. 12 |          | SYNTHESIZER                     |       |

|         | 2. 13 | POWER    | DOWN MANAGEMENT                 |       |

|         |       | 2.13.1   | System Power-Down Mode          | 13-6  |

|         |       | 2.13.2   | Suspend/Resume Mode             | 13-7  |

|         |       | 2.13.3   | Display Idle Mode               | 13-7  |

| 3.0     | INTEF | RFACES   |                                 | 13-9  |

|         | 3. 1  | INTROD   | UCTION                          | 13-9  |

|         | 3. 2  | CPU AN   | D BIOS ROM INTERFACE            | 13-9  |

|         | 3. 3  | DRAM IN  | NTERFACE                        | 13-9  |

|         |       | 3.3.1    | Configurations                  | 13-9  |

|         |       | 3.3.2    | Features                        | 13-10 |

|         | 3. 4  | CRT DIS  | PLAY INTERFACE                  | 13-10 |

|         | 3. 5  | FLAT PA  | NEL INTERFACE                   | 13-10 |

| 4.0     | MEMC  | ORY MODE | CONFIGURATION                   | 13-11 |

|         | 4. 1  | HOST IN  | ITERFACE                        | 13-11 |

| 5.0     | CONF  | IGURATIO | NS                              | 13-12 |

|         | 5. 1  | INTROD   | UCTION                          | 13-12 |

|         | 5. 2  | SINGLE   | MEMORY INTERFACE CONFIGURATION. | 13-13 |

6.0

| 5.3    | 1 MB MEM  | MORY CONFIGURATION 13 |                                      |       |  |

|--------|-----------|-----------------------|--------------------------------------|-------|--|

| 5.4    | SIMULTAN  | NEOUS DISF            | LAY CONFIGURATION                    | 13-15 |  |

| 5.5    | 512 KB HI | GH-PERFOF             | MANCE CONFIGURATION                  | 13-16 |  |

| 5.6    | 256 KB W  | TH SIMULT             | ANEOUS DISPLAY CONFIGURATION         | 13-17 |  |

| SIGNAL | DESCRIP   | FIONS                 |                                      | 13-18 |  |

| 6. 1   | INTRODU   | CTION                 | TION 13                              |       |  |

| 6. 2   |           |                       | O PIN LOCATION                       |       |  |

| 6. 3   |           |                       | SCRIPTIONS                           |       |  |

|        | 6.3.1     |                       | ce Pin Definitions                   |       |  |

|        | 6.3.2     | Display Buff          | er Memory Interface Pins             | 13-31 |  |

|        |           | 6.3.2.1               | Bank A Video Memory Bus              | 13-31 |  |

|        |           | 6.3.2.2               | Bank B Video Memory Bus              | 13-33 |  |

|        | 6.3.3     | RAM DAC/C             | RT Interface Pins                    | 13-35 |  |

|        | 6.3.4     | Clock Gene            | ration Interface Pins                | 13-37 |  |

|        | 6.3.5     | Panel Interfa         | ace Pins                             | 13-38 |  |

|        | 6.3.6     | Power and (           | Ground Pins                          | 13-44 |  |

| 6. 4   | PIN MULT  | IPLEXING R            | EFERENCE TABLES                      | 13-45 |  |

|        | 6.4.1     | Host Interfa          | ce Pins                              | 13-46 |  |

|        | 6.4.2     | Display Buff          | er Memory Interface Pin Multiplexing | 13-48 |  |

|        | 6.4.3     | RAM DAC/C             | RT Interface Pin Multiplexing        | 13-50 |  |

|        | 6.4.4     | Clock Gene            | ration Interface Pin Multiplexing    | 13-50 |  |

|        | 6.4.5     | Panel Interfa         | ace Pin Multiplexing                 | 13-51 |  |

|        | 6.4.6     | Power and (           | Ground Pins                          | 13-52 |  |

| REGIST | ER SUMM   | ARY                   |                                      | 13-53 |  |

| 7. 1   | INTRODU   | CTION                 |                                      | 13-53 |  |

| 7.2    | VGA REG   | ISTERS                |                                      | 13-53 |  |

| 7.3    |           |                       | ERS                                  |       |  |

| 7.4    |           |                       | EGISTERS                             |       |  |

| 7.5    | GRAPHIC   | S CONTROL             | LER REGISTERS                        | 13-54 |  |

| 7.6    | ATTRIBUT  | E CONTRO              | LER REGISTERS                        | 13-54 |  |

| 7.7    | VIDEO PA  | LETTE REG             | ISTERS                               | 13-54 |  |

| 7.8    | PARADISE  | E REGISTER            | S                                    | 13-55 |  |

|        | 7.8.1     | General Par           | adise Registers                      | 13-55 |  |

|        | 7.8.2     | Paradise Ex           | tended Registers                     | 13-56 |  |

|        | 7.8.3     | Flat Panel F          | aradise Registers                    | 13-57 |  |

|        | 7.8.4     | Local Bus R           | egisters                             | 13-58 |  |

| 7.9    | COMPATI   | BILITY REGI           | STERS                                | 13-60 |  |

13-ii

7.0

| 8.0  | VGA GE | ENERAL REGISTERS                        | 13-61 |

|------|--------|-----------------------------------------|-------|

|      | 8. 1   | MISCELLANEOUS OUTPUT REGISTER           | 13-61 |

|      | 8. 2   | INPUT STATUS REGISTER 0                 | 13-62 |

|      | 8. 3   | INPUT STATUS REGISTER 1                 | 13-62 |

|      | 8.4    | FEATURE CONTROL REGISTER                | 13-63 |

| 9.0  | VGA SE | EQUENCER REGISTERS                      | 13-63 |

|      | 9. 1   | SEQUENCER INDEX REGISTER                | 13-63 |

|      | 9. 2   | RESET REGISTER                          | 13-64 |

|      | 9. 3   | CLOCKING MODE REGISTER                  | 13-64 |

|      | 9.4    | MAP MASK REGISTER                       | 13-65 |

|      | 9. 5   | CHARACTER MAP SELECT REGISTER           | 13-65 |

|      | 9.6    | MEMORY MODE REGISTER                    | 13-66 |

| 10.0 | VGA CF | RT CONTROLLER REGISTERS                 | 13-67 |

|      | 10. 1  | CRT ADDRESS REGISTER                    | 13-67 |

|      | 10. 2  | HORIZONTAL TOTAL REGISTER               | 13-67 |

|      | 10. 3  | HORIZONTAL DISPLAY ENABLE END REGISTER  | 13-67 |

|      | 10. 4  | START HORIZONTAL RETRACE PULSE REGISTER | 13-67 |

|      | 10. 5  | END HORIZONTAL RETRACE REGISTER         | 13-67 |

|      | 10. 6  | VERTICAL TOTAL REGISTER                 | 13-68 |

|      | 10. 7  | OVERFLOW VERTICAL REGISTER              | 13-68 |

|      | 10. 8  | PRESET ROW SCAN REGISTER                | 13-69 |

|      | 10. 9  | MAXIMUM SCAN LINE REGISTER              | 13-69 |

|      | 10. 10 | CURSOR START REGISTER                   | 13-70 |

|      | 10. 11 | CURSOR END REGISTER                     | 13-70 |

|      | 10. 12 | START ADDRESS HIGH REGISTER             | 13-70 |

|      | 10. 13 | START ADDRESS LOW REGISTER              | 13-71 |

|      | 10. 14 | CURSOR LOCATION HIGH REGISTER           | 13-71 |

|      | 10. 15 | CURSOR LOCATION LOW REGISTER            | 13-71 |

|      | 10. 16 | VERTICAL RETRACE START REGISTER         | 13-71 |

|      | 10. 17 | VERTICAL RETRACE END REGISTER           | 13-71 |

|      | 10. 18 | VERTICAL DISPLAY ENABLE END REGISTER    | 13-72 |

|      | 10. 19 | OFFSET REGISTER                         | 13-72 |

|      | 10. 20 | UNDERLINE LOCATION REGISTER             | 13-73 |

|      | 10. 21 | START VERTICAL BLANK REGISTER           | 13-73 |

|      | 10. 22 | END VERTICAL BLANK REGISTER             | 13-73 |

|      | 10. 23 | CRT MODE CONTROL REGISTER               | 13-74 |

|      | 10. 24 | LINE COMPARE REGISTER                   | 13-75 |

| 11.0 | GRAPH  | IICS CONTROLLER REGISTERS 13-76                              |

|------|--------|--------------------------------------------------------------|

|      | 11. 1  | GRAPHICS INDEX REGISTER 13-76                                |

|      | 11.2   | SET/RESET REGISTER 13-76                                     |

|      | 11.3   | ENABLE SET/RESET REGISTER 13-76                              |

|      | 11.4   | COLOR COMPARE REGISTER 13-76                                 |

|      | 11.5   | DATA ROTATE REGISTER 13-77                                   |

|      | 11.6   | READ MAP SELECT REGISTER 13-77                               |

|      | 11.7   | GRAPHICS MODE REGISTER 13-78                                 |

|      | 11.8   | MISCELLANEOUS REGISTER 13-80                                 |

|      | 11.9   | COLOR DON'T CARE REGISTER 13-80                              |

|      | 11. 10 | BIT MASK REGISTER 13-80                                      |

| 12.0 | ATTRIE | BUTE CONTROLLER REGISTERS 13-81                              |

|      | 12. 1  | ATTRIBUTE INDEX REGISTER 13-81                               |

|      | 12. 2  | PALETTE REGISTERS (00h-0Fh) 13-81                            |

|      | 12. 3  | ATTRIBUTE MODE CONTROL REGISTER 13-81                        |

|      | 12.4   | OVERSCAN COLOR REGISTER 13-82                                |

|      | 12. 5  | COLOR PLANE ENABLE REGISTER 13-83                            |

|      | 12. 6  | HORIZONTAL PEL PANNING REGISTER 13-83                        |

|      | 12. 7  | COLOR SELECT REGISTER 13-84                                  |

| 13.0 | REGUL  | AR PARADISE REGISTERS 13-84                                  |

|      | 13. 1  | ADDRESS OFFSET REGISTERS PR0(A) and PR0(B) 13-84             |

|      | 13. 2  | PR1 - MEMORY SIZE 13-85                                      |

|      | 13. 3  | PR2 - VIDEO SELECT REGISTER 13-89                            |

|      | 13. 4  | PR3 - CRT LOCK CONTROL REGISTER 13-90                        |

|      | 13. 5  | PR4 - VIDEO CONTROL REGISTER13-91                            |

|      | 13. 6  | PR5 - GENERAL PURPOSE STATUS BITS/ UNLOCK<br>PR0 THROUGH PR4 |

|      | 13. 7  | PR10 UNLOCK PR11 - PR1A 13-93                                |

|      | 13. 8  | PR11 EGA SWITCHES 13-93                                      |

|      | 13. 9  | PR12 SCRATCH PAD 13-94                                       |

|      | 13. 10 | PR13 INTERLACE H/2 START 13-94                               |

|      | 13. 11 | PR14 INTERLACE H/2 END 13-94                                 |

|      | 13. 12 | PR15 MISCELLANEOUS CONTROL 1 13-95                           |

|      | 13. 13 | PR16 MISCELLANEOUS CONTROL 2 13-97                           |

|      | 13. 14 | PR17 MISCELLANEOUS CONTROL 3 13-98                           |

|      | 13. 15 | PR18A CRTC VERTICAL TIMING OVERFLOW 13-98                    |

|      | 13. 16 | PR20 UNLOCK SEQUENCER EXTENDED REGISTERS                     |

|      | 13. 17 | PR21 DISPLAY CONFIGURATION AND SCRATCH PAD 13-99             |

|      | 13. 18 | PR22 SCRATCH PAD REGISTER 13-99                              |

*″*,

| 13. 19  | PR23 SCRATCH PAD REGISTER                        | . 13-99 |

|---------|--------------------------------------------------|---------|

| 13. 20  | PR30(A) WRITE BUFFER AND FIFO CONTROL REGISTER   | . 13-99 |

| 13. 21  | PR31 SYSTEM INTERFACE CONTROL                    | 13-100  |

| 13. 22  | PR32 MISCELLANEOUS CONTROL 4                     | 13-101  |

| 13. 23  | PR33(A) DRAM TIMING AND ZERO WAIT STATE          |         |

|         | CONTROL REGISTER                                 |         |

| 13. 24  | PR34(A) VIDEO MEMORY MAPPING REGISTER            |         |

| 13. 25  | PR35(A) USR0, USR1 OUTPUT SELECT REGISTER        | 13-103  |

| 13. 26  | PR45 VIDEO SIGNATURE ANALYZER CONTROL REGISTER   | 13-104  |

|         | 13.26.1 PR45A Signature Analyzer Data I          | 13-104  |

|         | 13.26.2 PR45B Signature Analyzer Data II         | 13-104  |

| 13. 27  | PR57 FEATURE REGISTER I                          | 13-104  |

| 13. 28  | PR58 FEATURE REGISTER II                         | 13-106  |

| 13. 29  | PR58(A) MEMORY MAP TO I/O REGISTER FOR           |         |

|         | BLT ACCESS IN PI/LOCAL BUS                       |         |

| 13. 30  | PR59 - MEMORY ARBITRATION CYCLE SETUP REGISTER   |         |

| 13. 31  | PR60 FRAME BUFFER CONTROLLER I TEST REGISTER     | 13-107  |

| 13. 32  | PR61 FRAME BUFFER CONTROLLER II TEST REGISTER    |         |

| 13. 33  | PR62 - FR TIMING REGISTER                        | 13-108  |

| 13. 34  | PR63 READ/WRITE FIFO CONTROL REGISTER            | 13-109  |

| 13. 35  | PR64 RESERVED FOR FUTURE NEED                    | 13-109  |

| 13. 36  | PR65 RESERVED FOR FUTURE NEED                    | 13-109  |

| 13. 37  | PR66 RAMDAC/PCLK REGISTER                        | 13-109  |

| 13. 38  | PR68 PROGAMMABLE CLOCK SELECTION REGISTER        | 13-109  |

| 13. 39  | PR69 PROGAMMABLE VCLK FREQUENCY REGISTER         | 13-110  |

| 13. 40  | PR70 MIXED VOLTAGE OVERRIDE REGISTER             | 13-110  |

| 13. 41  | PR71 PROGRAMMABLE REFRESH TIMING REGISTER        | 13-110  |

| 13. 42  | PR72 PROGRAMMABLE CLOCK UNLOCK                   | 13-110  |

| 13. 43  | PR73 VGA STATUS DETECT                           | 13-111  |

| FLAT PA | ANEL PARADISE REGISTERS                          | 13-111  |

| 14. 1   | PR18 FLAT PANEL STATUS REGISTER                  | 13-111  |

| 14. 2   | PR19 FLAT PANEL CONTROL I REGISTER               | 13-113  |

| 14. 3   | PR1A FLAT PANEL CONTROL II REGISTER              | 13-114  |

| 14. 4   | PR1B FLAT PANEL UNLOCK REGISTER                  | 13-115  |

| 14. 5   | PR30 MAPPING RAM UNLOCK REGISTER                 | 13-115  |

| 14. 6   | PR33 MAPPING RAM ADDRESS COUNTER REGISTER        | 13-115  |

| 14. 7   | PR34 MAPPING RAM DATA REGISTER                   | 13-115  |

| 14. 8   | PR35 MAPPING RAM AND POWER-DOWN CONTROL REGISTER | 13-115  |

| 14. 9   | PR36 PANEL HEIGHT SELECT REGISTER                | 13-118  |

|         |                                                  |         |

14.0

|      | 14. 10 | PR37 FLA    | AT PANEL BLINKING CONTROL                                 | 13-118 |

|------|--------|-------------|-----------------------------------------------------------|--------|

|      | 14. 11 | PR39 CO     | LOR LCD CONTROL REGISTER                                  | 13-120 |

|      | 14. 12 | PR41 VEI    | RTICAL EXPANSION INITIAL VALUE REGISTER                   | 13-120 |

|      | 14. 13 | PR44 PO     | WER-DOWN MEMORY REFRESH CONTROL REGISTER                  | 13-121 |

| 15.0 | COMP   | ATIBILITY F | REGISTERS                                                 | 13-121 |

|      | 15. 1  | HERCULI     | ES/MDA MODE CONTROL REGISTER, MDA OPERATION               | 13-121 |

|      | 15. 2  | HERCULI     | ES REGISTERS                                              | 13-122 |

|      | 15. 3  | ENABLE      | MODE REGISTER 3B8h                                        | 13-122 |

|      | 15.4   | HERCUL      | ES COMPATIBILITY REGISTER                                 | 13-122 |

|      | 15.5   | COLOR C     | GA OPERATION REGISTER                                     | 13-123 |

|      | 15.6   | CGA COL     | OR SELECT REGISTER                                        | 13-123 |

|      | 15. 7  | CRT STA     | TUS REGISTER MDA OPERATION                                | 13-124 |

|      | 15. 8  | CRT STA     | TUS REGISTER CGA OPERATION                                | 13-124 |

|      | 15.9   |             | 4 REGISTER                                                | 13-125 |

| 16.0 |        |             | STER ACCESS FOR HARDWARE                                  |        |

|      |        |             | , AND LINE DRAWING                                        |        |

|      | 16. 1  |             |                                                           |        |

|      | 16.2   |             | ONTROL REGISTER - PORT 23C0h/23C1h                        | 13-126 |

|      | 16. 3  |             | IPT STATUS REGISTER, SYSTEM CONTROL<br>RS BLOCK - INDEX 0 | 13-127 |

|      |        | 16.3.1      | Global Interrupt Map                                      | 13-127 |

| 17.0 | HARD   | VARE CUR    | SOR                                                       | 13-128 |

|      | 17. 1  | CURSOR      | CONTROL REGISTER, INDEX 0                                 | 13-128 |

|      | 17. 2  | CURSOR      | PATTERN ADDRESS                                           | 13-129 |

|      |        | 17.2.1      | Cursor Pattern Address Low, Index 1                       | 13-129 |

|      |        | 17.2.2      | Cursor Pattern Address High, Index 2                      | 13-129 |

|      | 17. 3  | CURSOR      | ORIGIN, INDEX 5                                           | 13-129 |

|      | 17.4   | CURSOR      | DISPLAY POSITION                                          | 13-129 |

|      |        | 17.4.1      | Cursor Display Position X, Index 6                        | 13-129 |

|      |        | 17.4.2      | Cursor Display Position Y, Index 7                        | 13-130 |

|      | 17. 5  | CURSOR      | COLOR REGISTERS                                           | 13-130 |

|      |        | 17.5.1      | Cursor Primary Color, Index 3                             | 13-130 |

|      |        | 17.5.2      | Cursor Secondary Color, Index 4                           | 13-130 |

|      |        | 17.5.3      | Cursor Auxiliary Color, Index 8                           | 13-130 |

| 18.0 | HARDV  | VARE BITB   | LT                                                        | 13-131 |

|      | 18. 1  | CONTRO      | L AND STATUS                                              | 13-131 |

|      |        | 18.1.1      | BITBLT Control - Part 1, Index 0                          | 13-131 |

|      |        | 18.1.2      | BITBLT Control - Part 2, Index 1                          | 13-132 |

|      |        |             |                                                           |        |

1/

| 18. 2  | SOURCE    | E AND DESTINATION                                      | 13-133 |

|--------|-----------|--------------------------------------------------------|--------|

|        | 18.2.1    | BITBLT Source Low, Index 2                             | 13-134 |

|        | 18.2.2    | BITBLT Source High, Index 3                            | 13-134 |

|        | 18.2.3    | BITBLT Destination Low, Index 4                        | 13-134 |

|        | 18.2.4    | BITBLT Destination High, Index 5                       | 13-134 |

| 18. 3  | ADDRES    | SS MAPPING                                             | 13-134 |

|        | 18.3.1    | Monochrome and Planar Modes                            | 13-134 |

|        | 18.3.2    | Packed Modes                                           | 13-134 |

| 18. 4  | DIMENS    | IONS AND ROW PITCH                                     | 13-135 |

|        | 18.4.1    | BITBLT Dimension X, Index 6                            | 13-135 |

|        | 18.4.2    | BITBLT Dimension Y, Index 7                            | 13-135 |

|        | 18.4.3    | BITBLT Row Pitch, Index 8                              | 13-135 |

| 18. 5  | FOREGF    | ROUND AND BACKGROUND COLORS                            | 13-136 |

|        | 18.5.1    | BITBLT Foreground Color, Index A                       | 13-136 |

|        | 18.5.2    | BITBLT Background Color, Index B                       | 13-136 |

| 18. 6  | MAP AN    | D PLANE MASK                                           | 13-136 |

|        | 18.6.1    | BITBLT Mask - VGA, Index E                             | 13-136 |

| 18. 7  | RASTER    | OPERATIONS                                             | 13-137 |

|        | 18.7.1    | BITBLT Raster Operation, Index 9                       | 13-137 |

| 18. 8  | PATTER    | NS                                                     | 13-137 |

|        | 18.8.1    | BITBLT Pattern Storage - Monochrome and Planar Modes   | 13-138 |

|        | 18.8.2    | BITBLT Pattern Storage - Packed Modes                  | 13-138 |

| 18. 9  | MONOC     | HROME TO COLOR EXPANSION                               | 13-138 |

| 18. 10 | EXTRAC    | TING MONOCHROME DATA                                   | 13-139 |

| 18. 11 | COLOR     | TRANSPARENCY                                           | 13-139 |

|        | 18.11.1   | BITBLT Transparency Color, Index C                     | 13-139 |

|        | 18.11.2   | BITBLT Transparency Mask, Index D                      | 13-139 |

| 18. 12 | FILLED F  | RECTANGLES                                             | 13-140 |

| 18. 13 | SYSTEM    | MEMORY TO DISPLAY MEMORY OPERATION                     | 13-140 |

| 18. 14 |           | Y MEMORY TO SYSTEM MEMORY OPERATIONS                   | 13-140 |

| 18. 15 |           | I MEMORY TO DISPLAY MEMORY TRANSFERS<br>DLOR EXPANSION | 13-141 |

| HARDV  | VARE LINE | E DRAWING                                              | 13-141 |

| 19. 1  | STRIP LI  | INE DRAWING                                            |        |

|        | 19.1.1    | Conditions                                             |        |

|        | 19.1.2    | Altered BLT Register Functions                         |        |

|        | 19.1.3    | Line Draw Operation                                    | 13-141 |

19.0

| 20.0         | APPLICATIONS AND PROGRAMMING |                                   |                                            |        |  |  |  |

|--------------|------------------------------|-----------------------------------|--------------------------------------------|--------|--|--|--|

|              | 20. 1                        | USING TH                          | E HARDWARE CURSOR IN 16-BIT PER COLOR MODE | 13-142 |  |  |  |

|              | 20. 2                        | BITBLT O                          | PERATIONS IN VGA MODES 4, 5, AND 6         | 13-143 |  |  |  |

|              | 20. 3                        | BITBLT OPERATIONS IN TEXT MODE 13 |                                            |        |  |  |  |

|              | 20. 4                        | USING BI                          | IBLT IN 16-BIT PER COLOR MODE              | 13-143 |  |  |  |

|              | 20. 5                        | PATTERN                           | S                                          | 13-144 |  |  |  |

|              |                              | 20.5.1                            | Using BITBLT For Arbitrary Sized Patterns  | 13-145 |  |  |  |

|              |                              | 20.5.2                            | Patterns Built On-Screen                   | 13-145 |  |  |  |

|              |                              | 20.5.3                            | Use Of Patterns In Text Mode               | 13-145 |  |  |  |

|              | 20.6                         | SUPPORT                           | FOR KANJI CHARACTERS                       | 13-146 |  |  |  |

|              | 20. 7                        | READING                           | AND WRITING THE VGA READBACK LATCHES       | 13-147 |  |  |  |

|              | 20. 8                        | TRANSFE                           | RRING MONOCHROME SOURCES TO COLOR          | 13-147 |  |  |  |

|              | 20. 9                        | EXTRACT                           | ING MONOCHROME DATA                        | 13-147 |  |  |  |

|              | 20. 10                       | COLOR TH                          | RANSPARENCY                                | 13-148 |  |  |  |

|              | 20. 11                       | DRAWING                           | FILLED RECTANGLES                          | 13-148 |  |  |  |

|              | 20. 12                       | SYSTEM N                          | MEMORY TO VIDEO MEMORY OPERATIONS          | 13-148 |  |  |  |

|              | 20. 13                       | VIDEO ME                          | MORY TO SYSTEM MEMORY OPERATIONS           | 13-148 |  |  |  |

|              | 20. 14                       |                                   | MEMORY TO DISPLAY MEMORY TRANSFERS         |        |  |  |  |

|              |                              |                                   | OR EXPANSION                               |        |  |  |  |

|              | 20. 15                       | CONTROL                           | AND STATUS                                 | 13-149 |  |  |  |

|              | 20.16                        |                                   | IC DESTINATION UPDATE                      |        |  |  |  |

|              | 20. 17                       | QUICK ST                          | ART MODE                                   | 13-152 |  |  |  |

|              | 20. 18                       |                                   | BITBLT                                     |        |  |  |  |

|              | 20.19                        | REGISTER                          | RACCESS                                    | 13-153 |  |  |  |

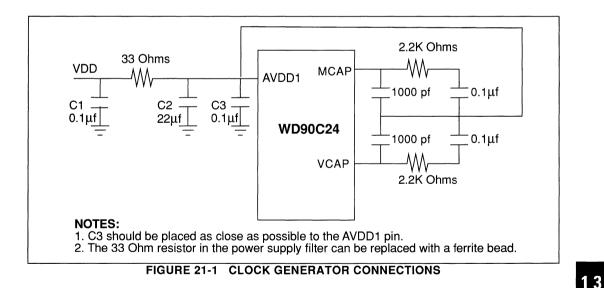

| 21.0         | EMBED                        | DED CLOC                          | K GENERATOR                                | 13-153 |  |  |  |

|              | 21. 1                        | FEATURE                           | S                                          | 13-153 |  |  |  |

|              | 21. 2                        | DESCRIPT                          | ΓΙΟΝ                                       | 13-154 |  |  |  |

|              |                              | 21.2.1                            | System Bus Interface                       | 13-154 |  |  |  |

|              |                              | 21.2.2                            | Firmware Interface                         | 13-154 |  |  |  |

|              |                              | 21.2.3                            | Analog Interface                           | 13-155 |  |  |  |

|              |                              | 21.2.4                            | External Clock Mode                        | 13-155 |  |  |  |

|              |                              | 21.2.5                            | ISO Support                                | 13-155 |  |  |  |

| 22.0<br>23.0 |                              |                                   | URATION REGISTERS                          |        |  |  |  |

| 2010         | 23. 1                        |                                   | FION                                       |        |  |  |  |

| 24.0         |                              |                                   | FICATIONS                                  |        |  |  |  |

| 25.0         |                              |                                   | RISTICS                                    |        |  |  |  |

|              | 25. 1                        |                                   | R DISTRIBUTION                             |        |  |  |  |

|              | 25. 2                        |                                   | . CLOCK DC CHARACTERISTICS                 |        |  |  |  |

|              | 25. 3                        | INTERNAL                          | CLOCK AC CHARACTERISTICS                   | 13-168 |  |  |  |

## LIST OF TABLES

# Table Title Page

| 4-1  | MEMORY MODE CONFIGURATION 13-1                          | 1 |

|------|---------------------------------------------------------|---|

| 4-2  | HOST INTERFACE 13-1                                     |   |

| 5-1  | CONFIGURATIONS AND MODES SUPPORTED 13-1                 | 2 |

| 6-1  | SIGNAL TO PIN LOCATION 13-1                             |   |

| 6-2  | HOST INTERFACE PIN SIGNAL DEFINITIONS 13-2              | 3 |

| 6-3  | BANK A VIDEO MEMORY SIGNALS 13-3                        | 1 |

| 6-4  | BANK B VIDEO MEMORY SIGNALS 13-3                        | 3 |

| 6-5  | INTERNAL DAC INTERFACE PINS 13-3                        |   |

| 6-6  | CLOCK GENERATION INTERFACE PIN TABLE 13-3               | 7 |

| 6-7  | PANEL INTERFACE PINS 13-3                               |   |

| 6-8  | POWER AND GROUND SIGNAL DEFINITIONS 13-4                | 4 |

| 6-9  | HOST INTERFACE PIN MULTIPLEXING 13-4                    | - |

| 6-10 | DISPLAY MEMORY INTERFACE PIN MULTIPLEXING               | 8 |

| 6-11 | RAMDAC PIN MULTIPLEXING 13-5                            | 0 |

| 6-12 | CLOCK SYNTHESIZER INTERFACE PIN MULTIPLEXING 13-5       | 0 |

| 6-13 | PANEL INTERFACE PIN MULTIPLEXING 13-5                   | 1 |

| 6-14 | POWER AND GROUND PIN MULTIPLEXING 13-5                  | 2 |

| 7-1  | VGA REGISTERS SUMMARY 13-5                              | 3 |

| 7-2  | SEQUENCER REGISTERS SUMMARY 13-5                        | 3 |

| 7-3  | CRT CONTROLLER REGISTERS SUMMARY 13-5                   | 4 |

| 7-4  | GRAPHICS CONTROLLER REGISTERS SUMMARY 13-5              | 4 |

| 7-5  | ATTRIBUTE CONTROLLER REGISTERS SUMMARY 13-5             | 4 |

| 7-6  | VIDEO PALETTE REGISTERS SUMMARY 13-5                    | 4 |

| 7-7  | GENERAL PARADISE REGISTERS 13-5                         | 5 |

| 7-8  | PARADISE EXTENDED REGISTERS SUMMARY 13-5                | 6 |

| 7-9  | FLAT PANEL PARADISE REGISTERS SUMMARY 13-5              | 7 |

| 7-10 | LOCAL BUS REGISTERS 13-5                                | 8 |

| 7-11 | COMPATIBILITY REGISTERS SUMMARY 13-6                    | 0 |

| 13-1 | IBM COMPATIBLE MEMORY ORGANIZATION - 256K TOTAL 13-8    | 6 |

| 13-2 | 64K/PLANE WD90C24 MEMORY ORGANIZATION - 256K TOTAL 13-8 | 6 |

| 13-3 | 128K PLANE WD9030 MEMORY ORGANIZATION - 1M TOTAL 13-8   | 7 |

| 13-4 | 256K PLANE MEMORY ORGANIZATION -1M TOTAL 13-8           | 7 |

| 14-1 | DISPLAY TYPE AND OPERATION SELECTION SUMMARY 13-11      | 2 |

| 17-1 | CURSOR REGISTERS 13-12                                  | 8 |

| 18-1 | BITBLT REGISTERS INDEX 13-13                            | 1 |

| 18-2 | RESULTS OF COMBINED SOURCE AND DESTINATION VALUES 13-13 | 7 |

| 18-3 | BASTER OPERATION CODE FUNCTIONS                         | 7 |

## LIST OF TABLES (Continued)

| Table | Title                                          | PaGE   |

|-------|------------------------------------------------|--------|

| 19-1  | BLT FUNCTIONS ALTERED BY LINE DRAW             | 13-141 |

| 21-1  | VCLK SELECTION                                 | 13-154 |

| 21-2  | MCLK SELECTION                                 | 13-154 |

| 22-1  | WD90C24 CONFIGURATION REGISTERS                | 13-156 |

| 22-2  | WD90C24 CONFIGURATION REGISTER BITS, CNF[31:0] | 13-157 |

| 23-1  | I/O MAPPING GROUPS                             | 13-159 |

| 25-1  | WD90C24 POWER DISTRIBUTION                     | 13-163 |

| 25-2  | DC POWER DISTRIBUTION                          | 13-164 |

| 25-3  | DC TIMING CHARACTERISTICS                      | 13-167 |

| 25-4  | AC TIMING CHARACTERISTICS                      | 13-168 |

## LIST OF FIGURES

#### Title Figure Page 2-1 2-2 5-1 5-2 SIMULTANEOUS DISPLAY CONFIGURATIO ...... 13-15 5-3 5-4 5-5 6-1 14-1 21-1 CLOCK GENERATOR CONNECTIONS 13-155 23-1 I/O MAPPING GROUP DIAGRAM 13-161 23-2

#### FEATURES

## 1.0 INTRODUCTION

## 1.1 FEATURES

- new frame buffer architecture that supports:

- simultaneous display and BITBLT without changing the performance.

- simultaneous display for all standard modes

- 16-bit true color resolution for both CRT and color flat panel display

- hardware window accelerator support (BITBLT)

- hardware line drawing (for both Bresenham and draw assist strip paint of Microsoft<sup>TM</sup> Window compatible)

- 256K color support for STN and TFT color LCDs

- single chip for 8 or 16 bit AT, MicroChannel, PI bus, and 32-bit local bus interface

- supports 16 or 32 bit memory interface

- 64K simultaneous color support for CRT, color DSTN LCD, and color TFT LCD

- direct interface to CRT with built-in RAMDAC

- direct interface to dual panel mono LCD, single panel color DSTN or TFT color LCD and plasma display

- 64 gray shades for monochrome STN LCD display

- 256 colors simultaneous display on one frame out of 256K possible choices of colors for CRTs, color DSTN LCD, and color TFT LCD display in none-true color mode

- on-chip programmable clock frequency synthesizer

- up to 80 Mhz video clock for the CRT display and up to 50 Mhz video clock for the flat panel display

- up to 50 Mhz memory clock

- 256K to 1 Mbytes of memory configuration with 64K x 16 or 256K x 16 memory

- with 256K DRAM, supports all IBM VGA modes for CRT and LCD display

- with more DRAM installed, supports up to 1024 x 768 x 256 colors for CRT display and up to 640 x 480 x 256 colors for LCD display

- 8- or 16- bit host data bus interface for CPU I/O and memory cycles.

- high performance graphic controller that supports high resolution graphics with up to

1024 x 768 x 256 color in CRT mode and 640 x 480 x 256 in flat panel mode

- operates with 5 volt and 3.3 volt power supplies

- 16-bit true color for CRT or flat panel display at up to 640 x 480 resolution to support 64K color simultaneous display on one frame for CRT, color DSTN LCD, and color TFT LCD displays

- true fast page display memory fetching for both graphic and text modes

- programmable virtual memory addressing for CPU memory address space

- four levels of write cache for zero wait state CPU memory write performance

- emulates planer mode addressing for packed pixel mode operation to achieve faster block transfers

- intelligent power management control:

- 3.3V Normal Mode 0.3 W Max

Display Idle 6.6 MW Max

PWRDN Mode 1.65 MW Max

- 5.0V Normal Mode 0.5 W Max Display Idle 30 MW Max PWRDN Mode 2.5 MW Max

- signature analyzer to help the IC and board level test for video data output from the chip

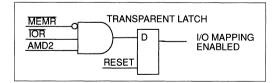

- I/O mapping allows the IC to enter a test mode, to help for quick open and short checks in board level test

- 208-pin EIAJ package

- 64 gray shades for monochrome flat panel displays

- on-chip PS/2-compatible RAMDAC with integral monitor detection logic

- on-chip WD90C63-compatible clock synthesizer with user programmable frequency for both video dot clock (VCLK) and video memory clock (MCLK)

- hardware support for the graphic cursor, which has 64 x 64 or 32 x 32 pattern sizes for CRT displays and a 32 x 32 pattern size for flat panel displays

- intelligent power management control to reduce the power requirement for the display subsystem

- drives directly without external components for all 640 x 480 (400) monochrome and color flat panel displays, such as STN, DSTN, TFT, and plasma displays

#### 1.2 GENERAL DESCRIPTION

The Western Digital WD90C24 is a 0.9 micron CMOS VLSI device that drives standard CRTs and flat panel displays. The WD90C24 allows simultaneous display for a CRT and a dual monochrome panel, or a CRT and signal color panel. It is backwards compatible with previous video standards such as MDA, EGA, CGA, Hercules, and AT&T 6300.

## 2.0 ARCHITECTURE

#### 2.1 INTRODUCTION

The WD90C24 is made up of the following major internal modules:

- CRT Controller

- Sequencer

- · Graphics Controller

- Attribute Controller

- Flat Panel Controller and Interface

- VLBI, or Local Bus Interface

- PI Bus Interface

- Hardware Cursor Controller

- Dithering Engine

- · Weighting and Mapping Logic

- RAMDAC, Clock Synthesizer

- Power Down Management

- BITBLT, or Window Accelerator Controller

- Line Drawing Engin

- Frame Buffer Controller for Simultaneous display on CRT and LCD Panel

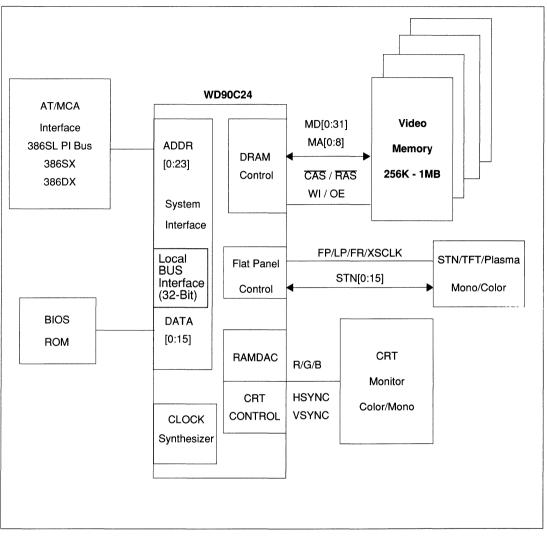

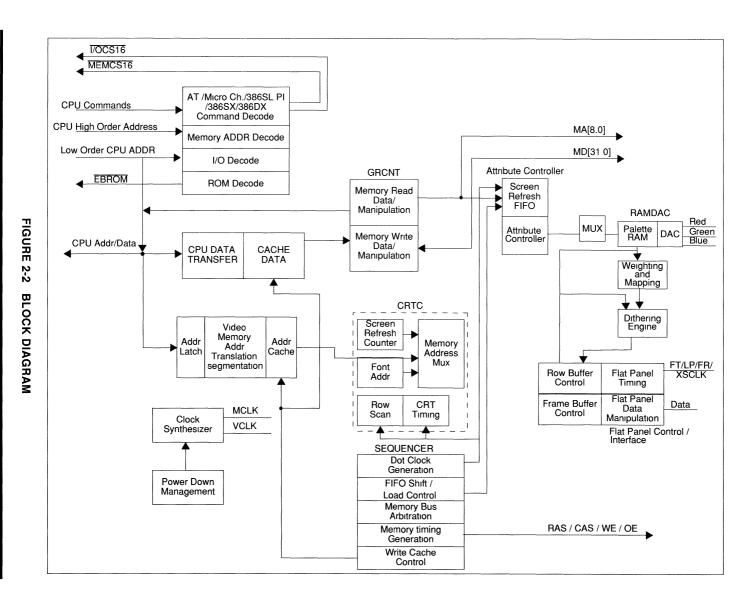

Each module described in detail in this section. Their relationships to each other are shown in Figure 2-1.

A 4-level deep write cache is used internally to achieve fast memory write. The zero wait state may be achieved for most memory write operations with a 32-bit video memory interface.

Utilize Fast Page mode memory fetching to improve memory bandwidth. A FIFO is also used internally to achieve the video display bandwidth necessary to interleave CPU accesses and display refresh cycle.

Weighting and Mapping Logic is used for color to gray scale mapping. A dithering engine works as a digital DAC to generate the gray scale level for monochrome flat panel displays, and generates colors for color flat panel display.

The internal Row Buffer supports the split screen panel display while driving the flat panel only. An external Frame Buffer, which resides in the offscreen memory of the display memory, supports split screen display while driving the CRT and flat panel at same time.

1

INTRODUCTION

FIGURE 2-1 ARCHITECTURE

13

## 2.2 CRT CONTROLLER MODULE

This module is used to perform the functions described below:

- generates horizontal sync (HSYNC) and vertical sync (VSYNC) for the CRT display monitor

- simultaneous CRT and dual flat panel display is performed using frame buffer architecture

- hidden display timing registers meet the fixed display timing for the flat panel display

- CRT display screen refresh is maintained for the various display modes defined by the BIOS ROM resident firmware

- performs video split screen refresh and screen size mapping

#### 2.3 SEQUENCER

The Sequencer Module provides the following functions:

- functions as a timing generator for the video memory cycles

- provides the character clock in the alphanumeric mode, and the dot clock in the graphics mode

- arbitrates between the video display refresh, memory refresh, and CRT access of the video memory for CRT only, flat panel only, or simultaneously CRT and single panel display

- arbitrates between the video display refresh, frame buffer access, memory refresh, and CRT access of the video memory for simultaneous CRT and dual panel display

- arbitrates cursor pattern access to the offscreen display memory when the hardware cursor is activated

- provides the write cache control for CPU memory write to the video display memory

## 2.4 GRAPHICS CONTROLLER

The Graphics Controller manipulates the data flow between the CPU and the video memory for CPU write and read cycles.

## 2.5 ATTRIBUTE CONTROLLER

The Attribute Controller allows the following functions:

- serializes the video memory data into a video data stream according to different display formats

- controls the following features in all display modes:

- blinking

- underlining

- text cursor

- pixel panning

- reverse video

- · background and foreground color

#### 2.6 FLAT PANEL CONTROLLER AND INTERFACE

The Flat Panel Controller and Interface performs the following functions:

- controls the video data flow after video data exits the RAMDAC's palette RAM, until the video data output to the flat panel interface

- generates the flat panel control signals:

- Frame Rate (FR)

- Frame Pulse (FP)

- Latch Pulse (LP)

- Shift Clock (XSCLK)

- Data Enable (ENABLE)

These signals are generated in different timing and polarity in order to drive different types of panels without external components

- split screen refresh for dual panel display and screen size mapping for both signal and dual panel displays

- controls the video data flow in and out of the frame buffer

- performs split screen refresh and screen size mapping using frame buffer architecture (screen mapping includes vertical expansion and auto-centering)

- controls the video data flow into and out of the row buffer (using row buffer architecture)

- generates different video data formats to drive different types of flat panels without external components

## 2.7 WEIGHT AND MAPPING LOGIC

For monochrome panel displays, this logic converts color information from the palette RAM into gray scale information using the following equation:

I =.3R +.59G +.11B.

Select from the following modes for monochrome display panels:

- Frame-Rate Modulation to select the shade code from the Mapping RAM, which is loaded with user-selected

- codes of shades with the optimum intensity

- 64-Shade Display Mode to select the shade from the Dithering Engine

- Pulse-Width Modulation to truncated or round off the information and send it to the panel directly

For color panel displays, the red, green, and blue color information that comes from the palette RAM is the code of the shade for each color.

Select from the following modes for color panel displays:

- Frame Rate Modulation to select the shade code is from the Dithering Engine

- Pulse-Width Modulation to truncate the R, G, B color information and send it to the panel directly

## 2.8 DITHERING ENGINE

The Dithering Engine uses a dithering pattern and frame rate modulation to constantly generate 64 gray shades. The dithering pattern for each shade is chosen so that it creates minimum flicker on the panel screen.

#### 2.9 HARDWARE WINDOW ACCELERATOR (BITBLT)

The WD90C24 was designed with hardware support for Microsoft Windows, resulting in accelerated Windows performance.

WD90C24 BITBLT increases speed. With BITBLT, blocks of pixels are transferred directly between regions of display memory and between display memory and system memory through an I/O port.

## 2.10 HARDWARE CURSOR CONTROLLER

The Hardware Cursor Controller provides up to a 64 x 64 pattern. Each pixel in the pattern is represented by two bits. These two bits determine how the cursor is displayed based on the color mode selected. The pattern is stored the off-screen display memory. The hardware cursor is controlled by the following registers:

- Cursor Control

- Cursor Pattern Address

- Cursor Primary Color

- Cursor Secondary Color

- Cursor Auxiliary Color

- Cursor Origin

- Cursor Display Address X

- Cursor Display Address Y

The Cursor Display Address is the location for the origin of the cursor on the display screen. The Cursor Pattern Address is the starting memory location where the cursor pattern is stored in the display memory.

The Cursor Origin and the Cursor Display Address are used to calculate the cursor's starting display address. The cursor pattern is displayed on the window and the controller clips off the pattern. The pattern fetching request is sent to the sequencer. The cursor pattern is displayed when the display location matches the cursor start location.

#### 2.11 RAMDAC

The on-chip RAMDAC is low-power, PS/2compatible with power-down control and built-in monitor detection logic with the following features:

- 3 256 x 6 RAMs as R, G, B

- color look-up table

- 3 6-bit DACs

- mask register

- supports 16-bit true color

The 16 bits of video data are formed by:

- 5 bits red

- 6 bits green

- 5 bits blue

- or

- 5 bits of each color with one bit ignored

When in true color mode, video data bypasses the color palette RAM but maintains a four pipe delay for the DAC output.

The LSB bit of the three DACs are forced to zero for 5-bit color configuration. The LSB bits of the Red DAC and Blue DAC are forced to zero for the 5-bit red, 6-bit green, and 5-bit blue configuration.

The DAC generates RS-343A/RS-170 compatible output and has +1/2 LSB of integral and differential linearity errors.

## 2.12 CLOCK SYNTHESIZER

The on-chip Clock Synthesizer is a dual clock generator for VGA applications. It simultaneously generates video memory clock (MCLK) and video dot clock (VCLK).

Both clock frequencies can be programed by the user and are derived from the 14.318Mhz system clock available in the IBM PC/XT/AT and PS/2 computer systems.

The clock synthesizer has power-down control to achieve a lower power requirement.

When programing a new clock frequency for both MCLK and VCLK, the Clock Synthesizer requires 50 ms to achieve a stable frequency. All the registers, palette RAM, and Mapping RAM must be reloaded after the clock frequency is stable.

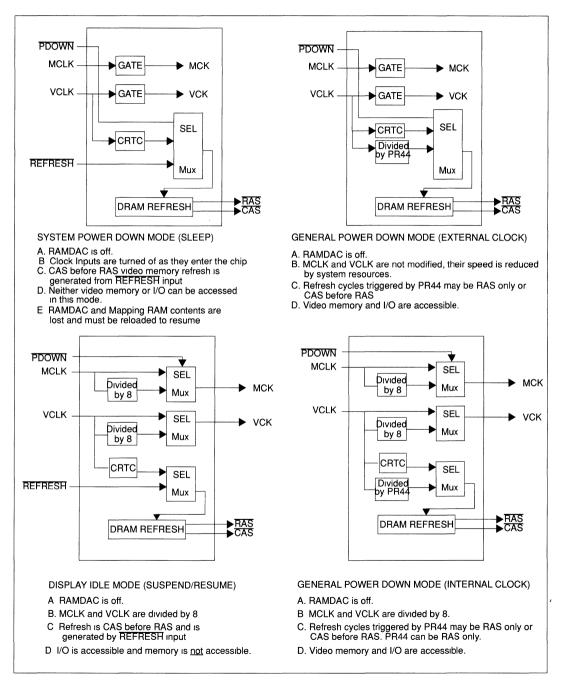

### 2.13 POWER DOWN MANAGEMENT

The WD90C24 provides two major power down modes:

- System Power-Down Mode

- Display Idle Mode

Each mode is described below.

#### 2.13.1 System Power-Down Mode

System power down mode is partitioned into three separate modes:

- Sleep Mode

- Suspend/Resume Mode

- Display Idle Mode

#### Sleep Mode

Sleep Mode is designed for when the system is not used for a long period of time and power savings is desired. Power consumption in this mode is less than 50uA. The disadvantage to Sleep Mode is that all registers and the RAM contents are lost after shutting down the  $V_{CC}$ , therefore a software routine is required to restore the registers and RAM value.

In Sleep Mode, all the  $V_{CC}$  pins are turned off except the PDOWN  $V_{CC}$ , which provides power for the logic generating memory refresh signals.

#### **Entering Sleep Mode:**

- Execute a power-down software routine that stores all data in the registers and RAM to the system main memory.

- The PDOWN signal is driven low by the power down control manager.

- After 300 ms, the power down control manager drives the RESET signal high.

- After another 300 ms, the power down control manager shuts off all the VCC pins except PDOWN V<sub>CC</sub> pin.

- During this time, WD90C24 is in the Sleep Mode. The logic powered by the PDOWN V<sub>CC</sub> receives the user-defined slow toggling signal from REFCKIN to generate CAS before RAS memory refresh cycles. The REFCKIN signal is the PCLK output in the normal active display

#### POWER DOWN MANAGEMENT

#### Leaving Sleep Mode:

- The power down control manager turns on the  $V_{CC}$  for Clock synthesizer, then all other  $V_{CC}{\rm 's.}$

- After 300 ms, the 14.318 Mhz system clock that drives the CKIN must be stable. The power down control manager drives the RESET signal low. The falling edge RESET wakes up the Clock Synthesizer.

- After another 100ns, the Clock Synthesizer generates stable default MCLK and VCLK signals. The power-down control manager then activates the software routine to restore all registers and RAM data.

- After another 300 ms, the power-down control manager drives the PDOWN high.

- After another 300 ms, the WD90C24 should be in the normal active display mode.

#### 2.13.2 Suspend/Resume Mode

This mode is designed for when the system is not used for a reasonably long time. All  $V_{CC}$ s are kept alive and the Clock Synthesizer is shut down. All registers and the RAM contents are maintained, therefore, minimum software control is required. In this mode, the following rules apply:

- The CPU can write to some registers but *not* to the RAM.

- The CPU can not read from WD90C24 and all outputs are tri-stated.

- All inputs are required to be in a known state and stable.

The only logic still toggling in this mode is the memory refresh generation logic. Power consumption is less than 1mA.

#### Entering Suspend/Resume Mode:

- The power down manager drives the PDOWN signal low to start entering the Suspend/ Resume Mode.

- After 10ms, the power-down control manager activates a software routine to write a "one" to the PR52 bit 7 to shut down the Clock synthesizer. This bit is power-up reset to zero.

- The WD90C24 then enters the Suspend/ Resume Mode. The memory refresh generation logic takes the slow toggling signal from REFCKIN pin and generate the CAS before RAS memory refresh cycles.

#### Leaving Suspend/Resume Mode:

- The power-down manager ensures that the 14.318 Mhz clock is stable, then activates a software routine to write the PR52 bit 7 to zero. This wakes up the Clock Synthesizer.

- After 100ms, the Clock Synthesizer generates stable VCLK and MCLK. The power-down manager then drives PDOWN high to leave the Suspend/Resume mode. The rising edge of PDOWN causes the MCLK and VCLK to start driving the WD90C24.

- After 300 ms, the WD90C24 is in normal active display mode.

#### 2.13.3 Display Idle Mode

Display Idle Mode is designed for when the system is not used for a short period of time. In this mode all the  $V_{CC}$ s and the Clock Synthesizer remain on. The MCLK and VCLK are slowed down by a user programmable frequency. In this mode:

- the CPU can access all the registers, RAM and display memory

- the DAC and the LCD logic is shut down

The memory refresh cycle is generated by the same logic for normal display mode but with slower MCLK and VCLK. By programming the memory refresh period and memory refresh cycles per horizontal line the user-defined memory refresh cycle can be achieved. In this mode, these two registers override the horizontal total register and memory refresh cycles per horizontal line register.

#### Entering Display Idle Mode:

The power down manager drives the PDOWN signal low to enter Display Idle Mode. The falling edge of PDOWN causes the MCLK and VCLK switch to program slower frequency. The WD90C24 enters the Display Idle Mode immediately.

#### Leaving Display Idle Mode:

The power-down manager drives the PDOWN signal high. The rising edge of PDOWN causes MCLK and VCLK to switch to the normal frequency. The WD90C24 is back to the normal display mode.

WD90C24

ARCHITECTURE POWER DOWN MANAGEMENT

13-8

$\gg$

#### INTRODUCTION

## 3.0 INTERFACES

#### 3.1 INTRODUCTION

The WD90C24's five major interfaces are described in this section.

- CPU and BIOS ROM Interface

- DRAM Display Memory Interface

- CRT Display Interface

- Flat Panel Display Interface

#### 3.2 CPU AND BIOS ROM INTERFACE

The WD90C24's VGA subsystem CPU and BIOS ROM interface operate in the following bus configurations:

- PC/XT/AT bus for CPU and BIOS ROM I/F

- IBM MicroChannel bus

- Direct interface with INTEL 386SL PI bus

- 386SX local bus

- 386 DX local bus

The selection of the mode depends on the setting of configuration register bits CNF(14), CNF(13), and CNF(2). These settings are determined upon power-up reset, and is described in the section called "Configurations".

The IOCS16 and MEMCS16 signals are generated to indicate 16-bit operation.

Interface features are as follows:

- · minimal use of external circuitry

- provides all signals, decodes all memory and I/O addresses to interface with any of the bus configurations in 8- or 16-bit mode.

- decoding for video BIOS ROM while in extension card application (8-bit operation only)

- reduced CPU wait states while writing to video memory with use of a display memory data and address write cache that hold CPU write data until it can be transferred to the display memory

- improved performance of CPU display memory access -- PROA and PROB registers may be addressed indirectly

- improved performance of CPU display memory access -- 32-bit memory data latch is addressable by the I/O port

- emulation of the planer mode operation in pack pixel mode to improve CPU block transfer speed

- 16 segments of 1 Mbyte virtual memory addressing range or 32 segments of 512Kbyte virtual memory addressing range for flexibility in memory allocation

#### 3.3 DRAM INTERFACE

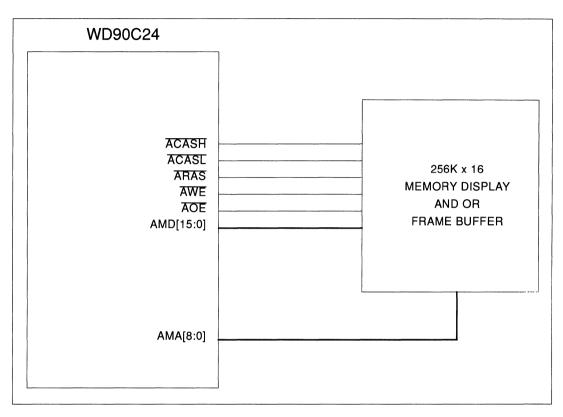

For a16-bit memory interface the following DRAM configurations can be used:

- 1 256K x 16 DRAM

- 2 256K x 16 DRAMs

- 3 64K x 16 DRAMs

For a 32-bit memory interface the following DRAM configurations can be used:

- 4 64K x 16 DRAMs

- 2 256K x 16 DRAMs

Refer to Table 5-1 for a summary of configurations.

In all cases, WD90C24 uses DRAM fast page mode for optimum performance.

#### 3.3.1 Configurations

In the minimum configuration, 2 64 x 16 DRAMS, the WD90C24 can support all standard IBM VGA modes.

When additional DRAMs are installed, the WD90C24 is capable of supporting high color resolution video modes, up to 1024 x 768 x 256 colors, non-interlaced.

#### 3.3.2 Features

- supports 60ns/70ns/80ns/100ns DRAMs with the dedicated MCLOCK which can operate from 32 MHz to 50 MHz

- fast page DRAM timing is used for all CPU access, graphics display and text display (a choice of page mode and non-page mode operation is provided to access fonts in text modes)

- generates CAS before RAS DRAM refresh for the display memory

#### 3.4 CRT DISPLAY INTERFACE

- on-chip RAMDAC provides the RED, GREEN, and BLUE signals directly to the analog CRT monitor

- provides HSYNC and VSYNC signals to control the monitor

- allows use of an external RAMDAC to drive the CRT

- supports Bt/471/478/476 compatible RAMDAC interface

#### 3.5 FLAT PANEL INTERFACE

- direct interface with 640 x 480(400) STN, DSTN, TFT 1024 x 768 LCD, and plasma panels

- flat panel interface signals change function to support the panel type chosen

- programmable timing and polarity for the flat panel control signals to meet the requirements of different panels

- video data groupings to meet the requirement for different panels

- controller supplies 8 pixel per shift clock with 8 bits of data for monochrome display with STN panel

- controller supplies one pixel per shift clock with 4 bit of data for 16 shade for plasma panel

- controller supplies 3-bit(1 pixel per shift clock) interface, 8-bit(2 and 2/3 pixel per shift clock) interface, and 16-bit(5 and 1/3 pixel per shift clock) interface for color display with STN panel

- controller supplies 3-bit, 6-bit, 9-bit, 18-bit (all are one pixel per shift clock) interface for TFT panel.

HOST INTERFACE

## 4.0 MEMORY MODE CONFIGURATION

The following table defines how to set up each register for the desired memory configuration (refer to Pages 12 through17 for additional information).

|         | MEMORY                                         |     |      |      |      |

|---------|------------------------------------------------|-----|------|------|------|

|         | DRAM                                           | CNF | CNF  | CNF  |      |

| MODE    | TYPE                                           | QTY | (16) | (14) | (13) |

| 1       | 256Kx16                                        | 1   | 1    | 0    | 1    |

| 2       | 256Kx16                                        | 2   | 1    | 0    | 0    |

|         | 256Kx16                                        | 1   |      |      |      |

| 3       | and<br>64Kx16                                  | 1   | 1    | 1    | 1    |

| 4       | 64Kx16                                         | 4   | 0    | 0    | 1    |

| 5       | 64Kx16                                         | 3   | 0    | 0    | 0    |

| NOTE: C | <b>NOTE:</b> CNF(16), CNF(14), and CNF(13) are |     |      |      |      |

readable via PR 11 register bits 7, 6, and 5, respectively (refer to Section 22).

#### TABLE 4-1 MEMORY MODE CONFIGURA-TION

In memory modes 1 and 5, the display memory data path is always 16 bits wide.

Memory modes 2, 3, and 4 should be used with a 32-bit wide display memory data path, unless one of the DRAM banks is used as the LCD panel frame buffer. For example, one DRAM bank is used as the LCD panel frame buffer when simultaneous display with an LCD panel and CRT is used, and also when 16-bit STN color dual panel is used.

By default, memory modes 2, 3, and 4 use a 32bit data path, unless one of the following conditions have been set up to use a 16-bit data path. However, only one of the following conditions is required to setup a 16-bit video memory data path.

- 1. PR30 register bit 5 is set to 1.

- 2. PR19 register bits 4 and 5 are both set to 1, which is used for simultaneous display.

- 3. Configure for memory mode 1 (refer to Table 5-1.

- 4. Configure for memory mode 5 (refer to Table 5-1.

### 4.1 HOST INTERFACE

The following table lists the conditions required for each type of host interface.

| CNF(17) | CNF(2) | HOST MODES          |

|---------|--------|---------------------|

| 0       | 0      | MicroChannel Bus    |

| 0       | 1      | AT Bus              |

| 1       | 0      | PI (also AT or ISA) |

| 1       | 1      | Local Bus           |

#### TABLE 4-2 HOST INTERFACE

## 5.0 CONFIGURATIONS

#### 5.1 INTRODUCTION

The WD90C24 can be configured in five different ways. The following table summarizes the configurations. Illustrations are also provided:

- Single-Memory Interface Configuration

- 1 Megabyte Memory Configuration

- Simultaneous Display Configuration

- 512 KB High-Performance Configuration

- 256 KB with Simultaneous Display Configuration

| MODES                  | <b>1</b> <sup>2</sup> | <b>2</b> <sup>1</sup> | <b>3</b> <sup>1</sup> | <b>4</b> <sup>1</sup> | <b>5</b> <sup>2</sup> |

|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 1024 x 768 x 256       |                       | C,L                   |                       |                       |                       |

| 1024 x 768 x 16        | C,L                   | S,C,L                 | C,L                   | C,L                   |                       |

| 800 x 600 x 256        | С                     | С                     | С                     | С                     |                       |

| 800 x 600 x 16         | С                     | С                     | С                     | С                     | С                     |

| 640 x 480 x 256        | C,L                   | S,C,L                 | S,C,L                 | C,L                   |                       |

| 640 x 480 x 16         | S,C,L                 | S,C,L                 | S,C,L                 | S,C,L                 | S,C,L                 |

| 640 x 400 x 256        | C,L                   | S,C,L                 | S,C,L                 | S,C,L                 | S,C,L                 |

| All IBM Standard Modes | S,C,L                 | S,C,L                 | S,C,L                 | S,C,L                 | S,C,L                 |

#### NOTES

S = Simultaneous Display

C = CRT Only

L = LCD Only

<sup>1</sup>In C and L modes, has 32-bit interface.

<sup>2</sup>In C and L modes, has 16-bit interface.

| TABLE 5-1 CONFIGURATIONS AND MODES SUPPORTED | TABLE 5-1 | CONFIGURATIONS | AND MODES | SUPPORTED |

|----------------------------------------------|-----------|----------------|-----------|-----------|

|----------------------------------------------|-----------|----------------|-----------|-----------|

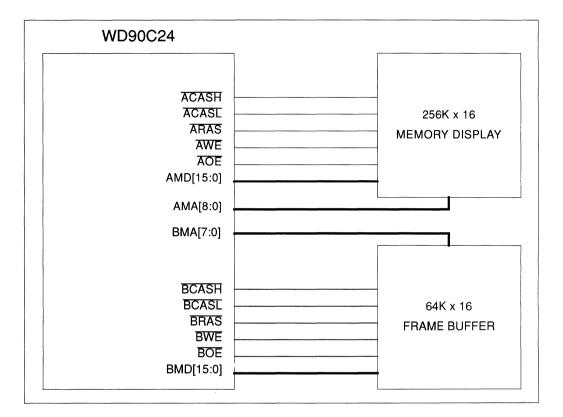

SINGLE MEMORY INTERFACE CONFIGURATION

#### 5.2 SINGLE MEMORY INTERFACE CONFIGURATION

#### FIGURE 5-1 SINGLE MEMORY INTERFACE CONFIGURATION

*1*/,

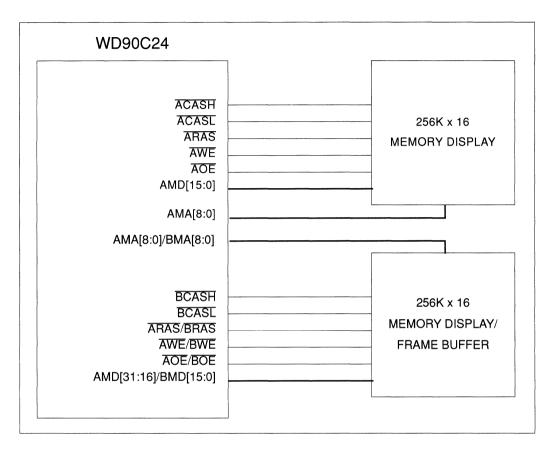

1 MB MEMORY CONFIGURATION

#### 5.3 1 MB MEMORY CONFIGURATION

#### FIGURE 5-2 1 MB MEMORY CONFIGURATION

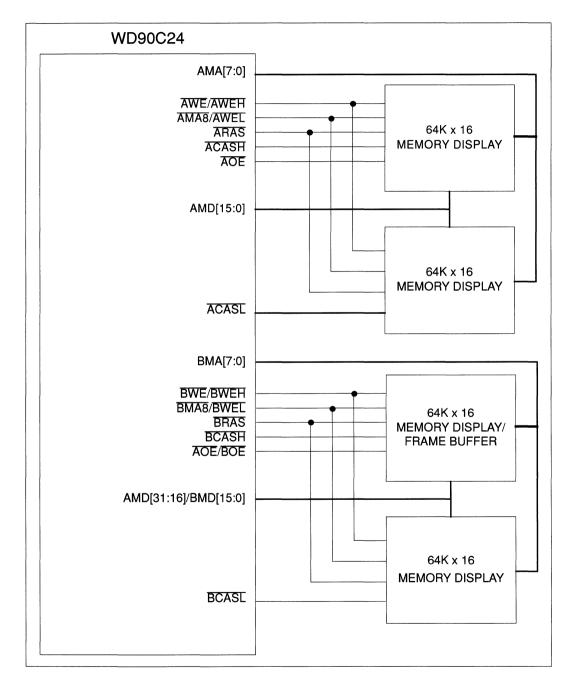

SIMULTANEOUS DISPLAY CONFIGURATION

#### 5.4 SIMULTANEOUS DISPLAY CONFIGURATION

#### FIGURE 5-3 SIMULTANEOUS DISPLAY CONFIGURATION

13

1/2

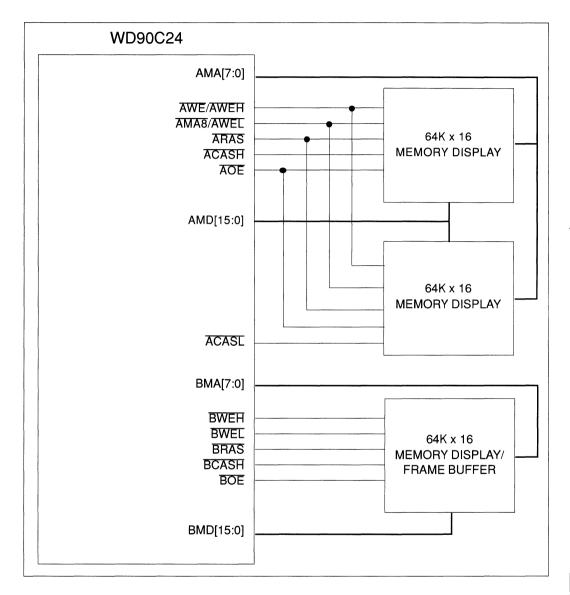

512 KB HIGH-PERFORMANCE CONFIGURATION

#### 5.5 512 KB HIGH-PERFORMANCE CONFIGURATION

#### FIGURE 5-4 512 KB HIGH-PERFORMANCE CONFIGURATION

256 KB WITH SIMULTANEOUS DISPLAY CONFIGURATION

#### 5.6 256 KB WITH SIMULTANEOUS DISPLAY CONFIGURATION

#### FIGURE 5-5 256 KB WITH SIMULTANEOUS DISPLAY CONFIGURATION

13

## 6.0 SIGNAL DESCRIPTIONS

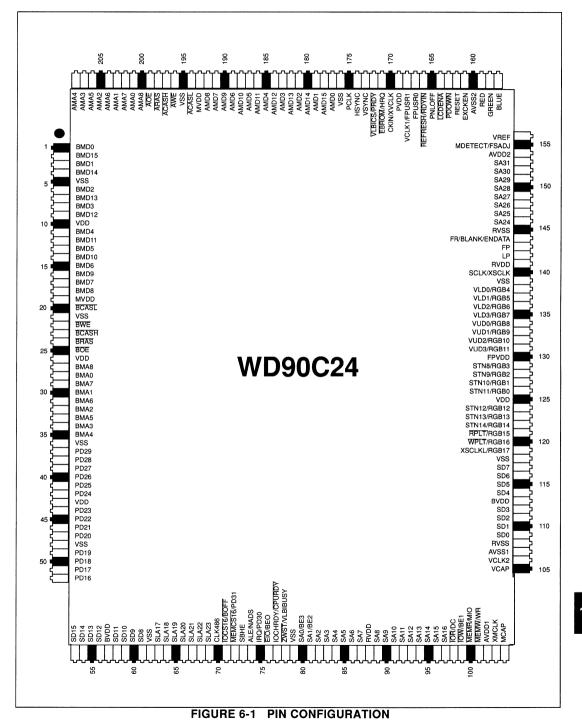

This section contains detailed information concerning signals and pin outs for the WD90C24 controller 208-pin package.

#### 6.1 INTRODUCTION

This section contains the following information:

- Signal Mnemonic to Pin Location Table

- Signal and Pin Configuration Diagram

- Detailed Signal Descriptions

- Pin Multiplexing Reference Tables

#### 6.2 SIGNAL MNEMONIC TO PIN LOCATION

| 1.       | BMD0               | 33. | BMA5 <sup>1</sup>  | 65. | SLA19 <sup>2</sup>    | 97.  | SA16 <sup>2</sup>             |

|----------|--------------------|-----|--------------------|-----|-----------------------|------|-------------------------------|

| 2.       | BMD15              | 34. | BMA3 <sup>1</sup>  | 66. | SLA20 <sup>2</sup>    | 98.  | IOR/DC <sup>2</sup>           |

| 3.       | BMD1               | 35. | BMA4 <sup>1</sup>  | 67. | SLA21 <sup>2</sup>    | 99.  | IOW/BE1 <sup>2</sup>          |

| 4.       | BMD14              | 36. | VSS <sup>3</sup>   | 68. | SLA22 <sup>2</sup>    | 100. | MEMR/MIO <sup>2</sup>         |

| 5.       | VSS <sup>3</sup>   | 37. | PD29               | 69. | SLA23 <sup>2</sup>    | 101. | MEMW/WR <sup>2</sup>          |

| 6.       | BMD2               | 38. | PD28               | 70. | CLK486 <sup>2</sup>   | 102. | AVDD1 <sup>3</sup>            |

| 7.       | BMD13              | 39. | PD27               | 71. | IOCS16/BOFF           | 103. | XMCLK <sup>2</sup>            |

|          |                    |     |                    | 72. | MEMCS16/              |      |                               |

| 8.       | BMD3               | 40. | PD26               |     | PD31                  | 104. | MCAP <sup>2</sup>             |

|          |                    |     |                    | 73. | SBHE/                 |      | _                             |

| 9.       | BMD12              | 41. | PD25               |     | CPURESET <sup>2</sup> | 105. | VCAP <sup>2</sup>             |

| 10.      | VDD <sup>3</sup>   | 42. | PD24               | 74. | ALE/NADS <sup>2</sup> | 106. | VCLK2 <sup>2</sup>            |

| 11.      | BMD4               | 43. | VDD <sup>3</sup>   | 75. | IRQ/PD30              | 107. | AVSS1 <sup>3</sup>            |

| 12.      | BMD11              | 44. | PD23               | 76. | EIO/BE0 <sup>2</sup>  | 108. | RVSS <sup>3</sup>             |

|          |                    |     |                    | 77. | IOCHRDY/              |      |                               |

| 13.      | BMD5               | 45. | PD22               |     | CPURDY                | 109. | SD0                           |

|          | DMD                |     |                    | 78. | ZWST/                 |      | 0.5.4                         |

| 14.      | BMD10              | 46. | PD21               |     | VLBIBUSY <sup>1</sup> | 110. | SD1                           |

| 15.      | BMD6               | 47. | PD20               | 79. | VSS <sup>3</sup>      | 111. | SD2                           |

| 16.      | BMD9               | 48. | VSS <sup>3</sup>   | 80. | SA0/BE3 <sup>2</sup>  | 112. | SD3                           |

| 17.      | BMD7               | 49. | PD19               | 81. | SA1/BE2 <sup>2</sup>  | 113. | BVDD <sup>3</sup>             |

| 18.      | BMD8               | 50. | PD18               | 82. | SA2 <sup>2</sup>      | 114. | SD4                           |

| 19.      | MVDD <sup>3</sup>  | 51. | PD17               | 83. | SA3 <sup>2</sup>      | 115. | SD5                           |

| 20.      | BCASL <sup>1</sup> | 52. | PD16               | 84. | SA4 <sup>2</sup>      | 116. | SD6                           |

| 21.      | VSS <sup>3</sup>   | 53. | SD15               | 85. | SA5 <sup>2</sup>      | 117. | SD7                           |

| 22.      | BWE <sup>1</sup>   | 54. | SD14               | 86. | SA6 <sup>2</sup>      | 118. | VSS <sup>3</sup>              |

|          | <del></del> 1      |     |                    |     | 2                     | 119. | XSCLKL <sup>1</sup> /         |

| 23.      | BCASH <sup>1</sup> | 55. | SD13               | 87. | SA7 <sup>2</sup>      |      | RGB17                         |

| 24.      | BRAS <sup>1</sup>  | 56. | SD12               | 88. | RVDD <sup>3</sup>     | 120. | WPLT <sup>1</sup> /RGB16      |

| 25.      | BOE <sup>1</sup>   | 57. | BVDD <sup>3</sup>  | 89. | SA8 <sup>2</sup>      | 121. | RPLT <sup>1</sup> /RGB15      |

|          | VDD3               | 50  | 0044               |     | 0.4.02                | 122. | STN14 <sup>1</sup> /          |

| 26.      | VDD <sup>3</sup>   | 58. | SD11               | 90. | SA9 <sup>2</sup>      |      | RGB14                         |

| 27.      | BMA8 <sup>1</sup>  | 59. | SD10               | 91. | SA10 <sup>2</sup>     | 123. | STN13 <sup>1</sup> /<br>RGB13 |

| <u> </u> | DIVIAO             | 59. | 3010               | 31. | JATU                  | 124. | STN12 <sup>1</sup> /          |

| 28.      | BMA0 <sup>1</sup>  | 60. | SD9                | 92. | SA11 <sup>2</sup>     | 124. | RGB12                         |

| 29.      | BMA7 <sup>1</sup>  | 61. | SD8                | 93. | SA12 <sup>2</sup>     | 125. | VDD <sup>3</sup>              |

| 30.      | BMA1 <sup>1</sup>  | 62. | VSS <sup>3</sup>   | 94. | SA13 <sup>2</sup>     | 126. | STN11 <sup>1</sup> /RGB0      |

| 31.      | BMA6 <sup>1</sup>  | 63. | SLA17 <sup>2</sup> | 95. | SA14 <sup>2</sup>     | 127. | STN10 <sup>1</sup> /RGB1      |

| 32.      | BMA2 <sup>1</sup>  | 64. | SLA18 <sup>2</sup> | 96. | SA15 <sup>2</sup>     | 128. | STN9 <sup>1</sup> /RGB2       |

|          |                    |     |                    | 30. | 0,110                 | 120. |                               |

NOTE: Refer to notes at the end of this table.

TABLE 6-1 SIGNAL TO PIN LOCATION

13

SIGNAL MNEMONIC TO PIN LOCATION

| 129. | STN8 <sup>1</sup> /RGB3 | 149. | SA27 <sup>2</sup>              | 169. | PVDD <sup>3</sup>        | 189. | AMD6               |

|------|-------------------------|------|--------------------------------|------|--------------------------|------|--------------------|

| 130. | FPVDD <sup>3</sup>      | 150. | SA28 <sup>2</sup>              | 170. | CKIN/XVCLK <sup>2</sup>  | 190. | AMD9               |

| 131. | VUD3/RGB11              | 151. | SA29 <sup>2</sup>              | 171. | EBROM/HRQ                | 191. | AMD7               |

| 132. | VUD2/RGB10              | 152. | SA30 <sup>2</sup>              | 172. | VLBICS/PRDY <sup>1</sup> | 192. | AMD8               |

| 133. | VUD1/RGB9               | 153. | SA31 <sup>2</sup>              | 173. | VSYNC <sup>1</sup>       | 193. | MVDD <sup>3</sup>  |

| 134. | VUD0/RGB8               | 154. | AVDD2 <sup>3</sup>             | 174. | HSYNC <sup>1</sup>       | 194. | ACASL <sup>1</sup> |

| 135. | VLD3/RGB7               | 155. | MDETECT/<br>FSADJ <sup>2</sup> | 175. | PCLK <sup>1</sup>        | 195. | VSS <sup>3</sup>   |

| 136. | VLD2/RGB6               | 156. | VREF <sup>2</sup>              | 176. | VSS <sup>3</sup>         | 196. | AWE <sup>1</sup>   |

| 137. | VLD1/RGB5               | 157. | BLUE <sup>1</sup>              | 177. | AMD0                     | 197. | ACASH <sup>1</sup> |

| 138. | VLD0/RGB4               | 158. | GREEN <sup>1</sup>             | 178. | AMD15                    | 198. | ARAS <sup>1</sup>  |

| 139. | VSS <sup>3</sup>        | 159. | RED <sup>1</sup>               | 179. | AMD1                     | 199. | AOE <sup>1</sup>   |

| 140. | SCLK/XSCLK <sup>1</sup> | 160. | AVSS2 <sup>3</sup>             | 180. | AMD14                    | 200. | AMA8 <sup>1</sup>  |

| 141. | RVDD <sup>3</sup>       | 161. | EXCKEN <sup>2</sup>            | 181. | AMD2                     | 201. | AMA0 <sup>1</sup>  |

| 142. | LP <sup>1</sup>         | 162. | RESET/<br>SYSRES <sup>2</sup>  | 182. | AMD13                    | 202. | AMA7 <sup>1</sup>  |

| 143. | FP <sup>1</sup>         | 163. | PDOWN <sup>2</sup>             | 183. | AMD3                     | 203. | AMA1 <sup>1</sup>  |

| 144. | FR/BLANK/<br>ENDATA     | 164. | LCDENA <sup>1</sup>            | 184. | AMD12                    | 204. | AMA6 <sup>1</sup>  |

| 145. | RVSS <sup>3</sup>       | 165. | PNLOFF <sup>1</sup>            | 185. | AMD4                     | 205. | AMA2 <sup>1</sup>  |

| 146. | SA24/VGACS <sup>2</sup> | 166. | REFRESH/<br>RDYIN <sup>2</sup> | 186. | AMD11                    | 206. | AMA5 <sup>1</sup>  |

| 147. | SA25 <sup>2</sup>       | 167. | FPUSR0 <sup>1</sup>            | 187. | AMD5                     | 207. | AMA3 <sup>1</sup>  |

| 148. | SA26 <sup>2</sup>       | 168. | VCLK1/FPUSR1                   | 188. | AMD10                    | 208. | AMA4 <sup>1</sup>  |

|      |                         |      |                                |      |                          |      |                    |

## NOTES:

<sup>1</sup> Indicates output only signal names.

<sup>2</sup> Indicates input only signal names.

<sup>3</sup> Indicates VDD and VSS supply pins.

<sup>4</sup> Indicates proprietary test pins for internal use only.

Signal names not otherwise indicated are input/output.

## TABLE 6-1 SIGNAL TO PIN LOCATIONS

#### SIGNAL MNEMONIC TO PIN LOCATION

13

#### 6.3 DETAILED SIGNAL DESCRIPTIONS

The following tables provide detailed signal descriptions for the WD90C24 controller 208-pin package. The signal descriptions are listed by the pin number and mnemonic given in Table 6-1. The definitions are listed in pin number order, as far as practical, within functional groups. Some signal definitions may appear in more than one functional group, if applicable, to aid the user in quick recovery of information for a particular group. The functional groups are listed below:

- Host Interface Pins

- Display Buffer Memory Interface Pins

- RAM DAC/CRT Interface Pins

- Clock Generation Interface Pins

- Panel Interface Pins

- Power and Ground Pins

Where more than one signal name is indicated on the same pin, the signal names are separated by a virgule (/) in Table 6-1. The pin usage, as described in Table 6-2, changes for each signal name depending upon the bus interface as follows:

1. The letters AT in the bus column indicate an Industry Standard Architecture (ISA) bus compatible signal. The terms AT bus and ISA bus are used interchangeably unless otherwise indicated.

- The letters MC in the bus column indicate an IBM MicroChannel bus compatible signal.

- 3. The letters PI in the bus column indicate an Intel 386SL Peripheral Interface bus compatible signal.

- 4. The letters LOC in the bus column indicate a local bus compatible signal.

#### NOTE

The PI bus does not use MEMCS16 or IOCS16 type signals and cannot distinguish between 8-bit and 16-bit transfers. The WD90C24 uses PI bus signals for I/O transfers and memory cycles. Therefore, if there is a coresident VGA device, it must use the ISA bus for I/O transfers and memory cycles. Because the IOR, IOW, and AEN (EION) signals are not multiplexed with the PI bus. these lines should not be connected on the WD90C24 controller.

DETAILED SIGNAL DESCRIPTIONS

#### 6.3.1 Host Interface Pin Definitions

| PIN<br>NO. | MNEMONIC                          | BUS            | TYPE                            | DESCRIPTION                                                                                                                                                                                                                                                 |

|------------|-----------------------------------|----------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71         | 71 IOCS16                         |                | Active Low<br>Output            | I/O Chip Select 16 Bits<br>In AT mode, this signal used to respond to the host to allow<br>16-bit access to the I/O bus.                                                                                                                                    |

|            |                                   | PI             | Active Low<br>Output            | I/O Chip Select 16 Bits<br>In PI mode, since no 8-bit access will occur, this signal<br>should be connected to Vss so it is always low.                                                                                                                     |

|            | BOFF                              | LOC            | Active Low<br>Output            | <b>Bus Backoff</b><br>Connects to the 80486 BOFF pin. When active low, the<br>80486 retracts its last cycle and enables other masters to<br>control the local bus. Its operation is similar to a read cycle<br>for the VGA when the write buffers are full. |

|            | CDSETUP                           | MC             | Active Low<br>Input             | <b>Card Setup</b><br>This signal is driven by the host to individually select chan-<br>nel connector slots during system configuration.                                                                                                                     |

| 72         | 72 MEMCS16 AT Active Lo<br>Output |                | Active Low<br>Output            | <b>Memory Chip Select 16 Bits</b><br>This line is used to respond to the host to enable 16-bit<br>video memory data transfer.                                                                                                                               |

|            | PM/IO                             | PI             | Active Low<br>Input             | <b>PI Bus Memory or I/O</b><br>Indicates the type of cycle currently executing on the PI<br>bus. When high, the cycle is a memory operation, and<br>when low the cycle is an Input/Output operation.                                                        |

|            | PD31                              | LOC            | Active High<br>Input/<br>Output | <b>CPU Data Bus Bit 32</b><br>Provides bit 32 on the Local bus. This bit is combined with<br>PD30 (pin 75), PD29:PD16, and SD15:SD0 to provide a<br>32-bit Local Data bus.                                                                                  |

|            | CDDS16                            | MC             | Active Low<br>Output            | <b>Card Data Size 16 Bits</b><br>Indicates that a 16-bit resource is available at the current<br>address.                                                                                                                                                   |

| 73         | SBHE                              | AT<br>PI<br>MC | Active High<br>Input            | System Byte High Enable<br>Indicates a data transfer on the upper byte of the data bus<br>(SD15:8).                                                                                                                                                         |

|            | CPURESET                          |                | Active High<br>Input            | CPU Reset<br>Local bus reset operation similar to AT bus RESET.                                                                                                                                                                                             |

TABLE 6-2 HOST INTERFACE PIN SIGNAL DEFINITIONS

| PIN<br>NO. | MNEMONIC | BUS | ТҮРЕ                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                        |