WD90C20, WD90C20A

VGA Flat Panel

Display Controller

# **TABLE OF CONTENTS**

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | Page                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------|

| 1.0     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 11-1<br>11-1<br>11-1                                                                                              |

| 2.0     | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | 11-2<br>11-2                                                                                                      |

| 3.0     | FLAT PANEL SUPPORT CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | 11-6                                                                                                              |

| 4.0     | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 11-9                                                                                                              |

| 5.0     | WD90C20 REGISTERS         5.1       VGA Registers Summary         5.2       Compatibility Registers         5.3       VGA Registers         5.4       General Registers         5.4.1       Miscellaneous Output Register, R Port = 3CC, W         5.4.2       Input Status Register 0,Read Only Port = 3C2         5.4.3       Input Status Register 1,Read Only Port = 3?A         5.4.4       Feature Control Register, Read Port = 3CA, Write         5.5       Sequencer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Port = 3C2 | 11-18<br>11-19<br>11-20<br>11-20<br>11-21<br>11-21<br>11-22<br>11-22                                              |

|         | <ul> <li>5.5.1 Sequencer Index Register, Read/Write Port = 3C4</li> <li>5.5.2 Reset Register, Read/Write Port = 3C5, Index = 0</li> <li>5.5.3 Clocking Mode Register, Read/Write Port = 3C5, I</li> <li>5.5.5 Character Map Select Register, R/W Port = 3C5, I</li> <li>5.5.6 Memory Mode Register, Read/Write Port = 3C5, I</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0H         | 11-23<br>11-23<br>11-23<br>11-24<br>11-25                                                                         |

|         | <ul> <li>5.6 CRT Controller Registers</li> <li>5.6.1 CRT Address Register, Read/Write Port = 3?4</li> <li>5.6.2 Horizontal Total Register, Read/Write Port = 3?5,</li> <li>5.6.3 Horizontal Display Enable End Register R/W Port</li> <li>5.6.4 Start Horizontal Blanking Register, R/W Port = 3?5,</li> <li>5.6.5 End Horizontal Blanking, Read/Write Port = 3?5,</li> <li>5.6.6 Start Horizontal Retrace Pulse Reg R/W Port=3?5,</li> <li>5.6.7 End Horizontal Retrace Register, R/W Port = 3?5,</li> <li>5.6.8 Vertical Total Register, Read/Write Port = 3?5,</li> <li>5.6.9 Overflow Vertical Register Read/Write Port = 3?5,</li> <li>5.6.10 Preset Row Scan Register, Read/Write Port = 3?5,</li> <li>5.6.11 Maximum Scan Line Register, Read/Write Port = 3?5,</li> <li>5.6.12 Cursor Start Register, Read/Write Port = 3?5,</li> <li>5.6.13 Cursor End Register, Read/Write, Port = 3?5,</li> <li>5.6.14 Start Address High Register, R/W Port = 3?5H, Inde</li> <li>5.6.15 Start Address Low Register, R/W Port = 3?5H, Inde</li> <li>5.6.16 Cursor Location High Register, R/W Port = 3?5H,</li> </ul> | Index=00H  | 11-27<br>11-27<br>11-27<br>11-27<br>11-28<br>11-28<br>11-28<br>11-29<br>11-29<br>11-30<br>11-30<br>11-31<br>11-31 |

1

| Section | Title |           |                                                                       | Page    |

|---------|-------|-----------|-----------------------------------------------------------------------|---------|

|         |       | 5.6.17    | Cursor Location Low Register, R/W Port = 3?5, Index = 0FH             | . 11-31 |

|         |       | 5.6.18    | Vertical Retrace Start Register, R/W Port = 3?5, Index=10H            | . 11-32 |

|         |       | 5.6.19    | Vertical Retrace End Register, R/W Port = 3?5, Index = 11H            | . 11-32 |

|         |       | 5.6.20    | Vertical Display Enable End Register, R/W Port = 3?5, I=12H           | . 11-33 |

|         |       | 5.6.21    | Offset Register, Read/Write Port = 3?5, Index = 13H                   | . 11-33 |

|         |       | 5.6.22    | Underline Location Register, Read/Write Port = 3?5, Index = 14H       | . 11-33 |

|         |       | 5.6.23    | Start Vertical Blank Register, Read/Write Port = 3?5, Index =15H      | . 11-34 |

|         |       | 5.6.24    | End Vertical Blank Register, Read/write Port=3?5, Index=16H .         | . 11-34 |

|         |       | 5.6.25    | CRT Mode Control Register, Read/Write Port = 3?5, Index = 17H         | . 11-34 |

|         |       | 5.6.26    | Line Compare Register, Read/Write Port = 3?5, Index = 18H             | . 11-36 |

|         | 5.7   | Graphic   | s Controller Registers                                                |         |

|         |       | 5.7.1     | Graphics Index Register, Read/Write Port = 3CE                        | . 11-36 |

|         | -     | 5.7.2     | Set/Reset Register, Read/Write Port 3CF, Index = 00H                  | . 11-37 |

|         |       | 5.7.3     | Enable Set/Reset Register, Read/Write Port = 3CF, Index = 01H         | . 11-37 |

|         |       | 5.7.4     | Color Compare Register, Read/Write PORT 3CF, Index = 02H .            |         |

|         |       | 5.7.5     | Data Rotate Register, Read/Write Port = 3CF, Index = 03H              |         |

|         |       | 5.7.6     | Read Map Select Register, Read/Write Port = 3CF, Index = $04H$ .      | . 11-39 |

|         |       | 5.7.7     | Graphics Mode Register, Read/Write Port = 3CF, Index = 05H .          | . 11-39 |

|         |       | 5.7.8     | Miscellaneous Register, Read/Write Port = 3CF, Index = 06H            | . 11-41 |

|         |       | 5.7.9     | Color Don't Care Register, Read/Write Port 3CF, Index = $07H$         |         |

|         |       | 5.7.10    | Bit Mask Register, Read/Write Port = 3CF, Index = 08H                 | . 11-42 |

|         | 5.8   | Attribute | e Controller Registers                                                |         |

|         |       | 5.8.1     | Attribute Index Register, Read/Write Port = 3C0                       | . 11-42 |

|         |       | 5.8.2     | Palette Registers (00-0F Hex), Read Port 3C1/Write Port 3C0           | . 11-43 |

|         |       | 5.8.3     | Attribute Mode Control Register, R Port 3C1/W Port 3C0, I=10H .       | . 11-43 |

|         |       | 5.8.4     | Overscan Color Reg, Read Port 3C1/Write Port 3C0, Index = 11H         |         |

|         |       | 5.8.5     | Color Plane Enable Reg, Read Port 3C1/Write Port 3C0, I=12H .         |         |

|         |       | 5.8.6     | Horizontal PEL Panning Reg, R Port 3C1/W Port 3C0, I=13H              |         |

|         |       | 5.8.7     | Color Select Reg, Read Port 3C1/Write Port 3C0, Index = 14H .         |         |

|         | 5.9   | Compat    | ibility Registers                                                     |         |

|         |       | 5.9.1     | Hercules/MDA Mode Control Reg, MDA Write Only Port = 3B8H .           | . 11-46 |

|         |       | 5.9.2     | Hercules Registers                                                    |         |

|         |       | 5.9.3     | Enable Mode Register 3B8                                              | . 11-47 |

|         |       | 5.9.4     | Hercules Compatibility Register, Write Only Port = 3BFH               |         |

|         |       | 5.9.5     | Color CGA Operation Register, Write Only Port = 3D8                   | . 11-48 |

|         |       | 5.9.6     | CGA Color Select Register, Write Only Port = 3D9                      |         |

|         |       | 5.9.7     | CRT Status Register, MDA Operation, Read Only Port = 3BA              |         |

|         |       | 5.9.8     | CRT Status Register, CGA Operation, Read Only Port = 3DA $\therefore$ |         |

|         |       | 5.9.9     | AT&T/M24 Register, Write Only Port = 3DE                              | . 11-50 |

|         |       |           |                                                                       |         |

. /

| Section | Title |                                                                                                                             | Page    |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------|---------|

|         | 5.10  | WD90C20 PR Registers                                                                                                        | . 11-51 |

|         |       | 5.10.1 Address Offset Registers, PR0A & PR0B                                                                                | . 11-52 |

|         |       | 5.10.2 PR1 - Memory Size, Read/write Port = 3CF, Index = 0BH                                                                | . 11-53 |

|         |       | 5.10.3 PR2-Video Select Register, R/W Port = 3CF, Index = 0CH                                                               | . 11-56 |

|         |       | 5.10.4 PR3 - CRT Lock Control Register, R/W Port=3CF, Index = 0DH .                                                         | . 11-58 |

|         |       | 5.10.5 PR4- Video Control Register, Read/Write Port=3CF, Index = 0EH                                                        | . 11-59 |

|         |       | 5.10.6 PR5 - General Purpose Status Bits R/W Port=3CF, Index = 0FH                                                          | . 11-60 |

|         |       | 5.10.7 PR10 Unlock PR11-PR17 Read/Write Port = 3?5, Index = 29H .                                                           | . 11-61 |

|         |       | 5.10.8 PR11 EGA Switches Read/Write Port = 3?5, Index = 2AH                                                                 | . 11-61 |

|         |       | 5.10.9 PR12 Scratch Pad Read/Write Port = 3?5, Index = 2BH                                                                  |         |

|         |       | 5.10.10 PR13 Interlace H/2 Start Read/Write Port = 3?5, Index = 2C                                                          |         |

|         |       | 5.10.11 PR14 Interlace H/2 End Read/Write Port = 3?5, Index = 2DH                                                           |         |

|         |       | 5.10.12 PR15 Miscellaneous Control 1R/W Port = 3?5, Index = 2EH                                                             |         |

|         |       | 5.10.13 PR16 Miscellaneous Control 2 R/W Port = 3?5, Index = 2FH                                                            |         |

|         |       | 5.10.14 PR17 Miscellaneous Control 3 R/W Port = 3?5, Index = 30                                                             |         |

|         |       | 5.10.15 PR18 Flat Panel Status Register R/W Port = 3?5, Index = 31                                                          |         |

|         |       | 5.10.16 PR19 Flat Panel Control Register, R/W Port = 3?5, Index 32                                                          |         |

|         |       | 5.10.17 PR1A Flat Panel Control II Register, R/W Port 3?5, Index = 33                                                       |         |

|         |       | 5.10.18 PR1B Flat Panel Unlock Register, R/W Port 3?5, Index = 34                                                           |         |

|         |       | 5.10.19 PR30 Mapping RAM Unlock Register, R/W Port = 3?5, Idx = 35                                                          |         |

|         |       | 5.10.20 PR33 Mapping RAM Add Counter Reg, R/W P = 3?5, I = 38                                                               |         |

|         |       | 5.10.21 PR34 Mapping RAM Data Reg, R/W P= 3?5, Index = 39 5.10.22 PR35 Mapping RAM and Powerdwn Ctl Reg, R/W P = 3?5, I= 3A |         |

|         |       | 5.10.23 PR36 Panel Height Select Register,R/W Port = 3?5, Index = 3B                                                        |         |

|         |       | 5.10.24 PR37 Flat Panel Blinking Control, $R/W$ Port = 3?5, Index = 3C .                                                    |         |

|         |       | -                                                                                                                           | . 11-74 |

|         |       | 5.10.26 PR41 Vertical Expansion Initial Value Reg, $R/W P = 3?5$ , $I = 37$ .                                               |         |

|         |       | 5.10.27 PR42 – PR43 Unlock Register, Write Only Port = $3C5$ , $I = 06$ .                                                   |         |

|         |       | 5.10.28 PR43 PR VGA Status Register, R/W Port = 3C5, Index = 07                                                             |         |

|         |       | 5.10.29 PR44 Powerdown Memory Refresh Ctl Reg, R/W P = 3?5, I= 3F                                                           |         |

|         | 5.11  | Internal I/O Ports                                                                                                          |         |

|         |       | 5.11.1 AT Mode, Write Only Port 46E8H (Port 56E8H, 66E8H, 76E8H) .                                                          |         |

|         |       | 5.11.2 Setup Mode Video Enable R/W Port = 102H                                                                              |         |

|         | 5.12  | Video RAMDAC Ports                                                                                                          | . 11-77 |

|         |       | 5.12.1 PEL Mask Register, Read/Write Port = 03C6                                                                            | . 11-77 |

|         |       | 5.12.2 Palette Status Register/Palette-Read PEL Addr Reg R/W= 03C7                                                          | . 11-77 |

|         |       | 5.12.3 Pallette-Write-Mode PEL Address Register R/W Port = 03C8                                                             | . 11-78 |

|         |       | 5.12.4 PEL Data Read/Write Port = 03C9                                                                                      | . 11-78 |

|         | 5.13  | WD90C20 Configuration Bits, CNF                                                                                             | . 11-78 |

|         | 5.14  | Mapping RAM – 32 by 5 Static RAM                                                                                            | . 11-80 |

|         | 5.15  | Shadow Timing Registers                                                                                                     | . 11-81 |

# WD90C20/WD90C20A

| Section | Title Pag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.0     | RAMDAC       11-80         6.1       General Description       11-80         6.2       Functional Description       11-80         6.3       Features       11-80         6.4       Test Mode       11-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

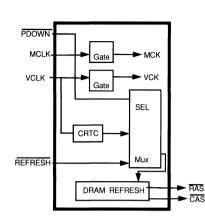

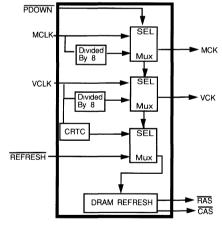

| 7.0     | POWER-DOWN MODES       11-83         7.1       System Power-Down Mode       11-83         7.1.1       Description of System Power-Down Mode (Sleep Mode)       11-83         7.1.2       Entering System Power-Down Mode       11-83         7.1.3       Exiting System Power-Down Mode       11-83                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 7.2       Display Idle Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 7.3       General Powerdown Modes       11-8         7.3.1       Description of General Power-Down Modes       11-8         7.3.2       Entering General Power-Down Mode with External Clock Control       11-8         7.3.3       Exiting General Power-Down Mode with External Clock Control       11-8         7.3.4       Entering General Power-Down Mode with External Clock Control       11-8         7.3.5       Exiting General Power-Down Mode with Internal Clock Control       11-8         7.3.5       Exiting General Power-Down Mode with Internal Clock Control       11-8         7.3.6       Example Calculations of PR44(6:0) Values       11-8         7.3.7       Disabling the WD90C20 to Accommodate an Alternate VGA       11-8 |

| 8.0     | LCD PANEL CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.0     | LCD POWER-ON/OFF OPERATIONS DESCRIPTION       11-90         9.1       System Power-on       11-90         9.2       System Power-off       11-90         9.3       Switching from CRT Mode to LCD Mode       11-90         9.4       Switching from LCD Mode to CRT Mode       11-90         9.5       Entering Power-Down Mode       11-90         9.6       Leaving Power-Down Mode       11-90                                                                                                                                                                                                                                                                                                                                                         |

| Section | Title |                                                              | Page   |

|---------|-------|--------------------------------------------------------------|--------|

| A.0     | APPL  | ICATIONS APPENDIX                                            | 11-91  |

| B.0     | EGA   | MODE APPENDIX                                                |        |

|         | B.1   | General Registers                                            |        |

|         |       | B.1.1 Miscellaneous Output Register (Write Port 3C2)         | 11-96  |

|         |       | B.1.2 Input Status Register 0 (Read Port 3C2)                | 11-96  |

|         |       | B.1.3 Input Status Register 1 (Read Port 3?A)                | 11-96  |

|         |       | B.1.4 Feature Control Register (Write Port 3?A)              | 11-97  |

|         | B.2   | Sequencer Registers (Port 3C5)                               |        |

|         |       | B.2.1 Clocking Mode Register, (Index = 01)                   | 11-97  |

|         |       | B.2.2 Character Map Select Register, (Index 03)              | 11-97  |

|         |       | B.2.3 Memory Mode Register, (Index = 04)                     |        |

|         | B.3   | CRT Controller Registers (Port 3?5)                          | 11-98  |

|         |       | B.3.1 Index Register (Port = 3?4)                            | 11-98  |

|         |       | B.3.2 Horizontal Total Register, (Index = 00)                | 11-98  |

|         |       | B.3.3 End Horizontal Blanking Register, (Index = 03)         | 11-98  |

|         |       | B.3.4 End Horizontal Retrace Register, (Index = 05)          | 11-98  |

|         |       | B.3.5 Vertical Total Register, (Index = 06)                  | 11-98  |

|         |       | B.3.6 CRT Controller Overflow Register, (Index = 07)         | 11-98  |

|         |       | B.3.7 Preset Row Scan Register, (Index = 08)                 | 11-98  |

|         |       | B.3.8 Maximum Scan Line Register, (Index = 09)               | 11-99  |

|         |       | B.3.9 Cursor Start Register (Index = 0A)                     | 11-99  |

|         |       | B.3.10 Cursor End Register (Index = 0B)                      | 11-99  |

|         |       | B.3.11 Vertical Retrace Start Register, (Index = 10) - Write | 11-99  |

|         |       | B.3.12 Vertical Retrace End Register, (Index = 11) - Write   | 11-99  |

|         |       | B.3.13 Underline Location Register, (Index = 14)             | 11-99  |

|         |       | B.3.14 End Vertical Blanking Register, (Index = 16)          | 11-100 |

|         |       | B.3.15 Mode Control Register, (Index = 17)                   | 11-100 |

|         | B.4   | Graphics Controller Registers (Port 3CF)                     | 11-100 |

|         |       | B.4.1 Read Map Select Register, (Index = 04)                 | 11-100 |

|         |       | B.4.2 Mode Register, (Index = 05)                            | 11-100 |

|         | B.5   | Attribute Controller Registers (Ports = 3C0/3C1)             | 11-100 |

|         |       | B.5.1 Mode Control Register, (Index = 10)                    | 11-101 |

|         |       | B.5.2 Overscan Color Register, (Index = 11)                  |        |

|         |       | B.5.3 Color Plane Enable Register, (Index = 12)              | 11-101 |

|         |       | B.5.4 Horizontal PEL Panning Register, (Index = 13)          | 11-101 |

|         | B.6   | Monitor Detection                                            |        |

| C.0     | AC OF | PERATING CHARACTERISTICS AND TIMING DIAGRAMS                 | 11-104 |

|         | C.1   | DC and RAMDAC Specifications                                 | 11-129 |

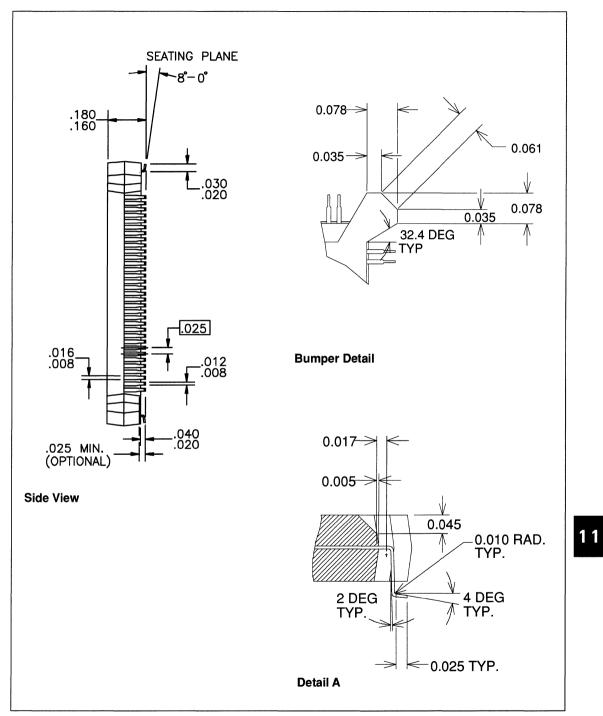

| D.0     | PACK  | AGE DIMENSIONS AND SPECIFICATIONS                            | 11-134 |

| E.0     | MAXI  | MUM RATINGS                                                  | 11-136 |

| Section | Title |          |                                     | Page  |

|---------|-------|----------|-------------------------------------|-------|

| F.0     | DIFFE | ERENCES  | S BETWEEN WD90C20 AND WD90C20A      | 1-137 |

|         | F.1   | Function | nal Changes                         | 1-137 |

|         | F.2   | Feature  | Enhancements for WD90C20A           | 1-137 |

|         |       | F.2.1    | DAC Enhancement                     | 1-137 |

|         |       | F.2.2    | Micro Channel Interface Enhancement | 1-137 |

|         |       | F.2.3    | Monochrome LCD Contrast Enhancement | 1-137 |

|         |       | F.2.4    | Plasma Panel Support                | 1-137 |

|         |       | F.2.5    | Color LCD Display Enhancement       | 1-137 |

|         |       | F.2.6    | Power Management Enhancement        | 1-138 |

|         | F.3   | Performa | ance Enhancements for WD90C20A      | 1-138 |

|         |       | F.3.1    | DAC Improvements                    | 1-138 |

|         | F.4   | WD90C2   | 20A DC Specifications               | 1-140 |

# LIST OF ILLUSTRATIONS

| Figure | Title P                                        | age  |

|--------|------------------------------------------------|------|

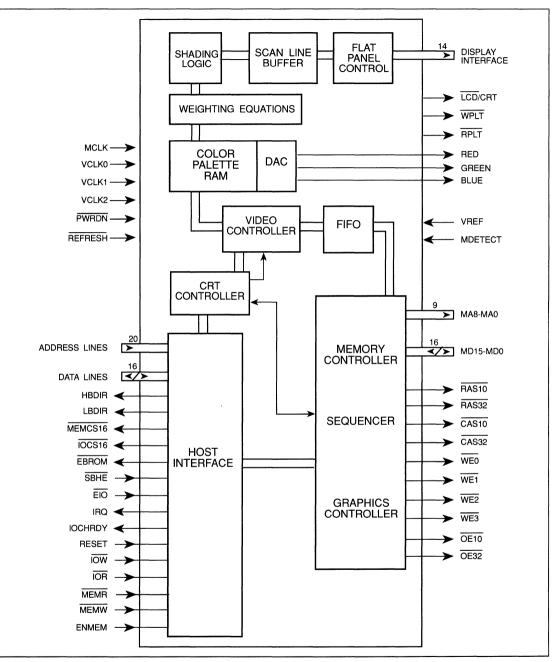

| 2-1    | WD90C20 Block Diagram                          | 11-3 |

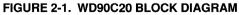

| 3-1    | Example of Screen Size Mapping                 | 11-6 |

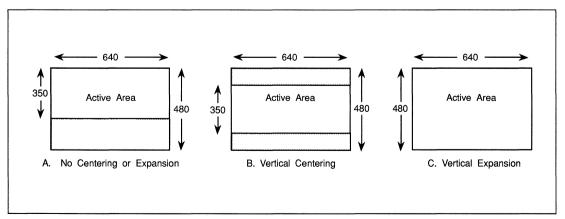

| 3-2    | WD90C20 Color Mapping                          | 11-8 |

| 4-1    | 132-Pin PQFP Pin Assignments                   | 11-9 |

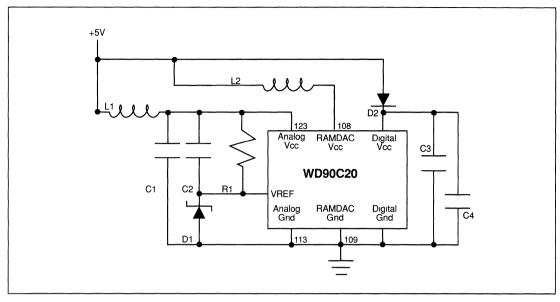

| 4-2    | Power Distribution for WD90C20                 | -17  |

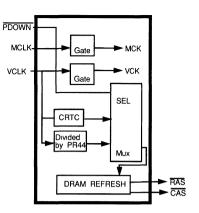

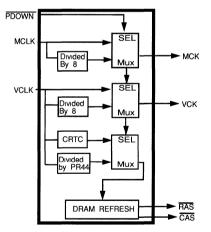

| 5-1    | System Power-Down Mode/Display Mode            | -71  |

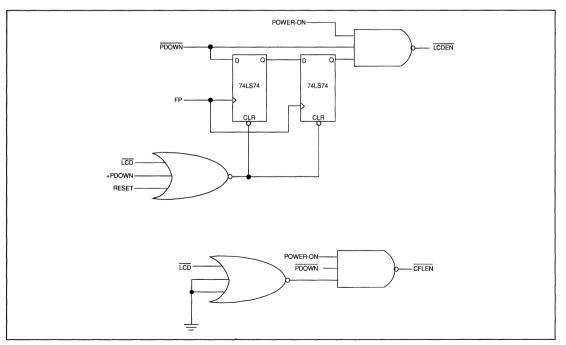

| 8-1    | LCD Panel Control                              | -89  |

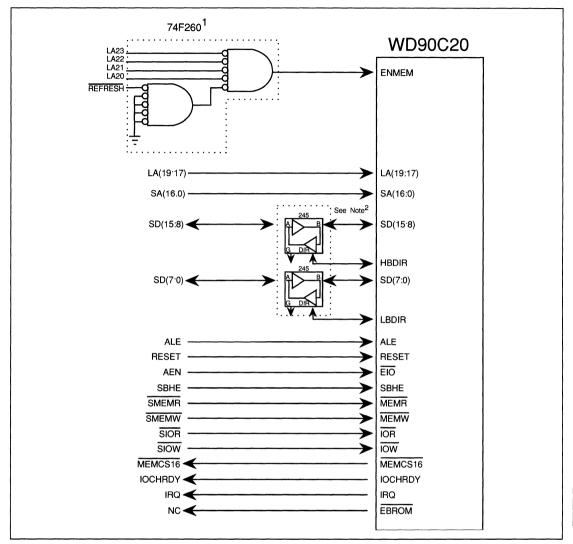

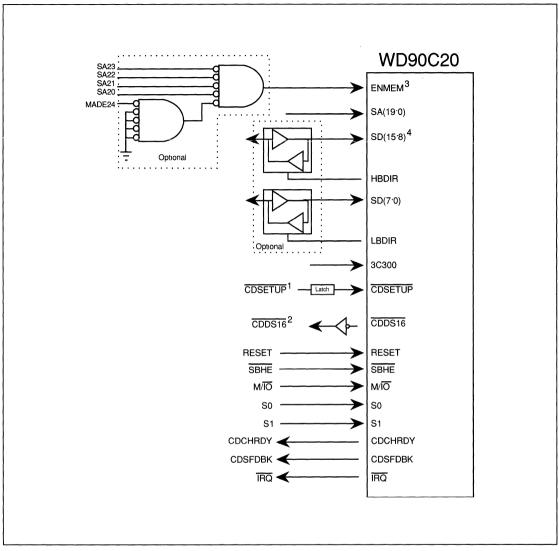

| A-1    | PC/AT Interface                                | -91  |

| A-2    | Micro Channel Interface                        | -92  |

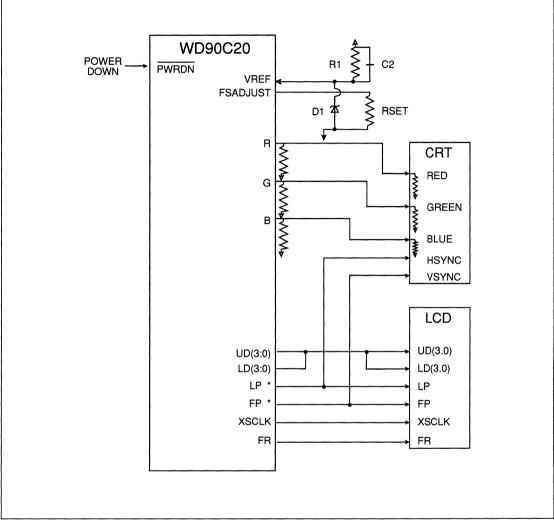

| A-3    | WD90C20 Display Interface                      | -93  |

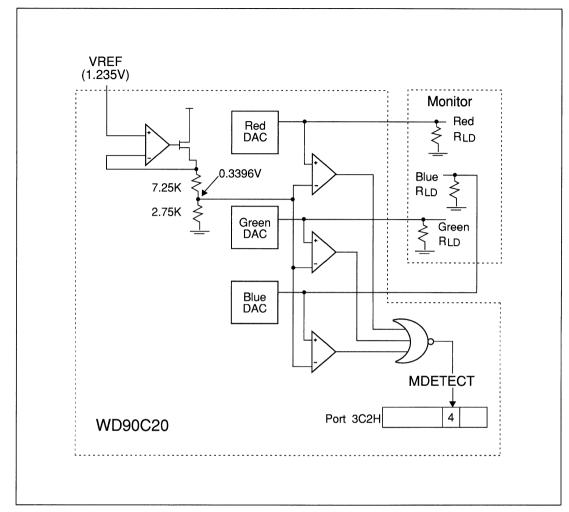

| B-1    | Monitor Detection for Internal RAMDAC          | 103  |

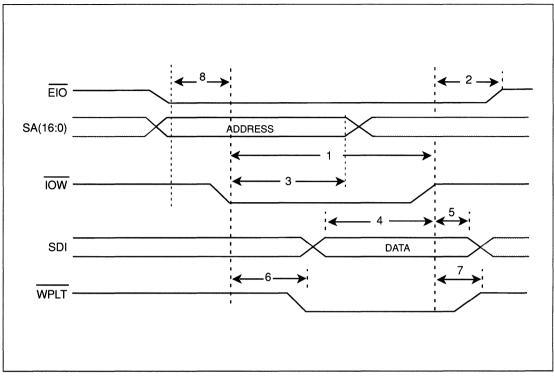

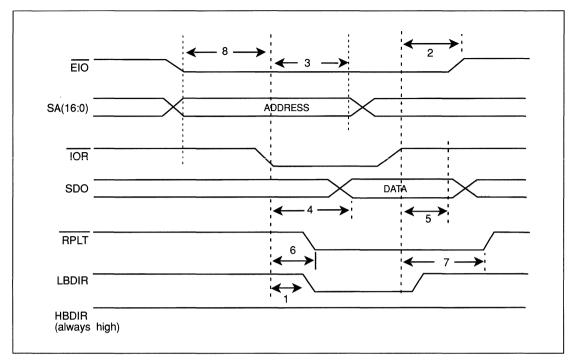

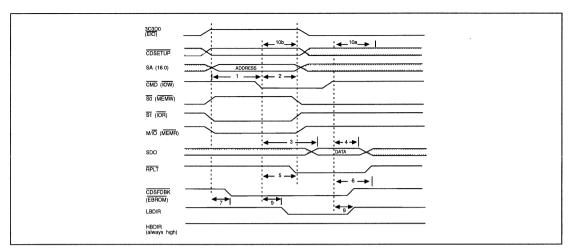

| C-1    | I/O Write – AT Mode                            | 105  |

| C-2    | I/O Read – AT Mode                             | 106  |

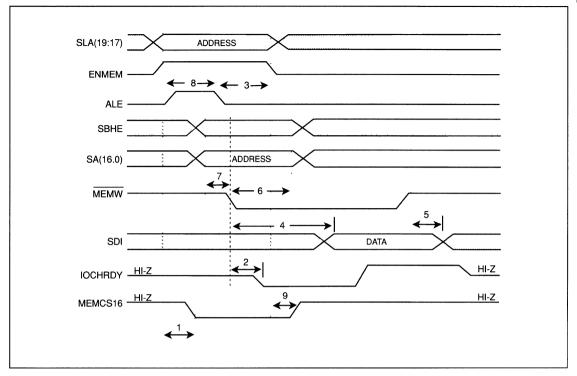

| C-3    | Memory Write – AT Mode                         | 107  |

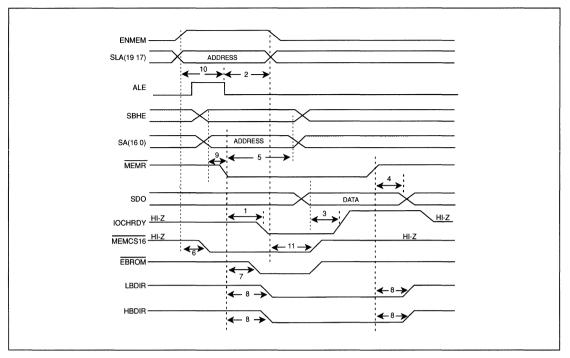

| C-4    | Memory Read – AT Mode                          | 108  |

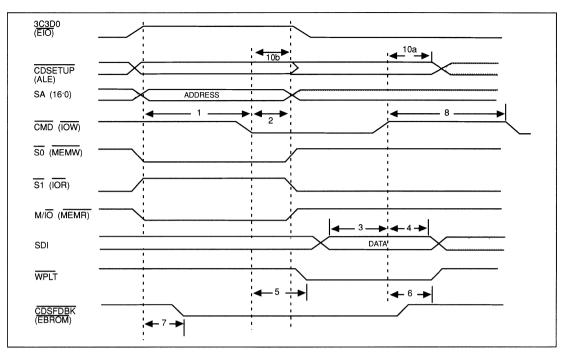

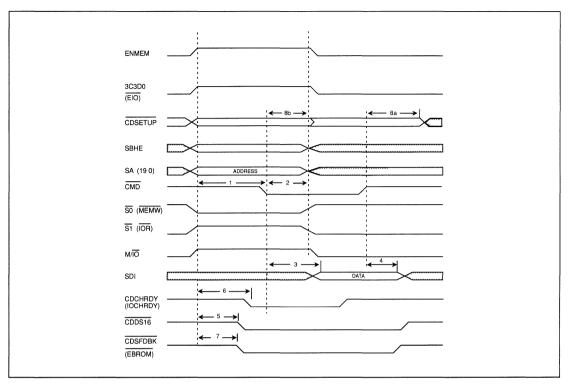

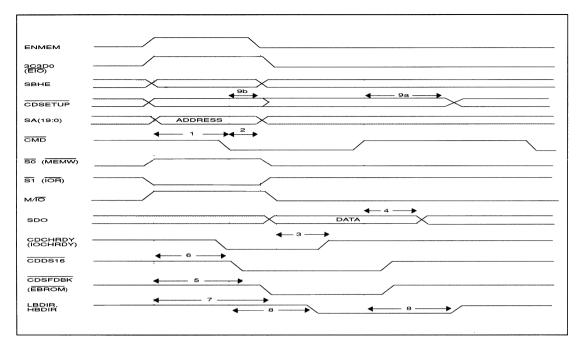

| C-5    | I/O Write – Micro Channel Mode                 | 109  |

| C-6    | I/O Read – Micro Channel Mode                  | 110  |

| C-7    | Memory Write – Micro Channel Mode              | 111  |

| C-8    | Memory Read – Micro Channel Mode               | 112  |

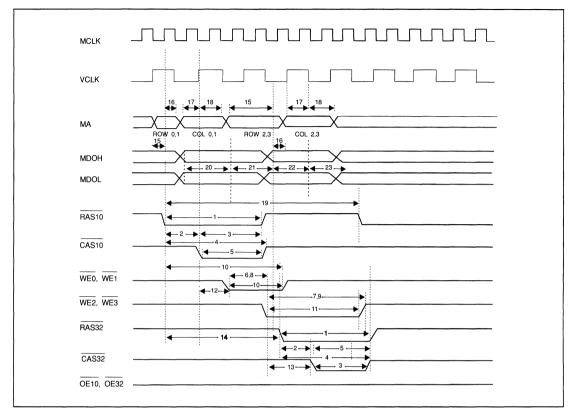

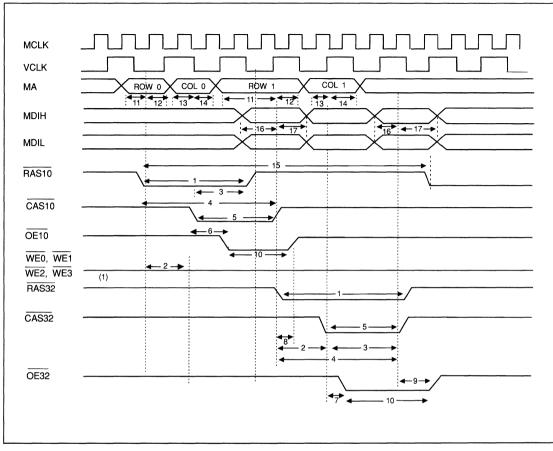

| C-9    | CPU Write Non-Page Mode                        | 113  |

| C-10   | CPU Read Non-Page Mode, CRT Read               | 115  |

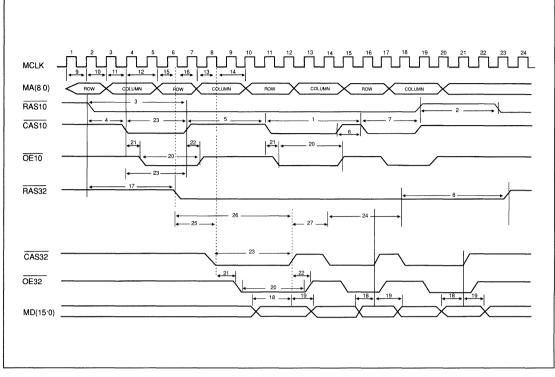

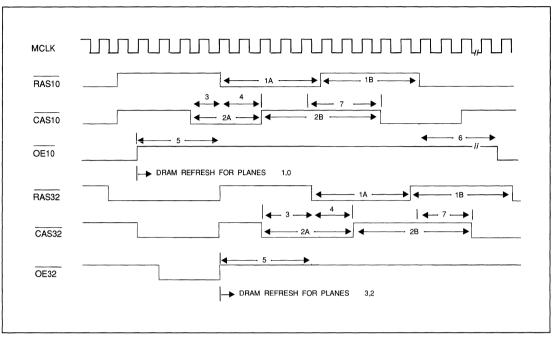

| C-11   | DRAM Page Mode – Read Timing                   | 117  |

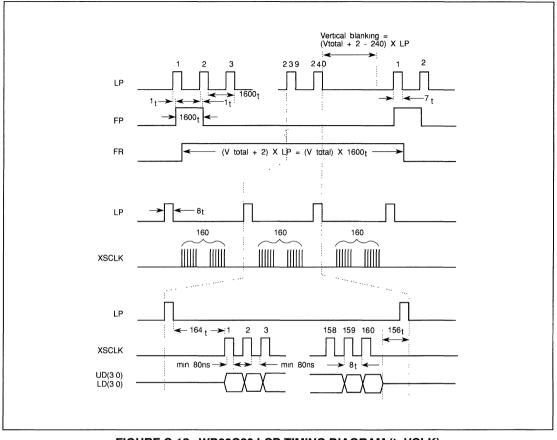

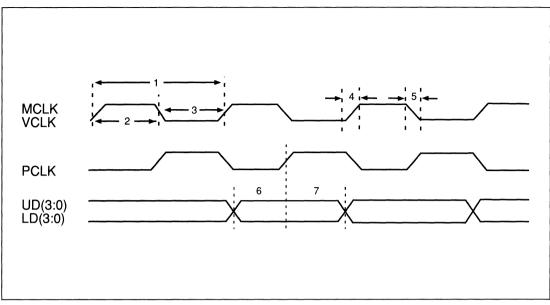

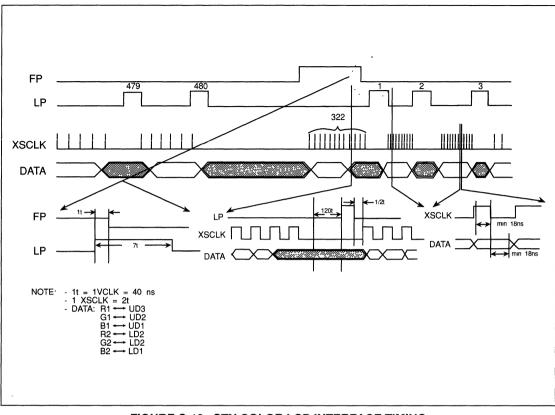

| C-12   | WD90C20 LCD Timing (t = VCLK)                  | 119  |

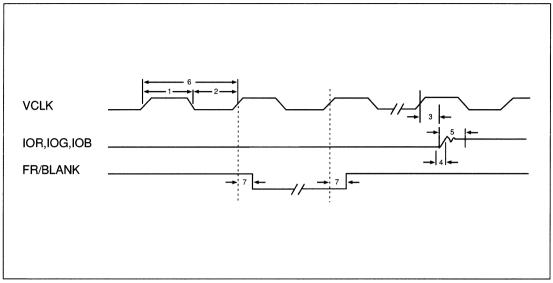

| C-13   | RAMDAC Timing                                  | 120  |

| C-14   | CRT Clock Timing                               | 121  |

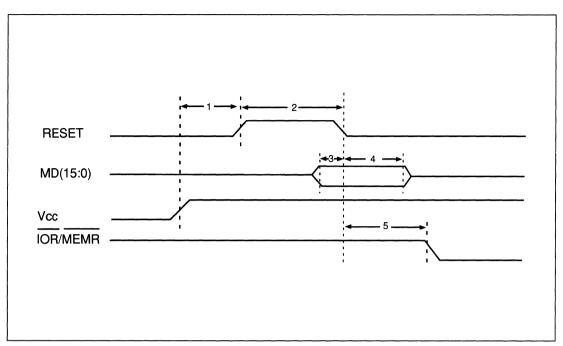

| C-15   | RESET Timing                                   | 122  |

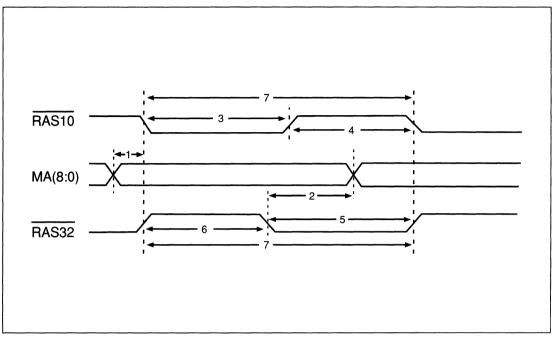

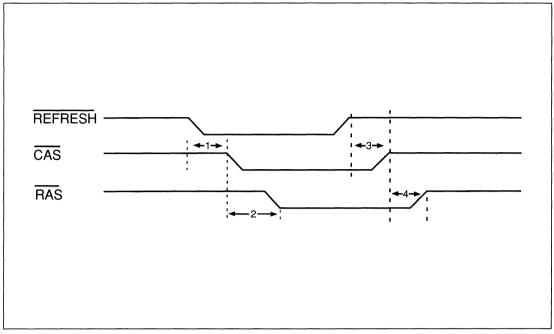

| C-16   | RAS Only DRAM Refresh Timing                   | 123  |

| C-17   | CAS Before RAS DRAM Refresh Timing             | 124  |

| C-18   | CAS Before RAS Refresh (Power-Down Mode)       | 125  |

| C-19   | STN Color LCD Interface Timing                 | 126  |

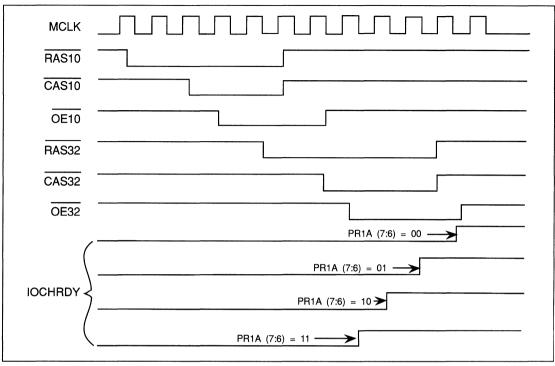

| C-20   | I/O CHRDY Release Timing in Memory Read Cycle  | 127  |

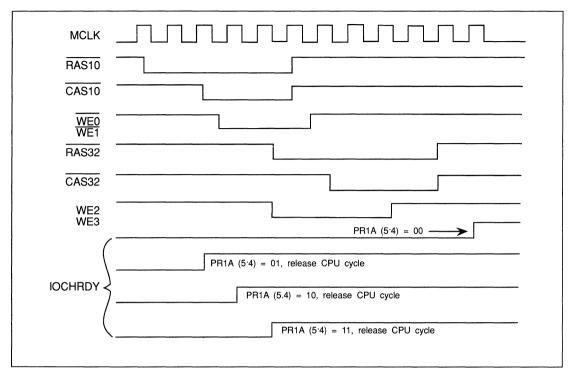

| C-21   | I/O CHRDY Release Timing in Memory Write Cycle | 128  |

| D-1    | 132-Pin PQFP Package Dimensions                | 134  |

# LIST OF TABLES

| Table | Title                                | Page   |

|-------|--------------------------------------|--------|

| 2-1   | Display Interface Output Functions   | 11-4   |

| 2-2   | LCD Data Bit Assignments             | 11-5   |

| 4-1   | Signal Description                   | 11-10  |

| 4-2   | PR Register Functions                | 11-17  |

| 4-3   | Recommended Component Values         | 11-17  |

| 5-1   | VGA Registers Summary                | 11-18  |

| 5-2   | Compatibility Registers Summary      | 11-19  |

| 5-3   | CRT Controller Registers             | 11-26  |

| 5-4   | PR Registers Summary                 | 11-51  |

| B-1   | EGA Registers Summary                | 11-95  |

| C-1   | Timing Diagrams                      | 11-104 |

| C-2   | D.C. Test Specifications             | 11-131 |

| C-3   | RAMDAC Specifications (WD90C20 only) | 11-133 |

| F-1   | WD90C20A RAMDAC Specifications       | 11-139 |

| F-2   | WD90C20A DC Specifications           | 11-140 |

# 1.0 INTRODUCTION

This data sheet applies to both the WD90C20, and WD90C20A. The WD90C20A is a 0.9 micron version of the WD90C20 VGA controller chip.

For convenience all references to these two devices will be referred to as the WD90C20. When a particular feature is available only on one of these devices, it is called out in the text.

See Appendix F for a detailed explanation of the differences between the WD90C20 and the WD90C20A.

### 1.1 DESCRIPTION

The WD90C20 is a VGA display controller that has been optimized for applications that require flat panel display support. It is an extension of the WD90C00 and as such supports all of the WD90C00's features and modes when driving a standard CRT. The WD90C20's highly integrated design includes a complete Micro Channel or AT compatible bus interface, as well as an on-chip PS/2 compatible RAMDAC with integral monitor detection logic.

The WD90C20 is a VGA controller for up to 640 by 480 plasma and LCD display applications. It provides complete flat panel display subsystems for Micro Channel and AT compatible interfaces and has expanded Micro Channel compatibility.

The WD90C20 is 1.25 micron device and the WD90C20A is a 0.9 micron CMOS device.

### 1.2 FEATURES

- On-chip Micro Channel interface

- On-chip 8-bit or 16-bit AT bus interface

- Direct interface with CRT and flat panel displays (monochrome and color TFT LCD)

- · On-chip frame rate modulation logic

- Supports all functions of WD90C00 VGA chip in CRT mode

- 32-shade gray scale mapping

- Software-selectable vertical screen centering

- Hardware vertical expansion(WD90C20A)\*

- On-chip PS/2 compatible RAMDAC\*

- On-chip monitor detection logic

- 32 MHz maximum LCD video clock (WD90C20)

36 MHz maximum LCD video clock (WD90C20A)

- 45 MHz maximum CRT video clock

- Flexible power management features \*

- · Vcc may be removed in powered system

- 256 out of 512 color support for DSTN color LCD( WD90C20)

256 out of 4K color support for DSTN color LCD (WD90C20A )

8-color or 512-color support for TFT color LCD

- Four power-down modes

- \* Patent pending

# 2.0 THEORY OF OPERATION

The WD90C20 contains six major functional modules. In addition to the CRT controller, there is a sequencer, a graphics controller, an attribute controller, a flat panel interface, and a RAMDAC. The WD90C20 handles all display buffer management functions, including display refresh cycles, memory refresh cycles, and the arbitration and sequencing of host access cycles.

#### Sequencer

The sequencer provides the display memory control signals and timing. It also provides the synchronization between the CRT controller and the attribute controller. The sequencer controls the arbitration between the CPU cycle and the CRT cycle, or the CPU cycle and the memory refresh cycle.

#### Graphics Controller

The graphics controller manages data flow between video memory and the attribute controller during active display (non-blanked) periods. It also controls system microprocessor reads from and writes to the video memory, using the time slots defined by the sequencer.

#### Attribute Controller

The attribute controller modifies the CRT display data stream in graphics and character modes. It controls display attributes such as blinking, underlining, cursor, scrolling, reverse video (as well as background or foreground video) in VGA and enhanced VGA BIOS modes.

### Flat Panel Adapter

The flat panel adapter section includes color-togray scale mapping\*, a dithering mapping RAM, a dithering engine, a row buffer\*, shading control\*, and panel interface logic.

\* Patent pending.

### RAMDAC

The WD90C20's on-board RAMDAC is a low power, PS/2-compatible device with special power-down modes and PS/2 monitor detection logic.

The RAMDAC's 256 by 18 color look-up table has triple 6-bit D/A converters, a pixel mask register, and composite blank generation on the three channels. It also supports the use of an external voltage reference. Without external buffering the RAMDAC will generate RS-343A-compatible video signals into a doubly terminated 75 ohm load or a 50 ohm load. Integral and differential linearity errors are a maximum of  $\pm$  1/2 LSB.

### 2.1 WD90C20 INTERFACES

The WD90C20 has five main system interfaces: the CPU, a display memory, a RAMDAC/CRT, a clock, and a flat panel display. In most implementations, these interfaces eliminate the need for glue logic.

#### CPU Interface

The WD90C20 host interface supports both the AT and Micro Channel buses with both 8-bit and 16-bit data path widths. The WD90C20 may also be directly connected to the bus if drive requirements permit. The bus mode is determined by the status of the configuration register bit, CNF(2), which is loaded by the de-assertion of reset. The value that is loaded reflects the status of one of the memory data pins at reset.

I/O transfers to and from the device are 8-bits wide, and display memory transfers are 8-bit or 16-bits wide, depending on the video mode selected. Because of their architecture, EGA type planar modes are restricted to 8-bit display data transfers. Text and 256 color extended modes allow 16-bit transfers on a 16-bit bus.

The controller generates wait states as required during display memory accesses. Wait states are not generated for I/O or video BIOS ROM accesses. Special I/O ports, such as 46E8H (when in AT bus mode) for setup, and 102H for VGA enable, are internally implemented.

#### Display Memory Interface

The WD90C20 generates all signals and memory timing required to operate the display memory. It directly controls three display memory sizes, 256 Kbyte, 512 Kbyte, and 1 Mbyte, as follows:

| MEMORY<br>SIZE | NUMBER AND TYPE OF<br>DRAM REQUIRED                   |  |

|----------------|-------------------------------------------------------|--|

| 256 Kbytes     | 8 64 Kbyte by 4 DRAMs, or<br>2 64 Kbyte by 16 DRAMs   |  |

| 512 Kbytes     | 16 64 Kbyte by 4 DRAMs*, or<br>4 64 Kbyte by 16 DRAMs |  |

| 1 Mbyte*       | 8 64 Kbyte by 16 DRAMs, or<br>8 256 Kbyte by 4 DRAMs  |  |

\* Requires minimal support logic.

Page mode memories are required for all configurations. With a 36 MHz memory clock (MCLK), 120 ns devices may be used. If 256 color CRT modes are to be supported, 100 ns DRAMs and a 45 MHz MCLK are required. The WD90C20 includes special offset registers that allow the host to address up to 1 Mbyte of display memory.

#### CRT/RAMDAC Interface

In addition to its internal RAMDAC, the WD90C20 allows the use of an external RAMDAC. This is helpful in specialized applications where a 24-bit wide color lookup table or pixel demultiplexing (to obtain higher video rates) is required. The external RAMDAC interface will support any Bt471/478/476 compatible device.

#### Clock Interface

The WD90C20 has four clock input signal pins. Three of these (VCLK0, VCLK1, and VCLK2) are normally connected to oscillators. VCLK1 and VCLK2 may be configured to control an external clock multiplexor or clock generator, such as the WD90C61. In this configuration, VCLK0 becomes the clock input while VCLK1 and VCLK2 become outputs used to drive the multiplexor select inputs.

The memory clock input, MCLK, is used by the internal logic to generate all memory timing and may be up to 36 MHz for 120 ns DRAMs or 45 MHz for 100 ns DRAMs.

#### Flat Panel Interface

The WD90C20 is designed to interface with 640 by 480 LCD or plasma panels. The flat panel interface lines change function to support the specific panel type chosen. Table 2-1 summarizes their use for each mode of operation.

When in LCD mode, with frame rate modulation selected, the controller supplies eight pixels per shift clock (four for the upper panel, and four for the lower). If pulse width modulation is selected, the controller provides two pixels per shift clock (one 4-bit pixel for the upper screen, and one 4-bit pixel for the lower screen).

When in Plasma mode, pulse width modulation is used to provide shading, while the controller supplies one pixel (four bits per pixel) per clock.

When in color STN LCD mode, the controller supplies two pixels per shift clock and uses hardware dithering. Each pixel (three bits, one each for R, G, and B), with dithering, provides 16 colors. The user can select:

<sup>- 256</sup> out of 4K colors (WD90C20A)

| LCD      | PLASMA   | CRT      |

|----------|----------|----------|

| UD (3:0) | VD (3:0) | P (7:4)  |

| LD (3:0) | Reserved | P (3:0)  |

| FR       | Reserved | BLANK    |

| FP       | VS       | VSYNC    |

| LP       | HS       | HSYNC    |

| XSCLK    | XSCLK    | Reserved |

| WGTCLK   | ENABLE   | Reserved |

| Reserved | Reserved | PCLK     |

TABLE 2-1. DISPLAY INTERFACE OUTPUT FUNCTIONS

<sup>- 256</sup> out of 512 colors (WD90C20)

| MONOCHROME<br>LCD | COLOR LCD<br>Device |

|-------------------|---------------------|

| UD (3)            | R1                  |

| UD (2)            | G1                  |

| UD (1)            | B1                  |

| UD (0)            | Border Information  |

| LD (3)            | R2                  |

| LD (2)            | G2                  |

| LD (1)            | B2                  |

| LD (0)            | Reserved            |

TABLE 2-2. LCD DATA BIT ASSIGNMENTS

### Powerup Configuration

An internal 8-bit configuration register, CNF, controls the behavior of the major interfaces. Its bits are loaded with the inverted state of memory data lines 0 through 7 at the time RESET is deas serted. Pullup or pulldown resistors on the MD lines are used to set the configuration.

# 3.0 FLAT PANEL SUPPORT CONSIDERATIONS

Supporting VGA compatible graphics on flat panel displays involves several non-trivial issues, including:

- Display Timing Differences

- Screen Size Mapping

- Color-to-Gray Scale Mapping

- Shading Mechanics

- Split Screen Refresh

The following paragraphs address each of these issues.

#### • Display Timing Differences

Typically, flat panel displays have different timing requirements from a CRT. To overcome this problem, the WD90C20 provides a set of hidden display timing registers, which are read/write protected in locked mode.

#### Screen Size Mapping

Unlike those of a CRT, the pixels on a flat panel display are real, discrete entities of a fixed size. This can result in problems when different display modes are mapped onto a single panel. The WD90C20 has been designed to support VGA and various backward compatible display modes on a 640 by 480 dot flat panel and it provides integral hardware support to deal with screen size incompatibilities. In case of backward compatible display modes, such as EGA, which has a maximum resolution of 640 by 350, the vertical resolution of the mode is less than the number of dots of vertical resolution of the panel. This results in an active display area that is smaller than that of the panel and shifted up on the display, as shown in Figure 3-1(A). There are two ways to enhance screen size mapping as described below.

The simplest approach, supported by the WD90C20 is to keep the vertical resolution of the display mode constant but center the active display area vertically on the panel. In the case of an EGA 350 line mode being displayed on a 480 line panel, this would involve shifting the active display area down 65 lines (that is, 480 minus 350, the quantity divided by two). The effect of such a mapping is shown in Figure 3-1(B).

If the goal is to have the active display area fill the panel in all modes, then the active display area can be expanded by double scanning a portion of the active scan lines. Previously available controllers simply double scan lines at regular intervals, every third line in the case of EGA 350 line modes.

The WD90C20A uses an advanced proprietary algorithm that automatically expands to fill all 480 lines\*. This algorithm can be used to support better "screen scrolling" when in 350 line modes.

\* Patent pending on Hardware Vertical Expansion.

### FIGURE 3-1. EXAMPLE OF SCREEN SIZE MAPPING

Under certain display conditions, any expansion scheme can result in undesirable aliasing effects of the displayed data. For this reason the WD90C20A allows the system designer flexibility to choose between vertical expansion or centering as shown below.

|          | CENTERING | VERTICAL<br>EXPANSION |

|----------|-----------|-----------------------|

| WD90C20  | Y         | N                     |

| WD90C20A | Y         | Y                     |

Horizontal resolution issues involve 720 dot modes such as VGA text and Hercules graphics. In VGA text mode, the 9th dot in each character box is dropped. The net effect is a slight compression in the spacing between characters. Alternatively, a different font may be loaded, although a nonstandard font size may not be fully compatible.

### Color-to-Gray Scale Mapping

The VGA standard defines how colors are mapped to 64 gray scale values on monochrome monitors. The mapping is based on the following RGB weighting equation:

I = .30R + .59G + .11B

Unfortunately, many of the currently available panels support at most sixteen shades and some only support two. In order to provide faithful support of all of the standard VGA modes on a flat panel, the WD90C20 provides a range of features to map colors to intensities and control panel shading. Foremost among these is sophisticated logic that converts gray scale values into dithering patterns. Additionally, the device allows software modification of the weighting values used in the gray scale mapping equation. Figure 3-2 gives an overview of the color-to-gray scale support provided by the WD90C20.

#### Shading Mechanics

The WD90C20 supports shading via either frame rate or pulse width modulation. Pulse width modulation is handled via the display panel. The controller transfers 2, 3, or 4 bits per pixel to the driver logic on the panel, along with a high speed clock signal used to sequence the shading logic. Frame rate modulation, on the other hand, must be implemented in the display controller. The WD90C20 provides support for 2, 4, 8, 16, or 32 shade frame rate modulation with its integrated dithering controller. Any combination of dithering patterns can be selected via the dithering controller's mapping RAM. This design allows the WD90C20 to provide flicker-free frame rate modulation with frame rates as low as 70 Hz.

#### Split Screen Refresh

The WD90C20 provides support for panels that are split into upper and lower panels requiring simultaneous refresh. This type of refresh is typically used by non-active matrix LCDs.

ŧ

$\sim$

# 4.0 SIGNAL DESCRIPTION

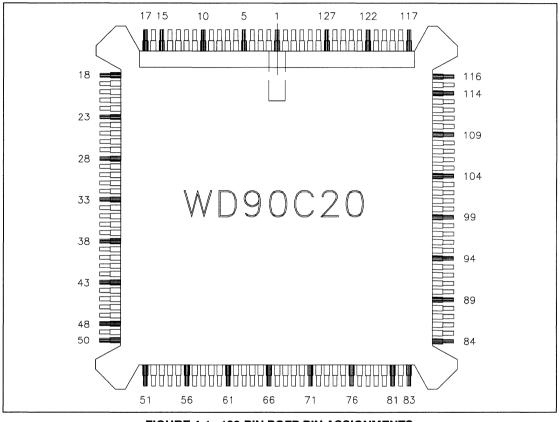

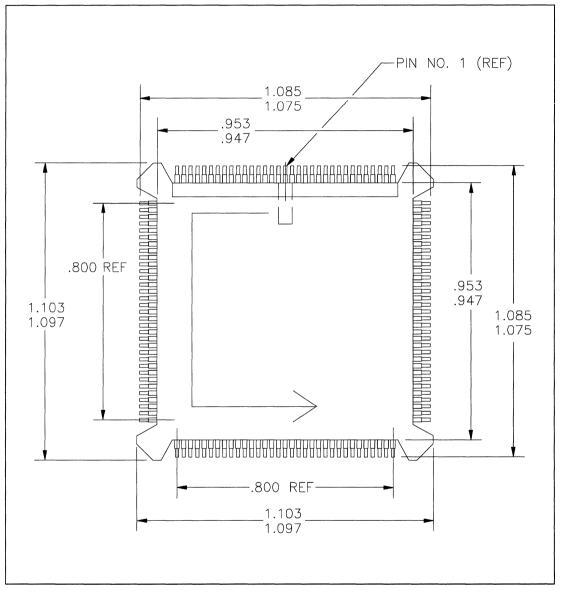

Figure 4-1 illustrates the 132-pin PQFP.

Table 4-1 lists all pins referenced in Figure 4-1 and provides a detailed description of each signal.

FIGURE 4-1. 132-PIN PQFP PIN ASSIGNMENTS

| PIN                             | MNEMONIC                               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------------------|----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                 | POWERON                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 42                              | RESET                                  | Ι   | <b>Reset</b><br>This signal input will reset the WD90C20. MCLK and VCLK0<br>should be connected to the WD90C20 in order for the WD90C20<br>to initialize during reset. Western Digital Imaging Registers, PR1<br>and CNF, are initialized at powerup reset based on the logic level<br>on the MD15-0 bus as determined by pullup/ pulldown resistors.<br>The reset pulse width should be at least ten MCLK clock periods.<br><i>CLOCK SELECTION</i>                                                           |  |  |

| 96                              | VCLK2                                  | I/O | Video Clock 2<br>This pin can be a third video display clock input or an output to the<br>external clock selection module. Pin direction is programmed<br>simultaneously with that of VCLK1. It acts as either a user-defined<br>external clock input, or as an output reflecting the content of bit<br>PR2(1) if CNF (3) is set to 1. Refer to the Configuration Register<br>description. MCLK should be greater than or equal to selected<br>VCLK.                                                          |  |  |

| 97                              | VCLK1                                  | 1/0 | Video Clock 1<br>This pin can be a second video display clock input or an output to<br>the external clock selection module. Pin direction is determined on<br>reset by a pullup/down resistor on pin MD3. A VCLK1 input fre-<br>quency of 28.322 MHz is used to display 720 pixels per horizontal<br>line. When it is an output, VCLK1 is an active low pulse during I/O<br>writes to port 3C2H. Refer to the Configuration Register descrip-<br>tion. MCLK should be greater than or equal to selected VCLK. |  |  |

| 98                              | MCLK                                   | I   | <b>Memory Clock</b><br>This clock signal determines the VGA graphics mode video DRAM<br>read/write access timing as well as system micro-processor I/O<br>and memory timing. MCLK should be approximately 36 MHz for<br>120 ns DRAMS, and 45.0 MHz for 100 ns DRAMS.                                                                                                                                                                                                                                          |  |  |

| 99                              | VCLK0                                  | ł   | Video Clock 0<br>This input is the video display clock for alphanumeric and graphics<br>display modes. Typically, VCLK0 is 25.175 MHz to display 640<br>pixels per horizontal display line. MCLK should be greater than or<br>equal to VCLK0. The Miscellaneous Output Register bits 2 and 3,<br>both set to 0, will select this clock if VCLK1 and VCLK2 are used<br>as inputs.                                                                                                                              |  |  |

|                                 |                                        |     | HOST INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 1 - 2<br>117 - 122<br>124 - 132 | SA15 - SA16<br>SA0 - SA5<br>SA6 - SA14 | I   | Address Bus (SA16-SA0)<br>These active high inputs form the lower order 17 bits of video<br>memory address. These inputs are directly connected to the sys-<br>tem bus.                                                                                                                                                                                                                                                                                                                                       |  |  |

# **TABLE 4-1. SIGNAL DESCRIPTION**

| PIN   | MNEMONIC         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | HOST INTERFACE   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3 - 5 | LA17 - LA19      | I   | Unlatched Address Bus (LA19 -LA17)<br>These active high inputs form the high-order three bits of video<br>memory address. These addresses are not decoded during I/O<br>accesses in AT or Micro Channel modes. These inputs are directly<br>connected to the system bus.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 6     | SBHE             | 1   | <b>System Byte High Enable</b><br>If SA0 is "0", this signal is used to enable 16-bit data transfer<br>mode when SBHE is "0". With SA0, this signal is also used to<br>select high byte data (SD[15:8]) or low byte data (SD[7:0]).                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 7     | ENMEM            | I   | <b>Enable Memory</b><br>This line is driven by external decode logic. In AT mode, this signal is decoded by LA23 - LA20 and REFRESH. In Micro Channel mode, this signal is decoded by LA23 - LA20 and MADE24 ("1" = enable).                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 8     | EIO/3C3D0        | I   | Enable I/O<br>In AT mode, this active low signal is used to enable I/O address<br>decoding and is connected directly to the system bus signal AEN<br>(address enable). In Micro Channel mode, this line is from I/O port<br>3C3 bit 0, and enables video subsystem memory and I/O address<br>decoding ("1" = enable).                                                                                                                                                                                                                                                                                                              |  |  |  |

| 11    | ALE<br>CDSETUP   | I   | ALE<br>In AT mode, this line is ALE; in Micro Channel mode, it is driven by<br>the host to individually select channel connector slots during sys-<br>tem configuration and error recovery procedures.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 12    | IRQ/ IRQ         | 0   | Interrupt Request<br>Programmable processor interrupt request. It is enabled via Bit 5<br>in the Vertical Retrace End register. It is active high in AT mode<br>and active low in Micro Channel mode. When the end of the verti-<br>cal display occurs, this signal goes active, causing an interrupt. It<br>will stay latched until CRTC11 Bit 4 clears it. In an AT system IRQ<br>is not connected, although you may connect it if you desire. IRQ9<br>is used to generate an interrupt in Micro Channel mode. For fur-<br>ther details, see the reference literature.                                                           |  |  |  |

| 13    | EBROM<br>CDSFDBK | 0   | <b>Enable BIOS ROM</b><br>In AT mode, this is an active low signal to enable BIOS ROM<br>(C0000H - C7FFFH) if enabled by PR1(0). It is not active for ac-<br>cess to addresses in the range C60000H-C67FFH, but this ad-<br>dress range may be mapped-in by setting PR17 (0) = 0. A write to<br>the WD90C20 internal I/O port address, 46E8H, causes this signal<br>to be used as a write strobe for an external register used in BIOS<br>ROM page mapping. In Micro Channel mode, this signal is used<br>as Card Selected Feedback to provide positive acknowledgement<br>of its presence at the addresses specified by the host. |  |  |  |

| PIN                | MNEMONIC                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 14                 | MEMCS16/<br>CDDS16      | 0   | Memory Chip Select 16 Bits<br>In AT mode, this line is used to respond to the host to enable a 16-<br>bit video memory data transfer. In Micro Channel mode, this line<br>provides CDDS16 for 16-bit video memory or I/O access. (For<br>WD90C20 only, this line must be inverted to provide CDDS16).                                                                                                                                                       |  |  |

| 15                 | IOCHRDY/<br>CDCHRDY     | 0   | <b>Ready</b><br>An active high output which signals to the system processor that a<br>memory access is complete. This signal is used only to add wait<br>states to the bus cycles during video memory accesses. It is<br>pulled inactive by the WD90C20 to allow additional time to com-<br>plete a bus operation. This signal is not generated on I/O cycles<br>and accesses to the BIOS ROM. For further details, refer to the ref<br>erence literature.  |  |  |

| 16                 | HBDIR/<br>HSYNC         | Ο   | High Byte Direction<br>This line is used to control the data direction of an external high<br>byte data buffer if the external data buffer is necessary for the im-<br>plementation. This line will be driven "LOW" only in memory<br>READ or I/O READ cycles.<br>(For the WD90C20A only simultaneous display mode, the HBDIR<br>pin can be programmed to output CRT HSYNC.)                                                                                |  |  |

| 17                 | LBDIR/<br>VSYNC         | 0   | Low Byte Direction<br>This line is used to control the data direction of an external low<br>byte data buffer if the external data buffer is necessary for the im<br>plementation. This line will be driven "LOW" only in memory<br>READ or I/O READ cycles.<br>(For the WD90C20A only simultaneous display mode, the LBDIR<br>pin can be programmed to output CRT VSYNC.)                                                                                   |  |  |

| 19 - 26<br>29 - 36 | SD15 - SD8<br>SD7 - SD0 | I/O | <b>Data Bus (SD15 - SD0)</b><br>These bidirectional signals may either be connected directly to a local data bus requiring less than 8 ma. of source/sink, or may be connected through two external bus buffers.                                                                                                                                                                                                                                            |  |  |

| 38                 | MEMR/<br>M/IO           |     | Memory Read<br>In AT mode, this signal is called SMEMR and is an active low<br>memory read strobe. It is asserted in 8-/16-bit memory read<br>cycles. In Micro Channel mode, the signal is called M/IO. It distin<br>guishes between memory and I/O cycles. When (M/IO) is high, a<br>memory cycle is in process. A low on (M/IO) shows that an I/O<br>cycle is in process. For further details, refer to the reference litera-<br>ture.                    |  |  |

| 39                 | MEMW/<br>So             | I   | <b>Memory Write</b><br>The active low memory write strobe in AT mode for 8-/16-bit data<br>transfers. In Micro Channel mode, it becomes $\overline{S0}$ and is the chan-<br>nel status signal which indicates the start and type of a channel<br>cycle. Along with the $\overline{S1}$ , M/ $\overline{I0}$ and $\overline{CMD}$ signals, it is decoded to<br>interpret I/O and memory commands. For further details, refer to<br>the reference literature. |  |  |

| PIN            | MNEMONIC                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------------|-------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 43             | REFRESH                 | I   | Refresh This active low input pin is connected to the system $\overrightarrow{\text{REFRESH}}$ signal from the I/O bus.                                                                                                                                                                                                                                          |  |  |  |

| 40             | IOR/ S1                 | 1   | <b>I/O Read</b><br>Active low I/O read strobe in AT mode. It is asserted in 8-/16-bit<br>I/O read bus cycles. $\overline{S1}$ is the alternate mnemonic used in Micro<br>Channel mode to indicate the start and type of a channel cycle.<br>For further details, refer to the reference literature.                                                              |  |  |  |

| 41             | IOW/<br>CMD             | 1   | I/O Write<br>Active low strobe. In AT mode, the strobe signals an I/O write for 8-<br>/16-bit I/O write cycles. In Micro Channel mode it is synonymous<br>with CMD; address bus validity is signaled by CMD going low<br>while the rising edge of CMD indicates the end of a Micro Channel<br>bus cycle. For further details, refer to the reference literature. |  |  |  |

|                |                         |     | DISPLAY MEMORY INTERFACE                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 45 - 52<br>55  | MA0 - MA7<br>MA8        | 0   | Memory Address (MA0 - MA8)<br>Display memory DRAM address.                                                                                                                                                                                                                                                                                                       |  |  |  |

| 56             | RAS10                   | 0   | Row Address Strobe<br>Active low Memory Maps 1 and 0 RAS output signal.                                                                                                                                                                                                                                                                                          |  |  |  |

| 57             | RAS32                   | 0   | Row Address Strobe<br>Active low Memory Maps 3 and 2 RAS output signal.                                                                                                                                                                                                                                                                                          |  |  |  |

| 58             | CAS10                   | 0   | Column Address Strobe<br>Active low Memory Maps 1 and 0 CAS output signal.                                                                                                                                                                                                                                                                                       |  |  |  |

| 59             | CAS32                   | 0   | Column Address Strobe<br>Active low Memory Maps 3 and 2 CAS output signal.                                                                                                                                                                                                                                                                                       |  |  |  |

| 60             | WEO                     | 0   | Write Enable<br>Active low Memory Map 0 DRAM write enable signal.                                                                                                                                                                                                                                                                                                |  |  |  |

| 61             | WE1                     | 0   | Write Enable<br>Active low Memory Map 1 DRAM write enable signal.                                                                                                                                                                                                                                                                                                |  |  |  |

| 62             | WE2                     | 0   | Write Enable<br>Active low, Memory Map 2 write enable signal.                                                                                                                                                                                                                                                                                                    |  |  |  |

| 63             | WE3                     | 0   | Write Enable<br>Active low, Memory Map 3 write enable signal.                                                                                                                                                                                                                                                                                                    |  |  |  |

| 64             | OE10                    | 0   | Output Enable<br>Active low, Memory Maps 1 and 0 output enable signal.                                                                                                                                                                                                                                                                                           |  |  |  |

| 65             | OE32                    | 0   | Active low, Memory Maps 1 and 0 output enable signal.<br>Output Enable<br>Active low, Memory Maps 3 and 2 output enable signal.                                                                                                                                                                                                                                  |  |  |  |

| 68-75<br>77-84 | MD15 - MD8<br>MD7 - MD0 | I/O | <b>Data Lines</b><br>Lines MD15 through MD0 are the data bus to the video display<br>DRAMS. Data lines MD0 through MD15 are pulled up or down<br>with resistors to provide setup information on power-up (reset) as<br>shown in Table 4-2.                                                                                                                       |  |  |  |

| PIN           | MNEMONIC  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                               |  |  |

|---------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MISCELLANEOUS |           |     |                                                                                                                                                                                                                                                                                           |  |  |

| 44            | PWRDN     | 1   | <b>Power Down Selected</b><br>This active low input signal is used to disable screen refresh cycle.                                                                                                                                                                                       |  |  |

| 110           | LCD/CRT   | 0   | LCD or CRT Selected<br>This active high output is used to power down an external RAM-<br>DAC chip whenever the WD90C20 operates in LCD mode. "1" is<br>CRT mode, and "0" is LCD mode.                                                                                                     |  |  |