WD16C452, WD16C552

Dual Enhanced Asynchronous

Communications Element (ACE)

with Parallel Port

# **TABLE OF CONTENTS**

| Section | Title Page                                                     |

|---------|----------------------------------------------------------------|

| 1.0     | INTRODUCTION         2-1           1.1 Description         2-1 |

|         | 1.2 Features                                                   |

|         | 1.3 General                                                    |

| 2.0     | SIGNAL DESCRIPTIONS                                            |

| 3.0     | SERIAL CHANNEL REGISTERS                                       |

|         | 3.1 Serial Port Register Addressing                            |

|         | 3.1.1 Master Reset                                             |

|         | 3.1.2 Software Reset                                           |

|         | 3.2 ACE Operational Description                                |

|         | 3.2.1 Master Reset                                             |

|         | 3.2.2 ACE Accessible Registers                                 |

|         | 3.3 Line Control Register                                      |

|         | 3.4 ACE Programmable Baud Rate Generator                       |

|         | 3.5 Line Status Register                                       |

|         | 3.6 Interrupt Identification Register                          |

|         | 3.7 Interrrupt Enable Register                                 |

|         | 3.8 Scratch Pad Register                                       |

|         | 3.9 FIFO Control Register                                      |

|         | 3.10 Modem Control Register                                    |

|         | 3.11 Modem Status Register                                     |

|         | 3.11.1 FIFO Interrupt Mode Operation                           |

|         | 3.11.2 FIFO Pointer                                            |

|         | 3.11.3 FIFO Polling Mode Operation                             |

| 4.0     |                                                                |

| 4.0     | PARALLEL PORT DESCRIPTION                                      |

|         | 4.1 Register Descriptions                                      |

|         | 4.1.1 Read Port Register                                       |

|         | 4.1.2 Read Status Register                                     |

|         | 4.1.3 Read Control Register                                    |

|         | 4.1.4 Write Port Register                                      |

|         | 4.1.5 Write Control Register                                   |

| 5.0     | TYPICAL APPLICATIONS                                           |

| 6.0     | ELECTRICAL SPECIFICATIONS                                      |

|         | 6.1 DC Operating Characteristics                               |

|         | 6.2 AC Operating Characteristics And Timing Diagrams           |

| 7.0     | PACKAGE DIAGRAM                                                |

# **LIST OF TABLES**

| Table | Title                                               | Page   |

|-------|-----------------------------------------------------|--------|

| 2-1   | Signal Descriptions                                 | . 2-4  |

| 3-1   | Register Addressing                                 | . 2-9  |

| 3-2   | Reset Control of Registers and Pinout Signals       | . 2-10 |

| 3-3   | Accessible WD16C452/WD16C552 Registers              |        |

| 3-4   | Baud Rates Using 1.8432 MHz Clock                   | . 2-14 |

| 3-5   | Baud Rates Using 3.072 MHz Clock                    |        |

| 3-6   | Baud Rates Using 8.0 MHz Clock                      |        |

| 3-7   | Interrupt Control Functions                         |        |

| 4-1   | Parallel Port (CS2=0) Register Addresses            |        |

| 4-2   | Accessible Parallel Port Registers                  |        |

| 4-3   | Parallel Port Operation Modes                       |        |

| 4-4   | Parallel Port Reset Control of Registers and Signal |        |

| 6-1   | DC Operating Characteristics                        |        |

| 6-2   | Capacitance                                         |        |

| 6-3   | WD16C452/WD16C552 Timing Diagrams                   |        |

| 6-4   | Read/Write Cycle Timing                             |        |

| 6-5   | Parallel Port Timing                                |        |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                   | Page   |

|--------|---------------------------------------------------------|--------|

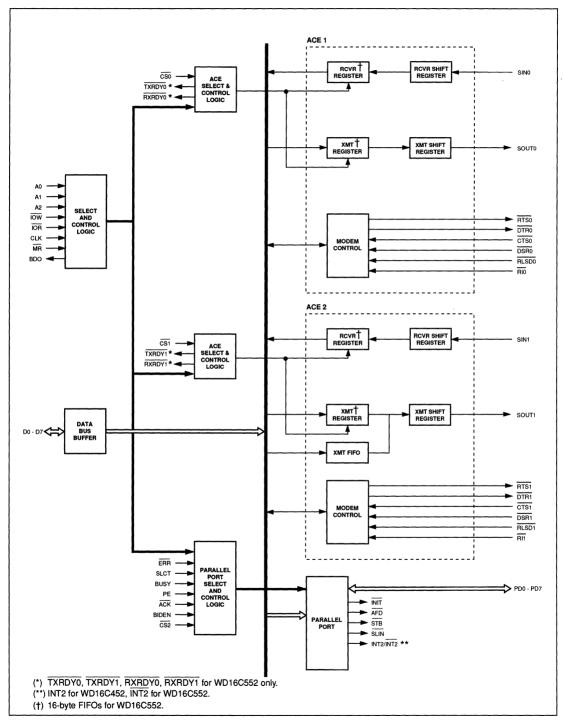

| 1-2    | WD16C452/WD16C552 Block Diagram                         | 2-2    |

| 2-1    | WD16C452/WD16C552 68-Pin PLCC Assembly                  | 2-3    |

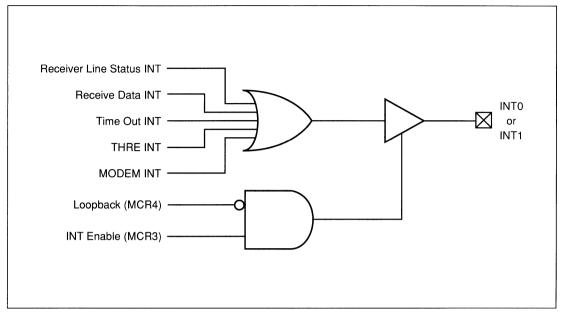

| 3-1    | Interrupt Signal Logic                                  | 2-21   |

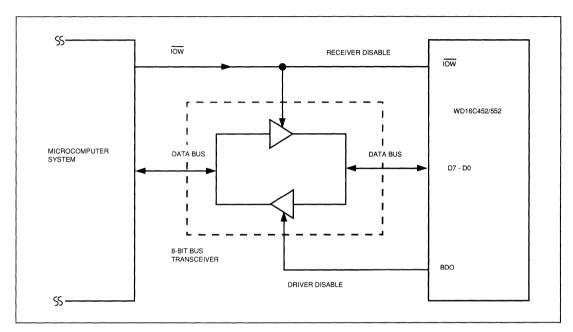

| 5-1    | Typical Interface for a High-Capacity Data Bus          | 2-25   |

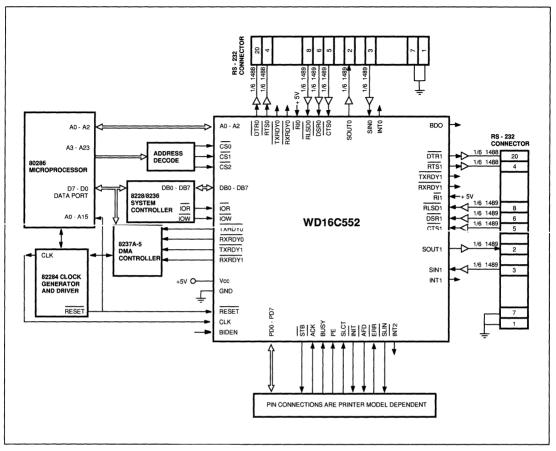

| 5-2    | Typical 16-Bit Microprocessor/RS-232 Terminal Interface | 2-26   |

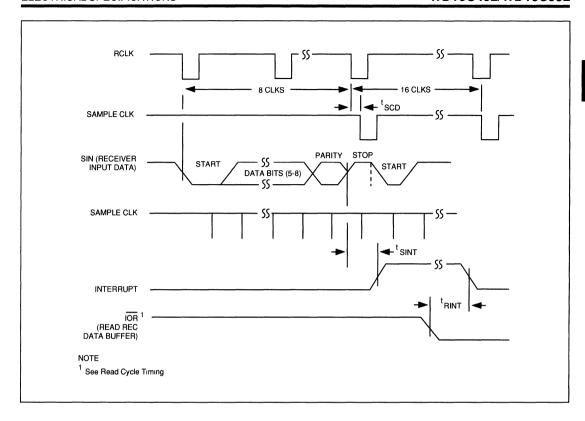

| 6-1    | Receiver Timing                                         | 2-31   |

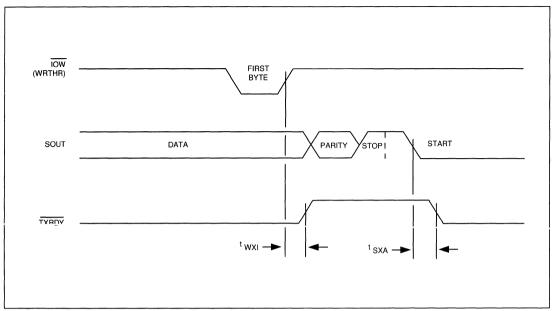

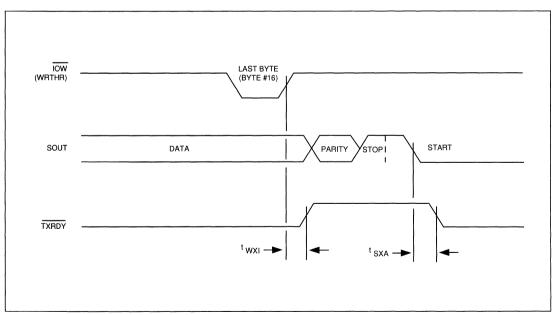

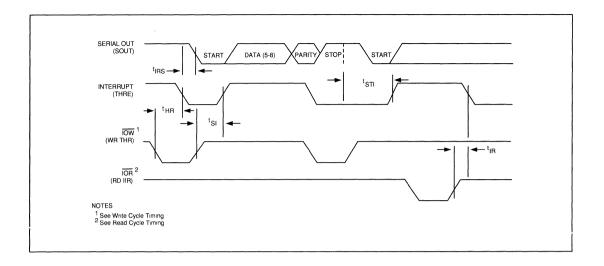

| 6-2    | Transmitter Timing                                      | 2-32   |

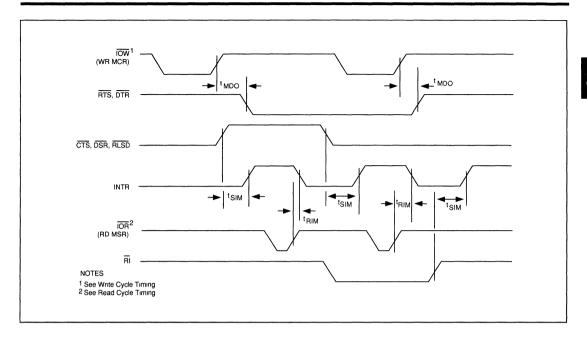

| 6-3    | Modem Control Timing                                    | 2-33   |

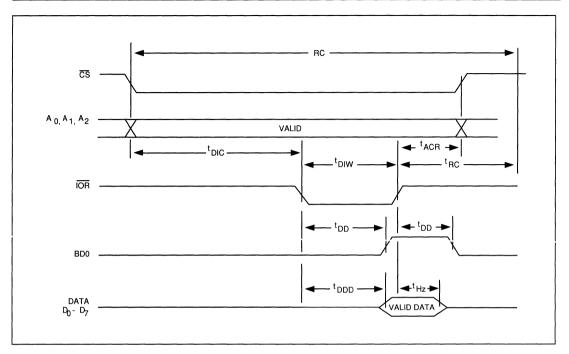

| 6-4    | Read Cycle Timing                                       | 2-34   |

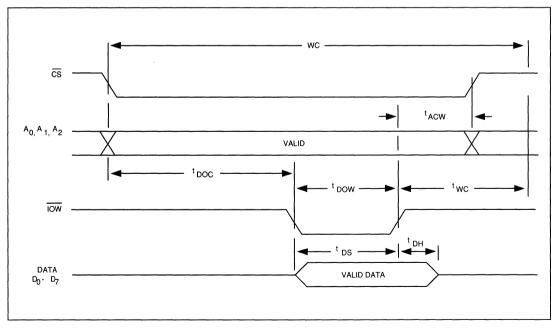

| 6-5    | Write Cycle Timing                                      | 2-34   |

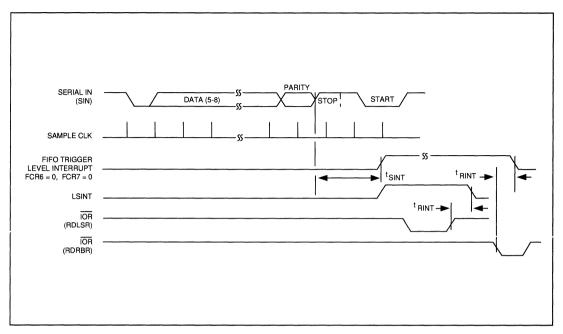

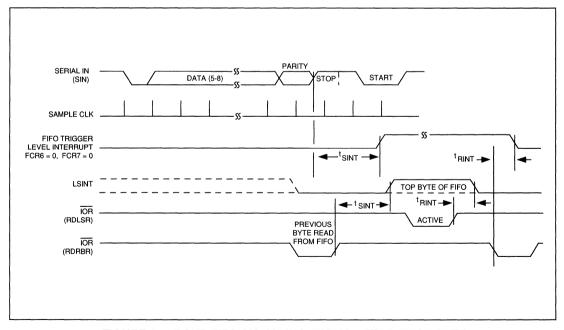

| 6-6    | RCVR FIFO Signaling Timing for First Byte               | 2-36   |

| 6-7    | RCVR FIFO Signaling Timing after First Byte             | 2-36   |

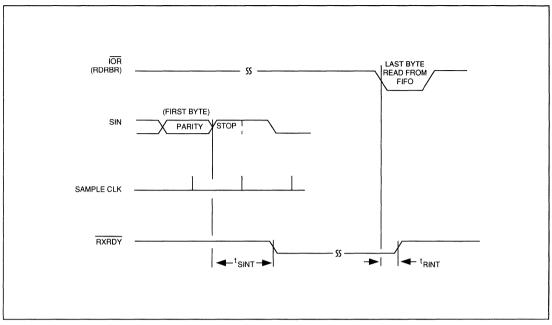

| 6-8    | Receiver DMA Mode 0 Timing                              | 2-37   |

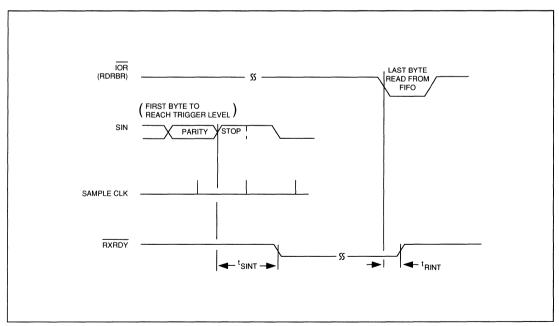

| 6-9    | Receiver DMA Mode 1 Timing                              | 2-37   |

| 6-10   | Transmitter DMA Mode 0 Timing                           | 2-38   |

| 6-11   | Transmitter DMA Mode 1 Timing                           | 2-38   |

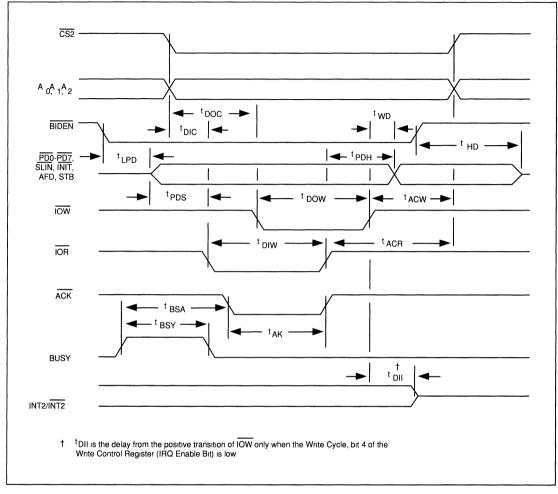

| 6-12   | Parallel Port Timing                                    | 2-39   |

| 6-13   | WD16C452 Parallel Port Interrupt Timing                 | 2-40   |

| 6-14   | WD16C552 Parallel Port Interrupt Timing                 |        |

| 7-1    | 68-Pin PLCC Package Dimensions                          | . 2-42 |

**//**

### 1.0 INTRODUCTION

### 1.1 DESCRIPTION

The low power CMOS WD16C452/552 is a single device solution for serving two serial input/output ports simultaneously and one bidirectional parallel port for the IBM PC XT, PC AT, PS/2, and compatible systems. The WD16C452 parallel port is compatible with the Centronics printer port and IBM Serial/Parallel Adapter, and each ACE is programmable and compatible with a WD16C450. The WD16C552 parallel port is compatible with the IBM PS/2 bi-directional parallel port and each ACE is compatible with the WD16C550. Each ACE in the WD16C552 is programmable, and it is capable of buffering up to 16 bytes of data for transmission and up to 16 bytes of data upon reception, relieving the CPU of interrupt overhead. Buffering of data also allows greater latency time in interrupt servicing. which is vital in a multitasking environment. DMA signaling, between the internal FIFO buffers and host CPU, allows single or multiple character transfers. Each ACE has a maximum recommended data rate of 512K with a clock frequency of 8.0 MHz.

#### 1.2 FEATURES

- Two fully programmable serial I/O channels (DC to 512K baud)

- Tristate TTL drive capabilities for bidirectional data bus and control bus on each channel

- Loopback controls for communications link fault isolation for each ACE

- Line break generation and detection for each \( \Delta \color \)

- Complete status reporting capabilities

- Generation and stripping of serial asynchronous data control bits (start, stop, parity)

- Programmable baud rate generator and Modem control signals for each channel

- Fully prioritized independent interrupt system controls for each channel

- 16 byte FIFO buffers on both transmit and receive of each channel for CPU relief during high speed data transfer †

- Programmable FIFO threshold levels of 1, 4, 8, or 14 bytes on each receive channel †

- Two modes of DMA signaling available for transfer of data characters to and from FIFO buffers †

- Bidirectional Centronics compatible parallel port for direct printer interface

- PS/2 compatible bidirectional parallel port †

- CMOS implementation for high speed and low power requirements

- (†) The FIFO mode of operation and PS/2 compatible parallel port are not available in the WD16C452.

#### 1.3 GENERAL

The WD16C452/WD16C552 is a dual ACE, plus a bidirectional parallel port. The two ACE's perform parallel-to-serial conversion on the output and serial-to-parallel conversion on the input. Each ACE is programmable, independent, and has a maximum recommended data rate of 512K baud.

The WD16C452 is a dual channel version of the WD16C450 ACE, plus a bidirectional parallel data port which supports a Centronics compatible printer interface. The parallel port, together with the two serial ports, provides IBM PC XT, PC AT, and compatibles with a single device solution for serving three ports.

The WD16C552 is a dual channel version of the WD16C550 Enhanced ACE, plus a compatible PS/2 bidirectional parallel port. After power-up and hardware reset, each ACE is functionally compatible to the WD16C450 (Character Mode). Each ACE in the WD16C552 has been enhanced with 16 byte FIFO buffers on both the receive and transmit lines, allowing an additional mode of operation called FIFO mode. FIFO mode (only available in WD16C552), can be activated through software, relieving the CPU of excessive overhead due to interrupts. The PS/2 parallel port, together with the two serial ports, provides IBM PS/2 and compatibles with a single device solution for serving three ports.

FIGURE 1-2. WD16C452/WD16C552 BLOCK DIAGRAM

FIGURE 6-10. TRANSMITTER DMA MODE 0 TIMING (FCR0 = 0 or FCR0 = 1 and FCR3 = 0)

FIGURE 6-11. TRANSMITTER DMA MODE 1 (FCR0 = 1 and FCR3 = 1)

FIGURE 6-12. PARALLEL PORT TIMING

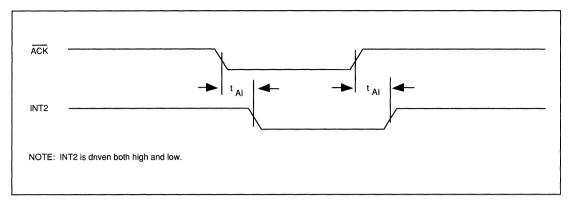

FIGURE 6-13. WD16C452 PARALLEL PORT INTERRUPT TIMING

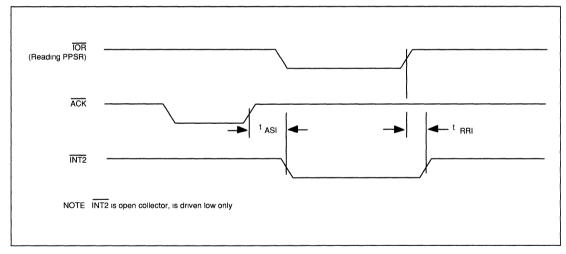

FIGURE 6-14. WD16C552 PARALLEL PORT INTERRUPT TIMING

| WD16C452/WD16C552 |                                                               |     |     |    |                                                |  |  |  |  |  |

|-------------------|---------------------------------------------------------------|-----|-----|----|------------------------------------------------|--|--|--|--|--|

| SYMBOL            | SYMBOL CHARACTERISTIC MIN MAX UNITS TEST CONDITIONS           |     |     |    |                                                |  |  |  |  |  |

| <sup>t</sup> DOC  | IOW Delay from Chip<br>Select and Address                     | 30  |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> DIC  | IOR Delay from Chip<br>Select and Address                     | 30  |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> WD   | IOW High to PD0-PD7,<br>SLIN, INIT, AFD, STB                  |     | 1   | ns | No External Pull-up<br>Resistor and 50 pF Load |  |  |  |  |  |

| <sup>t</sup> HD   | BIDEN High to PD0-PD7 tri-state                               | 120 |     | ns |                                                |  |  |  |  |  |

| t <sub>LPD</sub>  | BIDEN Low to PD0-PD7<br>Delay                                 | 100 |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> PDH  | PD0- <u>PD7</u> Hold Time from IOR                            | 100 |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> PDS  | PD0-PD7 Set-up Time from IOR                                  | 100 |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> DOW  | IOW Strobe Width                                              | 100 |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> DIW  | IOR Strobe Width                                              | 125 |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> ACW  | Chip Select and Address<br>Hold Time from IOW                 | 20  |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> ACR  | Chip Select and Address<br>Hold Time from IOR                 | 20  |     | ns |                                                |  |  |  |  |  |

| <sup>t</sup> BSA  | BUSY Start to ACK                                             |     |     | ms | Printer Dependent                              |  |  |  |  |  |

| <sup>t</sup> BSY  | BUSY Width                                                    |     |     | ns | Printer Dependent                              |  |  |  |  |  |

| <sup>t</sup> AK   | ACK Width                                                     |     |     | ns | Printer Dependent                              |  |  |  |  |  |

| <sup>t</sup> AI   | INT2 Delay from ACK<br>(WD16C452)                             |     | 60  | ns | 1TTL Lpad                                      |  |  |  |  |  |

| tASI              | ACK to set interrupt<br>(WD16C452)                            |     | 60  | ns | 1TTL Lpad                                      |  |  |  |  |  |

| <sup>t</sup> RRI  | Read Parallel Port Status<br>Register (PPSR) to reset<br>INT2 |     | 60  | ns | 1TTL Lpad                                      |  |  |  |  |  |

| <sup>t</sup> DII  | IOW High to INT2/INT2<br>tri-state                            | 0   | 100 | ns | 1TTL Lpad                                      |  |  |  |  |  |

**TABLE 6-5. PARALLEL PORT TIMING**

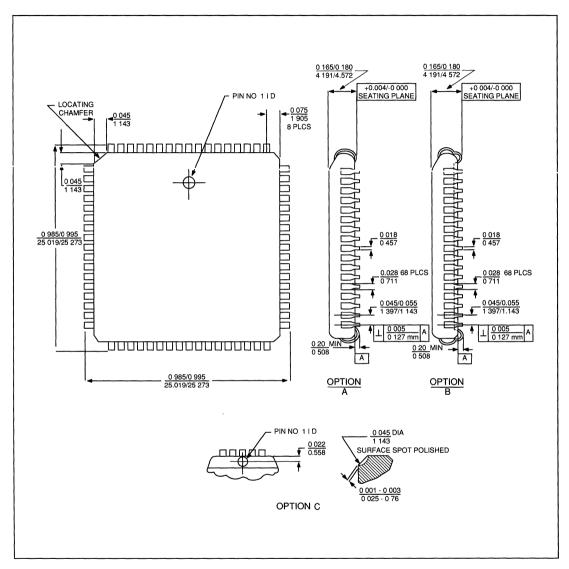

# 7.0 PACKAGE DIAGRAM

Figure 7-1 illustrates the 68-pin PLCC package showing dimensions in inches.

FIGURE 7-1. 68-PIN PLCC PACKAGE DIMENSIONS

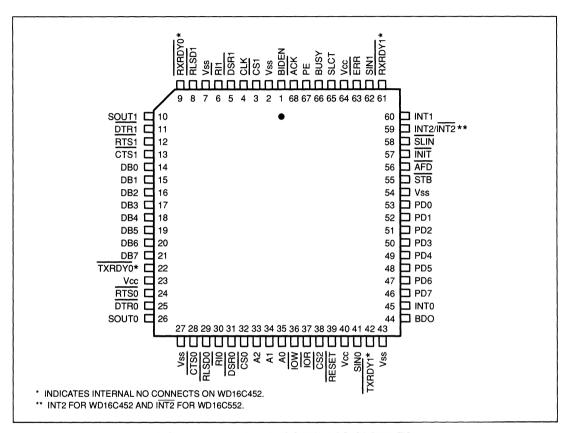

# 2.0 SIGNAL DESCRIPTIONS

Figure 2-1 illustrates the 68-pin PLCC assembly. Table 2-1 lists all signal descriptions.

FIGURE 2-1. 68-PIN PLCC PIN ASSIGNMENTS

| PIN             | MNEMONIC     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | BIDEN        | Bidirectional Enable Input signal in the WD16C452, when low enables the parallel port data lines as outputs. When high the WD16C452 will hold the parallel port data pins in a high impedance state, allowing these pins to be driven with data. The BIDEN input signal on the WD16C552 works in conjunction with the DIR bit (see Table 4-3) to control the direction of the parallel port data bit. |

| 2, 7, 27,43, 54 | Vss          | Ground System signal ground.                                                                                                                                                                                                                                                                                                                                                                          |

| 3               | CS1          | Chip Select 1 Chip Select input when active (low), selects serial channel 1.                                                                                                                                                                                                                                                                                                                          |

| 4               | CLK (1 time) | Clock Input<br>External clock input.                                                                                                                                                                                                                                                                                                                                                                  |

| 5, 31           | DSR1, DSR0   | Data Set Ready When low, this input signal from the communication link indicates that it is ready to exchange data with the associated ACE. Bit 5 of the associated Modem Status Register reflects the logical state of DSR.                                                                                                                                                                          |

| 6, 30           | RI1, RIO     | Ring Indicator Input when low indicates, for the associated ACE, a ringing signal is being received by the modem or data set. This logical value is reflected in bit 6 of the associated Modem Status Register.                                                                                                                                                                                       |

| 8, 29           | RLSD1, RLSD0 | Received Line Signal Detect Input from the DCE indicating that the associated ACE is receiving a signal which meets its signal quality conditions. Bit 3 of the associated Modem Status Register reflects this value.                                                                                                                                                                                 |

(♦) These pins are internal no connects on the WD16C452.

**TABLE 2-1. SIGNAL DESCRIPTIONS**

| PIN     | MNEMONIC            | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|---------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 61   | RXRDY0,<br>RXRDY1 ◆ | Receiver Ready Receiver ready output is used to signal DMA transfer to the CPU from the associated ACE. Two modes of operation are available when using FIFO Mode, and one (Mode 0) when using Character Mode.                                                                                             |

|         |                     | Mode 0: When in Character Mode (FCR0=0), or in the FIFO Mode (FCR0=1) with FCR3=0, RXRDY will be active (low) if there is at least one character in the RCVR holding register or RCVR FIFO register. RXRDY will go inactive when the RCVR FIFO (FIFO Mode), or holding register (Character Mode) is empty. |

|         |                     | Mode 1: In FIFO Mode (FCR0=1) with FCR3=1, RXRDY will go active (low) when the trigger level or time out has been reached. RXRDY goes inactive (high) when the FIFO is empty.                                                                                                                              |

| 10, 26  | SOUT1, SOUT0        | Serial Data Output Transmitted Serial Data Out to the communication link from the associated ACE. The SOUT signal is set to a marking condition (logical 1) upon a Master Reset.                                                                                                                           |

| 11, 25  | DTR1, DTR0          | Data Terminal Ready Output when low informs the modem or data set that the associated ACE is ready to receive. This value is reflected in bit 0 of the Modem Control Register.                                                                                                                             |

| 12, 24  | RTS1, RTS0          | Request to Send Output when low informs the modem or data set that the associated ACE is ready to transmit data. This value is reflected in bit 1 of the Modem Control Register.                                                                                                                           |

| 13, 28  | CTS1, CTS0          | Clear to Send Input from DCE to the associated ACE indicating remote device is ready to transmit. This value is reflected in bit 4 of the Modem Status Register                                                                                                                                            |

| 14 - 21 | DB0-DB7             | Data Bits Tri-state, bidirectional communication lines between the ACE and Data Bus. D0 is the least significant bit (LSB) and the first serial transmitted or received bit.                                                                                                                               |

<sup>(♦)</sup> These pins are internal no connects on the WD16C452.

**TABLE 2-1. SIGNAL DESCRIPTIONS (Continued)**

| PIN        | MNEMONIC       | DESCRIPTION                                                                                                                                                                                                                                                                                                |  |  |

|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 22, 42     | TXRDY0*,TXRDY1 | Transmitter Ready FIFO Control Transmit ready output is used to signal DMA transfer to the CPU from the associated ACE. Two modes of operation are available when using FIFO Mode, and one (Mode 0) when using Character Mode.                                                                             |  |  |

|            |                | Mode 0: In Character Mode (FCR0=0) or in FIFO Mode (FCR0=1) with FCR3=0, TXRDY will be active (low) if there are no characters in the Xmit FIFO (FIFO Mode) or Xmit holding register (Character Mode). TXRDY will go inactive after the first character is loaded.                                         |  |  |

|            |                | Mode 1: In FIFO Mode (FCR0=1) with FCR3=1, if there is one, or more, unfilled position in the Xmit FIFO TXRDY will be active (low). TXRDY will go inactive when the FIFO is completely full                                                                                                                |  |  |

| 23, 40, 64 | Vcc            | Power Supply<br>+5V power supply.                                                                                                                                                                                                                                                                          |  |  |

| 32         | CS0            | Chip Select 0 Chip Select input when active (low) selects serial channel 0.                                                                                                                                                                                                                                |  |  |

| 33 - 35    | A2, A1, A0     | Address lines A2-A0 These three inputs are used to select an internal register of the ACE, or parallel port.                                                                                                                                                                                               |  |  |

| 36         | IOW            | Input/Output Write Strobe Input when active (low), causes data from the data bus (DB0-DB7) to be input to the selected port's addressed register. The data will be written to the register chosen by A0-A2 and the port is chosen by CS0, CS1, or CS2 to be ACE#1, ACE#2, or parallel port (respectively). |  |  |

| 37         | ĪOR            | Input/Output Read Strobe Input active (low) will display data from the selected internal register on the data bus DB0-DB7. The chip select line determines within which port the register being accessed resides, and A0-A2 choose the internal register to be read.                                       |  |  |

| 38         | CS2            | Chip Select 2 Chip Select input when active (low),enables the line printer port.                                                                                                                                                                                                                           |  |  |

**TABLE 2-1. SIGNAL DESCRIPTIONS (Continued)**

<sup>(†)</sup> These outputs are open drain with internal pull-ups. (††) This pin is INT2 for WD16C452 and INT2 for WD16C552.

| PIN     | MNEMONIC   | DESCRIPTION                                                                                                                                                                                                                             |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39      | Reset      | Reset Input when active (low), will force the device into an idle mode in which all serial data activities are suspended. The device will remain in an idle state until programmed to begin data activities.                            |

| 41, 62  | SIN0, SIN1 | Serial Data Inputs Received Serial Data Input from the communication link to the associated ACE. Data on the serial data inputs are disabled when exercising loopback mode, and internally connected to their respective SIN lines.     |

| 44      | BDO        | <b>Bus Buffer Output</b> Output goes active when either serial channel, or the parallel port is selected as an output. BDO is used to control the system bus driver device (74LS245).                                                   |

| 45, 60  | INTO, INT1 | Serial Channel Interrupts Tristate output (enabled by bit 3 of MCR) goes high whenever an enabled interrupt is pending for the associated ACE. INT is reset when the pending interrupt(s) are serviced, or a Master Reset is performed. |

| 46 - 53 | PD7-PD0    | Parallel Data Bits Bidirectional data port which provides parallel input and output to the system. The eight lines are held in a high impedance state when BIDEN is high.                                                               |

| 55      | STB†       | Line Printer Strobe Output line, when active, provides the line printer with a signal to latch the data currently on the parallel port.                                                                                                 |

| 56      | ĀFD†       | Line Printer Autofeed Output line, when active, provides a signal for the line printer to autofeed continuous form paper.                                                                                                               |

| 57      | INIT†      | Line Printer Initialize Output line to printer, when active (low), signals the line printer to begin an initialization routine.                                                                                                         |

| 58      | SLIN†      | Line Printer Select Output line, when active (low), selects the printer.                                                                                                                                                                |

(†) These outputs are open drain with internal pull-ups.

**TABLE 2-1. SIGNAL DESCRIPTIONS (Continued)**

| PIN | MNEMONIC    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 59  | INT2/INT2†† | Interrupt Printer Port Tri-state output enabled by bit 4 of WCR. For the WD16C452, INT2 goes active (high) on the rising transition of ACK and reset (low) on the falling transition of ACK. For the WD16C552 INT2 goes active (low) on the rising edge of ACK. INT2 is reset (high) on the rising edge of IOR, when reading the parallel port status register. |

| 63  | ERR         | Line Printer Error Input line from the line printer, informs the parallel port of an error by inputting an active low signal. Set low by the printer upon a deselect condition, PE, or other error condition.                                                                                                                                                   |

| 65  | SLCT        | Line Printer Select Input from the line printer that goes high when the line printer has been selected.                                                                                                                                                                                                                                                         |

| 66  | BUSY        | Line Printer Busy Input from the line printer that goes high when the line printer has an operation in progress.                                                                                                                                                                                                                                                |

| 67  | PE          | Line Printer Paper Empty Input from the line printer goes high when the printer is out of paper.                                                                                                                                                                                                                                                                |

| 68  | ACK         | Line Printer Acknowledge Input from line printer that goes low to confirm the data transfer from the WD16C552 to the printer was successful.                                                                                                                                                                                                                    |

**TABLE 2-1. SIGNAL DESCRIPTIONS (Continued)**

<sup>(†)</sup> These outputs are open drain with internal pull-ups. (††) This pin is INT2 for WD16C452 and INT2 for WD16C552.

# 3.0 SERIAL CHANNEL REGISTERS

The WD16C552 contains two serial ports. Therefore, the following registers exist in duplicate, one per channel.

# 3.1 SERIAL PORT REGISTER ADDRESSING

Chip Select (CS0, CS1): When CS0 is low, registers for serial channel 0 can be accessed, and when CS1 is low, registers for serial channel 1 can be accessed. No more than one CS (CS0, CS1) should ever be low at any time (an invalid condition).

#### 3.1.1 Master Reset

A low level input on this pin causes the ACE to reset to the condition listed in Table 3-2.

#### 3.1.2 Software Reset

A software reset is performed by writing to the Divisor Latches, forcing the transmitter and receiver to an Idle Mode. (Registers are not reset

by this operation.) Prior to enabling interrupts, the LSR and RBR registers should be read to clear out any data. This is used to return to a known state without resetting the system.

Chip Select (CS0, CS1) and register select (A0, A1, A2) signals must be stable for the duration of a read or write operation.

Register Select (A0, A1, A2): To select a register for read or write operation, see Table 3-1.

Note: Divisor Latch Access Bit (DLAB) is the MSB of the Line Control Register. DLAB must be programmed high (logic 1) by the system software to access the Baud Rate Generator Divisor Latches.

| DLAB | A2 | <b>A</b> 1 | AO | REGISTER                                                                 |  |  |

|------|----|------------|----|--------------------------------------------------------------------------|--|--|

| 0    | 0  | 0          | 0  | Receiver Buffer Register (Read),<br>Transmitter Holding Register (Write) |  |  |

| 0    | 0  | 0          | 1  | Interrupt Enable Register                                                |  |  |

| Х    | 0  | 1          | 0  | Interrupt Identification Register (Read Only)                            |  |  |

| Х    | 0  | 1          | 0  | FIFO Control Register (Write Only)                                       |  |  |

| Х    | 0  | 1          | 1  | Line Control Register                                                    |  |  |

| X    | 1  | 0          | 0  | Modem Control Register                                                   |  |  |

| Х    | 1  | 0          | 1  | Line Status Register (Read Only)                                         |  |  |

| Х    | 1  | 1          | 0  | Modem Status Register                                                    |  |  |

| Х    | 1  | 1          | 1  | Scratch Pad Register                                                     |  |  |

| 1    | 0  | 0          | 0  | Divisor Latch Register (Least Significant Byte)                          |  |  |

| 1    | 0  | 0          | 1  | Divisor Latch Register (Most Significant Byte)                           |  |  |

TABLE 3-1, REGISTER ADDRESSING

11/21/90

2-9

## 3.2 ACE OPERATIONAL DESCRIPTION

#### 3.2.1 Master Reset

A low-level input on this pin causes the ACE to reset to the condition listed in Table 3-2.

# 3.2.2 ACE Accessible Registers

The system programmer has access to any of the registers as summarized in Table 3-3. For individual register descriptions, refer to the following pages under register heading.

| REGISTER/SIGNAL                   | RESET CONTROL                                                                                | RESET STATE                                                                                |

|-----------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Receiver Buffer Register          | First Word Received                                                                          | Data                                                                                       |

| Transmitter Holding Register      | Writing into the<br>Transmitter Holding Register                                             | Data                                                                                       |

| Interrupt Enable Register         | Master Reset                                                                                 | All Bits Low (0-3 forced and 4-7 permanent)                                                |

| Interrupt Identification Register | Master Reset                                                                                 | Bit 0 is High and Bits 1-3; 6<br>and 7 are forced Low. Bits 4<br>and 5 are permanently Low |

| Line Control Register             | Master Reset                                                                                 | All Bits Low                                                                               |

| Modem Control Register            | Master Reset                                                                                 | All Bits Low                                                                               |

| Line Status Register              | Master Reset                                                                                 | All Bits Low, except Bits 5 and 6 are High                                                 |

| Modem Status Register             | Master Reset<br>Modem Signal Inputs                                                          | Bits 0-3 Low,<br>Bits 4-7 at Input Signal                                                  |

| Divisor Latch (low order byte)    | Writing into the Latch                                                                       | Data                                                                                       |

| Divisor Latch (high order byte)   | Writing into the Latch                                                                       | Data                                                                                       |

| SOUT                              | Master Reset                                                                                 | High                                                                                       |

| BDO                               | BDO = RCLK • IOR (At Master Reset, the CPU sets RCLK and IOR = Low when device is selected.) | High                                                                                       |

| INT0,1 (RCVR ERRS)                | Master Reset/Read LSR                                                                        | Low                                                                                        |

| INT0,1 (RCVR DATA READY)          | Master Reset/Read RBR                                                                        | Low                                                                                        |

| INT2 (WD16C452)                   | Master Reset/ACK (High)                                                                      | Low                                                                                        |

| NT2 (WD16C552)                    | Master Reset/Read PPSR                                                                       | High                                                                                       |

| RTS                               | Master Reset                                                                                 | High                                                                                       |

| DTR                               | Master Reset                                                                                 | High                                                                                       |

| RCVR FIFO Counter (WD16C552 only) | MR or FCR1• FCR0 or ∆FCR0                                                                    | All Bits Low                                                                               |

| XMIT FIFO Counter (WD16C552 only) | MR or FCR2 • FCR0 or ΔFCR0                                                                   | All Bits Low                                                                               |

| FIFO CONTROL (WD16C552 only)      | Master Reset                                                                                 | All Bits Low                                                                               |

| D7 - D0 Data Bus Lines            | InTri-state Mode,<br>Unless IOR = Low<br>or IOW = Low when<br>Device is Selected             | Tri-state Data (ACE to CPU) Data (CPU to ACE)                                              |

TABLE 3-2. RESET CONTROL OF REGISTERS AND PINOUT SIGNALS

|            | REGISTER ADDRESS                              |                                                    |                                                                               |                                                        |                                                |                                          |  |  |

|------------|-----------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|------------------------------------------|--|--|

|            | 0 DLAB=0                                      | 0 DLAB=0                                           | 1 DLAB=0                                                                      | 2                                                      | 2                                              | 3                                        |  |  |

| Bit<br>No. | Receiver<br>Buffer<br>Register<br>(Read Only) | Transmitter<br>Holding<br>Register<br>(Write Only) | Interrupt<br>Enable<br>Register                                               | Interrupt<br>Identification<br>Register<br>(Read Only) | FIFO Control<br>Register<br>(Write Only)       | Line<br>Control<br>Register              |  |  |

| 0          | Data Bit 0                                    | Data Bit 0                                         | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBFI)               | "0" if<br>Interrupt<br>Pending<br>(IP)                 | FIFO<br>Enable<br>(Write Only)<br>(FEWO)       | Word Length<br>Select Bit<br>0 (WLS0)    |  |  |

| 1          | Data Bit 1                                    | Data Bit 1                                         | Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt<br>(ETBEI) | Interrupt<br>ID Bit 0<br>(IIDB0)                       | Rcvr<br>FIFO<br>Reset<br>(RFR)                 | Word Length<br>Select Bit<br>1 (WLS1)    |  |  |

| 2          | Data Bit 2                                    | Data Bit 2                                         | Enable<br>Receiver<br>Line Status<br>Interrupt<br>(ERLSI)                     | Interrupt<br>ID Bit 2<br>(IIDB2)                       | Transmitter<br>FIFO<br>Reset<br>(TFR)          | Number of<br>Stop Bits<br>(STB)          |  |  |

| 3          | Data Bit 3                                    | Data Bit 3                                         | Enable<br>Modem<br>Status<br>Interrupt<br>(EDSSI)                             | Interrupt<br>ID Bit 3<br>(IIDB3)*                      | DMA<br>Mode<br>Select<br>(DMS)                 | Parity<br>Enable<br>(PEN)                |  |  |

| 4          | Data Bit 4                                    | Data Bit 4                                         | 0                                                                             | 0                                                      | Reserved                                       | Even<br>Parity<br>Select<br>(EPS)        |  |  |

| 5          | Data Bit 5                                    | Data Bit 5                                         | 0                                                                             | 0                                                      | Reserved                                       | Stick Parity<br>(STP)                    |  |  |

| 6          | Data Bit 6                                    | Data Bit 6                                         | 0                                                                             | FIFO<br>Enabled *<br>(Read Only)<br>(FERO)             | Rcvr FIFO<br>Trigger Level<br>(LSB)(RTLSB)     | Set Break<br>Control<br>(SBR)            |  |  |

| 7          | Data Bit 7                                    | Data Bit 7                                         | 0                                                                             | FIFO<br>Enabled *<br>(Read Only)<br>(FERO)             | Rcvr FIFO<br>Trigger Level<br>(MSB)<br>(RTMSB) | Divisor<br>Latch<br>Access Bit<br>(DLAB) |  |  |

| (♦) The    | (♦) These bits are 0 in Character Mode.       |                                                    |                                                                               |                                                        |                                                |                                          |  |  |

TABLE 3-3. ACCESSIBLE WD16C452/WD16C552 REGISTERS

| REGISTER ADDRESS |                                         |                                                    |                                                      |                            |                           |                           |

|------------------|-----------------------------------------|----------------------------------------------------|------------------------------------------------------|----------------------------|---------------------------|---------------------------|

|                  | 4                                       | 5                                                  | 6                                                    | 7                          | 0 DLAB=1                  | 1 DLAB=1                  |

| Bit<br>No.       | Modem<br>Control<br>Register            | Line<br>Status<br>Register                         | Modem<br>Status<br>Register                          | Scratch<br>Pad<br>Register | Divisor<br>Latch<br>(LSB) | Divisor<br>Latch<br>(MSB) |

| 0                | Data<br>Terminal<br>Ready<br>(DTR)      | Data<br>Ready<br>(DR)                              | Delta<br>Clear to<br>Send<br>(DCTS)                  | Bit 0                      | Bit 0                     | Bit 8                     |

| 1                | Request<br>to Send<br>(RTS)             | Overrun<br>Error<br>(OE)                           | Delta<br>Data Set<br>Ready<br>(DDSR)                 | Bit 1                      | Bit 1                     | Bit 9                     |

| 2                | Not<br>Connected<br>(NC)                | Parity<br>Error<br>(PE)                            | Trailing<br>Edge Ring<br>Indicator<br>(TERI)         | Bit 2                      | Bit 2                     | Bit 10                    |

| 3                | Interrupt<br>(Int)                      | Framing<br>Error<br>(FE)                           | Delta<br>Receive<br>Line Signal<br>Detect<br>(DRLSD) | Bit 3                      | Bit 3                     | Bit 11                    |

| 4                | Loop                                    | Break<br>Interrupt<br>(BI)                         | Clear to<br>Send<br>(CTS)                            | Bit 4                      | Bit 4                     | Bit 12                    |

| 5                | 0                                       | Transmitter<br>Holding<br>Register<br>Empty (THRE) | Data Set<br>Ready<br>(DSR)                           | Bit 5                      | Bit 5                     | Bit 13                    |

| 6                | 0                                       | Transmitter<br>Empty<br>(TEMT)                     | Ring<br>Indicator<br>(RI)                            | Bit 6                      | Bit 6                     | Bit 14                    |

| 7                | 0                                       | Error in<br>RCVR<br>FIFO <sup>†</sup><br>(EIRF)    | Received<br>Line Signal<br>Detect<br>(RLSD)          | Bit 7                      | Bit 7                     | Bit 15                    |

| ( <b>♦</b> ) The | (♦) These bits are 0 in Character Mode. |                                                    |                                                      |                            |                           |                           |

TABLE 3-3. ACCESSIBLE WD16C452/WD16C552 REGISTERS (Contd)

#### 3.3 LINE CONTROL REGISTER

**Bits 0 and 1:** These two bits specify the number of bits in each transmitted or received serial character. The encoding of bits 0 and 1 are as follows:

| Bit 1 | Bit 0 | Word Length |

|-------|-------|-------------|

| 0     | 0     | 5 bits      |

| 0     | 1     | 6 bits      |

| 1     | 0     | 7 bits      |

| 1     | 1     | 8 bits      |

**Bit 2:** This bit specifies the number of stop bits in each transmitted or received serial character. If bit 2 is logic 0, 1 Stop bit is generated or checked in the transmit or receive data, respectively. If bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, 1-1/2 Stop bits are generated or checked. If bit 2 is a logic 1 when either a 6-, 7-, or 8-bit word length is selected, 2 Stop bits are generated or checked.

**Bit 3:** This bit is the Parity Enable bit. When bit 3 is a logic 1, a Parity bit is generated (Transmit data) or checked (Receive data) between the last data word bit and Stop bit of the serial data. (The Parity bit is used to produce an even or odd number of 1's when the data word bits and the Parity bit are summed.)

**Bit 4:** This bit is the Even Parity Select bit. When bit 3 is a logic 1 and bit 4 is a logic 0, an odd number of logic 1's is transmitted or checked in the data word bits and Parity bit. When bit 3 is a logic 1 and bit 4 is a logic 1, an even number of bits is transmitted or checked.

**Bit 5:** This bit is the Stick Parity bit. When bit 3 is a logic 1 and bit 5 is a logic 1, the Parity bit is

transmitted and then detected by the receiver in the opposite state indicated by bit 4.

**Bit 6:** This bit is the Set Break Control bit. When bit 6 is a logic 1, the serial output (SOUT) is forced to the Spacing (logic 0) state and remains there (until reset by a low-level bit 6) regardless of other transmitter activity. This feature enables the CPU to alert a terminal in a computer communications system.

**Bit 7:** This bit is the Divisor Latch Access Bit (DLAB). It must be set high (logic 1) to access the Divisor Latches of the Baud Rate Generator during a Read or Write operation. It must be set low (logic 0) to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.

# 3.4 ACE PROGRAMMABLE BAUD RATE GENERATOR

The ACE contains a programmable Baud Rate Generator capable of taking any clock input (dc to 8.0 MHz) and dividing it by any divisor from 1 to (2<sup>16</sup> - 1). The output frequency of the Baud Generator is 16 times the baud rate. Two 8-bit latches store the divisor in a 16-bit binary format. These Divisor Latches must be loaded during initialization in order to insure desired operation of the Baud Rate Generator. Upon loading either of the Divisor Latches, a 16-bit Baud counter is immediately loaded. This prevents long counts on initial load.

Tables 3-3, 3-5, and 3-6 illustrate the use of the Baud Generator with three different driving frequencies. One is referenced to a 1.8432 MHz clock. Another is a 3.072 MHz clock. The third is an 8.0 MHz clock.

Note: The maximum operating frequency of the Baud Generator is 8.0 MHz.

In no case should the data rate be greater than 512K baud.

| Desired<br>Baud<br>Rate | Divisor Used<br>to Generate<br>16 Times Clock | Percent Error<br>Difference Between<br>Desired and Actual |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 50                      | 2304                                          |                                                           |

| 75                      | 1536                                          | <del></del>                                               |

| 110                     | 1047                                          | 0.026                                                     |

| 134.5                   | 857                                           | 0.058                                                     |

| 150                     | 768                                           |                                                           |

| 300                     | 384                                           |                                                           |

| 600                     | 192                                           |                                                           |

| 1200                    | 96                                            |                                                           |

| 1800                    | 64                                            |                                                           |

| 2000                    | 58                                            | 0.690                                                     |

| 2400                    | 48                                            |                                                           |

| 3600                    | 32                                            |                                                           |

| 4800                    | 24                                            |                                                           |

| 7200                    | 16                                            |                                                           |

| 9600                    | 12                                            | <del></del>                                               |

| 19200                   | 6                                             |                                                           |

| 38400                   | 3                                             |                                                           |

| 56000                   | 2                                             | 2.860                                                     |

TABLE 3-4. BAUD RATES USING 1.8432 MHz CLOCK

| Desired<br>Baud<br>Rate | Divisor Used<br>to Generate<br>16 Times Clock | Percent Error<br>Difference Between<br>Desired and Actual |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 50                      | 3840                                          |                                                           |

| 75                      | 2560                                          |                                                           |

| 110                     | 1745                                          | 0.026                                                     |

| 134.5                   | 1428                                          | 0.034                                                     |

| 150                     | 1280                                          | <del></del>                                               |

| 300                     | 640                                           |                                                           |

| 600                     | 320                                           | <del></del>                                               |

| 1200                    | 160                                           |                                                           |

| 1800                    | 107                                           |                                                           |

| 2000                    | 96                                            |                                                           |

| 2400                    | 80                                            |                                                           |

| 3600                    | 53                                            | 0.628                                                     |

| 4800                    | 40                                            |                                                           |

| 7200                    | 27                                            | 1.230                                                     |

| 9600                    | 20                                            |                                                           |

| 19200                   | 10                                            |                                                           |

| 38400                   | 5                                             |                                                           |

| 56000                   | 3                                             | 14.285                                                    |

TABLE 3-5. BAUD RATES USING 3.072 MHz CLOCK

| Desired<br>Baud<br>Rate | Divisor Used<br>to Generate<br>16 Times Clock | Percent Error<br>Difference Between<br>Desired and Actual |

|-------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 50                      | 10000                                         |                                                           |

| 75                      | 6667                                          | 0.005                                                     |

| 110                     | 4545                                          | 0.010                                                     |

| 134.5                   | 3717                                          | 0.013                                                     |

| 150                     | 3333                                          | 0.010                                                     |

| 300                     | 1667                                          | 0.020                                                     |

| 600                     | 833                                           | 0.040                                                     |

| 1200                    | 417                                           | 0.080                                                     |

| 1800                    | 277                                           | 0.080                                                     |

| 2000                    | 250                                           |                                                           |

| 2400                    | 208                                           | 0.160                                                     |

| 3600                    | 139                                           | 0.080                                                     |

| 4800                    | 104                                           | 0.160                                                     |

| 7200                    | 69                                            | 0.644                                                     |

| 9600                    | 52                                            | 0.160                                                     |

| 19200                   | 26                                            | 0.160                                                     |

| 38400                   | 13                                            | 0.160                                                     |

| 56000                   | 9                                             | 0.790                                                     |

| 128000                  | 4                                             | 2.344                                                     |

| 256000                  | 2                                             | 2.344                                                     |

| 512000                  | 1                                             | 2.344                                                     |

TABLE 3-6. BAUD RATES USING 8.0 MHz CLOCK

#### 3.5 LINE STATUS REGISTER

This 8-bit read and write register provides status information to the CPU concerning the data transfer. Its contents are indicated in Table 3-3 and are described below.

**Bit 0:** This bit is the Receiver Data Ready (DR) indicator. Bit 0 is set to a logic 1 whenever a complete incoming character has been received and transferred into the Receiver Buffer Register, or to the RCVR FIFO (when in FIFO Mode). Bit 0 will be reset to a logic 0 by the CPU reading the data in the Receiver Buffer Register (for Character Mode).

In FIFO Mode, Receiver Data Ready is set when the receiver shift register is loaded into the FIFO and reset when the receiver FIFO is empty.

**Bit 1:** This bit is the Overrun Error (OE) indicator. Bit 1 indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, thereby destroying the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register.

When in FIFO Mode, an OE occurs after the RCVR FIFO is full and the receiver shift register has completely received the next character. An OE is indicated to the CPU as soon as it occurs. The character in the shift register will be written over, but nothing will be transferred to the FIFO.

**Bit 2:** This bit is the Parity Error (PE) indicator. Bit 2 indicates that the received data character does not have the correct even or odd parity, as selected by the even-parity-select bit. The PE bit is set to a logic 1 upon detection of a parity error and is reset to logic 0 whenever the CPU reads the contents of the Line Status Register.

When in FIFO Mode a parity error is associated with a particular character in the FIFO, and revealed to the CPU when the associated character is in the top of the FIFO.

**Bit 3:** This bit is the Framing Error (FE) indicator. Bit 3 indicates that the received character did not have a valid Stop Bit. Bit 3 is set to a logic 1 whenever the Stop Bit following the last data bit or parity bit is detected as a zero bit (Spacing Level). Bit 3 is reset to logic 0 whenever the CPU reads the contents of the Line Status Register. When in FIFO

Mode, an FE is associated with a particular character in the FIFO, and revealed to the CPU when the associated character is in the top of the FIFO.

**Bit 4:** This bit is the Break Interrupt (BI) indicator. Bit 4 is set to a logic 1 whenever the received data input is held in the Spacing (Logic 0) state for longer than a full word transmission time (that is, the total time of Start Bit + data bits + Parity + Stop Bits). Bit 4 is reset to logic 0 whenever the CPU reads the contents of the Line Status Register. Restarting after a break is received requires the SIN pin be high for at least one-half (1/2) bit time.

When in FIFO Mode, BI is associated to the particular character in the FIFO, and this bit is set when the associated character is in the top of the FIFO.

Note: Bits 1 through 4 are the error conditions that produce a Receiver Line Status interrupt whenever any of the corresponding conditions are detected and Receiver Line Status interrupt is enabled. All bits except bit 7 of the Status Register can be set or reset by writing to the register.

**Bit 5:** This bit is the Transmitter Holding Register Empty (THRE) indicator. Bit 5 indicates that the ACE is ready to accept a new character for transmission. This bit also causes the ACE to issue an interrupt to the CPU when the Transmit Holding Register Empty Interrupt enable is set high. The THRE bit is set to a logic 1 when a character is transferred from the Transmitter Holding Register into the Transmitter Shift Register. The bit is reset to logic 0 concurrently with the loading of the Transmitter Holding Register by the CPU.

When in the FIFO Mode, this bit will be set when the XMIT FIFO is empty, and cleared after at least one character is written into the XMIT FIFO. The Transmitter FIFO Empty indications will be delayed one character time minus the last Stop bit time whenever the following occurs: the Transmitter FIFO is empty and there have not been at least two characters in Transmitter FIFO at the same time since the last time that Transmitter FIFO was empty. The first transmitter interrupt after changing the first bit of FIFO Control Register will be immediate if it is enabled.

**Bit 6:** This bit is the Transmitter Empty (TEMT) indicator. Bit 6 is set to a logic 1 when both transmitter registers (Transmitter Holding Register and Transmitter Shift Register) are idle (empty). It is reset to a logic 0 upon loading of data into the Transmitter Holding Register.

In FIFO Mode this bit is set when the XMIT FIFO and XMIT Shift Register are both empty. It is cleared when at least one byte is written into the XMIT FIFO.

**Bit 7:** This bit (LSR7) is 0 when in Character Mode. When in FIFO Mode, this bit is a one if there is at least one parity error, framing error or break indication in the FIFO. LSR7 is cleared when this register is read as long as there are no additional errors in the FIFO.

# 3.6 INTERRUPT IDENTIFICATION REGISTER

The ACE has an interrupt capability that allows for complete flexibility in interfacing to all popular microprocessors presently available. In order to provide minimum software overhead during data character transfers, the ACE prioritizes interrupts into four levels. The four levels of interrupt conditions are as follows: Receiver Line Status (priority 1); Received Data Ready (priority 2); Transmitter Holding Register Empty (priority 3); and Modem Status (priority 4).

Information indicating that a prioritized interrupt is pending and source of that interrupt is stored in the Interrupt Identification Register (refer to Table 3-3).

This register (IIR), when addressed during chipselect time, freezes the highest priority interrupt pending and no other interrupts are acknowledged until the particular interrupt is serviced by the CPU. Its contents are indicated in Table 3-7 and are described below.

**Bit 0:** This bit can be used in either a hardwired prioritized or polled environment to indicate whether an interrupt is pending. When bit 0 is a logic 0, an interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When bit 0 is a logic 1, no interrupt is pending and polling (if used) continues.

**Bits 1 through 3:** These three bits are used to identify the highest priority interrupt pending (see Table 3-7).

Bits 4 and 5: These bits are always logic 0.

Bits 6 and 7: These bits, when set, indicate that the device is in FIFO Mode (FCR0 = 1).

| INT   | INTERRUPT IDENTIFICATION REGISTER |       |       |                   | INTERR                                      | UPT SET AND RES                                                                                                                                     | ET FUNCTIONS                                                                                                      |

|-------|-----------------------------------|-------|-------|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Bit 3 | Bit 2                             | Bit 1 | Bit 0 | Priority<br>Level | Interrupt<br>Flag                           | Interrupt<br>Source                                                                                                                                 | Interrupt<br>Reset Control                                                                                        |

| 0     | 0                                 | 0     | 1     |                   | None                                        | None                                                                                                                                                |                                                                                                                   |

| 0     | 1                                 | 1     | 0     | Highest           | Receiver<br>Line Status                     | Overrun Error<br>or Parity Error<br>or Framing Error<br>or Break Interrupt                                                                          | Reading the<br>Line Status<br>Register                                                                            |

| 0     | 1                                 | 0     | 0     | Second            | Received Data<br>Available                  | Receiver Data<br>Available                                                                                                                          | Reading the<br>Receiver Buffer<br>Register                                                                        |

| 1     | 1                                 | 0     | 0     | Second            | Character<br>Timeout<br>Identification      | No Characters have been input or removed from RCVR FIFO during the last 4 character times, and at least one character occupies it during this time. | Reading the<br>Receiver Buffer<br>Register                                                                        |

| 0     | 0                                 | 1     | 0     | Third             | Transmitter<br>Holding<br>Register<br>Empty | Transmitter<br>Holding<br>Register<br>Empty                                                                                                         | Reading the IIR<br>Register (if source<br>of interrupt) or<br>Writing into the<br>Transmitter<br>Holding Register |

| 0     | 0                                 | 0     | 0     | Fourth            | Modem<br>Status                             | Clear to Send<br>or Data Set or<br>Ring Indicator<br>or Received Line<br>Signal Detect                                                              | Reading the<br>MODEM Status<br>Register                                                                           |

**TABLE 3-7. INTERRUPT CONTROL FUNCTIONS**

#### 3.7 INTERRRUPT ENABLE REGISTER

This 8-bit register enables the four interrupt sources of the ACE to separately activate the device Interrupt (INT) output signal, when bit 3 of MCR is a logic 1. Its contents are indicated in Table 3-3 and are described below. It is possible to totally disable the interrupt system by resetting bits 0 through 3 of the Interrupt Enable Register. Similarly, by setting the appropriate bits of this register to a logic 1, selected interrupts can be enabled. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INT output from the device. All other system functions operate in their normal manner, including the setting of the Line Status and Modem Status Registers.

**Bit 0:** This bit enables the Received Data Available Interrupt when set to logic 1.

**Bit 1:** This bit enables the Transmitter Holding Register Empty Interrupt when set to logic 1.

**Bit 2:** This bit enables the Receiver Line Status Interrupt when set to logic 1.

**Bit 3:** This bit enables the Modern Status Interrupt when set to logic 1.

**Bits 4 through 7:** These four bits are always logic 0

#### 3.8 SCRATCH PAD REGISTER

This 8-bit register does not control or report status on any part of the ACE. It is a read/write register that can be used by the programmer as a general purpose register.

#### 3.9 FIFO CONTROL REGISTER

This write only register is located at the same address as the IIR (read only). This register is used to enable FIFO Mode, clear FIFOs, set the RCVR

FIFO trigger levels, and select the mode of DMA signaling.

**Bit 0:** Writing a one to this bit enables the XMIT and RCVR FIFOs. When changing from Character Mode to FIFO Mode, data in the FIFOs does not automatically clear. Resetting FCR0 will clear all characters from RCVR Error FIFO. The FIFOs should be cleared immediately after changing to FIFO mode. This bit must be a 1 before writing to other FCR bits or they will not be programmed.

**Bit 1:** Writing a 1 to FCR1 will clear all bytes from RCVR Error FIFO and reset its counters to 0, and then self clear this bit to 0. The shift register and RCVR FIFO are not cleared.

**Bit 2:** Functions the same as bit 1, but for XMIT FIFO.

**Bit 3:** If FCR0 = 1, setting FCR3 to a 1 will cause the RXRDY and TXRDY pins to change from Mode 0 to Mode 1 (see pin description of RXRDY and TXRDY).

Bits 4 and 5: Reserved for future use.

**Bits 6 and 7:** These bits control the trigger level of the RCVR FIFO interrupt.

| 7 | 6 | RCVR FIFO TRIGGER<br>LEVEL (BYTES) |

|---|---|------------------------------------|

| 0 | 0 | 01                                 |

| 0 | 1 | 04                                 |

| 1 | 0 | 08                                 |

| 1 | 1 | 14                                 |

#### 3.10 MODEM CONTROL REGISTER

This 8-bit register controls the interface either with the modem or data set (or a peripheral device emulating a modem). The contents of the Modem Control Register are indicated in Table 3-3.

**<u>Bit 0</u>**: This bit controls the Data Terminal Ready (<u>DTR</u>) output. When bit 0 is set to a logic 1, the DTR output is forced to a logic 0. When bit 0 is reset to a logic 0, the DTR output is forced to a logic 1.

Note: The DTR output of the ACE may be applied to an EIA inverting line driver (such as the DS1488) to obtain the proper polarity input at the succeeding MODEM or data set.

- **Bit 1:** This bit controls the <u>Request to Send (RTS)</u> output. Bit 1 affects the RTS output in a manner identical to that described above for bit 0.

- **Bit 2:** No connect. In loopback mode this bit is connected to the Modem Status Register bit 6.

- **Bit 3:** This bit enables the INT output pin. When this bit is a logic 0 the INT output pin is tristated. In loopback mode this bit is connected to bit 7 of the Modem Status Register.

- **Bit 4:** This bit provides a loopback feature for diagnostic testing of the ACE. When bit 4 is set to logic 1, the following occurs: the transmitter Serial Output (SOUT) is set to a logic 1 (high) state; the receiver Serial Input (SIN) is disconnected; the output of the Transmitter Shift Register is "looped back" into the Receiver Shift Register input; the four Modem Control Inputs (CTS, DSR, RLSD, and Rl) are disconnected; and the four Modem Control bits (0-3) are internally connected to the four MODEM Control inputs. The INT output pin is tri-stated when in loopback mode. In the diagnostic mode, data that is transmitted is immediately received. This feature allows the processor to verify the transmit- and receive-data paths of the ACE.

In the diagnostic mode, the receiver and transmitter interrupts are fully operational. The Modem Control Interrupts are also operational but the interrupts' sources are now the lower four bits of the Modem Control Register instead of the four Modem Control inputs. The interrupts are still controlled by the Interrupt Enable Register.

The ACE modem interrupt system can be tested by writing into the lower four bits of the Modem Status Register. To return to this operation, the registers must be reprogrammed for normal operation and then bit 4 must be reset to a logic 0.

**Bits 5 through 7**: These bits are permanently set to a logic 0.

#### 3.11 MODEM STATUS REGISTER

This 8-bit register provides the current state of the control lines from the modem (or peripheral device) to the CPU. In addition to this information, four bits of the Modem Status Register provide change information. These bits are set to a logic 1 whenever a control input from the modem changes state. They are reset to logic 0 whenever the CPU reads the MODEM Status Register.

The contents of the Modem Status Register are indicated in Table 4-2 and are described below.

- **Bit 0:** This bit is the Delta Clear to Send (DCTS) indicator. Bit 0 indicates that the CTS input to the device has changed state since the last time it was read by the CPU.

- **Bit 1:** This bit is the Delta Data Set Ready (DDSR) indicator. Bit 1 indicates that the DSR input to the device has changed since the last time it was read by the CPU.

- **Bit 2:** This bit is the Trailing Edge of Ring Indicator (TERI) detector. Bit 2 indicates that the RI input to the device has changed from an On (logic 1) to an Off (logic 0) condition.

- **Bit 3:** This bit is the Delta Received Line Signal <u>Detector</u> (DRLSD) indicator. Bit 3 indicates that the RLSD input to the device has changed state.

Note: Whenever bit 0, 1, 2, or 3 is set to logic 1, a Modern Status Interrupt is generated.

- **Bit 4:** This bit is the complement of the Clear to Send (CTS) input. This bit becomes equivalent to RTS of the Modem Control Register, if Bit 4 of the Modem Control Register is set to 1.

- **Bit 5:** This bit is the complement of the Data Set Ready (DSR) input. This bit becomes equivalent to DTR of the Modem Control Register, if Bit 4 of the Modem Control Register is set to 1.

//

FIGURE 3-1. INTERRUPT SIGNAL LOGIC

**Bit 6:** This bit is the complement of the Ring Indicator (RI) input. This bit becomes equivalent to Bit 2 of the Modem Control Register, if Bit 4 of the Modem Control Register is set to 1.