# WD7910/LP

ISA-Based System Controller

with Cache for 80386SX and 80286

Desktop and Portable Compatibles

## **TABLE OF CONTENTS**

| Section | Title Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | INTRODUCTION       7-1         1.1 Document Scope       7-1         1.2 Features       7-1         1.3 General Description       7-2         1.3.1 WD7710       7-2         1.3.2 WD7710LP       7-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.0     | ARCHITECTURE 7-2 2.1 Initialization And Clocking 7-2 2.2 AT Bus 7-2 2.3 Main Processor Control 7-2 2.4 Numeric Processor Control 7-2 2.5 Data Bus 7-2 2.6 Memory and EMS Control 7-2 2.7 Power Management Control 7-2 2.8 Register File 7-5 2.8.1 Lock Status Register 7-5 2.8.2 Lock/Unlock Register 7-6 2.9 VLBI Control 7-6 2.10 Cache Control 7-6                                                                                                                                                                                                                                                                                                                          |

| 3.0     | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.0     | INITIALIZATION AND CLOCKING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.0     | AT BUS       7-24         5.1       Interrupt Multiplexing       7-24         5.1.1       Data Acknowledge DACK7-5, 3-0       7-24         5.1.2       Data Request DRQIN       7-24         5.1.3       Interrupt Requests       7-24         5.1.4       AT Address Bus, Data Bus, And Terminal Count (TC) Signal       7-24         5.2       Power Management Control PMCIN       7-24         5.3       Numeric Processor       7-26         5.3.1       Numeric Processor Busy, Bus Timing, And Power Down Register       7-26         5.3.2       Numeric Processor Busy (NPBUSY)       Reset       7-28         5.3.3       Numeric Processor Reset (NPRST)       7-28 |

| Section | Title |         |            |                                          |        | Page     |

|---------|-------|---------|------------|------------------------------------------|--------|----------|

|         | 5.4   | DMA C   | ontrol     |                                          |        | 7-29     |

|         |       | 5.4.1   | Transfer   | Modes                                    |        | <br>7-29 |

|         |       | 5.4.2   | Transfer ' | Types                                    |        | <br>7-29 |

|         |       | 5.4.3   | Autoinitia | lize                                     |        | <br>7-30 |

|         |       | 5.4.4   | Priority   |                                          |        | <br>7-30 |

|         |       | 5.4.5   | Extended   |                                          |        | <br>7-30 |

|         |       | 5.4.6   | Base and   | Current Address                          |        | <br>7-30 |

|         |       | 5.4.7   | Base and   | Current Word Count                       |        | <br>7-30 |

|         |       | 5.4.8   | Comman     | d Register                               |        | <br>7-32 |

|         |       | 5.4.9   | Status Re  | egister                                  |        | <br>7-32 |

|         |       | 5.4.10  | Request    |                                          |        |          |

|         |       | 5.4.11  | Mask Reg   | gisters                                  |        | <br>7-32 |

|         |       |         | 5.4.11.1   | Single Mask Register                     |        | <br>7-33 |

|         |       |         | 5.4.11.2   | Clear Mask Register                      |        | <br>7-33 |

|         |       |         | 5.4.11.3   | Mask Multiple Register                   |        |          |

|         |       | 5.4.12  | Mode Re    | gister                                   |        | <br>7-33 |

|         |       | 5.4.13  |            | nter Register                            |        | <br>7-34 |

|         |       | 5.4.14  | Master C   | ear Register                             |        | <br>7-34 |

|         |       | 5.4.15  | DMA Mod    | le Shadow Register                       |        |          |

|         | 5.5   | System  |            | 8259 Interrupt Controllers               |        | 7-35     |

|         |       | 5.5.1   |            | Sequence                                 |        | <br>7-35 |

|         |       | 5.5.2   | Setup - In | itialization Command Words (ICW)         |        | <br>7-37 |

|         |       |         | 5.5.2.1    | ICW1 - Initialization Command Word 1     |        | <br>7-37 |

|         |       |         | 5.5.2.2    | ICW2 - Initialization Command Word 2     | <br>٠. | <br>7-37 |

|         |       |         | 5.5.2.3    | ICW3 - Initialization Command Word 3     |        | <br>7-37 |

|         |       |         | 5.5.2.4    | ICW4 - Initialization Command Word 4     |        | <br>7-38 |

|         |       | 5.5.3 O | peration . |                                          |        | <br>7-38 |

|         |       |         | 5.5.3.1    | OCW1 - Operation Control Word 1          |        | <br>7-38 |

|         |       |         | 5.5.3.2    | OCW2 - Operation Control Word 2          |        | <br>7-39 |

|         |       |         | 5.5.3.3    | OCW3 - Operation Control Word 3          |        | <br>7-39 |

|         | 5.6   | System  | Controller | 8254 Timer                               |        | <br>7-40 |

|         |       | 5.6.1   | Setup .    |                                          |        | <br>7-41 |

|         |       |         | 5.6.1.1    | Mode 0 Interrupt On Terminal Count       |        | <br>7-41 |

|         |       |         | 5.6.1.2    | Mode 1 Hardware Retriggerable One Shot . |        | <br>7-41 |

|         |       |         | 5.6.1.3    | Mode 2 Rate Generator                    |        | <br>7-41 |

|         |       |         | 5.6.1.4    | Mode 3 Square Wave Generator             |        | <br>7-41 |

|         |       |         | 5.6.1.5    | Mode 4 Software Triggered Strobe         |        | <br>7-41 |

|         |       |         | 5.6.1.6    | Mode 5 Hardware Triggered Strobe         |        | <br>7-41 |

|         |       | 5.6.2   | Reading 7  | The Counter                              |        | <br>7-42 |

| Section | Title |                                                         | Page |

|---------|-------|---------------------------------------------------------|------|

|         |       | 5.6.3 Reading Status                                    | 7-42 |

|         |       | 5.6.4 Page                                              | 7-42 |

|         |       | 5.6.5 Refresh Address                                   | 7-42 |

|         | 5.7   | System Controller Decode                                | 7-43 |

|         |       | 5.7.1 Page Register Decodes                             | 7-43 |

|         | 5.8   | NMI and Real-time Clock                                 | 7-44 |

|         |       | 5.8.1 Real-Time Clock Address Register                  | 7-44 |

|         |       | 5.8.2 Real-Time Clock Data Register                     | 7-44 |

|         |       | 5.8.3 Lock Pass, Alternate A20G, And Hot Reset Register | 7-44 |

|         | 5.9   | Parity Error and I/O Channel Check                      | 7-45 |

| 6.0     | MEM   | ORY AND EMS CONTROL                                     | 7-46 |

|         | 6.1   | DRAM Address And Data Bus                               | 7-46 |

|         | 6.2   | Memory Configuration                                    | 7-47 |

|         |       | 6.2.1 Memory Control                                    | 7-47 |

|         |       | 6.2.2 Memory Bank 3 Through Bank 0 Starting Address     | 7-49 |

|         |       | 6.2.3 Split Starting Address                            | 7-50 |

|         |       | 6.2.4 RAM Shadow And Write Protect                      | 7-52 |

|         |       | 6.2.5 High Memory Write Protect Boundary                | 7-54 |

|         | 6.3   | Memory Timing                                           | 7-55 |

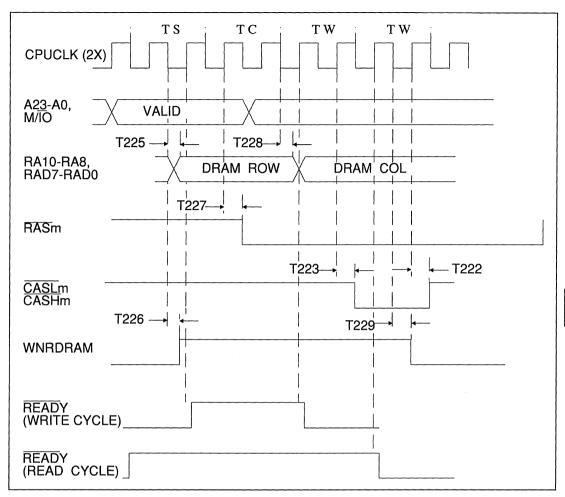

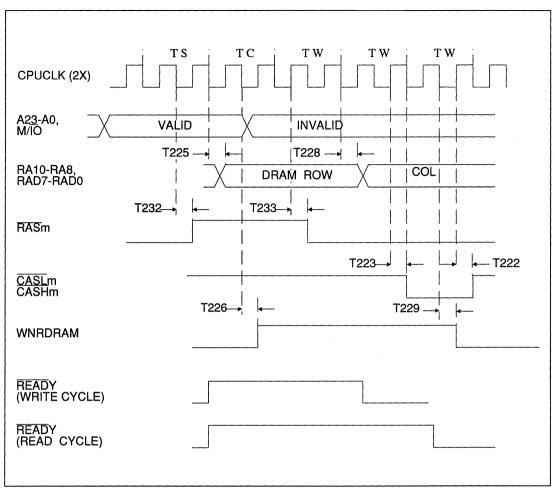

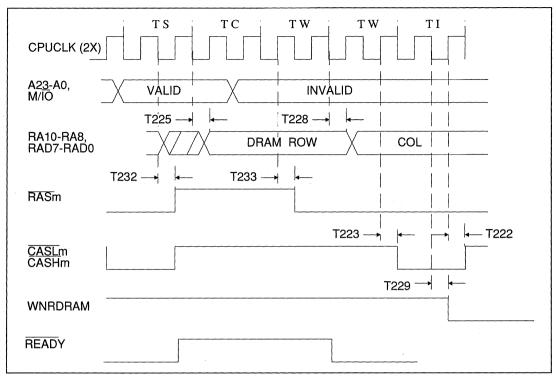

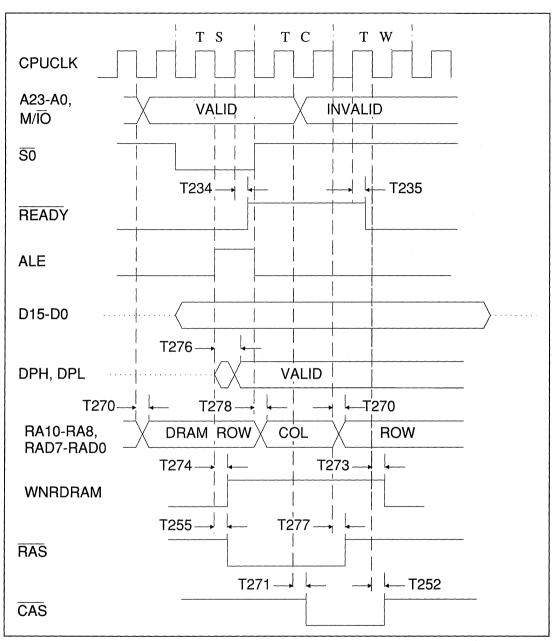

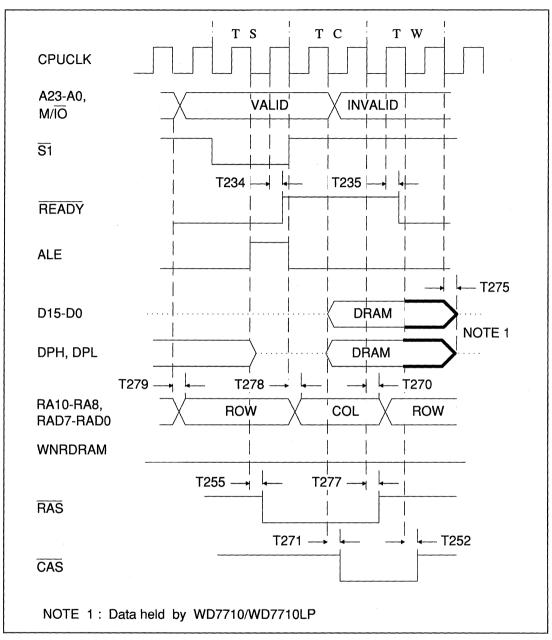

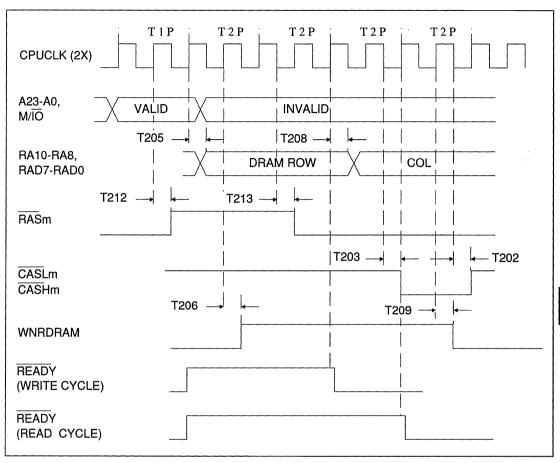

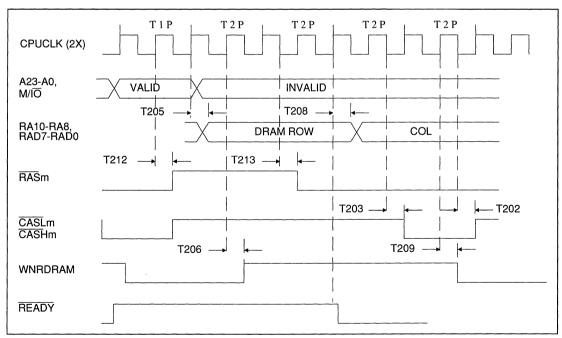

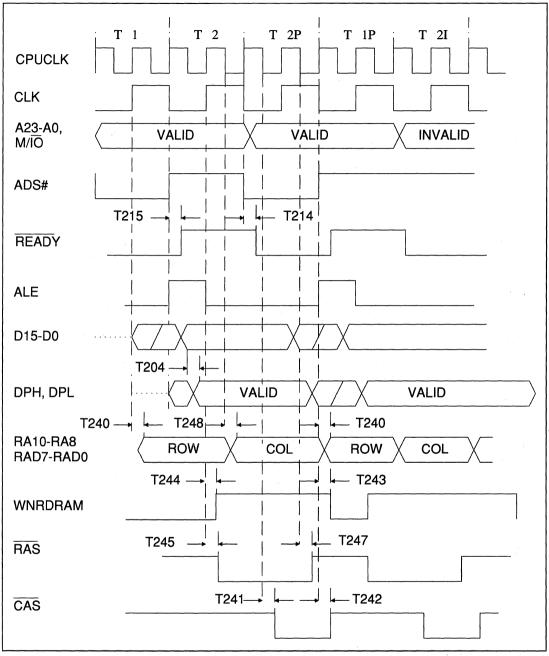

|         |       | 6.3.1 Non-page Mode DRAM Memory Timing                  | 7-55 |

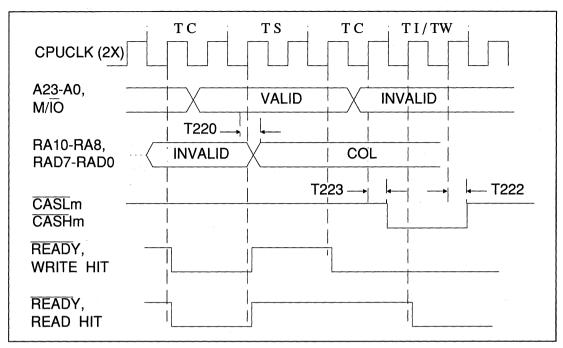

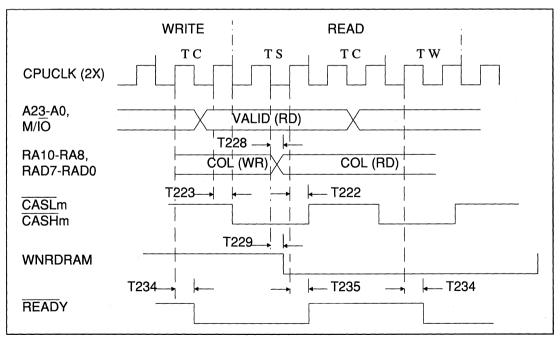

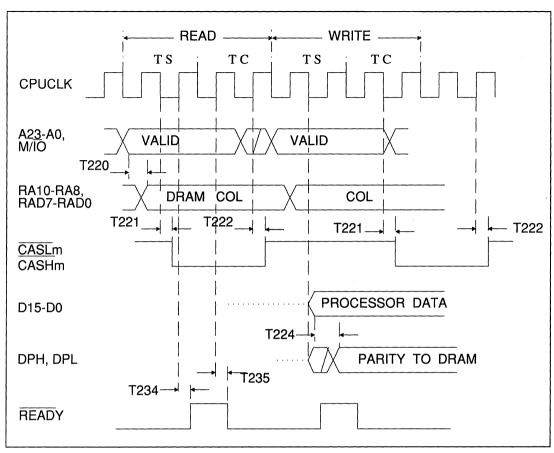

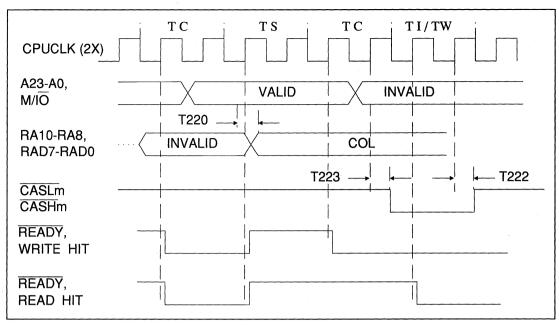

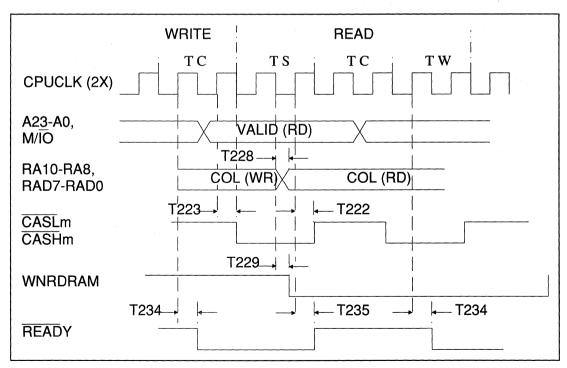

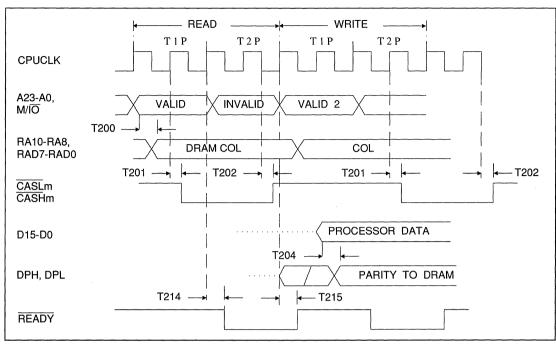

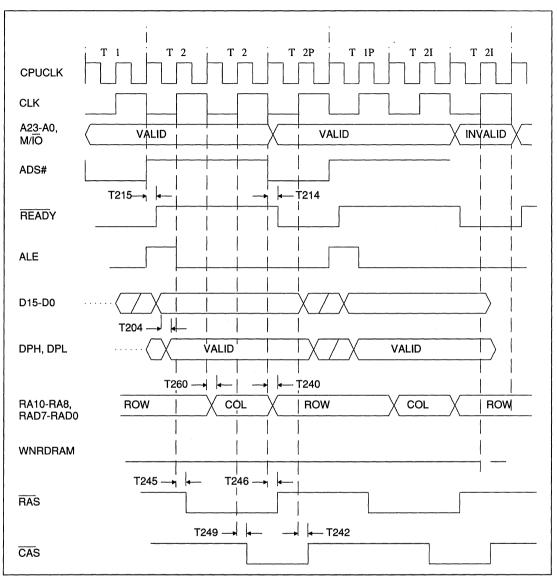

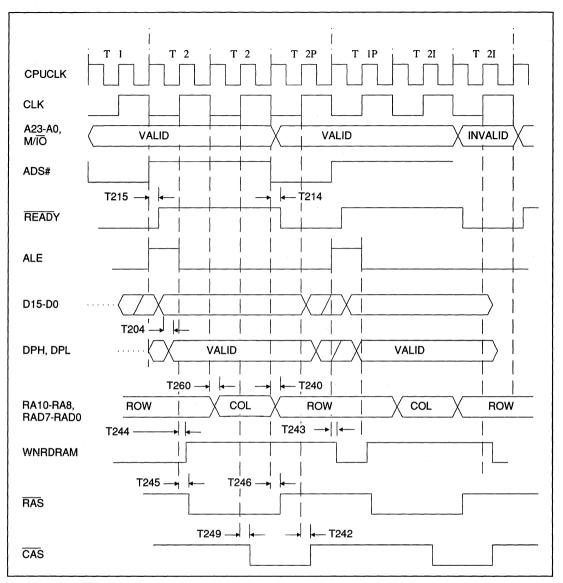

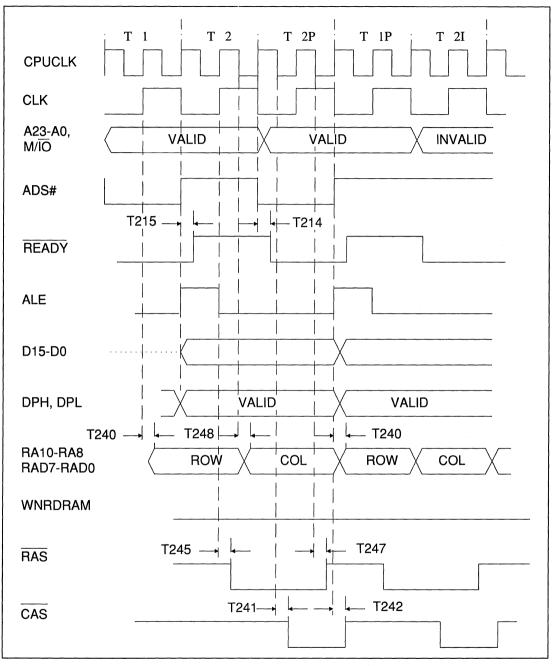

|         |       | 6.3.2 Page Mode                                         | 7-58 |

|         |       | 6.3.3 Memory Address Multiplexer                        | 7-59 |

|         | 6.4   | EMS                                                     | 7-61 |

|         |       | 6.4.1 EMS Control And Lower EMS Boundary                | 7-61 |

|         |       | •                                                       | 7-62 |

|         |       | 6.4.3 EMS Page Register                                 | 7-64 |

| 7.0     | CACH  | HE CONTROLLER                                           | 7-65 |

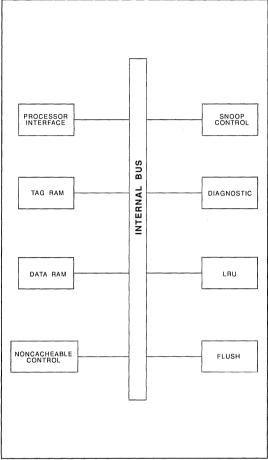

|         | 7.1   | Cache Architecture                                      | 7-65 |

|         |       | 7.1.1 Processor Interface                               | 7-65 |

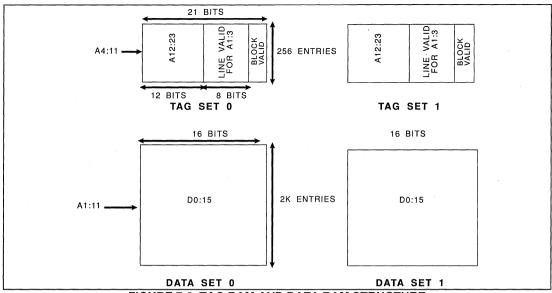

|         |       | 7.1.2 Tag RAM                                           | 7-65 |

|         |       | 7.1.3 Data RAM                                          | 7-66 |

|         |       | 7.1.4 Snoop Interface                                   | 7-66 |

|         |       | 7.1.5 Noncacheable Control                              | 7-67 |

|         |       | 7.1.6 Diagnostic Control Logic                          | 7-67 |

|         |       | 7.1.7 LRU                                               | 7-67 |

|         |       | 7.1.8 Flush                                             | 7-67 |

|         | 7.2   | Cache Control Register                                  | 7-67 |

|         |       | 7.2.1 Cacheable Region 1 Upper Boundary                 | 7-68 |

|         |       | 7.2.2 Noncacheable Region 1 Lower Boundary              | 7-69 |

|         |       | 7.2.3 Noncacheable Region 2 Lower Boundary              | 7-70 |

|         |       | 7.2.4 Flush                                             | 7-70 |

|         |       |                                                         |      |

| Section | Title                                                                                                                                                                                                                                          | Page                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 8.0     | PORT CHIP SELECT AND WD7710LP REFRESH CONTROL  8.1 Refresh Control, Serial And Parallel Chip Selects  8.2 RTC, PVGA, 80287 Timing, Disk Chip Selects  8.3 Programmable Chip Select Address  8.4 I/O Port Addresses And Chip Select Assignments | 7-71<br>7-73<br>7-75                                         |

| 9.0     | 9.5       PMC Inputs                                                                                                                                                                                                                           | 7-78<br>7-82<br>7-83<br>7-83<br>7-84<br>7-85                 |

|         |                                                                                                                                                                                                                                                | 7-86<br>7-87<br>7-88<br>7-90<br>7-92<br>7-92<br>7-93<br>7-94 |

| 10.0    | 9.14 Save And Resume  DIAGNOSTIC MODE  10.1 Diagnostic Register  10.2 Delay Line Diagnostic Register  10.3 Test Enable Register  10.4 Test Status Register                                                                                     | 7-96<br>7-96<br>7-98<br>7-98                                 |

| 11.0    | DC ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                   | 7-101                                                        |

| 12.0    | AC OPERATING CHARACTERISTICS                                                                                                                                                                                                                   | 7-105<br>7-105<br>7-125<br>7-129<br>7-132                    |

| Section | Title |          |                           |    |  |  |  |    |  |  |  | Page    |

|---------|-------|----------|---------------------------|----|--|--|--|----|--|--|--|---------|

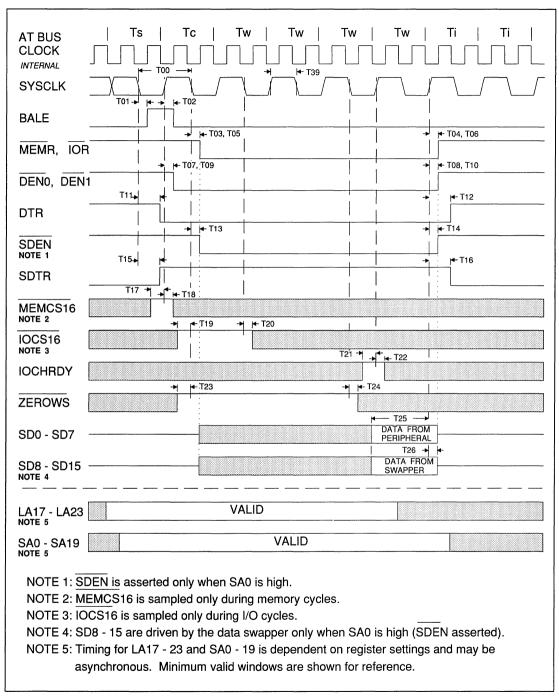

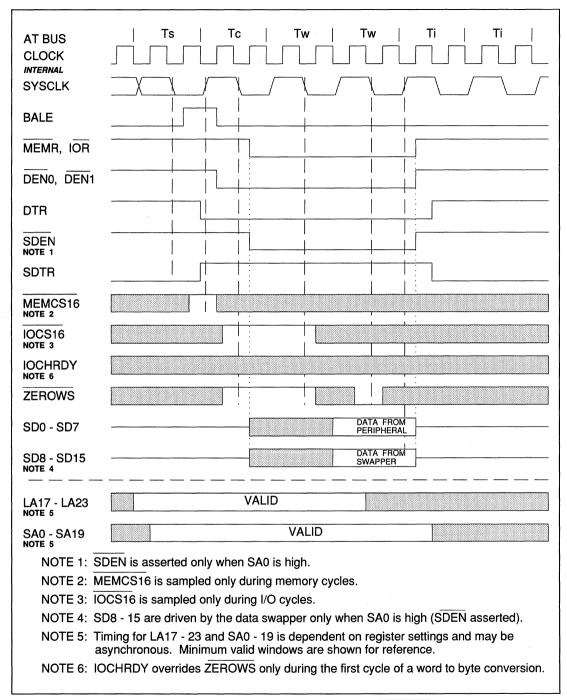

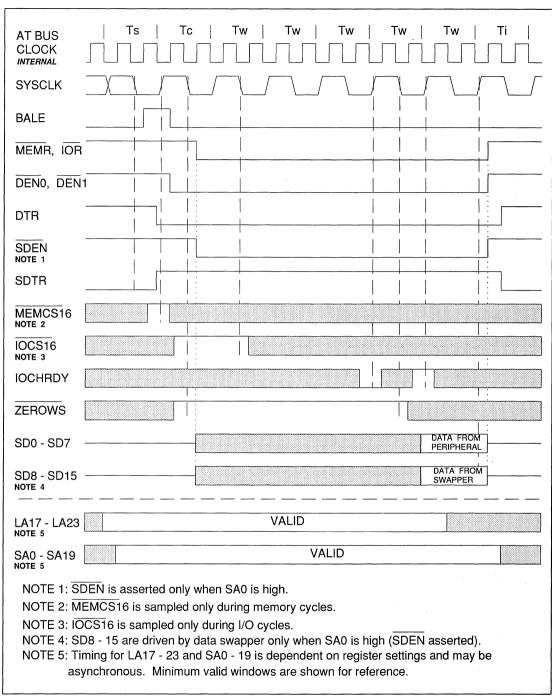

|         | 12.2  | AT Bus T | ning                      |    |  |  |  |    |  |  |  | . 7-129 |

|         |       | 12.2.1   | CPU Initiated AT Bus Cycl | es |  |  |  |    |  |  |  | . 7-129 |

|         |       | 12.2.2   | Entering The AT Bus       |    |  |  |  |    |  |  |  | . 7-141 |

|         |       | 12.2.3   | Exiting The AT Bus        |    |  |  |  |    |  |  |  | . 7-146 |

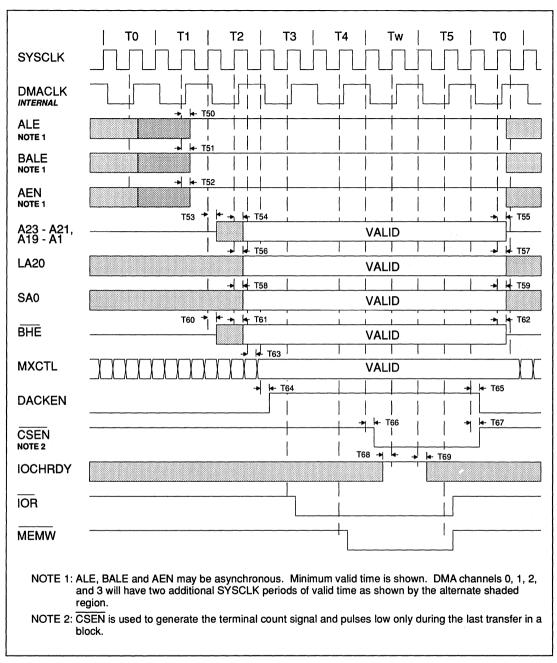

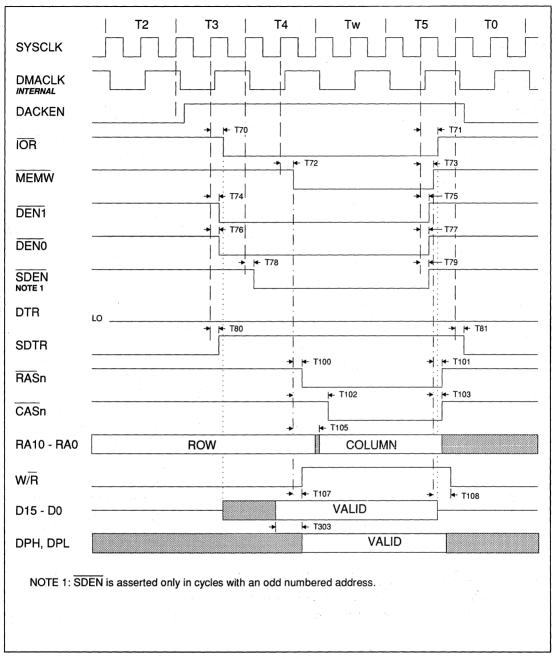

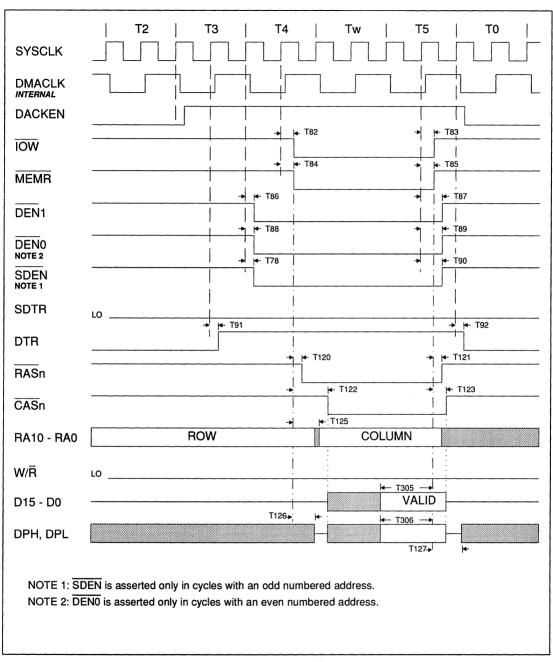

|         |       | 12.2.4   | DMA Cycles                |    |  |  |  |    |  |  |  | . 7-151 |

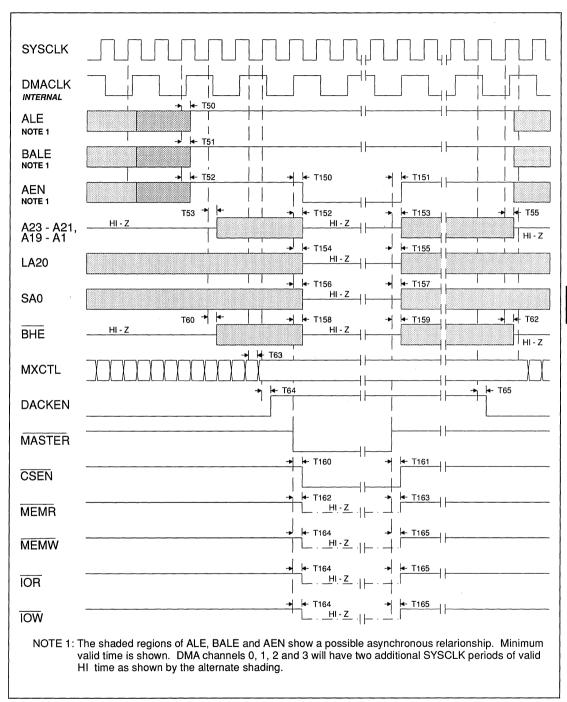

|         |       | 12.2.5   | AT Bus Master             |    |  |  |  |    |  |  |  | . 7-156 |

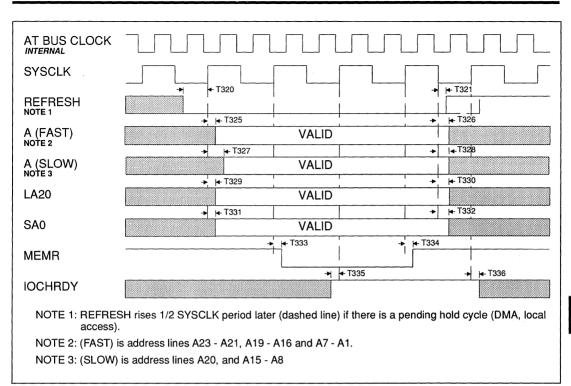

|         |       | 12.2.6   | AT Bus Refresh            |    |  |  |  | ٠. |  |  |  | . 7-162 |

|         | 12.3  | Process  | r Timing                  |    |  |  |  |    |  |  |  | . 7-164 |

|         | 12.4  | Cache C  | ontroller                 |    |  |  |  |    |  |  |  | . 7-177 |

# **LIST OF TABLES**

| Table | Title                                                |

|-------|------------------------------------------------------|

| 2-1   | Register Index                                       |

| 3-1   | Signal/Pin Assignments                               |

| 3-2   | Signal Description                                   |

| 4-1   | Clock Switch Selection                               |

| 4-2   | Speedup Activity                                     |

| 5-1   | MXCTL2-0 Decoding                                    |

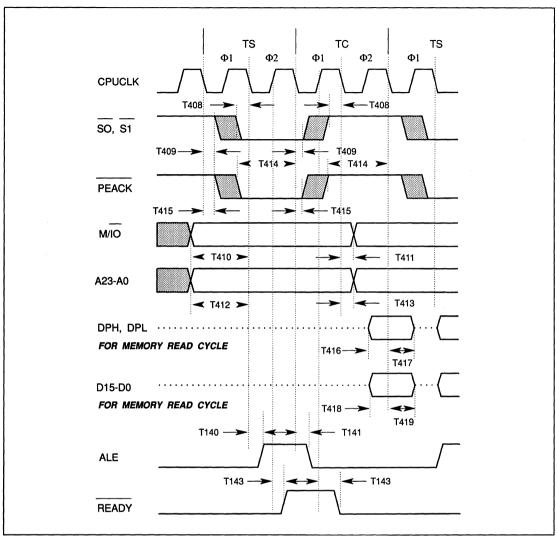

| 5-2   | Bus Timing Parameters                                |

| 5-3   | DMA Transfer Types                                   |

| 5-4   | DMA Controller/Channel Function Map                  |

| 5-5   | Interrupt Sequence                                   |

| 5-6   | Interrupt Controller Function Map                    |

| 5-7   | Control Word Format                                  |

| 5-8   | Decode Addresses                                     |

| 5-9   | Page Register Decodes                                |

| 6-1A  | Typical DRAM Speeds                                  |

| 6-1B  | Non-page Mode Timing                                 |

| 6-2   | Page Mode Wait States                                |

| 6-3   | Page Mode DRAM Address Multiplexer Configuration     |

| 6-4   | Non-page Non-interleave Address Configuration        |

| 6-5   | Non-page 2-WAY Interleave Address Configuration      |

| 6-6   | Upper Page Frame Assignments                         |

| 6-7   | Lower Page Frame Assignments                         |

| 8-1   | I/O Address and Chip Select Assignments              |

| 9-1   | PMC Output Signals                                   |

| 9-2   | PMCIN Inputs                                         |

| 10-1  | Diagnostic Tests                                     |

| 11-1  | DC Operating Characteristics                         |

| 12-1  | Timing Figure/Table Numbers                          |

| 12-2  | Signal Loading                                       |

| 12-3  | 80286 - Page Mode Memory Timing                      |

| 12-4  | 80286 - Non-page Mode 00 Memory Timing               |

| 12-5  | 80286 - Non-page Mode 01 Memory Timing               |

| 12-6  | 80386SX - Page Mode Memory Timing                    |

| 12-7  | 80386SX - Non-page Mode 00 and Mode 01 Memory Timing |

| 12-8  | CPU Initiated AT Bus Cycles                          |

| 12-9  | Entering the AT Bus                                  |

# WD7710/WD7710LP

| Table | Title                                | Page  |

|-------|--------------------------------------|-------|

| 12-10 | Exiting the AT Bus                   | 7-146 |

| 12-11 | DMA Cycles                           | 7-151 |

| 12-12 | AT Bus Master Cycle                  | 7-156 |

| 12-13 | AT Bus Refresh Cycle, Default Timing | 7-162 |

| 12-14 | 80286 CPU Timing                     | 7-164 |

| 12-15 | 80386SX CPU Timing                   | 7-170 |

# **LIST OF ILLUSTRATIONS**

| Figure | Title                                                                    | Page    |

|--------|--------------------------------------------------------------------------|---------|

| 1-1    | System Block Diagram                                                     | . 7-3   |

| 2-1    | WD7710, and WD7710LP Block Diagram                                       | . 7-7   |

| 3-1    | WD7710 Pinout Diagram                                                    | . 7-11  |

| 4-1    | Clock Control                                                            | . 7-20  |

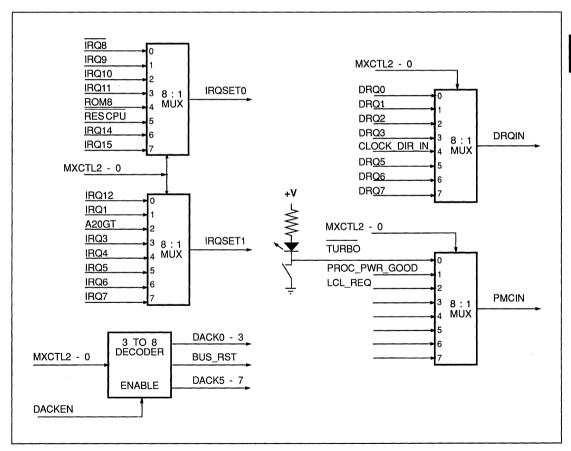

| 5-1    | MXCTL2-0 Multiplexing                                                    | . 7-25  |

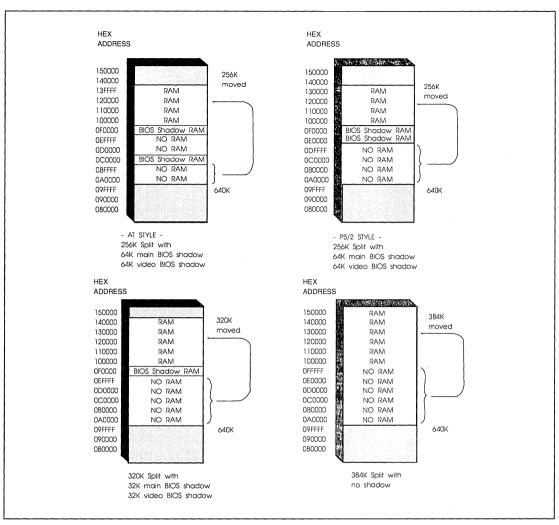

| 6-1    | Split Size                                                               | . 7-51  |

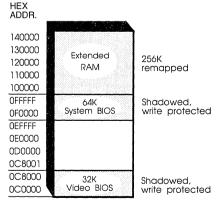

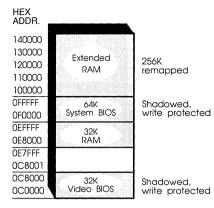

| 6-2    | X_MEM = 0                                                                |         |

| 6-3    | X_MEM = 1                                                                | . 7-53  |

| 7-1    | Cache Controller Functional Diagram                                      | . 7-65  |

| 7-2    | Tag RAM Data Ram Structure                                               | . 7-66  |

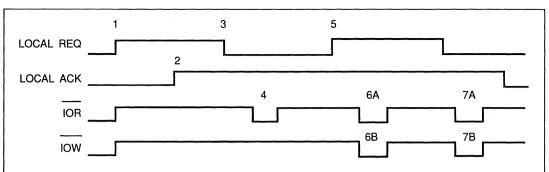

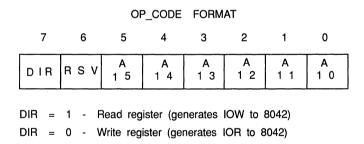

| 9-1    | Register Access by Keyboard Controller                                   | . 7-81  |

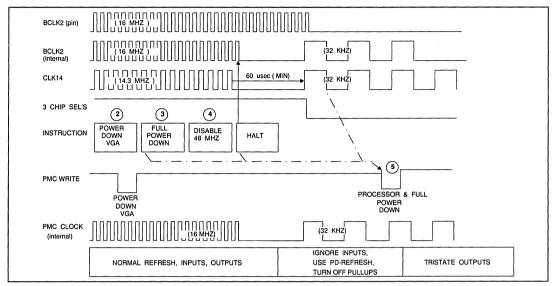

| 9-2    | Power-down                                                               |         |

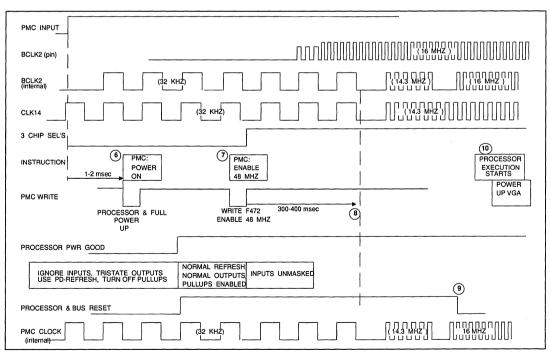

| 9-3    | Power-up                                                                 | . 7-95  |

| 12-1   | 80286 - Page Mode First Access Read/Write                                | . 7-120 |

| 12-2   | 80286 - Page Mode Read Cycle Followed by Page Hit                        | . 7-121 |

| 12-3   | 80286 - Page Mode Read After Write                                       |         |

| 12-4   | 80286 - Page Mode, Page Miss Read/Write                                  | . 7-122 |

| 12-5   | 80286 - Page Mode, Write Miss Following Write                            | . 7-123 |

| 12-6   | 80286 - Page Mode Read Hit Followed by a Write Hit                       | . 7-124 |

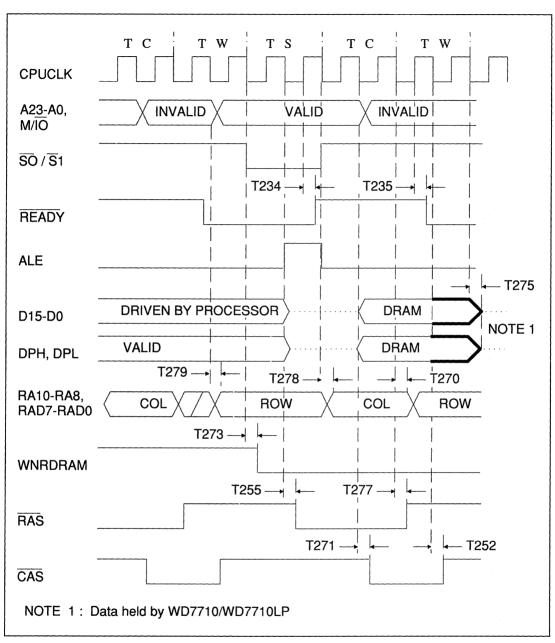

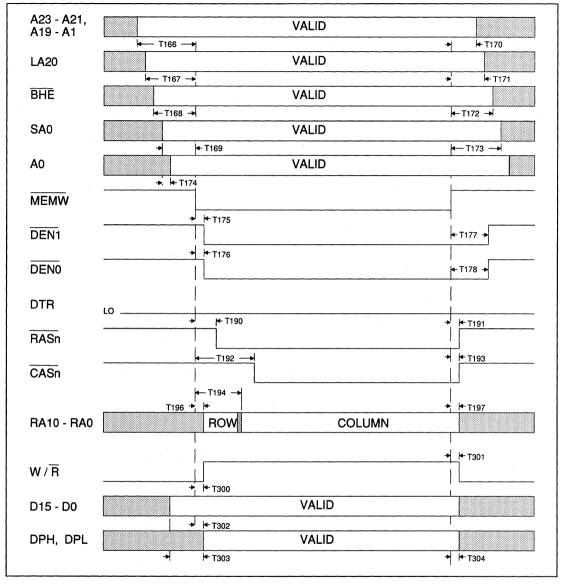

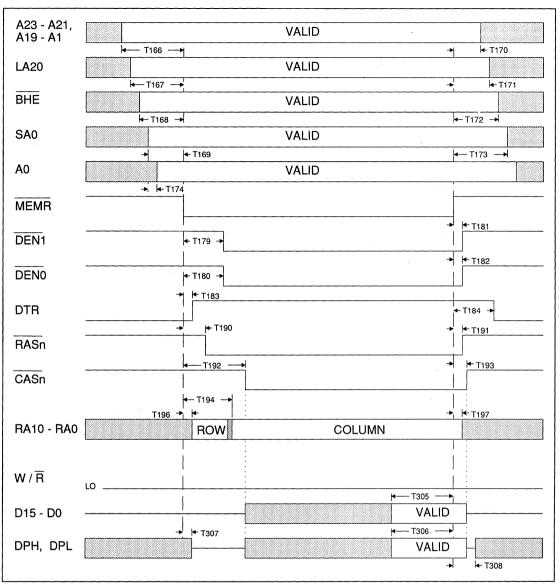

| 12-7   | 80286 - Non-page Mode 00, 1 Wait State Write (4072H = 0001)              | . 7-126 |

| 12-8   | 80286 - Non-page Mode 00, 1 Wait State Read (4072H = 0001)               | . 7-127 |

| 12-9   | 80286 - Non-page Mode 00, 2 Wait States Read After Write                 |         |

|        | (4072H = 0001)                                                           | . 7-128 |

| 12-10  | 80286 - Non-page Mode 01, 0 Wait State Write (4072H = 3560H)             |         |

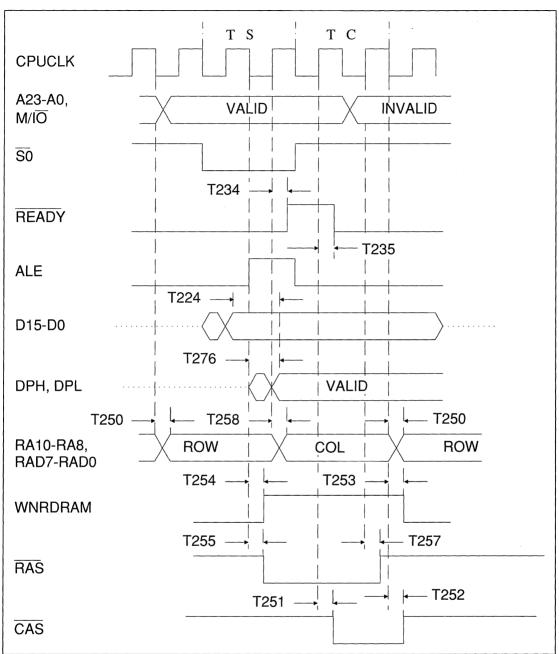

| 12-11  | 80286 - Non-page Mode 01, 0 Wait State Read (4072H = 3560H)              |         |

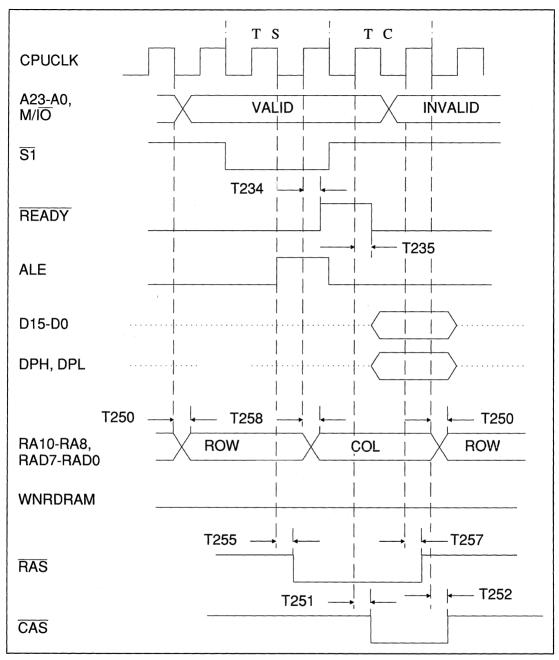

| 12-12  | 80386SX - Page Mode, First Access Read/Write                             |         |

| 12-13  | 80386SX - Page Mode, Page Miss Read/Write                                | . 7-137 |

| 12-14  | 80386SX - Page Mode, Read Cycle Followed by a Page Hit                   | . 7-135 |

| 12-15  | 80386SX - Page Mode, Read After Write                                    | . 7-135 |

| 12-16  | 80386SX - Page Mode, Read Hit Followed by a Write Hit                    | . 7-136 |

| 12-17  | 80386SX - Page Mode, Write Miss Cycle Following a Write Cycle            | . 7-136 |

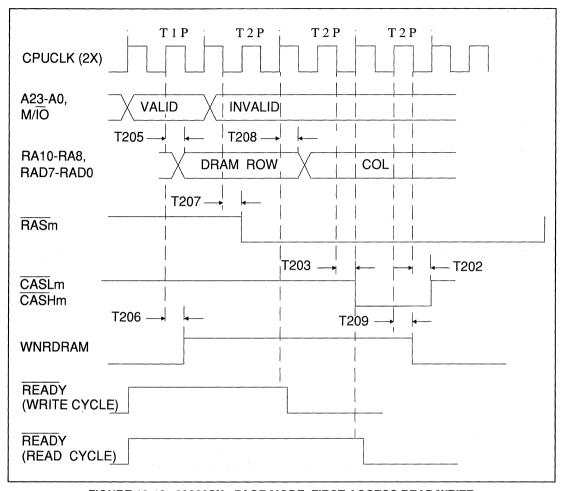

| 12-18  | 80386SX - Non-page Mode 00, 1 Wait State (Pipeline) (4072H = 0001)       | . 7-138 |

| 12-19  | 80386SX - Non-page Mode 00, 1 Wait State Write (Pipeline) (4072H = 0001) | . 7-139 |

| 12-20  | 80386SX - Non-page Mode 01 / 0 Wait State Read                           |         |

|        | (Pipeline) (4072H = 3560H)                                               | . 7-140 |

| 12-21  | 80386SX - Non-page Mode 01, 0 Wait State Read                            |         |

|        | (Pipeline) (4072H = 3560H)                                               | . 7-141 |

| igure | Title                                                                           | Page    |

|-------|---------------------------------------------------------------------------------|---------|

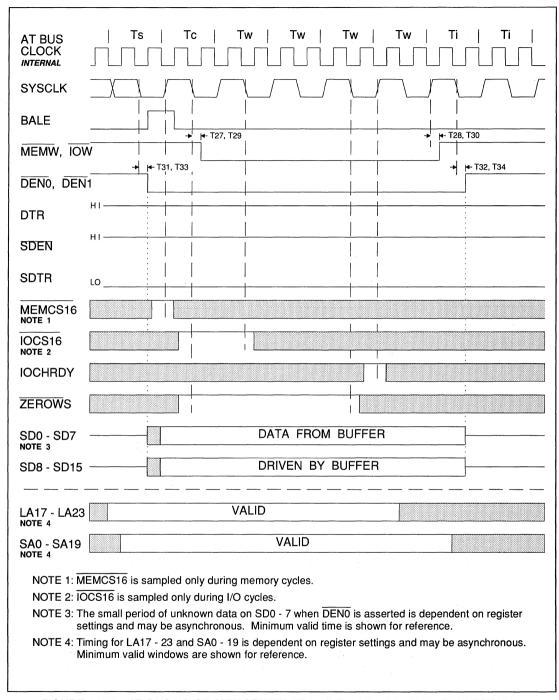

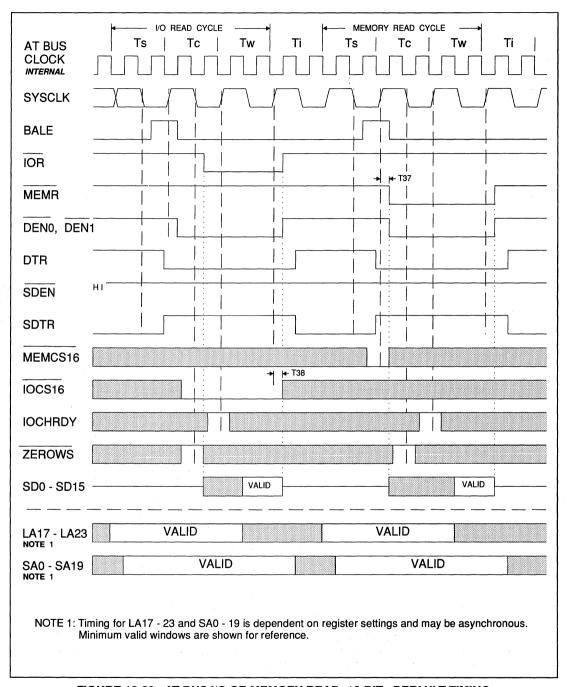

| 12-22 | AT Bus I/O or Memory Read: 8-Bit, Default Timing                                | . 7-131 |

| 12-23 | AT Bus I/O or Memory Read: 8-BIT, Zeroes Asserted                               | . 7-132 |

| 12-24 | AT Bus I/O or Memory Read: 8-Bit Extra Wait State Added                         | . 7-133 |

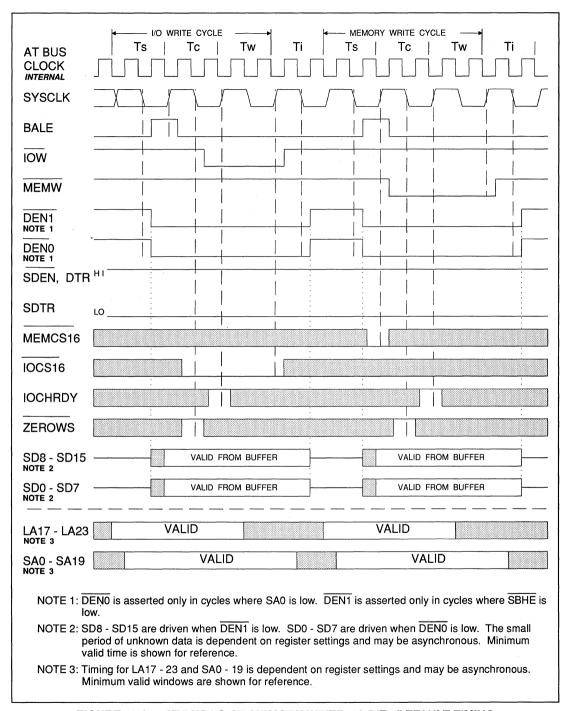

| 12-25 | AT Bus I/O or Memory Write: 8-Bit, Even Byte, Default Timing                    | . 7-134 |

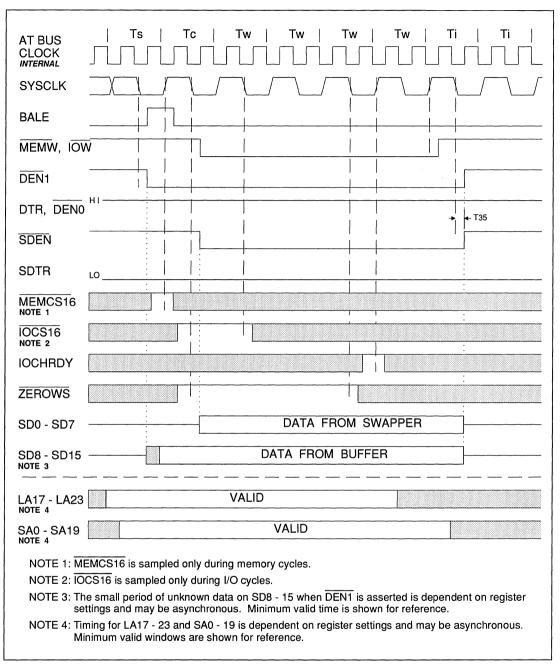

| 12-26 | AT Bus I/O or Memory Write: 8-Bit, Odd Byte, Default Timing                     |         |

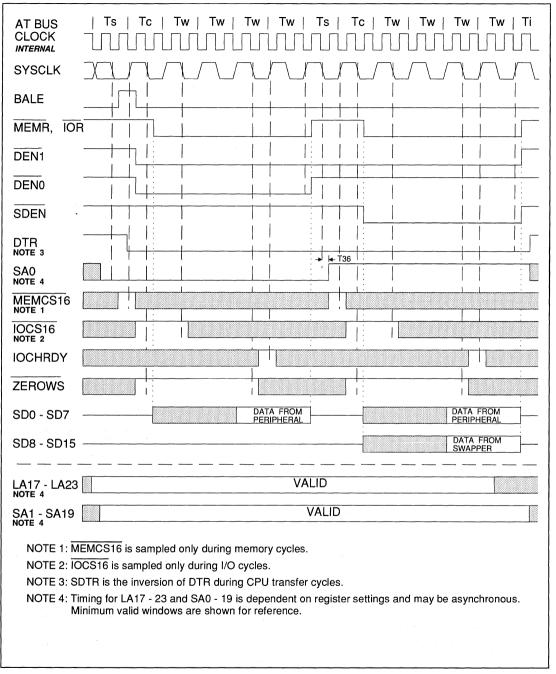

| 12-27 | AT BUS I/O or Memory Read: 8-Bit, Word to Byte Conversion, Default Timing       |         |

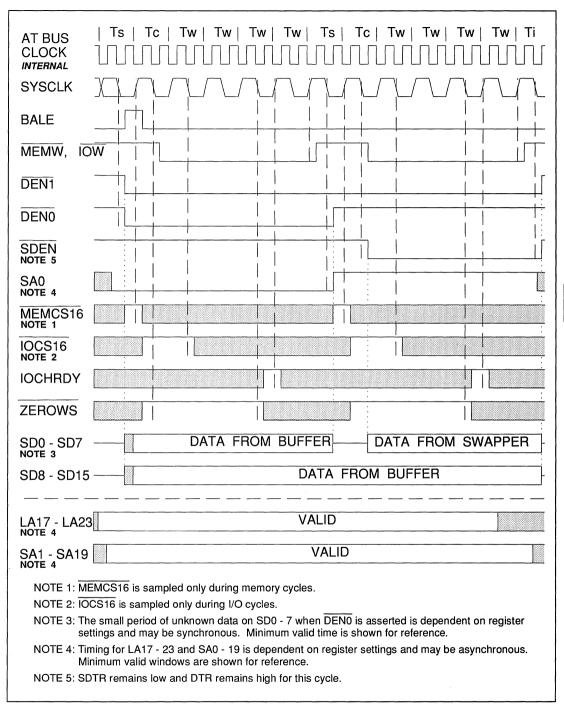

| 12-28 | AT Bus I/O or Memory Write: 8-Bit, Word to Byte Conversion, Default Timing      | . 7-137 |

| 12-29 | AT Bus I/O or Memory Read: 16-Bit, Default Timing                               | . 7-138 |

| 12-30 | AT Bus I/O or Memory Read: 16-Bit, 0WS Asserted and Extra Wait State Added      |         |

| 12-31 | AT Bus I/O or Memory Write: 16-Bit, Default Timing                              | . 7-140 |

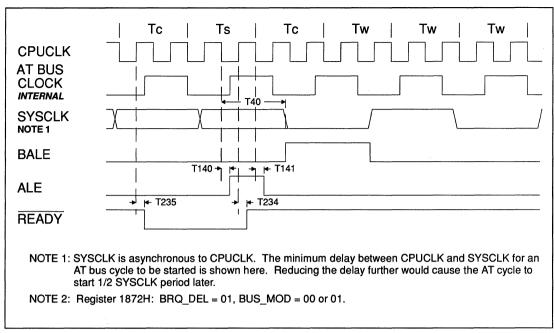

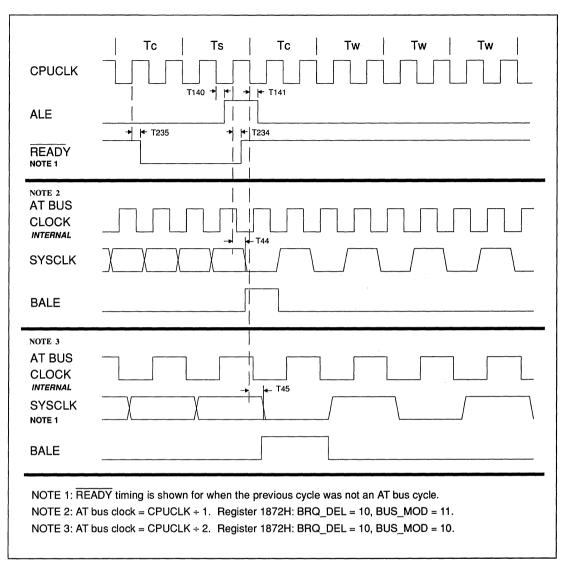

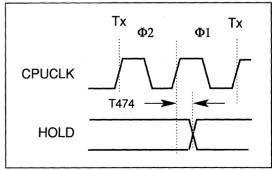

| 12-32 | 80286 CPU - Asynchronous CPUCLK to SYSCLK, BREQ Delay = 1/2 Clock               | . 7-142 |

| 12-33 | 20006 CDLL Asymphronous CDLICLK to SVSCLK                                       |         |

|       | BREQ Delay = 1 Clock                                                            | . 7-142 |

| 12-34 | 80286 CPU - Synchronous CPUCLK to SYSCLK                                        | . 7-143 |

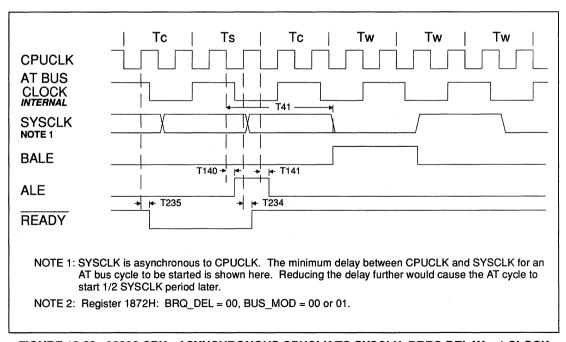

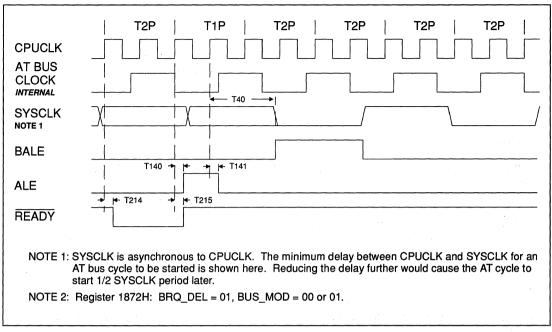

| 12-35 | 80386SX CPU - Asynchronous CPUCLK to SYSCLK, BREQ Delay = 1/2 Clock             | . 7-144 |

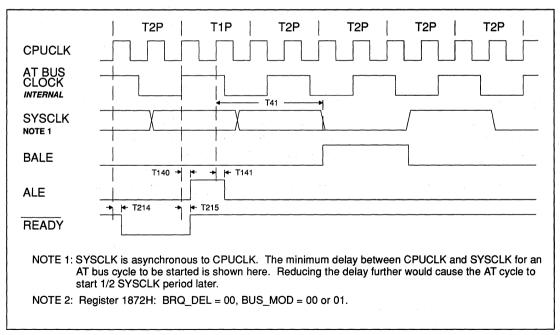

| 12-36 | 80386SX CPU - Asynchronous CPUCLK to SYSCLK,                                    |         |

|       | BREQ Delay = 1 Clock                                                            | . 7-144 |

| 12-37 | 80386SX CPU - Synchronous CPUCLK to SYSCLK                                      | . 7-145 |

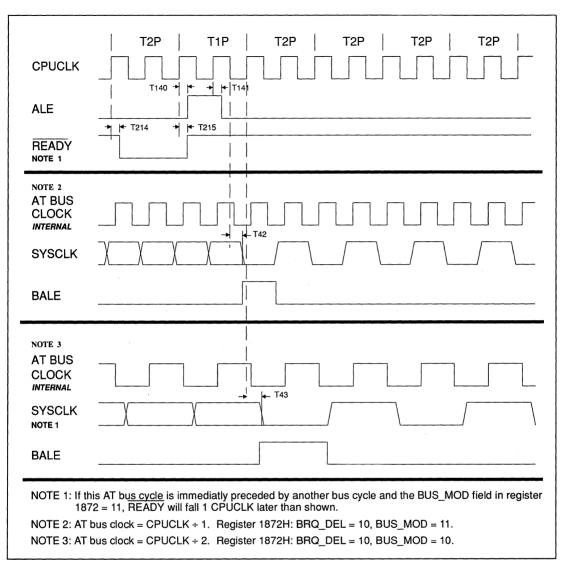

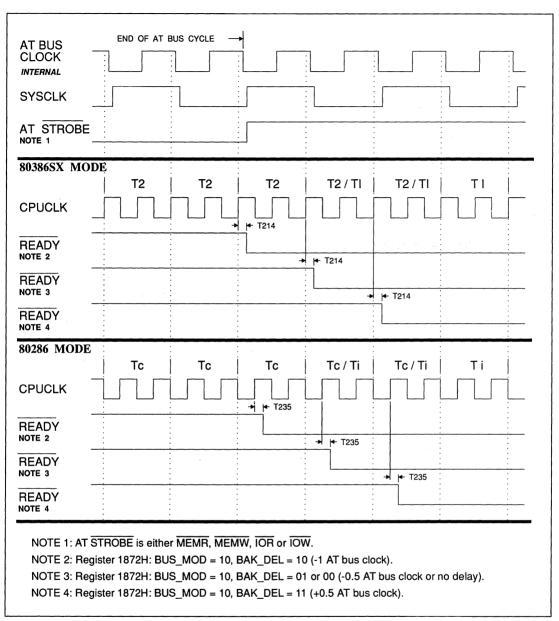

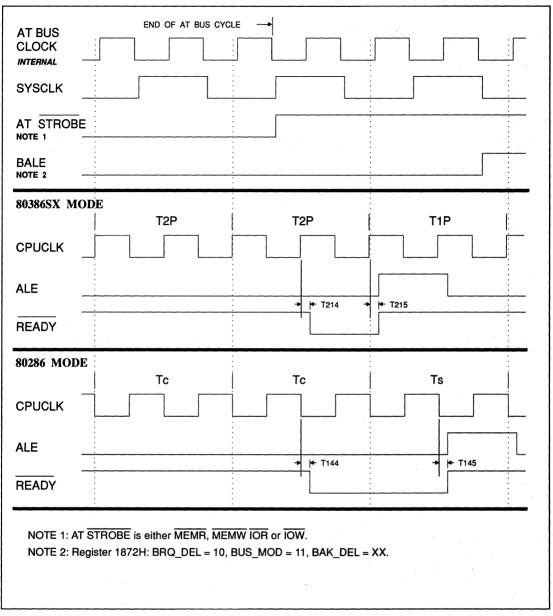

| 12-38 | Synchronous AT Bus Cycle Completion, AT Bus Clock = CPUCLK ÷ 2                  | . 7-147 |

| 12-39 | Synchronous AT Bus Cycle Completion, AT Bus Clock = CPUCLK ÷ 1                  |         |

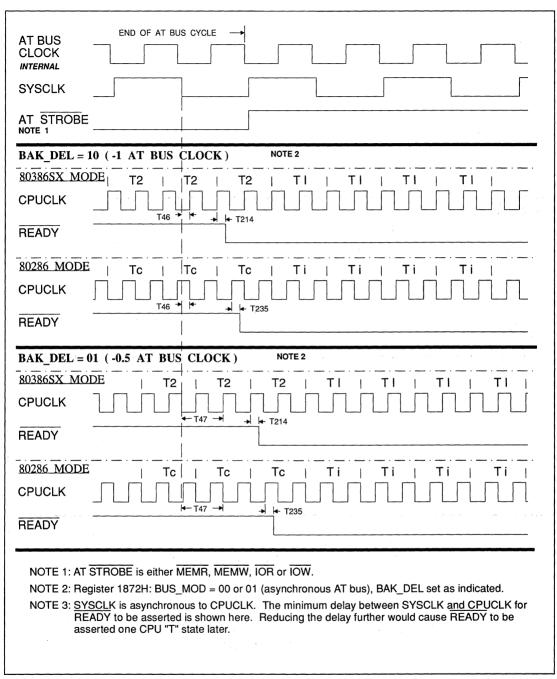

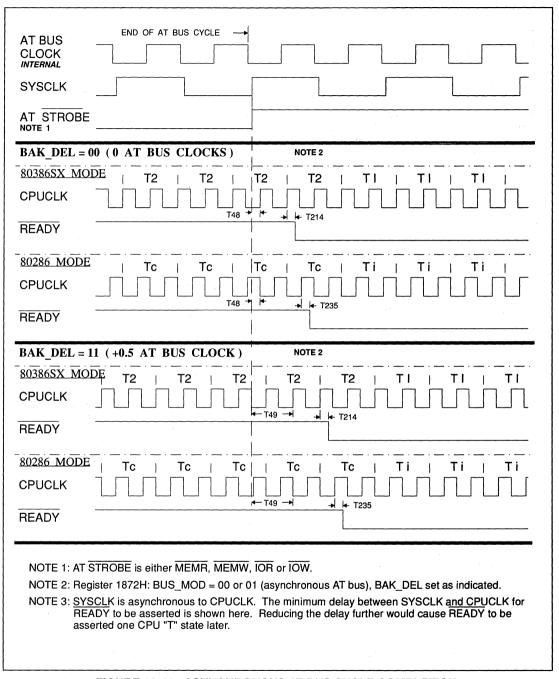

| 12-40 | Asynchronous AT Bus Cycle Completion, BAK_DEL = -1 OR -0.5 AT Bus Cycles        |         |

| 12-41 | Asynchronous AT Bus Cycle Completion,  BAK_DEL = 0 OR +0.5 AT Bus Cycles        | 7 150   |

| 12-42 | Basic DMA Cycle, Default Timing                                                 |         |

| 12-42 | DMA Cycle, 8-Bit I/O to On-board Memory                                         |         |

| 12-43 | DMA Cycle, On-board Memory to 8-Bit I/O                                         |         |

| 12-44 | AT Bus Master, Bus Acquisition/Release                                          |         |

| 12-45 | · ·                                                                             |         |

|       | AT Bus Master, Write to On-board Memory                                         |         |

| 12-47 | AT Bus Master, Read from On-board Memory                                        |         |

| 12-48 | AT Bus Refresh Cycle, Default Timing                                            |         |

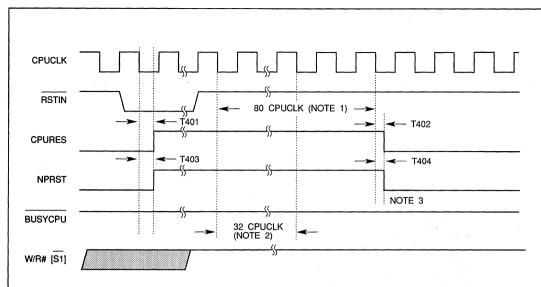

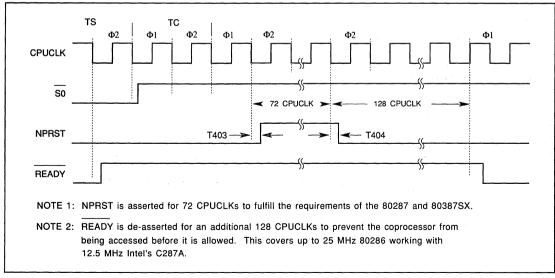

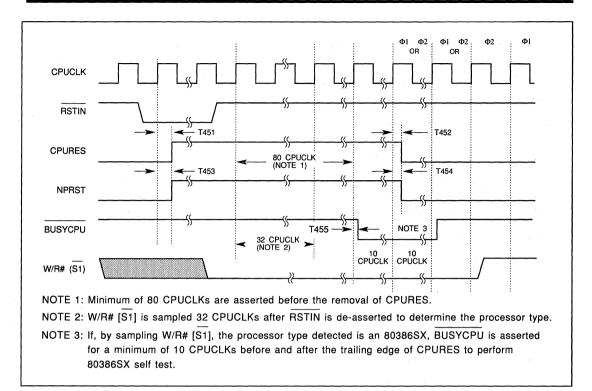

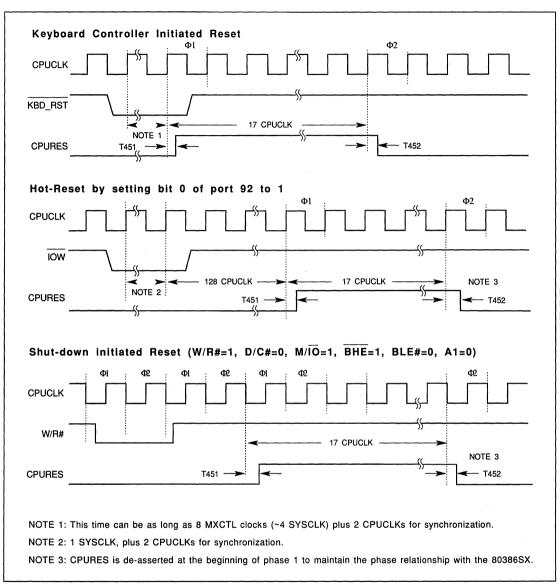

| 12-49 | 80286 - CPURES and NPRST During Power-up                                        |         |

| 12-50 | 80286 - Coprocessor Reset (NPRST) Initiated by IOW to Port F1                   | . /-165 |

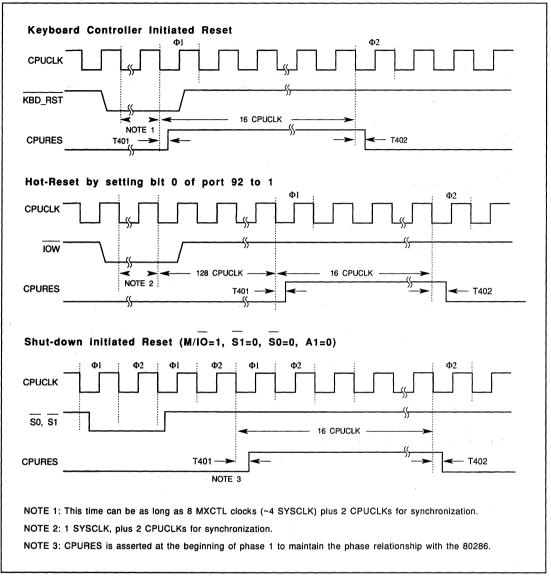

| 12-51 | 80286 - Processor Reset (CPURES) Initiated by Sources Other Than Power-up Reset | . 7-166 |

## WD7710/WD7710LP

| Figure | Title                                                        | Page    |

|--------|--------------------------------------------------------------|---------|

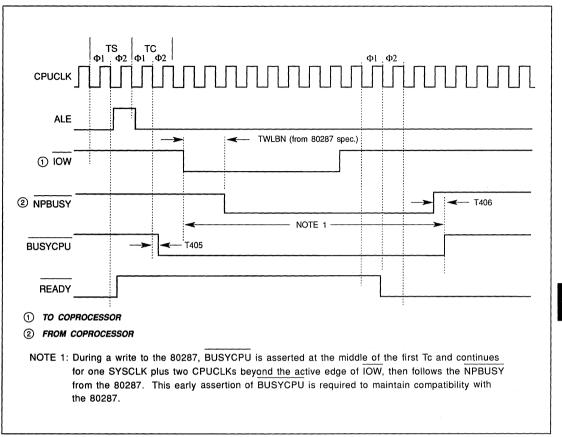

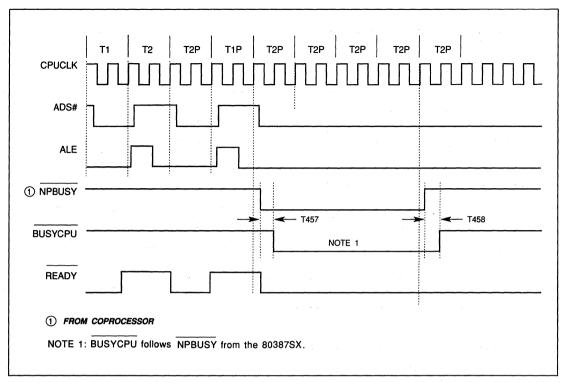

| 12-52  | 80286 - BusyCPU Asserted During Coprocessor Access           | . 7-167 |

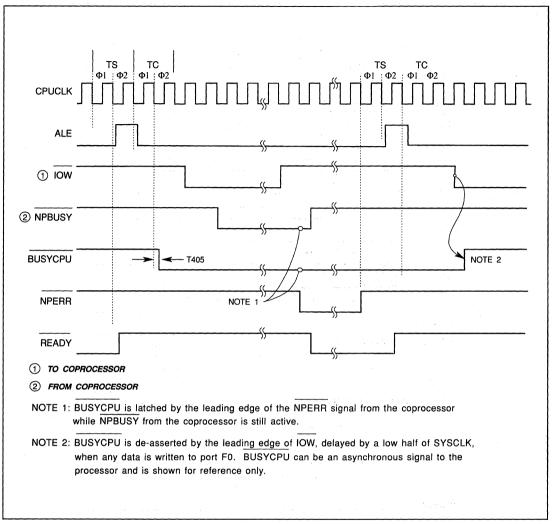

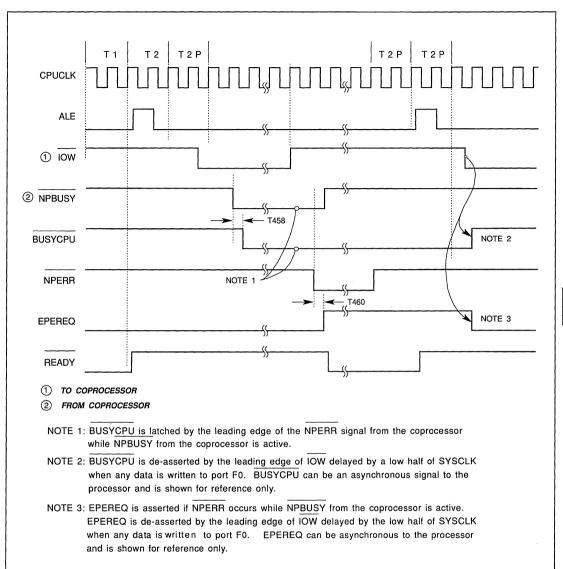

| 12-53  | 80286 - Latching BusyCPU When An Error Occurs And            |         |

|        | Clearing It With A Write To Port F0                          |         |

| 12-54  | 80286 - Miscellaneous Timing                                 | . 7-169 |

| 12-55  | 80386SX - CPURES NPRST During Power-up                       | . 7-172 |

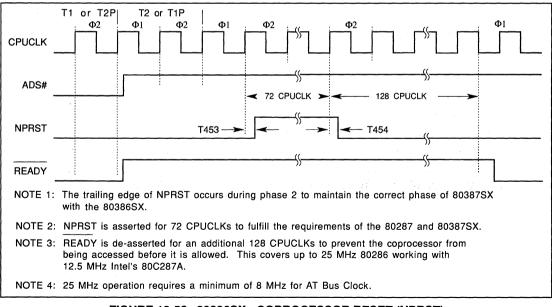

| 12-56  | 80386SX - Coprocessor Reset (NPRST) Initiated IOW to Port F1 |         |

| 12-57  | 80386SX - Processor Reset (CPURES) Initiated by Sources      |         |

|        | Other Than Power-up ReseT                                    | . 7-173 |

| 12-58  | 80386SX - BusyCPU Assertion During Coprocessor Access        |         |

| 12-59  | 80386SX - Latching BusyCPU When An Error Occurs              |         |

|        | And Clearing It With A Write To Port F0                      | . 7-175 |

| 12-60  | 80386SX - Miscellaneous Timing                               | . 7-176 |

| 12-61  | 80386SX - Input Setup And Hold Timing                        | . 7-176 |

| 12-62  | 80386SX - Output Delay Timing                                | . 7-176 |

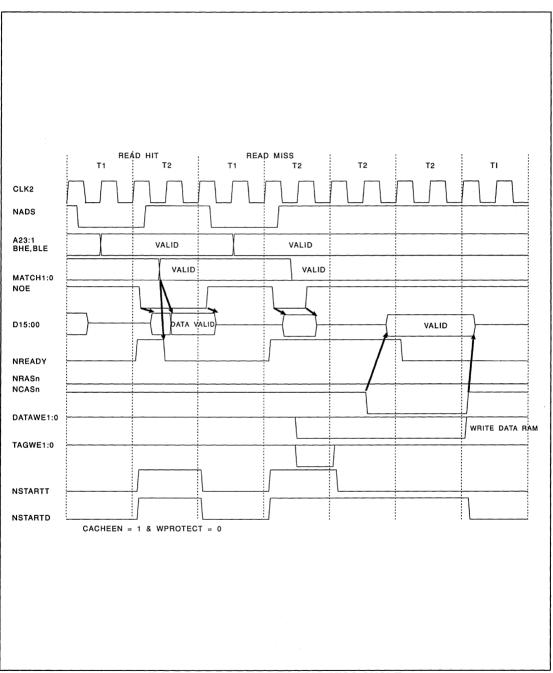

| 12-63  | Read Hit/Read Miss Cycle                                     |         |

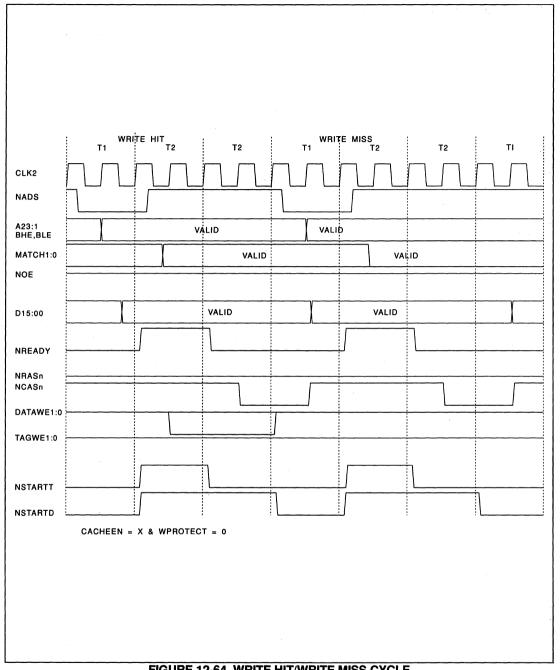

| 12-64  | Write Hit/Write Miss Cycle                                   |         |

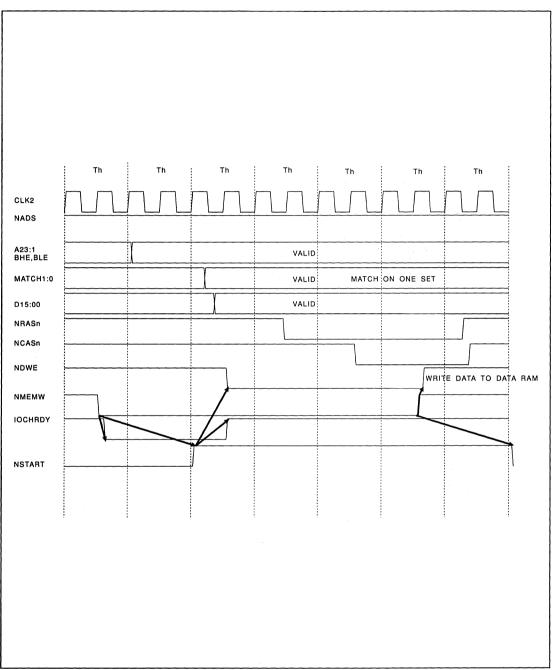

| 12-65  | DMA/Master Memory Write Hit Cycle                            |         |

| 12-66  | DMA/Master Memory Write Miss Cycle                           |         |

| 12-67  | Tag RAM and Data RAM Timing                                  |         |

## 1.0 INTRODUCTION

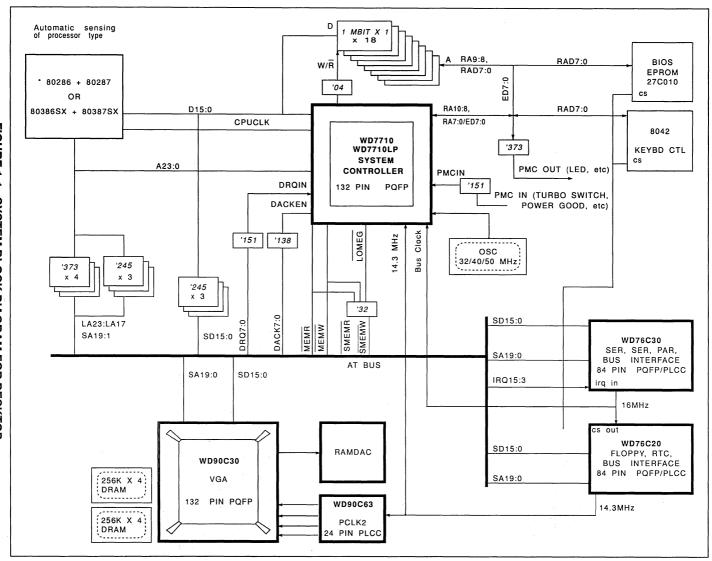

The WD7710 is the second generation single chip AT solution based on the WD76C10A core. It is fabricated in 0.9 micron CMOS. The WD7710 provides 8 Kbytes of direct-mapped or two-way set associative lookaside caching, a page-interleaved memory controller, and enhanced power management features. Figure 1-1 shows the block diagram of the WD7710-based system.

The standard version of the WD7710 operates from 5 VDC ( $\pm 10\%$ ) supplies. An extended low-power version, the WD7710LP, can operate with 3.3 VDC ( $\pm 0.3$ V) or 5 VDC ( $\pm 0.5$ V).

#### 1.1 DOCUMENT SCOPE

This document describes the function and operation of the WD7710 and WD7710LP System Controller devices. It includes the description of external logic necessary for efficient use of these devices. In most instances the WD7710 and WD7710LP operate similarly and are referred to in this document as the System Controller. Where there are differences, the devices are identified specifically.

#### 1.2 FEATURES

- Software and pin compatible with WD76C10A

- 8Kbyte on-chip cache for 80386SX

- Direct map or 2 way set-associative

- Self timed Integrated RAM arrays

- Programmable non-cacheable regions

- Diagnostic mode to test Tag and Data Ram

- Flush command

- 25 Mhz zero wait state cache hit

- ROM may be shadowed and/or cached

- Supports Static CPU for power savings in sleep mode

- Supports extra wait state for page mode

- Operates at speeds of 16 MHz, 20 MHz and 25 MHz

- Interfaces with 80286, or 80386SX CPUs.

- Supports memory in four banks with 64 Kbits, 256 Kbits, 1 Mbits or 4 Mbits DRAMs. Also supports new 512k x 8, 1M x 16 and 2M x 8 DRAM configurations.

- Page mode zero wait state access at 25 MHz with 70 ns DRAM.

- Supports up to 16 Mbyte of real memory, or 32 Mbyte of EMS memory.

- Maintains controlled propagation delay for 80386SX reset.

- Employs an internal self-tuning delay line for DRAM control.

- Self-adjusting output drivers minimize output rise/fall time variations and reduces EMI and ground noise.

- DRAM address multiplexer drives 350 pF with adjustable strength drivers.

- Main and VGA BIOS may be mapped into one physical PROM.

- Advanced 64 Kbyte and 128 Kbyte ROM shadowing allows main BIOS and video BIOS shadowing along with 320 Kbyte and 256 Kbyte remap to extended or expanded memory.

- Offers additional power saving modes:

- Slow Refresh

- Stop DMA Clock

- Parity generation and checking.

- 132-pin PQFP package

- 3.3V low power operation

- I/O Pin mapping for testability

- Low power 0.9 micron CMOS technology.

Additional features of WD7710LP only:

- Provides System Activity Monitor (SAM).

- Provides power control with suspend and resume.

- Provides processor stop clock.

- Features CAS before RAS slow refresh for portable applications.

- Offers automatic processor clock speed switching.

- · 3V Suspend to hard disk

#### 1.3 GENERAL DESCRIPTION

The WD7710 is designed for use in a high performance desktop AT computer using an 80286 or 80386SX processor up to 25 MHz. The WD7710LP has the features of the WD7710 and is designed to operate in a high-performance notebook/laptop AT compatible computer using an 80286 or 80386SX processor.

## 1.3.1 WD7710

The WD7710 contains a high-performance memory controller with programmable modes of operation. It supports non-page, zero wait state read and write memory control. A maximum of four banks of 64 Kbit, 256 Kbit, 1 Mbit, 4 Mbit or 16 Mbit DRAM may be controlled, allowing up to 16 Mbytes of real or 32 Mbytes EMS (Expanded Memory Specification) memory. Any combination of DRAM sizes may be used. In addition, the WD7710 controls page mode DRAM or static column DRAM with page mode operation.

The on-board memory can be allocated either to extended or EMS memory in 128 Kbyte increments. Forty EMS registers support EMS 4.0 multitasking.

An internal self-tuning delay line is used for DMA and Bus Master memory cycles. Delay line information is also used to adjust the strength of the output drivers. This stabilizes the output rise and fall times, which reduces ground noise and electromagnetic interference (EMI).

EMS access to external RAM or ROM may be used to support Kanji or other extended character sets.

The WD7710 interfaces with either an 80286 or 80386SX processor. The processor type is automatically sensed at power-up. No extra logic is required to interface with the 80386SX. The variation in processor reset propagation delay is controlled to meet the strict reset timing of the 80386SX.

#### 1.3.2 WD7710LP

In addition to supporting all the features of the WD7710, the WD7710LP also supports portable notebook/laptop computers. To provide this support, the WD7710LP makes use of Power Management Control (PMC) for powering down peripherals or the processor, which includes processor stop clock, slow clock, automatic processor clock speed switching modes and CAS before RAS slow refresh. Suspend and resume is supported when low power DRAM is refreshed while the processor and other power consuming devices are turned off. The power drain for the core logic and VGA controller is less than 5 mA in this mode. Power and clock speed may be controlled by the keyboard processor, transparently to the 80286 or 80386SX.

The System Activity Monitor (SAM) provided by WD7710LP is a transparent feature that replaces the functions previously performed by software. It determines when the system has been idle for a previously programmed period of time and determines a clean break point in which to perform powerdown activities such as suspend.

FIGURE 1-1. SYSTEM BLOCK DIAGRAM FOR DESKTOP

ADVANCED INFORMATION 11/25/91

## 2.0 ARCHITECTURE

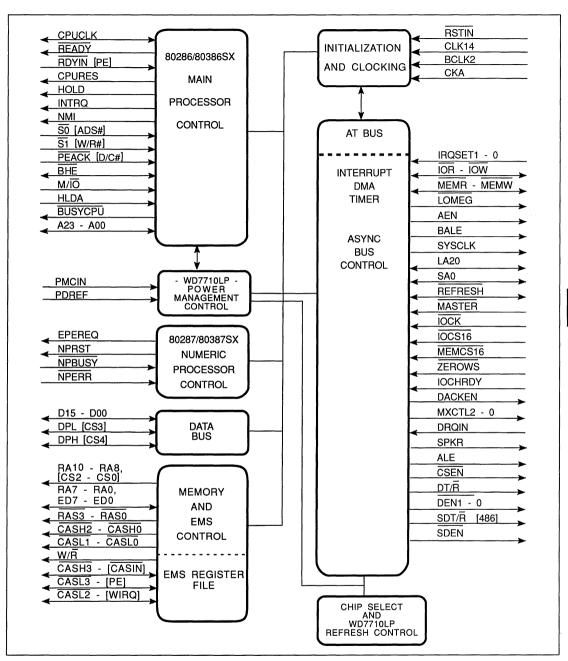

All versions of the System Controller are comprised of eight major blocks:

- · Initialization and clocking

- AT bus

- 80286/80387SX processor control

- 80287/80387SX numeric processor control

- · Data bus

- · Memory and EMS control

- Power Management Control (WD7710LP only)

- Register File

- Cache control

Sections 2.1 through 2.10 provide an overview of these blocks and are described in more detail in sections 4 through 10.

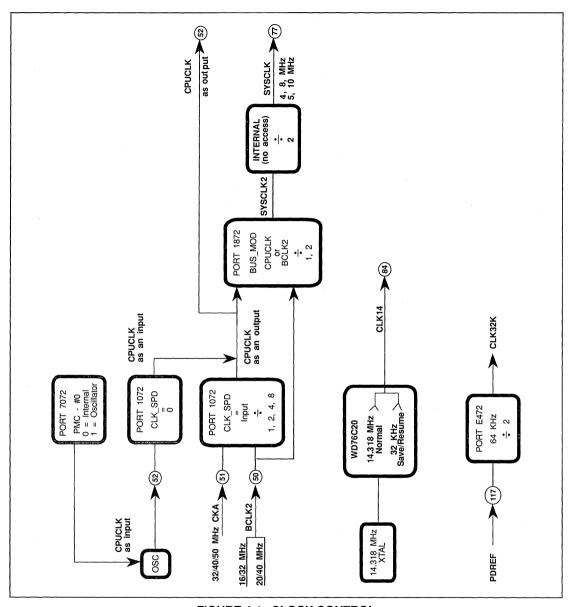

#### 2.1 INITIALIZATION AND CLOCKING

At power up, the System Controller receives the RSTIN signal, which it uses to reset the AT bus and assert CPURES and NPRST to reset the main and numeric processors. The processor and AT bus resets are held for 84 processor clocks beyond the removal of the RSTIN signal. It is at this time that the type of processor in use (80286, 80287 or 80386SX, 80387SX) is determined by examining the \$\overline{S1}[W/R#]\$ signal.

CLK14 is a 14.318 MHz clock for the 8254 compatible timers and is switched by the WD76C20 to 32 KHz during a suspend and resume operation.

BCLK2 is used to generate an 8 MHz or 10 MHz bus clock and may also be used as the source for the main processor clock, CPUCLK.

#### 2.2 AT BUS

The AT bus provides the logic necessary to control the system clock, memory read and write access, I/O read and write cycles, data bus direction, data and interrupt requests and speaker driver.

## 2.3 MAIN PROCESSOR CONTROL

At the termination of reset, this block determines whether the local processor is an 80286 or 80386SX by examining the \$\overline{S1}[W/R#]\$ signal. This block also controls whether the CPUCLK is to be an input or output. While both devices have the ability to reduce the processor clock rate, only the WD7710LP has the ability to stop the clock to the processor. The WD7710LP also has the ability to power down the processor, at which time it tristates the CPUCLK, READY, HOLD, INTRQ and NMI signals.

#### 2.4 NUMERIC PROCESSOR CONTROL

Both System Controllers support an 80287 or 80387SX processor.

## 2.5 DATA BUS

The Data Bus is a 16-bit (two bytes) bidirectional bus that connects to the processor's, System Controller, DRAM, and to AT data bus transceivers. The parity of each DRAM byte is indicated by DPL and DPH.

#### 2.6 MEMORY AND EMS CONTROL

This block controls the access to 16 Mbytes of real memory or 32 Mbytes of expanded memory. Both versions of the System Controller supports non-page mode memory and independent two-way interleave page mode access to the DRAM banks.

# 7

## 2.7 POWER MANAGEMENT CONTROL

The Power Management Control (PMC) is internal logic which interfaces with external multiplexers and latches. Only the WD7710LP makes full use of the PMC. It has the ability to power down only the main processor or the main processor and peripherals, conserving power essential to portable notebook/laptop computers. When in a power down state, the WD7710LP tristates the CPUCLK, READY, HOLD, INTRQ and NMI output signals to the main processor. Also contained within this functional block are the SMI and SAM logic.

## 2.8 REGISTER FILE

The register file provides software control of the interface signals. The function of each register is described in the same section as the logic block which it controls. Some registers, such as the Bus Timing and Power Down Control Register at Port 1872H, serve more than one area. In this instance the register description appears only in one section but is referred to in all appropriate sections.

The registers, and the section in which they are described, are listed in Table 2-1.

In most cases, the registers are addressed by all 16 address bits, A15 through A00. Within the text, when the address is expressed as a three digit number, i.e., 092H - ALT A20 GATE and HOT RESET, only address bits A09 through A00 are used, A15 through A10 are ignored. If the address is expressed as a four digit number, all 16 address bits are used.

With the exception of the EMS Registers at port E072H and E872H and Port 70H Shadow Register at E472H, all registers located at Ports 1072H through FC72H are locked and inaccessible until unlocked by performing an eight bit I/O write of DA to the Lock/Unlock Register at Port F073H. Writing anything other than DA locks the registers. The lock/unlock status can be determined by reading the Lock/Unlock Status Register at Port FC72H twice. If the T bit (bit 15) toggles, the registers are unlocked. If the registers are locked, the read cycle is directed to the AT bus, and the data is undetermined.

#### 2.8.1 Lock Status Register

Port Address FC72H - Read only

Bits 11 through 03 are particularly useful in laptop applications by allowing the suspend/resume software to restore correct status to on-board devices.

| 15 | 14       | 13 | 12 | 11     | 10  | 09  | 08  |  |  |

|----|----------|----|----|--------|-----|-----|-----|--|--|

| Т  | Not Used |    |    | DMA #2 |     |     |     |  |  |

|    |          |    |    | СНЗ    | CH2 | CH1 | CH0 |  |  |

| 07  | 06  | 05   | 04  | 03 | 02       | 01 | 00 |  |  |

|-----|-----|------|-----|----|----------|----|----|--|--|

|     | DM  | A #1 |     | P4 | Not Used |    |    |  |  |

| СНЗ | CH2 | CH1  | CH0 |    |          |    |    |  |  |

| Signal | Default  |

|--------|----------|

| Name   | At RSTIN |

All signals . . . . . . . . . . . . None

Bit 15 - T, Toggle

Changes state after every read of this port.

Bits 14-12 - Not used, state is ignored

## Bits 11-08 - DMA #2, Channel Enable

This field represents the state of the Enable Bit (Mask) for channels 3 through 0 of DMA Controller #2. For a description of the Mask Registers, refer to section 5.4.11.

- 1 = Channel enabled

- 0 = Channel disabled

## Bits 07-04 - DMA #1, Channel Enable

This field represents the state of the Enable Bit (Mask) for channels 3 through 0 of DMA Controller #1. For a description of the Mask Registers, refer to section 5.4.11.

- 1 = Channel enabled

- 0 = Channel disabled

## Bit 03 - P, Parallel Port Direction

The P bit represents the state of the Direction Bit (bit 5) of the parallel port Write Control Register. For a description of this bit, refer to the WD76C30 Data Book, section 4.3

Bits 02-00 - Not used, state is ignored

## 2.8.2 Lock/Unlock Register

## Port Address F073H - Write only

| 15       | 14 | 13 | 12 | 11 | 10 | 09 | 08 |

|----------|----|----|----|----|----|----|----|

| Not Used |    |    |    |    |    |    |    |

| 07         | 06 | -5 | 04 | 03 | 02 | 01 | 00 |

|------------|----|----|----|----|----|----|----|

| L/UL = DA- |    |    |    |    |    |    |    |

Signal Name Default At RSTIN

All signals

None

Bits 15-08 - Not used, state is ignored

Bits 07-00 - L/UL, Lock/Unlock

L/UL = DA -

11011010 unlocks the registers, allowing read and write access to the registers. Refer to Table 2-1 for the registers capable of being locked.

L/UL ≠ DA -

Anything other than 11011010 locks the registers. Any attempt to access a locked register I/O port address goes to the AT bus rather than the locked register.

## 2.9 Cache Control

This functional block contains the 8Kbyte integrated cache (both tag and data RAM) as well as cache control logic.

FIGURE 2-1. WD7710 AND WD7710LP BLOCK DIAGRAM

| PORT<br>ADDRESS<br>(HEX) | REGISTER NAME                                     | LOCK/<br>UNLOCK | SECTION        |

|--------------------------|---------------------------------------------------|-----------------|----------------|

| 000 - 00F ①              | DMA Control #1 (Channel 0:3)                      | No              | 5.4, 5.6,      |

| 020 - 021 ②              | Interrupt Controller #1                           | No              | 5.5            |

| 040                      | Timer 0. Time Of Dav                              | No              | 5.7            |

| 041                      | Timer 1, Refresh                                  | No              | 5.7            |

| 042                      | Timer 1, Refresh                                  | No              | 5.7            |

| 043                      | Control Word                                      | No              | 5.7            |

| 060 - 06E even           | Keyboard Controller                               | No              | 8.5, Table 8-1 |

| 061 - 06F odd            | Port B Parity Error And I/O Channel Check         | No              | 5.9            |

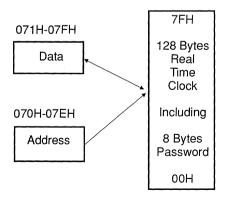

| 070 - 07E even           | Real-Time Clock Address Register                  | No              | 5.8.1          |

| 071 - 07F odd            | Real-Time Clock Data Register                     | No              | 5.8.2          |

| 080 - 09F                | (except 092H) DMA Page Registers                  | No              | 5.6.4          |

| 092                      | ALT A20 Gate and Hot Reset                        | No              | 5.8.3          |

| 0A0 - 0A1 @              | Interrupt Control Slave #2                        | No              | 5.4, 5.6       |

| 0C0 - 0DE ①              | DMA Control #2 (Channel 4:7)                      | No              | 5.4            |

| 00F0                     | Clear 287 Busy                                    | No              | 5.3.2          |

| 00F1                     | Reset 287/387SX                                   | No              | 5.3.3          |

| 1072                     | CPU Clock Control                                 | Yes             | 4.2.4          |

| 1872                     | Bus Timing And Power Down Control                 | Yes             | 5.3.1          |

| 2072                     | Refresh Control, Serial And Parallel Chip Selects | Yes             | 8.1            |

| 2872                     | Chip Selects                                      | Yes             | 8.2            |

| 3072                     | Programmable Chip Select Address                  | Yes             | 8.3            |

| 3872                     | Memory Control                                    | Yes             | 6.2.1          |

| 3C72                     | DMA Shadow Register 1                             | Yes             | 9.14           |

| 4072<br>4472             | Non-page Mode DRAM Memory Timing                  | Yes<br>Yes      | 6.3.1<br>9.14  |

| 4472<br>4872             | DMA Shadow Register 2                             | Yes<br>Yes      | 9.14<br>6.2.2  |

| 4672<br>4C72             | DMA Shadow Register 3                             | Yes             | 9.14           |

| 5072                     | Bank 3 And Bank 2 Start Address                   | Yes             | 6.2.2          |

| 5872                     | Split Start Address                               | Yes             | 6.2.3          |

| 5072<br>5C72             | Reserved                                          | 165             | 0.2.3          |

| 6072                     | RAM Shadow And Write Protect                      | Yes             | 6.2.4          |

| 6472                     | Reserved                                          | 163             | 0.2.4          |

| 6872                     | EMS Control And Lower EMS Boundary                | Yes             | 6.4.1          |

| 6C72                     | Reserved                                          | 100             | 0.1.1          |

| 7072                     | PMC Output Control 7:0                            | Yes             | 9.3            |

| 7472                     | Reserved                                          | .00             | 0.0            |

| 7872                     | PMC Output Control 15:8                           | Yes             | 9.3            |

| 7C72                     | Reserved                                          |                 |                |

| 8072                     | PMC Timers                                        | Yes             | 9.4            |

| 8872                     | PMC Timers                                        | Yes             | 9.5            |

| 8C72                     | Reserved                                          |                 |                |

| 9072                     | NMI Status                                        | Yes             | 9.7            |

| 9472                     | Reserved                                          |                 |                |

| 9872                     | Diagnostic                                        | Yes             | 10.1           |

| 9C72                     | Reserved                                          |                 |                |

| l A072                   | Delay Line                                        | Yes             | 10.2           |

**TABLE 2-1. REGISTER INDEX**

| PORT<br>ADDRESS<br>(HEX)                                                                                                                             | REGISTER NAME                                                                                                                                                                                                                                                                                                                                                           | LOCK/<br>UNLOCK                                                  | SECTION                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| A472<br>A872<br>AC72<br>B072<br>B872<br>C072<br>C872<br>D072<br>D472<br>D472<br>D872<br>DC72<br>E072<br>E472<br>E872<br>F072<br>F472<br>F872<br>F073 | Reserved Test Enable Reserved Activity Monitor Control DMA Control Shadow High Memory Write Protect Boundary PMC Interrupt Enables Serial/Parallel Shadow Register Interrupt Controller Shadow Activity Monitor Mask Test Status EMS Page Register Pointer Port 70H Shadow EMS Page Register 48 MHz Oscillator Disable 48 MHz Oscillator Enable Cache Flush Lock/Unlock | Yes Yes Yes Yes Yes Yes Yes Yes No No No Yes Yes Yes Yes Yes Yos | 9.11<br>5.4.15<br>6.2.5<br>9.6<br>9.8<br>9.9<br>9.12<br>10.4<br>6.4.2<br>9.10<br>6.4.3<br>8.5, Table 8-1<br>8.5, Table 8-1<br>8.4<br>2.8.1 |

See Table 5-4. DMA Controller/Channel Function Map

See Table 5-6. Interrupt Controller Function Map

**TABLE 2-1. REGISTER INDEX (cont.)**

WD7710/WD7710LP SIGNAL DESCRIPTION

## 3.0 SIGNAL DESCRIPTION

The signals are listed according to their pin number in Table 3-1. The signals are grouped according to their application and described in Table 3-2.

| PIN | NAME          | PIN | NAME                | PIN | NAME      | PIN | NAME       |

|-----|---------------|-----|---------------------|-----|-----------|-----|------------|

| 1   | RA5/ED5       | 34  | EPEREQ              | 67  | VSS       | 100 | A10        |

| 2   | VCC           | 35  | NPRST               | 68  | D11       | 101 | VCC        |

| 3   | RA4/ED4       | 36  | LOMEG               | 69  | VCC       | 102 | <b>A</b> 9 |

| 4   | RA3/ED3       | 37  | MEMW                | 70  | D12       | 103 | A8         |

| 5   | VSS           | 38  | MEMR                | 71  | D13       | 104 | A7         |

| 6   | RA2/ED2       | 39  | ĪOW                 | 72  | D14       | 105 | A6         |

| 7   | RA1/ED1       | 40  | IOR                 | 73  | D15       | 106 | <b>A</b> 5 |

| 8   | RA0/ED0       | 41  | BHE                 | 74  | DT/R      | 107 | A4         |

| 9   | CASH2         | 42  | NPERR               | 75  | DEN1      | 108 | АЗ         |

| 10  | CASL2 [WIRQ]  | 43  | PEACK [D/C]         | 76  | DEN0      | 109 | A2         |

| 11  | RAS2          | 44  | M/IO                | 77  | SYSCLK    | 110 | IRQSET1    |

| 12  | CASH3 [CASIN] | 45  | S0 [ADS#]           | 78  | CPURES    | 111 | IRQSET0    |

| 13  | CASL3 [PE]    | 46  | S1 [W/R#]           | 79  | BALE      | 112 | MXCTL0     |

| 14  | RAS3          | 47  | READY               | 80  | A23       | 113 | MXCTL1     |

| 15  | DPH [CS4]     | 48  | HLDA                | 81  | A22       | 114 | MXCTL2     |

| 16  | DPL [CS3]     | 49  | HOLD                | 82  | A21       | 115 | CSEN       |

| 17  | RSTIN         | 50  | BCLK2               | 83  | IOCK      | 116 | DACKEN     |

| 18  | DRQIN         | 51  | RDYIN [CKA]<br>[PE] | 84  | CLK14     | 117 | PDREF      |

| 19  | IOCHRDY       | 52  | CPUCLK              | 85  | NPBUSY    | 118 | PMCIN      |

| 20  | ZEROWS        | 53  | BUSYCPU             | 86  | A0 [BLE#] | 119 | W/R        |

| 21  | IOCS16        | 54  | NMI                 | 87  | A1        | 120 | CASH0      |

| 22  | MEMCS16       | 55  | INTRQ               | 88  | A20       | 121 | CASL0      |

| 23  | SPKR          | 56  | D0                  | 89  | A19       | 122 | RAS0       |

| 24  | SA0           | 57  | D1                  | 90  | A18       | 123 | CASH1      |

| 25  | LA20          | 58  | D2                  | 91  | A17       | 124 | CASL1      |

| 26  | MASTER        | 59  | D3                  | 92  | A16       | 125 | RAS1       |

| 27  | ALE           | 60  | D4                  | 93  | A15       | 126 | RA10 [CS2] |

| 28  | AEN           | 61  | D5                  | 94  | A14       | 127 | RA9 [CS1]  |

| 29  | SDEN          | 62  | D6                  | 95  | A13       | 128 | RA8 [CS0]  |

| 30  | SDT/R [486]   | 63  | D7                  | 96  | A12       | 129 | VSS        |

| 31  | VCC           | 64  | D8                  | 97  | A11       | 130 | RA7/ED7    |

| 32  | REFRESH       | 65  | D9                  | 98  | VSS       | 131 | RA6/ED6    |

| 33  | VSS           | 66  | D10                 | 99  | VSS       | 132 | VSS        |

Note: Some pins are multi-functional depending upon the mode of operation. The alternate signal for these pins is enclosed in brackets.

**TABLE 3-1. PIN ASSIGNMENTS**

| PIN     | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                |

|---------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |     | INITIALIZATION AND CLOCKING                                                                                                                                                                                                                                |

| 84      | CLK14    | 1   | Clock 14 CLK14 is derived from a 14.318 MHz crystal and is used internally for the 8254 compatible timers. CLK14 is externally switched to 32 KHz during a suspend and resume.                                                                             |

| 17      | RSTIN    |     | System Reset In RSTIN drives a CMOS input level Schmitt Trigger and is used to reset the entire system at powerup. For a detailed description, see Section 4, Initialization and Clocking.                                                                 |

| 50      | BCLK2    | 1   | Bus Clock BCLK2 is used to generate an 8 MHz or 10 MHz expansion bus clock. For an 8 MHz bus, BCLK2 is a 16 MHz or 32 MHz input signal. For a 10 MHz bus clock, BCLK2 is a 20 or 40 MHz input signal. BCLK2 may also be used to drive the processor clock. |

|         |          |     | AT BUS                                                                                                                                                                                                                                                     |

| 110     | IRQSET1  | İ   | Interrupt Request Set 1 IRQSET1, along with MXCTL2 - 0, selects one of the of the following: A20GT, IRQ1, IRQ3 - IRQ7, IRQ12. Refer to Table 5-1 and Figure 5-1.                                                                                           |

| 111     | IRQSET0  |     | Interrupt Request Set 0 IRQSET0, along with MXCTL2 - 0, selects one of the following: ROM8, RESCPU, IRQ8, IRQ9 - IRQ11, IRQ14 and IRQ15. Refer to Table 5-1 and Figure 5-1.                                                                                |

| 114-112 | MXCTL2:0 | 0   | Multiplexer Control 2-0 MXCTL2 - MXCTL0, along with DRQIN, DACKEN, IRQSET1, IRQSET0 and PMCIN, control the external multiplexer for the selection of DRQs, DACKs, IRQs, ROM8, A20GT and RESCPU. Refer to Table 5-1 and Figure 5-1.                         |

| 115     | CSEN     | 0   | Chip Select Enable When CSEN is asserted, DPH, DPL, and RA10-RA8 are used to generate one of 28 different chip selects. Refer to Table 8-1.                                                                                                                |

| 116     | DACKEN   | 0   | DACK Enable When DACKEN is asserted, MXCTL2-0 are used to generate DACK7-5, 3-0 and BUS_RST. Refer to Table 5-1 and Figure 5-1.                                                                                                                            |

| 18      | DRQIN    | I   | Multiplexed DRQ Inputs DRQIN, along with MXCTL2 - 0, selects one of the DRQs or CLOCK_DIR_IN. Refer to Table 5-1 and Figure 5-1                                                                                                                            |

| 19      | IOCHRDY  | I/O | I/O Channel Ready Indicates extra wait states are required for the AT bus cycles.                                                                                                                                                                          |

**TABLE 3-2. SIGNAL DESCRIPTION**

| PIN | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                        |

|-----|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | ZEROWS   | 1   | Zero Wait States Indicates the current AT bus cycle can be finished in zero wait state.                                                                                                                                                            |

| 21  | IOCS16   | 1   | 16-Bit I/O Cycle<br>Inicates the I/O device on the AT bus is a 16-bit slave.                                                                                                                                                                       |

| 22  | MEMCS16  | 1   | 16-Bit Memory Cycle Indicates that the memory device on the AT bus is a 16-bit slave.                                                                                                                                                              |

| 23  | SPKR     | 0   | Speaker SPKR drives the speaker transistor.                                                                                                                                                                                                        |

| 24  | SA0      | I/O | System Address 0 When not in Master Mode, SA0 is an output and is asserted by the System Controller to place address 00 on the AT Bus SA0 line. When in Master Mode, SA0 is an input and is asserted by the Bus Master to place address on A0.     |

| 25  | LA20     | I/O | Early Address 20 When not in Master Mode, LA20 is an output and is asserted by the System Controller to place address 20 on the AT Bus LA20 line. When in Master Mode, LA20 is an input and is asserted by the Bus Master to place address on A20. |

| 26  | MASTER   | ı   | Master MASTER is asserted by the Bus Master to indicate that a Bus Master cycle is occurring. This causes LA20, SA0, MEMR, MEMW, IOR, and IOW to be selected as input signals.                                                                     |

| 27  | ALE      | 0   | Address Latch Enable ALE is used to clock the SA1 - SA19 address latches.                                                                                                                                                                          |

| 28  | AEN      | 0   | Address Enable AEN is asserted by the System Controller while performing DMA and Refresh cycles.                                                                                                                                                   |

| 29  | SDEN     | 0   | Swap Data Enable SDEN enables the data transfer between high and low bytes of the AT Bus.                                                                                                                                                          |

**TABLE 3-2. SIGNAL DESCRIPTION (Continued)**

| PIN | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | SDT/R    | I/O | Swap Data Transmit/Receive [80486] SDT/R controls the direction of the buffer between the low byte and high byte of the AT bus. SDT/R is tristated by a 50K pullup resistor internal to the WD7910 when RSTIN at pin 80 is low. SDT/R Mode - Output When SDT/R is high, it directs data from the low byte of the AT Bus to the high byte. When SDT/R is low, it directs data from the high byte of the AT bus to the low byte. Forcing SDT/R high while RSTIN is low selects the SDT/R mode. Holding SDT/R high as RSTIN goes high maintains the SDT/R mode. 80486 Mode - Input Selecting 80486 mode sets the SRC bit in Port 1072H to 1. This causes RDYIN at Pin 51 to be the default processor clock source input. Forcing SDT/R low while RSTIN is low selects the 80486 mode. holding SDT/R low as RSTIN goes high, maintains the 80486 mode. SDT/R pin may be forced low at reset with a 5K pulldown resistor or an open collector or tristate driver driven by RSTIN. |

| 32  | REFRESH  | I/O | Refresh As an output, REFRESH is asserted by the System Controller to refresh memory on the AT Bus. As an input, REFRESH is asserted by the Bus Master in conjunction with MEMR to refresh memory on the AT Bus and DRAM controlled by the System Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 36  | LOMEG    | 0   | First Megabyte LOMEG is asserted when the AT bus address is below 1 Mbyte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 37  | MEMW     | I/O | Memory Write MEMW is an output and it is asserted by the System Controller when a memory write access to the AT bus is to take place. It is an input during Master mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 38  | MEMR     | I/O | Memory Read MEMR is an output and it is asserted by the System Controller when a memory read access to the AT bus is to take place. It is an input during Master mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 39  | IOW      | I/O | I/O Write IOW is an output and it is asserted by the System Controller during processor or DMA access to indicate that an I/O write operation is to take place on the AT bus. IOW is an input during Master Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 40  | ĪŌŔ      | I/O | I/O Read IOR is an output and iit s asserted by the System Controller during processor or DMA access to indicate that an I/O read operation is to take place on the AT bus. IOR is an input during Master Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

**TABLE 3-2. SIGNAL DESCRIPTIONS (Continued)**

| PIN | MNEMONIC     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                    |

|-----|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74  | DT/R         | 0   | Data Transmit/Receive DT/ $\overline{R}$ controls the direction of the AT Data Bus D00 through D15. When DT/ $\overline{R}$ is high, data is directed to the AT Bus. When DT/ $\overline{R}$ is low, data is transferred from the AT bus.                                      |

| 75  | DEN1         | 0   | Data Bus Enable 1 When asserted, DEN1 enables the high order byte data buffer.                                                                                                                                                                                                 |

| 76  | DEN0         | 0   | Data Bus Enable 0 When asserted, DEN0 enables the low order byte data buffer.                                                                                                                                                                                                  |

| 77  | SYSCLK       | 0   | System Clock In asynchronous bus mode, SYSCLK is equal to BCLK2 divided by two when BCLK2 is less than 28 MHz, and divided by four when BCLK2 is greater than 28 MHz. In synchronous bus mode, SYSCLK is equal to CPUCLK divided by two or four, depending on the programming. |

| 79  | BALE         | 0   | AT Bus Address Latch Enable Address Latch Enable for the AT bus. BALE is synchronous with the Bus Clock (BCLK2).                                                                                                                                                               |

| 83  | IOCK         | ı   | I/O Channel Check When asserted, IOCK indicates a bus or memory error is on the AT bus and generates an NMI to the processor.                                                                                                                                                  |

|     |              |     | MAIN PROCESSOR CONTROL                                                                                                                                                                                                                                                         |

| 4   | BHE          | I/O | Bus High Enable As an input, BHE indicates a transfer of the high byte on the processor data bus. BHE is an output during DMA transfers.                                                                                                                                       |

| 43  | PEACK [D/C#] | ı   | Processor Extension Acknowledge [Data Control] In the 80286 mode, pin 43 is PEACK. in the 80386SX mode, pin 43 is D/C#.                                                                                                                                                        |

| 44  | M/IO         | I   | Memory or I/O Processor Memory cycle or I/O Status cycle.                                                                                                                                                                                                                      |

| 45  | S0 [ADS#]    | ı   | Processor Status 0 [Address Status] In the 80286 mode pin 45 is \$\overline{S0}\$. in the 80386SX mode, this pin 45 is ADS#.                                                                                                                                                   |

| 46  | S1 [W/R#]    | I   | Processor Status 1 [Write/Read] In the 80286 mode, pin 46 is S1. In the 80386SX mode, pin 46 is W/R#.                                                                                                                                                                          |

| 47  | READY        | 0   | Processor Ready READY is an output to the processor                                                                                                                                                                                                                            |

| 48  | HLDA         | ı   | Hold Acknowledge Processor hold acknowledge.                                                                                                                                                                                                                                   |

**TABLE 3-2. SIGNAL DESCRIPTIONS (Continued)**

| PIN                                    | MNEMONIC                           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                        |

|----------------------------------------|------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49                                     | HOLD                               | 0   | Hold Request Processor hold cycle request.                                                                                                                                                                                                                                         |

| 51                                     | RDYIN/CKA/PE                       | ı   | Processor Ready In / Alternate Clock / Parity Error The Memory Control Register at port address 3872H determines whether pin 51 is to be used as RDYIN, CKA or PE.                                                                                                                 |

|                                        |                                    |     | RDYIN is used in a discrete cache system to indicate a hit or miss.                                                                                                                                                                                                                |

|                                        |                                    |     | CKA is used as a source for the CPU clock.                                                                                                                                                                                                                                         |