#### XL-8237 32-BIT RASTER IMAGE PROCESSOR

## PRELIMINARY DATA October 1988

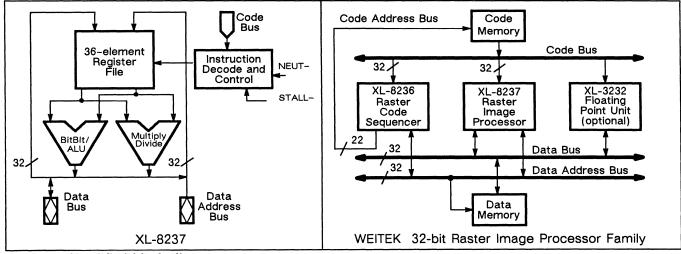

The WEITEK XL-8237 is a fullyintegrated CMOS 32-bit raster image processor. It is used with the WEITEK XL-8236 22-bit raster code sequencer to make the HyperScript-Processor, a high-performance graphics CPU capable of driving raster printers at up to 60 pages per minute. WEITEK's single-precision floatingpoint unit may also be used to produce a tightly-coupled raster image printing system.

| Contents                            |            |

|-------------------------------------|------------|

| Features                            | 1          |

| Description                         | 1          |

| Architecture                        | 2          |

| Block Diagram                       | 4          |

| Signal Description                  | 5          |

| Memory Addressing                   | 6          |

| Registers                           | 7          |

| Instruction Set                     | 9          |

| Memory Operations                   | 51         |

| Instruction Neutralizatio           | n 53       |

| NOP                                 | 53         |

| Overflow Detection                  | 53         |

| Development Tools                   | 54         |

| Design Requirements                 | 55         |

| Specifications                      | 56         |

| Recommended Operation<br>Conditions | n<br>56    |

| DC Specifications                   | 56         |

| AC Timing Description               | 57         |

| AC Specifications                   | 58         |

| Timing Diagrams                     | 59         |

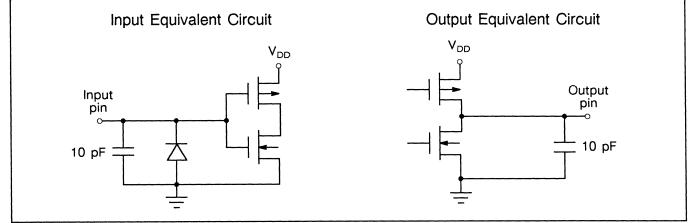

| I/O Characteristics                 | 61         |

| Pin Configuration                   | 62         |

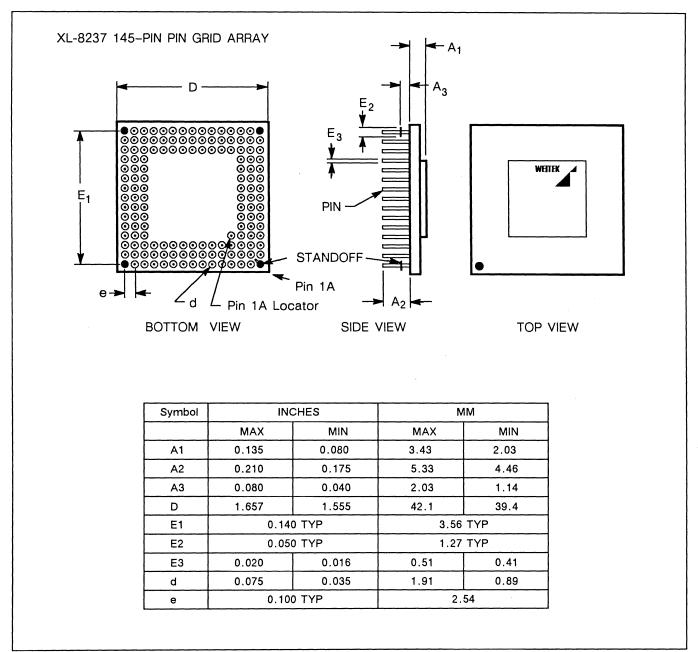

| Physical Dimensions                 | 63         |

| Ordering Information                | 64         |

| Revision Summary                    | 64         |

| Documentation Request               | Form 65    |

| Sales Offices                       | back cover |

The masters for this document were printed on an XL-8200 development system

XL-8237 Raster Image Processor Data Sheet October, 1988

Copyright ©WEITEK Corporation 1988 All rights reserved

WEITEK Corporation 1060 East Arques Avenue Sunnyvale, California 94086 Telephone (408) 738-8400

WEITEK is a trademark of WEITEK Corporation

PostScript is a registered trademark of Adobe Systems, Incorporated BITSTREAM and FontWare are trademarks of BITSTREAM Corporation UNIX is a trademark of AT&T Bell Laboratories XENIX and MS-DOS are trademarks of Microsoft Corporation NIMBUS is a registered trademark of URW Corporation

WEITEK reserves the right to make changes to these specifications at any time

Printed in the United States of America 90 89 88 6 5 4 3 2 1

#### PRELIMINARY DATA October 1988

## Features

32-BIT, SINGLE-CHIP GRAPHICS PROCESSOR

32-bit integer ALU Four-port 36×32 register file Parallel multiply/divide unit for Bezier computation 32-bit shift/field merge unit for BitBlt Single-cycle execution

#### HIGH PERFORMANCE

10 to 60 pages per minute running WEITEK's HyperScript interpreter Peak BitBlt rate of over 65 million pixels per second Bezier computations at 750 thousand endpoints per second

#### LOW SYSTEM COST

145-pin plastic PGA (pin grid array) package Low power CMOS with TTL-compatible I/O

#### POWERFUL INSTRUCTION SET

Add, subtract, multiply, and divide Complete set of logical operations Shifts up to 31 bits in one cycle Priority encode Field extract/deposit/merge instructions Perfect exchange (including bit reverse)

POWERFUL DEVELOPMENT TOOLS

PostScript-compatible interpreter C compiler Graphics development system

#### **INTERFACES WITH OTHER XL-8200 PRODUCTS**

Interfaces with the XL-8236 raster control sequencer Interfaces with XL-8232 graphics floating point unit

## Description

The XL-8237 is a RISC-architecture 32-bit raster image processor (RIP). It is used with the XL-8236 32-bit raster code sequencer (RCS) to form the XL-8200 HyperScript-Processor, a high-performance graphics processor that can run WEITEK's HyperScript interpreter and other page description languages. These chips also interface directly with WEITEK's 32-bit graphics floating point unit, the XL-3232. The XL-8237 was designed specifically as a laser beam printer controller running a page description language. WEITEK supplies the HyperScript interpreter, a Post-Script-compatible interpreter for its HyperScript-Processors. The architecture supports speeds from 10 to 60 pages per minute; thus it is a powerful and cost effective solution for a wide range of speeds, resolutions, colors, and page description languages.

Figure 1. Simplified block diagrams

## Description, continued

#### SPEED

6000 sans serif 10-point characters per second font placement rate

750 sans serif 10-point characters per second font-generation rate using URW's NIMBUS font-scaling from

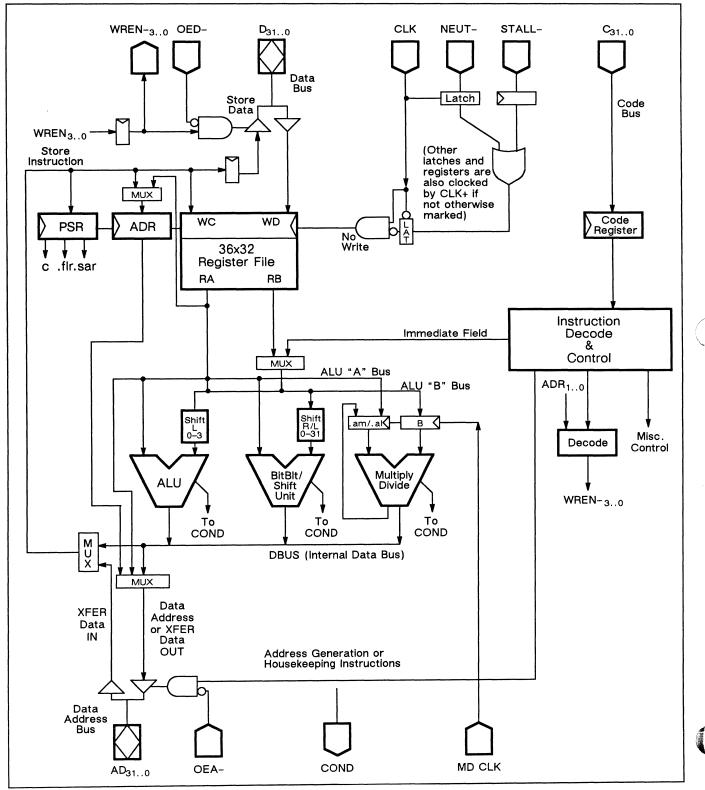

#### Architecture

#### ALU

The heart of the XL-8237 RIP is the 32-bit ALU, which contains the hardware for arithmetic and logical functions. The ALU performs 32-bit addition and sub-traction, sixteen different logical functions, and address generation. All ALU operations are performed in a single cycle.

#### BITBLT/SHIFTER/FIELD MERGE UNIT

The shift/merge unit provides a rich set of instructions for key raster image processing applications such as bit block transfer (BitBlt) and character placement.

The shifter unit provides 0-31 bits of shifting in either direction in the deposit, extract, and merge operations. This allows the RIP to extract bit fields of any length, operate on them, and replace them in the original word. Bit fields can also be combined through the bitwise merge instruction.

The perfect exchange function is used to rearrange the bits within a single word in a variety of ways. It can Bezier outlines

75 sans-serif 10-point characters per second font-generation rate using BITSTREAM FontWare font-scaling from Bezier outlines

be used to swap fields of 2, 4, 8, or 16 bits, reverse the bit order within these fields, or both.

The priority encode function counts the number of zero bits before the first one bit is encountered.

#### MULTIPLY/DIVIDE UNIT

The multiply/divide unit make the RIP very effective in mathematically-intensive operations such as character generation and scaling from Bezier outlines.

Hardware multiply and divide functions give a 64-bit product of two 32-bit operands in 8 cycles, and a 32-bit quotient and 32-bit remainder from a mixed 64/32 bit division in 20 cycles. The multiply/divide unit operates independently of the rest of the ALU, so other operations can be performed in parallel with multiplication and division. The integer multiply/divide unit can emulate floating point operations in software at a 25-cycle rate (0.3 MFLOP at 120 ns).

PRELIMINARY DATA October 1988

#### Architecture, continued

## **REGISTER FILE**

The four-port register file contains 36 registers, each 32 bits wide. This large register file allows frequently-used variables to be kept on-chip, reducing the number of memory accesses and increasing performance.

Registers 28–31 are duplicated in a second bank to give four temporary registers which can be used during interrupt handling.

#### **BUS STRUCTURE**

There are three independent 32-bit buses: Code, Data, and Data Address (C, D, and AD buses, respectively).

Independent code and data buses allow data-intensive operations such as BitBlt and character placement to run continuously, without being interrupted by code fetches.

The Code Bus provides the RIP with its instruction stream. When used with the XL-8236 raster code sequencer (RCS), both chips share the same 32-bit instruction stream. Many instructions also use the code word to provide immediate data fields.

The Data Bus provides bidirectional access to external memory, at the rate of one load per cycle or one store every two cycles. The Data Bus has individual write-select lines (WREN lines) for each byte in the word.

The Data Address bus is used to provide memory addresses and to transfer data to and from the RCS and I/O devices. A word can be transferred over the AD Bus every cycle.

#### MEMORY ACCESS

Loading and storing from memory is done with the address generation instructions and Load and Store Data instructions. The RIP uses a delayed load/delayed store scheme which overlaps memory access with other RIP operations in a straightforward way.

Memory access includes load and store instructions with features such as indexed addressing and pre- and post-increment addressing. The basic memory word is 32 bits wide, but bytes and halfwords can be accessed individually. Load and store operations take two instructions, but are pipelined to allow other operations to occur in parallel with memory access.

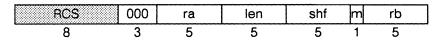

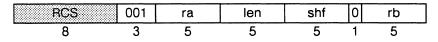

## INSTRUCTION FORMAT

The RIP's instruction set is based on register-to-register operations specified in a 32-bit instruction word. The basic instruction format has three 5-bit register select fields, opcode and extended opcode fields, and a condition code select field. Thus a three-address instruction of the form rc := ra + rb can be specified in a single word.

In many instructions, one of the operands can be replaced by an immediate value, allowing operations on constants to be specified in a single instruction without first loading the constant into a register.

Most instructions reserve the most-significant eight bits of the instruction word for an RCS opcode. When the RIP is used with the RCS, the two chips share the same 32-bit instruction stream.

# **Block Diagram**

Figure 2. XL-8237 block diagram

PRELIMINARY DATA October 1988

## Signal Description

#### C+

The  $C_{31..0}$  Code Bus contains a 32-bit instruction word. Because it contains a built-in pipeline register, it is not necessary to use an external pipeline register between code memory and the XL-8237.

#### D+

The  $D_{31..0}$  Data Bus is used as a bidirectional input/output bus. Data flow is in the form of memory-to-register and register-to-memory transfers. Tri-stating of the D Bus is controlled by the currently executing instruction and the OED- signal.

### AD+

The AD<sub>31..0</sub> Data Address Bus provides addresses for data memory operations. It is driven with either the contents of the address register (.adr) or the result of an address computation instruction. Tri-stating of the AD Bus is controlled by the currently executing instruction and the OEA- signal. It can also be used as a bidirectional data bus for transfers from the RCS or other hardware.

## COND+

The COND output is a single-bit condition code signal that indicates one of several possible one-bit status values derived from the result of the current instruction. See *Condition Code Generation* section on page 13.

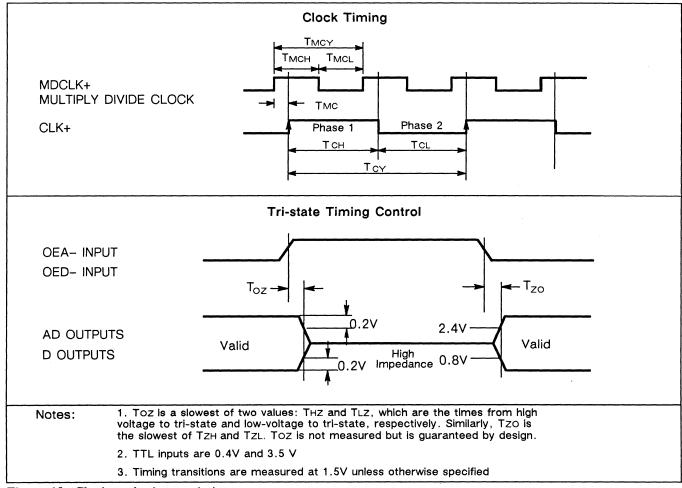

#### CLK

The clock input, CLK, is a single-phase TTL-level clock signal. One instruction is executed per clock cycle. The CLK signal selects whether the current clock cycle is to be "phase one" (CLK high) or "phase two" (CLK low). Many of the external signals are synchronized to either the rising or falling edge of this signal.

#### MDCLK

The Multiply/Divide clock input, MDCLK, is a singlephase TTL-level clock signal. The internal multiply/divide registers are synchronized to the positive-going edge of this clock. This signal must be synchronized to the rising and falling edges of the CLK signal, and runs at twice the frequency of CLK.

## NEUT-

The NEUT- input causes the currently executing instruction to be neutralized or canceled; that is, any internal effects that the instruction was to have (such as modification of register contents or status bits) are canceled.

### STALL-

The STALL- input cancels the next instruction.

#### WREN-

The WREN-3... outputs indicate which bytes of the data word are to be stored to the data memory. This control information is driven when a Store Data instruction is executed by the RIP, otherwise these signals are high.

## OEA-, OED-

OEA- and OED- are asynchronous output enable signals for the AD and D buses respectively. The buses drive when their respective output enables are low, and float when output enables are high.

If the OEA- signal is de-asserted, then the AD Bus is tri-stated regardless of the OEA signal or the executing instruction. If the OEA- signal is asserted, then the AD Bus is driven under control of the OEA+ signal or the currently executing instruction. Note that OEA- is *not* simply the complement of OEA+.

The OED- signal functions similarly. If the OED- signal is de-asserted, then the D Bus is tri-stated.

#### VCC, GND

The VCC and GND pins provide a supply voltage of +5.0 volts, and system ground of 0 volts, respectively. All VCC and GND pins must be connected.

#### TIE HIGH, TIE LOW

Signals marked "Tie High" should be tied to VCC. Signals marked "Tie Low" should be tied to GND. Future versions of the XL-8237 may redefine these as signal pins, so it's advisable to tie them through traces rather than directly to power and ground planes.

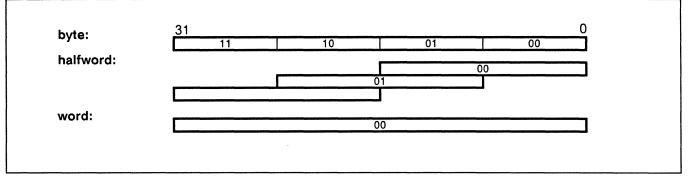

# **Memory Addressing**

The XL-8237 provides address generation functions, including addressing of bytes, halfwords, or words in a word-wide memory. These functions determine byte and halfword positioning within a word from the least significant two bits of the memory address. This is illustrated in figure 3.

Halfword addresses ending with "11" and word addresses ending with "01," "10," or "11" are not defined for Load and Store operations—that is, data to be loaded cannot straddle a word boundary. Data that straddles a word boundary can be obtained using two loads and a merge.

Figure 3. Memory addressing

## Registers

#### **REGISTER FILE**

The register file contains 36 registers, each 32 bits wide, which are accessed through four independently addressable ports.

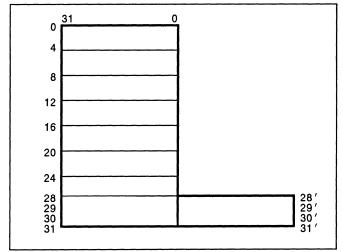

The 36 registers are numbered 0-31 and 28'-31'. (See figure 4.) Only registers 0-31 can be directly accessed through the five-bit register numbers contained in an instruction. A special instruction, swap (one of the housekeeping instructions), exchanges the contents of registers 28-31 and 28'-31' in a single cycle. Normally the four extra registers are used only by interrupt routines for temporary working storage.

Figure 4. Data registers

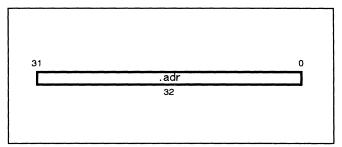

### ADDRESS HOLDING REGISTER

The XL-8237 retains the last address generated by any of the address generation instructions in the .adr register. The .adr register serves two purposes. It is used by the interrupt mechanism to aid in saving and restoring the state of the system. It is used by the byte alignment instructions to indicate the beginning byte offset. The format is given in figure 6.

Figure 5. Address register

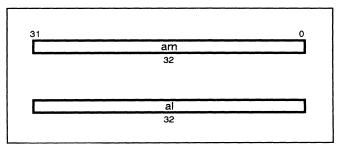

#### PRODUCT REGISTERS

There are two 32-bit product registers: .am and .al. They are used by the multiply and divide hardware and the bitwise merge instruction. During the operation of the multiply and divide hardware the contents of these registers are undefined. This implies that the bitwise merge instruction cannot be used during a multiply or divide operation. Several instructions in the housekeeping instruction set explicitly manipulate the contents of these registers. The format is given in figure 6.

Figure 6. Product registers

# Registers, continued

## PROCESSOR STATUS REGISTER

The RIP retains some control information in the *proc*essor status register, .psr. The format is given in figures 7 and 8.

| 31 |          |        |     | 0   |

|----|----------|--------|-----|-----|

|    | reserved | be z c | flr | sar |

|    | 20       | 1 1 1  | 5   | 5   |

Figure 7. Processor status register

| Symbol   | Meaning                                               |

|----------|-------------------------------------------------------|

| sar      | shift amount register                                 |

| fir      | field length register                                 |

| с        | carry bit                                             |

| z        | register bank select (for registers 28-31 or 28'-31') |

| be       | reserved for future extension. Must be set to zero    |

| reserved | reserved for future extension. Must be set to zero.   |

Figure 8. Processor status register bit fields

# **Instruction Set**

## TERMS AND SYMBOLS

The instructions are listed on page 11, then described in detail on the following pages. Each description includes a pseudo-code definition of the instruction. The following symbols are used:

- || Concatenate fields. abc || def gives abcdef.

- Indicates that operations separated by this symbol occur in parallel.

- a dup b Duplicate b a times. 3 dup 0 gives 000.

- reg(ra) Register number ra

- COND Condition Code

- { } Begin and end comment

- ≪ ixs Shift left by ixs bits

- tcovf Two's complement overflow

- usovf Unsigned overflow

- unadd Unsigned add

- unsub Unsigned subtract

- result The result of any internal operation that is available on the *internal* DBUS (see Simplified Block Diagram, figure 2). Typically, result will be driven out on the AD Bus but can also be driven out on the D Bus.

- [31..0] Specifies the bit field from bits 31 to bit 0, inclusive. For example, reg (ra) [3..0] gives the lower four bits of register ra.

- a op b Perform an operation on operands a and b

# **Instruction Format**

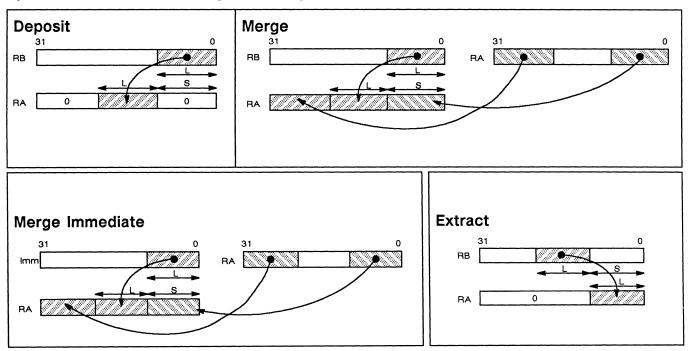

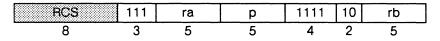

A 32-bit instruction word is used to control the operation of the XL-8237. This instruction word is designed to be directly shared by the XL-8236 RCS. Therefore, the two parts should be considered together.

Normally the instruction word is divided into two sections. The first, the most significant 8 bits, is used to control I/O operation of the RIP as well as perform many RCS operations. The second, the least significant 24 bits, is normally used to control the internal operations of the RIP. However, this second field can be used by certain, so-called "long" RCS operations and by inter-chip transfer instructions.

The following table gives the abbreviations used for bit fields. The instruction formats are given in figure 10 on the next page.

| Field               | Meaning                                           |

|---------------------|---------------------------------------------------|

| RCS                 | RCS control field                                 |

| ra                  | register select                                   |

| rb                  | register select                                   |

| rc                  | register select                                   |

| rd                  | register select                                   |

| shf                 | controls amount of shift in Extract/Deposit/Merge |

| len                 | controls field length in Extract/Deposit/Merge    |

| р                   | controls Perfect Exchange                         |

| imm16               | 16-bit signed immediate data field                |

| imm11               | 11-bit signed immediate data field                |

| imm10               | 10-bit signed immediate data field                |

| imm5                | 5-bit signed immediate data field                 |

| cn                  | selects condition to be generated                 |

| e,ext,m             | operation code extensions                         |

| ixs                 | shift specification                               |

| S                   | specifies signed or unsigned                      |

| siz                 | size of data item                                 |

| processor operation | any 24-bit RIP instruction                        |

| x                   | Reserved for future definition*                   |

Figure 9. Instruction fields

## PRELIMINARY DATA October 1988

# Instruction Format, continued

(

C

| Arithmetic and Logical Instruction                           |            |            |         |             |           |          |              | Deta<br>Descri |

|--------------------------------------------------------------|------------|------------|---------|-------------|-----------|----------|--------------|----------------|

| Arithmetic instructions                                      | 8<br>RCS   | 3          | 5<br>ra | 5<br>  rc   | ext       | 6<br>  c | 5<br>rb/imm5 | Page<br>13     |

| Add Signed Immediate                                         | RCS        | 101        | ra      | rc          | 1<br>1 ii | mmec     | liate10      | 15             |

| Logical instructions                                         | BCS        | 101        | ra      | rc          | 0 ext     | c Ic     | rb           | 16             |

| -                                                            |            | <u>a</u> 1 |         |             | 101 0/1   |          |              |                |

| Field Manipulation Instructions<br>Deposit/Deposit and Merge | RCS        | 000        | ra      | len         | shf       | m        | rb           | 19             |

| Merge Immediate                                              | RCS        | 000        |         | 1           | - <u></u> | 1        |              | 20             |

| Extract                                                      |            |            | ra      |             | shf       |          | imm5         | 20             |

|                                                              | RCS        | 001        | ra      | len         | shf       | 0        | rb           | 21             |

| Dynamic Extract/Deposit/Merge                                | RCS        | 100        | ra      | len         | 111       | ext      | rb           | 22             |

| Merge Halfword High                                          | RCS        | 011        | ra      |             | immedia   | ate16    |              | 23             |

| Bitwise Merge                                                | RCS        | 111        | ra      | rc          | 1111      | 01       | rb           | 24             |

| Perfect Exchange                                             | RCS        | 111        | ra      | р           | 1111      | 10       | rb           | 25             |

| Address Generation Instructions                              |            |            |         |             |           |          |              |                |

| Load/Store Address with                                      | RCS        | 110        | ra      | I           | immedia   | ate16    |              | 27             |

| Signed Displacement<br>Load/Store Address with               |            | <u> </u>   |         | ı           |           | 1.       |              |                |

| Index/Signed Displacement                                    | RCS        | 111        | ra      | rc          | 1 ext     | ixs      | rb/imm5      | 28             |

| Lood/Storo and Alignment Instru                              | ationa     |            |         |             |           |          |              |                |

| Load/Store and Alignment Instru<br>Load Halfword Immediate   | RCS        | 010        | ra      | 1           | immedia   | te16     |              | 31             |

| Load Data to RIP                                             | [          |            |         | RIP oper    |           |          |              | l 32           |

| Store Data from RIP                                          |            |            |         |             |           |          |              |                |

|                                                              | 00001001   | <u> </u>   |         | peration (r |           |          |              | 33             |

| Byte Align for Load Data                                     | RCS        | 111        | ra      | X 0 s siz   |           | 00       | rb           | 34             |

| Byte Align and Store Data                                    | RCS        | 111        | ra      | e 1 s siz   | z 1111    | 00       | rb           | 36             |

| Miscellaneous                                                |            |            |         |             |           |          |              |                |

| Multiply/Divide/Priority<br>Encode/Housekeeping              | RCS        | 111        | ra      | ext         | 1111      | 11       | rb/imm5      | ] 38           |

|                                                              |            |            |         |             |           |          |              |                |

| Coprocessor/Sequencer Operation                              | ons<br>RCS | 111        | ×       | ×           | 0 ×       | ×        | ×            | ] 47           |

| Store Data from Coprocessor                                  |            |            | L       | RIP ope     | 1-1       | <u> </u> | <u> </u>     | ]<br>] 48      |

| Load Data to Coprocessor                                     | 101 rd     |            |         |             |           |          |              | 49             |

| ·                                                            | 111 rd     |            | r       | RIP ope     |           |          |              | 3              |

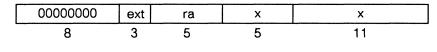

| Transfer to/from RIP                                         | 0000000    | ext        | ra      | <u> </u>    |           |          |              | 50             |

| Long RCS instruction                                         | 0000001    |            |         | cs          |           |          |              |                |

| Long RCS instruction                                         | 0000010    |            |         | CS          |           |          |              |                |

| Long RCS instruction                                         | 00000011   |            | R       | CS          |           |          |              | ]              |

| Long RCS instruction                                         | 0001       |            | R       | CS          |           |          |              |                |

Figure 10. XL-8237 Instruction formats

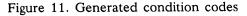

# **Condition Code Generation**

All instructions that could produce a meaningful condition code, generate one automatically. These are single-cycle instructions. Specific condition codes generated by each single-cycle instruction are summarized in the table below. The condition code generated by an instruction is available on the COND pin at the end of the cycle during which the instruction is executed. Instructions not listed in the table do not generate any condition. See descriptions of individual instructions for details.

| Condition | Format    |                |                                                                            | Function                               |

|-----------|-----------|----------------|----------------------------------------------------------------------------|----------------------------------------|

| cond      | ra        | := ra (        | deposit rb[shf,len]                                                        | deposit                                |

| cond      | ra        | := ra e        | extract rb[shf,len]                                                        | extract                                |

| cond      | ra        | := ra (        | deposit imm5[shf,len]                                                      | deposit imm5                           |

| cond      | ra        | := imn         | n16                                                                        | load imm16                             |

| cond      | ra        | := ra (        | deposit imm16[16,16]                                                       | merge imm16                            |

| cond1     | c,rc      | := rb/i        | mm5 <u>+</u> ra+c                                                          | arithmetic                             |

| cond      | ra        | := ra (        | deposit rb [.sar,.flr]                                                     | dynamic deposit                        |

| cond      | ra        | := extr        | ract rb[.sar,.flr]                                                         | dynamic extract                        |

| cond2     | ra        | := ra          | op rb                                                                      | logical                                |

| cond3     | rc        | := ra+imm10    |                                                                            | add imm10                              |

| cond4     | .adr      | := ra+         | imm16                                                                      | load/store address generation          |

| cond3     | rc        | := ra+         | (rb< <ixs)< td=""><td>add with index</td></ixs)<>                          | add with index                         |

| cond4     | ra,.adr   | := ra+         | (rb/imm5< <ixs)< td=""><td>load/store indexed address generat</td></ixs)<> | load/store indexed address generat     |

| cond      | mem[.a    | adr]:= rb a    | align[signed siz]                                                          | byte align for store                   |

| cond      | rc        | := (ra         | and not al) or (rb and al)                                                 | bitwise merge                          |

| cond      | ra        | := p e         | exchange rb                                                                | perfect exchange                       |

| cond      | ra        | := pric        | prity encode rb                                                            | priority encode                        |

| cond      | ra        | := am          | +rb+al[31]                                                                 | retrieve multiply/divide result        |

| Co        | nditions: |                |                                                                            |                                        |

|           |           | cond           | non-zero result                                                            |                                        |

|           |           | cond1          |                                                                            | (unsigned or two's complement)         |

|           |           | cond2          | non-zero, or all bytes                                                     |                                        |

|           |           | cond3<br>cond4 | two's complement over                                                      | tiow<br>wo's complement shift overflow |

PRELIMINARY DATA October 1988

## **Arithmetic Instructions**

| RCS | 100 | ra | rc | ext | cn | rb/imm5 |  |

|-----|-----|----|----|-----|----|---------|--|

| 8   | 3   | 5  | 5  | 4   | 2  | 5       |  |

### FORMAT

| instruction                       | ext  | meaning                               |

|-----------------------------------|------|---------------------------------------|

| c,rc := unsigned(ra + rb)         | 0000 | unsigned add                          |

| c,rc := unsigned(rb - ra)         | 0001 | unsigned subtract                     |

| c,rc := unsigned(ra + rb + c)     | 0010 | unsigned add with carry               |

| c,rc := unsigned(rb - ra - 1 + c) | 0011 | unsigned subtract with borrow         |

| rc := ra + imm5                   | 0100 | two's complement add immediate        |

| rc := imm5 - ra                   | 0101 | two's complement subtract immediate   |

| rc := ra + rb                     | 0110 | two's complement add                  |

| rc := rb - ra                     | 0111 | two's complement subtract             |

| c,rc := ra + rb                   | 1000 | two's complement add                  |

| c,rc := rb - ra                   | 1001 | two's complement subtract             |

| c,rc := ra + rb + c               | 1010 | two's complement add with carry       |

| c,rc := rb - ra - 1 + c           | 1011 | two's complement subtract with borrow |

| c,rc := ra + imm5                 | 1100 | two's complement add immediate        |

| c,rc := imm5 - ra                 | 1101 | two's complement subtract immediate   |

#### DESCRIPTION

Arithmetic instructions include signed and unsigned add (with and without carry), and signed and unsigned subtract (with and without borrow).

Depending on the value of the ext field, the contents of register ra is either added or subtracted from either the contents of register rb, or a sign-extended immediate value. Four forms of this instruction also add in the c bit from the .psr, and ten forms update the c bit. The result is placed in register rc.

## CONDITION

The condition generated depends on the value of the *ext* and *cn* fields of the instruction. For most operations, the condition generated assumes that the result is a two's complement value; however, for the unsigned add and subtract operations, the condition generated assumes that the result is an unsigned quantity. The unsigned and two's complement equal-to conditions and less-than conditions remain arithmetically valid for all valid input values, even if unsigned or two's complement overflow occurs as a result of the addition or subtraction operation.

| cn | condition signal generated                              |

|----|---------------------------------------------------------|

| 00 | two's complement/unsigned not equal to zero             |

| 01 | two's complement/unsigned greater than or equal to zero |

| 10 | two's complement/unsigned overflow                      |

| 11 | two's complement/unsigned greater than zero             |

|    |                                                         |

## Arithmetic Instructions, continued

#### **OPERATION**

```

temp := 28 dup imm[4] || imm[3..0];

case ext of

0000b: c || result := reg(ra) + reg(rb);

0001b: c || result := (not reg(ra)) + reg(rb) + 1;

0010b: c || result := reg(ra) + reg(rb) + c;

0011b: c || result := (not reg(ra)) + reg(rb) + c;

0100b:

result := reg(ra) + temp;

0101b:

result := (not reg(ra)) + temp + 1;

0110b:

result := reg(ra) + reg(rb);

result := (not reg(ra)) + reg(rb) + 1;

0111b:

1000b: c || result := reg(ra) + reg(rb);

1001b: c || result := (not reg(ra)) + reg(rb) + 1;

1010b: c || result := reg(ra) + reg(rb) + c;

1011b: c || result := (not reg(ra)) + reg(rb) + c;

1100b: c || result := reg(ra) + temp;

1101b: c || result := (not reg(ra)) + temp + 1;

endcase;

reg(rc) := result;

if ext [3..2] \neq 00b then

tcovf:= c32 xor c31

case c of

00b: cond := (result \neq 0) or tcovf; *

01b: cond := result[31] xnor tcovf;

10b: cond := tcovf;

11b: cond := (result \neq 0 or tcovf) and (result[31] xnor tcovf);

endcase:

else

usovf := unsub xor c32;

case c of

00b: cond := result \neq 0 or usovf;

01b: cond := unadd or c32;

10b: cond := usovf;

11b: cond := (result \neq 0 or usovf) and (unadd or c32);

endcase;

endif:

COND := cond;

```

\* See Overflow Detection.

PRELIMINARY DATA October 1988

# Arithmetic Instructions, continued

## ADD SIGNED IMMEDIATE

### FORMAT

rc := ra + imm10

## DESCRIPTION

The 10-bit signed immediate value is added to the contents of register ra. The result is placed in register rc. This instruction does not affect the c bit of the .psr.

## **OPERATION**

The condition generated is TRUE (1) if a signed 32-bit overflow is encountered, otherwise the condition generated is FALSE (0).

| result  | := reg(ra) + (23 dup imm10[9])    imm10[80]; | <pre>{sign-extend and add}</pre> |

|---------|----------------------------------------------|----------------------------------|

| reg(rc) | := result;                                   |                                  |

| COND    | := tcovf;                                    |                                  |

1 5

# Logical Instructions

## LOGICAL INSTRUCTIONS

| RCS 101 ra                  | rc | 0 ext    | С | rb              |

|-----------------------------|----|----------|---|-----------------|

| 8 3 5                       | 5  | 1 4      | 1 | 5               |

| FORMAT                      |    | <b>.</b> |   |                 |

| instruction                 |    | ext      |   | meaning         |

| rc := zeros                 |    | 1111     |   | clear all bits  |

| rc := ra and rb             |    | 1110     |   | logical and     |

| rc := ra and (not rb)       |    | 1101     |   | logical and-not |

| rc := ra                    |    | 1100     |   | pass            |

| rc := (not ra) and rb       |    | 1011     |   | logical not-and |

| rc := rb                    |    | 1010     |   | pass            |

| rc := ra xor rb             |    | 1001     |   | logical xor     |

| rc := ra or rb              |    | 1000     |   | logical or      |

| rc := (not ra) and (not rb) |    | 0111     |   | logical nor     |

| rc := ra xnor rb            |    | 0110     |   | logical xnor    |

| rc := not rb                |    | 0101     |   | logical not     |

| rc := ra or (not rb)        |    | 0100     |   | logical or-not  |

| rc := not ra                |    | 0011     |   | logical not     |

| rc := (not ra) or rb        |    | 0010     |   | logical not-or  |

| rc := (not ra) or (not rb)  |    | 0001     |   | logical nand    |

| rc := ones                  |    | 0000     |   | set all bits    |

|                             |    | 1        |   |                 |

## DESCRIPTION

The contents of register ra and the contents of register rb are combined in a logical or bitwise function. The function performed depends on the value of the *ext* field. The result is placed in register rc.

#### CONDITION

The condition generated depends on the value of the the c field. The condition "all bytes non-zero" permits quick scanning through byte data, using word operations.

#### PRELIMINARY DATA October 1988

## Logical Instructions, continued

| condition                | с | condition signal generated  |

|--------------------------|---|-----------------------------|

| $\neq$ 0                 | 0 | not equal to zero           |

| all bytes of rc $\neq$ 0 | 1 | all bytes not equal to zero |

# OPERATION

```

case ext of

1111b: result := 32 dup 0;

1110b: result := reg(ra) and reg(rb);

1101b: result := reg(ra) and (not reg(rb));

1100b: result := reg(ra);

1011b: result := (not reg(ra)) and reg(rb);

1010b: result := reg(rb);

1001b: result := reg(ra) xor reg(rb);

1000b: result := reg(ra) or reg(rb);

0111b: result := (not reg(ra)) and (not reg(rb));

0110b: result := reg(ra) xnor reg(rb);

0101b: result := not reg(rb);

0100b: result := reg(ra) or (not reg(rb));

0011b: result := not reg(ra);

0010b: result := (not reg(ra)) or reg(rb);

0001b: result := (not reg(ra)) or (not reg(rb));

0000b: result := 32 dup 1;

endcase:

case c of

0b: cond := (result \neq 0);

1b: cond := not((result[31..24]=0) or (result[23..16]=0) or (result[15..8]=0) or (result[7..0]=0));

endcase;

reg(rc) := result;

COND := cond;

```

## **Field Manipulation Instructions**

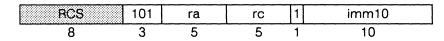

The Extract, Deposit, and Merge instructions are used to perform computations on portions of a word. Typically, the desired bit field is converted into a full word, using an Extract instruction, operated on and converted back into a bit field by the Deposit or Merge instructions. These instructions can also be used to perform simple left and right shifts as well as rotations. Figure 12 shows the operation of these instructions.

The Extract/Deposit/Merge instructions have two forms: static and dynamic. The static form specifies the field length and shift amount in the instruction as constants. The dynamic form uses the .flr and .sar fields from the .psr.

-The Extract instruction converts a bit field within a register into a 32-bit value which is stored into another register. The extracted bit field is aligned to the leastsignificant bit of the destination register. The high order bits of the destination are filled with zeros or sign extended, controlled by the field length and shift amount. If the sum of the field length and shift amount is greater than 32, sign extension is performed; otherwise zero-fill is selected.

The Deposit and Merge instructions perform the inverse operation: a 32-bit register is inserted into a specified field of a destination register. For Deposit instructions, all other bits of the destination are set to zero. For Merge instructions, the other bits of the destination are not modified.

There is a special form of the Merge instruction: Merge Immediate, which uses a 5-bit signed constant instead of a register as the value to be inserted. This instruction allows convenient bit set and reset as well as many other useful operations.

Figure 12. Deposit, extract, and merge instructions

PRELIMINARY DATA October 1988

## Field Manipulation Instructions, continued

DEPOSIT/DEPOSIT AND MERGE

### FORMAT

ra := deposit rb [shf, len]

ra := ra deposit rb [shf, len]

### DESCRIPTION

A right justified field of length specified by *len* is taken from the contents of register *rb*. The field is left-shifted by *shf* bits. If the sum of *shf* and *len* is greater than 32,

#### CONDITION

The condition generated is TRUE (1) if the result of the operation is non-zero and is FALSE (0) if the result is zero.

the field is truncated. If the m bit is zero, the result is the field, otherwise the field is merged with the contents of register ra. The result is placed in register ra.

OPERATION

if len > 0 then 1 := len: else 1 := 32; endif; f := 1 + shf;if f > 32 then f := 32; 1 := 32 - shf;endif; if m = 0 then result := (32-f dup 0) || reg(rb)[I-1..0] || (shf dup 0); {shift rb left by shf bits} else result := reg(ra) [31..f] || reg(rb) [I-1..0] || reg(ra) [shf-1..0]; {overlay field from rb on top of ra} endif; reg(ra) := result; COND := (result  $\neq$  0); {condition is TRUE if result is non-zero}

• ~

## Field Manipulation Instructions, continued

#### MERGE IMMEDIATE

| RCS | 001 | ra | len | shf | 1 | imm5 |

|-----|-----|----|-----|-----|---|------|

| 8   | 3   | 5  | 5   | 5   | 1 | 5    |

#### FORMAT

ra := ra deposit imm5 [shf, len]

#### DESCRIPTION

A right justified field of length specified by *len* is taken from the sign extended value contained in the *imm5* field. The field is left shifted by *shf* bits. If the sum of *shf* and *len* is greater than 32, the field is truncated. The field is merged with the contents of register ra. The result is placed in register ra.

#### **OPERATION**

if len > 0 then

# CONDITION

The condition generated is TRUE (1) if the result of the operation is non-ZERO and is FALSE (0) if the result is ZERO.

#### PRELIMINARY DATA October 1988

## Field Manipulation Instructions, continued

## EXTRACT

## FORMAT

ra := extract rb [shf, len]

### DESCRIPTION

The contents of register rb is right-shifted by the number of bits specified by shf, and a right-justified field of length specified by *lon* is extracted from it. If the sum of *shf* and *lon* is greater than 32, the extracted field is sign-extended. The result is the extracted field, which is placed in register ra.

## OPERATION

# if len > 0 then | := len; else | := 32; endif; temp := (shf dup reg(rb)[31]) || reg(rb)[31..shf]; {shift rb right by shf bits} result := (32-I dup 0) || temp[I-1..0]; {zero all the bits outside the selected field} reg(ra) := result; COND := (result $\neq$ 0);

CONDITION

result is ZERO.

The condition generated is TRUE (1) if the result of

the operation is non-ZERO and is FALSE (0) if the

## © Copyright WEITEK 1988 All rights reserved

## Field Manipulation Instructions, continued

## DYNAMIC EXTRACT/DEPOSIT/MERGE

| RCS | 100 | ra | len | 111 | ext | rb |

|-----|-----|----|-----|-----|-----|----|

| 8   | 3   | 5  | 5   | 3   | 3   | 5  |

## FORMAT

| ext    | format                                                           | meaning                                          |

|--------|------------------------------------------------------------------|--------------------------------------------------|

| 0      | ra := deposit rb [sar, len]<br>ra := deposit rb [sar, flr]       | dynamic deposit, fixed length<br>dynamic deposit |

| 2      | ra := ra deposit rb [sar, len]<br>ra := ra deposit rb [sar, flr] | dynamic merge, fixed length<br>dynamic merge     |

| 4<br>5 | ra := extract rb [sar, len]<br>ra := extract rb [sar, flr]       | dynamic extract, fixed length<br>dynamic extract |

## DESCRIPTION

These instructions perform Deposit, Deposit and Merge, Extract, and Deposit Immediate and Merge instructions with the shift amount determined by the contents of the *sar* register and the field length controlled either by the *flr* register of the *psr* or by the *len* field in the instruction. See the Extract and Deposit

instructions for details on the function of these operations.

## CONDITION

The condition generated is TRUE (1) if the result of the operation is non-ZERO, otherwise the condition generated is FALSE (0).

#### PRELIMINARY DATA October 1988

# Field Manipulation Instructions, continued

#### MERGE HALFWORD HIGH

| RCS | 011 | ra | imm16 |

|-----|-----|----|-------|

| 8   | 3   | 5  | 16    |

## FORMAT

ra := ra deposit imm16 [16, 16]

#### DESCRIPTION

The 16-bit immediate value is merged into the most significant 16 bits of register ra, and the result is placed in register ra.

## CONDITION

The condition generated is TRUE (1) if the result of the operation is non-ZERO and is FALSE (0) if the result is ZERO.

## **OPERATION**

| result  | := imm16[150]    reg(ra)[150]; | {merge onto ra after shifting by 16 bits} |

|---------|--------------------------------|-------------------------------------------|

| reg(ra) | := result;                     |                                           |

| COND    | $:=$ (result $\neq$ 0);        |                                           |

## Field Manipulation Instructions, continued

## BITWISE MERGE

| RCS | 111 | ra | rc | 1111 | 01 | rb |

|-----|-----|----|----|------|----|----|

| 8   | 3   | 5  | 5  | 4    | 2  | 5  |

#### FORMAT

rc := (ra and not al) or (rb and al)

## DESCRIPTION

This instruction performs a so called Bitwise Merge between the bits of the contents of register *rb* and register *ra*, controlled by the contents of register *al*. The result is placed in register *rc*.

Note that Multiply and Divide also use the al register. Therefore, a Bitwise Merge should not be executed while a Multiply or Divide operation is in progress.

#### OPERATION

result := (reg(ra) and not al) or (reg(rb) and al); reg(rc) := result; COND := (result  $\neq$  0);

## CONDITION

The condition generated is TRUE (1) if the result of the operation is non-ZERO, otherwise the condition generated is FALSE (0).

#### PRELIMINARY DATA October 1988

## Field Manipulation Instructions, continued

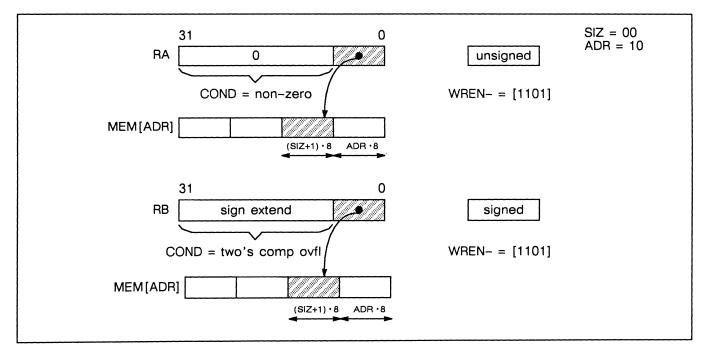

#### PERFECT EXCHANGE

## FORMAT

ra := p exchange rb

#### DESCRIPTION

This flexible bit manipulation command is used to swap fields or reverse the bit order on 2, 4, 8, 16, or 32-bit fields. One use of bit reversal is to calculate addresses in Fast Fourier Transforms. The Perfect Exchange operation is controlled by the 5-bit p field in the instruction.

This instruction performs a perfect exchange among the bits of the contents of register *rb*. The result is placed in register *ra*. Each bit, p[i], of the p field controls the exchange of pair-wise adjacent fields of size  $2^i$  bits. For example, when p[0] is set, each even-odd pair of bits is exchanged, and when p[4] is set, the upper halfword is exchanged with the lower halfword. This general capability provides several important special cases. For example, setting p[4..0] to 11111 causes all bits in a word to be placed in reverse order (radix-2 bit reverse), and setting p[4..0] to 11110 causes all pairs of bits to be reversed (radix-4 bit reverse). Setting p[4..0] to 11000 will reverse the order of bytes in a word.

## CONDITION

The condition generated is TRUE (1) if the result of the operation is non-ZERO, otherwise the condition generated is FALSE (0).

| 310                                      | p=11111: Reverse all bits in word      |

|------------------------------------------|----------------------------------------|

| Original first second third fourth       | first second third fourth              |

| p=11000: Reverse Byte Order              | p=10000: Reverse halfword order        |

| fourth third second first                | third fourth first second              |

| p=00111: Reverse bits within byte fields | p=01111: Reverse bits within halfwords |

| fourth third second first                | third fourth first second              |

Figure 13. Examples of perfect exchange

# Field Manipulation Instructions, continued

**OPERATION**

```

t := reg(rb);

if p[4] then

t := t[15..0] || t[31..16];

endif;

if p[3] then

for i := 0 to 16 by 16 do

t[i+15..i] := t[i+7..i] || t[i+15..i+8];

enddo:

endif;

if p[2] then

for i := 0 to 24 by 8 do

t[i+7..i] := t[i+3..i] || t[i+7..i+4];

enddo;

endif;

if p[1] then

for i := 0 to 28 by 4 do

t[i+3..i] := t[i+1..i] || t[i+3..i+2];

enddo;

endif;

if p[0] then

for i := 0 to 30 by 2 do

t[i+1..i] := t[i] || t[i+1];

enddo;

endif;

reg(ra)

:= t;

COND

:= (t \neq 0);

```

PRELIMINARY DATA October 1988

# Address Generation Instructions

ſ

LOAD/STORE ADDRESS WITH SIGNED DISPLACEMENT

| RCS                                                  | 110                 | ra                      | imm16                                                                                                                          |                                                                                                                                         |

|------------------------------------------------------|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 8                                                    | 3                   | 5                       | 16                                                                                                                             |                                                                                                                                         |

| FORMAT                                               |                     |                         |                                                                                                                                |                                                                                                                                         |

| adr := ra + imm                                      | 16                  |                         |                                                                                                                                |                                                                                                                                         |

|                                                      |                     |                         |                                                                                                                                |                                                                                                                                         |

| DESCRIPTION                                          |                     |                         |                                                                                                                                | CONDITION                                                                                                                               |

| to the unsigned b passed out the A                   | ase addr<br>D Bus a | ess in reg<br>nd placed | extended and added<br>ister <i>ra</i> . The result is<br>d in the <i>adr</i> register.<br>the <i>c</i> bit of the <i>psr</i> . | The condition generated is TRUE $(1)$ if an unsigned 32-bit overflow is encountered, otherwise the condition generated is FALSE $(0)$ . |

| OPERATION                                            |                     |                         |                                                                                                                                |                                                                                                                                         |

| result := reg(ra)<br>adr := result;<br>AD := result; | + (17 c             | dup imm <sup>1</sup>    | 16[15])    imm16[14                                                                                                            | 0]; {add the sign-extended displacement}<br>{internal address register}<br>{external address bus}                                       |

```

if imm16[15] = 0 then

COND :=usovf;

else

COND := not (usovf);

endif;

```

## Address Generation Instructions, continued

#### LOAD/STORE ADDRESS OR ADD WITH INDEX/SIGNED DISPLACEMENT

| RCS | 111 | ra | rc | 1 | ext | ixs | rb/imm5 |

|-----|-----|----|----|---|-----|-----|---------|

| 8   | 3   | 5  | 5  | 1 | 3   | 2   | 5       |

#### FORMAT

| instruction                                                                                                          | ext | meaning                                       |

|----------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------|

| adr := ra, rc := ra + (rb << ixs)                                                                                    | 000 | load/store indexed, modify after              |

| adr := ra, rc := ra + (imm5 < <ixs)< td=""><td>001</td><td>load/store signed displacement, modify after</td></ixs)<> | 001 | load/store signed displacement, modify after  |

| adr := rc := ra + (rb << ixs)                                                                                        | 010 | load/store indexed, modify before             |

| adr := rc := ra + (imm5 < <ixs)< td=""><td>011</td><td>load/store signed displacement, modify before</td></ixs)<>    | 011 | load/store signed displacement, modify before |

| adr := ra + (rb << ixs)                                                                                              | 100 | load/store indexed, no modify                 |

| adr := ra + (imm5 < <ixs)< td=""><td>101</td><td>load/store signed displacement, no modify</td></ixs)<>              | 101 | load/store signed displacement, no modify     |

| rc := ra + (rb << ixs)                                                                                               | 110 | add indexed                                   |

#### DESCRIPTION

Address generation instructions take a left-shifted (0-3) bits), signed value from an immediate field or register and add it to a base register, optionally writing the result to another register. The address driven onto the AD Bus may be the result of the addition or the contents of the base register *before* the addition. This corresponds to pre-increment and post-increment indexing. Again, the shifting facility simplifies the generation of halfword, word, and doubleword array addresses in a byte-addressable environment.

```

{Post-modify:}

adr := ra, rc := ra + imm5

adr := ra, rc := ra + rb

{Pre-modify:}

adr := (rc := ra + imm5)

adr := (rc := ra + rb)

{No modify:}

adr := ra + imm5

adr := ra + rb

```

The contents of register rb (index) or a 5-bit signed displacement is shifted left the number of bits specified by *ixs* (a value of 0 causes no shift), and added to the unsigned base address in register ra. If modification is requested, the result is stored in register rc. The calculated address is the result of the add operation unless modify after is requested, in which case it is the contents of register ra. The calculated address is placed in the *adr* register and driven on the AD Bus. These instructions do not affect the *c* bit of the *psr*.

28

## PRELIMINARY DATA October 1988

# Address Generation Instructions, continued

## CONDITION

The condition generated is TRUE (1) if a two's complement overflow is encountered when shifting or an unsigned 32-bit overflow is encountered when adding; otherwise the condition generated is FALSE (0). For the Add With Shift instruction (ext 6), the addition operation tests for two's complement addition overflow.

## **OPERATION**

| if $ext[0] = 0$ then                                |                                                     |

|-----------------------------------------------------|-----------------------------------------------------|

| temp := reg(rb);                                    |                                                     |

| else                                                |                                                     |

| temp := (28 dup imm5[4])    imm5[30];               | {sign-extend the immediate field}                   |

| endif;                                              |                                                     |

| result := reg(ra) + (temp[31-ixs0]    (ixs dup 0)); | {shift the displacement by <i>ixs</i> bits and add} |

| case ext[21] of                                     |                                                     |

|                                                     |                                                     |

| 00b: adr := AD := reg(ra); reg(rc) := result;       | {do the operation}                                  |

| 01b: adr := AD := reg(rc) := result;                |                                                     |

| 10b: adr := AD := result;                           |                                                     |

| 11b: reg(rc) := result;                             |                                                     |

| endcase;                                            |                                                     |

| if ext [20] = 110 then                              |                                                     |

| COND := tcovf;                                      |                                                     |

| else                                                |                                                     |

| COND := (reg(rb) [3132-ixs] $\neq$ (ixs dup reg(rb  | )[31-ixs])) or usovf;                               |

| endif;                                              |                                                     |

|                                                     |                                                     |

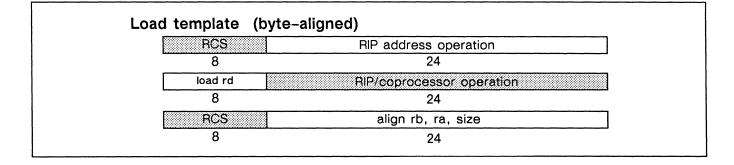

## Load/Store and Alignment Instructions

Data transfers to and from memory take two operations: address generation and data transfer.

To load data, the RIP first executes a Load/Store Address instruction, which calculates an address and drives it onto the AD Bus. The RIP executes a Load Data instruction during a subsequent cycle, which takes the contents of the D Bus and puts it into a register.

Another instruction can be performed at the same time as the Load Data instruction, since Load Data uses only the RCS field of the instruction word. For instance, you can put an address generation instruction in the field, reducing the time for consecutive loads to one cycle per word.

Storing data is similar. Addresses are again generated with a Load/Store Address command, and data is stored with the Store Data command. The Store Data command takes up the RCS field, and the instruction in the RIP field generates the data to be stored. For instance, if the instruction was rc := ra+rb, the sum of ra+rb would be stored in rc and stored into memory.

The Byte Align and Store command can be used to store bytes, halfwords, and words. Because this is a separate instruction, it requires an extra cycle.

## PRELIMINARY DATA October 1988

|                                                         |         |          |                     | October 1988                                                                                                           |

|---------------------------------------------------------|---------|----------|---------------------|------------------------------------------------------------------------------------------------------------------------|

| Load/Store ar                                           | nd Alig | nment Ir | nstructions, contin | ued                                                                                                                    |

| LOAD HALFW                                              | ORD IM  | IMEDIAT  | Έ                   |                                                                                                                        |

| RCS                                                     | 010     | ra       | imm16               |                                                                                                                        |

| 8                                                       | 3       | 5        | 16                  |                                                                                                                        |

| FORMAT                                                  |         |          |                     |                                                                                                                        |

| ra := imm16                                             |         |          |                     |                                                                                                                        |

| DESCRIPTION                                             |         |          |                     | CONDITION                                                                                                              |

| The 16-bit imr<br>placed into regis                     |         | value is | sign-extended and   | The condition generated is TRUE (1) if the result of the operation is non-ZERO and is FALSE (0) if the result is ZERO. |

| OPERATION                                               |         |          |                     |                                                                                                                        |

| result := (17 c<br>reg(ra) := result<br>COND := (result | t;      |          | imm16[140];         | {sign-extend to 32 bits}                                                                                               |

ſ

ı

ι

## Load/Store and Alignment Instructions, continued

## LOAD DATA

## FORMAT

rd := mem[adr]

#### DESCRIPTION

This instruction specifies that data is to be loaded from the D Bus into register rd in the register file. Because this instruction uses the RCS field of the instruction word, it can be performed simultaneously with other RIP operations. The loaded data is not available for use until the next instruction. Care must be taken to avoid writing of the data into the same register as specified by the operation in the remainder of the instruction word. If the other RIP instruction specifies that register *rd* is to be modified, then the contents of *rd* becomes undefined at the end of this instruction.

#### CONDITION

This instruction does not generate any condition. However, a condition may be generated by any instruction that is combined with this instruction; the condition so generated will not be affected by this instruction.

#### **OPERATION**

reg(rd) := D;

#### **PROGRAMMING EXAMPLES**

| adr := ra+imm;<br>rd := mem[adr]   rc := rd op rb;                                     | {any RIP address instruction}<br>{here the old value of rd is used in the calculation} |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| adr := ra+imm;<br>rd := mem[adr]   <other instruction="">;<br/>rc := rd op rb;</other> | {here the new, loaded value of rd is used in the calculation}                          |

| adr := ra + imm;<br>rd := mem[adr]   rd := rc <i>op</i> rb;                            | {value of rd becomes undefined, not allowed}                                           |

## PRELIMINARY DATA October 1988

## Load/Store and Alignment Instructions, continued

## STORE DATA

00001001

RIP operation

8

24

#### FORMAT

mem[adr] := result; {RIP operation}

#### DESCRIPTION

This instruction specifies that the result of an RIP operation is to be stored to the previously addressed memory location. The Store Data instruction is specified in the uppermost 8 bits of the instruction. The lower 24 bits are used to specify any RIP operation that produces a result.

The Store Data instruction places the result of the current RIP operation onto the D Bus, and asserts all four WREN- bits.

#### OPERATION

D := result;

PROGRAMMING EXAMPLES

adr := ra+imm; mem[adr]:= rc := ra op rb; {any RIP address instruction} {write result to rc and memory}

## CONDITION

The Store Data does not generate any condition. However, a condition may be generated by the RIP operation that is combined with this instruction; the condition thus generated will not be affected by this instruction.

## Load/Store and Alignment Instructions, continued

## BYTE ALIGN FOR LOAD DATA

| RCS | 111 | ra | x | 0 | s | siz | 1111 | 00 | rb |

|-----|-----|----|---|---|---|-----|------|----|----|

| 8   | 3   | 5  | 1 | 1 | 1 | 2   | 4    | 2  | 5  |

## FORMAT

ra := rb align [unsigned siz] ra := rb align [signed siz]

| siz | Size of operand  |  |  |  |

|-----|------------------|--|--|--|

| 00  | byte             |  |  |  |

| 01  | halfword         |  |  |  |

| 10  | tri–byte<br>word |  |  |  |

| 11  | word             |  |  |  |

## DESCRIPTION

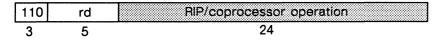

This instruction extracts a byte, halfword, tri-byte, or a word from a previously loaded word in the *rb* register. The instruction uses the byte address in the *adr* register together with the two-bit *siz* field from the instruction to extract the correct byte(s). The extracted value is zero-extended or sign-extended to a full 32-bit value. Zero- or sign-extension is controlled by the *s* bit in the instruction. The resulting 32-bit value is stored in the destination register *ra*.

The typical sequence of instructions to load a byte requires two instructions and three cycles. (The extra cycle is used to load the word containing the desired byte. This does not require the ALU and it could perform any other operation on this cycle.)

This instruction is defined to be register-to-register only; condition and AD Bus outputs are undefined.

### CONDITION

This instruction does not generate a condition output.

#### PRELIMINARY DATA October 1988

#### Load/Store and Alignment Instructions, continued

**OPERATION**

$\bigcirc$

ź

| a         | := adr[10] • 8;                             |                                 |

|-----------|---------------------------------------------|---------------------------------|

| I         | := (siz + adr[10]) • 8 + 7;                 |                                 |

| size      | := siz • 8 + 7;                             |                                 |

| case s of |                                             |                                 |

| 0b: res   | := (31-size dup 0)    reg(rb)[Ia];          |                                 |

| 1b: res   | := (31-size dup reg(rb)[I])    reg(rb)[Ia]; |                                 |

| endcase;  |                                             |                                 |

| reg(ra)   | := res;                                     |                                 |

| COND      | := undefined;                               | $\{NOTE: siz + adr[10] \le 3\}$ |

| result    | := undefined;                               |                                 |

|           |                                             |                                 |

Figure 14. Byte align for load data instruction

#### Load/Store and Alignment Instructions, continued

BYTE ALIGN AND STORE DATA

|                                        |                                      |                        | <del></del> |     | · · · · · |             |             |                                                                    |

|----------------------------------------|--------------------------------------|------------------------|-------------|-----|-----------|-------------|-------------|--------------------------------------------------------------------|

| RCS                                    | 111                                  | ra                     | е           | 1 s | siz       | 1111        | 00          | rb                                                                 |

| 8                                      | 3                                    | 5                      | 1           | 1 1 | 2         | 4           | 2           | 5                                                                  |

| FORMAT                                 |                                      |                        |             |     |           |             |             |                                                                    |

| instruction                            |                                      |                        |             |     |           | е           | S           | meaning                                                            |

| mem[adr] :<br>mem[adr] :<br>mem[adr] : | = rb align [                         | unsigned<br>signed siz | siz]        |     |           | 0<br>0<br>1 | 0<br>1<br>x | align for store unsigned<br>align for store signed<br>no alignment |

| siz                                    | Size of op                           | perand                 |             |     |           |             |             |                                                                    |

| 00<br>01<br>10<br>11                   | byte<br>halfword<br>tri-byte<br>word |                        |             |     |           |             |             |                                                                    |

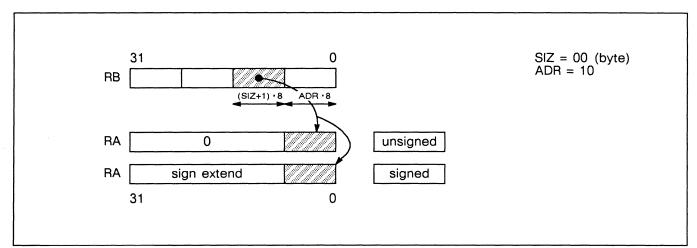

#### DESCRIPTION

These operations transfer from the register file to the external (D+) data bus, while aligning and truncating or sign extending the value to allow byte, halfword, and tri-byte addressing into word-wide memory. The correct alignment is specified by the *adr* register, the data size by the *siz* field, and sign extension by the *s* field. To implement this instruction properly the external memory must be capable of writing individual bytes as controlled by the WREN- bus.

The Byte Align and Store instruction is used to store bytes, halfwords, tri-bytes, and words in a byte addressable environment. The instruction performs two operations: data alignment and byte-write control.

The instruction takes as input a register number, the *adr* register, the data size (a constant in the instruction), and other miscellaneous controls in the instruction. The register number designates the data to be stored (the rightmost byte or halfword.) The *adr* regis-

ter indicates the particular byte alignment to use; this register is automatically set by any address generation instruction. The data size is used to indicate whether a byte or halfword is being stored.

The input data to be stored is shifted the correct number of places to align it to the correct byte as specified by the low order two bits of the *adr* register. The correct byte write controls are driven so that the external memory subsystem will only write the correct bytes. The condition pin is also driven to indicate if the signed or unsigned data value would not fit into the destination format (overflow).

#### CONDITION

The generated is TRUE (1) if the operation truncates significant bits from the operand, otherwise the condition generated is FALSE (0).

PRELIMINARY DATA October 1988

#### Load/Store and Alignment Instructions, continued

OPERATION

```

а

:= adr[1..0] • 8;

:= (siz + adr[1..0]) \cdot 8 + 7;

1

size := siz • 8 + 7;

if e = 0 then

case s of

0b:

result := (31-I dup 0) || reg(rb) [size..0] || (a dup 0);

D

:= result:

COND := (reg(rb) [31..size+1] = 0);

result := (31-I dup 0) || reg(rb) [size..0] || (a dup 0);

1b:

D

:= result;

COND := (reg(rb)[31..size+1] = (31-size dup reg(rb)[size]));

endcase;

else

result := reg (ra);

D

:= result;

COND := undefined;

endif;

for i := 0 to 3 do

WREN-[i] := FALSE;

endfor;

for i := 0 to siz do

WREN-[adr [1..0] + i] := TRUE; {NOTE: siz + adr[1..0] \le 3}

endfor;

```

Figure 15. Byte align and store instruction

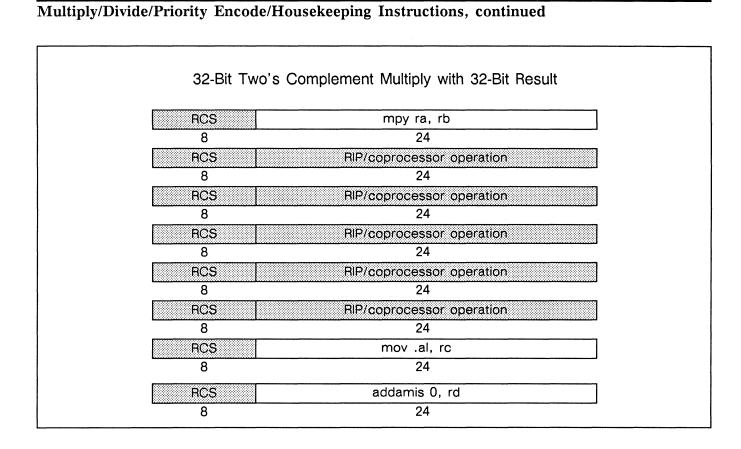

#### Multiply/Divide/Priority Encode/Housekeeping Instructions

#### MULTIPLY/DIVIDE/PRIORITY ENCODE/HOUSEKEEPING INSTRUCTIONS

| RCS | 111 | ra | ext | 1111 | 11 | rb/imm5 |

|-----|-----|----|-----|------|----|---------|

| 8   | 3   | 5  | 5   | 4    | 2  | 5       |

#### FORMAT

| instruction                                                                                                                                              | ext                                                                  | meaning                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| am, al := $ra \cdot rb$<br>al, am := $am  ra \div rb$<br>am := $rb$ , al := $ra$<br>ra := $alra$ := $am + rbra$ := $am + imm5 + al[31]ra$ := $am + imm5$ | 00000<br>00001<br>00010<br>00011<br>00100<br>00101<br>00110<br>00111 | start 32-bit two's complement multiply<br>start 64-bit/32-bit unsigned integer divide<br>load/reload am and al<br>unload quotient/ls product<br>unload remainder/ms product plus register<br>unload remainder/ms product plus immediate plus sign<br>unload remainder/ms product plus immediate |

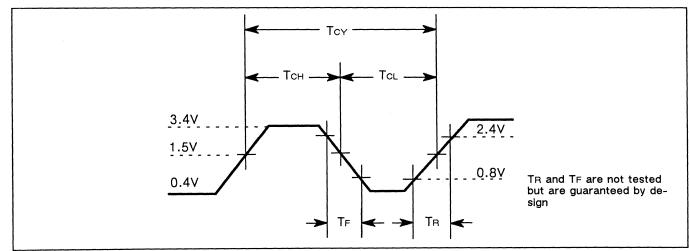

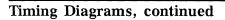

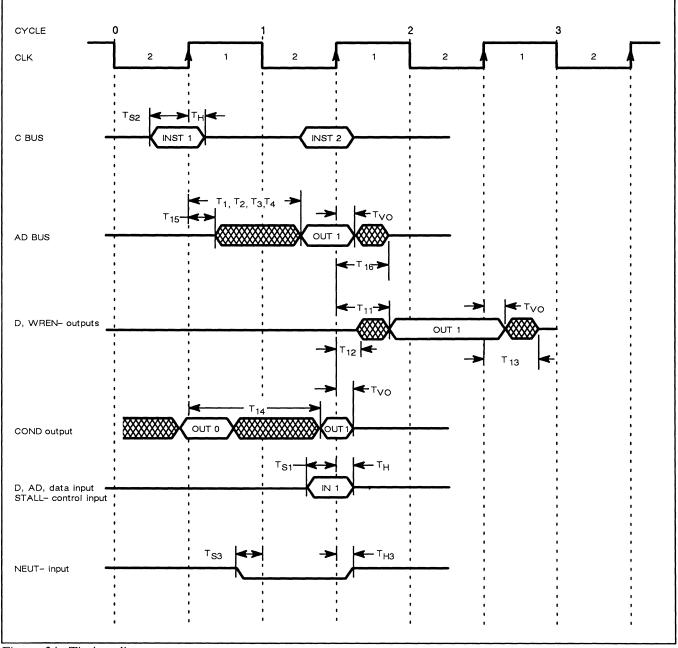

| ra := priority encode rb<br>-<br>fir := rb<br>sar := rb<br>-<br>-<br>-<br>-                                                                              | 01000<br>01001<br>01010<br>01011<br>01100<br>01101<br>01110<br>01111 | priority encode<br>–<br>load field length register<br>load shift amount register<br>–<br>–<br>–<br>–                                                                                                                                                                                            |