# GATE ARRAY DESIGN MANUAL

VGC SERIES

# VGC Series CMOS Gate Array Design Manual

Version 4.0

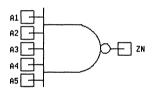

©1985 VLSI Technology, Inc. All rights reserved.

This document and the software that it describes are the proprietary and confidential property of VLSI Technology Inc ("VTI") and Xidak Inc, for distribution and use only under license from VTI and may not be copied without VTI's written consent.

VTI reserves the right to make changes in the contents of this document without notice. VTI assumes no responsibility for any errors that appear in this document.

Mainsail is a trademark of Xidak, Inc. Bitpad is a trademark of Summagraphics, Inc. VAX and Vax/VMS are trademarks of Digital Equipment Corporation. Unix is a trademark of AT&T Bell Laboratories. EMBOS is a trademark of Elxsi, Inc. ROS is a trademark of Ridge Computers. Aegis is a trademark of Apollo Computer, Inc.

Portions of this manual reprinted with permission of Fairchild, a Schlumberger company.

# CONTENTS

| 1   | INTRODUCTION |                                                | 1  |

|-----|--------------|------------------------------------------------|----|

|     |              | GENERAL INFORMATION                            | 1  |

|     |              | Terminology                                    | 2  |

|     |              | The VGC Series                                 | 2  |

|     |              | Additional Publications                        | 2  |

|     |              | FEATURES                                       | 4  |

|     |              | VTI'S ADVANCED CMOS<br>TECHNOLOGY              | 5  |

| · . |              | DESIGNING A GATE ARRAY OPTION                  | 7  |

|     |              | Objective Specification                        | 7  |

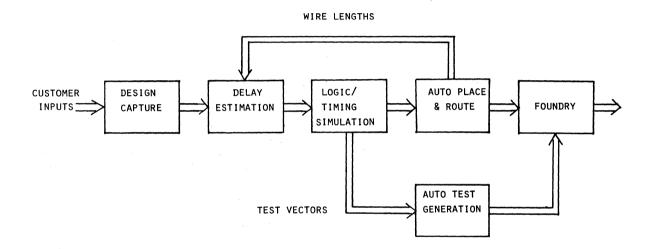

|     |              | Computer Aided Design With VTI's Design System | 7  |

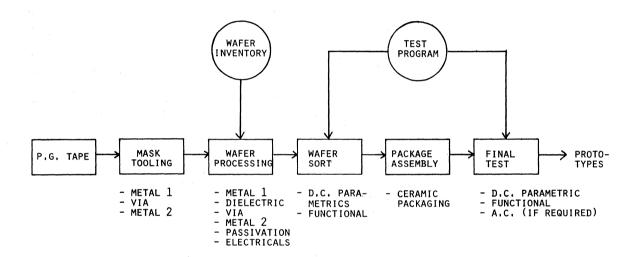

|     |              | Fabrication and Assembly                       | 10 |

|     |              | DESIGN SUPPORT                                 | 11 |

|     |              | Training                                       | 11 |

|     |              | Applications Assistance                        | 11 |

| ${f 2}$ | PHYSICAL DESC | CRIPTION                           | 13   |

|---------|---------------|------------------------------------|------|

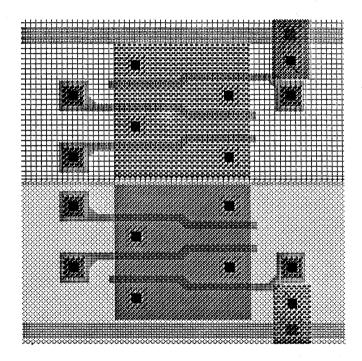

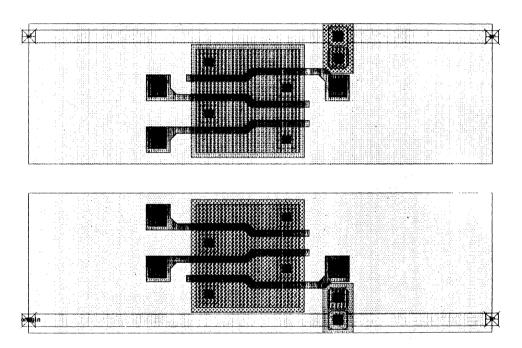

|         |               | ARRAY ARCHITECTURE                 | 13   |

|         |               | CELLS                              | 13   |

|         |               | Internal Cells                     | 14   |

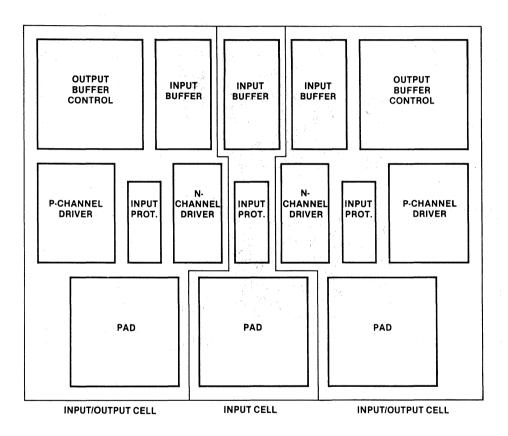

|         |               | I/O Cells                          | 14   |

|         |               | Input Cells                        | 14   |

|         |               | VOLTAGE AND GROUND BUSES           | 19   |

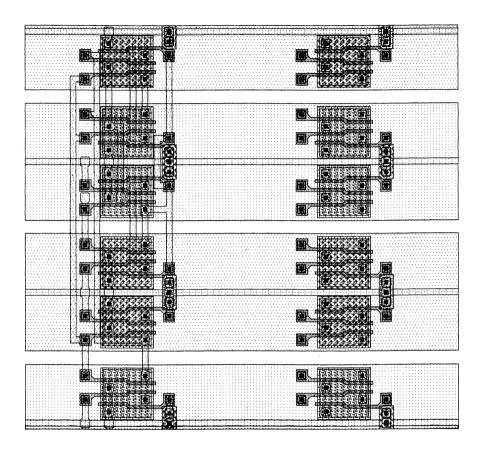

|         |               | SIGNAL ROUTING                     | 19   |

|         |               | First-layer Routing Channels       | 19   |

|         |               | Secondlayer Routing Channels       | 20   |

|         |               | PREDEFINED METALLIZATION           | 20   |

|         |               | Power and Ground Buses             | 20   |

|         |               | Internal Macros                    | 20   |

|         |               | I/O and Input Macros               | 21   |

|         |               | 4                                  |      |

| 3       | CIRCUIT TOPO  | LOGY AND OPERATIO                  | N 23 |

|         |               | INTRODUCTION                       | 23   |

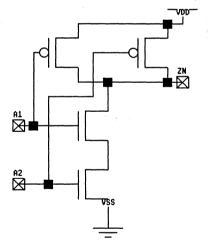

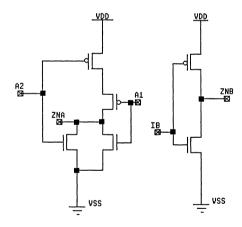

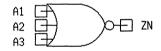

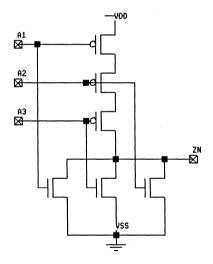

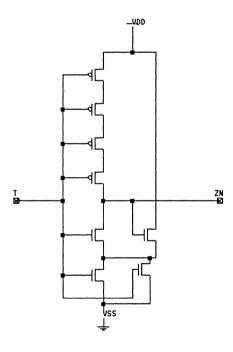

|         |               | CMOS CIRCUIT FUNDAMENTALS          | 23   |

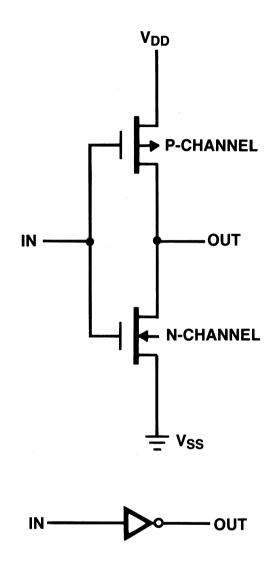

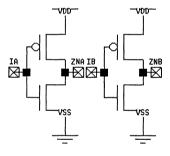

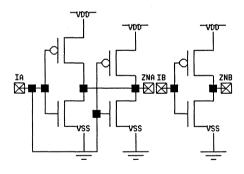

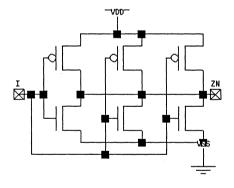

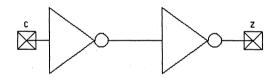

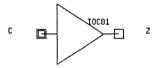

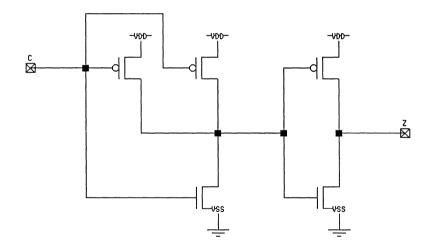

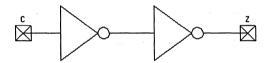

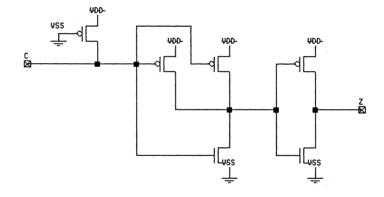

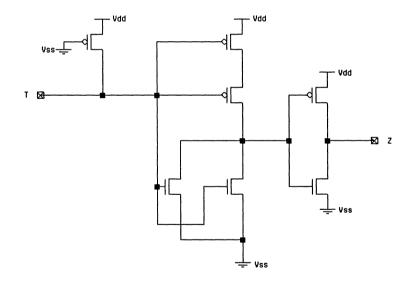

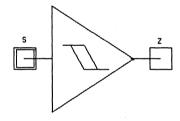

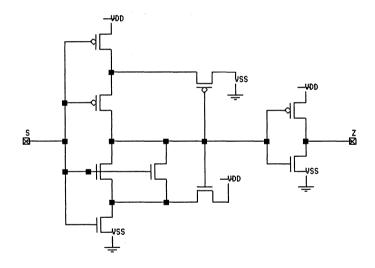

|         |               | Inverter                           | 24   |

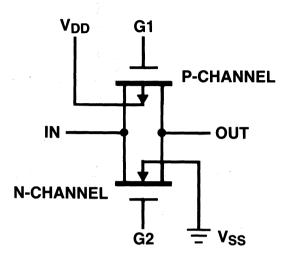

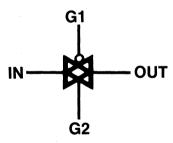

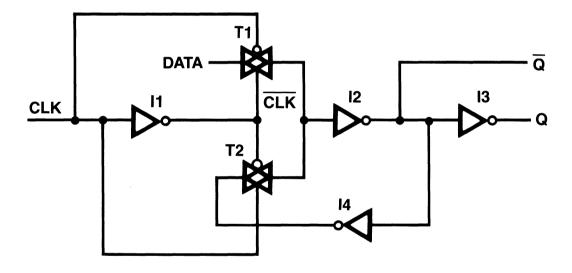

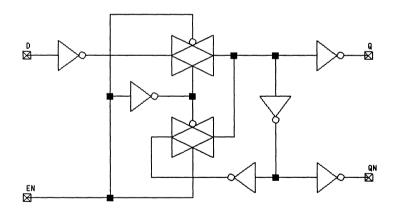

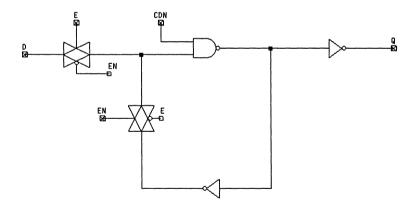

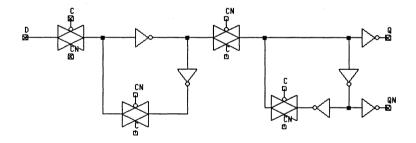

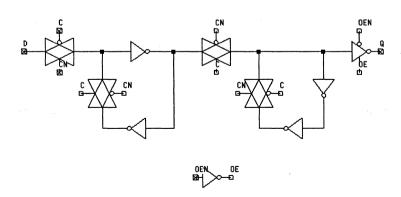

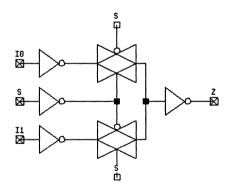

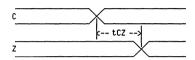

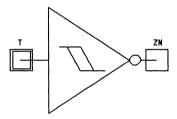

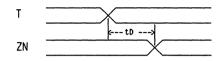

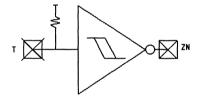

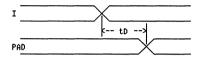

|         |               | Transmission Gate                  | 24   |

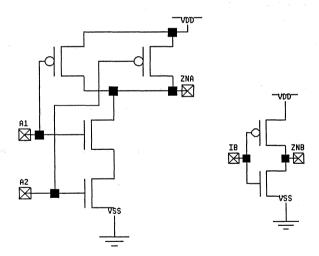

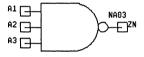

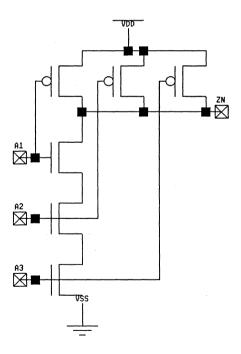

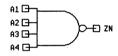

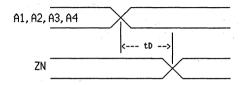

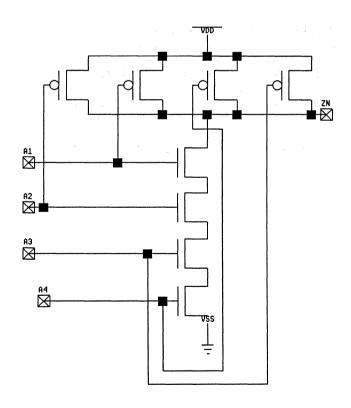

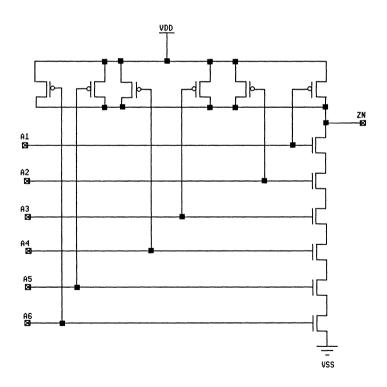

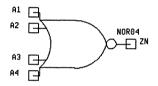

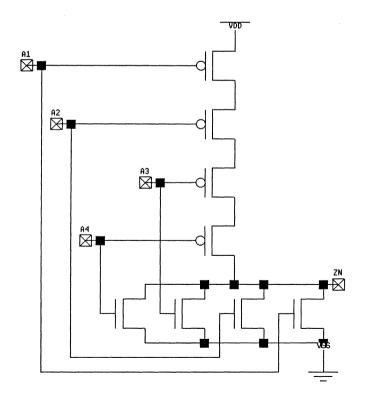

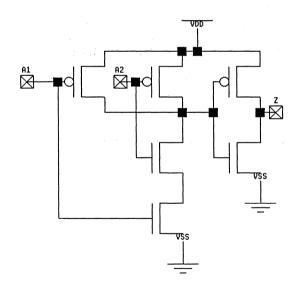

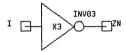

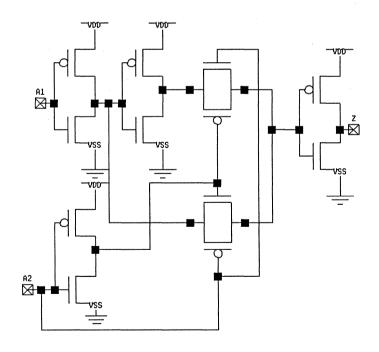

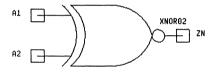

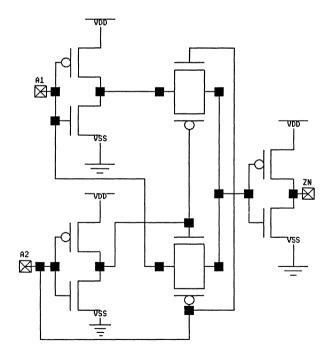

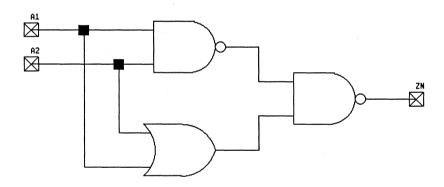

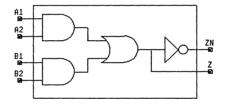

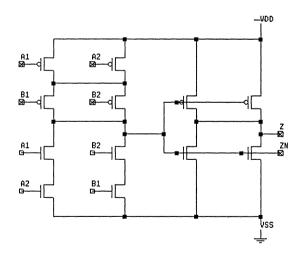

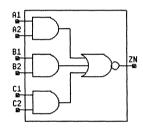

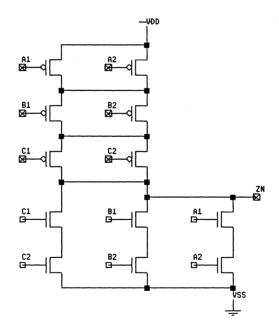

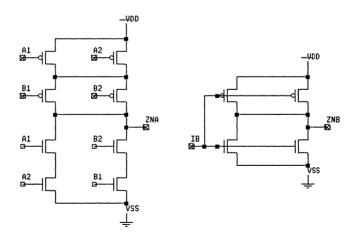

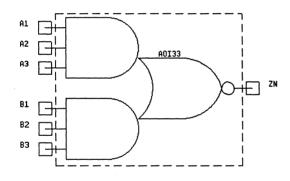

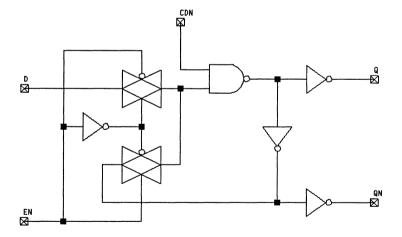

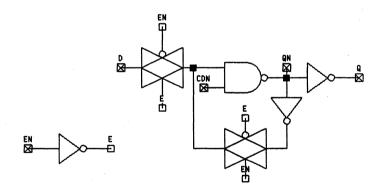

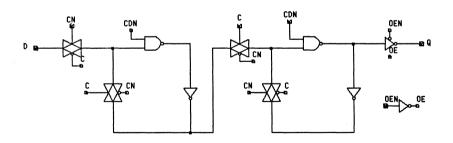

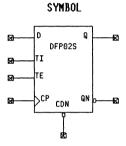

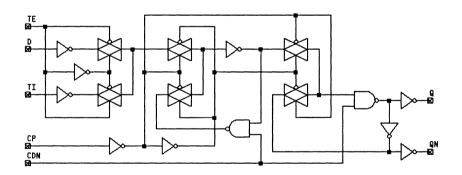

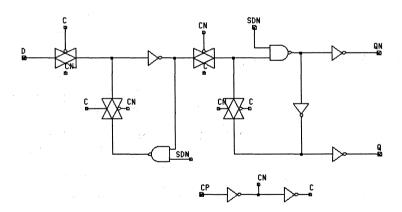

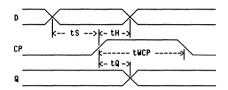

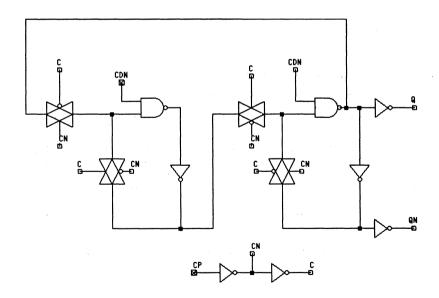

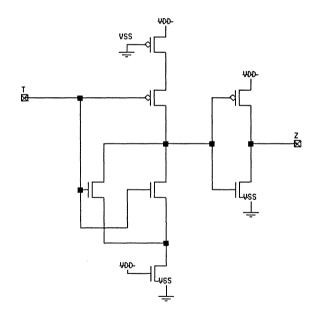

|         |               | INTERNAL CELLS AND MACROS          | 27   |

|         |               | Internal Cell Components           | 2    |

|         |               | InternalCell Macro Operation       | 2    |

|         | 14.           | Example InternalCell Macro Routing | 30   |

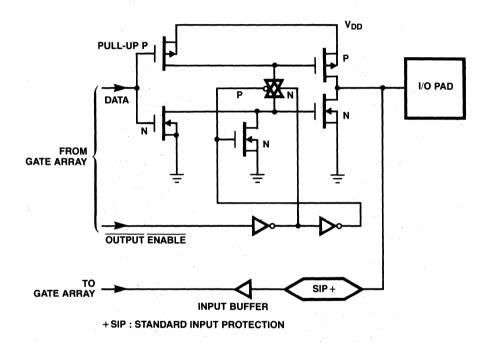

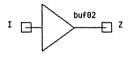

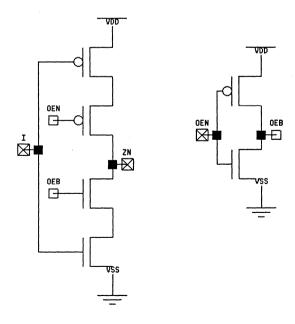

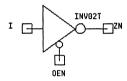

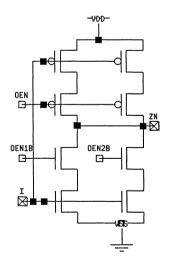

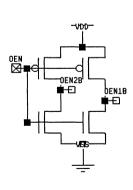

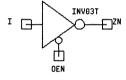

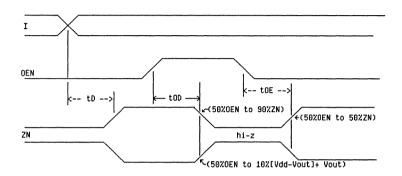

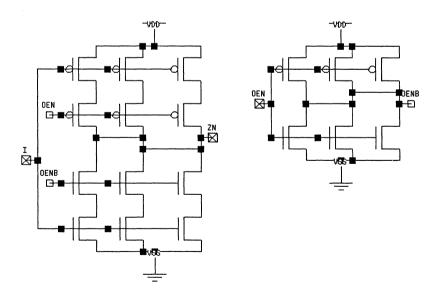

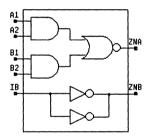

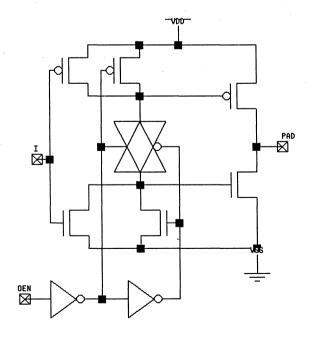

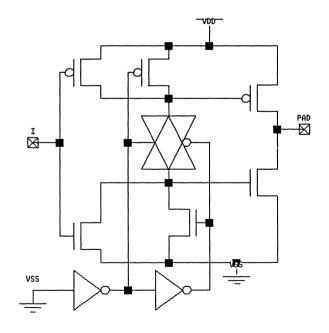

|         |               | I/O CELLS AND MACROS               | 30   |

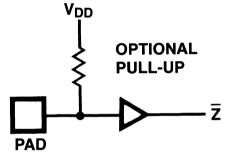

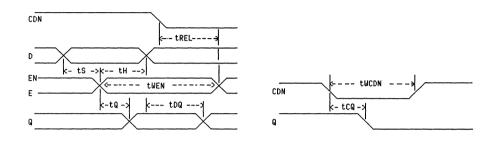

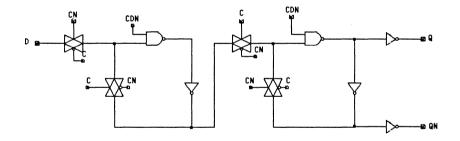

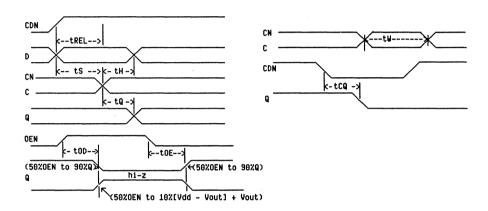

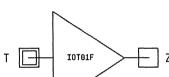

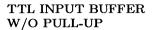

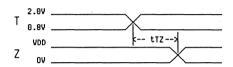

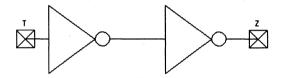

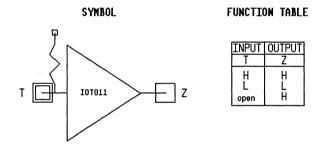

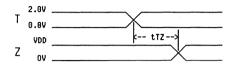

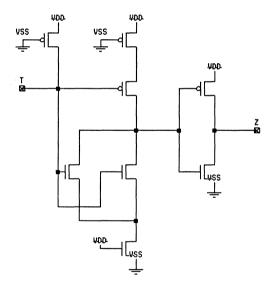

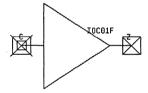

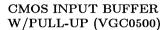

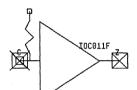

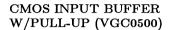

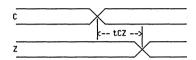

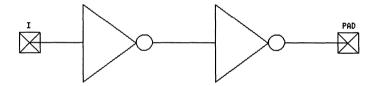

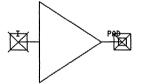

|         |               | Input Buffer Macros                | 30   |

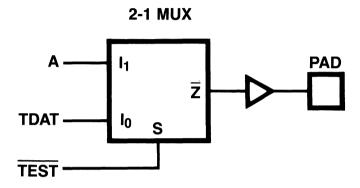

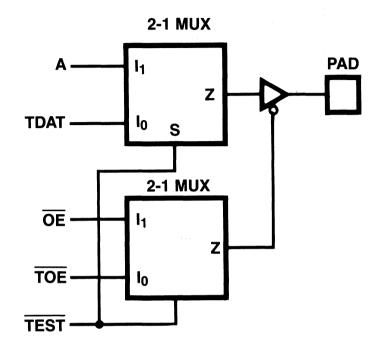

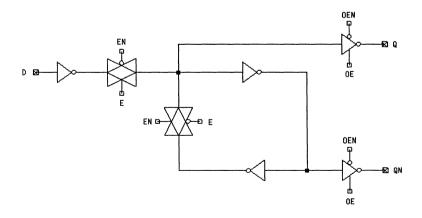

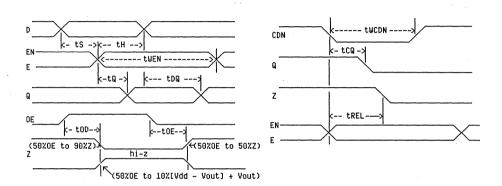

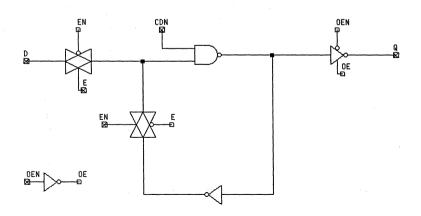

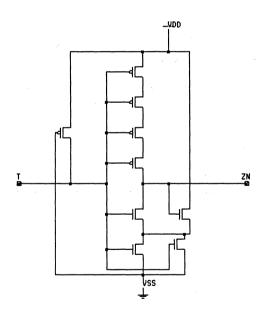

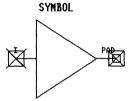

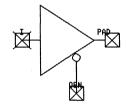

|         |               | Output Buffer Macros               | 3    |

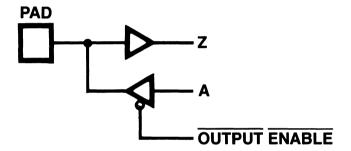

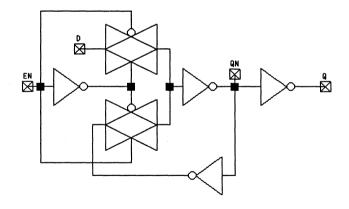

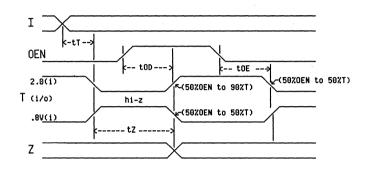

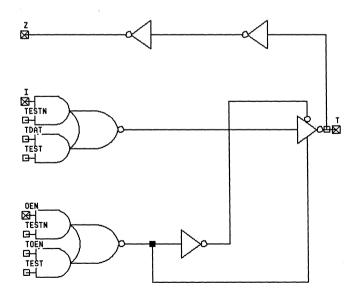

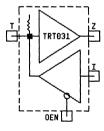

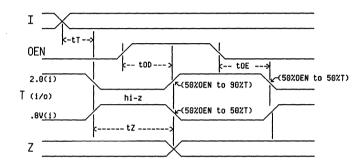

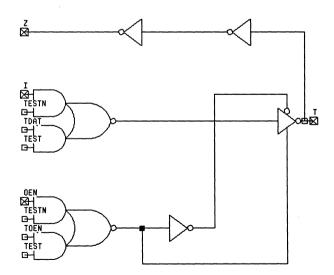

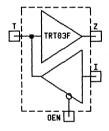

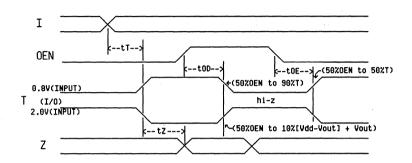

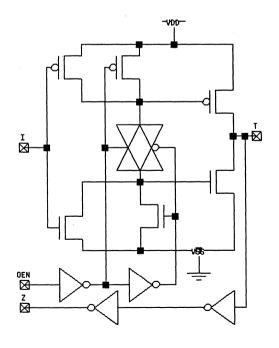

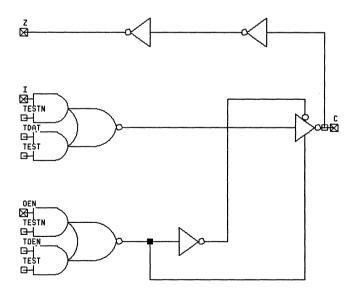

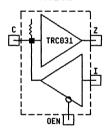

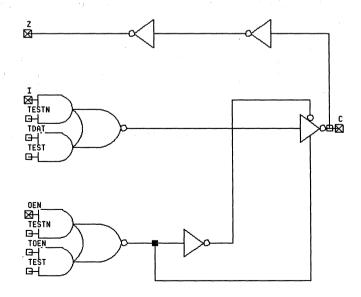

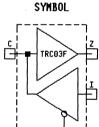

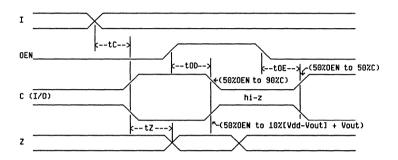

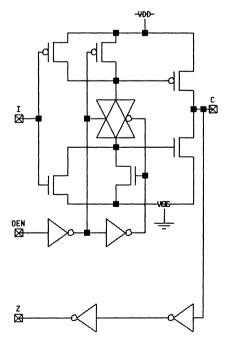

|         |               | Transceiver Macros                 | 3    |

|         |               | INPUT CELLS                        | 4    |

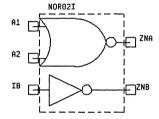

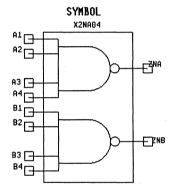

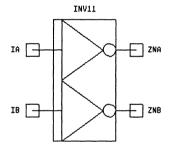

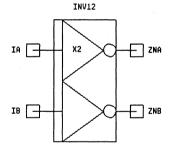

| 4 | MACRO LIBRARY | Y SUMMARY                             | <b>43</b> |

|---|---------------|---------------------------------------|-----------|

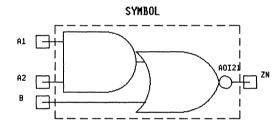

|   |               | INTRODUCTION                          | 43        |

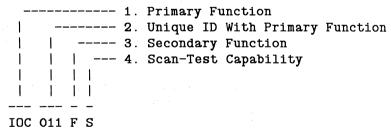

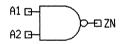

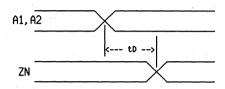

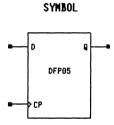

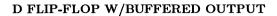

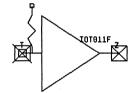

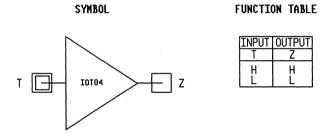

|   |               | LIBRARY FORMAT                        | 49        |

|   |               | First Page                            | 49        |

|   |               | Second And/or Third Page              | 50        |

|   |               | NAMING CONVENTIONS                    | 50        |

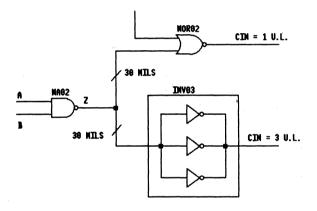

|   |               | UNIT LOADS                            | 52        |

|   |               | MACRO LIBRARY EXAMPLE                 | 53        |

| 5 | LOGIC DESIGN  |                                       | <b>57</b> |

| J | Logic besign  | INTRODUCTION                          | 57        |

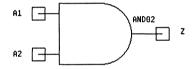

|   |               | PHYSICAL MACROS                       | 57<br>57  |

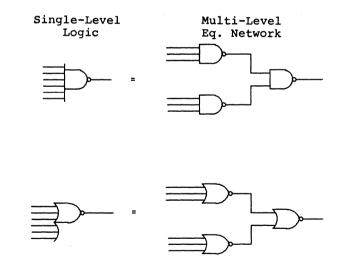

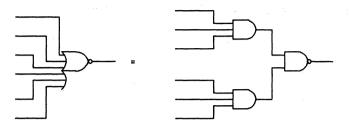

|   |               | Combining Existing Physical Macros to | 01        |

|   |               | Form a Logical Macro                  | 58        |

|   |               | Designing New Physical Macros         | 58        |

|   |               | LOGIC SCHEMATIC                       | 58        |

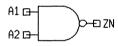

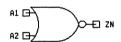

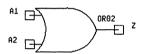

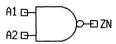

|   |               | Logic Symbols                         | 58        |

|   |               | Maximum Cell Utilization              | 59        |

|   |               | Pin-Out Limitations                   | 59        |

|   |               | LOGIC DESIGN RULES                    | 59        |

|   |               | AC Fan-out                            | 59        |

|   |               | Unused Inputs                         | 60        |

|   |               | Internal 3-state Buses                | 60        |

|   |               | DC Characteristics                    | 60        |

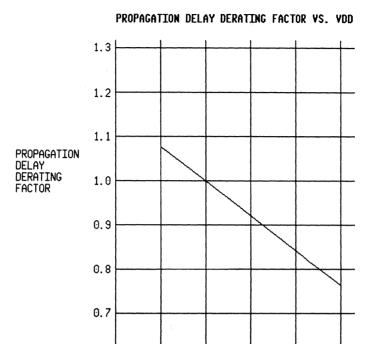

|   |               | PERFORMANCE                           | 63        |

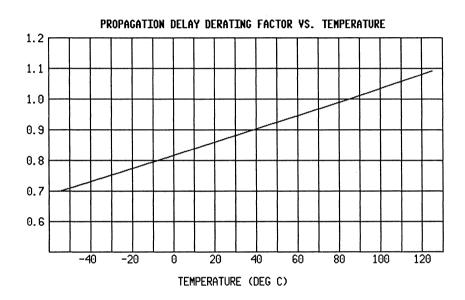

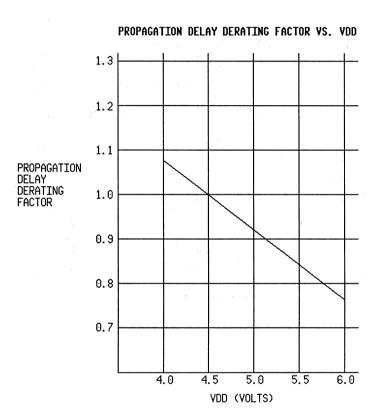

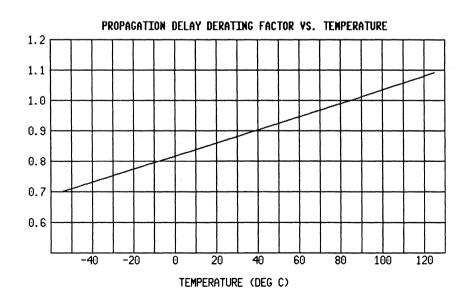

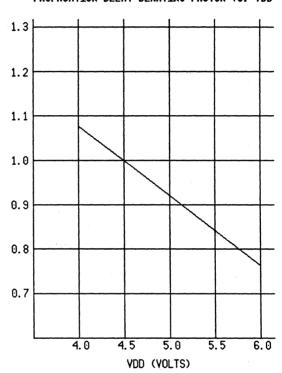

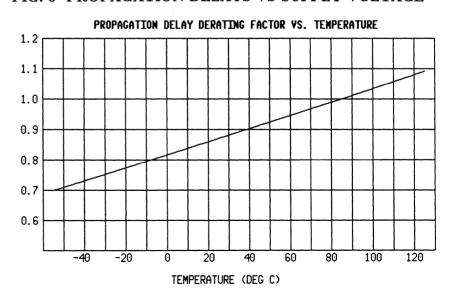

|   |               | Temperature Voltage & Process Effects | 63        |

|   |               | Estimation of PerformanceDegradation  | 64        |

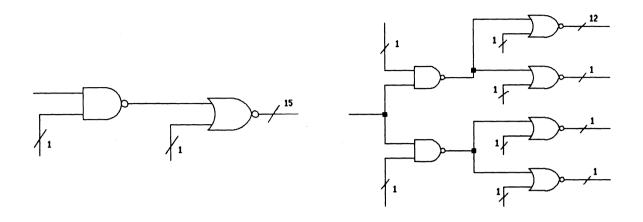

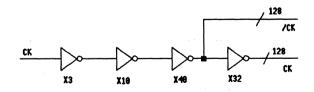

|   |               | Propagation Delay Calculations        | 68        |

|   |               | Sample Calculations                   | 70        |

| 6 | DESIGN PROCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DURE                                           | 73 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----|

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTRODUCTION                                   | 7  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SPECIFICATIONS                                 | 7  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Objective Specification                        | 7  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Final Specification                            | 7  |

|   | The first of the second of the | LOGIC DESIGN                                   | 7  |

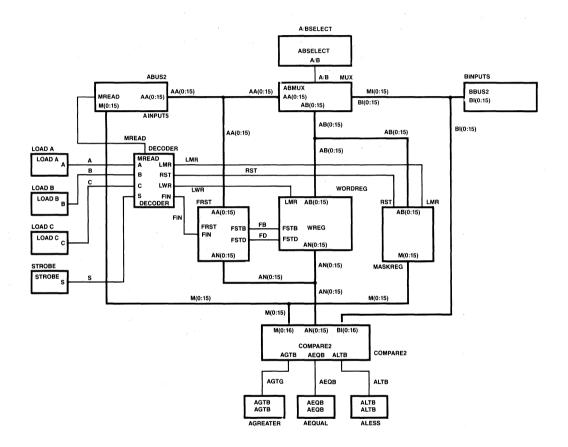

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FUNCTIONAL BLOCK DIAGRAM                       | 7  |

|   | 4 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Requirements                                   | 7  |

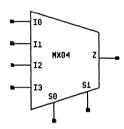

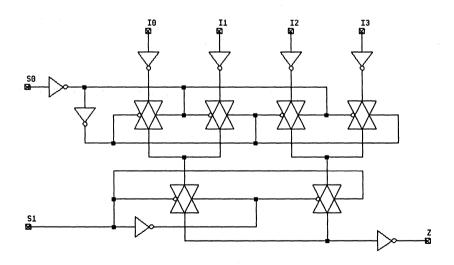

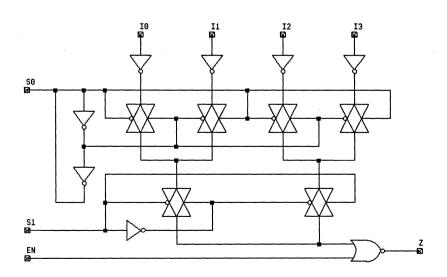

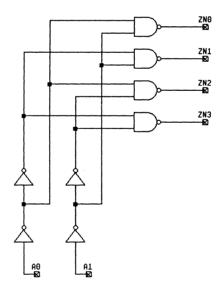

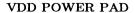

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | An Example Design                              | 75 |

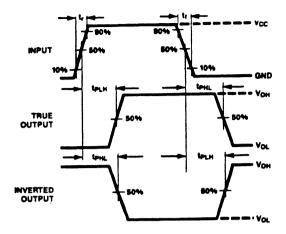

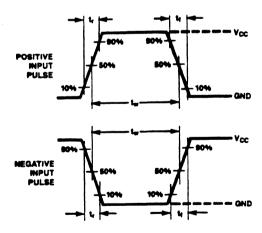

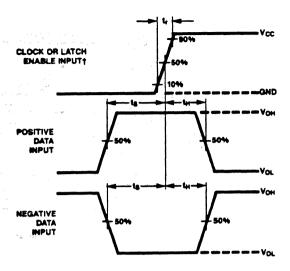

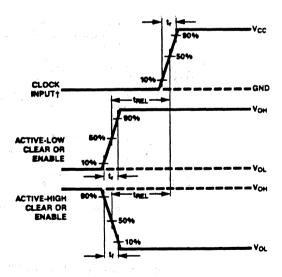

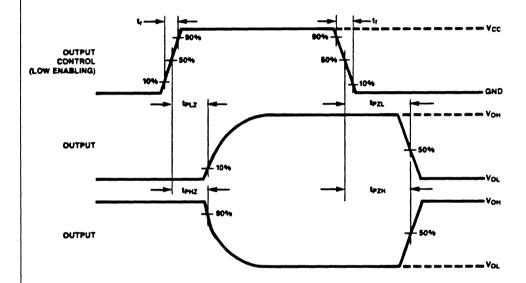

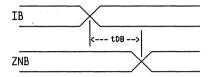

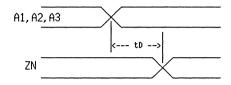

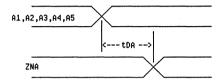

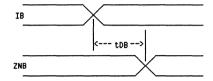

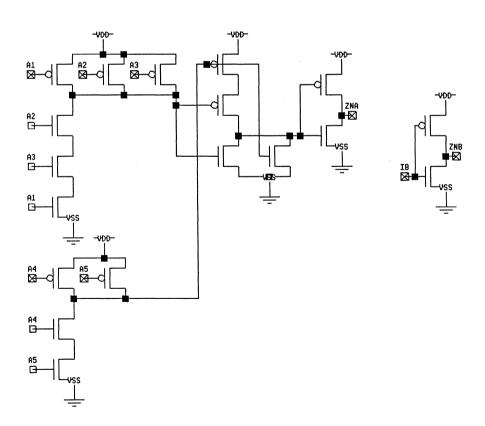

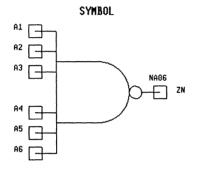

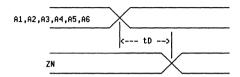

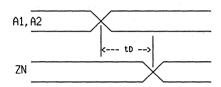

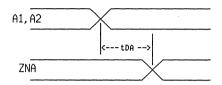

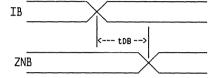

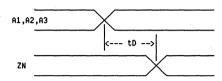

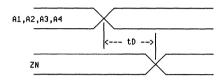

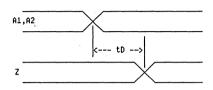

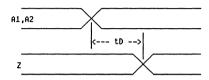

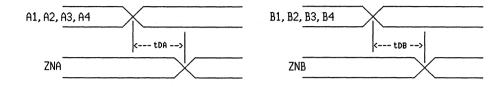

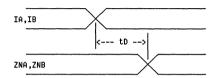

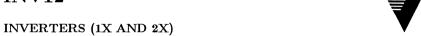

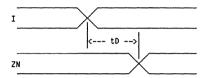

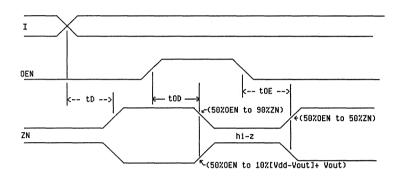

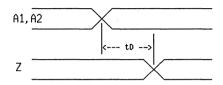

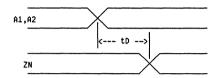

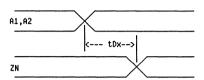

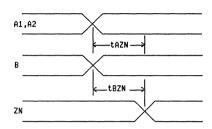

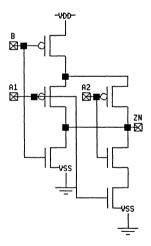

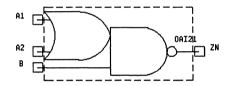

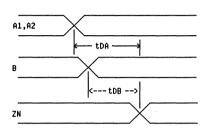

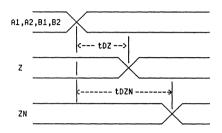

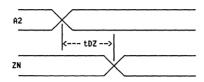

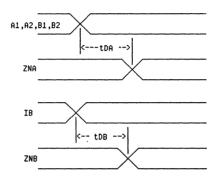

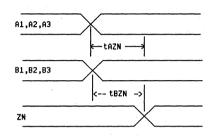

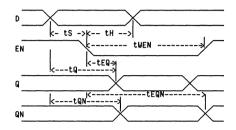

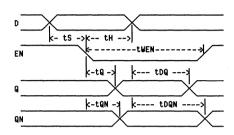

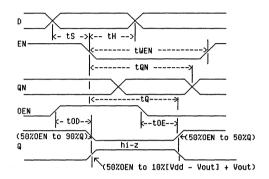

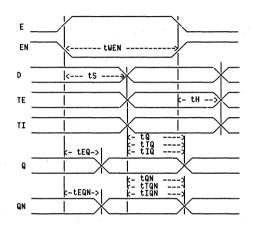

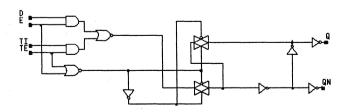

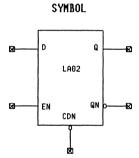

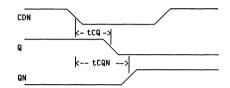

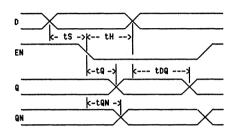

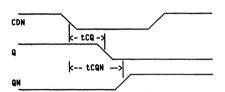

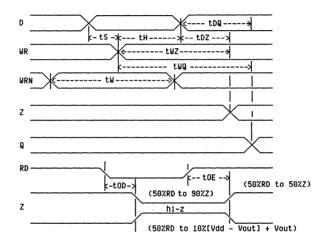

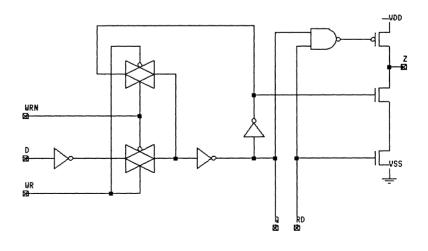

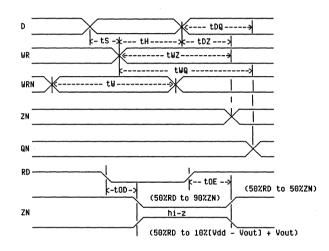

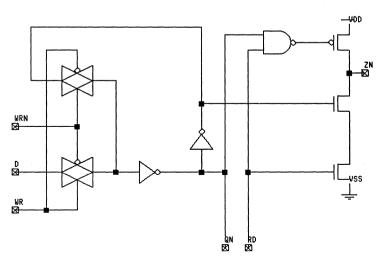

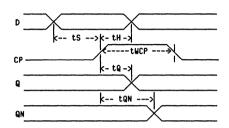

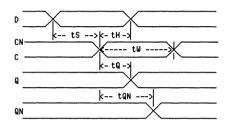

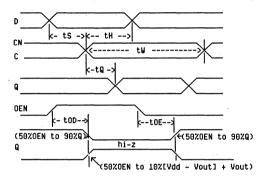

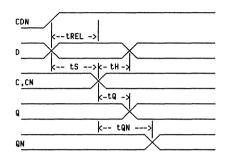

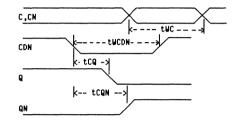

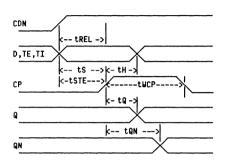

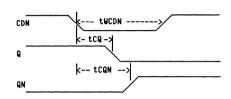

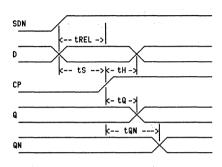

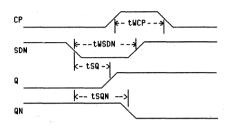

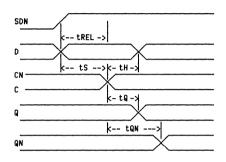

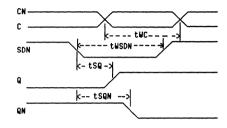

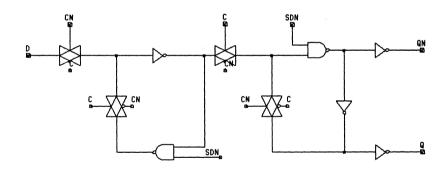

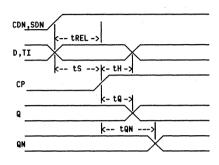

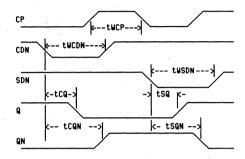

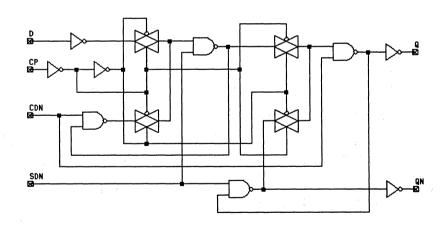

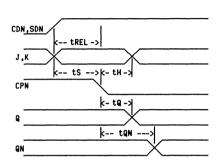

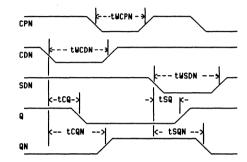

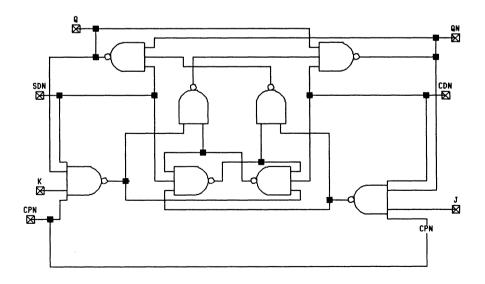

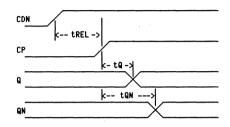

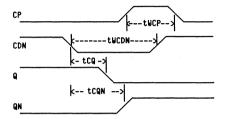

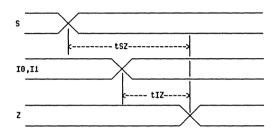

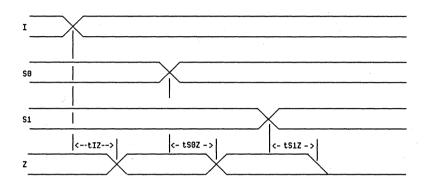

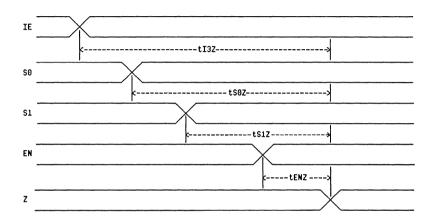

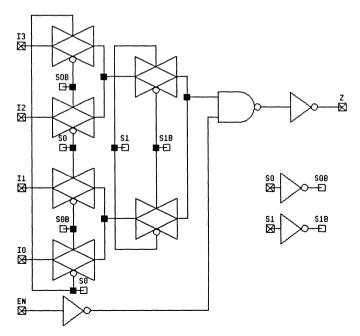

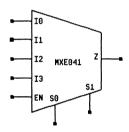

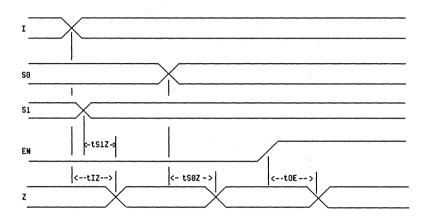

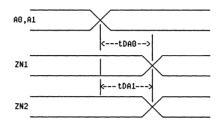

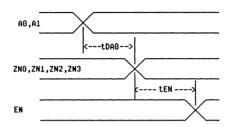

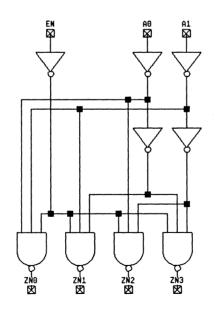

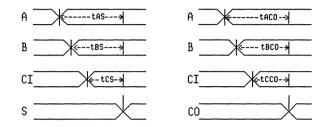

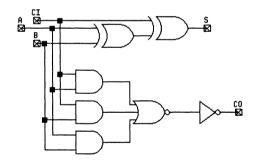

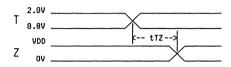

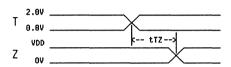

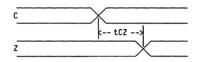

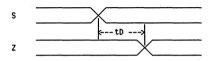

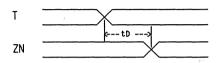

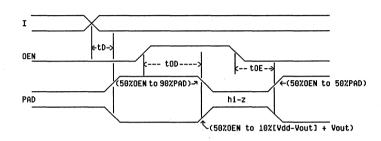

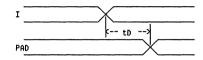

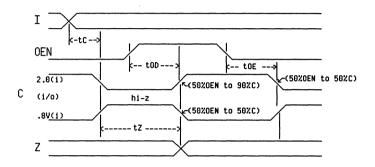

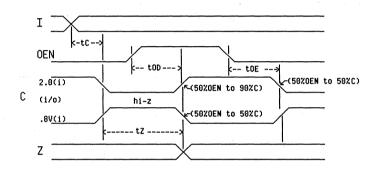

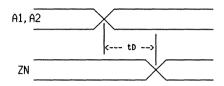

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Timing Diagrams and Definitions                | 77 |

|   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Estimating Propagation Delay Times             | 77 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | POWER DISSIPATION                              | 7' |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power Pins                                     | 77 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power Supply                                   | 78 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power Dissipation Calculation                  | 78 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MACRO PREPLACEMENT AND BONDING PAD ASSIGNMENTS | 80 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Macro PrePlacement Diagram                     | 8  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PrePlacement Procedure                         | 8  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |    |

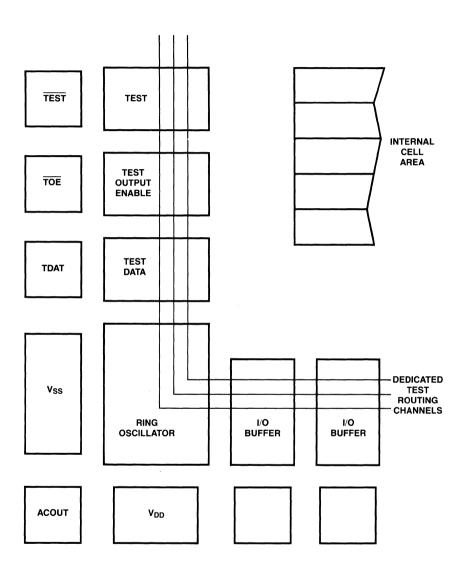

| 7 | TESTABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                | 83 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTRODUCTION                                   | 8  |

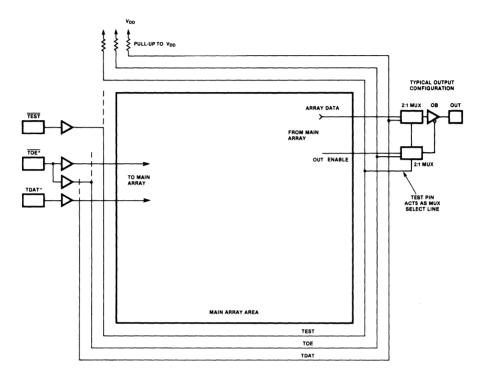

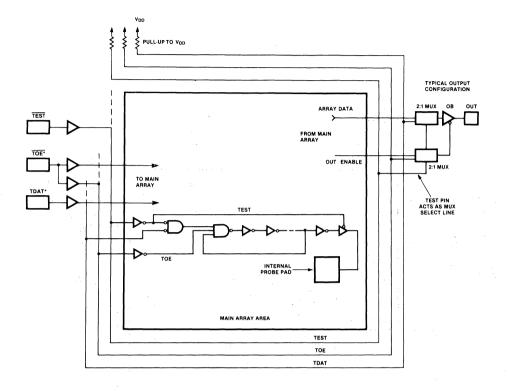

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STANDARD TESTING FEATURES                      | 8  |

|   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Output Buffer Parametric Tests                 | 8  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DC Functional Tests                            | 8  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AC Monitor Test                                | 8  |

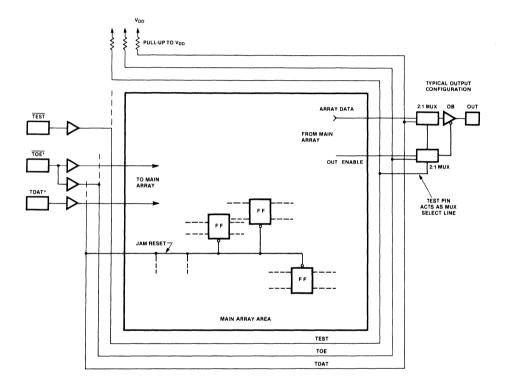

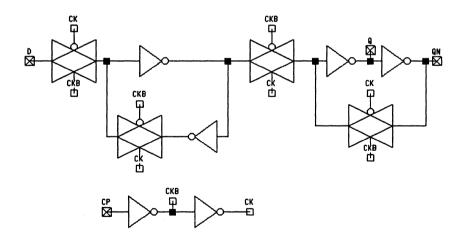

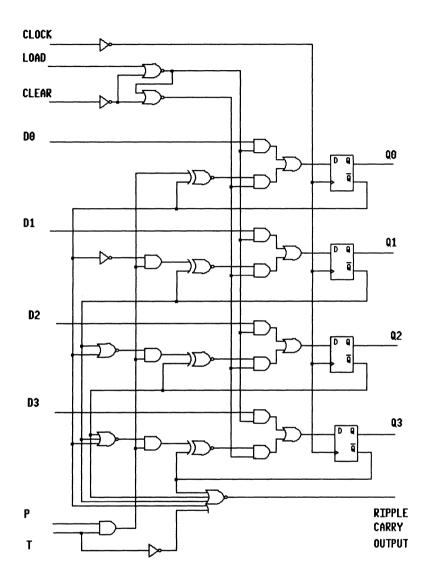

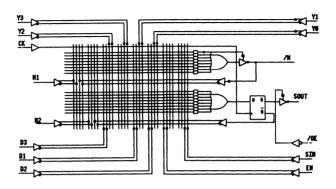

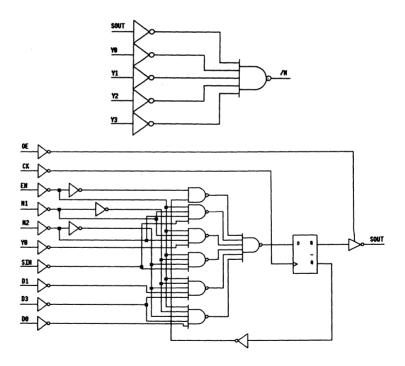

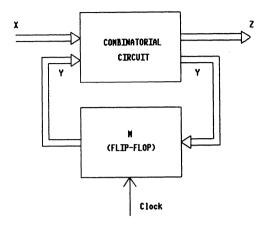

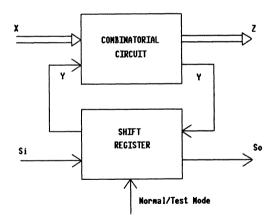

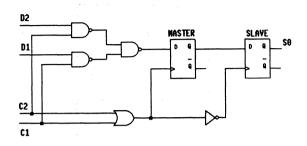

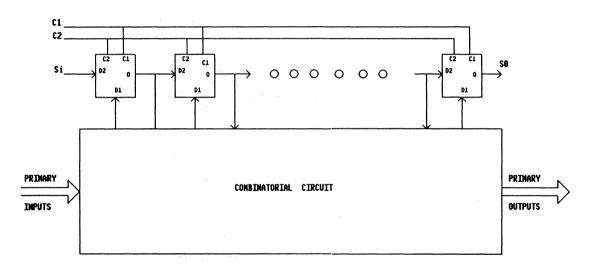

|   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LEVEL SENSITIVE SCAN DESIGN                    | 9  |

|   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Definition                                     | 9  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Operation                                      | 9  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Tests                                          | 9  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Summary                                        | 9  |

|   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |    |

$\mathbf{C}$

Application Note

393

#### CHAPTER 1

#### INTRODUCTION

# GENERAL INFORM-ATION

This manual provides the information necessary to prepare a design for implementation in any VTI VGC Series 2-micron CMOS gate array. VTI also offers classroom instruction covering this information. The VGC Series Design Manual consists of two parts:

- Part I (Chapters 1 9) contains the general information, design rules and procedures for design preparation prior to computer-aided design.

- Part II (Appendices) contains the VGC Series Macro Library, which

includes the individual specifications for each available macro. The

other appendices contain the VGC data sheets and an application

note. Refer to Chapter 4 for a detailed description of macro

specifications and their use.

logy

Unless otherwise noted, the terms "chip" and "array" in all descriptions and illustrations refer to the VGC gate array.

## The VGC Series

Figure 1-1 presents a brief comparison of the main elements of each array in the VGC Series. Refer to the section, **Features**, for a more detailed description of the VGC Series features.

# Additional Publica-

Where applicable, this manual refers to the VLSI Design System Reference Manual, a reference guide to the VTI's Computer-Aided Design system.

|                 | VGC0500 | ,0900 | 1200 | '1900 | '2400 | '3200 | '4000 | .6000 | ,8000 |

|-----------------|---------|-------|------|-------|-------|-------|-------|-------|-------|

| Internal Cells  | 360     | 576   | 792  | 1288  | 1728  | 2160  | 2640  | 4000  | 5264  |

| Equiv. Gates (1 | ) 540   | 864   | 1188 | 1932  | 2592  | 3240  | 3960  | 6000  | 7896  |

|                 |         |       |      |       |       |       |       |       |       |

| Pin Count:      |         |       |      |       |       |       |       |       |       |

| Input-only Cell | s 0     | 23    | 27   | 35    | 39    | 43    | 47    | 55    | 63    |

| I/O Cells       | 40      | 38    | 46   | 58    | 70    | 78    | 86    | 106   | 118   |

| Power Pins      | 4       | 4     | 8    | 8     | 8     | 8     | 8     | 8     | 16    |

| Testability Pin | s 0     | 3     | 3    | 3     | 3     | 3     | 3     | 3     | 3     |

| Total Pins      | 44      | 68    | 84   | 104   | 120   | 132   | 144   | 172   | 200   |

Note 1: An "equivalent gate" is one 2-input NAND gate.

Figure 1-1. VGC Series Summary

## FEAT-URES

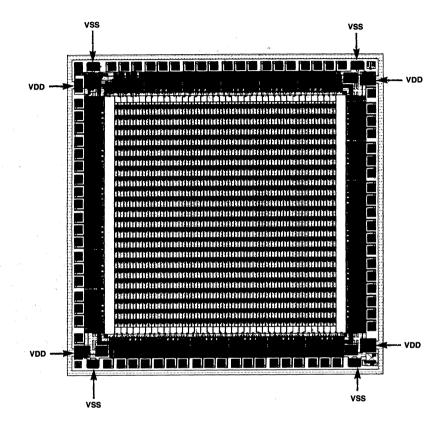

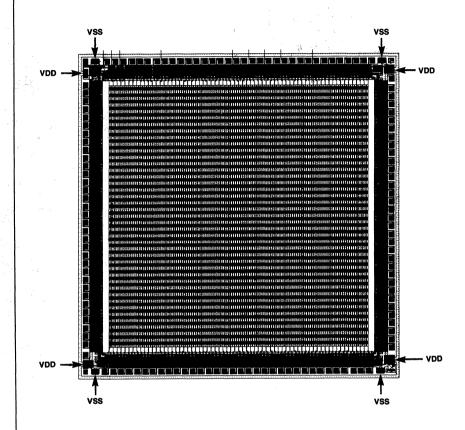

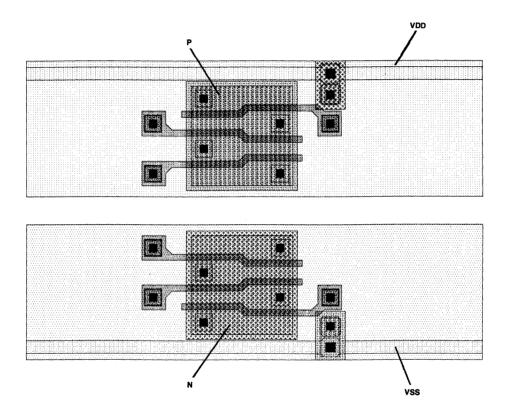

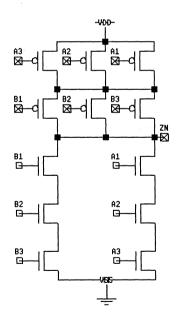

VGC Series gate arrays are fabricated with VTI's advanced 2-micron double-metal silicon gate CMOS technology. Each array consists of a mixture of functionally differentiated cell types (Internal, Input-only and I/O) and dedicated support structures such as power buses. The key features of the arrays are:

- 500 to 8000 equivalent gates

- True 2-micron Silicon Gate Geometries

- High Performance 1.1 ns typical gate delay

- 1.9 ns worst case gate delay (Commercial/Industrial)

- 2.0 ns worst case gate delay (Military)

- High output drive 8 mA for single-output buffer (10 mA for VGC0500)

- Low Power Dissipation 20 microWatts/gate/MHz

- Individually Selectable CMOS or TTL Inputs

- Single 5 V Power Supply

- On-chip Testability Features (Except on the VGC0500)

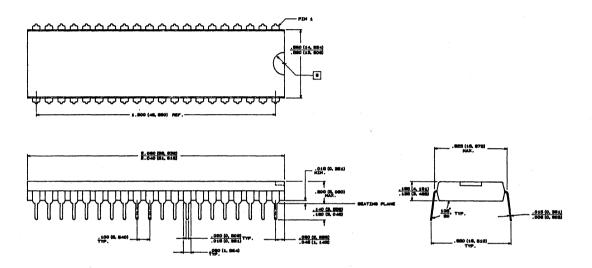

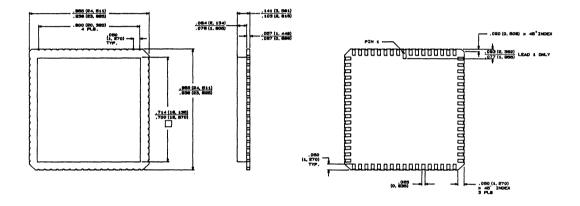

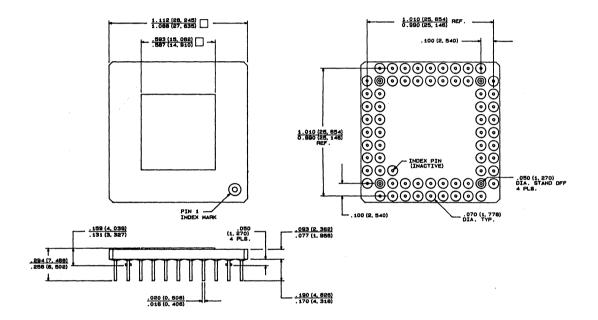

- Wide Choice of Package Pin-counts and Styles

- CAD Support on VAX\* and Apollo using VTI's proprietary design system

- CAD support on popular Daisy and Mentor engineering workstations

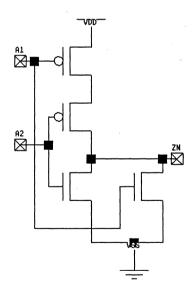

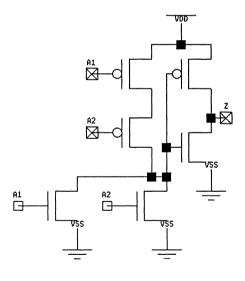

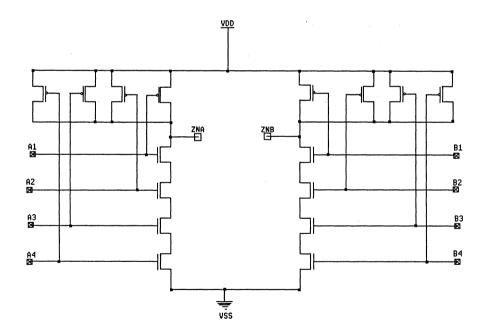

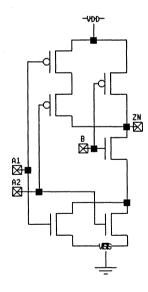

The transistors that make up the cells are diffused in standard patterns and interconnected using a combination of standard and special (user-selected) metal patterns. The standard metal patterns include power and ground buses, pads and the I/O cell control buses. The special metal patterns interconnect the transistors in one or more cells to form functional logic macros.

# VTI'S AD-VANCED CMOS TECHNO-LOGY

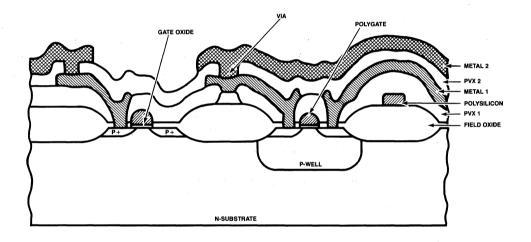

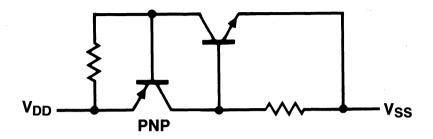

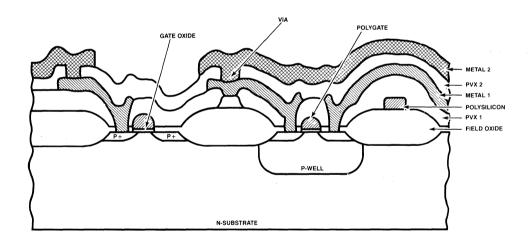

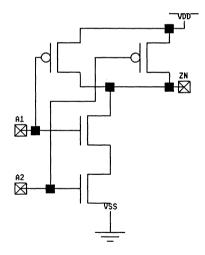

VTI'S advanced CMOS technology is a 2-micron CMOS process; the circuits use true 2-micron design rules. The bulk CMOS process uses p-wells and all devices are ion implanted. Oxide isolation between devices is employed and interconnections are made by two layers of metal. The process uses plasma etching for all etching steps.

Figure 1-2 shows a typical cross section of the process. Both p- and n-channel transistors are shown with their associated conductors, through which the CMOS structure is formed. The p- and n-channel device areas and substrate contacts are defined by the selectively grown field oxide shown between and on the left- and right-hand sides of the devices.

A single layer of n+ doped polysilicon conductors provide the common gate electrode for both devices. This gate, as well as source and drain implants, are contacted by first-layer metal (metal 1), which in turn connects to second-layer metal (metal 2) through vias in the inter-metal (SiO2) insulator.

The key design rules of the process are:

- 2-micron polysilicon gate width

- 2.5-micron x 2.5-micron first contact

- 3-micron x 3-micron via

- 6-micron metal I pitch

- 7-micron metal II pitch

Figure 1-2. VTI Advanced CMOS Cross Section

# **DESIGN-**ING A GATE **ARRAY OPTION**

A specific gate-array circuit design is called an "option". The option must first be defined in an objective specification, explained in the next section.

All aspects of option logic design, simulation, testing, placement, routing, checking and mask-tape generation are done on VTI's proprietary design system, which is described later in this chapter. Alternatively, logic design capture and simulation can be done on engineering workstations such as Gate array design kits for other engineering Daisy and Mentor. workstations will be available in the near future.

A brief description of fabrication and assembly is included in this chapter.

# **Objective** Specification

The first step in designing an option is to establish an objective This specification is the focal point of communication between the designer and VTI and will ultimately define the circuit to be produced. Chapter 6 provides information the gate array designer needs to prepare for the objective specification.

# Computer Aided Design With VTI's Design System

VTI's design system is an interactive CAD system that combines gate array design functions in a single system. It performs schematic capture, logic and timing simulation, test vector grading, macro placement and routing. The same basic system is used for all VTI's gate arrays. The system runs on VAX 11/780 and Apollo computers at VTI, provides local and remote access and works in the following manner:

#### Logic Schematic Entry

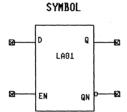

Initially, a logic design may be entered through an interactive graphics system. The user selects and places symbols representing library macros and interconnects them using a graphics terminal. (The VGC Series macro library is summarized in Chapter 4). The designer may also specify logic design by entering a netlist through an alphanumeric terminal.

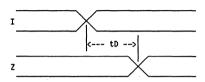

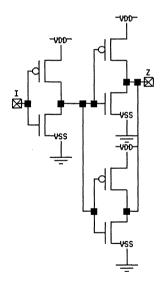

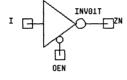

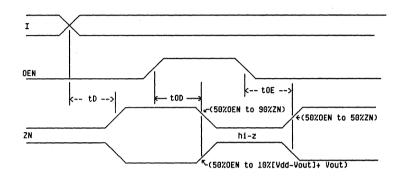

## Logic Simulation and Test Grading